**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

H01L 21/70

H01L 29/40

(21) 출원번호

특 1989-0008007

(22) 출원일자

1989년 06월 10일

(45) 공고일자

1992년 05월 30일

(11) 공고번호

92-0004179

(30) 우선권주장

63-141769 1988년 06월 10일 일본(JP)

(71) 출원인

가부시키가이샤 도시바

아오이 죠이치

일본국 가나가와현 가와사키시 사이와이구 호리가와정 72번지

(72) 발명자

다카쿠라 히로시

일본국 가나가와현 가와사키시 사이와이구 호리가와정 580번 1호 가부시

키가이샤 도시바 반도체시스템 기술센터내

이이다 데츠야

일본국 가나가와현 가와사키시 사이와이구 호리가와정 580번 1호 가부시

키가이샤 도시바 반도체시스템 기술센터내

고토 준케이

일본국 가나가와현 가와사키시 사이와이구 호리가와정 580번 1호 가부시

키가이샤 도시바 반도체시스템 기술센터내

(74) 대리인

김윤배

**심사관 : 조성록 (책자공보 제2787호)**

**(54) 반도체집적회로**

**요약**

내용 없음.

**대표도**

**도1**

**영세서**

[발명의 명칭]

반도체집적회로

[도면의 간단한 설명]

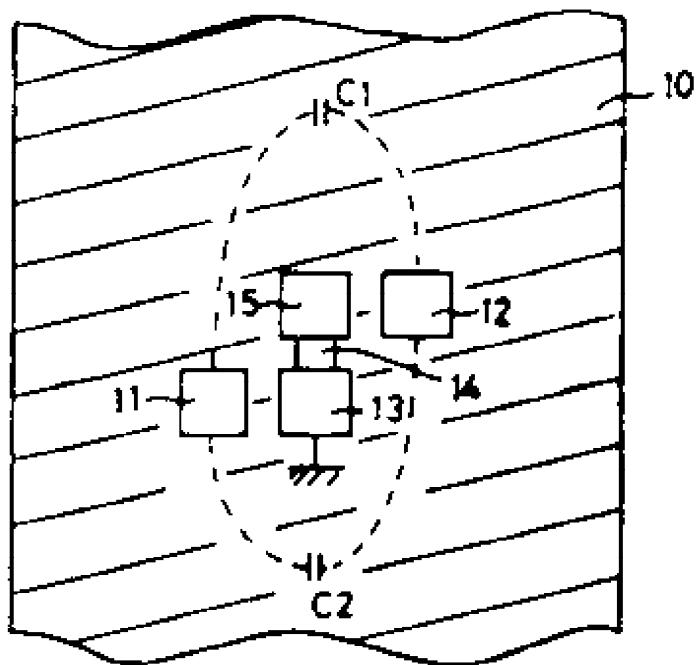

제 1 도는 본 발명에 따른 반도체집적회로의 개략적인 구성을 나타낸 단면도.

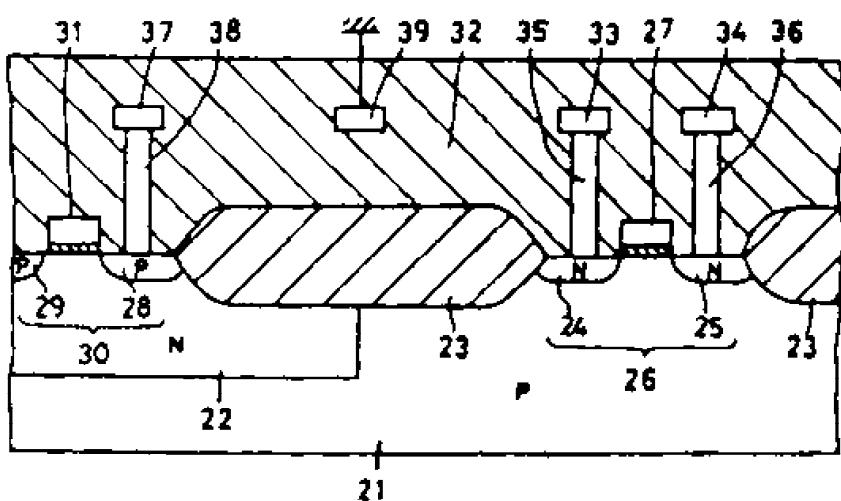

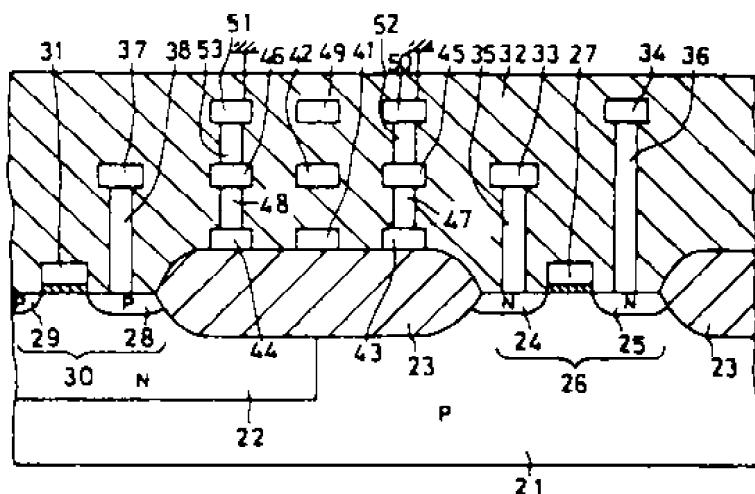

제 2 도는 본 발명에 따른 1실시예 장치의 단면도.

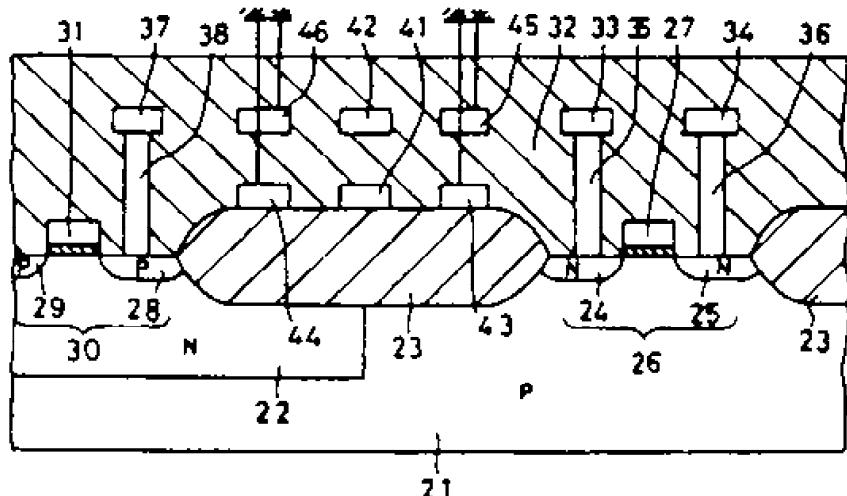

제 3 도는 본 발명에 따른 다른 실시예 장치의 단면도.

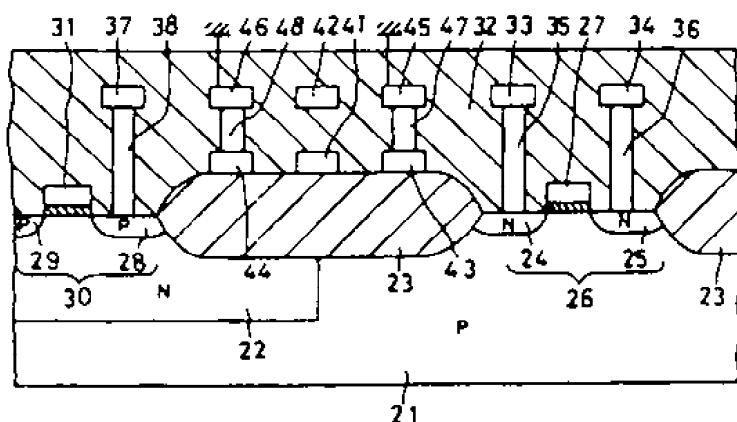

제 4 도는 반 발명에 따른 또 다른 실시예 장치의 단면도.

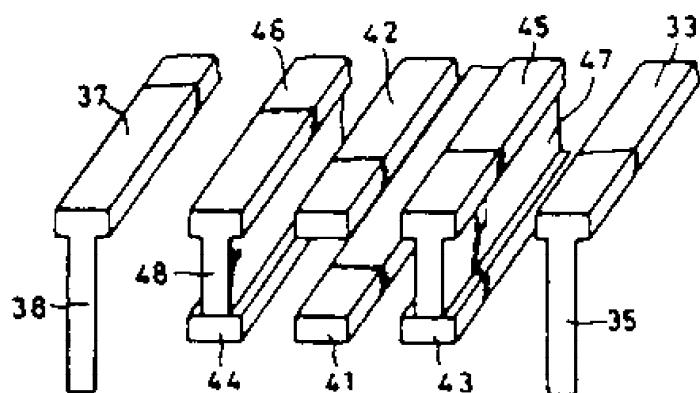

제 5 도는 제 4 도에 나타낸 실시예 장치의 일부를 발췌해서 나타낸 사시도.

제 6 도는 본 발명에 따른 또 다른 실시예 장치의 단면도.

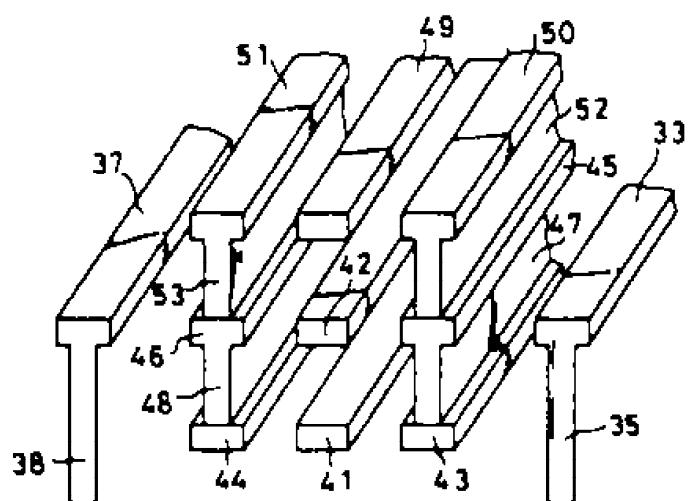

제 7 도는 제 6 도에 나타난 실시예 장치의 일부를 발췌해서 나타난 사시도.

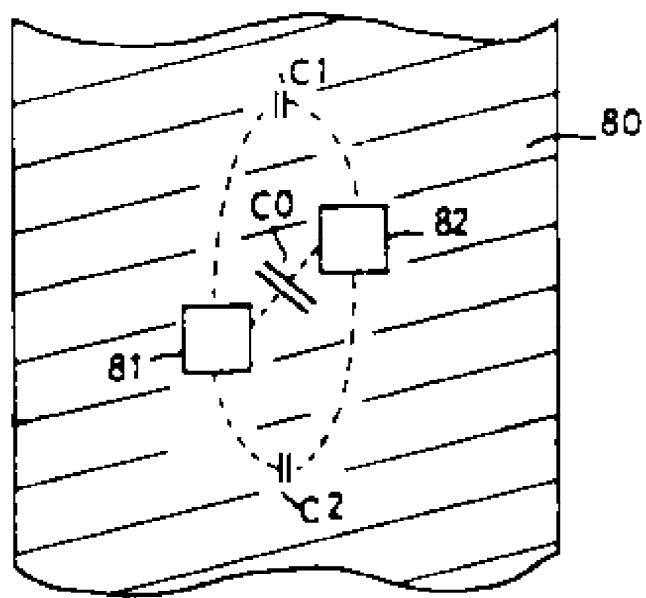

제 8 도는 종래장치의 개략적인 구성을 나타낸 단면도.

제 9 도는 종래장치에서의 신호파형도이다.

\* 도면의 주요부분에 대한 부호의 설명

C0, C1, C2 : 기생용량

14 : 접촉구멍

21 : 실리콘 반도체기판

22 : 웨이영역

23 : 필드산화막

24, 28 : 소오스영역

25, 29 : 드레인영역

26 : N채널 MOS트랜지스터

|                                                                 |                   |

|-----------------------------------------------------------------|-------------------|

| 27, 31 : 게이트전극                                                  | 30 : P챈널 MOS트랜지스터 |

| 32 : 총간절연막                                                      | 33, 37 : 소오스배선    |

| 34 : 드레인배선                                                      | 35, 38 : 소오스인출전극  |

| 36 : 드레인인출전극                                                    |                   |

| 11, 12, 13, 15, 39, 41, 42, 44, 45, 46, 49, 50, 51, 81, 82 : 배선 |                   |

| 47, 48, 52, 53 : 접속전극                                           | 10, 80 : 절연층      |

#### [발명의 상세한 설명]

#### [산업상의 이용분야]

본 발명은 배선상호간의 신호간섭을 방지하도록 된 반도체집적회로에 관한 것이다.

#### [종래의 기술 및 그 문제점]

최근 반도체집적회로에 대해 고집적화가 강력하게 요구되고 있는 바, 소자의 미세화기술과 다층배선화기술등이 진보됨에 따라 그 집적도는 더욱 증가되고 있고, 또는 소자의 미세화기술에 따른 배선폭 및 배선상호간의 거리의 축소화에 따라 종래에는 거의 문제로 되지 않았던 배선간의 신호간섭에 의해 정확한 신호전달이 곤란하게 되었다.

제 8 도는 종래의 반도체집적회로의 개략적인 구성을 나타낸 단면도로서, 도면중 절연층(80)내에는 제 1 층째의 도전체층으로 구성된 배선(81)와 제 2 층째의 도전체층으로 구성된 배선(82)이 배치되어 있고, 상기 양 배선(81, 82)의 상호간에는 기생적으로 용량(C0, C1, C2)이 발생되어 있다.

그중 상기 용량(C0)은 상기 양 배선(81, 82)을 연결하는 최단의 거리간에서 발생하고 있고, 상기 용량(C1, C2)은 각각 상기 양 배선(81, 82)간의 양측으로부터 타원형태로 발생되는데, 통상적으로 상기 용량값사이에는  $C0 > C1, C2$ 로 되는 관계가 성립한다.

여기서 상기 양 배선(81, 82)간에는 각각 다른 신호 또는 전압이 전달되는 바, 예컨대 상기 한쪽의 배선(81)에는 제 9 도에 나타낸 파형도(a)와 같은 아날로그신호가 전달되고, 다른 쪽의 배선(82)에는 제 9 도에 나타낸 파형도(b)와 같은 디지털신호가 전달되는 경우, 상기 기생용량(C0, C1, C2)을 통해 신호간섭이 발생하게 됨으로써 아날로그신호는 디지털신호의 영향을 받게 되어 제 9c 도에 나타낸 바와 같이 왜곡이 발생하게 된다.

이 결과 배선(81)에서는 정확한 아날로그신호를 전달할 수 없게 된다. 또 미세화 및 다층화된 배선 구조를 갖춘 반도체집적회로에서는 주위 배선과의 신호간섭의 기회가 많아지게 되어 정확한 신호전달이 더욱 곤란하게 된다.

상기한 바와 같이 종래에는 소자의 미세화 및 다층배선화에 따라 배선상호간에서 신호간섭이 증대함으로써 정확한 신호전달이 곤란하게 되는 결점이 있었다.

#### [발명의 목적]

본 발명은 상기한 점을 감안해서 발명된 것으로, 소자의 미세화 및 다층배선화를 도모해도 배선상호간에서 신호간섭의 증대가 방지되어 정확하게 신호를 전달할 수 있도록 된 반도체집적회로를 제공하는데 그목적이 있다.

#### [발명의 구성]

상기 목적을 달성하기 위한 본발명은 반도체기판과, 이 기판상에 형성된 절연층, 이 절연층내에 형성되어 각각 서로다른 신호를 전달하는 배선으로 사용되는 다층구조의 복수의 제 1 도전체층 및, 이 복수의 제 1 도전체층 인접하는 2개의 제 1 도전체층의 상호간에 설치되며 일정전위로 고정된 신호간섭방지용의 제 2 도전체층을 구비하여 구성된 것을 특징으로 한다.

#### [작용]

상기와 같이 구성된 본 발명은, 서로다른 신호를 전달하는 배선으로 사용되는 복수의 제 1 도전체층 인접한 2개의 제 1 도전체층의 상호간에 발생되는 기생적인 용량의 값이 충분하게 작아지게 되어 양 배선간의 신호간섭이 감소하게 된다.

#### [실시예]

이하 예시도면에 의거해서 본 발명에 따른 각 실시예를 상세히 설명한다.

제 1 도는 본 발명에 따른 반도체집적회로의 개략적인 구성을 나타낸 단면도로서, 도면중 절연층(10)내에는 제 1 층째의 도전체층에 의해 배선(11)이 구성되고, 제 2 층째의 도전체층에 의해 배선(12)이 각각 구성되며, 상기 양 배선(11, 12)상호간에는 제 1 층째의 도전체층에 의해 구성되는(13)과 제 2 층째의 도전체층에 의해 구성되는 접촉구멍(14)을 매개해서 상기 배선(13)와 전기적으로 접속된 배선(15)이 배치되어 있다. 그리고 상기 양 배선(13, 15)은 일정전위, 예컨대, 접지전위와 더불어 전원전위로 고정되어 있다.

이와 같이 각각 서로다른 신호가 전달되는 배선(11)과 배선(12)간에 일정전위로 고정된 배선을 배치시킴으로써 상기 제 8 도중의 기생용량(C0)에 대등한 용량은 발생하지 않고, 용량(C1, C2)만이 기생용량으로서 발생하게 된다.

그러나 상기 한 바와 같이 통상  $C0 > C1, C2$ 라는 관계가 성립해서 용량(C1, C2)이 충분하게 작은 값으로 되기 때문에 용량(C1, C2)만을 개재시키는 것에 의해 배선(11, 12)간에 발생하는 신호간섭도

충분하게 작게 할 수 있게 된다.

다음에 본 발명의 여러 종류의 실시예의 이용해서 설명한다.

제 2 도는 본 발명의 1층배선구조의 CMOS형 반도체집적회로에다 실시한 경우의 일부분의 소자구조를 나타낸 단면도로서, 도면중 참조부호 21은 P형실리콘반도체기판, 22는 상기 기판(21)내에 형성된 N형웰 영역, 23은 소자분리용의 필드산화막, 24 및 25는 상기 기판(21)의 표면영역에 형성된 N형 확산영역으로 이루어진 N챈널 MOS트랜지스터(30)의 소오스와 드레인영역, 역, 31은 예컨대 다결정실리콘으로 구성된 P챈널 MOS트랜지스터(30)의 게이트전극, 32은 기판표면상에 설치된 BPSG(보론, 인, 실리콘유리)막 또는 PSG(인, 실리콘유리)막등으로 이루어진 층간절영막, 33은 예컨대 알루미늄 등의 금속을 이용해서 상기 층간절연막(32)내에 형성시킨 N챈널 MOS트랜지스터(26)의 소오스배선, 34는 마찬가지로 예컨대 알루미늄등의 금속을 이용해서 상기 층간절연막(32)내에 형성시킨 상기 N챈널 MOS트랜지스터(26)의 드레인 배선, 35는 상기 소오스배선(33)과 동일한 도전체재료인 알루미늄 등의 금속을 이용해서 구성되어 상기 소오스배선(33)과 소오스영역(24)을 접속시키는 소오스인출전극, 36은 상기 드레인배선(34)과 동일한 도전체재료인 알루미늄 등의 금속의 이용해서 구성되어 상기 드레인배선(34)과 드레인영역(25)을 접속시키는 드레인인출전극, 37은 예컨대 알루미늄 등의 금속을 이용해서 상기 층간절연막(32)내에 형성시킨 P챈널 MOS트랜지스터(30)의 소오스배선, 38은 상기 소오스배선(37)과 동일한 도전체재료인 알루미늄 등의 금속을 이용해서 구성되어 상기 P챈널 MOS트랜지스터(30)측의 소오스배선(37)과 소오스영역 (28)을 접속시키는 소오스인출전극이다.

그리고 상기 층간절연막(32)내의 상기 양 배선(33, 37)상호간에는 예컨대 알루미늄같은 금속으로 구성되어 일정전위, 예컨대 접지전위로 고정된 배선(38)이 형성되어 있다.

한편 상기 제 2 도에서는 P챈널 MOS트랜지스터(30)측의 드레인배선과 드레인인출전극의 도시를 생략하였다.

본 실시예에 따른 집적회로에서 상기 제 1 도중의 배선(11)에 대응하는 배선은 예컨대 N챈널 MOS트랜지스터(26)측의 소오스배선(33)이고, 상기 제 1 도중의 배선(12)에 대응하는 배선은 예컨대 P챈널 MOS트랜지스터(30)측의 소오스배선(37)이며, 또 상기 제 1 도중의 배선(13)또는 배선(15)에 대응하는 배선은 양 소오스배선(33, 37)상호간에 배치된 배선(39)이다.

상기와 같은 구성에 있어서, 양 소오스배선(33, 37)상호간에 배치된 배선 (39)이 접지전위로 고정되어 있기 때문에 상기 양 소오스배선(33, 37)에 각각 다른 신호가 전달되어도 배선(39)이 존재함으로써 양 배선(33, 37)간에 발생하는 기생용량의 값이 작아지게 된다. 이 결과 배선의 미세화에 따라 각 배선상호간의 거리가 축소되어도 양 소오스배선(33, 37)상호간에서 신호간섭의 발생을 충분하게 작게 할 수 있으므로 정확하게 신호를 전달할 수 있게 된다.

제 3 도는 본 발명을 2층배선구조의 CMOS형 반도체집적회로에다 실시한 경우의 일부분의 소자구조를 나타낸 단면도로서, 제 2 도와 대응하는 장소에는 동일한 참조부호를 붙이고 그에 대한 상세한 설명은 생략한다.

본 실시예에 따른 집적회로에서는 상기 필드산화막(23)에 예컨대 알루미늄 등의 금속으로 구성된 배선(41)이 추가되어 있고, 또 층간절연막(32)내에 상기 배선(41)의 상부에 대응하는 위치에 예컨대 알루미늄 등의 금속을 이용해서 구성된 배선(42)이 추가 되어 있는데, 상기 양 배선(41, 42)은 각각 도시되지 않는 다른 회로끼리를 접속시키기 위한 배선으로서 사용되고 있다. 그리고 상기 배선(41)과 상기 N챈널 MOS트랜지스터(26)측의 소오스인출전극 (35)간의 필드산화막(23)상에는 상기 배선(41)과 동일한 도전체재료인 알루미늄 등의 금속으로 구성된 배선(43)이 추가 되어 있고 상기 배선(41)과 상기 P챈널 MOS트랜지스터(30)측의 소오스인출전극(28)간의 필드산화막(23) 상에도 상기 배선(41)과 동일한 도전체재료인 알루미늄 등의 금속으로 구성된 배선(44)이 추가 되어 있다. 또는 층간절연막(32)내에는 상기 배선(42)과 상기 N챈널 MOS트랜지스터(26)측의 소오스배선(33)간에 상기 배선(42)과 동일한 층이면서 동일한 도전체재료인 알루미늄 등의 금속으로 구성된 배선(45)이 추가되어 있고, 상기 배선(42)와 상기 P챈널 MOS트랜지스터(30)측의 소오스배선(37)간에도 알루미늄 등의 금속으로 구성된 배선(46)이 추가되어 있다. 그리고 상기 각 배선(43, 44, 45, 46)은 각각 독립적으로 도시되지 않는 장소에 일정전위, 예컨대 접지전위로 고정되어 있다.

상기 실시예에 따른 집적회로에서는 배선(42)과 소오스배선(33)상호간에 접지전위로 고정된 배선 (45)이 배치되어 있고, 배선(42)과 소오스배선(37) 상호 간에 접지전위로 고정된 배선(46)이 각각 배치되어 있기 때문에 양 소오스배선(33, 37)와 배선(42)에 따른 신호가 전달되어도 신호의 상호간섭의 발생을 충분히 작게 할 수 있으므로 정확하게 신호를 전달할 수 있게 된다.

또 상기 실시예에서는 배선(41)와 소오스인출전극(35)상호간에도 접지전위로 고정된 배선(43)이 배치되어 있고, 배선(41)과 소오스인출전극(38) 상호간에도 접지전위로 고정된 배선(44)이 각각 배치되어 있기 때문에 배선(41)와 소오스인출전극(35)간의 신호간섭 및, 배선(41)와 소오스 인출전극(38)간의 신호간섭도 각각 충분히 작게 할 수 있게 된다.

제 4 도는 본 발명의 상기 제 3 도의 경우와 동일한 2층배선구조의 CMOS형 반도체집적회로에다 실시한 경우의 일부분의 소자구조를 나타낸 단면도로서, 제 3 도와 대응하는 장소에는 동일한 참조부호를 붙이고 그에 대한 상세한 설명은 생략한다.

본 실시예에 따른 집적회로에서는 상기 제 3 도중 필드산화막(23)상에 형성된 상기 배선(43)과 층간절연막(32)내에 형성된 배선(45)이 층간절연막(32)에 형성된 관통구멍을 메우도록 설치되는데, 예컨대, 배선(45)과 동일한 도전체재료인 알루미늄 등의 금속으로 구성된 접속전극(47)을 이용해서 전기적으로 접속시킨다. 또 상기 필드산화막(23)상에 형성된 상기 배선(44)과 층간절연막(32)내에 형성된 상기 배선(46)이 층간절연막(32)에 형성된 관통구멍을 메우도록 설치되는데, 예컨대 배선(46)과 동일한 도전체재료인 알루미늄등의 금속으로 구성된 접속전극(48)을 이용해서 전기적으로 접속시키도록 구성된다.

제 5 도는 상기 제 4 도에 나타낸 실시예장치로부터 소오스배선(33, 37)과 소오스인출전극(35, 38), 배선(41, 42), 배선(43, 44) 및 접속전극(47, 48)을 골라서 나타낸 사시도로서, 도시한 바와 같이 접속전극(47, 48)을 이용해서 접속된 재선(43, 45) 및 배선(44, 46)은 평면적으로 그 양측에 배치된 소오스배선(33, 37)와 배선(41, 42)각각의 연장방향에 따라 벽상(壁狀)으로 형성되어, 소오스배선 전극(33, 37)과 배선(41, 42)을 각각 분리하고 있다.

상기한 바와 같이 배선이 다층화된 집적회로에서는 일정전위로 고정된 각각 다른 층의 배선을 접속전극을 이용해서 전기적으로 접속시키고, 이들의 배선을 벽상으로 구성시킴으로써 신호가 타원형태로 발생되는 것을 방지하는 효과가 향상되어 그양측에 배치된 배선상호간의 신호간섭의 발생을 역시 작게 할 수 있게 된다.

제 6 도는 본 발명을 3층배선구조의 CMOS형 반도체집적회로에다 실시한 경우의 일부분의 소자구조를 나타낸 단면도로서, 상기 제 4 도와 대응하는 장소에는 동일한 참조부호를 붙이고 그에 대한 상세한 설명은 생략한다.

본 실시예에 따른 집적회로에서는, 상지 배선(41, 43, 44)을 제 1 층째의 예컨대 알루미늄등으로 이루어진 금속을 이용해서 구성하고, 상기 배선(42, 45, 46)을 제 2 층째의 예컨대 알루미늄등으로 이루어진 금속을 이용해서 구성되면서 층간절연막(32)내에 새로운 제3층째의 예컨대 알루미늄등으로 이루어진 금속을 이용해서 구성된 배선(49, 50, 51)을 설치하도록 한 것이다. 그리고 상기 배선(49, 50, 51)중 배선(49)은 상기 배선(41, 42)과 마찬가지로 도시되지 않는 다른 회로끼리 접속시키기 위한 배선으로 사용되고, 또는 배선(50, 51)은 신호간섭방지용의 배선으로서 사용된다. 상기 배선(50)와 상기 배선(45)은 예컨대 배선(50)과 동일한 도전체재료인 알루미늄 등의 금속으로 구성되고, 층간절연막(32)에 형성된 관통구멍의 메우도록 설치한 접속전극(52)을 이용해서 전기적으로 접속되어 있다. 마찬가지로 배선(51)과 상기 배선(46)은 예컨대 배선(51)과 동일한 도전체재료인 알루미늄 등의 금속으로 구성되고, 층간 절연막 (32)에 형성된 관통구멍을 메우도록 설치된 접속전극(52)을 이용해서 전기적으로 접속되어 있다.

제 7 도는 상기 제 6 도에 나타낸 실시예장치로부터 소오스배선(33, 37)과 소오스인출전극(35, 38), 배선(41, 42, 43, 44, 45, 46, 49, 50, 51) 및 접속전극(47, 48, 52, 53)을 골라서 나타낸 사시도로서, 동시한 바와 같이 접속전극(47, 52)과 접속전극(48, 53)을 이용해서 각각 접속된 3층의 배선(43, 45, 50) 및 배선(44, 46, 51)은 평면적으로 그양측에 배치된 소오스배선 (33, 37) 및 배선(41, 42, 49)각각의 연장방향에 따라 벽상으로 형성되고, 소오스배선(33, 37)와 배선(41, 42, 49)을 각각 분리하고 있다.

상기와 같은 3층배선구조의 집적회로에서는 소자의 미세화에 따라 배선 상호간의 거리가 축소되면 동일층의 배선상호간 뿐만 아니라 다른 층의 배선상호간의 신호간섭도 문제로 된다. 그러나 일정전위로 고정된 각각 다른 층의 배선을 접속전극을 이용해서 접속시켜 벽상으로 구성시킴으로써 신호가 타원 형태로 발생되는 것을 방지하는 효과가 향상되어, 그 양측에 배치된 배선상호간의 신호간섭의 발생을 극도로 작게할 수 있게 됨에 따라 각 배선에 정확한 신호를 전달할 수 있게 된다.

또 본 발명은 상기 각 실시예에 한정되지 않고 여러 가지로 변형해서 실시할 수 있는 바, 예컨대 상기 각 실시예에서는 본발명을 CMOS형 반도체집적회로에다 실시하면서 소오스배선끼리 또는 소오스배선과 다른 배선간의 신호간섭방지를 도모한 경우에 대해서만 설명했지만, 이것은 신호간섭이 문제로 되는 반도체집적회로내의 모든 배선에 대해 실시할 수 있다. 또 신호간섭방지용의 배선은 접지전위로 고정하는 경우에 대해서만 설명했지만, 이것은 일정전위이면 어떠한 전위로 고정해도 되고, 또는 신호간섭방지용의 배선의 전위를 여러 가지 값으로 설정해도 된다.

#### [발명의 효과]

상기한 바와 같이 본 발명에 의하면, 소자의 미세화 및 다층배선화를 도모해도 배선상호간에서 신호간섭의 증대가 방지될 수 있어서 정확한 신호를 전달할 수 있는 반도체집적회로를 제공할 수 있게 된다.

#### (57) 청구의 범위

##### 청구항 1

반도체기판(21)와, 이 기판(21)상에 형성된 절연층(32), 이 절연층(32)내에 형성되어 각각 서로다른 신호를 전달하는 배선으로 사용되는 다층구조의 복수의 제 1 도전체층(33, 37) 및, 이 복수의 제 1 도전체층중 인접하는 2개의 제 1 도전체층(33, 37)의 상호간에 설치되며 일정전위로 고정된 신호간섭방지용의 제 2 도전체층(39)을 구비해서 구성된 것을 특징으로 하는 반도체집적회로.

##### 청구항 2

제 1 항에 있어서, 상지 제 2 도전체층(39)이 상기 절연층(32)내에 형성된 적어도 2층 이상의 도전체층(44, 46)으로 대체되어 구성된 것을 특징으로 하는 반도체집적회로.

##### 청구항 3

제 2 항에 있어서, 상지 제 2 도전체층(39)에 대체되어 구성되는 적어도 2층이상의 도전체층(44, 46)이 상기 절연층(32)내에 형성된 제 3 도전체층(48)을 매개해서 전기적으로 접속되고, 상기 제 3 도전체층(48)이 상기 2개의 제 1 도전체층(33, 37)의 연장방향에 따라 상기 2개의 제 1 도전체층(33, 37)을 분리하도록 벽상으로 형성된 것을 특징으로 하는 반도체집적회로.

#### 도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9-a

도면9-b

도면9-c