(12) 发明专利申请

(10) 申请公布号 CN 113687768 A

(43) 申请公布日 2021.11.23

(21) 申请号 202110277407.9

(22) 申请日 2021.03.15

(30) 优先权数据

10-2020-0059971 2020.05.19 KR

(71) 申请人 三星电子株式会社

地址 韩国京畿道

(72) 发明人 吴成一 孙钟弼 孙教民

(74) 专利代理机构 北京市立方律师事务所

11330

代理人 李娜 王凯霞

(51) Int.Cl.

G06F 3/06 (2006.01)

权利要求书4页 说明书12页 附图12页

(54) 发明名称

存储设备及其操作方法

(57) 摘要

一种包括根据不同字节序格式转换数据的接口电路的存储设备包括：接口电路，所述接口电路根据存储体、处理元件(PE)以及主机设备的字节序格式，利用硬件在位于所述存储设备内部的数据传输路径中执行数据转换。所述接口电路位于(i)存储器物理层接口(PHY)区域与串行器/解串器(SERDES)区域之间；(ii)所述SERDES区域与所述存储体或所述PE之间；(iii)所述SERDES区域与耦接到包括多个存储体的存储体组的存储体组输入/输出线之间；以及(iv)所述PE与耦接到所述存储体的存储体本地输入/输出线之间。

1.一种存储设备,包括:

存储体;

处理元件,所述处理元件耦接到所述存储体并被配置为执行计算处理;

串行器/解串器区域,所述串行器/解串器区域包括串行器/解串器,所述串行器/解串器被配置为执行将从所述存储设备外部的主机设备接收到的串行数据流并行化的操作,以及将从所述存储体或所述处理元件输出的并行数据流串行化的操作;以及

接口电路,所述接口电路包括与所述存储体、所述处理元件和所述串行器/解串器有关的数据传输路径,并且被配置为使得所述存储设备能够基于根据所述主机设备的字节序格式设置的控制信号在所述数据传输路径中执行数据转换。

2.根据权利要求1所述的存储设备,其中,所述接口电路包括:

第一输入数据总线,所述第一输入数据总线被配置为接收第一字节;

第二输入数据总线,所述第二输入数据总线被配置为接收第二字节;

控制信号线,所述控制信号线被配置为接收所述控制信号;

第一输出数据总线;

第二输出数据总线;以及

数据总线转换器,所述数据总线转换器连接到所述第一输入数据总线和所述第二输入数据总线、所述控制信号线以及所述第一输出数据总线和所述第二输出数据总线,

其中,所述数据总线转换器被配置为响应于所述控制信号的第一逻辑状态,将所述第一输入数据总线的所述第一字节传递给所述第一输出数据总线,以及将所述第二输入数据总线的所述第二字节传递给所述第二输出数据总线,并响应于所述控制信号的与所述第一逻辑状态相反的第二逻辑状态,将所述第一输入数据总线的所述第一字节重新配置并传输到所述第二输出数据总线,以及将所述第二输入数据总线的所述第二字节重新配置并传输到所述第一输出数据总线。

3.根据权利要求2所述的存储器设备,还包括存储器物理层接口区域,所述存储器物理层接口区域被配置为与所述主机设备通信,

其中,所述接口电路设置在所述存储器物理层接口区域与所述串行器/解串器区域之间,并且被配置为使得:

当从所述主机设备向所述存储设备输入数据时,所述第一输入数据总线和所述第二输入数据总线耦接到所述存储器物理层接口区域,而所述第一输出数据总线和所述第二输出数据总线耦接到所述串行器/解串器区域,并且

当从所述存储设备向所述主机设备输出所述数据时,所述第一输入数据总线和所述第二输入数据总线耦接到所述串行器/解串器区域,而所述第一输出数据总线和所述第二输出数据总线耦接到所述存储器物理层接口区域。

4.根据权利要求2所述的存储设备,其中,所述接口电路位于所述串行器/解串器区域与所述存储体或所述处理元件之间,并且被配置为使得:

当从所述主机设备向所述存储设备输入数据时,所述第一输入数据总线和所述第二输入数据总线耦接到所述串行器/解串器区域,而所述第一输出数据总线和所述第二输出数据总线耦接到所述存储体或所述处理元件,并且

当从所述存储设备向所述主机设备输出所述数据时,所述第一输入数据总线和所述第

二输入数据总线耦接到所述存储体或所述处理元件，而所述第一输出数据总线和所述第二输出数据总线耦接到所述串行器/解串器区域。

5. 根据权利要求2所述的存储设备，还包括：

存储体组，所述存储体组包括多个存储体；

存储体组输入/输出线，所述存储体组输入/输出线耦接到所述存储体组，以在所述存储设备外部的所述主机设备与所述存储体组之间传输数据；

第一存储体本地输入/输出线，所述第一存储体本地输入/输出线耦接到第一存储体，并被配置为传输提供给所述第一存储体的数据和从所述第一存储体读取的数据；以及

第二存储体本地输入/输出线，所述第二存储体本地输入/输出线耦接到第二存储体，并被配置为传输提供给所述第二存储体的数据和从所述第二存储体读取的数据。

6. 根据权利要求5所述的存储设备，其中，所述处理元件由所述第一存储体和所述第二存储体共享，

其中，所述接口电路位于所述串行器/解串器区域与所述存储体组输入/输出线之间，并被配置为：

当从所述主机设备向所述存储设备输入数据时，所述第一输入数据总线和所述第二输入数据总线耦接到所述串行器/解串器区域，而所述第一输出数据总线和所述第二输出数据总线耦接到所述存储体组输入/输出线，并且

当从所述存储设备向所述主机设备输出所述数据时，所述第一输入数据总线和所述第二输入数据总线耦接到所述存储体组输入/输出线，而所述第一输出数据总线和所述第二输出数据总线耦接到所述串行器/解串器区域。

7. 根据权利要求5所述的存储设备，还包括：

第一处理元件，所述第一处理元件耦接到所述第一存储体；以及

第二处理元件，所述第二处理元件耦接到所述第二存储体，

其中，所述接口电路位于所述第一处理元件与所述第一存储体本地输入/输出线之间以及所述第二处理元件与所述第二存储体本地输入/输出线之间，并且被配置为使得：

当从所述主机设备向所述存储设备输入数据时，所述第一输入数据总线和所述第二输入数据总线分别耦接到所述第一处理元件和所述第二处理元件，而所述第一输出数据总线和所述第二输出数据总线分别耦接到所述第一存储体本地输入/输出线和所述第二存储体本地输入/输出线，并且

当从所述存储设备向所述主机设备输出所述数据时，所述第一输入数据总线和所述第二输入数据总线分别耦接到所述第一存储体本地输入/输出线和所述第二存储体本地输入/输出线，而所述第一输出数据总线和所述第二输出数据总线分别耦接到所述第一处理元件和所述第二处理元件。

8. 根据权利要求1所述的存储设备，其中，所述控制信号在所述存储设备的模式寄存器组中被提供，或者根据所述存储设备内部的非易失性存储器件的状态被提供。

9. 根据权利要求1所述的存储设备，其中，所述存储设备是高带宽存储器，并且还包括：

缓冲器裸片，所述缓冲器裸片包括所述串行器/解串器区域；以及

动态随机存取存储器裸片，所述动态随机存取存储器裸片包括所述存储体和所述处理元件。

10. 一种存储设备,包括:

存储体;

串行器/解串器区域,所述串行器/解串器区域包括串行器/解串器,所述串行器/解串器被配置为执行将从所述存储设备外部的主机设备接收到的串行数据流并行化的操作,以及将从所述存储体输出的并行数据流串行化的操作;以及

接口电路,所述接口电路包括与所述存储体和所述串行器/解串器有关的数据传输路径,所述接口电路耦接到所述串行器/解串器区域,并且被配置为使得所述存储设备能够基于根据所述主机设备的字节序格式设置的控制信号在所述数据传输路径中执行数据转换。

11. 根据权利要求10所述的存储设备,其中,所述接口电路包括:

第一数据线,通过所述第一数据线传输第一字节序格式的第一数据位;

控制信号线,所述控制信号线被配置为接收所述控制信号;

第二数据线;以及

数据转换器,所述数据转换器连接到所述第一数据线、所述控制信号线和所述第二数据线,

其中,所述数据转换器被配置为响应于所述控制信号的第一逻辑状态,以所述第一字节序格式将所述第一数据线的所述第一数据位传递给所述第二数据线,并且响应于所述控制信号的与所述第一逻辑状态相反的第二逻辑状态,将所述第一数据线的所述第一数据位重新配置为与所述第一字节序格式不同的第二字节序格式,并将所述第一数据位传输到所述第二数据线。

12. 根据权利要求11所述的存储设备,还包括存储器物理层接口区域,所述存储器物理层接口区域被配置为与所述主机设备通信,

其中,所述接口电路位于存储器物理层接口区域与所述串行器/解串器区域之间,并且被配置为使得:

当从所述主机设备向所述存储设备输入数据时,所述第一数据线耦接到所述存储器物理层接口区域,所述第二数据线耦接到所述串行器/解串器区域,并且

当从所述存储设备向所述主机设备输出所述数据时,所述第一数据线耦接到所述串行器/解串器区域,所述第二数据线耦接到所述存储器物理层接口区域。

13. 根据权利要求11所述的存储设备,其中,所述接口电路位于所述串行器/解串器区域与所述存储体之间,并且被配置为使得:

当从所述主机设备向所述存储设备输入数据时,所述第一数据线耦接到所述串行器/解串器区域,所述第二数据线耦接到所述存储体,并且

当从所述存储设备向所述主机设备输出所述数据时,所述第一数据线耦接到所述存储体,所述第二数据线耦接到所述串行器/解串器区域。

14. 根据权利要求10所述的存储设备,其中,所述控制信号在所述存储设备的模式寄存器组中被提供,或者根据所述存储设备内部的非易失性存储器件的状态被提供。

15. 根据权利要求10所述的存储设备,其中,所述存储设备是还包括处理元件的双倍数据速率动态随机存取存储器,所述处理元件耦接到所述存储体并且被配置为执行计算处理。

16. 一种操作包括接口电路的存储设备的方法,所述接口电路被配置为调整主机设备

与所述存储设备之间的字节序格式,所述方法包括:

从所述主机设备接收第一字节序格式的串行数据流;

将所述串行数据流并行化为第一数据;以及

基于控制信号将所述串行数据流转换为所述存储设备的第二字节序格式,或将并行化的所述第一数据转换为所述第二字节序格式,该转换由所述接口电路执行。

17. 根据权利要求16所述的方法,还包括:

从存储体输出并行数据流;

将所述并行数据流串行化为第二数据;以及

将所述并行数据流转换为所述第一字节序格式,或将串行化的所述第二数据转换为所述第一字节序格式,该转换由所述接口电路执行。

18. 根据权利要求16所述的方法,还包括:将并行化的所述第一数据提供给存储体,或将并行化的所述第一数据提供给耦接到所述存储体的处理元件以执行计算处理。

19. 根据权利要求18所述的方法,其中,当所述接口电路耦接到与所述存储体或所述处理元件有关的数据传输路径时,执行将并行化的所述第一数据转换为所述第二字节序格式。

20. 根据权利要求16所述的方法,还包括:在所述存储设备的模式寄存器组中或根据所述存储设备内部的非易失性存储器件的状态来提供所述控制信号。

## 存储设备及其操作方法

[0001] 相关申请的交叉引用

[0002] 本申请要求于2020年5月19日在韩国知识产权局提交的韩国专利申请No. 10-2020-0059971的权益，其全部公开内容通过引用合并于此。

### 技术领域

[0003] 本发明构思涉及存储设备，更具体地，涉及包括根据字节序格式 (endian format) 进行数据转换的接口电路的存储设备。

### 背景技术

[0004] 诸如更高性能的应用和/或图形算法是数据密集型和/或计算密集型的。诸如神经网络的机器学习应用会包括大量运算，其具有大量的计算和存储需求。因此，机器学习应用需要具有大型计算和存储能力的计算系统，来更准确地训练或学习不同的数据集。为了执行作为内部处理的计算系统的某些计算操作，正在开发存储器中处理器 (PIM, processor-in-memory) 类型的处理器设备。通过存储设备的内部处理，可以减少计算系统的计算操作负荷。

[0005] 高带宽存储器 (HBM) 是用于3D堆叠动态随机存取存储器 (DRAM) 的高性能随机存取存储器 (RAM) 接口。HBM可以用于以存储器为中心的计算密集型神经网络或其他人工智能 (AI)。这是由于训练数据集大小的增加、模型参数的增加以及中间处理结果的增加。另外，HBM被配置为执行PIM功能，并且可以包括执行内部处理 (例如，诸如加法和乘法的算术计算以及诸如异或 (XOR) 的逻辑计算) 的处理元件 (PE)。

[0006] HBM可以基于来自使用HBM的主机的命令，通过数据总线来发送和接收数据。数据总线可以包括例如64位的总线，在数据总线上字节被视为原子单位 (atomic unit)，并且数据总线可以被划分为字节宽度的通道 (byte-wide lane)。然而，主机中数据总线使用的总线字节序可能与HBM使用的总线字节序不同。例如，主机可以使用大字节序 (big-endian) 总线，而HBM可以使用小字节序 (little-endian) 总线。

### 发明内容

[0007] 本发明构思为数据不变性提供了不同总线字节序格式之间的数据转换。

[0008] 本发明构思提供一种包括根据不同字节序格式进行数据转换的接口电路的存储设备。

[0009] 根据本发明构思的一方面，提供了一种存储设备，包括：存储体；处理元件 (PE)，所述PE耦接到所述存储体并被配置为执行计算处理；串行器/解串器 (SERDES) 区域，所述SERDES区域包括SERDES，所述SERDES被配置为执行将从所述存储设备外部的主机设备接收到的串行数据流并行化的操作，以及将从所述存储体或所述PE输出的并行数据流串行化的操作；以及接口电路，所述接口电路包括与所述存储体、所述PE和所述SERDES有关的数据传输路径，并且被配置为使得所述存储设备能够基于根据所述主机设备的字节序格式设置的

控制信号在所述数据传输路径中执行数据转换。

[0010] 根据本发明构思的另一方面，提供了一种存储设备，包括：存储体；串行器/解串器(SERDES)区域，所述SERDES区域包括SERDES，所述SERDES被配置为执行将从所述存储设备外部的主机设备接收到的串行数据流并行化的操作，以及将从所述存储体输出的并行数据流串行化的操作；以及接口电路，所述接口电路包括与所述存储体和所述SERDES有关的数据传输路径，所述接口电路耦接到所述SERDES区域，并且被配置为使得所述存储设备能够基于根据所述主机设备的字节序格式设置的控制信号在所述数据传输路径中执行数据转换。

[0011] 根据本发明构思的另一方面，提供了一种操作包括接口电路的存储设备的方法，所述接口电路被配置为调整主机设备与所述存储设备之间的字节序格式，所述方法包括：从所述主机设备接收第一字节序格式的串行数据流；将所述串行数据流并行化为第一数据；以及基于控制信号将所述串行数据流转换为所述存储设备的第二字节序格式，或将并行化的所述第一数据转换为所述第二字节序格式，该转换由所述接口电路执行。

## 附图说明

- [0012] 通过以下结合附图的详细描述，将更清楚地理解本发明构思的示例实施例，其中：

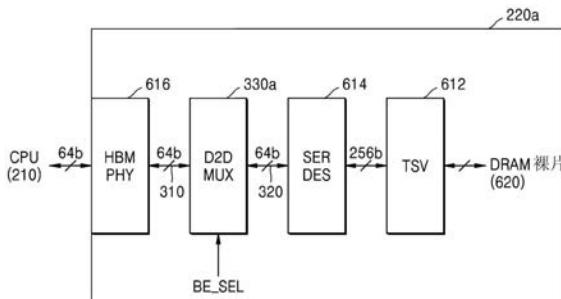

- [0013] 图1是示出根据本发明构思的示例实施例的数据转换的框图；

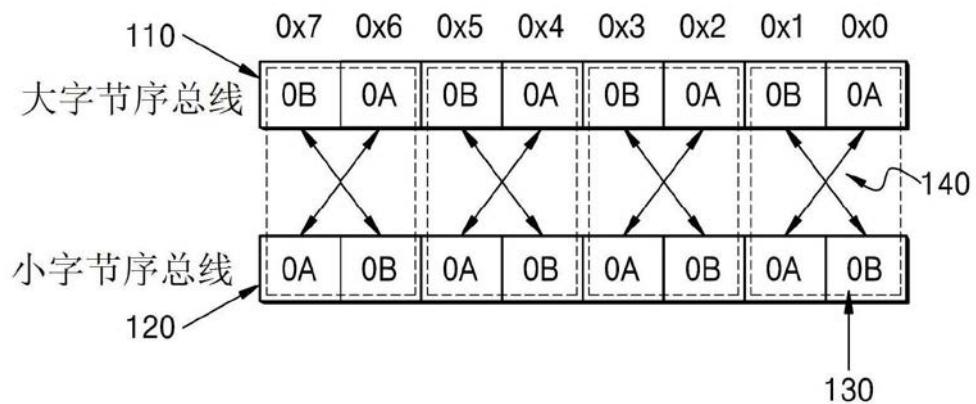

- [0014] 图2是根据本发明构思的示例实施例的具有数据转换的系统的框图；

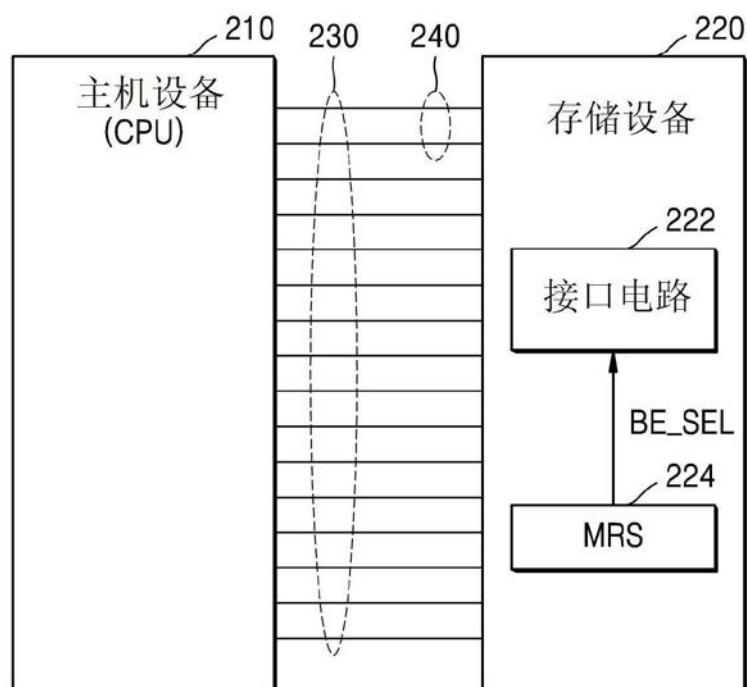

- [0015] 图3是示出根据本发明构思的示例实施例的接口电路的框图；

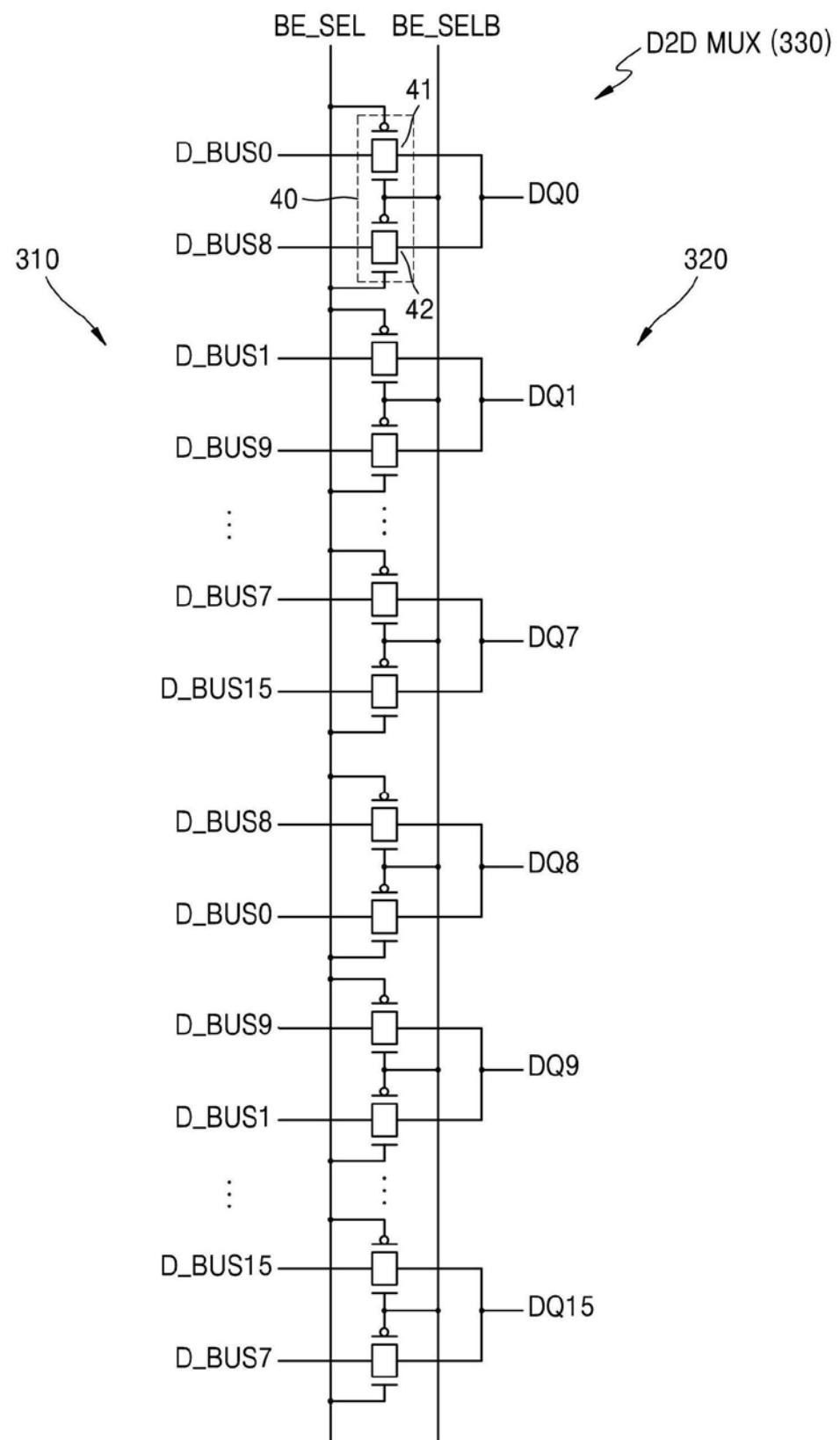

- [0016] 图4是实现图3的数据转换器(数据到数据(D2D)多路复用器(MUX))的电路图；

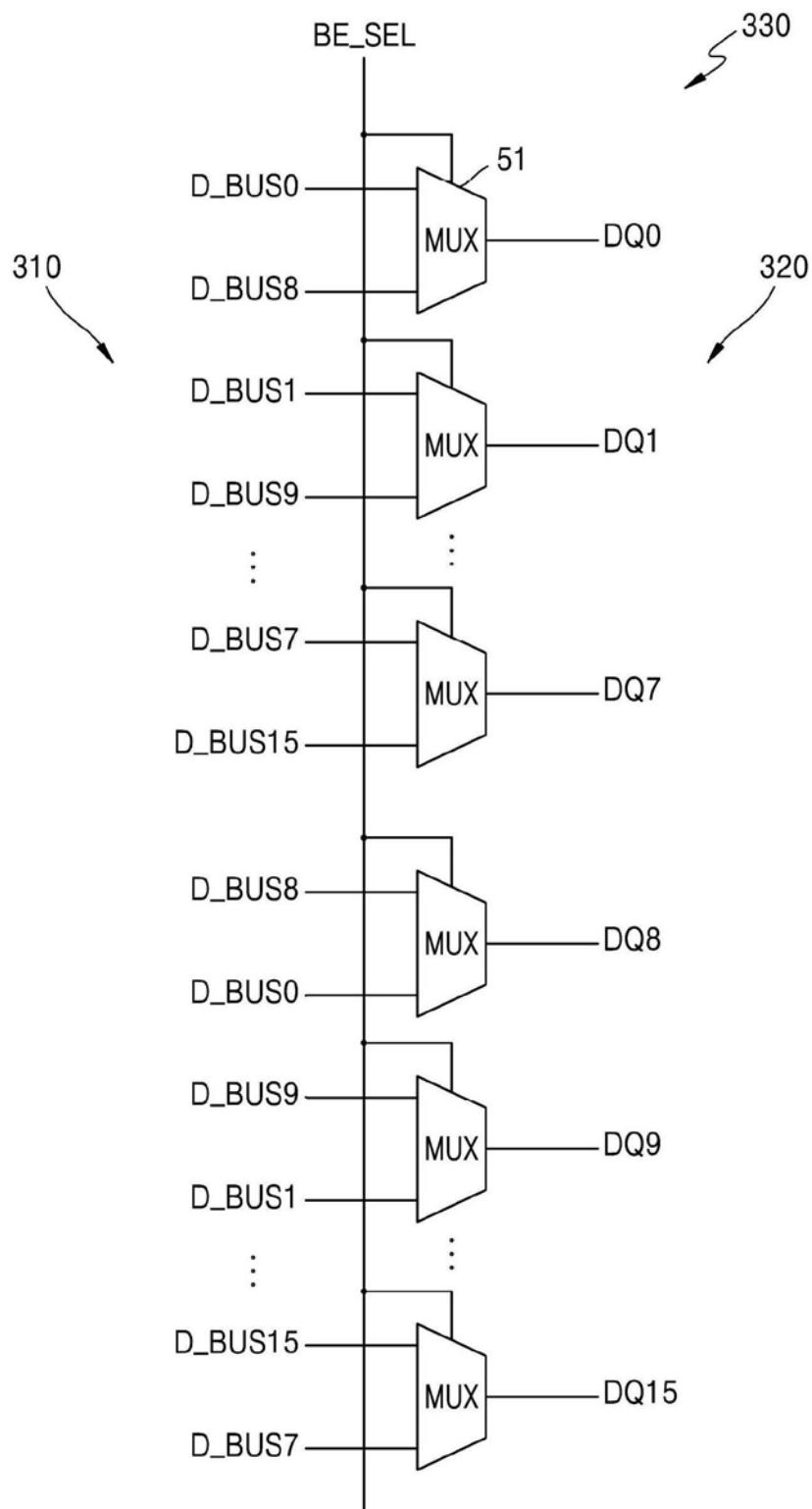

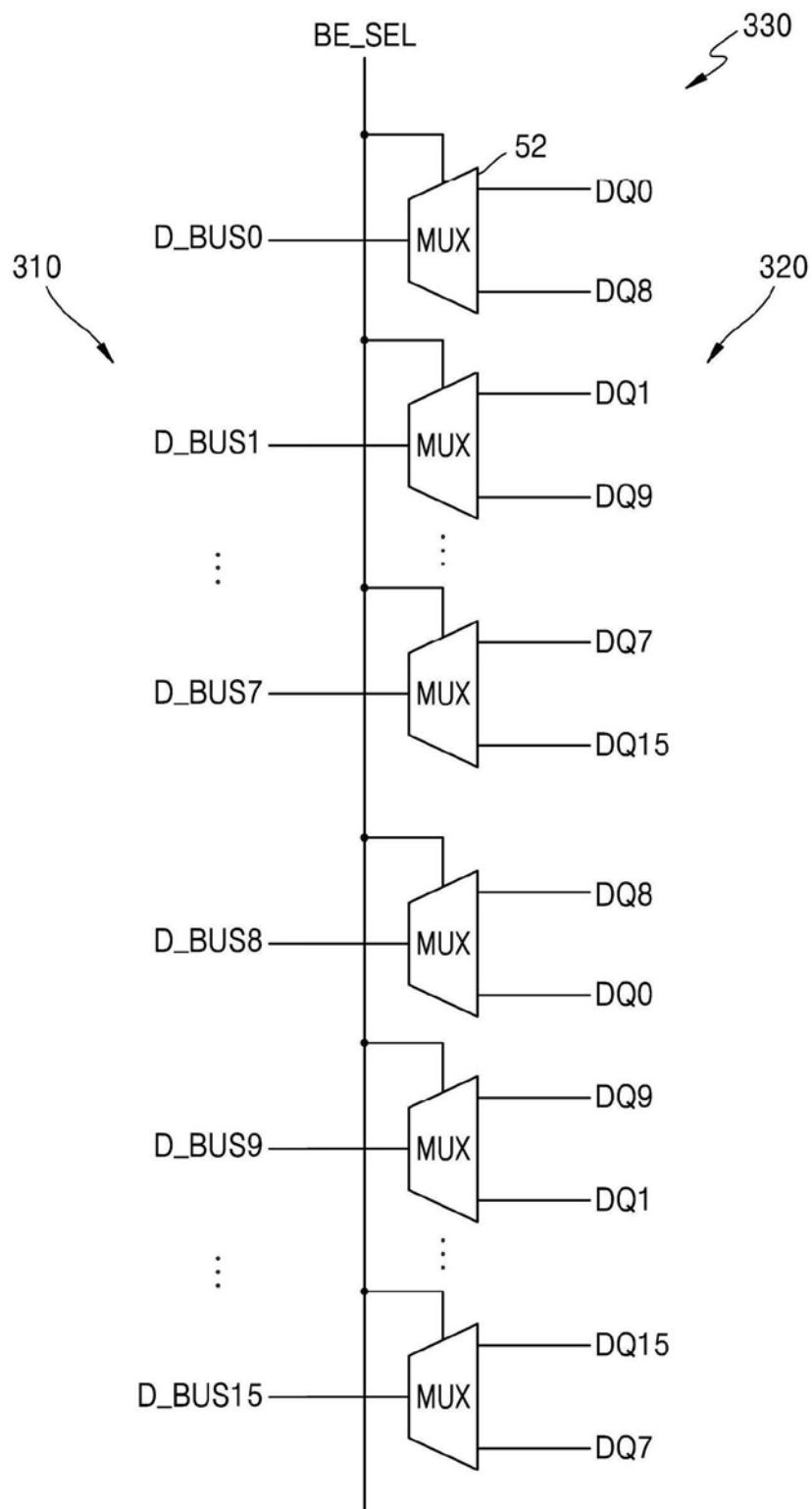

- [0017] 图5A至图5C是实现图3的D2D MUX的电路图；

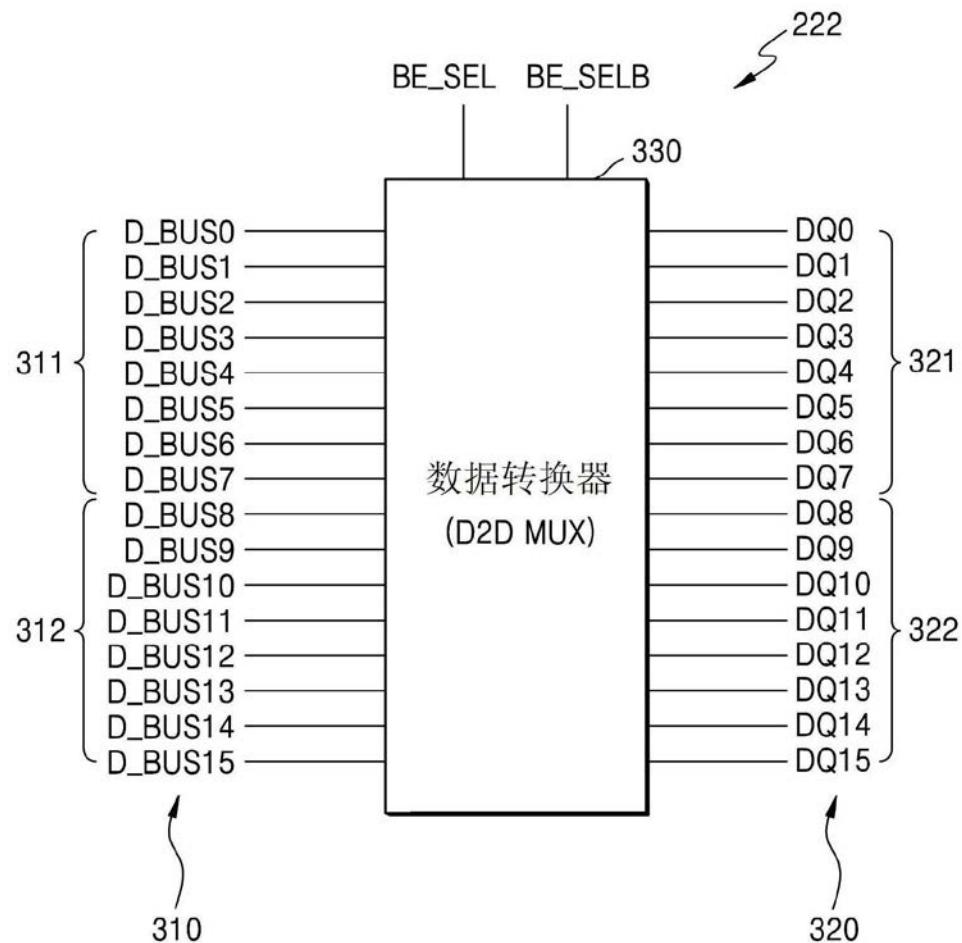

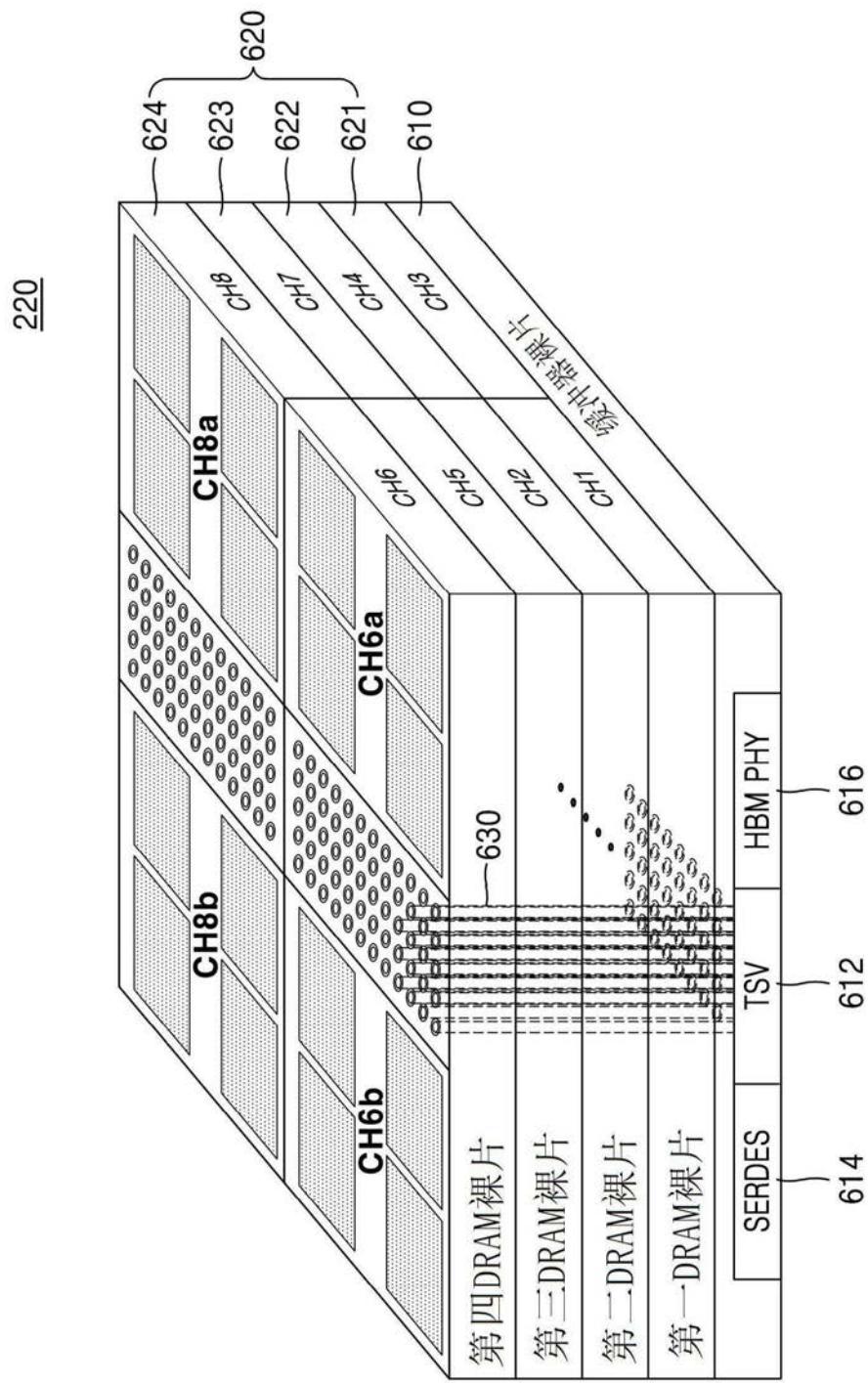

- [0018] 图6是示出根据本发明构思的示例实施例的存储设备的示图；

- [0019] 图7是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；

- [0020] 图8是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；

- [0021] 图9是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；

- [0022] 图10是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；

- [0023] 图11是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；

- [0024] 图12是示出根据本发明构思的示例实施例的存储设备中的D2D MUX的布置的示图；和

- [0025] 图13是示出图12的D2D MUX的操作的示图。

## 具体实施方式

- [0026] 图1是示出根据本发明构思的示例实施例的数据转换的框图。

- [0027] 参照图1，示出了包括大字节序总线110和小字节序总线120的两种类型的总线字节序。例如，假设通过数据总线230(图2)发送64位的数据。为了说明的简单，图1示出了64位(即，8个字节)数据的配置，但是不限于此，并且其他配置是可能的。64位的数据对应于从主机设备(或CPU 210)发送的数据大小，将参照图2和图7对此进行描述。8个字节的数据的索

引可以分别为十六进制码0x0至0x7。

[0028] 在数据总线结构中,可以将0x0索引的第一个字节放置在最右边的字节或数位,将0x7索引的第8个字节放置在最左边的字节或数位。为了便于描述,描述了如下示例:8个字节的数据中的每个字节可以包括具有0xA码位的1个字节或具有0xB码位的1个字节,即,具有0xA码位、0xB码位的2个字节中的任何一者。在本发明构思的一些示例实施例中,2个字节将被描述为数据转换单位130。

[0029] 在大字节序总线110中,从数据转换单位130右边的数位开始放置具有0xA码位、0xB码位的2个字节,即,0xA码位放置在0x0索引中,并且0xB码位放置在0x1索引中。类似地,0xA码位放置在0x2索引中,并且0xB码位放置在0x3索引中。0xA码位放置在0x4索引中,0xB码位放置在0x5索引中,0xA码位放置在0x6索引中,并且0xB码位放置在0x7索引中。

[0030] 在小字节序总线120中,从数据转换单位130左边的数位开始放置具有0xA码位、0xB码位的2个字节,例如,0xA码位放置在0x1索引中,并且0xB码位放置在0x0索引中。类似地,0xA码位放置在0x3索引中,并且0xB码位放置在0x2索引中。0xA码位放置在0x5索引中,0xB码位放置在0x4索引中,0xA码位放置在0x7索引中,并且0xB码位放置在0x6索引中。

[0031] 在大字节序总线110和小字节序总线120混合的环境中,需要进行数据转换140以使字节序一致。当主机的处理使用大字节序总线110,并且连接到处理器的存储设备使用小字节序总线120时,存储设备以软件方式执行数据转换140。这是因为处理器以其自己的大字节序总线110格式处理数据。当存储设备执行数据转换140时,需要一系列移位和交换。这样的软件操作消耗大量的存储空间和时间,这会导致存储设备的性能下降。因此,当存储设备可以利用硬件执行数据转换140并且可能存在这样的设备(硬件)时,将有利于提高存储设备的性能。

[0032] 图2是根据本发明构思的示例实施例的具有数据转换的系统200的框图。

[0033] 参照图2,在系统200中,主机设备210和存储设备220可以使用各种协议彼此通信,例如,诸如快速外围组件互连(PCI-E)、高级技术附件(ATA)、串行ATA(SATA)、并行ATA(PATA)或串行连接的SCSI(SAS)的接口协议。此外,诸如通用串行总线(USB)、多媒体卡(MMC)、增强型小磁盘接口(ESDI)或集成驱动电子设备(IDE)等各种其他接口协议可以应用于主机设备210与存储设备220之间的协议。

[0034] 主机设备210与存储设备220之间的数据传输是以数据信号(即,数据位)的形式执行的,数据信号是在数据总线230的并行通道(channel)240中驱动的。主机设备210可以生成数据位并通过数据总线230向存储设备220发送数据位。主机设备210是系统200中的执行计算机操作的功能块,并且可以对应于中央处理单元(CPU)、图形处理单元(GPU)、数字信号处理器(DSP)或应用处理器(AP)。在本说明书中,主机设备210可以被称为CPU210。

[0035] CPU 210可以被配置为执行可由一个或更多个机器执行的指令或软件、固件或它们的各种组合。CPU 210可以包括任意数目的处理器核。例如,CPU210可以包括单核或诸如双核、四核、六核等的多核。尽管在图2中示出了包括一个CPU 210的系统200,但是根据一些示例实施例,系统200可以包括多个CPU。

[0036] 数据总线230可以是双向数据总线,并且在一些示例实施例中,存储设备220可以

生成数据位，并且通过数据总线230向主机设备200发送数据位。数据总线230可以包括被称为通道240的并行导电线，其端部被分别耦接到主机设备210和存储设备220的引脚。术语“引脚”广义上是指与集成电路的电互连，并且可以包括例如在焊盘或集成电路上的另一电触点。数据总线230可以包括任意数目的通道240，并且可以包括例如2、4、8、16、32或64个通道。

[0037] 通道240可以在CPU 210与存储设备220之间配置独立的接口。例如，当以HBM实现存储设备220时，堆叠在HBM中的DRAM裸片621至624(图6)中的每一者可以包括2个通道，每个通道(例如，图6的CH6)可以包括2个伪通道(例如，图6的CH6a和CH6b)，并且每个伪通道可以包括64条导线。因此，HBM DRAM裸片621至624中的每一者可以包括4个伪通道并且包括256条导线。数据总线230可以通过与HBM架构相关联的组织耦接到8个通道240。

[0038] 可以使用表述“连接”和/或“耦接”及其派生词来描述一些示例。这些术语不一定是彼此的同义词。例如，使用术语“连接”和/或“耦接”的描述可以指示两个或更多个元件彼此直接物理接触或电接触。另外，术语“连接”和/或“耦接”还可以表示两个或更多个元件彼此不直接接触，但彼此仍协作或相互作用。

[0039] 数据总线230可以被耦接以将数据位传输到接口电路222，该接口电路222是存储设备220的硬件组件之一。接口电路222可以从数据总线230接收数据，并且根据主机设备210的大字节序格式对接收到的数据执行数据转换。在存储设备220中可以包括各种数据路径，并且接口电路222可以基于预定或期望路径中的控制信号BE\_SEL来执行数据转换。

[0040] 可以在存储设备220的模式寄存器集(MRS)224中提供控制信号BE\_SEL。当从CPU 210发出MRS命令时，可以利用提供给存储接口的地址总线的适当位值对MRS 224进行编程。在MRS 224中可以设置存储设备220的多个操作选项、各种功能、特性和模式。在本发明构思中，MRS 224可以包括特殊控制信号BE\_SEL，其设置是否改变为大字节序格式。例如，当指示改变为大字节序格式时，MRS 224可以提供逻辑高电平控制信号BE\_SEL。

[0041] 根据一些示例实施例，可以使用存储设备220中的非易失性存储器件(例如，反熔丝)来提供控制信号BE\_SEL。反熔丝是这样的电阻熔丝器件：该电阻熔丝器件具有与熔丝器件相反的电阻特性，并且在未被编程的状态下具有较高的电阻值，而在被编程的状态下具有较低的电阻值。例如，当对反熔丝进行编程时，控制信号BE\_SEL可以指示改变为大字节序格式。

[0042] 图3是示出根据本发明构思的一些示例实施例的接口电路222的框图。

[0043] 参照图2和图3，接口电路222可以包括连接在第一数据总线310与第二数据总线320之间的数据转换器330。第一数据总线310指耦接到CPU 210的数据线D\_BUS[15:0]，并且第二数据总线320指耦接到存储设备220的数据线DQ[0:15]。

[0044] 数据转换器330根据控制信号BE\_SEL和BE\_SELB，根据第一数据总线310的特定字节序格式，选择性地重新配置第二数据总线320的字节序格式，并进行传输。响应于控制信号BE\_SEL和BE\_SELB，数据转换器330可以在第一数据总线310处于大字节序格式时将第二数据总线320的字节序格式重新配置为大字节序格式，而在第一数据总线310处于小字节序格式时将第二数据总线320的字节序格式重新配置为小字节序格式。

[0045] 控制信号BE\_SEL可以确定数据转换器330是否(将第二数据总线320的字节序格式)重新配置为大字节序格式。控制信号BE\_SELB是逻辑电平与控制信号BE\_SEL的逻辑电平

相反的信号。

[0046] 第一数据总线310可以包括传输第一字节311的D\_BUS0至D\_BUS7线以及传输第二字节312的D\_BUS8至D\_BUS15线,第二数据总线320可以包括传输第一字节321的DQ0至DQ7线以及传输第二字节322的DQ8至DQ15线。当第一数据总线310处于小字节序格式并且控制信号BE\_SEL不指示重新配置为大字节序格式时,数据转换器330可以将第一数据总线310的第一字节311传递到第二数据总线320的第一字节321,并将第一数据总线310的第二字节312传递到第二数据总线320的第二字节322。此外,数据转换器330可以将第二数据总线320的第一字节321传递到第一数据总线310的第一字节311,并将第二数据总线320的第二字节322传递到第一数据总线310的第二字节312。

[0047] 当第一数据总线310处于大字节序格式并且控制信号BE\_SEL指示重新配置为大字节序格式时,数据转换器330可以将第一数据总线310的第一字节311重新配置并传输到第二数据总线320的第二字节322,并且可以将第一数据总线310的第二字节312重新配置并传输到第二数据总线320的第一字节321。另外,数据转换器330可以将第二数据总线320的第一字节321重新配置并传输到第一数据总线310的第二字节312,并且可以将第二数据总线320的第二字节322重新配置并传输到第一数据总线310的第一字节311。

[0048] 数据转换器330执行选择性地交换第一数据总线310的第一字节311和第二字节312与第二数据总线320的第一字节321和第二字节322的功能,该功能实际在物理上可以以数据到数据多路复用器(D2D MUX)的形式实现。在下文中,为了便于描述,数据转换器330将被称为D2D MUX,并将被描述为D2D MUX 330。此外,假设第一数据总线310以大字节序格式传输数据,第二数据总线320以小字节序格式传输数据,并且控制信号BE\_SEL的逻辑高电平控制D2D MUX 330重新配置为大字节序格式。

[0049] 图4是实现图3的D2D MUX 330的电路图。

[0050] 参照图3和图4,D2D MUX 330可以包括16个传输门电路40。传输门电路40分别被划分为第一数据总线310的第一字节311的一条位线、第一数据总线310的第二字节312的一条位线、以及第二数据总线320的第一字节321或第二字节322的一条位线。例如,传输门电路40可以包括连接在D\_BUS0线与DQ0线之间的第一传输门41、以及连接在D\_BUS8线与DQ0线之间的第二传输门42。响应于控制信号BE\_SEL的逻辑低电平,第一传输门41将D\_BUS0线连接到DQ0线,并且响应于控制信号BE\_SEL的逻辑高电平,第二传输门42将D\_BUS8线连接到DQ0线。其他传输门电路40类似地操作。

[0051] 因此,当控制信号BE\_SEL处于逻辑低电平时,D2D MUX 330将第一数据总线310的第一字节311传递到第二数据总线320的第一字节321,将第一数据总线310的第二字节312传递到第二数据总线320的第二字节322,将第二数据总线320的第一字节321传递到第一数据总线310的第一字节311,以及将第二数据总线320的第二字节322传递到第一数据总线310的第二字节312。当控制信号BIG\_SEL处于逻辑高电平时,D2D MUX 330将第一数据总线310的第二字节312重新配置并传输到第二数据总线320的第一字节321,将第一数据总线310的第一字节311重新配置并传输到第二数据总线320的第二字节322,将第二数据总线320的第二字节322重新配置并传输到第一数据总线310的第一字节311,以及将第二数据总线320的第一字节321重新配置并传输到第一数据总线310的第二字节312。

[0052] 图5A至图5C是实现图3的D2D MUX 330的电路图。图5A的D2D MUX330可以包括图5B

和图5C。

[0053] 参照图3和图5B,D2D MUX 330可以包括16个第一多路复用器51。第一多路复用器51分别被划分为第一数据总线310的第一字节311的一条位线、第一数据总线310的第二字节312的一条位线、以及第二数据总线320的第一字节321或第二字节322的一条位线。例如,第一多路复用器51连接在D\_BUS0线、D\_BUS8线和DQ0线之间,以响应于控制信号BE\_SEL的逻辑低电平,将D\_BUS0线的位传输到DQ0线,并响应于控制信号BE\_SEL的逻辑高电平,将D\_BUS8线的位传输到DQ0线。其他的第一多路复用器51类似地操作。

[0054] 相应地,当控制信号BE\_SEL处于逻辑低电平时,D2D MUX 330将第一数据总线310的第一字节311传递到第二数据总线320的第一字节321,并将第一数据总线310的第二字节312传递到第二数据总线320的第二字节322。当控制信号BE\_SEL处于逻辑高电平时,D2D MUX 330将第一数据总线310的第二字节312重新配置并传输到第二数据总线320的第二字节321,以及将第一数据总线310的第一字节311重新配置并传输到第二数据总线320的第二字节322。

[0055] 参照图3和图5C,D2D MUX 330可以包括16个第二多路复用器52。第二多路复用器52分别被划分为第二数据总线320的第一字节321的一条位线、第二数据总线320的第二字节322的一条位线、以及第一数据总线310的第一字节311或第二字节312的一条位线。例如,第二多路复用器52连接在DQ0线、DQ8线和D\_BUS0线之间,响应于控制信号BE\_SEL的逻辑低电平,将DQ0线的位传输到D\_BUS0线,并且响应于控制信号BE\_SEL的逻辑高电平,将DQ8线的位传输到D\_BUS0线。其他的第二多路复用器52类似地操作。

[0056] 相应地,当控制信号BE\_SEL处于逻辑低电平时,D2D MUX 330将第二数据总线320的第一字节321传递到第一数据总线310的第一字节311,并将第二数据总线320的第二字节322传递到第一数据总线310的第二字节312。当控制信号BE\_SEL处于逻辑高电平时,D2D MUX 330将第二数据总线320的第二字节322重新配置并传输到第一数据总线310的第一字节311,以及将第二数据总线320的第一字节321重新配置并传输到第二数据总线320的第二字节322。

[0057] 图6是示出根据本发明构思的一些示例实施例的存储设备220的示图。

[0058] 参照图2和图6,存储设备220可以是HBM,其包括具有彼此独立的接口的多个通道CH1至CH8。存储器件220可以包括多个裸片,多个裸片包括缓冲器裸片610和堆叠在缓冲器裸片610上的至少一个DRAM裸片620。例如,第一DRAM裸片621可以包括第一通道CH1和第三通道CH3,第二DRAM裸片622可以包括第二通道CH2和第四通道CH4,第三DRAM裸片623可以包括第五通道CH5和第七通道CH7,第四DRAM裸片624可以包括第六通道CH6和第八通道CH8。

[0059] 缓冲器裸片610可以通过形成在存储设备220的外表面上的导电元件(例如,凸块或焊球)与CPU 210通信。缓冲器裸片610可以从CPU 210接收命令、地址和数据,并将接收到的命令、地址和数据提供给至少一个DRAM裸片620的通道。此外,缓冲器裸片610可以将从至少一个DRAM裸片620的通道输出的数据提供给CPU 210。

[0060] 存储设备220可以包括穿透第一至第四DRAM裸片621至624的多个穿硅通路(TSV)630。当通道CH1至CH8均具有128位的带宽时,TSV 630可以包括1024位数据输入和输出的配置。通道CH1至CH8中的每个通道可以从左至右分开设置,例如,在第四DRAM裸片624中,第六通道CH6被分为伪通道CH6a和CH6b,第八通道CH8可以被分为伪通道CH8a和CH8b.TSV 630可

以设置在第六通道CH6的伪通道CH6a和CH6b之间以及第八通道CH8的伪通道CH8a和CH8b之间。

[0061] 缓冲器裸片610可以包括TSV区域612、串行器/解串器(SERDES)区域614和/或HBM物理层接口(即,HBM PHY区域616)。TSV区域612是其中形成有用于与至少一个DRAM裸片620通信的TSV 630的区域。

[0062] SERDES区域614是随着CPU 210的处理吞吐量增加并且对存储器带宽的需求增加而提供联合电子设备工程委员会(JEDEC)标准的SERDES接口的区域。SERDES区域614可以包括串行器/解串器(SERDES)。SERDES可以包括SERDES发送器部分、SERDES接收器部分和/或控制器部分。SERDES发送器部分可以包括并行-串行电路和发送器,可以接收并行数据流,并将接收到的并行数据流串行化。SERDES接收器部分可以包括接收器放大器、均衡器、时钟和数据恢复(CDR)电路以及串行-并行电路,接收串行数据流,并将接收到的串行数据流并行化。控制器部分可以包括诸如错误检测电路、错误纠正电路和先进先出(FIFO)的寄存器。

[0063] HBM PHY区域616可以包括物理或电层以及逻辑层,其被提供用于CPU210与存储设备220之间的有效通信所需的信号、频率、定时、驱动、详细的操作参数和功能。HBM PHY区域616可以执行存储器接口连接,诸如选择与存储单元相对应的行和列,将数据写入存储单元或读取写入数据。HBM PHY区域616可以支持JEDEC标准的HBM协议的特征。例如,HBM PHY区域616可以与CPU 210执行64位数据通信。

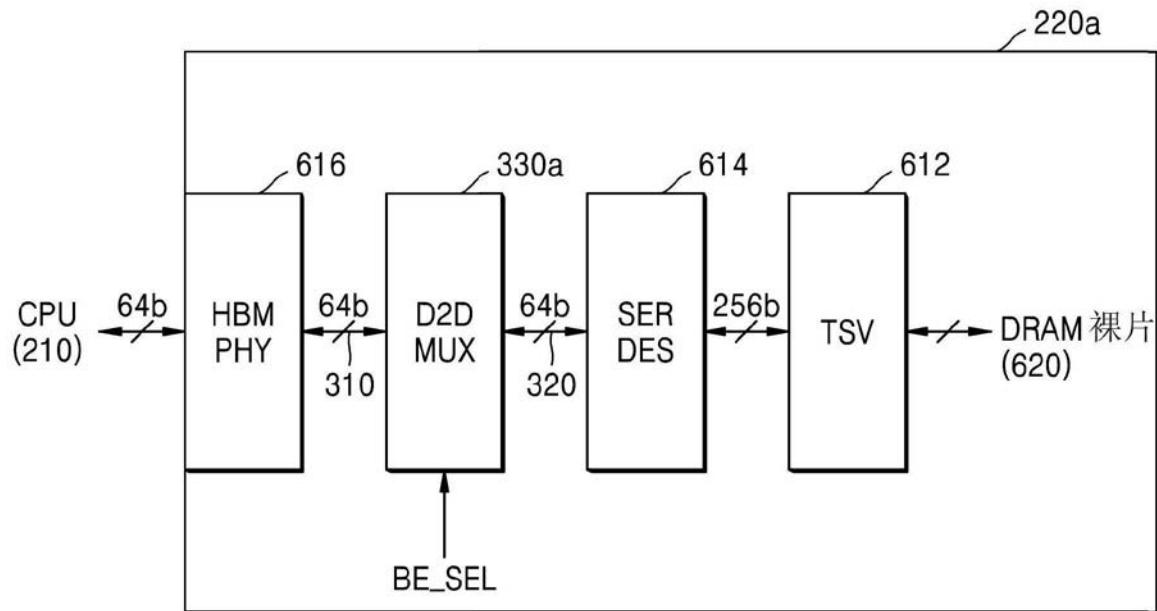

[0064] 图7是示出根据本发明构思的一些示例实施例的D2D MUX 330a在存储设备220a中的布置的示图。在下文中,附于附图标记的下标(例如,220a中的a和330a中的a)用于区分具有相同功能的多个电路。

[0065] 参照图6和图7,在存储设备220a中,D2D MUX 330a可以设置在HBM PHY区域616与SERDES区域614之间。HBM PHY区域616可以从CPU 210接收64位输入数据并且将接收到的64位输入数据划分成字节宽度,以将划分后的64位输入数据传输到D2D MUX 330a。D2D MUX 330a可以响应于控制信号BE\_SEL,基于数据传递或转换操作,以2字节为单位对64位输入数据执行数据转换,并输出64位输出数据。D2D MUX 330a可以被实现为上面描述的图4和图5A至图5C的D2D MUX 330,并且64位输入数据可以被划分为8个字节并被承载在第一数据总线310上,而64位输出数据可以被划分为8个字节并被承载在第二数据总线320上。

[0066] D2D MUX 330a可以根据逻辑高电平控制信号BE\_SEL,将第一数据总线310的第一字节重新配置并传输到第二数据总线320的第二字节,以及将第一数据总线310的第二字节重新配置并传输到第二数据总线320的第一字节,类似于图1所示的数据转换140。类似地,D2D MUX 330a可以将第一数据总线310的第三字节重新配置并传输到第二数据总线320的第四字节,将第一数据总线310的第四字节重新配置并传输到第二数据总线320的第三字节,将第一数据总线310的第五字节重新配置并传输到第二数据总线320的第六字节,将第一数据总线310的第六字节重新配置并传输到第二数据总线320的第五字节,将第一数据总线310的第七字节重新配置并传输到第二数据总线320的第八字节,以及将第一数据总线310的第八字节重新配置并传输到第二数据总线320的第七字节。即,D2D MUX 330a可以根据逻辑高电平控制信号BE\_SEL在第一数据总线310和第二数据总线320的2个字节之间交换。

[0067] D2D MUX 330a可以根据逻辑低电平控制信号BE\_SEL将未改变的数据从第一数据

总线310的第一字节至第八字节传递到第二数据总线320的第一字节至第八字节。

[0068] 在由D2D MUX 330a执行数据转换之后,第二数据总线320可以耦接到SERDES区域614。SERDES区域614可以连续地接收第二数据总线320的64位数据,并且通过串行-并行电路将64位数据转换并输出为256位并行数据。从SERDES区域614输出的256位并行数据可以通过TSV区域612提供给至少一个DRAM裸片620。

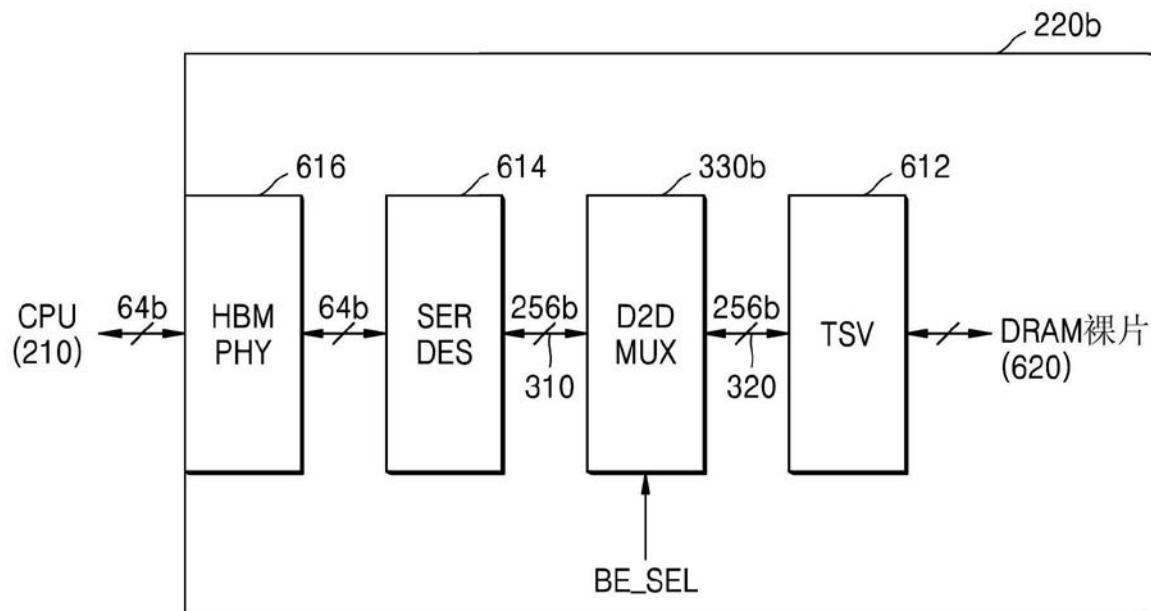

[0069] 图8是示出根据本发明构思的一些示例实施例的D2D MUX 330b在存储设备220b中的布置的示图。图8的D2D MUX 330b与图7的D2D MUX 330a的不同之处在于D2D MUX 330b设置在SERDES区域614与TSV区域612之间。在下文中,将描述图7和图8之间的不同。

[0070] 参照图6和图8,连续地接收到的从CPU 210到HBM PHY区域616的64位输入数据可以被提供给SERDES区域614,并被转换为256位并行数据。从SERDES区域614输出的256位并行数据可以通过第一数据总线310传输到D2D MUX 330b。D2D MUX 330b可以响应于控制信号BE\_SEL,基于以2字节为单位执行的数据传递或转换操作对256位输入数据执行数据转换,并通过第二数据总线320输出256位输出数据。D2D MUX 330b可以被实现为上面描述的图4和图5A至图5C的D2D MUX 330,并且256位输入数据可以被划分为16个字节并被承载在第一数据总线310上,而256位输出数据可以被划分为16个字节并被承载在第二数据总线320上。

[0071] D2D MUX 330b可以根据逻辑高电平控制信号BE\_SEL在第一数据总线310和第二数据总线320的两个字节之间交换,即,在第一字节和第二字节之间,在第三字节和第四字节之间,在第五字节和第六字节之间,在第七字节和第八字节之间,在第九字节和第十字节之间,在第十一字节和第十二字节之间,在第十三和第十四字节之间,以及在第十五字节和第十六字节之间。

[0072] D2D MUX 330b可以根据逻辑低电平控制信号BE\_SEL将未改变的数据从第一数据总线310的第一字节至第十六字节传递到第二数据总线320的第一字节至第十六字节。

[0073] 在D2D MUX 330b执行数据总线转换之后,第二数据总线320可以耦接到TSV区域612。

[0074] 因为图7的D2D MUX 330a耦接到根据CPU 210的操作速度(例如,1.2GHz)进行通信的HBM PHY区域616,所述可能需要适合于HBM PHY区域616的高速操作的高频操作的数据总线转换。相比之下,因为图8的D2DMUX 330b对在HBM PHY区域616和SERDES区域614中以高速操作处理后的256位并行数据执行数据总线转换,所述比图7的D2D MUX 330a相对低的低频操作的数据总线转换可以满足图8的D2D MUX 330b。

[0075] 图7的D2D MUX 330a对第一数据总线310和第二数据总线320的64位数据执行数据总线转换,而图8的D2D MUX 330b对第一数据总线310和第二数据总线320的256位数据执行数据总线转换。因为图7的D2D MUX330a的尺寸相对小于图8的D2D MUX 330b的尺寸,所以图7的D2D MUX330a就面积而言是有利的。

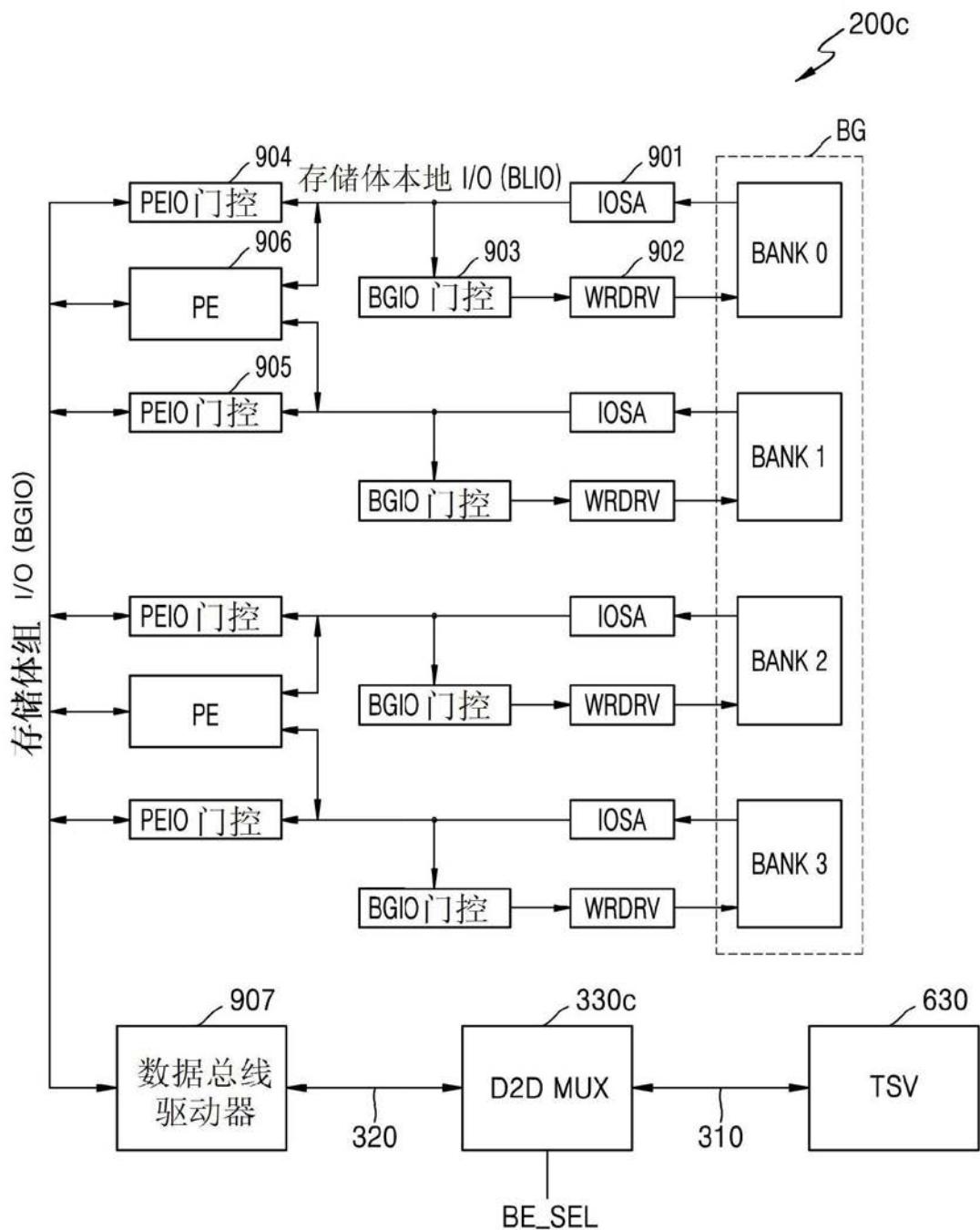

[0076] 图9是示出根据本发明构思的一些示例实施例的D2D MUX 330c在存储设备220c中的布置的示图。在描述图9的存储设备220c的配置和操作时,该配置可以对应于图6的HBM中的至少一个DRAM裸片620。示出了许多硬件配置以描述至少一个DRAM裸片620,但是不限于此,其他配置也是可能的。

[0077] 参照图2、图6和图9,示出了如下示例:存储设备220c的至少一个DRAM裸片620可以

包括被定义为一个存储体组BG的第一至第四存储体BANK0至BANK3，并且第一至第四存储体BANK0至BANK3共享一条存储体组输入/输出线I/O。存储体组I/O BGI0可以在CPU 210与存储体组BG之间在两个方向上传输数据。为了简化附图，存储体组I/O BGI0和存储体本地I/OBLI0被示出为一条信号线，但是实际上可以被实现为多条信号线。

[0078] 处理元件(PE) 906可以与两个或更多个存储体对应地设置，可以与第一存储体BANK0和第二存储体BANK1对应地设置，并且可以与第三存储体BANK2和第四存储体BANK3对应地设置。PE 906是执行PIM功能的概念组件，并且可以被定义为包括与算术计算和/或逻辑计算处理有关的各种其他组件。例如，PE 906可以包括执行各种功能的组件，诸如控制计算处理的所有操作的控制器，存储指令的指令存储器(或指令队列)和/或指令解码。

[0079] 读出放大器901、写入驱动器902和/或存储体组输入/输出门控电路(以下称为BGI0门控电路903)可以与第一存储体BANK0对应地耦接。此外，读出放大器901和写入驱动器902可以布置在存储体本地I/O BLI0上，并且BGI0门控电路903可以布置成选择存储体本地I/O BLI0的数据传输方向。在图9中，示出了BGI0门控电路903被设置在通过写入驱动器902传输数据的路径中的示例，但是BGI0门控电路903不必限于此。作为另一个示例，BGI0门控电路903可以布置在通过读出放大器901输出数据的路径中。

[0080] 第一PE输入/输出(PEI0)门控电路904可以与第一存储体BANK0对应地设置，并且第二PEI0门控电路905可以与第二存储体BANK1对应地设置。第一PEI0门控电路904和第二PEI0门控电路905可以被布置为在存储操作和计算处理操作中控制数据的移动路径。在存储操作中，第一PEI0门控电路904可以将存储体本地I/O BLI0电连接到存储体组I/O BGI0，以在CPU 210与第一存储体BANK0之间发送和接收数据，并且可以通过第二PEI0门控电路905在CPU 210与第二存储体BANK1之间发送和接收数据。同时，在计算处理期间，第一PEI0门控电路904和第二PEI0门控电路905电阻断开存储体本地I/O BLI0和存储体组I/O BGI0，以在CPU 210与PE 906之间或者在PE 906与第一存储体BANK0和第二存储体BANK1之间发送和接收数据。

[0081] PE 906可以与第一存储体BANK0和第二存储体BANK1对应地设置。PE 906可以通过使用从CPU 210提供的数据、从第一存储体BANK0和第二存储体BANK1读取的数据以及在设置在PE 906中的寄存器中存储的信息中的至少一者来执行计算处理。在一些示例实施例中，当PE 906使用来自第一存储体BANK0的数据执行计算处理时，与第二存储体BANK1对应设置的第二PEI0门控电路905可以阻断存储体组I/O BGI0与对应于第二存储体BANK1的存储体本地I/O BLI0之间的电连接。在一些示例实施例中，当PE 906与第一存储体BANK0和第二存储体BANK1共享时，使用任何一个存储体的数据的计算处理的结果可以被存储在另一存储体中。作为示例，从第一存储体BANK0读取的数据可以作为操作数被提供给PE 906，并且PE 906的计算结果可以被存储在第二存储体BANK1中。

[0082] 存储体组I/O BGI0可以通过数据总线驱动器907耦接到D2D MUX 330c，并且D2D MUX 330c可以耦接到TSV 630。被传输到至少一个DRAM裸片620的TSV 630的数据可以通过第一数据总线310传输到D2D MUX 330c。D2D MUX 330c可以响应于控制信号BE\_SEL，基于数据传递或转换操作，以2字节为单位对256位输入数据执行数据总线转换，并通过第二数据总线320输出256位输出数据。

[0083] D2D MUX 330c可以被实现为上面描述的图4和图5A至图5C的D2DMUX 330，并且256

位输入数据可以被划分为16个字节并被承载在第一数据总线310上，并且256位输出数据可以被划分为16个字节并被承载在第二数据总线320上。D2D MUX 330c可以根据逻辑高电平控制信号BE\_SEL在第一数据总线310和第二数据总线320的256位、16个字节中的两个字节之间交换，即，在第一字节和第二字节之间，在第三字节和第四字节之间，在第五字节和第六字节之间，在第七字节和第八字节之间，在第九字节和第十字节之间，在第十一字节和第十二字节之间，在第十三字节和第十四字节之间，以及在第十五字节和第十六字节之间。D2D MUX 330c可以根据逻辑低电平控制信号BE\_SEL将未改变的数据从第一数据总线310的第一字节至第十六字节传递到第二数据总线320的第一字节至第十六字节。

[0084] 在D2D MUX 330c执行数据总线转换之后，第二数据总线320可以通过数据总线驱动器907耦接到存储体组I/O BGIO。

[0085] 图9所示的DRAM裸片配置被提供为示例，但不一定是实际的DRAM裸片配置。另外，图9所示的DRAM裸片配置并不指示或暗示对发明构思的限制。

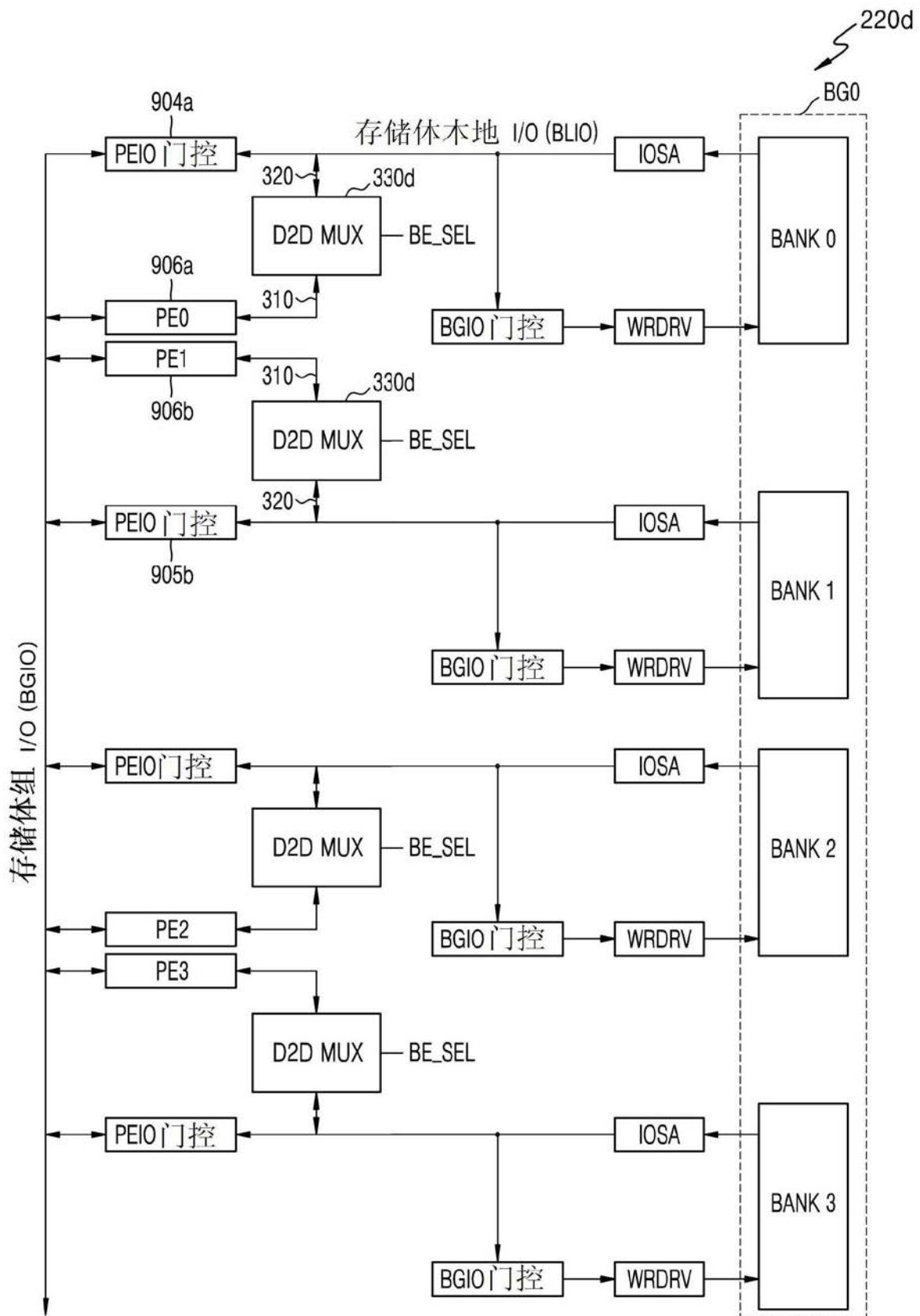

[0086] 图10是示出根据本发明构思的一些示例实施例的D2D MUX 330d在存储设备220d中的布置的示图。图10的存储设备220d与图9的存储设备220c的不同之处在于：PE分别与第一至第四存储体BANK0至BANK3相对应地布置。在下文中，将描述图9与图10之间的不同。

[0087] 参照图10，第一PE 906a和第二PE 906b分别单独地与第一存储体BANK0和第二存储体BANK1对应地布置。第一PEI0门控电路904a可以被布置为控制存储体组I/O BGIO和第一存储体BANK0的存储体本地I/O BLIO的连接，第二PEI0门控电路905b可以被布置为控制存储体组I/O BGIO和第二存储体BANK1的存储体本地I/O BLIO的连接。D2D MUX 330d可以连接在第一PE 906a与第一PEI0门控电路904a之间，以及第二PE 906b与第二PEI0门控电路905b之间。从第一PE 906a和第二PE 906b传输的数据可以通过第一数据总线310传输到D2D MUX 330d。D2D MUX 330d可以响应于控制信号BE\_SEL，基于数据传递或转换操作，以2字节为单位对256位输入数据执行数据总线转换，并通过第二数据总线320将256位输出数据输出到第一PEI0门控电路904a和第二PEI0门控电路905b。

[0088] D2D MUX 330d可以被实现为上面描述的图4和图5A至图5C的D2DMUX 330，并且256位输入数据可以被划分为16个字节并被承载在第一数据总线310上，并且256位输出数据可以被划分为16个字节并被承载在第二数据总线320上。D2D MUX 330d可以根据逻辑高电平控制信号BE\_SEL在第一数据总线310和第二数据总线320的256位、16个字节中的两个字节之间交换，即，在第一字节和第二字节之间，在第三字节和第四字节之间，在第五字节和第六字节之间，在第七字节和第八字节之间，在第九字节和第十字节之间，在第十一字节和第十二字节之间，在第十三字节和第十四字节之间，以及在第十五字节和第十六字节之间。D2D MUX 330d可以根据逻辑低电平控制信号BE\_SEL将未改变的数据从第一数据总线310的第一字节至第十六字节传递到第二数据总线320的第一字节至第十六字节。

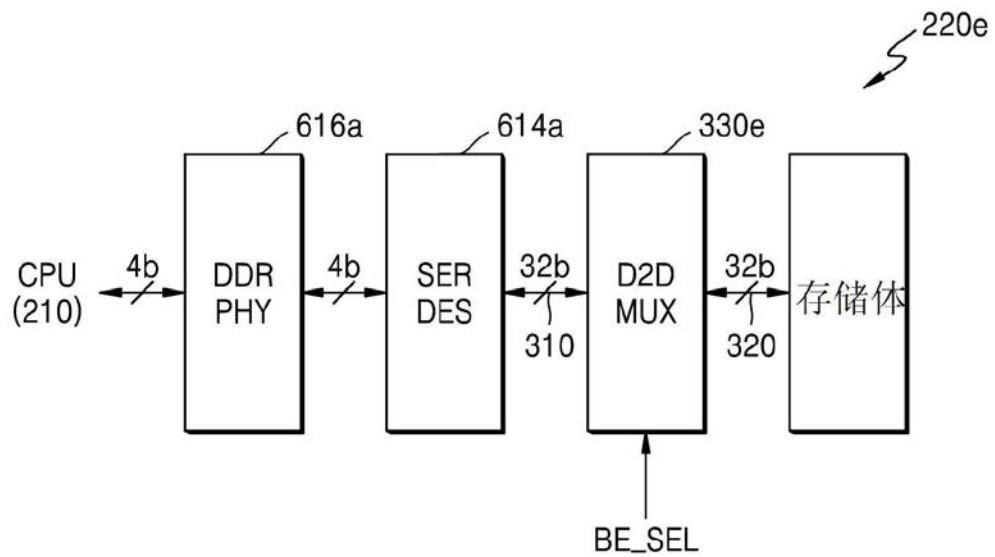

[0089] 图11是示出根据本发明构思的一些示例实施例的D2D MUX 330e在存储设备220e中的布置的示图。图11的存储设备220e是独立类型的双倍数据速率(DDR) DRAM，并且可以包括执行PIM功能的PE。

[0090] 参照图2和图11，在存储设备220e中，D2D MUX 330e可以设置在SERDES区域614a与存储体BANK之间。DDR PHY区域616a可以从CPU210接收4位输入数据，并且将4位输入数据传输到SERDES区域614a。DDR PHY区域616a可以支持JEDEC标准的HBM协议的特征。SERDES区域

614a可以连续接收通过DDR PHY区域616a传输的CPU 210的4位数据，并且通过串行-并行电路将4位数据转换并输出为32位并行数据。从SERDES区域614a输出的32位并行数据可以划分为字节宽度，并通过第一数据总线310传输到D2D MUX 330e。D2D MUX 330e可以响应于控制信号BE\_SEL，基于数据传递或转换操作，以2个字节为单位对32位输入数据执行数据转换，并输出32位输出数据。

[0091] D2D MUX 330e可以被实现为上面描述的图4和图5A至图5C的D2DMUX 330，并且32位输入数据被划分为4个字节并被承载在第一数据总线310上，并且32位输出数据可以被划分为4个字节并被承载在第二数据总线320上。D2D MUX 330e可以根据逻辑高电平控制信号BE\_SEL在第一数据总线310和第二数据总线320的32位、4个字节中的两个字节之间交换，即，在第一字节和第二字节之间以及在第三字节和第四字节之间。D2D MUX330e可以根据逻辑低电平控制信号BE\_SEL将未改变的数据从第一数据总线310的第一字节至第四字节传递到第二数据总线320的第一字节至第四字节。

[0092] 在由D2D MUX 330e执行数据总线转换之后，第二数据总线320可以耦接到存储体BANK。

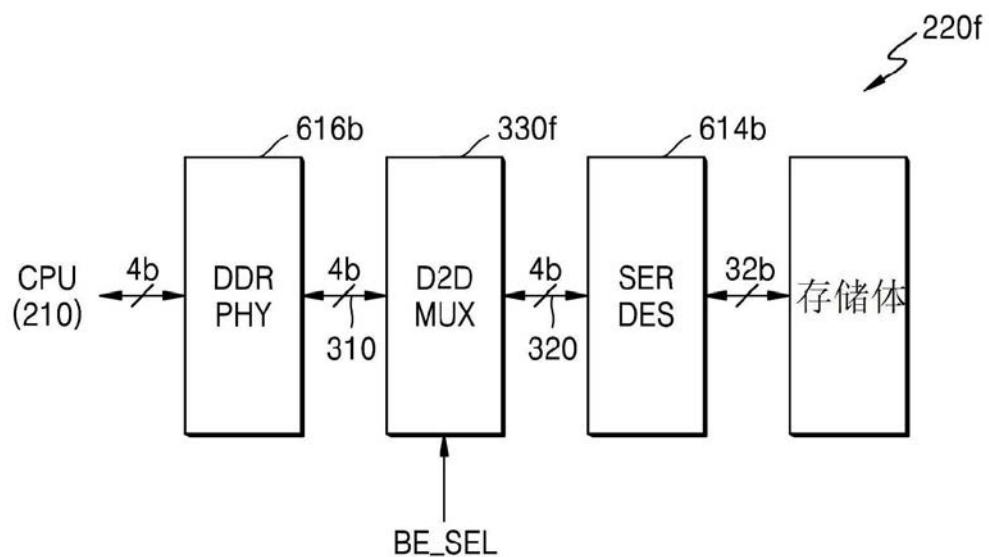

[0093] 图12是示出根据本发明构思的一些示例实施例的D2D MUX 330f在存储设备220f中的布置的示图。图12的D2D MUX 330f与图11的D2D MUX330e的不同之处在于，D2D MUX 330f设置在DDR PHY区域616b与SERDES区域614b之间。在下文中，将描述图11和图12之间的差异。

[0094] 参照图2和图12，在存储设备220f中，DDR PHY区域616b可以从CPU210接收4位输入数据，并且通过第一数据总线310将4位输入数据传输到D2D MUX 330f。例如，在大字节序格式的第一数据总线310中，第一地址指的是第一数据总线310的最高有效(例如，最左边的)位，而递增的地址(increasing addresses)则指的是越来越低的有效位(increasingly less significant bits)。相比之下，在小字节序格式的第二数据总线320中，相同的第一地址指的是第二数据总线320的最低有效(例如，最右边的)位，并且递增的地址指的是越来越高有效位(increasingly more significant bits)。

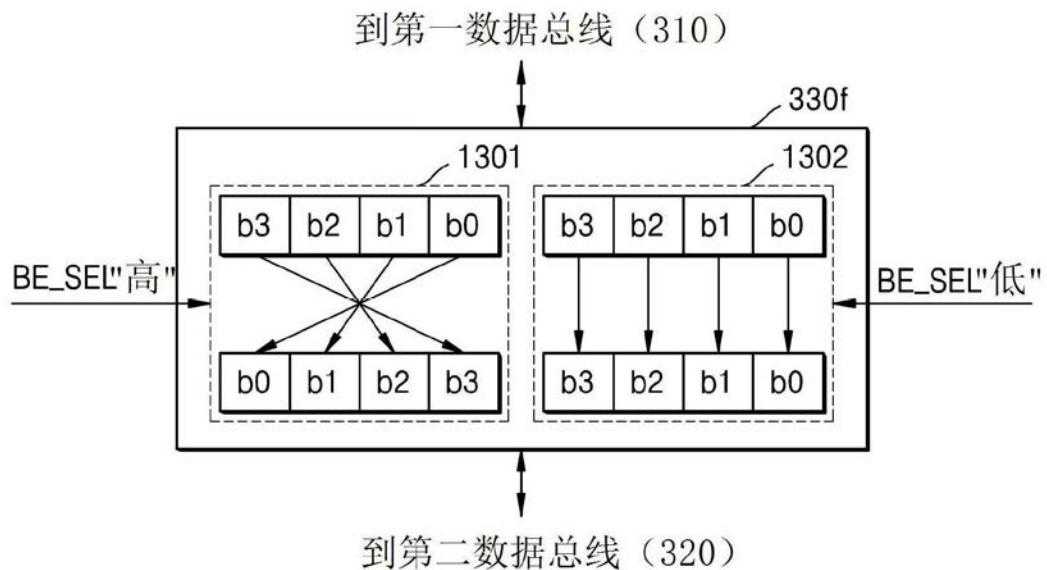

[0095] 如图13所示，D2D MUX 330f可以响应于控制信号BE\_SEL对第一数据总线310的4位输入数据执行位传递或位转换操作。D2D MUX 330f可以根据逻辑高电平控制信号BE\_SEL执行位交换1301，使得第一数据总线310的b3-b2-b1-b0位可以被转换为b0-b1-b2-b3位并被输出到第二数据总线320。相比之下，D2D MUX 330f可以根据逻辑低电平控制信号BE\_SEL执行位传递1302，使得第一数据总线310的b3-b2-b1-b0位可以不改变并作为b3-b2-b1-b0位输出到第二数据总线320。

[0096] 在由D2D MUX 330f执行数据总线转换之后，第二数据总线320可以耦接到SERDES区域614b。SERDES区域614b可以连续地接收第二数据总线320的4位数据，并且通过串行-并行电路将4位数据转换并输出为32位并行数据。从SERDES区域614b输出的32位并行数据可以传输到存储体BANK。

[0097] 如上所述，数据转换器330可以以硬件来实现(如所示出的但不限于图4至图5C所示的示例)，以及以等效的硬件实施方式来实现。

[0098] 以上公开的任何其余元件可以包括或被实现在诸如以下项的处理电路中：包括逻辑电路的硬件；诸如执行软件的处理器的硬件/软件组合；或它们的组合。例如，处理电路更

具体地可以包括但不限于中央处理单元(CPU)、算术逻辑单元(ALU)、数字信号处理器、微型计算机、现场可编程门阵列(FPGA)、片上系统(SoC)、可编程逻辑单元、微处理器、专用集成电路(ASIC)等。

[0099] 尽管已经参考本发明构思的示例实施例具体示出和描述了本发明构思，但是将理解，在不脱离所附权利要求的精神和范围的情况下，可以在形式和细节上进行各种改变。

图1

200

图2

图3

图4

330

图5A

图5B

图5C

图6

图7

图8

图9

图10

图11

图12

图13