(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4402074号

(P4402074)

(45) 発行日 平成22年1月20日(2010.1.20)

(24) 登録日 平成21年11月6日(2009.11.6)

(51) Int.Cl.

H01L 25/10 (2006.01)

H01L 25/11 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/14

Z

請求項の数 10 外国語出願 (全 10 頁)

(21) 出願番号 特願2006-136747 (P2006-136747)

(22) 出願日 平成18年5月16日 (2006.5.16)

(65) 公開番号 特開2006-324665 (P2006-324665A)

(43) 公開日 平成18年11月30日 (2006.11.30)

審査請求日 平成21年5月1日 (2009.5.1)

(31) 優先権主張番号 60/594,884

(32) 優先日 平成17年5月16日 (2005.5.16)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 11/383,403

(32) 優先日 平成18年5月15日 (2006.5.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 506164899

スタッツ・チップパック・リミテッド

S T A T S C H I P P A C L T D.

シンガポール、768442 シンガポー

ル、イーション・ストリート、23、5

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

最終頁に続く

(54) 【発明の名称】オフセット集積回路パッケージオンパッケージ積層システムおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

ベース基板を設けるステップと、

コンタクトパッドを前記ベース基板上に形成するステップと、

第1の集積回路を前記ベース基板上に取付けるステップと、

成形材料により前記第1の集積回路を囲むように、ベースパッケージ成形体を形成する

ステップと、

オフセット基板を設けるステップと、

第2の集積回路を前記オフセット基板上に取付けるステップと、

前記ベース基板の上面の一部が露出するように、前記オフセット基板を前記ベースパッ

ケージ成形体の一部のみの上、および、ベースパッケージ成形体が形成されていないベ

基板の上方に位置するように配置するとともに、前記オフセット基板を、システム相互

接続部を介在させて、前記コンタクトパッドに電気的に接続するステップとを備える、オ

フセット集積回路パッケージオンパッケージ積層システムの製造方法。

## 【請求項2】

受動構成要素、能動構成要素、またはそれらの組合せを前記ベース基板に取付けるステ

ップをさらに含む、請求項1に記載のオフセット集積回路パッケージオンパッケージ積層

システムの製造方法。

## 【請求項3】

オフセットパッケージがベースモールドキャップの角にある状態で、前記オフセットパ

ツケージを前記ベース基板に取付けるステップをさらに含む、請求項 1 に記載のオフセット集積回路パッケージオンパッケージ積層システムの製造方法。

【請求項 4】

前記ベースパッケージ成形体と前記オフセット基板との間に隙間充填接着剤を与えるステップをさらに含む、請求項 1 に記載のオフセット集積回路パッケージオンパッケージ積層システムの製造方法。

【請求項 5】

オフセットパッケージがベースモールドキャップの 1 つの端縁と整列された状態で、前記オフセットパッケージを前記ベース基板上に取付けるステップをさらに含む、請求項 1 に記載のオフセット集積回路パッケージオンパッケージ積層システムの製造方法。 10

【請求項 6】

オフセット集積回路パッケージオンパッケージ積層システムであって、

ベース基板と、

前記ベース基板上に形成されるコンタクトパッドと、

前記ベース基板上に取付けられる第 1 の集積回路と、

成形材料により前記第 1 の集積回路を囲むように形成されたベースパッケージ成形体と、

オフセット基板と、

前記オフセット基板上に取付けられる第 2 の集積回路と、を備え、

前記オフセット基板は、システム相互接続部を介在させて前記コンタクトパッドに電気的に接続され、かつ、前記ベース基板の上面の一部が露出するように、前記ベースパッケージ成形体の一部のみの上、および、前記ベースパッケージ成形体が形成されていないベース基板の上方に位置するように配置される、システム。 20

【請求項 7】

前記ベース基板に取付けられる受動構成要素、能動構成要素、またはそれらの組合せをさらに含む、請求項 6 に記載のシステム。

【請求項 8】

オフセットパッケージがベースモールドキャップの角にある状態で前記ベース基板上に取付けられる前記オフセットパッケージをさらに含む、請求項 6 に記載のシステム。 30

【請求項 9】

前記ベースパッケージ成形体と前記オフセット基板との間に隙間充填接着剤をさらに含む、請求項 6 に記載のシステム。

【請求項 10】

オフセットパッケージがベースモールドキャップの 1 つの端縁と整列された状態で前記ベース基板上に取付けられる前記オフセットパッケージをさらに含む、請求項 6 に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

この出願は、2005年5月16日に出願された米国仮特許出願連続番号第 60 / 594,884 号の利益を主張する。

【0002】

この出願は、「オフセット集積回路パッケージオンパッケージ積層システム (Offset Integrated Circuit Package-on-Package Stacking System)」と題される、シム (Shim) によって同時に出願された米国特許出願に関する主題を含む。関連出願はスタッツ・チップパック・リミテッド (STATS ChipPAC Ltd.) に譲渡され、事件番号 27-173 によって識別される。

【0003】

技術分野

40

50

この発明は概して集積回路パッケージシステムおよびその製造方法に関し、より特定的には、積み重ねられたパッケージを有する集積回路パッケージシステムのためのシステムおよびその製造方法に関する。

【背景技術】

【0004】

背景技術

集積回路を他の回路と接続するために、集積回路をリードフレームまたは基板に取付けることが一般的である。各々の集積回路は、極めて高純度の金またはアルミニウムのワイヤを使用してリードフレームのリードフィンガーパッドに個々に接続されるボンディングパッドを有する。このアセンブリは、次いで、成形されたプラスチックまたはセラミックの本体にアセンブリを個々に封入することによってパッケージ化されて、集積回路パッケージを作る。

【0005】

集積回路パッケージング技術では、単一の回路板または回路基板に取付けられる集積回路の数の増加がみられてきた。新しいパッケージングの設計は、集積回路の物理的な大きさおよび形状などの形状要因の点でよりコンパクトであり、集積回路の密度全体の大幅な増加をもたらしている。しかしながら、集積回路の密度は、個々の集積回路を基板に取付けるのに利用可能な「リアルエステート」によって制限され続ける。P C、計算サーバ、および記憶サーバなどのより大きな形状要因のシステムであっても、同一の「リアルエステート」またはより小さな「リアルエステート」の中により多くの集積回路が必要となる。携帯電話、デジタルカメラ、音楽プレーヤ、P D A、およびロケーションベースの装置などの携帯型個人用電子機器の必要性は、特に切実であり、集積回路の密度の必要性をさらに推し進めてきた。

【0006】

この集積回路の密度の増加は、2つ以上の集積回路がパッケージ化され得るマルチチップパッケージの発展を招いてきた。各々のパッケージは、個々の集積回路、および集積回路が周囲の回路に電気的に接続されることを可能にする相互接続線の1つ以上の層に機械的な支持をもたらす。現在のマルチチップパッケージは、通常マルチチップモジュールとも称されるが、典型的には、別個の集積回路構成要素の組が直接に取付けられるP C B基板から成る。このようなマルチチップパッケージは、集積回路の密度および小型化を高め、信号伝搬速度を向上させ、集積回路全体の大きさおよび重量を低減し、性能を向上させ、コストを下げることがわかつってきた。これらはすべて、コンピュータ業界の第一義的な目標である。

【0007】

マルチチップパッケージはさらに、垂直に配置されていようと、水平に配置されていようと、問題を提示する可能性がある。なぜなら、マルチチップパッケージは通常、集積回路および集積回路の接続部が検査され得る前に予め組立てられなければならないからである。したがって、集積回路がマルチチップモジュールにおいて取付けられ、接続されるとき、個々の集積回路および接続部は個々に検査されることができず、より大きな回路に組立てられる前に品質保証チップ（「known-good-die」）（「K G D」）を識別することが不可能である。その結果、従来のマルチチップパッケージは組立プロセスの歩留りの問題を招く。したがって、K G Dを識別しないこの製造プロセスは信頼性の低いものになり、組立ての欠陥を被りやすい。

【0008】

さらに、典型的なマルチチップパッケージにおいて垂直に積み重ねられた集積回路は、水平に配置された集積回路パッケージの問題以上に問題を提示する可能性があり、これはさらに製造プロセスを複雑にする。個々の集積回路の実際の故障モードを検査し、したがって実際の故障モードを判断することはより困難である。さらに、基板および集積回路は、組立または検査の間に損傷を受けることが多く、これは製造プロセスを複雑にし、コストを増大させる。垂直に積み重ねられた集積回路の問題は利点よりも大きい可能性がある

10

20

30

40

50

。

### 【発明の開示】

#### 【発明が解決しようとする課題】

##### 【0009】

したがって、改良されたパッケージング方法、システム、および設計の必要性が依然として残されている。家庭用電子機器の小型化および限られた空間により精巧な機能を求める需要を考慮して、これらの問題に対する解決策が見出されることが益々重要である。商業的な競争圧力の益々の増加、顧客の期待の高まり、および市場において意義のある製品の差別化のための機会が減少していることを考慮して、これらの問題に対する解決策が見出されることが益々重要である。さらに、コストを節約し、効率を高め、このような競争圧力に対処する必要性が益々増大することにより、これらの問題に対する解決策が見出されなければならないという重大な必要性にさらなる緊急性が加わる。

10

##### 【0010】

これらの問題に対する解決策は長く求められてきたが、先行技術の開発は如何なる解決策も教示または提案せず、したがって、これらの問題に対する解決策は長く当業者に発見されて来なかつた。

#### 【課題を解決するための手段】

##### 【0011】

###### 発明の開示

この発明は、ベース基板を設けることと、コンタクトパッドをベース基板上に形成することと、第1の集積回路をベース基板上に取付けることと、ベースパッケージ本体を第1の集積回路を囲むように形成することと、オフセット基板を設けることと、第2の集積回路をオフセット基板上に取付けることと、オフセット基板をベースパッケージ本体上に置くことを含む、オフセット基板をコンタクトパッドに結合することとを含むオフセット集積回路パッケージオンパッケージ積層システムを提供する。

20

##### 【発明を実施するための最良の形態】

##### 【0012】

この発明の特定の実施例は、上述の実施例に加えてまたは上述の実施例の代わりに他の局面を有する。この局面は、添付の図面を参照して取り入れられるときに以下の詳細な説明を読むことによって当業者に明らかになる。

30

##### 【0013】

###### 発明を実施するための最良の形態

以下の実施例は、当業者がこの発明をなし、使用することができるよう十分詳細に記載される。この開示に基づいて他の実施例が明らかであろうということが理解されるべきであり、この発明の範囲から逸脱することなくプロセスまたは機械的な変更がなされ得ることが理解されるべきである。

##### 【0014】

以下の記載では、この発明を完全に理解できるようにするために多くの具体的な詳細が与えられる。しかしながら、この発明はこれらの具体的な詳細がなくても実施され得ることが明らかである。この発明を曖昧にするのを避けるために、いくつかの周知の回路、システムの構成、およびプロセスのステップは詳細に開示されない。

40

##### 【0015】

同様に、この装置の実施例を示す図面は半概略的であり、一定の比例に応じて描かれているわけではなく、特に、寸法のうちのいくつかは表示を明確にするためのものであり、図面を描く際に大幅に誇張されて示される。さらに、共通のいくつかの特徴を有する複数の実施例が開示され、記載される場合には、それらの記載、説明、および理解を明確にし、容易にするために、同様および同一の特徴はそれぞれ、同一の参照番号を用いて通常は記載される。

##### 【0016】

本明細書において使用される「水平な」という用語は、向きにかかわらず、パッケージ

50

基板の面または表面に平行な面として規定される。「垂直な」という用語は、今までに規定された水平位置に直交する方向を指す。「上方に」、「下方に」、「底部」、「上部」、「側」（「側壁」におけるように）、「より高い」、「より低い」、「より上の」、「真上に」、および「真下に」などの用語は、水平面に対して規定される。「上に（on）」という用語は、要素間に直接的な接触があることを意味する。本明細書において使用される「処理する」という用語は、記載される構造を形成する際に必要な材料のスタンピング、鍛造、パターニング、露光、現像、エッチング、洗浄、および／もしくは除去またはレーザトリミングを含む。

#### 【0017】

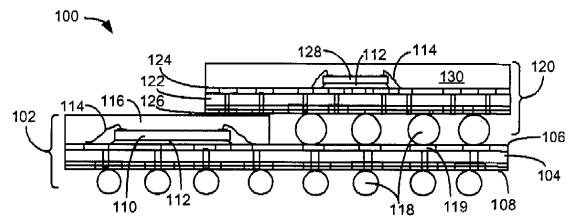

ここで図1を参照して、この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システム100の断面図が示される。オフセット集積回路パッケージオンパッケージ積層システム100の断面図は、ベース上部面106およびベース底部面108を備えるベース基板104を有する、ポールグリッドアレイパッケージなどのベースパッケージ102を示す。第1の集積回路110は、ダイ接着材料などの接着剤112でベース上部面106に取付けられる。第1の集積回路110は、ボンドワイヤ、はんだバンプ、はんだコラム、またはスタッドバンプなどの電気的な相互接続部114によってベース上部面106に結合される。成形材料などのベースパッケージ本体116は、第1の集積回路110、電気的な相互接続部114、およびベース上部面106の一部を囲むように射出成形される。はんだボール、はんだコラムインターポーラまたはスタッドバンプなどのシステム相互接続部118は、システムの次のレベル（図示せず）に取付けるためにベース底部面108に取付けられる。コンタクトパッド119のアレイは、ベースパッケージ本体116の周りの領域に分散される。

#### 【0018】

上部面124および底部面126を備えるオフセット基板122を有するオフセットパッケージ120は、オフセット位置でベースパッケージ102に取付けられる。オフセットパッケージ120は、接着剤112で上部面124に取付けられた第2の集積回路128を有する。第2の集積回路128は、電気的な相互接続部114によって上部面124に結合される。成形材料などのオフセットパッケージ本体130は、第2の集積回路128、上部面124、および電気的な相互接続部114を覆って射出成形される。システム相互接続部118は、オフセット基板122の底部面126に取付けられる。オフセットパッケージ120はベースパッケージ102に取付けられ、その結果、オフセット基板122の底部面126はベースパッケージ本体116およびシステム相互接続部118の上に置かれる。この構成は、印刷回路基板（図示せず）上で必要とされる空間を低減するが、オフセット集積回路パッケージオンパッケージ積層システム100の一部の上に低いプロファイルを維持する。

#### 【0019】

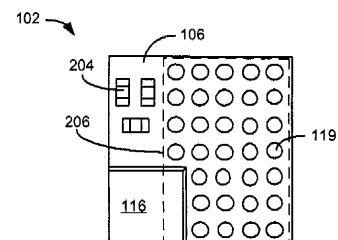

ここで図2を参照して、この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システム100のためのベースパッケージ102の上面図が示される。図1のベースパッケージ102の上面図は、図1のベース上部面106上の、図1のベースパッケージ本体116を示し、ベース上部面106は、図1のコンタクトパッド119のアレイおよび受動構成要素204を有する。アウトライン206は、図1のオフセットパッケージ120によって覆われることになる領域を示す。コンタクトパッド119のアレイは、図1のオフセットパッケージ120の、図1のシステム相互接続部118と整列するように間隔をあけられる。コンタクトパッド119の非対称的なアレイは、オフセットパッケージ120がベースパッケージ本体116上に延在することを可能にする。

#### 【0020】

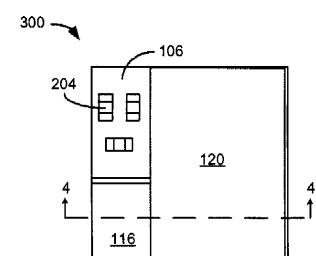

ここで図3を参照して、この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システム100の組立てられたパッケージ300の上面図が示される。組立てられたパッケージ300の上面図は、ベースパッケージ本体116、受動構成要素204、および上に取付けられたオフセットパッケージ120を有するベース上部面106

10

20

30

40

50

を示す。切断線 4 - 4 は、図 4 における図面の位置を示す。

【 0 0 2 1 】

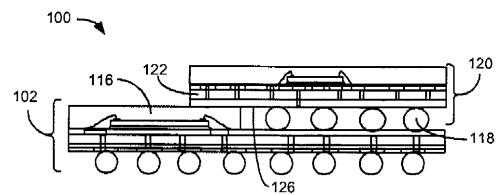

ここで図 4 を参照して、切断線 4 - 4 に沿った図 3 のオフセット集積回路パッケージオンパッケージ積層システム 100 の断面図が示される。オフセット集積回路パッケージオンパッケージ積層システム 100 の断面図は、上に取付けられたオフセットパッケージ 120 を有するベースパッケージ 102 を示す。オフセット基板 122 の底部面 126 はベースパッケージ本体 116 の上にある。ベースパッケージ本体 116 は、リフロープロセス中にシステム相互接続部 118 の崩壊を防ぐオフセットパッケージ 120 を支持する。

【 0 0 2 2 】

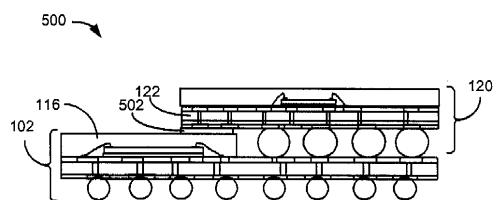

ここで図 5 を参照して、この発明の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システム 500 の断面図が示される。オフセット集積回路パッケージオンパッケージ積層システム 500 の断面図は、システム相互接続部 118 を介して電気的に結合されるオフセットパッケージ 120 を有するベースパッケージ 102 を示す。ダイ接着材料またはエポキシ樹脂などの隙間充填接着剤 502 が、ベースパッケージ本体 116 とオフセット基板 122 の底部面 126 との間に塗布される。隙間充填接着剤 502 の塗布は、パッケージ構造にさらなる機械的な安定性をもたらす。

【 0 0 2 3 】

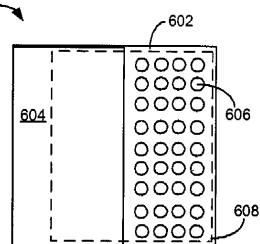

ここで図 6 を参照して、この発明の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システム 100 のためのベースパッケージ 600 の上面図が示される。ベースパッケージ 600 の上面図は、ベースモールドキャップ 604、システムコンタクト 606 のアレイ、およびアウトライン 608 を有するベース基板上部 602 を示し、アウトライン 608 は図 1 のオフセットパッケージ 120 を加えることによって覆われるであろう領域を示す。

【 0 0 2 4 】

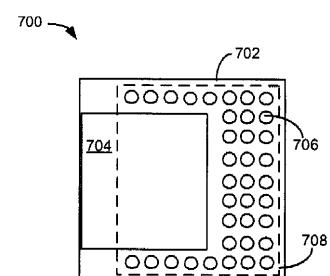

ここで図 7 を参照して、この発明の別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システム 100 のためのベースパッケージ 700 の上面図が示される。ベースパッケージ 700 の上面図は、ベースモールドキャップ 704、ベースモールドキャップ 704 の周りに部分的に分散されるコンタクトパッド 706 のアレイを有するベース基板上部 702 を示す。アウトライン 708 は、図 1 のオフセットパッケージ 120 が加えられる場合に、それを加えることによって覆われるであろう領域を示す。コンタクトパッド 706 のアレイは、ベースパッケージ 700 とオフセットパッケージ 120 との間に電気的なインターフェイスをもたらす。

【 0 0 2 5 】

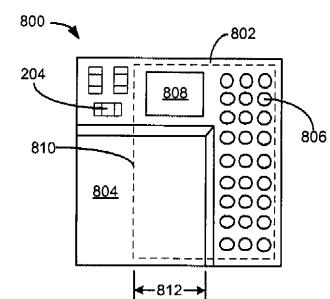

ここで図 8 を参照して、この発明のさらに別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システム 100 のためのベースパッケージ 800 の上面図が示される。ベースパッケージ 800 の上面図は、ベースモールドキャップ 804、システムコンタクトパッド 806 のアレイ、フリップチップ集積回路などの能動素子 808、受動構成要素 204、およびオフセットパッケージアウトライン 810 を有するベース基板上部 802 を示し、オフセットパッケージアウトライン 810 は図 1 のオフセットパッケージ 120 を加えることによって覆われるであろう領域を示す。オーバーラップ領域 812 は、ベースモールドキャップ 804 とオフセットパッケージ 120 との間の接触領域を示す。ベースモールドキャップ 804 の角はオフセットパッケージ 120 によって覆われることになり、オフセットパッケージ 120 はベースモールドキャップ 804 の上に置かれることになる。能動素子 808 はオフセットパッケージ 120 の下に置かれ、図 1 のオフセット基板 122 の、図 1 の底部面 126 と接触することはない。

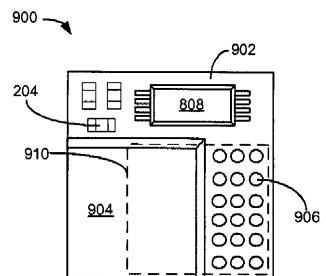

【 0 0 2 6 】

ここで図 9 を参照して、この発明のさらに別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システム 100 のためのベースパッケージ 900 の上面図が示される。ベースパッケージ 900 の上面図は、ベースモールドキャップ 904、システムコンタクトパッド 906 のアレイ、小さなアウトラインの集積回路などの図 8 の

10

20

30

40

50

能動素子 808、受動構成要素 204、およびオフセットパッケージアウトライン 910 を有するベース基板上部 902 を示し、オフセットパッケージアウトライン 910 は図 1 のオフセットパッケージ 120 を加えることによって覆われるであろう領域を示す。オフセットパッケージ 120 は、オフセットパッケージがベースモールドキャップの端縁と整列された状態で、ベースモールドキャップ 904 の上に置かれることになる。能動素子 808 は、ベースパッケージ 900 内の回路、システムコンタクトパッドのアレイ、またはそれらの組合せに電気的に接続される能動的な小さなアウトラインの集積回路構成要素であり得る。

【0027】

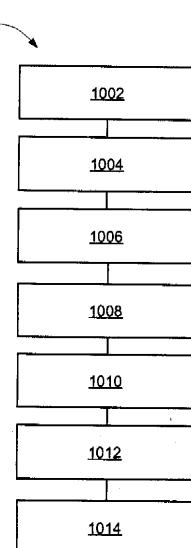

ここで図 10 を参照して、この発明の実施例に従ってオフセット集積回路パッケージオンパッケージ積層システム 100 を製造するためのオフセット集積回路パッケージオンパッケージ積層システム 1000 のフロー図が示される。システム 1000 は、ブロック 1002 においてベース基板を設けることと、ブロック 1004 においてコンタクトパッドをベース基板上に形成することと、ブロック 1006 において第 1 の集積回路をベース基板上に取付けることと、ブロック 1008 においてベースパッケージ本体を第 1 の集積回路を囲むように形成することと、ブロック 1010 においてオフセット基板を設けることと、ブロック 1012 において第 2 の集積回路をオフセット基板上に取付けることと、ブロック 1014 においてオフセット基板をベースパッケージ本体上に置くことを含む、オフセット基板をコンタクトパッドに結合することとを含む。

【0028】

より詳細には、この発明の実施例に従って、オフセット集積回路パッケージオンパッケージ積層システムを製造するためのシステムは以下のとおりに実行される。

【0029】

1. システム相互接続部を有するベース基板を設けること。（図 1）

2. コンタクトパッドをベース基板上に形成すること。（図 1）

3. 第 1 の集積回路をコンタクトパッドに結合することを含む、第 1 の集積回路をベース基板上に取付けること。（図 1）

4. 成形材料を射出することを含む、ベースパッケージ本体を第 1 の集積回路を囲むように形成すること。（図 1）

5. システム相互接続部を設けることを含む、オフセット基板を設けること。（図 1）

6. オフセットパッケージ本体を第 2 の集積回路を覆って形成することを含む、第 2 の集積回路をオフセット基板上に取付けること。（図 1）

7. オフセット基板をベースパッケージ本体上に置くことを含む、オフセット基板をコンタクトパッドに結合すること。（図 1）

このように、この発明は多くの局面を有することが分かってきた。

【0030】

空間が限られている家庭用電子機器装置において、オフセット集積回路パッケージオンパッケージ積層システムは限られた空間により多くの機能を加えることができることが分かってきた。

【0031】

原理的な局面は、この発明がさらなるパッケージの大きさを追加することなくさらなる構成要素をベース基板上に追加する柔軟性を有することである。

【0032】

この発明のさらに別の重要な局面は、コストの低減、システムの単純化、および性能の向上という歴史的傾向をこの発明が有益に支持し、要求に応えることである。

【0033】

この発明のこれらのおよび他の有益な局面は、その結果、技術の状態を少なくとも次のレベルにまで推し進める。

【0034】

このように、この発明のオフセット集積回路パッケージオンパッケージ積層システムは

10

20

30

40

50

、利用可能な空間を減少させてきた家庭用電子機器において集積回路の密度を増大させるための重要で、今まで知られておらず、利用できなかつた解決策、機能、および機能的な局面を提供することが分かってきた。結果として生じるプロセスおよび構成は、単純明快なものであり、費用対効果が高く、複雑ではなく、非常に汎用性のある効果的なものであり、公知の技術を適合させることによって実現されることが可能、したがって、従来の製造プロセスおよび技術と十分に互換性のあるオフセット集積回路パッケージオンパッケージ積層装置を効率的および経済的に製造することに容易に適合される。

#### 【0035】

この発明は具体的な最良の形態に関連して記載されてきたが、多くの代替例、修正例、および変形例が上の記載の觀点で当業者に明らかであることが理解されるべきである。したがって、上の記載は、含まれる特許請求の範囲内のすべてのこのようないきな代替例、修正例、および変形例を包含するように意図される。これまで本明細書に記載されたすべての事項、または添付の図面に示されたすべての事項は、例示的および非限定的な意味で解釈されるべきである。

10

#### 【図面の簡単な説明】

#### 【0036】

【図1】この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システムの断面図である。

【図2】この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システムのためのベースパッケージの上面図である。

20

【図3】この発明の実施例におけるオフセット集積回路パッケージオンパッケージ積層システムの組立てられたパッケージの上面図である。

【図4】切断線4-4に沿った図3のオフセット集積回路パッケージオンパッケージ積層システムの断面図である。

【図5】この発明の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システムの断面図である。

【図6】この発明の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システムのためのベースパッケージの上面図である。

【図7】この発明の別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システムのためのベースパッケージの上面図である。

30

【図8】この発明のさらに別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システムのためのベースパッケージの上面図である。

【図9】この発明のさらに別の代替的な実施例におけるオフセット集積回路パッケージオンパッケージ積層システムのためのベースパッケージの上面図である。

【図10】この発明の実施例においてオフセット集積回路パッケージオンパッケージ積層システムを製造するためのオフセット集積回路パッケージオンパッケージ積層システムのフロー図である。

#### 【符号の説明】

#### 【0037】

104 ベース基板

40

110 第1の集積回路

116 ベースパッケージ本体

119 コンタクトパッド

122 オフセット基板

128 第2の集積回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(74)代理人 100109162

弁理士 酒井 將行

(72)発明者 イル・クウォン・シム

シンガポール、737938 シンガポール、ローズウッド・コンド、ローズウッド・ドライブ、

9、ナンバー・17-20

(72)発明者 ビョン・ジュン・ハン

シンガポール、259959 シンガポール、アードモア・パーク、15、ナンバー・08-02

(72)発明者 セン・グアン・チョウ

シンガポール、760131 シンガポール、イーシュン・ストリート、11、ブロック・131

、ナンバー・07-243

審査官 酒井 英夫

(56)参考文献 特開平08-222692 (JP, A)

特表2003-534643 (JP, A)

特開2004-241713 (JP, A)

特開2005-101132 (JP, A)

特開2001-044362 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/10

H01L 25/11

H01L 25/18