(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6562467号

(P6562467)

(45) 発行日 令和1年8月21日(2019.8.21)

(24) 登録日 令和1年8月2日(2019.8.2)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| H01L 23/12   | (2006.01) |

| H01L 21/3205 | (2006.01) |

| H01L 21/768  | (2006.01) |

| H01L 23/522  | (2006.01) |

|      |       |      |

|------|-------|------|

| H01L | 23/12 | 501B |

| H01L | 21/88 | T    |

請求項の数 16 (全 26 頁)

(21) 出願番号 特願2017-44923 (P2017-44923)

(22) 出願日 平成29年3月9日 (2017.3.9)

(65) 公開番号 特開2017-228762 (P2017-228762A)

(43) 公開日 平成29年12月28日 (2017.12.28)

審査請求日 平成29年9月12日 (2017.9.12)

(31) 優先権主張番号 10-2016-0077593

(32) 優先日 平成28年6月21日 (2016.6.21)

(33) 優先権主張国・地域又は機関

韓国 (KR)

(31) 優先権主張番号 10-2016-0112983

(32) 優先日 平成28年9月2日 (2016.9.2)

(33) 優先権主張国・地域又は機関

韓国 (KR)

前置審査

(73) 特許権者 503447036

サムスン エレクトロニクス カンパニー

リミテッド

大韓民国・16677・キョンギード・ス

ウォンーシ・ヨントン-ク・サムスン-ロ

・129

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

最終頁に続く

(54) 【発明の名称】ファンーアウト半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

貫通孔を有する第1接続部材と、

前記第1接続部材の貫通孔に配置され、接続パッドが配置された活性面と前記活性面とは反対側に配置された非活性面を有する半導体チップと、

前記半導体チップの非活性面の少なくとも一部を封止する封止材と、

前記第1接続部材と前記半導体チップの活性面上に配置された第2接続部材と、

を含み、

前記第1接続部材及び前記第2接続部材は、それぞれ前記接続パッドと電気的に接続された再配線層を含み、

前記半導体チップは、前記接続パッドの少なくとも一部を露出させる開口部を有するパッシベーション膜を含み、

前記第2接続部材の再配線層は、ビアを介して前記接続パッドと接続されて、

前記ビアは前記パッシベーション膜の少なくとも一部を覆い、

前記パッシベーション膜の前記開口部を囲み、且つ前記ビアと接する面の前記パッシベーション膜の全体の面積をS1とし、

前記パッシベーション膜を覆う前記ビアの面積をS2としたとき、

S2/S1は0.2から0.8であり、

前記パッシベーション膜の前記開口部を囲み、且つ前記ビアと接する面の前記パッシベーション膜の幅をWとし、

10

20

前記パッシベーション膜と接する前記ビアの縁が、前記パッシベーション膜の前記開口部を囲み、且つ前記ビアと接する面の前記パッシベーション膜の中心線Cから離れている距離をdとするとき、

d / Wは0.3以内であり、

前記半導体チップの非活性面は、前記第1接続部材の上面よりも下方に位置する、

ファン・アウト半導体パッケージ。

【請求項2】

前記ビアは、前記接続パッドの露出している表面をすべて覆う、

請求項1に記載のファン・アウト半導体パッケージ。

【請求項3】

前記ビアは、フィルドビア(Filled via)である、

請求項1または2に記載のファン・アウト半導体パッケージ。

【請求項4】

貫通孔を有する第1接続部材と、

前記第1接続部材の貫通孔に配置され、接続パッドが配置された活性面と前記活性面とは反対側に配置された非活性面を有する半導体チップと、

前記半導体チップの非活性面の少なくとも一部を封止する封止材と、

前記第1接続部材と前記半導体チップの活性面上に配置された第2接続部材と、

を含み、

前記第1接続部材及び前記第2接続部材は、それぞれ前記接続パッドと電気的に接続された再配線層を含み、

前記半導体チップは、前記接続パッドの少なくとも一部を露出させる開口部を有するパッシベーション膜を含み、

前記第2接続部材の再配線層は、ビアを介して前記接続パッドと接続されて、

前記ビアは前記パッシベーション膜の少なくとも一部を覆い、

前記第1接続部材は、

第1絶縁層と、

前記第1絶縁層の下側に埋め込まれた第1再配線層と、

前記第1絶縁層の上面上に配置され、下面が前記第1絶縁層の上面と接する第2再配線層と、

前記第1絶縁層を貫通し、前記第1再配線層及び前記第2再配線層を電気的に接続する第1ビアと、

前記第1絶縁層の上面上に配置され、前記第2再配線層を覆う第2絶縁層と、

前記第2絶縁層の上面上に配置され、下面が前記第2絶縁層の上面と接する第3再配線層と、及び

前記第2絶縁層を貫通し、前記第2再配線層及び前記第3再配線層を電気的に接続する第2ビアと

を含み、

前記第1再配線層及び前記第2再配線層は前記接続パッドと電気的に接続され、

前記半導体チップの非活性面は、前記第1接続部材の上面よりも下方に位置する、

ファン・アウト半導体パッケージ。

【請求項5】

前記第2接続部材の再配線層と前記第1再配線層との間の距離が、前記第2接続部材の再配線層と前記接続パッドとの間の距離よりも大きい、

請求項4に記載のファン・アウト半導体パッケージ。

【請求項6】

前記第1再配線層は、前記第2接続部材の再配線層よりも厚さが厚い、

請求項4または5に記載のファン・アウト半導体パッケージ。

【請求項7】

前記第1再配線層の下面是、前記接続パッドの下面より上側に位置する、

10

20

30

40

50

請求項 4 から 6 のいずれか一項に記載のファン - アウト半導体パッケージ。

【請求項 8】

前記第 2 再配線層は、前記半導体チップの活性面と非活性面との間に位置する、

請求項 4 から 7 のいずれか 1 項に記載のファン - アウト半導体パッケージ。

【請求項 9】

前記第 1 接続部材は、

第 1 絶縁層と、

前記第 1 絶縁層の両面に配置された第 1 再配線層及び第 2 再配線層と、

前記第 1 絶縁層上に配置され、前記第 1 再配線層を覆う第 2 絶縁層と、

前記第 2 絶縁層上に配置された第 3 再配線層と、

を含み、

前記第 1 再配線層、及び前記第 2 再配線層、及び前記第 3 再配線層は前記接続パッドと電気的に接続される、

請求項 1 から 3 のいずれか一項に記載のファン - アウト半導体パッケージ。

【請求項 10】

前記第 1 接続部材は、

前記第 1 絶縁層上に配置され、前記第 2 再配線層を覆う第 3 絶縁層と、

前記第 3 絶縁層上に配置された第 4 再配線層と、

をさらに含み、

前記第 4 再配線層は前記接続パッドと電気的に接続される、

請求項 9 に記載のファン - アウト半導体パッケージ。

【請求項 11】

前記第 1 絶縁層は、前記第 2 絶縁層よりも厚さが厚い、

請求項 9 または 10 に記載のファン - アウト半導体パッケージ。

【請求項 12】

前記第 3 再配線層は、前記第 2 接続部材の再配線層よりも厚さが厚い、

請求項 9 から 11 のいずれか一項に記載のファン - アウト半導体パッケージ。

【請求項 13】

前記第 1 再配線層は、前記半導体チップの活性面と非活性面との間に位置する、

請求項 9 から 12 のいずれか一項に記載のファン - アウト半導体パッケージ。

30

【請求項 14】

前記第 3 再配線層の下面是、前記接続パッドの下面より下側に位置する、

請求項 9 から 13 のいずれか一項に記載のファン - アウト半導体パッケージ。

【請求項 15】

前記ピアは、シード層と、導体層とを含む、

請求項 1 から 14 のいずれか一項に記載のファン - アウト半導体パッケージ。

【請求項 16】

前記シード層は、チタン (Ti)、チタン - タングステン (Ti - W)、モリブデン (Mo)、クロム (Cr)、ニッケル (Ni)、及びニッケル (Ni) - クロム (Cr) のうち一つ以上の金属材料を含む、

40

請求項 15 に記載のファン - アウト半導体パッケージ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージ、例えば、接続端子を半導体チップが配置された領域外にも拡張することができるファン - アウト半導体パッケージに関するものである。

【背景技術】

【0002】

最近、半導体チップに関する技術開発の主な傾向の一つは、部品のサイズを縮小することである。そこで、パッケージ分野においても、小型の半導体チップなどの需要の急増に

50

併し、サイズが小型でありながらも、多数のピンを実現することが要求されている。

【0003】

これに応えるために提案されたパッケージ技術の一つがファン・アウト半導体パッケージである。ファン・アウト半導体パッケージは、接続端子を半導体チップが配置されている領域外にも再配線し、サイズが小型でありながらも、多数のピンを実現可能とする。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の様々な目的の一つは、様々な原因で発生し得る接続パッドの腐食を防止することができるファン・アウト半導体パッケージを提供することにある。

10

【課題を解決するための手段】

【0005】

本発明により提案する様々な解決手段の一つは、接続パッドが露出している表面をビアで全て覆うことにより、高温または高湿度によって信頼性が損なわれる環境下において様々な原因で発生し得る接続パッドの腐食を防止する工夫である。

【0006】

本発明の一例によるファン・アウト半導体パッケージは、貫通孔を有する第1接続部材と、第1接続部材の貫通孔に配置され、接続パッドが配置された活性面及び活性面とは反対側に配置された非活性面を有する半導体チップと、第1接続部材及び半導体チップの非活性面の少なくとも一部を封止する封止材と、第1接続部材及び半導体チップの活性面上に配置された第2接続部材と、を備え、第1接続部材及び第2接続部材はそれぞれ接続パッドと電気的に接続された再配線層を含み、半導体チップは接続パッドの少なくとも一部を露出させる開口部を有するパッシベーション膜を含み、第2接続部材の再配線層はビアを介して接続パッドと接続され、ビアはパッシベーション膜の少なくとも一部を覆うように構成されている。

20

【発明の効果】

【0007】

本発明の様々な効果の一つとして、本発明によれば、様々な原因で発生し得る接続パッドの腐食を防止することができるファン・アウト半導体パッケージを提供することができる。

30

【図面の簡単な説明】

【0008】

【図1】電子機器システムの例を概略的に示すブロック図である。

【図2】電子機器の一例を概略的に示す斜視図である。

【図3】ファン・イン半導体パッケージのパッケージング前後を概略的に示す断面図である。

【図4】ファン・イン半導体パッケージのパッケージング過程を概略的に示す断面図である。

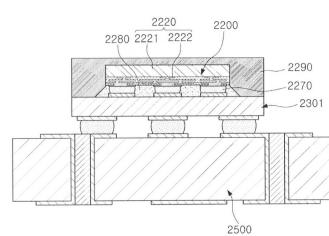

【図5】ファン・イン半導体パッケージがインターポーラ基板上に実装され、最終的に電子機器のメインボードに実装された場合を概略的に示す断面図である。

40

【図6】ファン・イン半導体パッケージがインターポーラ基板内に内蔵され、最終的に電子機器のメインボードに実装された場合を概略的に示す断面図である。

【図7】ファン・アウト半導体パッケージの概略的な形状を示す断面図である。

【図8】ファン・アウト半導体パッケージが電子機器のメインボードに実装された場合を概略的に示す断面図である。

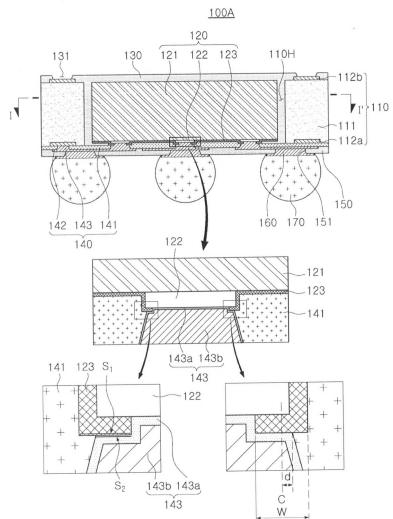

【図9】ファン・アウト半導体パッケージの一例を概略的に示す断面図である。

【図10】図9に示すファン・アウト半導体パッケージの概略的なI-I'の切断平面図である。

【図11】図9に示すファン・アウト半導体パッケージの第2接続部材のビアが半導体チップのパッシベーション膜を覆う位置によるストレス変化を概略的に示す図面である。

50

【図12】ファン - アウト半導体パッケージの他の一例を概略的に示す断面図である。

【図13】ファン - アウト半導体パッケージの他の一例を概略的に示す断面図である。

【図14】接続パッドに腐食が発生する場合を概略的に示す図面である。

【図15】電圧が印加されていない状態の接続パッドの腐食を概略的に示す図面である。

【図16】電圧が印加された状態の接続パッドの腐食を概略的に示す図面である。

【発明を実施するための形態】

【0009】

以下では、添付の図面を参照して本発明の好ましい実施形態について説明する。しかし、本発明の実施形態は様々な他の形態に変形することができ、本発明の範囲は以下で説明する実施形態に限定されない。また、本発明の実施形態は、当該技術分野で平均的な知識を有する者に本発明をより完全に説明するために提供されるものである。したがって、図面における要素の形状及び大きさなどはより明確な説明のために拡大縮小表示（または強調表示や簡略化表示）がされることがある。10

【0010】

電子機器

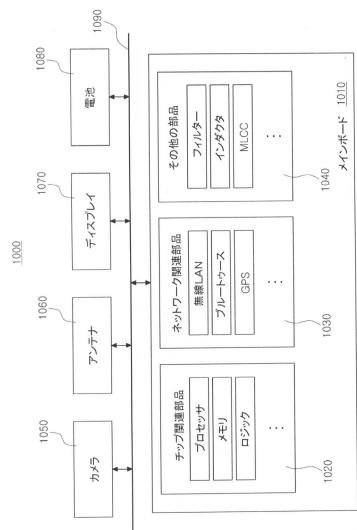

図1は電子機器システムの例を概略的に示すブロック図である。

【0011】

図面を参照すると、電子機器1000はメインボード1010を収容する。メインボード1010には、チップ関連部品1020、ネットワーク関連部品1030、及びその他の部品1040などが物理的及び/または電気的に接続されている。これらは、後述する他の部品とも結合されて、様々な信号ライン1090を形成する。20

【0012】

チップ関連部品1020としては、揮発性メモリー（例えば、DRAM）、不揮発性メモリー（例えば、ROM）、フラッシュメモリーなどのメモリーチップ；セントラルプロセッサ（例えば、CPU）、グラフィックプロセッサ（例えば、GPU）、デジタル信号プロセッサ、暗号化プロセッサ、マイクロプロセッサ、マイクロコントローラなどのアプリケーションプロセッサチップ；アナログ - デジタルコンバータ、ASIC(application-specific IC)などのロジックチップなどが含まれるが、これらに限定されるものではなく、これら以外にも、その他の形態のチップ関連部品が含まれ得ることはいうまでもない。また、これら部品1020が互いに組み合わされてもよいことはいうまでもない。30

【0013】

ネットワーク関連部品1030としては、Wi-Fi（IEEE 802.11ファミリなど）、WiMAX（IEEE 802.16ファミリなど）、IEEE 802.20、LTE（long term evolution）、EV-DO、HSPA+、HSUPA+、EDGE、GSM（登録商標）、GPS、GPRS、CDMA、TDMA、DECT、ブルートゥース（登録商標）（Bluetooth（登録商標））、3G、4G、5G、及びそれ以降のものとして指定された任意の他の無線及び有線プロトコルが含まれるが、これらに限定されるものではなく、これら以外にも、その他の多数の無線または有線標準やプロトコルのうち任意のものが含まれ得る。また、ネットワーク関連部品1030が、チップ関連部品1020とともに互いに組み合わされてもよいことはいうまでもない。40

【0014】

その他の部品1040としては、高周波インダクタ、フェライトインダクタ、パワーインダクタ、フェライトビーズ、LTCC（Low Temperature Co-Firing Ceramics）、EMI（Electro Magnetic Interference）フィルター、MLCC（Multi-Layer Ceramic Condenser）などが含まれるが、これらに限定されるものではなく、これら以外にも、その他の様々な用途のために用いられる受動部品などが含まれ得る。また、他の部品1040が、チップ関連部品1020及び/またはネットワーク関連部品103050

とともに互いに組み合わされてもよいことはいうまでもない。

**【0015】**

電子機器1000の種類に応じて、電子機器1000は、メインボード1010に物理的及び／または電気的に接続されているか接続されていない他の部品を含むことができる。他の部品としては、例えば、カメラ1050、アンテナ1060、ディスプレイ1070、電池1080、オーディオコーデック（図示せず）、ビデオコーデック（図示せず）、電力増幅器（図示せず）、羅針盤（図示せず）、加速度計（図示せず）、ジャイロスコープ（図示せず）、スピーカー（図示せず）、大容量記憶装置（例えば、ハードディスクドライブ）（図示せず）、CD(compact disk)（図示せず）、及びDVD(digital versatile disk)（図示せず）などが挙げられる。但し、これらに限定されるものではなく、これら以外にも、電子機器1000の種類に応じて様々な用途のために用いられるその他の部品などが含まれ得ることはいうまでもない。10

**【0016】**

電子機器1000は、スマートフォン(smart phone)、携帯情報端末(personal digital assistant)、デジタルビデオカメラ(digital video camera)、デジタルスチルカメラ(digital still camera)、ネットワークシステム(network system)、コンピューター(computer)、モニター(monitor)、タブレット(tablet)、ラップトップ(laptop)、ネットブック(netbook)、テレビジョン(television)、ビデオゲーム(video game)、スマートウォッチ(smart watch)、オートモーティブ(Automotive)などであることができる。但し、これらに限定されるものではなく、これら以外にも、データを処理する任意の他の電子機器であってもよいことはいうまでもない。20

**【0017】**

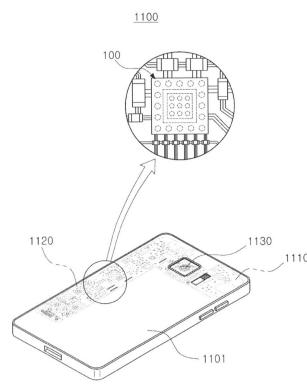

図2は電子機器の一例を概略的に示す斜視図である。

**【0018】**

図面を参照すると、半導体パッケージは、上述のような種々の電子機器において様々な用途に適用される。例えば、スマートフォン1100の本体1101の内部にはメインボード1110が収容されており、メインボード1110には種々の部品1120が物理的及び／または電気的に接続されている。また、カメラ1130のように、メインボード1110に物理的及び／または電気的に接続されているか接続されていない他の部品が本体1101内に収容されている。部品1120の一部はチップ関連部品であることができ、半導体パッケージ100は、例えば、そのうちアプリケーションプロセッサであることができるが、これに限定されるものではない。電子機器が必ずしもスマートフォン1100に限定されるものではなく、上述のように、他の電子機器であってもよいことはいうまでもない。30

**【0019】**

**半導体パッケージ**

一般に、半導体チップには、数多くの微細な電気回路が集積されているが、それ自体が半導体完成品としての役割を果たすことはできず、外部からの物理的衝撃または化学的浸蝕により損傷する可能性がある。したがって、半導体チップ自体をそのまま用いるのではなく、半導体チップをパッケージングして、パッケージングされた状態で電子機器などに用いている。40

**【0020】**

半導体パッケージングが必要な理由は、電気的接続という観点から、半導体チップと電子機器のメインボードの回路幅が異なるためである。具体的に、半導体チップは、接続パッドのサイズ及び接続パッド間の間隔が非常に微細であるのに対し、電子機器に用いられるメインボードは、部品実装パッドのサイズ及び部品実装パッド間の間隔が半導体チップのスケールより著しく大きい。したがって、半導体チップをこのようなメインボード上にそのまま取り付けることは困難であり、相互間の回路幅の差を緩和することができるパッ50

ケージング技術が要求される。

**【0021】**

このようなパッケージング技術により製造される半導体パッケージは、構造及び用途によって、ファン・イン半導体パッケージ(Fan-in semiconductor package)とファン・アウト半導体パッケージ(Fan-out semiconductor package)とに区分することができる。

**【0022】**

以下では、図面を参照して、ファン・イン半導体パッケージとファン・アウト半導体パッケージについてより詳細に説明する。

**【0023】**

(ファン・イン半導体パッケージ)

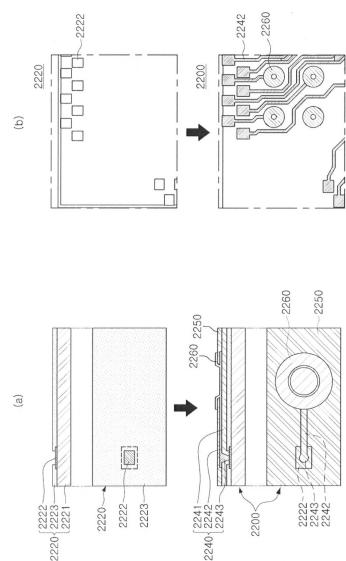

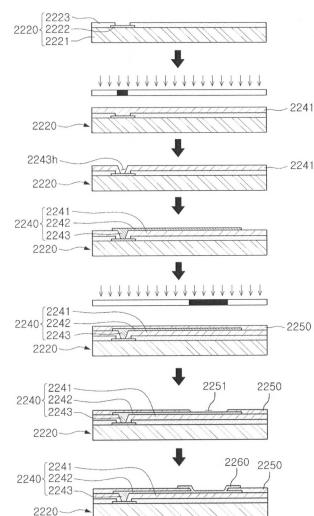

図3はファン・イン半導体パッケージのパッケージング前後を概略的に示す断面図であり、図4はファン・イン半導体パッケージのパッケージング過程を概略的に示す断面図である。

**【0024】**

図面を参照すると、半導体チップ2220は、シリコン(Si)、ゲルマニウム(Ge)、ガリウムヒ素(GaAs)などを含む本体2221と、本体2221の一面上に形成された、アルミニウム(Al)などの導電性物質を含む接続パッド2222と、本体2221の一面上に形成され、接続パッド2222の少なくとも一部を覆う酸化膜または窒化膜などのパッシベーション膜2223と、を含む、例えば、ペア(Bare)状態の集積回路(ASIC)であることができる。この際、接続パッド2222が非常に小さいため、集積回路(ASIC)は、電子機器のメインボードなどは勿論、中間レベルの印刷回路基板(PCB)にも実装されにくい。

**【0025】**

そのため、接続パッド2222を再配線するために、半導体チップ2220上に半導体チップ2220のサイズに応じて接続部材2240を形成する。接続部材2240は、半導体チップ2220上に感光性絶縁樹脂(PID)などの絶縁物質で絶縁層2241を形成し、接続パッド2222をオープンさせるビアホール2243hを形成した後、配線パターン2242及びビア2243を形成することで形成することができる。その後、接続部材2240を保護するパッシベーション層2250を形成し、開口部2251を形成した後、アンダーバンプ金属層2260などを形成する。すなわち、一連の過程を経て、例えば、半導体チップ2220、接続部材2240、パッシベーション層2250、及びアンダーバンプ金属層2260を含むファン・イン半導体パッケージ2200が製造される。

**【0026】**

このように、ファン・イン半導体パッケージは、半導体チップの接続パッド、例えば、I/O(Input/Output)端子のすべてを素子の内側に配置したパッケージ形態である。ファン・イン半導体パッケージは、電気的特性に優れており、安価なコストで生産することができる。したがって、スマートフォンに内蔵される多くの素子がファン・イン半導体パッケージの形態で製作されており、具体的には、小型で、且つ速い信号伝達を実現するよう開発が行われている。

**【0027】**

しかし、ファン・イン半導体パッケージは、I/O端子のすべてを半導体チップの内側に配置しなければならないため、空間的な制約が多い。したがって、このような構造を、多数のI/O端子を有する半導体チップや、サイズが小さい半導体チップに適用するには困難な点がある。また、このような欠点により、電子機器のメインボードにファン・イン半導体パッケージを直接実装して用いることができない。これは、再配線工程により半導体チップのI/O端子のサイズ及び間隔を拡大したとしても、電子機器のメインボードに直接実装可能な程度のサイズ及び間隔を有するわけではないためである。

**【0028】**

10

20

30

40

50

図5はファン・イン半導体パッケージがインターポーラ基板上に実装され、最終的に電子機器のメインボードに実装された場合を概略的に示した断面図であり、図6はファン・イン半導体パッケージがインターポーラ基板内に内蔵され、最終的に電子機器のメインボードに実装された場合を概略的に示した断面図である。

#### 【0029】

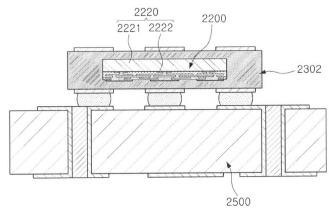

図面を参照すると、ファン・イン半導体パッケージ2200は、半導体チップ2220の接続パッド2222、すなわち、I/O端子がインターポーラ基板2301によりさらに再配線され、最終的には、インターポーラ基板2301上にファン・イン半導体パッケージ2200が実装された状態で電子機器のメインボード2500に実装することができる。この際、半田ボール2270などはアンダーフィル樹脂2280などにより固定することができ、外側はモールディング材2290などで覆うことができる。または、ファン・イン半導体パッケージ2200は、別のインターポーラ基板2302内に内蔵(Emb edded)されてもよく、内蔵された状態で、インターポーラ基板2302により半導体チップ2220の接続パッド2222、すなわち、I/O端子がさらに再配線され、最終的に電子機器のメインボード2500に半導体パッケージを実装することができる。10

#### 【0030】

このように、ファン・イン半導体パッケージは電子機器のメインボードに直接実装された状態で用いることが困難であるため、別のインターポーラ基板上に実装された後、さらにパッケージング工程を経て電子機器のメインボードに実装されるか、またはインターポーラ基板内に内蔵された状態で電子機器のメインボードに実装されて用いられる。20

#### 【0031】

(ファン・アウト半導体パッケージ)

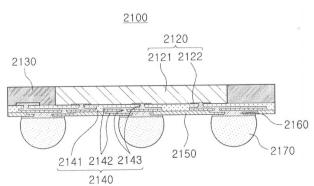

図7はファン・アウト半導体パッケージの概略的な形状を示す断面図である。

#### 【0032】

図面を参照すると、ファン・アウト半導体パッケージ2100は、例えば、半導体チップ2120の外側が封止材2130に保護され、半導体チップ2120の接続パッド2122が接続部材2140によって半導体チップ2120の外側まで再配線されている。この際、接続部材2140上にパッシベーション層2150をさらに形成することができ、パッシベーション層2150の開口部には、アンダーバンプ金属層2160をさらに形成することができる。アンダーバンプ金属層2160上に半田ボール2170をさらに形成することができる。半導体チップ2120は、本体2121、接続パッド2122、パッシベーション膜(図示せず)などを含む集積回路(IC)であることができる。接続部材2140は、絶縁層2141、絶縁層2241上に形成された再配線層2142、及び接続パッド2122と再配線層2142などを電気的に接続するビア2143を含むことができる。30

#### 【0033】

このように、ファン・アウト半導体パッケージは、半導体チップ上に形成された接続部材により、半導体チップの外側までI/O端子を再配線して配置した形態である。上述のように、ファン・イン半導体パッケージは、半導体チップのI/O端子のすべてを半導体チップの内側に配置しなければならず、そのため、素子のサイズが小さくなると、ボールのサイズ及びピッチを減少させなければならないため、標準化されたボールレイアウトを用いることができない。これに対し、ファン・アウト半導体パッケージは、このように半導体チップ上に形成された接続部材により、半導体チップの外側までI/O端子を再配線して配置した形態であるため、半導体チップのサイズが小さくなても標準化されたボールレイアウトをそのまま用いることができる。したがって、後述のように、電子機器のメインボードに別のインターポーラ基板がなくても半導体パッケージを実装することができる。40

#### 【0034】

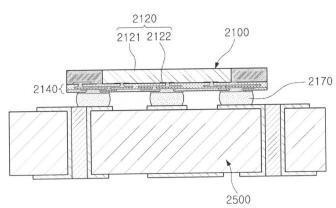

図8はファン・アウト半導体パッケージが電子機器のメインボードに実装された場合を概略的に示した断面図である。50

## 【0035】

図面を参照すると、ファン・アウト半導体パッケージ2100は半田ボール2170などを介して電子機器のメインボード2500に実装することができる。すなわち、上述のように、ファン・アウト半導体パッケージ2100は、半導体チップ2120上に半導体チップ2120のサイズを超えるファン・アウト領域まで接続パッド2122を再配線できる接続部材2140を形成するため、標準化されたボールレイアウトをそのまま用いることができる。その結果、別のインターポーラ基板などがなくても電子機器のメインボード2500に半導体パッケージを実装することができる。

## 【0036】

このように、ファン・アウト半導体パッケージは、別のインターポーラ基板がなくても電子機器のメインボードに実装することができるため、インターポーラ基板を用いるファン・イン半導体パッケージに比べてより薄い厚さを実現することができ、小型化及び薄型化が可能である。また、耐熱特性及び電気的特性に優れるため、モバイル製品に特に好適である。また、印刷回路基板（P C B）を用いる一般的なP O P（P a c k a g e o n P a c k a g e）タイプに比べて、よりコンパクトに実現することができ、反り返り現象の発生による問題を解決することができる。10

## 【0037】

一方、ファン・アウト半導体パッケージは、このように半導体チップを電子機器のメインボードなどに実装するための、また、外部からの衝撃から半導体チップを保護するためのパッケージ技術を意味するものであり、本発明の実施形態とはスケール、用途などが異なり、また、ファン・イン半導体パッケージが内蔵されるインターポーラ基板などの印刷回路基板（P C B）とも異なる概念である。20

## 【0038】

以下では、様々な原因により発生し得る接続パッドの腐食を防止することができるファン・アウト半導体パッケージについて図面を参照して説明する。

## 【0039】

図9はファン・アウト半導体パッケージの一例を概略的に示した断面図であり、図10は図9に示すファン・アウト半導体パッケージをI-I'線に沿って切って見た場合の断面図である。

## 【0040】

図面を参照すると、一例によるファン・アウト半導体パッケージ100Aは、貫通孔110Hを有する第1接続部材110と、第1接続部材110の貫通孔110Hに配置され、接続パッド122が配置された活性面及び活性面とは反対側に配置された非活性面を有する半導体チップ120と、第1接続部材110及び半導体チップ120の非活性面の少なくとも一部を封止する封止材130と、第1接続部材110及び半導体チップ120の活性面上に配置された第2接続部材140と、第2接続部材140上に配置されたパッシベーション層150と、パッシベーション層150上に配置され、パッシベーション層150の開口部151上に配置されたアンダーバンプ金属層160と、アンダーバンプ金属層160上に配置された接続端子170と、を含む。30

## 【0041】

半導体チップ120は、接続パッド122の少なくとも一部を露出させる開口部を有するパッシベーション膜123を含む。接続パッド122は、第2接続部材140のビア143を介して再配線層142と接続される。この際、ビア143はパッシベーション膜123の少なくとも一部を覆う。したがって、パッシベーション膜123の開口部により露出している接続パッド122の表面は、ビア143によってすべて覆われる。すなわち、接続パッド122は絶縁層141と接していない。40

## 【0042】

通常、半導体パッケージは、前工程でシリコンウェハーに回路が形成されたチップを、後工程でリードフレーム基板に実装してからモールディングする、伝統的な方式のパッケージング方法により製造されてきた。しかし、最近は、リードフレーム基板を用いず、チ50

ップを先にモールディングし、モールディング領域まで含む領域に微細回路を直接形成する、ファン - アウトパッケージング技術が浮上している。ファン - アウトパッケージング技術は、チップの接続パッドが露出した状態でモールディングを先に行うこと、微細な回路及び接続端子の形成領域をモールディング領域まで拡張する技術であって、低コストなパッケージモールディング技術を用いて、実装に必要な I / O 端子の数及び離間間隔に必要な空間を確保することができる。したがって、超小型化 / 高集積化した高価なシリコンウェハー内にチップを内蔵してボードとの接続性を確保することができるだけでなく、リードフレーム基板を用いないため原価を低減でき、さらには、配線距離を短縮することでインダクタンス及び消費電力を低減することができる。

## 【0043】

10

実際に、半導体産業のシリコン前工程の微細化競争がほぼ物理的限界に達しているため、シリコンウェハーの小型化の限界及び新しい露光方式である EUV ( Extreme Ultra-violet ) リソグラフィ技術の投資負担によって、ファン - アウトウェハーレベルパッケージを含む低コストなチップパッケージング技術の開発が加速化している。しかし、各構成材料の薄層化による微小部位へのストレスの集中に起因して、ボード実装段階における落下及び加速に対する信頼性が不足することによって、長期間の量産に適用できないという限界がある。このようなボード実装段階における信頼性を改善するために、実装後にパッケージとボードとを接続する接続端子の間の空間を接合樹脂で満たすアンダーフィル工法が考えられる。

## 【0044】

20

ところが、アンダーフィル工法では、工程性を確保するために、再作業が可能な材料を用いる必要があり、このような材料には、C1 イオンが相当以上の濃度で含まれている。このようにアンダーフィル材料に含まれた C1 イオンは、図 14 に例示的に示したように、高温または高湿度によって信頼性が損なわれる環境 ( THB ; Temperature Humidity Bias ) 下で高分子絶縁層 141' に拡散され、半導体チップの接続パッド 122' に到達し得る。このように到達した C1 イオンは、図 15 及び図 16 に例示的に示したように、電圧が印加されていない状態及び電圧が印加されている状態の両方で、半導体チップの接続パッドの腐食を引き起こす原因となり得る。このような C1 イオンによる腐食を防止するために、アンダーフィル工程中における C1 イオンの低減、C1 イオン捕獲層の挿入、ダミー電極の追加などが考えられる。しかし、アンダーフィル工程中における C1 イオンの低減は再作業性を低下させ、C1 イオン捕獲層は、殆どの場合に無機フィラーを必要とするため、微細パターンを実現しなければならない絶縁層内に挿入することが困難である。また、ダミー電極の挿入は、実際には接続パッドの腐食速度を単に遅らせるだけであるため、高温または高湿度によって長期間をかけて進行する信頼性劣化を防止する条件を確保するための根本的な対策とはならない。

30

## 【0045】

これに対し、一例によるファン - アウト半導体パッケージ 100A のように、パッシベーション膜 123 の少なくとも一部まで覆うように第 2 接続部材 140 のビア 143 を形成して、接続パッド 122 が絶縁層 141 と接していないように、すなわち、ビア 143 によって接続パッド 122 がイオンに露出する経路を遮断する被覆を行う場合、接続パッド 122 へのイオン流入を効果的に遮断することができ、その結果、高温または高湿度によって信頼性が損なわれる環境下において様々な原因で発生し得る上述のような半導体チップ 120 の接続パッド 122 の腐食を防止することができる。

40

## 【0046】

一方、パッシベーション膜 123 の開口部を囲み、ビア 143 と接する面のパッシベーション膜 123 の幅を W とし、パッシベーション膜 123 と接するビア 143 の縁が、パッシベーション膜 123 の開口部を囲み、且つビア 143 の上記縁がビア 143 と接する面のパッシベーション膜 123 の中心線 C から離間した距離を d とするとき、d / W が 0 . 3 以内となるようにビア 143 を形成することができる。ここで、d は内側方向 d<sub>1</sub> または外側方向 d<sub>2</sub> における離隔距離であることができる。このように、ビア 143 の縁が

50

パッシベーション膜123の内側及び外側の縁から20%以上離れる位置に位置するよう<sup>。</sup>にビア143を形成する場合、耐ストレスの側面において安定な構造となり得る。ビア143の縁がパッシベーション膜123の縁の近くに位置する場合、パッシベーション膜123にかかるストレスが増加してT/Cの信頼性が低下する問題が発生する可能性がある。

#### 【0047】

また、パッシベーション膜123の開口部を囲み、且つビア143と接する面のパッシベーション膜123の全体の面積をS<sub>1</sub>とし、パッシベーション膜123を覆うビア143の面積をS<sub>2</sub>としたとき、S<sub>2</sub>/S<sub>1</sub>が0.2~0.8程度となるようにビア143を形成することができる。同様の観点から、ビア143の縁がパッシベーション膜123の内側及び外側の縁から20%以上離間する位置にビア143を形成する場合、耐ストレスの側面において安定な構造となり得るため、パッシベーション膜123を覆うビア143の面積は全体の面積の20%~80%程度であり、このような範囲内で耐ストレスの側面において最も安定な構造となり得る。<sup>10</sup>

#### 【0048】

一方、ビアはフィルドビア(Filled via)であってもよい。ビアがこのようにフィルドビアである場合、金属の比率(proportion)が上がり耐ストレスの側面においてより安定な構造となるため、より効果的にイオン流入を遮断することができる。

#### 【0049】

以下、一例によるファン・アウト半導体パッケージ100Aに含まれるそれぞれの構成についてより詳細に説明する。<sup>20</sup>

#### 【0050】

第1接続部材110は、接続パッド122を再配線させる再配線層112a、112bを含むことで、第2接続部材140の層数を減少させることができる。必要に応じて、具体的な材料に応じてパッケージ100Aの剛性を維持することができ、封止材130の厚さの均一性を確保するなどの役割を果たすことができる。場合に応じて、第1接続部材110により、一例によるファン・アウト半導体パッケージ100Aをパッケージオンパッケージ(Package on Package)の一部として用いることができる。第1接続部材110は貫通孔110Hを有する。貫通孔110H内には、半導体チップ120が第1接続部材110と所定距離を隔てて離隔されるように配置される。半導体チップ120の側面の周囲は第1接続部材110により囲まれることができる。但し、これは一例に過ぎず、他の形態に多様に変形されることができ、その形態に応じて他の機能を担うことができる。<sup>30</sup>

#### 【0051】

第1接続部材110は、第2接続部材140と接する絶縁層111と、第2接続部材140と接して絶縁層111に埋め込まれた第1再配線層112aと、絶縁層111の第1再配線層112aが埋め込まれた側とは反対側に配置された第2再配線層112bと、を含む。第1接続部材110は、絶縁層111を貫通して第1及び第2再配線層112a、112bを電気的に接続するビア113を含む。第1及び第2再配線層112a、112bは接続パッド122と電気的に接続される。第1再配線層112aを絶縁層111内に埋め込む場合、第1再配線層112aの厚さによって発生する段差が最小化され<sup>40</sup>、第2接続部材140の絶縁距離が一定になる。すなわち、第2接続部材140の再配線層142から絶縁層111の下面までの距離と、第2接続部材140の再配線層142から接続パッド122までの距離との差は、第1再配線層112aの厚さより小さい。したがって、第2接続部材140の高密度配線設計が容易であるという利点がある。

#### 【0052】

絶縁層111の材料は特に限定されず、例えば、絶縁物質を用いることができる。この際、絶縁物質としては、エポキシ樹脂などの熱硬化性樹脂、ポリイミドなどの熱可塑性樹脂、またはこれら樹脂が無機フィラーとともにガラス纖維(Glass Cloth、G<sup>50</sup>

lass Fabric)などの芯材に含浸された樹脂、例えば、プリプレグ (prep reg)、ABF (Ajinomoto Build-up Film)、FR-4、BT (Bismaleimide Triazine)などが用いられることができる。必要に応じて、感光性絶縁 (Photo Imageable Dielectric: PID) 樹脂を用いてもよい。

#### 【0053】

再配線層 112a、112b は、半導体チップ 120 の接続パッド 122 を再配線する役割を果たすものであって、形成物質としては、銅 (Cu)、アルミニウム (Al)、銀 (Ag)、スズ (Sn)、金 (Au)、ニッケル (Ni)、鉛 (Pb)、チタン (Ti)、またはこれらの合金などの導電性物質を用いることができる。再配線層 112a、112b は、該当層の設計デザインに応じて様々な機能を担うことができる。例えば、グランド (Ground: GND) パターン、パワー (Power: PWR) パターン、信号 (Signal: S) パターンなどを含むことができる。ここで、信号 (S) パターンは、グランド (GND) パターン、パワー (PWR) パターンなどを除いた各種信号、例えば、データ信号などを含む。また、ビアパッド、接続端子パッドなどを含むことができる。制限されない一例として、再配線層 112a、112b のすべてがグランドパターンを含むことができ、この場合、第 2 接続部材 140 の再配線層 142 にグランドパターンを最小化して形成することができるため、配線の設計自由度を向上させることができる。

#### 【0054】

再配線層 112a、112b のうち、封止材 130 に形成された開口部 131 を介して露出した一部の再配線層 112b 上には、必要に応じて表面処理層 (図示せず) をさらに形成することができる。表面処理層 (図示せず) は、公知のものであれば特に限定されるものではなく、例えば、電解金めっき、無電解金めっき、OSP または無電解スズめっき、無電解銀めっき、無電解ニッケルめっき / 置換金めっき、DIGめっき、HASL などにより形成することができる。

#### 【0055】

ビア 113 は、互いに異なる層に形成された再配線層 112a、112b を電気的に接続させ、その結果、第 1 接続部材 110 内に電気的経路を形成する。ビア 113 の形成物質としても導電性物質を用いることができる。ビア 113 は、図 10 に示したように、導電性物質で完全に充填されていてもよく、または導電性物質がビアホールの壁面に沿って形成されたものであってもよい。また、テーパ状だけでなく、円筒状など公知のすべての形状が適用されることができる。

#### 【0056】

半導体チップ 120 は、数百～数百万個以上の素子が一つのチップ内に集積化されている集積回路 (Integrated Circuit: IC) であることができる。集積回路は、例えば、セントラル・プロセッサ・ユニット (例えば、CPU)、グラフィックプロセッサ (例えば、GPU)、デジタル信号プロセッサ、暗号化プロセッサ、マイクロプロセッサ、マイクロコントローラなどのアプリケーションプロセッサチップができるが、これに限定されるものではない。半導体チップ 120 は、活性ウェハーをベースとして形成することができ、この場合、本体 121 をなす母材としては、シリコン (Si)、ゲルマニウム (Ge)、ガリウムヒ素 (GaAs) などが用いられることがある。本体 121 には様々な回路を形成することができる。接続パッド 122 は、半導体チップ 120 を他の構成要素と電気的に接続させるためのものであって、その形成物質としては、特に限定せずにアルミニウム (Al) などの導電性物質を用いることができる。本体 121 上には接続パッド 122 を露出させる開口部を有するパッシベーション膜 123 を形成することができる。パッシベーション膜 123 は、SiO などの酸化膜または SiN などの窒化膜などであってもよく、または酸化膜と窒化膜の二重層であってもよい。パッシベーション膜 123 により、接続パッド 122 の下面是封止材 130 の下面と段差を有することができ、その結果、封止材 130 が接続パッド 122 の下面へブリードすることをある程度防止することができる。その他の必要な位置に、絶縁膜 (図示せず) など

10

20

30

40

50

がさらに配置されてもよい。

#### 【0057】

半導体チップ120の非活性面は、第1接続部材110の第2再配線層112bの上面よりも下方に位置することができる。例えば、半導体チップ120の非活性面は、第1接続部材110の絶縁層111の上面よりも下方に位置することができる。半導体チップ120の非活性面と第1接続部材110の第2再配線層112bの上面との高さの差は2μm以上、例えば、5μm以上とすることができる。この場合、半導体チップ120の非活性面の角部分で発生するクラックを効果的に防止することができる。また、封止材130を適用する場合における、半導体チップ120の非活性面上の絶縁距離のばらつきを最小化することができる。

10

#### 【0058】

封止材130は第1接続部材110及び/または半導体チップ120を保護することができる。封止形態は特に制限されず、第1接続部材110及び/または半導体チップ120の少なくとも一部を囲む形態であればよい。例えば、封止材130は第1接続部材110及び半導体チップ120の非活性面を覆うことができ、貫通孔110Hの壁面と半導体チップ120の側面との間の空間を充填することができる。また、封止材130は、半導体チップ120のパッシベーション膜123と第2接続部材140との間の空間の少なくとも一部を充填することもできる。一方、封止材130が貫通孔110H内を充填することで、接着剤の役割を果たすとともに、バックリングを減少させることができる。

20

#### 【0059】

封止材130の具体的な物質としては特に限定されず、例えば、絶縁物質が用いられることがある。この際、絶縁物質としては、同様にエポキシ樹脂などの熱硬化性樹脂、ポリイミドなどの熱可塑性樹脂、またはこれらに無機フィラーなどの補強材が含まれた樹脂、例えば、ABF、FR-4、BT、PID樹脂などを用いることができる。また、EMCなどの公知のモールディング物質を用いてもよいことはいうまでもない。必要に応じて、熱硬化性樹脂や熱可塑性樹脂が無機フィラーとともにガラス纖維(Glass Cloth、Glass Fabric)などの芯材に含浸された樹脂を用いてもよい。

20

#### 【0060】

封止材130は、複数の物質からなる複数の層で構成されることができる。例えば、貫通孔110H内の空間を第1封止材で充填し、その後、第1接続部材110及び半導体チップ120を第2封止材で覆うことができる。または、第1封止材を用いて貫通孔110H内の空間を充填するとともに、所定の厚さで第1接続部材110及び半導体チップ120を覆って、その後、第2封止材を用いて第1封止材の上を所定の厚さでさらに覆う形態でもよい。この他にも、様々な形態に応用されることがある。

30

#### 【0061】

封止材130には、電磁波遮断のために、必要に応じて導電性粒子を含有させることができる。導電性粒子としては、電磁波遮断が可能なものであればいかなるものでも用いることができ、例えば、銅(Cu)、アルミニウム(Al)、銀(Ag)、スズ(Sn)、金(Au)、ニッケル(Ni)、鉛(Pb)、チタン(Ti)、半田(solder)などで形成することができるが、これは一例に過ぎず、特にこれに限定されるものではない。

40

#### 【0062】

第2接続部材140は半導体チップ120の接続パッド122を再配線するための構成である。第2接続部材140により、様々な機能を有する数十~数百個の接続パッド122を再配線することができ、後述する接続端子170を介して、その機能に応じて外部に物理的及び/または電気的に接続されることができる。第2接続部材140は、絶縁層141、絶縁層141上に配置された再配線層142、及び絶縁層141を貫通して再配線層142を接続するビア143を含む。第2接続部材140は、単層で構成されてもよく、図面とは異なって複数の層で構成されてもよい。

#### 【0063】

50

絶縁層141の物質としては絶縁物質を用いることができる。この際、絶縁物質としては、上述のような絶縁物質の他にも、P I D樹脂などの感光性絶縁物質を用いることもできる。この場合、絶縁層141をより薄く形成することができ、ビア143のファインピッチをより容易に達成することができる。絶縁層141が多層で構成される場合、それぞれの絶縁層の物質は互いに同一であってもよく、互いに異なってもよい。絶縁層141が多層で構成される場合、これらが一体化され、その境界が不明確であってもよい。

#### 【0064】

再配線層142は、実質的に接続パッド122を再配線する役割を果たすものであって、形成物質としては、銅(Cu)、アルミニウム(Al)、銀(Ag)、スズ(Sn)、金(Au)、ニッケル(Ni)、鉛(Pb)、チタン(Ti)、またはこれらの合金などの導電性物質を用いることができる。再配線層142は、該当層の設計デザインに応じて様々な機能を担うことができる。例えば、グランド(Ground: GND)パターン、パワー(Power: PWR)パターン、信号(Signal: S)パターンなどを含む。ここで、信号(S)パターンは、グランド(GND)パターン、パワー(PWR)パターンなどを除いた各種信号、例えば、データ信号などを含む。また、ビアパッド、接続端子パッドなどを含むことができる。

#### 【0065】

再配線層142のうち一部の露出したパターン上には、必要に応じて表面処理層(図示せず)をさらに形成することができる。表面処理層(図示せず)は、当該技術分野において公知のものであれば特に限定されるものではなく、例えば、電解金めっき、無電解金めっき、OSPまたは無電解スズめっき、無電解銀めっき、無電解ニッケルめっき/置換金めっき、DIGめっき、HASLなどにより形成することができる。

#### 【0066】

ビア143は、互いに異なる層に形成された再配線層142や接続パッド122などを電気的に接続させ、その結果、パッケージ100A内に電気的経路を形成する。ビア143の形成物質としては、銅(Cu)、アルミニウム(Al)、銀(Ag)、スズ(Sn)、金(Au)、ニッケル(Ni)、鉛(Pb)、チタン(Ti)、またはこれらの合金などの導電性物質を用いることができる。ビア143は、パッシベーション膜123の少なくとも一部を覆い、接続パッド122の露出している表面をすべて覆う。ビア143はフィルドビア(Filled via)であってもよいが、必ずしもこれに限定されるものではない。ビア143は接続パッド122に向かうほど直径が小さくなるテーパ状であってもよいが、これに限定されるものではない。

#### 【0067】

ビア143は、シード層143a及び導体層143bを含むことができる。シード層143aは、露出している接続パッド122の表面、パッシベーション膜123の壁面、パッシベーション膜123の表面、及び絶縁層141を貫通するビアホールの壁面上に形成されることがある。導体層143bは、シード層143a上に形成されてビアホール内部を充填することができる。シード層143aは、チタン(Ti)、チタン-タングステン(Ti-W)、モリブデン(Mo)、クロム(Cr)、ニッケル(Ni)、及びニッケル(Ni)-クロム(Cr)のうち一つ以上の金属材料を含む第1シード層と、第1シード層上に配置され、導体層143bと同一の材料、例えば、銅(Cu)を含む第2シード層と、を含むことができる。第1シード層は接着の役割を果たし、第2シード層は下地のめつき層の役割を果たすことができる。導体層143bは、導電性物質、例えば、銅(Cu)、アルミニウム(Al)、銀(Ag)、スズ(Sn)、金(Au)、ニッケル(Ni)、鉛(Pb)、またはこれらの合金などを含むことができ、一般的には銅(Cu)を含むことができる。

#### 【0068】

パッシベーション膜123の開口部を囲み、且つビア143と接する面のパッシベーション膜123の幅をWとし、パッシベーション膜123と接するビア143の縁が、パッシベーション膜123の開口部を囲み、且つビア143の上記縁がビア143と接する面

10

20

30

40

50

のパッシベーション膜 123 の中心線 C から離間している距離を d とするとき、d / W が 0.3 以内となるようにビア 143 を形成することができる。ここで、d は内側方向 d<sub>1</sub> または外側方向 d<sub>2</sub> における離隔距離であることができる。このように、ビア 143 の縁がパッシベーション膜 123 の内側及び外側の縁から 20 % 以上離間した位置に位置するようにビア 143 を形成する場合、耐ストレスの側面において安定な構造となり得る。ビア 143 の縁がパッシベーション膜 123 の縁の近くに位置する場合、パッシベーション膜 123 のストレスが増加して T/C の信頼性が低下する問題が発生する可能性がある。

#### 【0069】

また、パッシベーション膜 123 の開口部を囲み、且つビア 143 と接する面のパッシベーション膜 123 の全体の面積を S<sub>1</sub> とし、パッシベーション膜 123 を覆うビア 143 の面積を S<sub>2</sub> としたとき、S<sub>2</sub> / S<sub>1</sub> が 0.2 ~ 0.8 程度となるようにビア 143 を形成することができる。同様の観点から、ビア 143 の縁がパッシベーション膜 123 の内側及び外側の縁から 20 % 以上離間する位置にビア 143 を形成する場合、耐ストレスの側面において安定な構造となり得るため、パッシベーション膜 123 を覆うビア 143 の面積は全体の面積の 20 % ~ 80 % 程度であり、このような範囲内で耐ストレスの側面において最も安定な構造となり得る。

#### 【0070】

第 1 接続部材 110 の再配線層 112a、112b の厚さは、第 2 接続部材 140 の再配線層 142 の厚さよりも厚くすることができる。第 1 接続部材 110 は、半導体チップ 120 以上の厚さを有することができるため、第 1 接続部材 110 に形成される再配線層 112a、112b も、そのスケールに応じてより大きいサイズに形成することができる。これに対し、第 2 接続部材 140 の薄型化のために、第 2 接続部材 140 の再配線層 142 は第 1 接続部材 110 の再配線層 112a、112b に比べて相対的に小さく形成することができる。

#### 【0071】

パッシベーション層 150 は、第 2 接続部材 140 を外部からの物理的損傷や化学的浸食などから保護するための構成である。パッシベーション層 150 は、第 2 接続部材 140 の再配線層 142 の少なくとも一部を露出させる開口部 151 を有することができる。開口部 151 は、再配線層 142 の一面を完全にまたは一部のみを露出させることができる。場合に応じて、側面も露出させることができる。

#### 【0072】

パッシベーション層 150 の形成物質としては、特に限定されず、例えば、感光性絶縁物質を用いることができる。または、半田レジストを用いてもよい。または、芯材は含まないが、フィラーは含む絶縁樹脂、例えば、無機フィラー及びエポキシ樹脂を含む A B F (Ajinomoto Build-up Film)などを用いることができる。パッシベーション層 150 の表面粗さは通常の場合より低くすることができる。このように表面粗さを低くする場合、回路の形成過程で発生し得る様々な副作用 (Side Effects)、例えば、表面におけるムラの発生、微細回路の実現の困難性などを改善することができる。

#### 【0073】

アンダーバンプ金属層 160 は、接続端子 170 の接続信頼性を向上させ、ボードレベル (board level) の信頼性を改善するための付加的な構成である。アンダーバンプ金属層 160 は、パッシベーション層 150 の開口部 151 の少なくとも一部を充填する。アンダーバンプ金属層 160 は公知の金属蒸着方法または金属メッキ方法により形成することができる。アンダーバンプ金属層 160 は公知の金属物質を含むことができる。例えば、電解銅めっきによりシード層を形成し、その上に無電解銅めっきによりめっき層を形成する方法によってアンダーバンプ金属層 160 を形成することができる。

#### 【0074】

接続端子 170 は、ファン - アウト半導体パッケージ 100A を外部と物理的及び/または電気的に接続させるための付加的な構成である。例えば、ファン - アウト半導体パッ

10

20

30

40

50

ケージ 100A は接続端子 170 を介して電子機器のメインボードに実装することができる。接続端子 170 は、導電性物質、例えば、半田 (solder) などで形成されることができるが、これは一例に過ぎず、材質が特にこれに限定されるものではない。接続端子 170 は、ランド (land)、ボール (ball)、ピン (pin) などであることができる。接続端子 170 は多重層または単一層からなることができる。多重層からなる場合には、銅ピラー (pillar) 及び半田を含むことができ、単一層からなる場合には、スズ・銀半田や銅を含むことができるが、これも一例に過ぎず、これに限定されるものではない。接続端子 170 の数、間隔、配置形態などは特に限定されず、通常の技術者であれば、設計事項に応じて十分に変形可能である。例えば、接続端子 170 の数は、半導体チップ 120 の接続パッド 122 の数に応じて数十～数千個とすることができます、それ以上またはそれ以下の数を有してもよい。

#### 【0075】

接続端子 170 の少なくとも一つはファン・アウト (fan-out) 領域に配置される。ファン・アウト領域とは、半導体チップ 120 が配置されている領域を外れた領域を意味する。すなわち、一例による半導体パッケージ 100A はファン・アウトパッケージである。ファン・アウト (fan-out) パッケージは、ファン・イン (fan-in) パッケージに比べて優れた信頼性を有し、多数の I/O 端子が実現可能であって、3D 接続 (3D interconnection) が容易である。また、BGA (Ball Grid Array) パッケージ、LGA (Land Grid Array) パッケージなどと異なって、別の基板なしに電子機器に実装可能であるため、薄型化が可能となり価格競争力に優れる。

#### 【0076】

図面に示していないが、必要に応じて、第 1 接続部材 110 の貫通孔 110H の内壁に金属層をさらに配置することができる。すなわち、半導体チップ 120 の側面の周囲が金属層により囲まれることもできる。金属層により、半導体チップ 120 から発生する熱をパッケージ 100A の上部及び / または下部に効果的に放出することができ、効果的な電磁波遮蔽が可能である。また、必要に応じて、第 1 接続部材 110 の貫通孔 110H 内に複数の半導体チップが配置されてもよく、第 1 接続部材 110 の貫通孔 110H が複数個設けられ、それぞれの貫通孔内に半導体チップが配置されてもよい。また、半導体チップの他に、別の受動部品とともに貫通孔 110H 内に封入することができる。また、パッシベーション層 150 上に表面実装部品を実装してもよい。

#### 【0077】

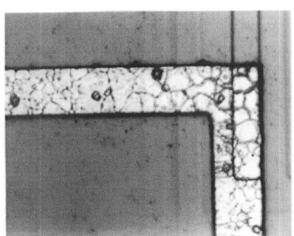

図 11 は図 9 に示すファン・アウト半導体パッケージの第 2 接続部材のビアが半導体チップのパッシベーション膜を覆う位置に応じたストレスの変化を概略的に示す図面である。

#### 【0078】

図面を参照すると、#1 は、ビア 143 の縁が、ビア 143 と接する面のパッシベーション膜 123 の内側の縁にほぼ近くなる場合 (20% 未満)、すなわち、パッシベーション膜 123 を覆うビア 143 の面積 S<sub>2</sub> が、ビア 143 と接する面のパッシベーション膜 123 の全体の面積 S<sub>1</sub> の 20% 未満である場合であり、#2～#5 は、ビア 143 の縁が、ビア 143 と接する面のパッシベーション膜 123 の中心線 C の近くに位置する場合 (離隔 : 30% 以内)、すなわち、パッシベーション膜 123 を覆うビア 143 の面積 S<sub>2</sub> が、ビア 143 と接する面のパッシベーション膜 123 の全体の面積 S<sub>1</sub> の 20%～80% である場合であり、#6 は、ビア 143 の縁が、ビア 143 と接する面のパッシベーション膜 123 の外側の縁にほぼ近くなる場合 (20% 未満)、すなわち、パッシベーション膜 123 を覆うビア 143 の面積 S<sub>2</sub> が、ビア 143 と接する面のパッシベーション膜 123 の全体の面積 S<sub>1</sub> の 80% を超える場合における T/C の信頼性テストの結果を示す。

#### 【0079】

これにより、パッシベーション膜 123 の開口部を囲み、且つビア 143 と接する面の

10

20

30

40

50

パッシベーション膜123の幅をWとし、パッシベーション膜123と接するビア143の縁が、パッシベーション膜123の開口部を囲み、且つビア143の上記縁がビア143と接する面のパッシベーション膜123の中心線Cから離間している距離をdとするとき、 $d / W$ が0.3以内となる場合、耐ストレスの側面において安定な構造となり得ることが分かる。また、パッシベーション膜123の開口部を囲み、且つビア143と接する面のパッシベーション膜123の全体の面積を $S_1$ とし、パッシベーション膜123を覆うビア143の面積を $S_2$ としたとき、 $S_2 / S_1$ が0.2～0.8程度である場合、耐ストレスの側面において安定な構造となり得ることが分かる。

#### 【0080】

図12はファン・アウト半導体パッケージの他の一例を概略的に示す断面図である。

10

#### 【0081】

図面を参照すると、他の一例によるファン・アウト半導体パッケージ100Bは、第1接続部材110が第2接続部材140と接する第1絶縁層111aと、第2接続部材140と接し、第1絶縁層111aに埋め込まれた第1再配線層112aと、第1絶縁層111aの第1再配線層112aが埋め込まれた側とは反対側上に配置された第2再配線層112bと、第1絶縁層111a上に配置され、第2再配線層112bを覆う第2絶縁層111bと、第2絶縁層111b上に配置された第3再配線層112cと、を含む。第1～第3再配線層112a、112b、112cは、接続パッド122と電気的に接続される。一方、図面には示していないが、第1及び第2再配線層112a、112bと第2及び第3再配線層112b、112cはそれぞれ第1及び第2絶縁層111a、111bを貫通する第1及び第2ビアを介して電気的に接続されることができる。

20

#### 【0082】

第1再配線層112aが埋め込まれているため、上述のように、第2接続部材140の絶縁層141の絶縁距離を実質的に一定に保つことができる。第1接続部材110が多数の再配線層112a、112b、112cを含むことで、第2接続部材140をさらに簡素化することができる。したがって、第2接続部材140の形成過程で発生する工程不良による収率低下を改善することができる。第1再配線層112aが第1絶縁層の内部に入り込むことで、第1絶縁層111aの下面と第1再配線層112aの下面が段差を有する。その結果、封止材130を形成する時に封止材130の形成物質がブリードして第1再配線層112aを汚染させることを防止することができる。

30

#### 【0083】

第1接続部材110の第1再配線層112aの下面は、半導体チップ120の接続パッド122の下面より上側に位置することができる。また、第2接続部材140の再配線層142と第1接続部材110の再配線層112aとの間の距離は、第2接続部材140の再配線層142と半導体チップ120の接続パッド122との間の距離より大きくすることができる。これは、第1再配線層112aが絶縁層111の内部に入り込むことができるようとするためである。第1接続部材110の第2再配線層112bは半導体チップ120の活性面と非活性面との間に位置することができる。第1接続部材110は半導体チップ120の厚さに対応する厚さに形成することができる。したがって、第1接続部材110の内部に形成された第2再配線層112bは、半導体チップ120の活性面と非活性面との間のレベルに配置されることができる。

40

#### 【0084】

第1接続部材110の再配線層112a、112b、112cの厚さは、第2接続部材140の再配線層142の厚さよりも厚くすることができる。第1接続部材110は半導体チップ120以上の厚さを有することができるため、再配線層112a、112b、112cも、そのスケールに応じてより大きいサイズに形成することができる。これに対し、第2接続部材140の再配線層142は、薄型化のために相対的に小さいサイズに形成することができる。

#### 【0085】

その他の構成については、一例によるファン・アウト半導体パッケージ100Aについて

50

ての説明と実質的に同一であるため、詳細な説明は省略する。

【0086】

図13はファン・アウト半導体パッケージの他の一例を概略的に示す断面図である。

【0087】

図面を参照すると、他の一例によるファン・アウト半導体パッケージ100Cは、第1接続部材110が、第1絶縁層111aと、第1絶縁層111aの両面に配置された第1再配線層112a及び第2再配線層112bと、第1絶縁層111a上に配置され、第1再配線層112aを覆う第2絶縁層111bと、第2絶縁層111b上に配置された第3再配線層112cと、第1絶縁層111a上に配置され、第2再配線層112bを覆う第3絶縁層111cと、第3絶縁層111c上に配置された第4再配線層112dと、を含む。第1～第4再配線層112a、112b、112c、112dは接続パッド122と電気的に接続される。第1接続部材110がさらに多数の再配線層112a、112b、112c、112dを含むことで、第2接続部材140をさらに簡素化することができる。10。したがって、第2接続部材140の形成過程で発生する工程不良による収率低下を改善することができる。一方、第1～第4再配線層112a、112b、112c、112dは、第1～第3絶縁層111a、111b、111cを貫通する第1～第3ビアを介して電気的に接続されることができる。

【0088】

第1絶縁層111aは第2絶縁層111b及び第3絶縁層111cより厚さを厚くすることができます。第1絶縁層111aは、基本的に剛性を維持するために相対的に厚くすることができます、第2絶縁層111b及び第3絶縁層111cは、より多数の再配線層112c、112dを形成するために導入したものであることができる。第1絶縁層111aは、第2絶縁層111b及び第3絶縁層111cと異なる絶縁物質を含むことができる。例えば、第1絶縁層111aは、芯材、無機フィラー、及び絶縁樹脂を含む、例えば、プリプレグであり、第2絶縁層111b及び第3絶縁層111cは、無機フィラー及び絶縁樹脂を含むABFまたは感光性絶縁フィルムであることができるが、これに限定されるものではない。20

【0089】

第1接続部材110の第3再配線層112cの下面は、半導体チップ120の接続パッド122の下面より下側に配置することができる。また、第2接続部材140の再配線層142と第1接続部材110の第3再配線層112cとの間の距離は、第2接続部材140の再配線層142と半導体チップ120の接続パッド122との間の距離より小さくすることができる。これは、第3再配線層112cが第2絶縁層111b上に突出した形態で配置されることが可能、その結果、第2接続部材140と接することができるようにするためである。第1接続部材110の第1再配線層112a及び第2再配線層112bは、半導体チップ120の活性面と非活性面との間に配置することができる。第1接続部材110は半導体チップ120の厚さに対応する厚さに形成することができ、これにより、第1接続部材110の内部に形成された第1再配線層112a及び第2再配線層112bが、半導体チップ120の活性面と非活性面との間のレベルに配置されることがある。30

【0090】

第1接続部材110の再配線層112a、112b、112c、112dの厚さは、第2接続部材140の再配線層142の厚さより厚くすることができる。第1接続部材110は半導体チップ120以上の厚さを有することができるため、再配線層112a、112b、112c、112dもより大きいサイズに形成することができる。これに対し、第2接続部材140の再配線層142は、薄型化のために相対的に小さいサイズに形成することができる。40

【0091】

その他の構成については、一例によるファン・アウト半導体パッケージ100Aについての説明と実質的に同一であるため、詳細な説明は省略する。

【0092】

図14は接続パッドに腐食が発生する場合を概略的に示す図面であり、図15は電圧が印加されていない状態の接続パッドの腐食を概略的に示す図面であり、図16は電圧が印加された状態の接続パッドの腐食を概略的に示す図面である。

#### 【0093】

図面を参照すると、半導体パッケージは接続端子170'を介してボード500'に実装することができる。接続端子170'は、ボード500'の絶縁層501'から露出した電極502'と電気的に接続することができる。接続端子170'は、高分子絶縁層141'の内部に形成された再配線層142'を介して接続パッド122'と電気的に接続することができる。一方、接続端子170'はアンダーフィル200'により固定されることができる。この際、高温高湿信頼性環境(THB; Temperature Humidity Bias)において、アンダーフィル200'のC1などのイオンは、高分子絶縁層141'を通過して半導体チップの接続パッド122'を腐食させるおそれがある。具体的に、高温高湿信頼性環境(THB; Temperature Humidity Bias)において、半導体チップの本体121'上に形成された接続パッド122'のパッシベーション膜123'から露出した表面が、C1などのイオンによって腐食されるおそれがある。すなわち、本発明によるファン-アウト半導体パッケージ100A~100Cのように、ピア143がパッシベーション膜123を覆うように形成しない場合、電圧が印加されていない状態及び/または電圧が印加されている状態で、半導体チップの接続パッドが腐食されるおそれがある。10

#### 【0094】

本発明で用いられた「一例」という表現は、互いに同一の実施例を意味せず、それぞれ互いに異なる固有の特徴を強調して説明するために提供されるものである。しかし、上記提示された一例は、他の一例の特徴と結合して実現されることを排除しない。例えば、特定の一例で説明された事項が他の一例で説明されていなくても、他の一例でその事項と反対であるか矛盾する説明がない限り、他の一例に関連する説明であると理解されることがある。20

#### 【0095】

本発明において「接続される」というのは、直接的に接続された場合だけでなく、間接的に接続された場合を含む概念である。また、「電気的に接続される」というのは、物理的に接続された場合と、接続されていない場合をともに含む概念である。なお、第1、第2などの表現は、一つの構成要素と他の構成要素を区分するために用いられるもので、該当する構成要素の順序及び/または重要度などを限定しない。場合によっては、本発明の範囲を外れずに、第1構成要素は第2構成要素と命名されることもでき、類似して第2構成要素は第1構成要素と命名することもできる。30

#### 【0096】

本発明において、「上部、下部、上側、下側、上面、下面」などは、添付の図面に基づいて判断する。例えば、第1接続部材は、再配線層よりも上部に位置する。但し、特許請求の範囲がこれに限定されるものではない。また、垂直方向とは上述した上部及び下部の方向を意味し、水平方向とはこれと垂直な方向を意味する。このとき、垂直断面とは垂直方向の平面で切断した場合を意味するもので、図面に示した断面図をその例として挙げることができる。また、水平断面とは水平方向の平面で切断した場合を意味するもので、図面で示す平面図をその例として挙げることができる。40

#### 【0097】

本発明で用いられた用語は、一例を説明するために説明されたものであり、本発明を限定しようとする意図ではない。このとき、単数の表現は文脈上明確に異なる意味でない限り、複数を含む。ここで、本実施形態に係る発明の例を項目として記載する。

#### [項目1]

貫通孔を有する第1接続部材と、

前記第1接続部材の貫通孔に配置され、接続パッドが配置された活性面と前記活性面とは反対側に配置された非活性面を有する半導体チップと、

10

20

30

40

50

前記第1接続部材と前記半導体チップの非活性面の少なくとも一部を封止する封止材と、

前記第1接続部材と前記半導体チップの活性面上に配置された第2接続部材と、を含み、

前記第1接続部材及び前記第2接続部材は、それぞれ前接続パッドと電気的に接続された再配線層を含み、

前記半導体チップは、前記接続パッドの少なくとも一部を露出させる開口部を有するパッシベーション膜を含み、

前記第2接続部材の再配線層は、ピアを介して前記接続パッドと接続されて、

前記ピアは前記パッシベーション膜の少なくとも一部を覆うことで前記接続パッドへのイオン伝搬経路を遮断可能な構造を有する、ファン・アウト半導体パッケージ。

10

[項目2]

前記パッシベーション膜の前記開口部を囲み、且つ前記ピアと接する面の前記パッシベーション膜の全体の面積をS1とし、前記パッシベーション膜を覆う前記ピアの面積をS2としたとき、S2/S1は0.2~0.8である、項目1に記載のファン・アウト半導体パッケージ。

[項目3]

前記パッシベーション膜の前記開口部を囲み、且つ前記ピアと接する面の前記パッシベーション膜の幅をWとし、前記パッシベーション膜と接する前記ピアの縁が、前記パッシベーション膜の前記開口部を囲み、且つ前記ピアと接する面の前記パッシベーション膜の中心線Cから離れている距離をdとするとき、d/Wは0.3以内である、項目1または項目2に記載のファン・アウト半導体パッケージ。

20

[項目4]

前記ピアは、前記接続パッドの露出している表面をすべて覆う、項目1から項目3の何れか一項に記載のファン・アウト半導体パッケージ。

[項目5]

前記ピアは、フィルドピア(Filled via)である、項目1から項目4の何れか一項に記載のファン・アウト半導体パッケージ。

[項目6]

前記第1接続部材は、第1絶縁層と、前記第2接続部材と接し、前記第1絶縁層に埋め込まれた第1再配線層と、前記第1絶縁層の前記第1再配線層が埋め込まれた側とは反対側上に配置された第2再配線層と、を含み、

30

前記第1及び第2再配線層は前記接続パッドと電気的に接続される、項目1から項目5の何れか一項に記載のファン・アウト半導体パッケージ。

[項目7]

前記第1接続部材は、前記第1絶縁層上に配置され、前記第2再配線層を覆う第2絶縁層と、前記第2絶縁層上に配置された第3再配線層と、をさらに含み、

前記第3再配線層は前記接続パッドと電気的に接続される、項目6に記載のファン・アウト半導体パッケージ。

[項目8]

40

前記第2接続部材の再配線層と前記第1再配線層との間の距離が、前記第2接続部材の再配線層と前記接続パッドとの間の距離よりも大きい、項目6または項目7に記載のファン・アウト半導体パッケージ。

[項目9]

前記第1再配線層は、前記第2接続部材の再配線層よりも厚さが厚い、項目6から項目8の何れか一項に記載のファン・アウト半導体パッケージ。

[項目10]

前記第1再配線層の下面是、前記接続パッドの下面より上側に位置する、項目6から項目9の何れか一項に記載のファン・アウト半導体パッケージ。

[項目11]

50

前記第2再配線層は、前記半導体チップの活性面と非活性面との間に位置する、項目7に記載のファン・アウト半導体パッケージ。

[項目12]

前記第1接続部材は、第1絶縁層と、前記第1絶縁層の両面に配置された第1再配線層及び第2再配線層と、前記第1絶縁層上に配置され、前記第1再配線層を覆う第2絶縁層と、前記第2絶縁層上に配置された第3再配線層と、を含み、

前記第1～第3再配線層は前記接続パッドと電気的に接続される、項目1から項目11の何れか一項に記載のファン・アウト半導体パッケージ。

[項目13]

前記第1接続部材は、前記第1絶縁層上に配置され、前記第2再配線層を覆う第3絶縁層と、前記第3絶縁層上に配置された第4再配線層と、をさらに含み、 10

前記第4再配線層は前記接続パッドと電気的に接続される、項目12に記載のファン・アウト半導体パッケージ。

[項目14]

前記第1絶縁層は、前記第2絶縁層よりも厚さが厚い、項目12または項目13に記載のファン・アウト半導体パッケージ。

[項目15]

前記第3再配線層は、前記第2接続部材の再配線層よりも厚さが厚い、項目12から項目14の何れか一項に記載のファン・アウト半導体パッケージ。

[項目16]

前記第1再配線層は、前記半導体チップの活性面と非活性面との間に位置する、項目12から項目15の何れか一項に記載のファン・アウト半導体パッケージ。

20

[項目17]

前記第3再配線層の下面是、前記接続パッドの下面より下側に位置する、項目12から項目16の何れか一項に記載のファン・アウト半導体パッケージ。

【符号の説明】

【0098】

|      |                |    |

|------|----------------|----|

| 1000 | 電子機器           |    |

| 1010 | メインボード         |    |

| 1020 | チップ関連部品        | 30 |

| 1030 | ネットワーク関連部品     |    |

| 1040 | その他の部品         |    |

| 1050 | カメラ            |    |

| 1060 | アンテナ           |    |

| 1070 | ディスプレイ         |    |

| 1080 | 電池             |    |

| 1090 | 信号ライン          |    |

| 1100 | スマートフォン        |    |

| 1101 | 本体             |    |

| 1110 | メインボード         | 40 |

| 1120 | 部品             |    |

| 1130 | カメラ            |    |

| 2200 | ファン・イン半導体パッケージ |    |

| 2220 | 半導体チップ         |    |

| 2221 | 本体             |    |

| 2222 | 接続パッド          |    |

| 2223 | パッシベーション膜      |    |

| 2240 | 接続部材           |    |

| 2241 | 絶縁層            |    |

| 2242 | 配線パターン         | 50 |

|                                 |                   |    |

|---------------------------------|-------------------|----|

| 2 2 4 3                         | ピア                |    |

| 2 2 5 0                         | パッシベーション層         |    |

| 2 2 6 0                         | アンダーバンプ金属層        |    |

| 2 2 7 0                         | 半田ボール             |    |

| 2 2 8 0                         | アンダーフィル樹脂         |    |

| 2 2 9 0                         | モールディング材          |    |

| 2 5 0 0                         | メインボード            |    |

| 2 3 0 1                         | インターポーザ基板         |    |

| 2 3 0 2                         | インターポーザ基板         |    |

| 2 1 0 0                         | ファン - アウト半導体パッケージ | 10 |

| 2 1 2 0                         | 半導体チップ            |    |

| 2 1 2 1                         | 本体                |    |

| 2 1 2 2                         | 接続パッド             |    |

| 2 1 4 0                         | 接続部材              |    |

| 2 1 4 1                         | 絶縁層               |    |

| 2 1 4 2                         | 再配線層              |    |

| 2 1 4 3                         | ピア                |    |

| 2 1 5 0                         | パッシベーション層         |    |

| 2 1 6 0                         | アンダーバンプ金属層        |    |

| 2 1 7 0                         | 半田ボール             | 20 |

| 1 0 0                           | 半導体パッケージ          |    |

| 1 0 0 A、1 0 0 B、1 0 0 C         | ファン - アウト半導体パッケージ |    |

| 1 1 0                           | 第1接続部材            |    |

| 1 1 1、1 1 2 a、1 1 2 b、1 1 2 c   | 絶縁層               |    |

| 1 1 2 a、1 1 2 b、1 1 2 c、1 1 2 d | 再配線層              |    |

| 1 1 3                           | ピア                |    |

| 1 2 0                           | 半導体チップ            |    |

| 1 2 1                           | 本体                |    |

| 1 2 2                           | 接続パッド             |    |

| 1 2 3                           | パッシベーション膜         | 30 |

| 1 3 0                           | 封止材               |    |

| 1 3 1                           | 開口部               |    |

| 1 4 0                           | 第2接続部材            |    |

| 1 4 1                           | 絶縁層               |    |

| 1 4 2                           | 再配線層              |    |

| 1 4 3                           | ピア                |    |

| 1 4 3 a                         | シード層              |    |

| 1 4 3 b                         | 導体層               |    |

| 1 5 0                           | パッシベーション層         |    |

| 1 5 1                           | 開口部               | 40 |

| 1 6 0                           | アンダーバンプ金属層        |    |

| 1 7 0                           | 接続端子              |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図16】

---

フロントページの続き

(72)発明者 バン、ヨウン ミン

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - ロ 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

(72)発明者 キム、ハン

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - ロ 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

(72)発明者 ジュン、キュン ムン

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - ロ 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

審査官 木下 直哉

(56)参考文献 米国特許出願公開第2013/0249101(US, A1)

米国特許出願公開第2015/0187742(US, A1)

米国特許出願公開第2016/0172329(US, A1)

特開2000-077570(JP, A)

国際公開第2011/058879(WO, A1)

米国特許出願公開第2016/0043047(US, A1)

米国特許出願公開第2009/0085192(US, A1)

特開2010-238702(JP, A)

特開2010-186847(JP, A)

特開2006-59992(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12 - 23/15

H01L 23/52 - 23/538

H01L 21/3205

H01L 21/768