(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-123770

(P2014-123770A)

(43) 公開日 平成26年7月3日(2014.7.3)

(51) Int.Cl.

**HO 1 L 27/146 (2006.01)**

**HO 4 N 5/3745 (2011.01)**

F

HO1L 27/14

HO4N 5/335

A

5

### テーマコード（参考）

4M118

5CO24

審査請求 有 請求項の数 13 O.L. (全 15 頁)

|            |                                   |

|------------|-----------------------------------|

| (21) 出願番号  | 特願2014-52326 (P2014-52326)        |

| (22) 出願日   | 平成26年3月14日 (2014. 3. 14)          |

| (62) 分割の表示 | 特願2013-70541 (P2013-70541)<br>の分割 |

| 原出願日       | 平成20年5月9日 (2008. 5. 9)            |

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 小林 昌弘

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 山下 雄一郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置及びそれを用いた撮像システム

(57) 【要約】

【課題】 耐圧を有しつつ、素子分離部から電荷保持部への電荷の混入を低減する。

【解決手段】 撮像領域に電荷保持部を有する光電変換装置において、電荷保持部のための素子分離部は、P N接合を用いた第1の素子分離部と絶縁体を用いた第2の素子分離部とを有する。

## 【選択図】 図 2

**【特許請求の範囲】****【請求項 1】**

第1の光電変換部を含む複数の光電変換部と、

前記第1の光電変換部にて生じた電荷を保持する第1の電荷保持部を少なくとも含み、それぞれが前記複数の光電変換部のうち対応する光電変換部にて生じた電荷を保持する複数の電荷保持部と、

前記第1の電荷保持部を電気的に分離する素子分離部と、を有する光電変換装置において、

前記素子分離部は、PN接合を用いた第1の素子分離部と、絶縁体を用いた第2の素子分離部と、を有することを特徴とする光電変換装置。 10

**【請求項 2】**

前記光電変換装置は、

前記複数の電荷保持部が配されるウエルと、

前記ウエルに電位を供給するためのコンタクトプラグに接して配された半導体領域と、をさらに有し、

前記第2の素子分離部は、前記第1の電荷保持部と前記半導体領域との間に配されたことを特徴とする請求項1に記載の光電変換装置。 20

**【請求項 3】**

前記光電変換装置は、

少なくとも前記第1の電荷保持部の電荷に基づく信号を出力するためのトランジスタを含む複数のトランジスタ、をさらに有し、 20

前記素子分離部は、前記第1の電荷保持部と前記複数のトランジスタの少なくとも一部との間に配され、絶縁体を用いた第3の素子分離部を含むことを特徴とする請求項1または請求項2に記載の光電変換装置。

**【請求項 4】**

前記複数の電荷保持部のうち対応する電荷保持部の電荷がそれぞれ転送される複数の浮遊拡散部をさらに有することを特徴とする請求項1乃至3のいずれか一項に記載の光電変換装置。 20

**【請求項 5】**

それぞれが前記複数の浮遊拡散部のうち対応する浮遊拡散部の電圧をリセットする複数のリセットトランジスタをさらに有することを特徴とする請求項4に記載の光電変換装置。 30

**【請求項 6】**

前記複数の電荷保持部は遮光されていることを特徴とする請求項1乃至請求項5のいずれか一項に記載の光電変換装置。

**【請求項 7】**

前記第1の素子分離部は、前記第1の電荷保持部と、前記複数の電荷保持部のうち前記第1の電荷保持部と隣接する電荷保持部との間に配されたことを特徴とする請求項1乃至請求項6のいずれか一項に記載の光電変換装置。 40

**【請求項 8】**

前記第1の素子分離部は、前記第1の電荷保持部と、前記複数の光電変換部のうち前記第1の光電変換部と隣接する光電変換部との間に配されたことを特徴とする請求項1乃至請求項7のいずれか一項に記載の光電変換装置。

**【請求項 9】**

前記第1の光電変換部と前記第1の電荷保持部との間の領域の上にゲート電極を有し、前記ゲート電極と前記第1の光電変換部と前記第1の電荷保持部とが、埋め込みチャネルを有するトランジスタを構成することを特徴とする請求項1乃至請求項8のいずれか一項に記載の光電変換装置。

**【請求項 10】**

前記第1の電荷保持部は第1導電型の第1の半導体領域を有し、 50

前記第1の半導体領域の下部に第2導電型の第2の半導体領域が配され、

前記第2の半導体領域は、前記第1の半導体領域への前記電荷の混入を低減する障壁として機能することを特徴とする請求項1乃至9のいずれか一項に記載の光電変換装置。

#### 【請求項11】

前記第2の素子分離部はS T I構造であることを特徴とする請求項1乃至請求項10のいずれか一項に記載の固体撮像装置。

#### 【請求項12】

請求項1乃至請求項11のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理回路と、を有することを特徴とする撮像システム。 10

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本件は複数の光電変換部及び複数の電荷保持部を有する光電変換装置の素子分離の構成に関する。 20

#### 【背景技術】

#### 【0002】

近年、CCD型やMOS型の光電変換装置は多くのデジタルスチルカメラやデジタルカムコーダに用いられている。MOS型の光電変換装置においては、光電変換部の蓄積時間を一定に揃えるグローバルシャッター機能を実現するための素子構造が開発されている。それは、光電変換部に対して電荷保持部を有する構成である。特許文献1には、この電荷保持部を有する構成においてLOCOS構造の素子分離部を有する構成が開示されている。また、特許文献2には、電荷保持部を有する構成において電荷保持部への光の入射を低減することを目的として、電荷保持部を囲むように間隙が設けられている構成が開示されている。 20

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【特許文献1】特開2007-053217号公報

【特許文献2】特開2007-157912号公報

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

本願発明者らは、特許文献1の構造において、素子分離部に光が入射した場合、素子分離部内で光の乱反射が生じて電荷保持部へと光が入射してしまうことを見出した。特許文献2においては、配線層付近における光の入射についての検討がなされているものの、特許文献1と同様に素子分離部に光が入射した場合の電荷保持部へ与える影響については検討がなされていなかった。しかし、素子分離部においては、光の影響だけではなく耐圧や寄生MOSなどの電気的特性について配慮が必要となる。そこで、本発明においては、耐圧を有しつつ、素子分離部から電荷保持部への電荷の混入を低減する光電変換装置を提供することを目的とする。 40

#### 【課題を解決するための手段】

#### 【0005】

本発明の一つの側面に係る光電変換装置は、第1の光電変換部を含む複数の光電変換部と、前記第1の光電変換部にて生じた電荷を保持する第1の電荷保持部を少なくとも含み、それぞれが前記複数の光電変換部のうち対応する光電変換部にて生じた電荷を保持する複数の電荷保持部と、前記第1の電荷保持部を電気的に分離する素子分離部と、を有する光電変換装置であって、前記素子分離部は、P N接合を用いた第1の素子分離部と、絶縁体を用いた第2の素子分離部と、を有することを特徴とする。

#### 【発明の効果】

50

## 【0006】

本発明によって、光電変換装置において、耐圧を有しつつ、素子分離部から電荷保持部への電荷の混入を低減することが可能となる。

## 【図面の簡単な説明】

## 【0007】

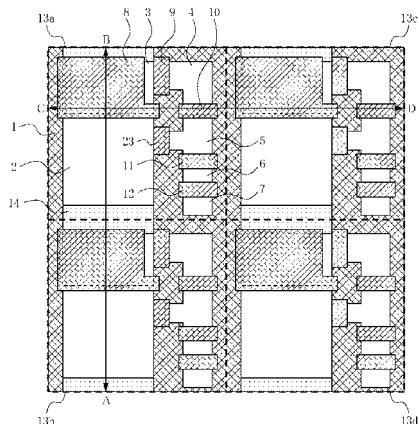

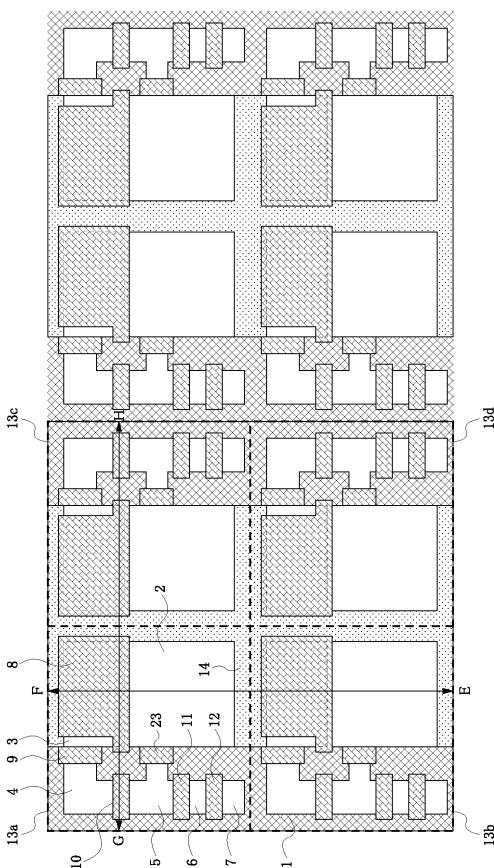

## 【図1】光電変換装置の画素回路の一例

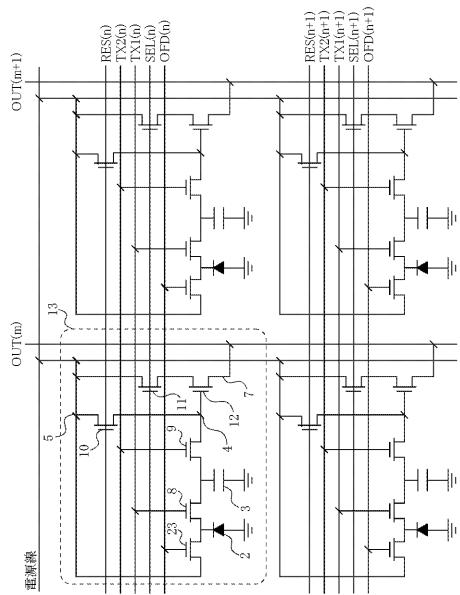

## 【図2】第1の実施形態を説明する光電変換装置の平面模式図

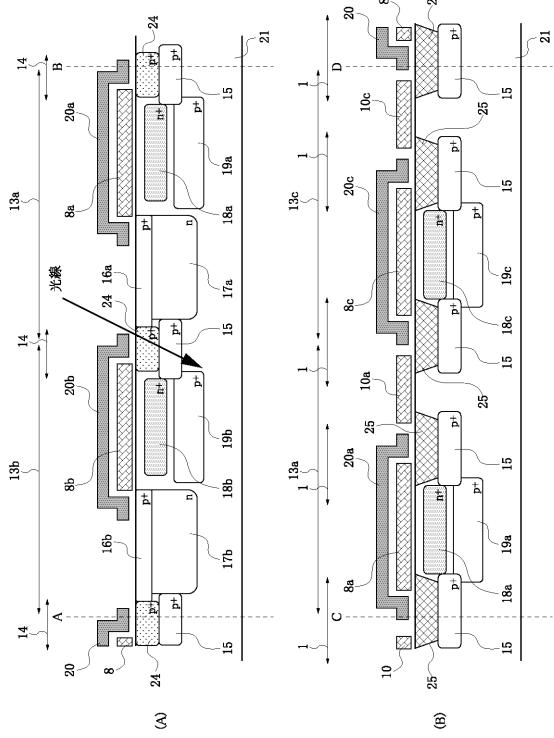

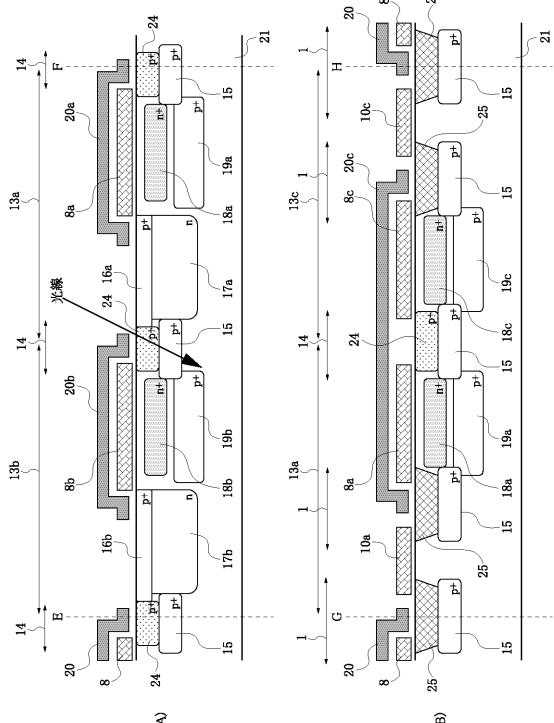

## 【図3】図2のA B線及びC D線での断面模式図

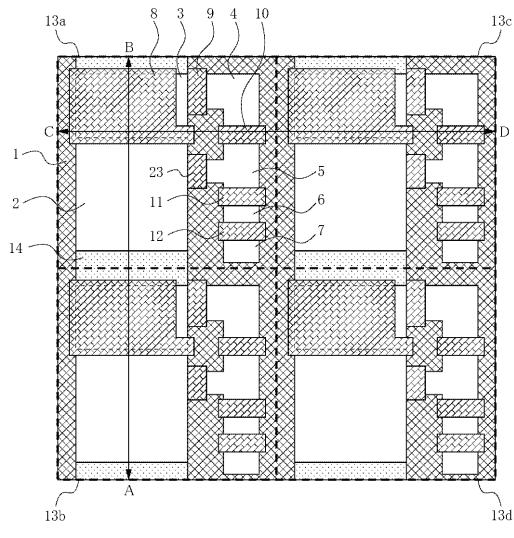

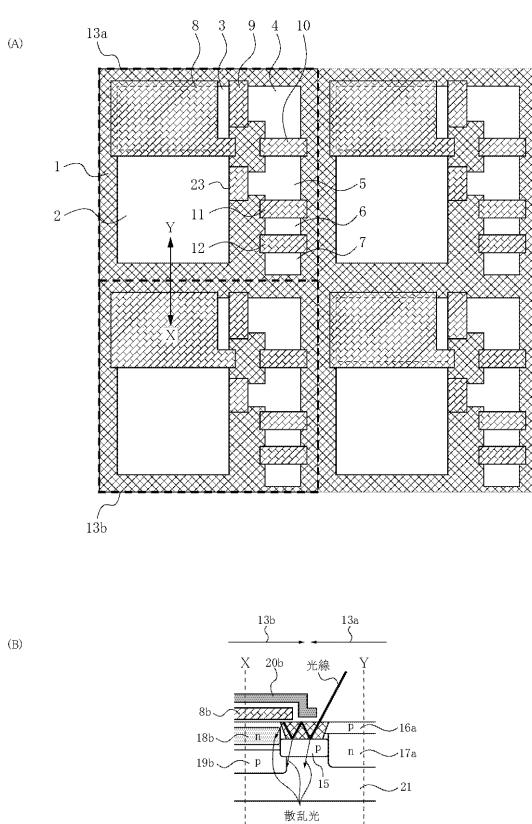

## 【図4】第1の実施形態を説明する光電変換装置の平面模式図

## 【図5】図4のE F線及びG H線での断面模式図

10

## 【図6】第1の実施形態を説明する光電変換装置の平面模式図と断面模式図

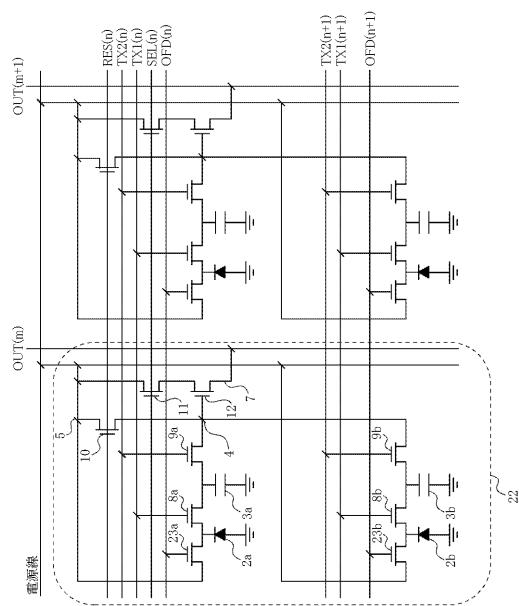

## 【図7】光電変換装置の画素回路の別の例

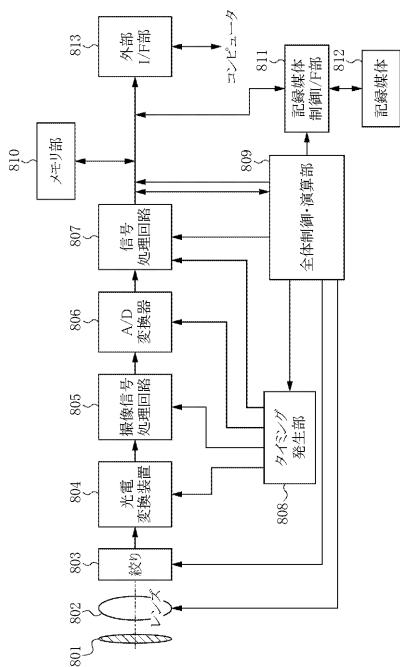

## 【図8】撮像システムを説明するブロック図

## 【発明を実施するための形態】

## 【0008】

本発明は、撮像領域に電荷保持部を有する光電変換装置において、電荷保持部のための素子分離部が、P N接合を用いた第1の素子分離部と絶縁体を用いた第2の素子分離部とを有する。そして、第2の素子分離部を電荷保持部と複数のトランジスタの少なくとも一部との間に配する。第1の素子分離部によって、酸化膜を用いた素子分離部で発生する乱反射の影響を低減し、また第2の素子分離部を電荷保持部とトランジスタとの間に配置することで、読み出し回路と電荷保持部との耐圧を維持することが可能となる。

20

## 【0009】

以下、実施形態について図面を用いて説明する。信号電荷を電子として、説明を行う。

## 【0010】

## (第1の実施形態)

始めに、図1を用いて電荷保持部を有する光電変換装置の画素回路の一例を説明する。図1は電荷保持部を有する画素13が2行2列で配列した構成を示している。2は光電変換部、3は電荷保持部、4は浮遊拡散部、5は電源部、7は画素出力部、8は第1の転送ゲート電極、9は第2のゲート電極である。10はリセット用トランジスタのゲート電極、11は選択用トランジスタのゲート電極、12は増幅用トランジスタのゲート電極、23は排出部となるオーバーフロードレイン(以下OFD)用のゲート電極である。電源線は所定の電圧を供給する配線であり、電源部5と接続している。ここで、電源部5はリセット用トランジスタのドレイン、選択用トランジスタのドレイン、OFDのドレインとも同一のノードとなっている。RES、TX1、TX2、SEL、OFDは各ゲート電極にパルスを供給する制御線である。RESはリセット用トランジスタのゲート電極10に、TX1は第1のゲート電極8に、TX2は第2のゲート電極9に、SELは選択用トランジスタのゲート電極11に、OFDはオーバーフロードレイン用のゲート電極23にパルスを供給する制御線である。OUTは信号線である。nやmとは自然数であり、ある行nとその隣の行n+1、ある列mとその隣の列m+1とを示している。ここで、画素13とは、1つの光電変換部2を含む構成であり、光電変換装置の構成における最小の繰り返し単位である。この画素13が複数配された領域を撮像領域と称する。

30

## 【0011】

このような画素13における、グローバルシャッターの動作は次のようになる。ある蓄積期間が経過した後に、光電変換部2にて生じた電荷を第1のゲート電極8によって、電荷保持部3へと転送する。電荷保持部3にてある蓄積期間の信号電荷を保持している間、光電変換部2では再び信号電荷の蓄積が始まる。電荷保持部3の信号電荷は第2のゲート電極9によって浮遊拡散部4へと転送され、増幅用トランジスタの画素出力部7から信号として出力される。また、電荷保持部3にて信号電荷を保持している間に光電変換部2にて生じた電荷が電荷保持部3へ混入しないように、OFD23によって光電変換部2の電荷を排出させる場合もある。リセット用トランジスタは、電荷保持部3から信号電荷が転

40

50

送される前に浮遊拡散部4を所定の電位に設定する(リセット動作)。この時の浮遊拡散部4の電位をノイズ信号として画素出力部7から出力し、後に出力される信号電荷に基づく信号との差分をとることで、ノイズ信号を除去することができる。

#### 【0012】

また、画素13において、第1のゲート電極8の下部が埋め込みチャネルとなっていてもよい。つまり光電変換部2と電荷保持部3とが導通している。このような構成のグローバルシャッターの動作は、次のようになる。光電変換部2にて生じた信号電荷は光電変換部2と電荷保持部3とで保持される。そして、ある蓄積期間が経過した後に、第2のゲート電極9によって浮遊拡散部4へ信号電荷が転送される。浮遊拡散部4に信号電荷が転送された後、再び光電変換部2と電荷保持部3とで信号電荷の蓄積が始まる。この構成においても、浮遊拡散部4にて信号電荷を保持している間に光電変換部2にて生じた電荷が浮遊拡散部4へ混入しないように、O F D 2 3によって光電変換部2の電荷を排出させる場合もある。また、リセット用トランジスタの動作としては、同様である。この動作は、第1のゲート電極8の下部が埋め込みチャネルになっていなくても第1のゲート電極8の駆動によって、行うことが可能である。本実施形態では、このような埋め込みチャネルとなっている構成を例に説明を行う。

10

#### 【0013】

図2は、図1のような画素構成の光電変換装置の平面模式図である。画素13が2行2列に配されている。13aを第1の画素、13bを第2の画素、13cを第3の画素、13dを第4の画素とする。図1と同様の機能を有する構成については、同一の符号を付し説明を省略する。各符号のa、b、c、dについては、それぞれ第1の画素、第2の画素、第3の画素、第4の画素の構成であることを示している。また、説明のため、コンタクトやゲート電極以外の配線の配置については省略している。図1において共通のノードとなっている部分は同一の半導体領域である場合や配線によって接続されている場合がある。

20

#### 【0014】

図1において、1及び14は素子分離部である。14は半導体領域のP N接合を利用した第1の素子分離部であり、1は絶縁体を利用した第2の素子分離部である。第2の素子分離部1以外の部分が活性領域となっており、各素子が形成される。

30

#### 【0015】

第1の画素13aに着目して説明する。第1のゲート電極8aは電荷保持部3aの上部まで延在して配置されている。第1のゲート電極8aが電荷保持部3aの上部まで配されていることで、電荷保持部3aへの光の入射を低減させ、また、第1のゲート電極8aに供給される電圧を制御することによって、電荷保持部3aの暗電流を低減することが可能である。ここで、電荷保持部3aは、第1の素子分離部14と第2の素子分離部1とを有する。隣接する光電変換部2(不図示)との間には第1の素子分離部14が配されている。つまり、例えば第2の画素13cの電荷保持部3bと第1の画素13aの電荷保持部3aとの間には第1の素子分離部14が配されている。このような素子分離部の構成について図3の断面模式図を用いてより詳細に説明する。以下、n型を第1導電型として説明する。

40

#### 【0016】

図3(A)は図2のAB線の断面模式図であり、図3(B)は図2のCD線における断面模式図である。図3(A)及び図3(B)において、21はウエルである。ウエル21は、n型であっても、p型であってもよく、半導体基板に設けられた構成であっても、半導体基板であってもよい。16は第2導電型の第1の半導体領域であり、17は第1導電型の第2の半導体領域であり、これらは光電変換部2を構成する。18は第1導電型の第3の半導体領域であり、電荷保持部3を構成する。19は第2導電型の第4の半導体領域であり、電荷保持部3への電子の混入を低減させる障壁として機能しうる。20は電荷保持部3への光の入射を低減させる遮光膜である。遮光膜20は図2においては省略している。そして、22は第2導電型の半導体領域であり、周囲の半導体領域とP N接合による

50

電気的な分離を行う第1の素子分離部14を構成する。第2導電型の半導体領域14は周囲の半導体領域に比べて第2導電型の不純物濃度が高く、即ち信号電荷に対するポテンシャルが高い。また、23は絶縁体であり、第2の素子分離部1を構成する。第2の素子分離部1はLOCOS構造( Local oxidation of Silicon)やSTI構造( Shallow trench isolation)である。15は第2導電型の第5の半導体領域であり、チャネルリストップとして、また電子に対する障壁として機能しうる。更に、第5の半導体領域15は絶縁体23を設けたことによる暗電流の防止の機能をも有してもよい。ここで、本実施形態においては、第2の半導体領域17と第3の半導体領域18との間に、第1導電型の第6の半導体領域を有する(不図示)。第6の半導体領域によって、第1のゲート電極8の下部に埋め込みチャネルが形成される。

10

#### 【0017】

ここで、課題について図6を用いて詳細な説明を行う。図6(A)は図2に対応した平面模式図であり、図2と同様に図1の画素回路に対応する。図6(B)は図6(A)のXY線における断面模式図である。図1から図3と同様の構成については、同一の符号を付し説明を省略する。ここで、図6(A)では電荷保持部3のための素子分離部は絶縁体を利用した第2の素子分離部1のみとなっている。この時のXY線における断面において、図6(B)のようなことが生じる。光電変換部2aには遮光膜20が無いため、光が入射しやすく、光電変換部2aと電荷保持部3bとの間にも光が入射する。ここで、発明者は、第2の素子分離部1に光が入射した場合、絶縁体と半導体基板21との界面で反射を繰り返し、様々な方向へ向かう散乱光が生じてしまうことを見出した。この散乱光による電子が、電荷保持部3bにて保持された信号電荷に混入し偽信号を生じてしまう場合がある。この時、素子分離部が半導体基板に深くまで絶縁体を設けたSTI構造を有する場合には、より反射が生じやすく散乱光が生じやすい。また、素子分離部への光の入射は、光電変換部2aの周りだけでなく、電荷保持部3bが並んでいる場合でも遮光膜20の切れ目で生じる可能性がある。

20

#### 【0018】

一方、図3(A)では、第2の画素13bの電荷保持部3bと、第1の画素13aの光電変換部2aとの間に第1の素子分離部14を設けている。図3(A)に示したように、遮光膜20が設けられていない光電変換部2aには光が入射しやすい。この光の入射量が多い部分に第1の素子分離部14を設けることによって、光はウエル21の深部へと透過し、散乱が低減される。また、第1の素子分離部14によって、光によって生じた電子が電荷保持部3bを構成する第3の半導体領域18bへに混入することを低減することが可能である。更には、第4の半導体領域19bが存在することによって、電子の第3の半導体領域18bへの混入をより低減することが可能となる。

30

#### 【0019】

また、図3(B)では、複数のトランジスタの少なくとも一部(ここではリセット用トランジスタ)と電荷保持部3aとの間には第2の素子分離部1が配されている。第2の素子分離部1によって、電気的な分離を十分に行うことが可能である。なお、トランジスタはリセット用トランジスタに限らない。電荷保持部がトランジスタのソース領域あるいはドレイン領域と同一のノードになっていなければよく、増幅用トランジスタや選択用トランジスタであってもよい。これら、トランジスタゲート電極には高いパルスが供給され、また、トランジスタのソース領域あるいはドレイン領域には高い電圧が供給される場合があるため電気的な分離及び耐圧が必要となる。また、第2の素子分離部は、電荷保持部とウエルの電位を固定するためのウエルコンタクトのための半導体領域との間に配されていても良い。リセット動作時には電荷保持部に高い電位がかかるため、ウエルコンタクトのための半導体領域との電気的な分離を十分に行うためである。

40

#### 【0020】

ここで、トランジスタのソース領域あるいはドレイン領域を形成する半導体領域は光電変換部を構成する第2の半導体領域17に比べて高い不純物濃度を有することが多い。このような高い不純物濃度の半導体領域を第1の素子分離部によって分離を行うとPN接合

50

界面に大きな電界がかかってしまう。従って、第2の素子分離部1にて耐圧を保ちつつ、電気的な分離を行うことが望まれる。更に、光電変換部2とは異なり複数のトランジスタは遮光することも可能であるため、第2の素子分離部1への光の入射を低減し、散乱光の発生を低減することが可能となる。

#### 【0021】

しかし、絶縁体を有する第2の素子分離部1は、絶縁体と半導体との界面の格子欠陥に起因する暗電流が生じる場合がある。そこで、本実施形態のように、信号電荷を保持する電荷保持部3や光電変換部2の近傍には、第1の素子分離部14を配置することで図6の構成に比べてノイズを低減することが可能となる。

#### 【0022】

本実施形態のように光電変換部2と電荷保持部3との間は埋め込みチャネルとなっている構成においては、電荷保持部3にて信号電荷を保持する期間が長くなるため、入射光による電子の混入や暗電流の低減に効果的である。しかし、光電変換部2と電荷保持部3との間が埋め込みチャネルの構成には限定されない。また、障壁となる第4の半導体領域19や第5の半導体領域15はなくてもよい。

#### 【0023】

##### (第2の実施形態)

本実施形態の光電変換装置は、第1の実施形態とは画素の平面レイアウトが異なり、画素同士が線対称となって配置されている構成である。また、電荷保持部及び光電変換部の周囲における素子分離部の配置が異なる。図4を用いて説明を行う。

#### 【0024】

図4は光電変換装置の平面模式図である。図4において図2と同一の構成については同一の符号を付し、説明を省略する。また、説明のため、コンタクトやゲート電極以外の配線、遮光膜については省略している。図4では2行4列の8つの画素13について示しているが、光電変換装置としては図4の8つの画素が繰り返し2次元に配置されている。その内、4つの画素13a、13b、13c、13dを用いて説明を行う。図4では図2と異なり、第1の画素13aと第3の画素13cの光電変換部2が向かい合って配置されている。即ち、第1の画素13a及び第2の画素13bの列と第3の画素13c及び第4の画素13dの列が線対称として配置されている。ここで、第1の実施形態と同様に、第1の画素13aの電荷保持部3aと不図示の隣接する画素の光電変換部との間には第1の素子分離部14が配置されている。そして、第1の画素13aのトランジスタと電荷保持部3aとの間には第2の素子分離部1が配置されている。しかし、更に、第1の画素13aの電荷保持部3aと第3の画素13cの電荷保持部3cとの間にも第1の素子分離部14が配されている。このような構成によって、第1の実施形態に比べてより、電荷保持部3aへ混入する電荷を低減することが可能となる。また、電荷保持部3aへ混入する暗電流を低減することが可能となる。また、光電変換部2aにおいても第3の画素13cの光電変換部2cとの間に第1の素子分離部14を有する。このような構成によって、光電変換部2a及び光電変換部2cへの暗電流を低減することが可能である。また、トランジスタと電荷保持部3aあるいは光電変換部2aとの間には第2の素子分離部1が配されていることによって、耐圧の低下や寄生MOSトランジスタの発生を抑制することが可能である。更に、図5の断面模式図を用いて説明する。

#### 【0025】

図5(A)は図4のE F線の断面模式図であり、図5(B)は図4のG H線における断面模式図である。図5(A)及び図5(B)において、図3(A)及び図3(B)と同様の構成については同一の符号を付し、説明を省略する。図5(A)においては、図3(A)とほぼ同一の構成となっているため説明を省略する。図5(B)においては、第1の画素13aの電荷保持部3aと第3の画素13cの電荷保持部3cとが隣接しており、同一の遮光膜20にて遮光されている。この遮光膜20によって、電荷保持部3aと電荷保持部3cとの間には光の入射はない。しかし、暗電流が発生しやすい第2の素子分離部1の絶縁体23ではなく第1の素子分離部14、即ち第2導電型の半導体領域22が配置され

ている。このような構成によって、電荷保持部 3 a 及び電荷保持部 3 c への暗電流を低減することが可能となる。

#### 【0026】

以上述べてきたように、ある画素の電荷保持部と隣接する画素の電荷保持部との間においても、第 1 の素子分離部を配置することによって、第 2 の素子分離部を配置した場合に生じる光の散乱による偽信号の発生の低減が可能となる。また、電荷保持部への暗電流の混入を低減することが可能となる。また、光電変換部の周囲においても同様である。あわせて、電荷保持部とトランジスタとの間には第 2 の素子分離部を設けることによって、耐圧が向上し、また寄生MOSトランジスタの発生を低減することが可能となる。なお、本実施形態の素子分離部の配置を異なる平面レイアウトに適用することも可能である。

10

#### 【0027】

##### (第 3 の実施形態)

本実施形態では、図 1 に記載の画素回路とは異なる画素回路について図 7 を用いて説明する。図 7 は画素ユニット 2 2 を有する構成を示している。図 1 と同様の構成については同一の符号を付し、説明を省略する。

#### 【0028】

図 7 の 2 a は第 1 の光電変換部、2 b は第 2 の光電変換部 2 b、3 a は第 1 の電荷保持部、3 b は第 2 の電荷保持部である。8 a と 9 a は第 1 の光電変換部に対応する第 1 のゲート電極と第 2 のゲート電極であり、8 b と 9 b は第 2 の光電変換部に対応する第 1 のゲート電極と第 2 のゲート電極である。2 3 a は第 1 の光電変換部に対応する排出部であり、2 3 b は第 2 の光電変換部に対応する排出部である。そして、第 1 の光電変換部 2 a と第 2 の光電変換部 2 b とが浮遊拡散部 4、リセット用トランジスタ、選択用トランジスタ、増幅用トランジスタとを共有化している。

20

#### 【0029】

つまり、図 7 の画素回路は、図 1 の画素回路において n 行目 m 列の画素と n + 1 行目 m 列の画素の浮遊拡散部 4 同士が接続された構成である。更に、リセット用トランジスタと選択用トランジスタと増幅用トランジスタとが共有化されている。また、図 1 の構成は、画素ユニット 2 2 が含む光電変換部 2 が 1 つの場合とも言える。

#### 【0030】

このような構成によれば図 1 の構成に比べて素子数を削減することができるため、電荷保持部や光電変換部の面積を大きくとることが可能となる。

30

#### 【0031】

この時の素子分離部の配置については、第 2 の実施形態に示したように、電荷保持部とトランジスタとの間には第 2 の素子分離部を配置し、第 1 の素子分離部は次のような場所に配置することが望ましい。まず、電荷保持部同士の間、例えば、第 1 の電荷保持部 3 a と第 2 の電荷保持部 3 b との間や第 1 の電荷保持部 3 a と隣接する画素ユニットの電荷保持部との間である。更に、電荷保持部と光電変換部との間、例えば、第 1 の電荷保持部 3 a と第 2 の光電変換部 2 b との間や第 1 の電荷保持部 3 a と隣接する画素ユニットの光電変換部との間である。このように、第 2 の実施形態に示したような第 1 の素子分離部と第 2 の素子分離部との配置を規定することで、耐圧を保ちつつ、電荷保持部への電荷の混入を低減することが可能となる。

40

#### 【0032】

##### (撮像システムへの応用)

本実施形態では、第 1 の実施形態及び第 3 の実施形態にて説明してきた光電変換装置を撮像システムに適用した場合について、図 8 を用いて説明する。撮像システムとは、デジタルスチルカメラやデジタルビデオカメラや携帯電話用デジタルカメラである。

#### 【0033】

図 8 はデジタルスチルカメラの構成図である。被写体の光学像は、レンズ 802 等を含む光学系によって光電変換装置 804 の撮像面に結像される。レンズ 802 の外側には、レンズ 802 のプロテクト機能とメインスイッチを兼ねるバリア 801 が設けられる。

50

レンズ 802 には、それから出射される光の光量を調節するための絞り 803 が設けられる。光電変換装置 804 から複数チャンネルで出力される撮像信号は、撮像信号処理回路 805 によって、各種の補正、クランプ等の処理が施される。撮像信号処理回路 805 から複数チャンネルで出力される撮像信号は、A/D 変換器 806 でアナログ - デジタル変換される。A/D 変換器 806 から出力される画像データは、信号処理部（画像処理部）807 によって各種の補正、データ圧縮などがなされる。光電変換装置 804、撮像信号処理回路 805、A/D 変換器 806 及び信号処理部 807 は、タイミング発生部 808 が発生するタイミング信号にしたがって動作する。各ブロックは、全体制御・演算部 809 によって制御される。その他、画像データを一時的に記憶するためのメモリ部 810、記録媒体への画像の記録又は読み出しのための記録媒体制御インターフェース部 811 を備える。記録媒体 812 は、半導体メモリ等を含んで構成され、着脱が可能である。さらに、外部コンピュータ等と通信するための外部インターフェース（I/F）部 813 を備えてもよい。ここで、805 から 808 は、光電変換装置 804 と同一チップ上に形成されてもよい。

10

#### 【0034】

次に、図 8 の動作について説明する。バリア 801 のオープンに応じて、メイン電源、コントロール系の電源、A/D 変換器 806 等の撮像系回路の電源が順にオンする。その後、露光量を制御するために、全体制御・演算部 809 が絞り 803 を開放にする。光電変換装置 804 から出力された信号は、撮像信号処理回路 805 をスルーして A/D 変換器 806 へ提供される。A/D 変換器 806 は、その信号を A/D 変換して信号処理部 807 に出力する。信号処理部 807 は、そのデータを処理して全体制御・演算部 809 に提供し、全体制御・演算部 809 において露出量を決定する演算を行う。全体制御・演算部 809 は、決定した露出量に基づいて絞りを制御する。

20

#### 【0035】

次に、全体制御・演算部 809 は、光電変換装置 804 から出力された信号処理部 807 で処理された信号にから高周波成分を取り出して、高周波成分に基づいて被写体までの距離を演算する。その後、レンズ 802 を駆動して、合焦か否かを判断する。合焦していないと判断したときは、再びレンズ 802 を駆動し、距離を演算する。

30

#### 【0036】

そして、合焦が確認された後に本露光が始まる。露光が終了すると、光電変換装置 804 から出力された撮像信号は、撮像信号処理回路 805 において補正等がされ、A/D 変換器 806 で A/D 変換され、信号処理部 807 で処理される。信号処理部 807 で処理された画像データは、全体制御・演算部 809 によりメモリ部 810 に蓄積される。その後、メモリ部 810 に蓄積された画像データは、全体制御・演算部 809 の制御により記録媒体制御 I/F 部を介して記録媒体 812 に記録される。また、画像データは、外部 I/F 部 813 を通してコンピュータ等に提供されて処理される。

30

#### 【0037】

このようにして、本発明の光電変換装置は撮像システムに適用される。本発明の光電変換装置を用いることによって、グローバルシャッターによる画像信号へのノイズを低減することが可能となるため、より高画質な画像を得ることが可能となる。また、信号処理回路等でのノイズ除去が容易となる。

40

#### 【0038】

以上、本発明のいくつかの実施形態について説明してきた。しかし、本発明は各実施形態に限定されるものではなく、適宜変更可能である。例えば、画素の回路構成は図 1 の構成に限らない。図 1 にして示したような排出部ではなく、半導体基板の垂直方向に電荷を排出する構成を有していても良い。また、第 1 のゲート電極 8 の構成は実施形態にて述べてきた構成に限られず、第 1 のゲート電極 8 が電荷保持部 3 の上部まで延在しなくても良い。電荷の極性、半導体領域の極性及びトランジスタの極性についても、適宜変更可能である。

50

#### 【符号の説明】

## 【 0 0 3 9 】

- 1 第2の素子分離部

- 2 光電変換部

- 3 電荷保持部

- 4 浮遊拡散部

- 8 第1のゲート電極

- 9 第2のゲート電極

- 1 4 第1の素子分離部

- 1 3 画素

- 2 2 画素ユニット

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

## 【手続補正書】

【提出日】平成26年4月14日(2014.4.14)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

## 【特許請求の範囲】

## 【請求項1】

第1導電型の第1半導体領域をそれぞれが含む複数の光電変換部と、前記複数の光電変換部のうち対応する光電変換部にて生じた電荷を保持する第1導電型の第2半導体領域をそれぞれが含む複数の電荷保持部と、前記電荷保持部の電荷が転送される浮遊拡散部を含み、前記浮遊拡散部に転送された電荷に基づく信号を出力する複数の増幅部と、第2導電型の第3半導体領域を用いた第1の素子分離部と、絶縁体を用いた第2の素子分離部と、を有する、ことを特徴とする光電変換装置。

## 【請求項2】

前記複数の電荷保持部の1つと、前記複数の増幅部の1つの間に、前記第2の素子分離部の一部が配された、ことを特徴とする請求項1に記載の光電変換装置。

## 【請求項3】

前記光電変換部の電荷が排出される第4半導体領域を有し、前記複数の電荷保持部の1つと、前記複数の増幅部の1つの間に、前記第2の素子分離部の一部が配された、

ことを特徴とする請求項 1 に記載の光電変換装置。

【請求項 4】

前記第 1 半導体領域と前記第 4 半導体領域との間の領域の上に配されたゲート電極を有する、

ことを特徴とする請求項 3 に記載の光電変換装置。

【請求項 5】

前記光電変換装置は、前記増幅部を構成するトランジスタを少なくとも含む複数のトランジスタ、を有し、

前記第 2 の素子分離部の一部が、前記複数の電荷保持部の 1 つと前記複数のトランジスタの少なくとも一部との間に配された、

ことを特徴とする請求項 1 に記載の光電変換装置。

【請求項 6】

前記複数のトランジスタは、前記浮遊拡散部の電圧をリセットするリセットトランジスタを含む、

ことを特徴とする請求項 5 に記載の光電変換装置。

【請求項 7】

前記複数の電荷保持部は遮光されていることを特徴とする請求項 1 乃至請求項 6 のいずれか一項に記載の光電変換装置。

【請求項 8】

前記第 1 の素子分離部は、前記複数の電荷保持部のうち隣接する 2 つの電荷保持部の間に配された、

ことを特徴とする請求項 1 乃至請求項 7 のいずれか一項に記載の光電変換装置。

【請求項 9】

前記第 1 の素子分離部は、前記複数の電荷保持部の 1 つと、前記複数の光電変換部の 1 つとの間に配されたことを特徴とする請求項 1 乃至請求項 8 のいずれか一項に記載の光電変換装置。

【請求項 10】

前記複数の光電変換部の 1 つと、当該 1 つに対応する電荷保持部との間の領域の上に配されたゲート電極を有する、

ことを特徴とする請求項 1 乃至請求項 9 のいずれか一項に記載の光電変換装置。

【請求項 11】

前記ゲート電極は、前記第 2 半導体領域の上にまで延在している、

ことを特徴とする請求項 10 に記載の光電変換装置。

【請求項 12】

前記第 2 の素子分離部は S T I 構造であることを特徴とする請求項 1 乃至請求項 11 のいずれか一項に記載の光電変換装置。

【請求項 13】

請求項 1 乃至請求項 12 のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理回路と、を有することを特徴とする撮像システム。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 5

【補正方法】変更

【補正の内容】

【0 0 0 5】

本発明の一つの側面に係る光電変換装置は、第 1 導電型の第 1 半導体領域をそれぞれが含む複数の光電変換部と、前記複数の光電変換部のうち対応する光電変換部にて生じた電荷を保持する第 1 導電型の第 2 半導体領域をそれぞれが含む複数の電荷保持部と、前記電荷保持部の電荷が転送される浮遊拡散部を含み、前記浮遊拡散部に転送された電荷に基づ

く信号を出力する複数の増幅部と、第2導電型の第3半導体領域を用いた第1の素子分離部と、絶縁体を用いた第2の素子分離部と、を有する、ことを特徴とする。

---

フロントページの続き

F ターム(参考) 4M118 AB01 BA14 CA04 DD04 DD12 FA06 FA14 FA25 FA26 FA27

FA28 FA34 FA38 GB03 GB07

5C024 BX01 CX32 CY47 GX16 GX18 GY31 GY39 GY41