(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-521496

(P2004-521496A)

(43) 公表日 平成16年7月15日(2004.7.15)

(51) Int.Cl.<sup>7</sup>

H01L 23/12

F 1

H01L 23/12

H01L 23/12 501B

テーマコード(参考)

審査請求 未請求 予備審査請求 有 (全 37 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2002-566551 (P2002-566551) |

| (86) (22) 出願日 | 平成14年2月13日 (2002. 2. 13)     |

| (85) 翻訳文提出日   | 平成15年8月18日 (2003. 8. 18)     |

| (86) 國際出願番号   | PCT/US2002/004193            |

| (87) 國際公開番号   | W02002/067326                |

| (87) 國際公開日    | 平成14年8月29日 (2002. 8. 29)     |

| (31) 優先権主張番号  | 09/785, 620                  |

| (32) 優先日      | 平成13年2月16日 (2001. 2. 16)     |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 503297121<br>アシュバッタ・セミコンダクター・インコ<br>ーポレーテッド<br>アメリカ合衆国カリフォルニア州9212<br>1, サンディエゴ, ワブレス・ストリート<br>95911 |

| (74) 代理人 | 100089705<br>弁理士 杜本 一夫                                                                               |

| (74) 代理人 | 100076691<br>弁理士 増井 忠式                                                                               |

| (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                                |

| (74) 代理人 | 100080137<br>弁理士 千葉 昭男                                                                               |

最終頁に続く

(54) 【発明の名称】干渉遮蔽を有する集積回路ダイ

## (57) 【要約】

【課題】 フラディ・ケージを一体化した集積回路パッケージを提供する。

【解決手段】 デバイス(例えば、集積回路チップまたはダイ)を収容するパッケージは、フラディ・ケージを含む。フラディ・ケージは、少なくとも部分的に、集積回路ダイ内に形成されている。ダイは、回路を包囲する導電性ピアとはんだボールとを含む。パッケージは、ボール・グリッド・アレイ(BGA)パッケージまたはフリップ・チップ・パッケージとすることができる。パッケージ基板は、接地面を含むことができる。

**【特許請求の範囲】****【請求項 1】**

集積回路パッケージであって、

第1回路と、少なくとも1つの第2回路とを含み、前記第1回路が、複数の導電性ピアによって、側面を包囲されている、集積回路と、

接地面を有することにより、前記導電性ピアおよび接地面が、前記第1回路からの電磁干渉から前記第2回路を保護するようにした、パッケージ基板と、

を備えている、集積回路パッケージ。

**【請求項 2】**

請求項1記載の集積回路パッケージにおいて、前記導電性ピアが、前記接地面に電気的に 10

結合されている、集積回路パッケージ。

**【請求項 3】**

請求項2記載の集積回路パッケージにおいて、前記導電性ピアが、はんだボールによって

、前記接地面に結合されている、集積回路パッケージ。

**【請求項 4】**

請求項1記載の集積回路パッケージにおいて、前記パッケージ基板が、ボール・グリッド

・アレイ基板である、集積回路パッケージ。

**【請求項 5】**

請求項1記載の集積回路パッケージであって、更に、

前記集積回路上部に導電性カバーを備えている、集積回路パッケージ。 20

**【請求項 6】**

請求項1記載の集積回路パッケージにおいて、前記集積回路が、複数の金属層を含み、前

記ピアが前記金属層全てを貫通する、集積回路パッケージ。

**【請求項 7】**

請求項6記載の集積回路パッケージにおいて、前記集積回路が、更に、前記金属層上部に

半導体基板を含み、該半導体基板が上端面上にあり、前記金属層が下端面上にあり、該下

端面が前記パッケージ基板に隣接する、集積回路パッケージ。

**【請求項 8】**

請求項1記載の集積回路パッケージにおいて、前記第1回路が発振器である、集積回路パ

ッケージ。 30

**【請求項 9】**

請求項6記載の集積回路パッケージにおいて、前記第1回路が、前記金属層の1つに配さ

れたインダクタを含み、前記1つの金属層が、前記半導体基板から最も離れた金属層である、

集積回路パッケージ。

**【請求項 10】**

フリップ・チップ・パッケージ上に実装するための集積回路であって、

半導体基板と、

複数の金属層と、

複数の導電性ピアであって、該導電性ピアによって規定される外周の内部に第1回路があ

り、前記外周の外側に第2回路があり、これによって電磁遮蔽を設ける、導電性ピアと、

を備えている、集積回路。 40

**【請求項 11】**

請求項10記載の集積回路において、前記フリップ・チップ・パッケージが、前記外周内

部において少なくともあるエリアに及ぶ接地面を有するボール・グリッド・アレイ基板で

ある、集積回路。

**【請求項 12】**

請求項10記載の集積回路において、前記金属層がインダクタを含む、集積回路。

**【請求項 13】**

請求項12記載の集積回路において、前記半導体基板がトランジスタを含む、集積回路。

**【請求項 14】**

10

20

30

40

50

請求項 1 3 記載の集積回路において、前記第 1 回路が発振器を含む、集積回路。

【請求項 1 5】

請求項 1 3 記載の集積回路において、前記発振器が広い周波数範囲で動作する、集積回路。

【請求項 1 6】

パッケージ内に内蔵した集積回路ダイにファラディ・ケージを設ける方法であって、前記集積回路ダイ内において回路の外周の周囲に導電性ピアを設けるステップと、前記集積回路をパッケージ基板上に実装するステップであって、前記導電性ピアを前記パッケージ基板の導電面に電気的に結合する、ステップと、

から成る方法。

10

【請求項 1 7】

請求項 1 6 記載の方法において、前記導電面が接地面である、方法。

【請求項 1 8】

請求項 1 6 記載の方法において、前記集積回路ダイが、前記基板の金属層を含み、前記ピアを前記金属層を貫通して設けた、方法。

【請求項 1 9】

請求項 1 8 記載の方法において、前記回路を、前記回路ダイ上の少なくとも 1 つの他の回路に結合し、前記少なくとも 1 つの他の回路を前記外周の外側に位置付ける、方法。

【請求項 2 0】

請求項 1 6 記載の方法において、前記回路が発振器である、方法。

20

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、一般的に、集積回路 ( I C ) および集積回路用パッケージに関する。更に特定すれば、本発明は、電磁遮蔽特性を改善した集積回路に関する。

【背景技術】

【0 0 0 2】

集積回路のパッケージは、一般に、集積回路チップまたはダイを内蔵した高度密集回路を内蔵している。多数の電子回路が集積回路上に近接して設けられているため、電磁干渉が発生する可能性がある。集積回路内部の回路が、隣接するセルまたは回路にエネルギーを散逸するのを防止することが望ましい。

30

【0 0 0 3】

1 つのシステムまたは回路が、他のシステムまたは回路内にエネルギーを放射して、他の回路の機能性または動作を混乱させる可能性がある。放射線またはその他のエネルギーは、基板結合、共通接地、または共通電源によって分散される可能性がある。エネルギーは、隣接する回路内に偽性信号を誘発し、他の回路構成要素の動作を阻害する可能性さえある。

【0 0 0 4】

干渉の問題は、高周波 ( H F ) および無線周波数 ( R F ) では格別な問題である。集積回路上の回路間の電磁干渉は、低い方の周波数においても問題となる可能性がある。

これまで、回路間の電磁干渉を防止するには、チップ上のシステムまたは回路数を制限していた。各チップは、一般に、電磁放射線源となる単一の回路または電磁放射線に感応する単一の回路と共に動作する。各チップを封入し、このパッケージを、ファラディ・ケージ (Faraday cage) におけるように、外部から遮蔽することができる。

40

【0 0 0 5】

チップ上の回路数を制限すると、システム全体のコスト上昇を招く。何故なら、システムはより多くのチップを用いなければならないからである。加えて、パッケージ毎に個別のファラディ・ケージを用いることによっても、システムのコスト上昇を招く。また、チップの遮蔽は、製造および組立コストの上昇を招く。更に、封入するチップおよび外部ファラディ遮蔽の数量増大によって、システム全体のサイズ増大に至る。

【0 0 0 6】

50

従来の電磁遮蔽技術の一例が、米国特許第5,986,340号に開示されている。これは、ボール・グリッド・アレイ(BGA)パッケージについて記載している。このパッケージは、集積回路ダイ周囲に形成された外部ファラディ・ケージを含む。外部ファラディ・ケージは、集積回路ダイを取り囲むヒート・シンク、およびヒート・シンクの上面上の金属板で構成されている。

#### 【0007】

米国特許第5,986,340号は、米国特許第5,955,789号に似ており、キャビティ・ダウン(cavity down)構成のプラスチック・ボール・グリッド・アレイ(BGA)電子パッケージを開示する。パッケージは、パッケージ基板上に実装されている能動素子を含み、HF用途に用いられる。外部ファラディ・ケージを実現し、外部HF干渉から能動素子を保護する。はんだボールの列が、パッケージ基板の底面上にジグザクに配され、めっきしたスルーホールが、外部ファラディ・ケージの側面からパッケージ基板を貫通している。外部ファラディ・ケージの上面には、金属キャップが形成され、更に外部ファラディ・ケージの底面には、主ボードの接地面が形成されている。米国特許第5,955,789号におけるパッケージは、集積回路(ICC)ダイ内部には、遮蔽効果をもたらさない。

【特許文献1】米国特許第5,986,340号

【特許文献2】米国特許第5,955,789号

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

したがって、ファラディ・ケージを一体化して含むパッケージ・システムが求められている。更に、内部チップ構造を利用したファラディ・ケージも求められている。更にまた、低価格の電磁遮蔽を含む、フリップ・チップ・パッケージと共に用いるダイも求められている。そして更に、電磁干渉保護機能を備え、BGAやフリップ・チップ・パッケージのような高度封入システムに貢献するチップも求められている。

#### 【課題を解決するための手段】

#### 【0009】

実施形態の一例は、集積回路のパッケージに関する。この集積回路のパッケージは、集積回路およびパッケージ基板を含む。集積回路は、第1回路と、少なくとも1つの第2回路とを含む。第1回路は、複数の導電性ピアによって、側面を包囲されている。パッケージ基板は、接地面を有する。導電性ピアおよび接地面は、第2回路を電磁干渉から保護する。

#### 【0010】

実施形態の別の例は、フリップ・チップ・パッケージ上に実装するための集積回路に関する。この集積回路は、半導体基板と、複数の金属層と、複数の導電性ピアとを含む。第1回路が、導電性ピアによって規定される周囲内部にあり、第2回路がこの周囲の外側にある。導電性ピアは、電磁遮蔽を担う。

#### 【0011】

更に別の実施形態は、パッケージ内に内蔵されている集積回路ダイにファラディ・ケージを設ける方法に関する。この方法は、集積回路ダイ内の回路の外周に沿って導電性ピアを設けるステップと、パッケージ基板上に集積回路を実装するステップとを含む。導電性ピアを、パッケージ基板の導電面に電気的に結合する。

#### 【0012】

本発明は、添付図面に関連付けた、以下の詳細な説明から一層深く理解されよう。図面においては、同様の参照番号は同様の部分を示すこととする。

#### 【発明を実施するための最良の形態】

#### 【0013】

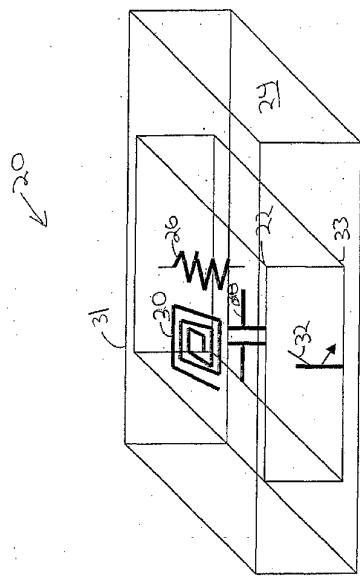

図1を参照すると、集積回路チップ即ちダイ20は、内部ファラディ・ケージ即ち電磁遮蔽によって保護されている回路22を含む。回路22は、外部ファラディ・ケージに伴う

10

20

30

40

50

高コストや組立の問題を生ずることなく、ダイ20内部にモノリシックに保護できる利点がある。回路22は、ダイ20の部分24に位置する別の回路からは物理的に分離することが好ましい。

#### 【0014】

ダイ20の別の部分24上に位置する回路は、回路22と電気的に接続することができる。しかしながら、回路22およびダイ2の別の部分24上の回路は、内部ファラディ・ケージ即ち遮蔽25(図2)によって干渉から保護されている。遮蔽25は、導電性ビア、はんだボール、および層のような、ダイ20の構成要素によって明示することができる。遮蔽25は、孔またはギャップを含んでもよい。好ましいことに、孔またはギャップを伴う構造は適当な遮蔽を設けることができる。何故なら、これらの孔またはギャップの寸法は、電磁放射線に関与する波長よりも遥かに小さいからである。10

#### 【0015】

回路22は、いずれの種類の回路とすることもできる。好ましくは、回路22は、抵抗26、コンデンサ28、インダクタ30、およびトランジスタ32のような、1つ以上の構成要素を含むことができる。好ましくは、トランジスタ32は、ダイ20の半導体基板または薄膜に接する面33上に位置し、インダクタ30は、集積回路ダイ20の上面31に付随する金属層内に位置する。例えば、インダクタ30は、最上位のメタル・レベル上に位置することができる。

#### 【0016】

ダイ20は、従来のIC製造プロセスおよびツールによって形成した従来の素子で形成した集積回路とすることができる。ダイ20は、多数の金属層(即ち、4層以上)を含み、半導体基板の上部に配することができる。これについては、図3に関して以下で詳細に説明する。ダイ20の構造の例には、BICMOS IC構造、CMOS IC構造、またはバイポーラIC構造がある。20

#### 【0017】

回路22は、種々の機能性を備え、多数の構成要素を含むことができる。例えば、回路22は、低周波から高周波までの範囲で動作する発振器とすることができる。発振器は、抵抗、インダクタ、およびコンデンサを含む発振器とすることができる。同様に、集積回路ダイ20の部分24内に位置するその他の回路は、種々の機能性を有することができる。これら他の回路は、発振器、論理回路、ドライバ、メモリ回路、クロック回路、またはその他のデバイスとすることができます。30

#### 【0018】

回路22、部分24上に位置する回路、およびダイ20上の構成要素についての記載は、限定を意図して行っているのではない。集積回路ダイ20上では、本発明の範囲から逸脱すことなく、様々な形式の回路および機能性を達成することができます。

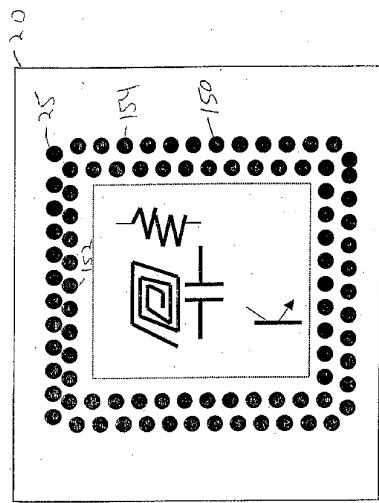

#### 【0019】

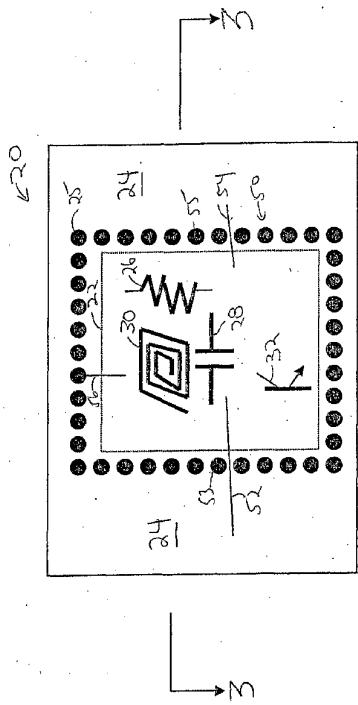

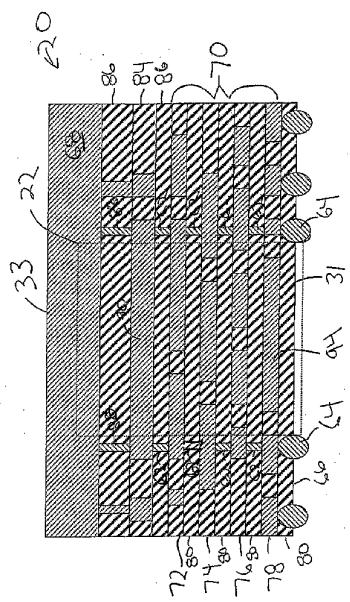

図1ないし図3を参照すると、集積回路ダイ20は、ファラディ・ケージ即ち遮蔽25を含み、その外周50が回路22を包囲している。集積回路ダイ20は、半導体基板68(図3)および導電層70を含む。全体的に、層70は、導電性金属層72、74、76および78で構成することができる。各導電層72、74、76および78の間に、誘電体層80を設けることができる。40

#### 【0020】

層72、74、および76の厚さは、約0.5ミクロンとすることができます。層78の厚さは、3ミクロンとすることができます。層72、74、および76間の間隔は、約1ミクロンとすることができます。層76および78間の間隔は、約2ないし3ミクロンとすることができます。

#### 【0021】

層72、74、76、および78は、種々の構成で配された導電線を含む。層72、74、76、および78は、従来のプロセスにしたがってパターニングした、従来の金属層(A1、Cu、およびその他の合金)とすることができます。図面および説明は、本開示をい50

ずれの特定数または構成の導電線にも限定することを意図するのではない。

#### 【0022】

導電性コンタクト即ちビア62は、好ましくは、層72、74、76、78および80全てを貫通するように設け、回路22に対して電磁干渉保護を備えるようにする。図3では、ビア62は互いにに対して垂直方向に位置合わせして示されている。しかしながら、ビア62を千鳥状に配することもでき、なおも回路22に対して有効な遮蔽即ち絶縁機能性を達成することができる。例えば、ビア62は、ポリシリコン、タングステン、およびアルミニウムを含むことができ、エッチングおよび充填プロセスにおいて形成することができる。ビア62は、好ましくは、回路22に沿って遮蔽25の外周50を規定し、ポリシリコン層84から層78まで達する。

10

#### 【0023】

ポリシリコン層84は、導電層70と半導体基板68との間に配置されている。ポリシリコン層84は、種々の構成にしたがってパターニングすることができる。誘電体層86は、層84を金属層70および半導体基板68から絶縁する。

#### 【0024】

ポリシリコン層84は、従来のドープしたポリシリコン金属（N型またはP型のいずれか）とすることができます。好ましくは、設計要件にしたがって、層84を部分的にN型およびP型にドープする。層84は、基板コンタクト88によって、基板68に結合されている。基板コンタクト88は、誘電体層86を貫通し、前述の導電性ビア62と同様とすることができる。層84は、コンタクト88によって基板68に結合されている中央部90を含む。層84の別の部分は、他のコンタクトによって基板68に結合されている。

20

#### 【0025】

抵抗26（図1および図2）は、好ましくは基板68内または回路22の層84内に位置する。コンデンサ28は、好ましくは、基板68または回路22の導電層70内に位置する。インダクタ30は、好ましくは、回路22の導電層70内に位置し、トランジスタ32は、回路22の基板68内に位置する。

#### 【0026】

最下位の導電層（例えば、層78）は、中央部94を含むことができる。インダクタ30は、部分94内部に製造することができる。あるいは、インダクタ30は、金属層72、74、または76のような、単一の下位金属層上、または層72、74、76、および78の組み合わせの上に位置することができる。

30

#### 【0027】

中央部94は、好ましくは、絶縁され、更に導電層70、導電性ビア62、およびポリシリコン層84の中央部90によって、ダイ20の部分24から電磁的に遮蔽されている。あるいは、ポリシリコン層84を除去することもできる。一般に、ポリシリコン層84の部分90がない構造でも、電磁放射線の波長未満に寸法を抑えておけば、十分な遮蔽を行うことができる。別の代替案では、導電層70の1つ（例えば、層72）の中央部が、層78の中央部84上で遮蔽を行うように機能することができる。

#### 【0028】

はんだボール64は、ダイ20の基板68とは反対側の端部（端部31）上に設けることができる。はんだボール64は、層78に（電気的および物理的に）結合され、更に接地されている。はんだボール64は、ビア62に電気的に結合されている。

40

#### 【0029】

回路22は、遮蔽25を貫通して設けられた入力／出力52（図2）（ファラディ・ケージのギャップを通じて）を含むことができる。一実施形態では、回路22は、一方側53に入力／出力52を含み、反対側55に入力／出力54を含む。入力／出力52および54は、ファラディ・ケージ25を貫通して（ビア62間に）設けられている。

#### 【0030】

一実施形態によれば、ビア62およびコンタクト68は円筒状（例えば、矩形または円形）である。ビア62は、クラスタ単位に配置され、遮蔽25の列として作用することができます。

50

きる。ビア 6 2 は、互いに数ミクロンないし数百ミクロンだけ離間することができる。コンタクト 6 8 も同様に離間することができる。

【 0 0 3 1 】

ビア 6 2 を 1 0 0 ミクロンだけ離間すると、多ギガヘルツ(multi-gigahertz)範囲までの周波数を十分遮蔽することができる。間隔は、周波数が低ければ、更に広くすることができる。ビア 6 2 間の間隔は、ダイ 2 0 のフリップ・チップ構成に対するはんだボール 6 4 のサイズ要件によって決定することができる。

【 0 0 3 2 】

別の代替実施形態では、ビア 6 2 およびコンタクト 6 8 は、外周 5 0 に沿った連続トレンチ(trench)である。層 7 0 は、本実施形態では、外周 5 0 に沿った導電線を含む。この代替実施形態によれば、入力 / 出力 5 2 および入力 / 出力 5 4 のために、層 7 0 の少なくとも 1 つにギャップを設けることができる。

【 0 0 3 3 】

好適な実施形態では、遮蔽 2 5 を接地し、導体 5 6 を通じて回路 2 2 に接地信号を供給する。遮蔽 2 5 は、好ましくは、導電性ビア 6 2 およびはんだボール 6 4 から成る。導電性ビア 6 2 は、好ましくは、ダイ 2 0 の層 7 8 上にあるはんだボール 6 4 に取り付けられている。コンタクトおよびその他のビアは、はんだボール 6 4 の表面 6 6 への取付に供するために用いることができる。

【 0 0 3 4 】

基板 6 8 は、絶縁物上シリコン基板、半導体基板、ガリウム砒素(GaAs)基板、ゲルマニウム(Ge)基板、薄膜、またはその他のデバイスを含む、いずれの種類の基板とすることもでき、その上に回路 2 2 を製造することができる。好ましくは、基板 6 8 は、低濃度にドープした P 型基板である。

【 0 0 3 5 】

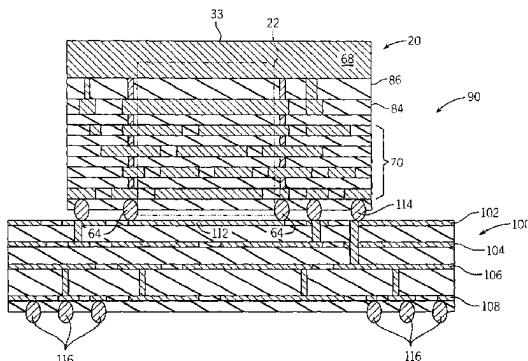

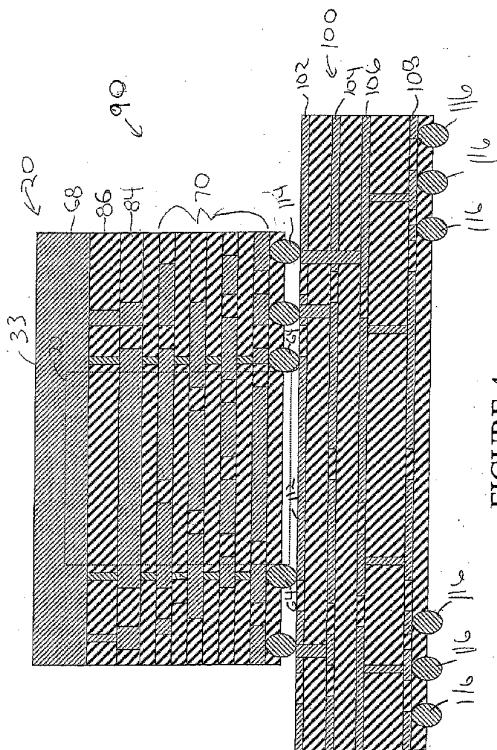

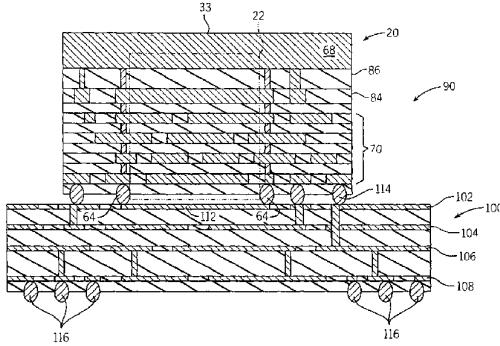

図 4 を参照すると、ここに示す集積回路ダイ 2 0 は、集積回路パッケージ基板 1 0 0 に結合されており、これによってパッケージ 9 0 を形成する。集積回路ダイ 2 0 は、好ましくは、フリップ・チップ構成で取り付ける。

【 0 0 3 6 】

パッケージ基板 1 0 0 は、プラスチック基板、PCB ボード基板、セラミック基板、またはダイ 2 0 を受容するいずれの材料とすることもできる。パッケージ基板 1 0 0 は、1 つの導電層または 2 つ以上の導電層を含む。図 4 では、パッケージ基板 1 0 0 は 4 つの導電層、層 1 0 2 、 1 0 4 、 1 0 6 、および 1 0 8 を含む。好ましくは、層 1 0 2 は、はんだボール 6 4 を受けるコンタクトを含む。

【 0 0 3 7 】

一実施形態では、層 1 0 2 は、電気的にはんだボール 6 4 に結合可能な導電面(conductive plane) 1 1 2 を含む。導電面 1 1 2 は、層 1 0 2 に付随し、ファラディ・ケージ即ち遮蔽 2 5 の底面となる。導電面 1 1 2 は、好ましくは、遮蔽 2 5 の外周 5 0 (図 2 )と対応するエリアを有する。導電面 1 1 2 は層 1 0 2 内に示されているが、層 1 0 4 、 1 0 6 、または 1 0 8 のいずれでも、導電面のために利用することができる。

【 0 0 3 8 】

また、パッケージ 9 0 は、ダイ 2 0 の部分 2 4 (図 1 )上にあるその他の回路をパッケージ基板 1 0 0 に結合するために、はんだボール 1 1 4 も含む。種々のコンタクトおよびビア構成を利用して、基板 1 0 0 に対する相互接続を設けることができる。また、基板 1 0 0 は、1 組のピンまたははんだボール 1 1 6 も含み、パッケージ基板 1 0 0 を印刷回路ボードまたはその他のモジュールに結合することができる。

【 0 0 3 9 】

また、ダイ 2 0 は、基板 6 8 上部に被覆層(図示せず)を含むことができる。好ましくは、被覆層は、導電性材料であり、集積回路ダイ 2 0 の基板 6 8 に対して電磁保護を設ける。

【 0 0 4 0 】

10

20

30

40

50

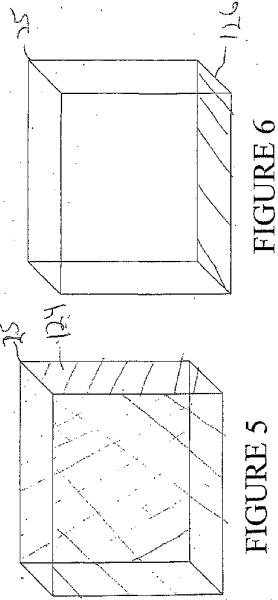

図5を参照すると、ファラディ・ケージ即ち遮蔽25は、側壁124(図5では斜線で示す)を含む。側面即ち側壁124は、導電性ビア62およびはんだボール64で形成されている(図3)。図6を参照すると、ファラディ・ケージ即ち遮蔽25の底面126(斜線で示す)は、接地面(ground plane)によって設けることができる。接地面は、パッケージ基板100の層102の面112とすることができる。あるいは、導電層70の1つ(例えば、層78)が接地面となることも可能である。あるいは、層78の下に追加の金属層を設け、集積回路ダイ20上に接地面を設けることもできる。

#### 【0041】

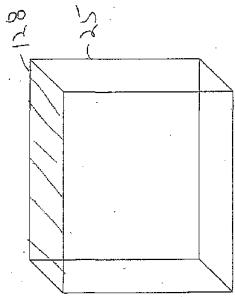

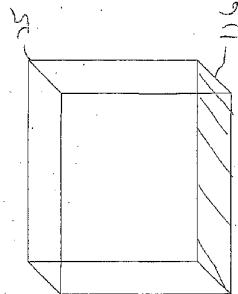

図7を参照すると、ファラディ・ケージ即ち遮蔽25のシーリング(ceiling)即ち上面128(斜線で示す)は、層84(図3)によって設けることができる。あるいは、基板20内部のドープ領域、または基板20上部の導電層を利用することもできる。

10

#### 【0042】

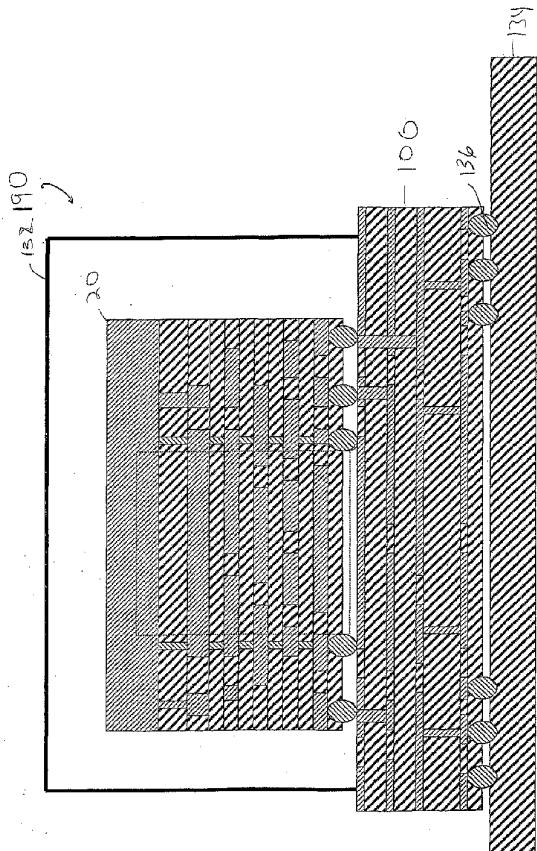

図8を参照すると、パッケージ90と同様のパッケージ190は、パッケージ基板100上に集積回路ダイ20を含む。パッケージ190は、ダイ20周囲に蓋132を含む。蓋132は、導電性であり、接地に結合することができる。パッケージ基板100は、印刷配線回路ボード134に結合するために、ピンまたははんだボール136を含むことができる。あるいは、パッケージ190は、マルチ・チップ・モジュールのようなモジュールまたはその他のデバイスとして接続し、ダイ20をシステム内部で結合させることもできる。

#### 【0043】

図9を参照すると、ファラディ・ケージ即ち遮蔽25に付随する側壁124(図5)は、はんだボールおよび導電性ビア150の二重層で構成することができる。二重層は、好ましくは、内側周囲152内のビア間の間隔が、外側周囲154上のビアおよびはんだボールによって覆われるように構成する。

20

#### 【0044】

これまでに図面に示し説明した実施形態は現時点では好適ではあるが、これらの実施形態は一例として提示したに過ぎないことは当然理解されよう。例えば、熱膨張、微細化、腐食、および開示した実施形態が取り組んだその他の設計要件に対処するのに適した実施形態の更に別の例として、代わりの材料および電気コンタクトの構成が考えられる。更に、導電性ビア、メッキ・スルーホール、導電線、およびその他の要素のサイズおよび形状は、限定の意味で示した訳ではない。本発明は、特定の実施形態に限定されるのではなく、添付した特許請求の範囲に該当する種々の変更にも及ぶものとする。

30

#### 【図面の簡単な説明】

#### 【0045】

【図1】図1は、実施形態の一例による集積回路ダイの全体的概略ブロック斜視図である。

。

【図2】図2は、図1に示す集積回路ダイの全体的概略ブロック底面図である。

【図3】図3は、図2に示す集積回路ダイの、線3-3に沿った、全体的概略ブロック断面図である。

【図4】図4は、別の実施形態にしたがってパッケージ基板上に実装した、図3に示した集積回路パッケージの全体的概略ブロック断面図である。

40

【図5】図5は、図3に示す集積回路ダイに付随するファラディ・ケージの側壁を示す全体的概略ブロック図である。

【図6】図6は、図3に示す集積回路ダイのフロアを示す、ファラディ・ケージの全体的概略ブロック図である。

【図7】図7は、図3に示す集積回路ダイのファラディ・ケージのシーリングを示す、全体的概略ブロック図である。

【図8】図8は、更に別の実施形態例にしたがって、パッケージ基板に取り付け、蓋で覆われた集積回路の全体的概略ブロック断面図である。

【図9】図9は、更に別の代替実施形態による、二重列の導電性ビアを含む、図2に示し

50

た集積回路ダイに類似した、集積回路ダイの全体的概略ブロック底面図である。

WO 02/067326

PCT/US02/04193

**INTEGRATED CIRCUIT DIE HAVING AN INTERFERENCE SHIELD****FIELD OF THE INVENTION**

[0001] The present specification relates generally to integrated circuits (ICs) and packages for integrated circuits. More specifically, the present specification relates to integrated circuits having improved electromagnetic shielding properties.

**BACKGROUND OF THE INVENTION**

[0002] Integrated circuit packages generally contain integrated circuit chips or die-containing densely packed circuits. Large numbers of electronic circuits placed in close proximity on an integrated circuit die can cause electromagnetic interference. It is desirous to prevent circuits within an integrated circuit from dispersing energy into adjacent cells or circuits.

[0003] One system or circuit can radiate energy into another system or circuit and disrupt the functionality or operation of the other circuit. Radiation or other energy can be disbursed by substrate coupling, through common ground, or through common power supplies. The energy can induce spurious signals in neighboring circuits or even prevent the operation of other circuit components.

[0004] The interference problem is a particular problem at high frequencies (HF) and radio frequencies (RF). Electromagnetic interference between circuits on an integrated circuit can also be a problem at lower frequencies.

[0005] Heretofore, electromagnetic interference between circuitry has been prevented by limiting the number of systems or circuits on a chip. Each chip is generally associated with a single circuit that is a source or is sensitive to electromagnetic radiation. Each chip is packaged and that package can be externally shielded, such as, in a Faraday cage.

[0006] Limiting the number of circuits on the chip increases costs of the entire system because the system must employ more chips. In addition,

WO 02/067326

PCT/US02/04193

the use of individual Faraday cages for each package increases the cost of the system. Shielding the chip also increases manufacturing and assembly costs. Further, the entire size of the system is increased by the increased number of packaged chips and the external Faraday shielding.

[0007] An example of conventional electromagnetic shielding techniques is disclosed in U.S. Patent No. 5,986,340 which describes a ball grid array (BGA) package. The package includes an external Faraday cage formed around the integrated circuit die. The external Faraday cage is comprised of a heat sink surrounding the integrated circuit die and a metal plate on an upper peripheral surface of the heat sink.

[0008] U.S. Patent No. 5,986,340 is similar to U.S. Patent No. 5,955,789 and discloses a plastic ball grid array (BGA) electronic package in a cavity down configuration. The package includes an active element mounted on a package substrate and is for use in HF applications. An external Faraday cage is realized to protect the active element from external HF interferences. A row of solder balls connected in a zig-zag fashion on a bottom of the package substrate and plated-through holes through the package substrate form lateral sides of the external Faraday cage. The top side of the external Faraday cage is formed of a metal cap and the bottom side of the external Faraday cage is formed by a ground plane of the main board. The package in U.S. Patent No. 5,955,789 does not provide shielding within the integrated circuit (IC) die.

[0009] Accordingly, there is a need for a package system that includes an integrated Faraday cage. Further, there is a need for a Faraday cage which utilizes internal chip structures. Further still, there is a need for a die for use with a flip chip package that includes a low-cost electromagnetic shield. Yet further, there is a need for a chip with electromagnetic interference protection that is conducive to advanced packaging systems, such as, BGA and flip chip packages.

#### SUMMARY OF THE INVENTION

[0010] An exemplary embodiment relates to an integrated circuit package. The integrated circuit package includes an integrated circuit and a

WO 02/067326

PCT/US02/04193

package substrate. The integrated circuit includes a first circuit and at least one second circuit. The first circuit is surrounded on lateral sides by a plurality of conductive vias. The package substrate has a ground plane. The conductive vias and the ground plane protect the second circuit from electromagnetic interference.

[0011] Another exemplary embodiment relates to an integrated circuit for mounting onto a flip chip package. The integrated circuit includes a semiconductor substrate, a plurality of metal layers, and a plurality of conductive vias. A first circuit is within a perimeter defined by the conductive vias and a second circuit is disposed outside the perimeter. The conductive vias provide electromagnetic shielding.

[0012] Still another embodiment relates to a method of providing a Faraday cage for an integrated circuit die contained in a package. The method includes providing conductive vias about a periphery of a circuit in the integrated circuit die, and mounting the integrated circuit die on a package substrate. The conductive vias are electrically coupled to a conductive plane of the package substrate.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0013] The invention will become more fully understood from the following detailed description, taken in conjunction with the accompanying drawings, wherein like reference numerals refer to like parts, and in which:

[0014] FIGURE 1 is a schematic general block diagram perspective view of an integrated circuit die according to an exemplary embodiment;

[0015] FIGURE 2 is a schematic general block diagram bottom planar view of the integrated circuit die illustrated in FIGURE 1;

[0016] FIGURE 3 is schematic general block diagram cross-sectional view of the integrated circuit die illustrated in FIGURE 2 about line 3-3;

[0017] FIGURE 4 is a schematic general block diagram cross-sectional view of the integrated circuit package illustrated in FIGURE 3 mounted on a package substrate in accordance with an alternative embodiment;

WO 02/067326

PCT/US02/04193

[0018] FIGURE 5 is a schematic general block diagram showing side walls of a Faraday cage associated with the integrated circuit die illustrated in FIGURE 3;

[0019] FIGURE 6 is a schematic general block diagram of a Faraday cage showing a floor for the integrated circuit die illustrated in FIGURE 3;

[0020] FIGURE 7 is a schematic general block diagram showing a ceiling of a Faraday cage for the integrated circuit die illustrated in FIGURE 3;

[0021] FIGURE 8 is a schematic general block diagram cross-sectional view of an integrated circuit die attached to a package substrate and covered by a lid in accordance with still another exemplary embodiment; and

[0022] FIGURE 9 is a schematic general block diagram bottom planar view of an integrated circuit die similar to the integrated circuit die illustrated in FIGURE 2 including a double row of conductive vias in accordance with still another alternative embodiment.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0023] With reference to FIGURE 1, an integrated circuit chip or die 20 includes a circuit 22 protected by an internal Faraday cage or electromagnetic shielding. Circuit 22 is advantageously protected monolithically within die 20 without the high costs and assembly problems associated with external Faraday cages. Circuit 22 is preferably physically separate from other circuits located on portions 24 of die 20.

[0024] Circuits located on other portions 24 of die 20 can be electrically connected with circuit 22. However, circuit 22 and circuits on other portions 24 of die 20 are protected from interference by internal Faraday cage or shielding 25 (FIGURE 2). Shielding 25 can be manifested by integral components of die 20, such as, conductive vias, solder balls, and layers. Shielding 25 may include holes or gaps. Preferably, structures with holes or gaps can provide adequate shielding because the dimension of those holes or gaps is significantly smaller than the wavelengths associated with the electromagnetic radiation.

WO 02/067326

PCT/US02/04193

[0025] Circuit 22 can be any type of circuit. Preferably, circuit 22 can include one or more components, such as, resistor 26, capacitor 28, inductor 30, and transistor 32. Preferably, transistor 32 is located on a side 33 associated with a semiconductor substrate or thin film of die 20, and inductor 30 is located in a metal layer associated with a top side 31 of integrated circuit die 20. For example, inductor 30 can be located on a top-most metal level.

[0026] Die 20 can be an integrated circuit formed of conventional elements formed by conventional IC fabrication processes and tools. Die 20 can include a number of layers of metal (i.e., 4 or more) disposed above a semiconductor substrate, as discussed in detail below with respect to FIGURE 3. Exemplary structures for die 20 are BICMOS IC structures, CMOS IC structures, or bipolar IC structures.

[0027] Circuit 22 can provide various functionality and can include any number of components. For example, circuit 22 can be an oscillator operating in low frequency to high frequency range. The oscillator can be an oscillator including resistors, an inductor, and a capacitor. Similarly, other circuits located in portions 24 of integrated circuit die 20 can have various functionalities. The other circuits can be oscillators, logic circuits, drivers, memory circuits, clock circuitry, or other devices.

[0028] Circuit 22, circuits located on portions 24, and components on die 20 are not described in a limiting fashion. Various types of circuits and functionality can be achieved on integrated circuit die 20 without departing from the scope of the invention.

[0029] With reference to FIGURES 1-3, integrated circuit die 20 includes a Faraday cage or shield 25 having a perimeter 50 surrounding circuit 22. Integrated circuit die 20 includes a semiconductor substrate 68 (FIGURE 3) and conductive layers 70. Generally, layers 70 can be comprised of conductive metal layers 72, 74, 76 and 78. A dielectric layer 80 can be provided between each of conductive layers 72, 74, 76 and 78.

[0030] Layers 72, 74, and 76 can be approximately 0.5 microns thick. Layer 78 can be 3 microns thick. The spacing between layers 72, 74,

WO 02/067326

PCT/US02/04193

and 76 can be approximately 1 micron. The spacing between layers 76 and 78 can be approximately 2-3 microns.

[0031] Layers 72, 74, 76, and 78 include conductive lines arranged in various configurations. Layers 72, 74, 76, and 78 can be conventional metal layers (Al, Cu, and other alloys) patterned according to a conventional process. The FIGURES and the description are not intended to limit the disclosure to any particular number or configuration of conductive lines.

[0032] Conductive contacts or vias 62 are preferably provided through all of layers 72, 74, 76, 78 and 80 to provide electromagnetic interference protection for circuit 22. Vias 62 are shown in FIGURE 3 as aligned vertically with respect to each other. However, vias 62 can be staggered and still achieve an advantageous shielding or isolation functionality for circuit 22. For example, vias 62 can include polysilicon, tungsten, and aluminum and can be formed in an etch and fill process. Vias 62 can be conventional interconnects formed in a conventional process. Vias 62 preferably define periphery 50 of shielding 25 about circuit 22 and extend from a polysilicon layer 84 to layer 78.

[0033] Polysilicon layer 84 is disposed between conductive layers 70 and semiconductor substrate 68. Polysilicon layer 84 can be patterned according to various arrangements. Dielectric layers 86 insulate layer 84 from metal layers 70 and semiconductor substrate 68.

[0034] Polysilicon layer 84 can be a conventional doped polysilicon material (either N-type or P-type). Preferably, portions of layer 84 are doped N-type and P-type according to design considerations. Layer 84 is coupled to substrate 68 by substrate contacts 88. Substrate contacts 88 extend through dielectric layer 86 and can be similar to conductive vias 62 described above. Layer 84 includes a center portion 90 coupled to substrate 68 by contacts 88. Other portions of layer 84 can be coupled to substrate 68 by other contacts.

[0035] Resistor 26 (FIGURES 1 and 2) is preferably located in substrate 68 or in layer 84 of circuit 22. Capacitors 28 are preferably located in substrate 68 or conductive layers 70 of circuit 22. Inductor 30 is preferably

WO 02/067326

PCT/US02/04193

located in conductive layers 70 of circuit 22, and transistor 32 is located in substrate 68 of circuit 22.

[0036] A bottom most conductive layer (e.g., layer 78) can include a center portion 94. Inductor 30 can be fabricated within portion 94. Alternatively, inductor 30 can be located on a single lower metal layers, such as, metal layers 72, 74, or 76 or on a combination of layers 72, 74, 76, and 78.

[0037] Center portion 94 is preferably isolated, and electromagnetically shielded from portions 24 of die 20 by conductive layers 70, conductive vias 62, and center portion 90 of polysilicon layer 84. Alternatively, polysilicon layer 84 can be eliminated. Generally, the structure without portion 90 of polysilicon layer 84 can still provide sufficient shielding if dimensions are kept below the wavelength of the electromagnetic radiation. In another alternative, a center portion of one of conductive layers 70 (e.g., layer 72) can serve to provide shielding above center portion 94 of layer 78.

[0038] Solder balls 64 can be provided on an opposite end of die 20 than substrate 68 (end 31). Solder balls 64 are coupled (electrically and physically) to layer 78 and are grounded. Solder balls 64 are electrically coupled to vias 62.

[0039] Circuit 22 can include an input/output 52 (FIGURE 2) provided through shielding 25 (through a gap in the Faraday cage). In one embodiment, circuit 22 includes an input/output 52 on one side 53 and an input/output 54 on an opposing side 55. Input/outputs 52 and 54 are provided through Faraday cage 25 (between vias 62).

[0040] According to one embodiment, vias 62 and contacts 68 are cylindrical (e.g., rectangular or circular). Vias 62 can be arranged in clusters and act as columns for shield 25. Vias 62 can be spaced apart from each other by a few microns to 100s of microns. Contacts 68 can be similarly spaced apart.

[0041] Vias 62 spaced apart by 100 microns can shield frequencies well into multi-gigahertz range. The spacing can be even greater for lower frequencies. Spacing between vias 62 can be determined by solder ball 64 size requirements for the flip-chip arrangement of die 20.

WO 02/067326

PCT/US02/04193

[0042] In another alternative embodiment vias 62 and contacts 68 are a continuous trench along periphery 50. Layers 70 include a conductive line following periphery 50 in this embodiment. According to this alternative, gaps can be provided in at least one of layers 70 for input/output 52 and input/output 54.

[0043] In a preferred embodiment, shielding 25 is grounded and provides a ground signal to circuit 22 via a conductor 56. Shielding 25 preferably comprises conductive vias 62 and solder balls 64. Conductive vias 62 are preferably attached to solder balls 64 on layer 78 of die 20. Contacts and other vias can be used to accommodate the attachment of solder balls 64 to surface 66.

[0044] Substrate 68 can be any type of substrate including a silicon-on-insulator substrate, a semiconductor substrate, a gallium arsenide (GaAs) substrate, a germanium (Ge) substrate, a thin film, or other device upon which circuit 22 can be fabricated. Preferably, substrate 68 is a lightly doped P-type substrate.

[0045] With reference to FIGURE 4, integrated circuit die 20 is shown coupled to an integrated circuit package substrate 100, thereby forming a package 90. Integrated circuit die 20 is preferably attached in a flip chip configuration.

[0046] Package substrate 100 can be a plastic substrate, a PCB board substrate, a ceramic substrate, or any material for receiving die 20. Package substrate 100 includes a conductive layer or two or more conductive layers. In FIGURE 4, package substrate 100 includes four conductive layers: layer 102, 104, 106, and 108. Preferably, layer 102 includes contacts for receiving solder balls 64.

[0047] In one embodiment, layer 102 includes a conductive plane 112 electric coupleable to solder balls 64. Conductive plane 112 associated with layer 102 provides a bottom for the Faraday cage or shield 25. Conductive plane 112 preferably has an area corresponding with periphery 50 (FIGURE 2) of shield 25. Although conductive plane 112 is shown in layer 102, any of layers 104, 106, or 108 can be utilized for the conductive plane.

WO 02/067326

PCT/US02/04193

[0048] Package 90 also includes solder balls 114 for coupling other circuitry on portion 24 (FIGURE 1) of die 20 to package substrate 100. Various contact and via arrangements can be utilized to provide interconnections to substrate 100. Substrate 100 can also include a set of pins or solder balls 116 for coupling package substrate 100 to a printed circuit board or other module.

[0049] Die 20 can also include a cover layer (not shown) above substrate 68. Preferably, the cover layer is a conductive material for providing electromagnetic protection for substrate 68 of integrated circuit die 20.

[0050] With reference to FIGURE 5, Faraday cage or shield 25 includes lateral walls 124 (indicated by cross hatching in FIGURE 5). Side or lateral walls 124 are formed by conductive vias 62 and solder balls 64 (FIGURE 3). With reference to FIGURE 6, a bottom 126 (indicated by cross hatching) of Faraday cage or shield 25 can be provided by ground plane. The ground plane can be plane 112 of layer 102 of package substrate 100. Alternatively, one of conductive layers 70 (e.g., layer 78) can provide the ground plane. Alternatively, an additional metal layer can be provided below layer 78 to provide the ground plane on integrated circuit die 20.

[0051] With reference to FIGURE 7, a ceiling or top surface 128 (indicated by cross hatching) of Faraday cage or shield 25 can be provided by layer 84 (FIGURE 3). Alternatively, a doped region within substrate 20 or a conductive layer above substrate 20 can be utilized.

[0052] With reference to FIGURE 8, a package 190 similar to package 90 includes integrated circuit die 20 on a package substrate 100. Package 190 can include a lid 132 surrounding die 20. Lid 132 can be conductive and coupled to ground. Package substrate 100 can include pins or solder balls 136 for coupling to a printed wire circuit board 134. Alternatively, package 190 can be connected as a module, such as, a multi-chip module or other device for allowing die 20 to be coupled within a system.

[0053] With reference to FIGURE 9, lateral walls 124 associated with Faraday cage or shield 25 (FIGURE 5) can be comprised of a double layer of solder balls and conductive vias 150. The double layer is preferably

WO 02/067326

PCT/US02/04193

configured so that a space between vias in an interior periphery 152 is covered by vias and solder balls on an outside periphery 154.

[0054] While the embodiments illustrated in the FIGURES and described above are presently preferred, it should be understood that these embodiments are offered by way of example only. For example, alternative materials and electrical contact configurations are contemplated as further examples of embodiments suitable to address the thermal expansion, miniaturization, corrosion and other design considerations addressed by the embodiments disclosed. Further, the sizes and shapes of conductive vias, plated through-holes, conductive lines, and other elements are not shown in a limiting fashion. The invention is not limited to a particular embodiment, but extends to various modifications that nevertheless fall within the scope of the appended claims.

WO 02/067326

PCT/US02/04193

**1 WHAT IS CLAIMED IS:**

1. An integrated circuit package, comprising:

2. an integrated circuit including a first circuit, and at least one second circuit, the first circuit being surrounded on lateral sides by a plurality of conductive vias; and

5. a package substrate having a ground plane, whereby the conductive vias and ground plane protect the second circuit from electromagnetic interference from the first circuit.

1. 2. The integrated circuit package of claim 1, wherein the conductive vias are electrically coupled to the ground plane.

1. 2. 3. The integrated circuit package of claim 2, wherein the conductive vias are coupled to the ground plane by solder balls.

1. 2. 4. The integrated circuit package of claim 1, wherein the package substrate is a ball grid array substrate.

1. 2. 5. The integrated circuit package of claim 1, further comprising:

2. a conductive cover above the integrated circuit.

1. 2. 6. The integrated circuit package of claim 1, wherein the integrated circuit includes a plurality of metal layers and wherein the vias extend through all of the metal layers.

1. 2. 3. 4. 7. The integrated circuit package of claim 6, wherein the integrated circuit further includes a semiconductor substrate above the metal layers, wherein the semiconductor substrate is on a top end and the metal layers are on a bottom end, the bottom end being adjacent the package substrate.

1. 2. 8. The integrated circuit package of claim 1, wherein the first circuit is an oscillator.

WO 02/067326

PCT/US02/04193

1        9. The integrated circuit package of claim 6, wherein the first circuit

2 includes an inductor disposed in one of the metal layers, the one metal layer

3 being a metal layer farthest from the semiconductor substrate.

1        10. An integrated circuit for mounting onto a flip chip package, the

2 integrated circuit comprising:

3              a semiconductor substrate;

4              a plurality of metal layers; and

5              a plurality of conductive vias, wherein a first circuit is within a

6 perimeter defined by the conductive vias and a second circuit is disposed

7 outside of the perimeter, whereby the conductive vias provide electromagnetic

8 shielding.

1        11. The integrated circuit of claim 10, wherein the flip chip package is

2 a ball grid array substrate having a ground plane extending at least over an area

3 within the perimeter.

1        12. The integrated circuit of claim 10, wherein the metal layers include

2 an inductor.

1        13. The integrated circuit of claim 12, wherein the semiconductor

2 substrate includes a transistor.

1        14. The integrated circuit of claim 13, wherein the first circuit includes

2 an oscillator.

1        15. The integrated circuit of claim 13, wherein the oscillator operates in

2 a wide frequency range.

WO 02/067326

PCT/US02/04193

1        16. A method of providing a Faraday cage for an integrated circuit die

2 contained in a package, the method comprising:

3                providing conductive vias about a periphery of a circuit in the

4 integrated circuit die; and

5                mounting the integrated circuit die on a package substrate, the

6 conductive vias being electrically coupled to a conductive plane of the package

7 substrate.

1        17. The method of claim 16, wherein the conductive plane is a ground

2 plane.

1        18. The method of claim 16, wherein the integrated circuit die includes

2 metal layers of the substrate, the vias being disposed through the metal layers.

1        19. The method of claim 18, wherein the circuit is coupled to at least

2 one other circuit on the circuit die, the at least one other circuit being located

3 outside the periphery.

1        20. The method of claim 16, wherein the circuit includes an oscillator.

Figure 1

Figure 2

WO 02/067326

PCT/US02/04193

3/7

FIGURE 3

WO 02/067326

PCT/US02/04193

4/7

FIGURE 4

FIGURE 7

FIGURE 5

FIGURE 6

WO 02/067326

PCT/US02/04193

6/7

FIGURE 8

WO 02/067326

7/7

PCT/US02/04193

Figure 9

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

29 August 2002 (29.08.2002)

PCT

(10) International Publication Number

WO 02/067326 A3(51) International Patent Classification<sup>5</sup>: H01L 23/552, 23/522, 23/498

(81) Designated States (national): AI, AG, AI, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI, GM, IIR, IH, ID, IL, IN, IS, JR, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PI, PT, RO, RU, SD, SE, SG, SI, SK, SL, TI, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(21) International Application Number: PCT/US02/04193

(22) International Filing Date: 13 February 2002 (13.02.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 09/785,620 16 February 2001 (16.02.2001) US

(71) Applicant: ASHVATTHA SEMICONDUCTOR, INC.

[US/US], 9591 Waples Street, San Diego, CA 92121 (US).

(72) Inventors: SRIDHARAN, Guruswami, M.; 2135 N. Walnut Creek Ct., Jacksonville, FL 32246 (US). SRIDHARAN, Karthik, M.; 2135 N. Walnut Creek Ct., Jacksonville, FL 32246 (US).

(74) Agent: ZIEBERT, JOSEPH, N.; Foley &amp; Lardner, 777 E. Wisconsin Avenue, 33rd Floor, Milwaukee, WI 53202-5367 (US).

(54) Title: INTEGRATED CIRCUIT DIE HAVING AN ELECTROMAGNETIC INTERFERENCE SHIELD

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AL, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SI, TR), OAPI patent (BR, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report

(88) Date of publication of the international search report:

18 December 2003

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

WO 02/067326 A3

**WO (57) Abstract:** A package for housing a device (e.g., an integrated circuit chip or die) includes a Faraday cage. The Faraday cage is at least partially formed in the integrated circuit die. The die includes conductive vias and solder balls surrounding a circuit. The package can be a ball grid array (BGA) package or flip chip package. The package substrate can include a ground plane.

**【手続補正書】**

【提出日】平成15年10月7日(2003.10.7)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

集積回路パッケージ(90)であって、集積回路およびパッケージ基板(100)を備え、前記集積回路が第1回路(22)と少なくとも1つの第2回路とを含み、前記第1回路が、複数の導電性ビア(62)によって、側面を包囲されており、前記パッケージ基板が導電面(112)を有し、これによって、前記導電性ビアおよび接地面が、前記第1回路からの電磁干渉から前記第2回路を保護し、前記集積回路が複数の導電層(70)を含み、前記導電性ビアが前記導電層全てを貫通し、前記集積回路(20)が、更に、前記導電層の上部に半導体基板(68)を含み、前記半導体基板(68)が上端面上にあり、前記導電層が下端面上にあり、該下端面が前記パッケージ基板に隣接する、集積回路パッケージ。

**【請求項2】**

請求項1記載の集積回路パッケージであって、更に、前記導電性ビアが、前記接地面に電気的に結合されていることを特徴とする、集積回路パッケージ。

**【請求項3】**

請求項1または2記載の集積回路パッケージであって、更に、前記導電性ビアが、はんだボールによって、前記接地面に結合されていることを特徴とする、集積回路パッケージ。

**【請求項4】**

請求項1記載の集積回路パッケージであって、更に、前記パッケージ基板が、ボール・グリッド・アレイ基板であることを特徴とする、集積回路パッケージ。

**【請求項5】**

請求項1、2または4記載の集積回路パッケージであって、更に、前記集積回路上部にある導電性カバー(132)を特徴とする、集積回路パッケージ。

**【請求項6】**

請求項5記載の集積回路パッケージであって、更に、前記フリップ・チップ・パッケージが、前記外周内部の少なくともあるエリアに及ぶ接地面を有するボール・グリッド・アレイ基板であることを特徴とする、集積回路パッケージ。

**【請求項7】**

請求項1、2または4記載の集積回路パッケージにおいて、前記第1回路が、前記金属層の1つに配されたインダクタを含み、前記1つの金属層が、前記半導体基板から最も離れている金属層である、集積回路パッケージ。

**【請求項8】**

パッケージ(90)内に内蔵した集積回路ダイにファラディ・ケージを設ける方法であって、該方法は、前記集積回路ダイ内において回路(22)の外周の周囲に導電性ビア(70)を設けることを含み、

前記集積回路ダイをパッケージ基板(100)上に実装し、前記導電性ビアを前記パッケージ基板の導電面(112)に電気的に結合し、前記集積回路ダイが、半導体基板(68)の上部に導電層を含み、前記ビアが前記導電層を貫通して配置され、前記導電層が前記半導体基板よりも前記パッケージ基板に近いこと、を特徴とする方法。

**【請求項9】**

請求項8記載の方法であって、更に、前記導電面が接地面であることを特徴とする、方法。

**【請求項10】**

請求項 8 または 9 記載の方法において、前記金属層が、最外側の導電層および前記外周内にインダクタを含む、方法。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                           |                                                                                                                                                                                                                 | International Application No<br>PCT/US 02/04193                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H01L23/552 H01L23/522 H01L23/498                                                                                                         |                                                                                                                                                                                                                 |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                     |                                                                                                                                                                                                                 |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                         |                                                                                                                                                                                                                 |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                         |                                                                                                                                                                                                                 |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                            |                                                                                                                                                                                                                 |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                |                                                                                                                                                                                                                 |                                                                                |

| Category *                                                                                                                                                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                              | Relevant to claim No.                                                          |

| X                                                                                                                                                                                     | US 6 130 483 A (KONNO MITSUO ET AL)<br>10 October 2000 (2000-10-10)<br>column 8, line 1 - line 25                                                                                                               | 16,17                                                                          |

| Y                                                                                                                                                                                     | column 17, line 11 - line 37<br>column 18, line 25 - line 37<br>figures 1B,23A<br>---                                                                                                                           | 1-15,<br>18-20                                                                 |

| Y                                                                                                                                                                                     | WO 97 35344 A (ERICSSON TELEFON AB L M<br>;JARSTAD TOMAS (SE); NORSTROEM HANS (SE))<br>25 September 1997 (1997-09-25)<br>column 4, line 27 -column 5, line 12<br>column 7, line 10 - line 17<br>figure 2<br>--- | 1-15,<br>18-20<br>-/-                                                          |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                        |                                                                                                                                                                                                                 | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :                                                                                                                                             |                                                                                                                                                                                                                 |                                                                                |

| 'A' document defining the general state of the art which is not considered to be of particular relevance                                                                              |                                                                                                                                                                                                                 |                                                                                |

| 'E' earlier document but published on or after the international filing date                                                                                                          |                                                                                                                                                                                                                 |                                                                                |

| 'L' document which may throw doubt on priority, claim(s) or publication date of another citation or other special reason (as specified)                                               |                                                                                                                                                                                                                 |                                                                                |

| 'O' document referring to an oral disclosure, use, exhibition or other means                                                                                                          |                                                                                                                                                                                                                 |                                                                                |

| 'P' document published prior to the international filing date but later than the priority date claimed                                                                                |                                                                                                                                                                                                                 |                                                                                |

| Date of the actual completion of the international search                                                                                                                             | Date of mailing of the international search report                                                                                                                                                              |                                                                                |

| 28 May 2003                                                                                                                                                                           | 05/06/2003                                                                                                                                                                                                      |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.O. 5816 Patentlaan 2<br>NL - 2290 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Ahlstedt, M                                                                                                                                                                           |                                                                                |

Form PCTISA/210 (second sheet) (July 1992)

| INTERNATIONAL SEARCH REPORT                         |                                                                                                                                                                       | International Application No<br>PCT/US 02/04193 |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                       |                                                 |

| Category *                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                                    | Relevant to claim No.                           |

| A                                                   | US 5 256 590 A (INOUE AKIRA)<br>26 October 1993 (1993-10-26)<br>page 1, line 8 - line 14<br>page 2, line 13 - line 24<br>page 6, line 24 - line 29; figure 5<br>----- | 1-20                                            |

Form PCT/SA/210 (continuation of second sheet) (July 1992)

page 2 of 2

| INTERNATIONAL SEARCH REPORT<br>Information on patent family members |                  |                         |  | International Application No<br>PCT/US 02/04193 |  |

|---------------------------------------------------------------------|------------------|-------------------------|--|-------------------------------------------------|--|

| Patent document cited in search report                              | Publication date | Patent family member(s) |  | Publication date                                |  |

| US 6130483                                                          | A 10-10-2000     | JP 10308478 A           |  | 17-11-1998                                      |  |

| -----                                                               |                  |                         |  |                                                 |  |

| WO 9735344                                                          | A 25-09-1997     | AU 2187397 A            |  | 10-10-1997                                      |  |

|                                                                     |                  | CA 2248141 A1           |  | 25-09-1997                                      |  |

|                                                                     |                  | CN 1218576 A            |  | 02-06-1999                                      |  |

|                                                                     |                  | EP 0888636 A1           |  | 07-01-1999                                      |  |

|                                                                     |                  | JP 2000507045 T         |  | 06-06-2000                                      |  |

|                                                                     |                  | SE 9601119 A            |  | 23-09-1997                                      |  |

|                                                                     |                  | WO 9735344 A1           |  | 25-09-1997                                      |  |

|                                                                     |                  | US 6472723 B1           |  | 29-10-2002                                      |  |

| -----                                                               |                  |                         |  |                                                 |  |

| US 5256590                                                          | A 26-10-1993     | JP 3165058 A            |  | 17-07-1991                                      |  |

|                                                                     |                  | GB 2238911 A ,B         |  | 12-06-1991                                      |  |

|                                                                     |                  | US 5151770 A            |  | 29-09-1992                                      |  |

| -----                                                               |                  |                         |  |                                                 |  |

Form PCT/ISA/210 (patent family annex) (July 1992)

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,P,L,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100120112

弁理士 中西 基晴

(72)発明者 スリドハラン , グルスワミ・エム

アメリカ合衆国フロリダ州32246 , ジャクソンビル , ノース・ウォルナット・クリーク・コート 2135

(72)発明者 スリドハラン , カーティク・エム

アメリカ合衆国フロリダ州32246 , ジャクソンビル , ノース・ウォルナット・クリーク・コート 2135