(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5978382号

(P5978382)

(45) 発行日 平成28年8月24日(2016.8.24)

(24) 登録日 平成28年7月29日(2016.7.29)

(51) Int.Cl.

HO3M 13/15 (2006.01)

F 1

HO3M 13/15

請求項の数 20 (全 24 頁)

(21) 出願番号 特願2015-503189 (P2015-503189)

(86) (22) 出願日 平成24年11月26日 (2012.11.26)

(65) 公表番号 特表2015-512585 (P2015-512585A)

(43) 公表日 平成27年4月27日 (2015.4.27)

(86) 國際出願番号 PCT/US2012/066554

(87) 國際公開番号 WO2013/147935

(87) 國際公開日 平成25年10月3日 (2013.10.3)

審査請求日 平成27年10月28日 (2015.10.28)

(31) 優先権主張番号 13/430,222

(32) 優先日 平成24年3月26日 (2012.3.26)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591025439

ザイリンクス インコーポレイテッド

X I L I N X I N C O R P O R A T E D

アメリカ合衆国 カリフォルニア州 95

124-3400 サンホセ ロジック

ドライブ 2100

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 クリシュナン, カルヤナ

アメリカ合衆国、95124 カリフォル

ニア州、サン・ノゼ、ロジック・ドライブ

、2100

最終頁に続く

(54) 【発明の名称】非バイナリ線形ブロックコードの並列符号化

## (57) 【特許請求の範囲】

## 【請求項 1】

K桁のメッセージのL桁の部分を、P個のパリティディジットを有するN桁の符号化メッセージに並列符号化するためのエンコーダモジュールであって、

前記K桁のメッセージの前記L桁の部分を受信するように構成された入力と、

前記N桁の符号化メッセージを出力するように構成された出力と、

L桁入力シフトレジスタ回路とを含み、前記L桁入力シフトレジスタの入力が、前記エンコーダモジュールの前記入力に連結され、前記L桁入力シフトレジスタの出力が、マルチプレクサを介して前記エンコーダモジュールの前記出力に連結され、

順次連結されたP/L個のパリティシフトレジスタを含み、前記P/L個のパリティシフトレジスタのうち最後のパリティシフトレジスタの入力が、前記エンコーダモジュールの前記入力に連結され、前記最後のパリティシフトレジスタの出力が、前記マルチプレクサを介して前記エンコーダモジュールの前記出力に連結され、

P/L個のパリティ生成モジュールを備えるフィードバック回路を含み、前記P/L個のパリティ生成モジュールの各々が、スイッチによって前記最後のパリティシフトレジスタの前記出力に連結され、さらに前記P/L個のパリティシフトレジスタのうち対応する1つのパリティシフトレジスタの入力に連結され、

前記P/L個のパリティ生成モジュールの各々は、前記スイッチが閉合されているときに、前記P/L個のパリティシフトレジスタのうち1つに対応するパリティシフトレジスタに格納されるべきL個のパリティディジットを生成するように構成され、

10

20

$L, K, N$  および  $P$  は正の整数であり、 $L$  は 1 よりも大きく、 $P$  は  $L$  の倍数である、エンコーダモジュール。

#### 【請求項 2】

(  $K / L$  ) 個のクロックサイクルの各々において、

前記フィードバック回路の前記スイッチは、閉合され、

前記エンコーダモジュールは、入力で受信した前記  $K$  枠のメッセージの前記  $L$  枠の部分のうち 1 つを、前記  $L$  枠入力シフトレジスタと、前記最後のパリティシフトレジスタの前記入力とに転送し、

前記最後のパリティシフトレジスタは、格納されたパリティディジットを、前記フィードバック回路の前記  $P / L$  個のパリティ生成モジュールの各々に転送し、前記  $P / L$  個のパリティ生成モジュールの各々は、前記  $P / L$  個のパリティシフトレジスタのうち 1 つに対応するパリティシフトレジスタに格納されるべき  $L$  個のパリティディジットを生成し、

前記最後のパリティシフトレジスタ以外の前記  $P / L$  個のパリティシフトレジスタの各々は、格納されたパリティディジットを前記  $P / L$  個のパリティシフトレジスタのうち次のパリティシフトレジスタに転送し、

前記  $L$  枠入力シフトレジスタは、格納されたデータを前記エンコーダモジュールの前記出力に転送し、当該データは、前記  $K$  枠のメッセージの前記  $L$  枠の部分のうち 1 つを含み、

(  $K / L$  ) + 1 クロックサイクルにおいて、

前記  $L$  枠入力シフトレジスタは、格納されたデータを前記エンコーダモジュールの前記出力に転送し、当該データは、前記  $K$  枠のメッセージの前記  $L$  枠の部分のうち 1 つを含み、

前記エンコーダモジュールは、入力で受信したゼロ入力を前記  $L$  枠入力シフトレジスタおよび前記最後のパリティシフトレジスタの前記入力に転送することによって、前記フィードバック回路の前記スイッチを開放し、

前記 (  $K / L$  ) + 2 ~ (  $N / L$  ) + 1 個のクロックサイクルの各々において、

前記最後のパリティシフトレジスタは、格納されたパリティディジットを前記エンコーダモジュールの前記出力に転送し、

前記最後のパリティシフトレジスタ以外の前記  $P / L$  個のパリティシフトレジスタの各々は、格納されたパリティディジットを前記  $P / L$  個のパリティシフトレジスタのうち次のパリティシフトレジスタに転送する、請求項 1 に記載のエンコーダモジュール。

#### 【請求項 3】

前記最後のパリティシフトレジスタの前記出力と前記  $L$  枠入力シフトレジスタの出力とは、マルチプレクサを介して前記エンコーダモジュールの前記出力に連結されている、請求項 2 に記載のエンコーダモジュール。

#### 【請求項 4】

前記 (  $K / L$  ) 個のクロックサイクルの各々において前記最後のパリティシフトレジスタの前記入力に転送された前記  $L$  枠の部分は、同一クロックサイクルにおいて前記最後のパリティシフトレジスタに格納された前記パリティディジットと合併される、請求項 2 に記載のエンコーダモジュール。

#### 【請求項 5】

前記 (  $K / L$  ) 個のクロックサイクルの各々において前記  $P / L$  個のパリティ生成モジュールの各々によって生成された前記  $L$  枠のパリティディジットは、同一クロックサイクルにおいて対応するパリティシフトレジスタに格納された前記パリティディジットと合併される、請求項 2 に記載のエンコーダモジュール。

#### 【請求項 6】

前記 (  $K / L$  ) + 1 クロックサイクルにおいて前記  $P / L$  個のパリティシフトレジスタの各々に格納された前記パリティディジットは、最終パリティディジット値である、請求項 2 に記載のエンコーダモジュール。

#### 【請求項 7】

10

20

30

40

50

前記 P 個のパリティディジットは、前記 ( K / L ) + 2 ~ ( N / L ) + 1 個のクロックサイクルにおいて、前記エンコーダモジュールによって出力される、請求項 1 に記載のエンコーダモジュール。

**【請求項 8】**

前記 P 個のパリティディジットは、 L 衍の並列出力として出力される、請求項 7 に記載のエンコーダモジュール。

**【請求項 9】**

前記 P / L 個のパリティシフトレジスタは、前記 P / L 個のパリティシフトレジスタの各々に連結された制御信号によって制御される、請求項 1 に記載のエンコーダモジュール。

10

**【請求項 10】**

前記エンコーダモジュールによって受信された前記 K 衍のメッセージの前記 L 衍の部分は、 ( K / L ) + 1 クロックサイクルにおいて、前記エンコーダモジュールによって出力される、請求項 1 に記載のエンコーダモジュール。

**【請求項 11】**

K 衍のメッセージの L 衍の部分を、 P 個のパリティディジットを有する N 衍の符号化メッセージに並列符号化するためのエンコーダモジュールであって、

前記 K 衍のメッセージの前記 L 衍の部分を受信するように構成された入力と、

前記 N 衍の符号化メッセージを出力するように構成された出力とを含み、前記エンコーダモジュールの前記入力が、前記出力に結合され。

20

P / L 段遅延器を含み、前記 P / L 段遅延器の入力は、前記エンコーダモジュールの前記入力に連結され、前記 P / L 段遅延器の出力は、 マルチプレクサを通じて前記エンコーダモジュールの出力に連結され、

順次連結された P / L 個のパリティシフトレジスタを含み、前記 P / L 個のパリティシフトレジスタのうち最初のパリティシフトレジスタの入力が、前記エンコーダモジュールの前記入力に連結され、前記 P / L 個のパリティシフトレジスタのうち最後のパリティシフトレジスタの出力が、 前記マルチプレクサを通じて前記エンコーダモジュールの前記出力に連結され、前記 P / L 個のパリティシフトレジスタの各々は、 L 個のパリティディジットを格納する容量を有し、

P / L 個のパリティ生成モジュールを備えるフィードバック回路を含み、前記 P / L 個のパリティ生成モジュールの各々が、対応するスイッチによって、前記 P / L 個のパリティシフトレジスタのうち 1 つの対応するパリティシフトレジスタの出力に連結され、さらに、前記最初のパリティシフトレジスタの前記入力に連結され、前記 P / L 個のパリティ生成モジュールの各々は、対応するスイッチが閉合されているときに、前記最初のパリティシフトレジスタの前記入力への転送のための L 個のパリティディジットを生成するよう構成され。

30

L , K , N および P は正の整数であり、 L は 1 よりも大きく、 P は L の倍数であり、

前記エンコーダモジュールの前記入力は、前記 P / L 段遅延器および前記マルチプレクサを通じて前記出力に結合される、エンコーダモジュール。

**【請求項 12】**

( K / L ) 個のクロックサイクルの各々において、

前記フィードバック回路の前記対応するスイッチの各々は、閉合され、

前記エンコーダモジュールは、入力で受信した前記 K 衍のメッセージの前記 L 衍の部分のうち 1 つを、前記最初のパリティシフトレジスタと、前記エンコーダモジュールの前記出力とに転送し、

前記 P / L 個のパリティシフトレジスタの各々は、格納されたパリティディジットを前記 P / L 個のパリティ生成モジュールのうち対応する 1 つのパリティ生成モジュールに転送し、前記対応する 1 つのパリティ生成モジュールは、前記最初のパリティシフトレジスタに転送されるべき前記 L 個のパリティディジットを生成し、

前記最後のパリティシフトレジスタ以外の前記 P / L 個のパリティシフトレジスタの各

40

10

20

30

40

50

々は、さらに、格納されたパリティディジットを前記 P / L 個のパリティシフトレジスタのうち次のパリティシフトレジスタに転送し、

( K / L ) + 1 ~ ( P / L ) 個のクロックサイクルの各々において、

前記エンコーダモジュールは、入力で受信したゼロ入力を、前記最初のパリティシフトレジスタに転送し、

前記フィードバック回路の 1 以上の前記対応するスイッチは、次々と開放され、

前記 P / L 個のパリティシフトレジスタの各々は、格納されたパリティディジットを、前記 P / L 個のパリティ生成モジュールのうち 1 つの対応するパリティ生成モジュールに転送し、

前記 ( ( K / L ) + ( P / L ) ) ~ ( ( N / L ) + ( P / L ) ) 個のクロックサイクル 10 の各々において、

前記最後のパリティシフトレジスタは、格納されたパリティディジットを前記エンコーダモジュールの前記出力に転送し、

前記最後のパリティシフトレジスタ以外の前記 P / L 個のパリティシフトレジスタの各々は、格納されたパリティディジットを前記 P / L 個のパリティシフトレジスタのうち次のパリティシフトレジスタに転送する、請求項 11 に記載のエンコーダモジュール。

#### 【請求項 13】

前記最後のパリティシフトレジスタの前記出力と前記エンコーダモジュールの前記入力とは、マルチプレクサを介して前記エンコーダモジュールの前記出力に連結されている、請求項 12 に記載のエンコーダモジュール。 20

#### 【請求項 14】

前記 ( K / L ) 個のクロックサイクルの各々において前記最初のパリティシフトレジスタの前記入力に転送された前記 L 衍の部分のうちの 1 つは、同一クロックサイクルにおいて前記最初のパリティシフトレジスタに格納された前記パリティディジットと合併される、請求項 12 に記載のエンコーダモジュール。

#### 【請求項 15】

前記 ( K / L ) 個のクロックサイクルの各々において前記 P / L 個のパリティ生成モジュールの各々によって生成された前記 L 個のパリティディジットは、前記最初のパリティシフトレジスタに格納された前記パリティディジットと合併される、請求項 12 に記載のエンコーダモジュール。 30

#### 【請求項 16】

前記エンコーダモジュールによって受信された前記 K 衍のメッセージの前記 L 衍の部分は、( K / L ) 個のクロックサイクルにおいて、前記エンコーダモジュールによって出力される、請求項 11 に記載のエンコーダモジュール。

#### 【請求項 17】

前記 P 個のパリティディジットは、前記 ( K / L ) + 1 ~ ( P / L ) 個のクロックサイクルにおいて、前記エンコーダモジュールによって出力される、請求項 11 に記載のエンコーダモジュール。

#### 【請求項 18】

前記 P 個のパリティディジットは、L 衍の並列出力として出力される、請求項 17 に記載のエンコーダモジュール。 40

#### 【請求項 19】

前記 P / L 個のパリティシフトレジスタは、前記 P / L 個のパリティシフトレジスタの各々に連結された制御信号によって制御される、請求項 11 に記載のエンコーダモジュール。

#### 【請求項 20】

前記最初のパリティシフトレジスタの前記入力に関連付けられた加算器モジュールをさらに含む、請求項 11 に記載のエンコーダモジュール。

#### 【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【0001】**

著作権のある資料の権利保留

開示された本特許文書の一部は、著作権保護の対象となる資料を含んでいる。著作権所有者は、特許商標庁の特許ファイルまたは記録に記載される特許文書または特許開示のファクシミリ複製に異議ないが、それ以外の全ての著作権を保留する。

**【0002】**

出願の分野

本願は、一般に、非バイナリ線形ブロックコードの符号化に関し、特に、非バイナリ線形ブロックコードの並列符号化を実施するためのシステムおよび方法に関する。

**【背景技術】**

10

**【0003】**

背景

線形前方誤り訂正（FEC）コードは、データの整合性および正確性が保護されなければならない通信および大容量記憶システムにおいて、広く応用されている。線形ブロック FEC は、データディジットのうち 1 つのブロックを取得し、冗長ディジットを追加することによってこのデータブロックを保護する。典型的には、エンコーダは、これらの冗長ディジットを計算するが、デコーダーは、冗長ディジットを用いて受信したデータブロックの正確性を判断し、可能な場合、冗長ディジットを用いてデータの誤ったブロックを訂正する。

**【0004】**

20

線形ブロックコードは、 $k$  桁のメッセージディジットがエンコーダモジュールによって  $n$  桁のディジットに符号化されたコードであり、 $(n, k)$  によって表記される。このように、エンコーダによって、 $n - k$  桁の冗長ディジットが  $k$  桁のメッセージディジット（たとえば、データブロック）に追加される。 $n - k$  桁の冗長ディジットは、パリティディジットとも呼ばれている。系統的符号化が実行される場合、 $n$  桁の符号化ディジットは、単に  $k$  桁のメッセージディジット（たとえば、データブロック）の後方に  $n - k$  桁パリティディジットが追加されたものである。

**【0005】**

パリティディジットは、ガロア域（GF）において定義された生成多項式  $g(x)$  に基づき計算される。線形ブロックコードに対し、生成多項式  $g(x)$  は、二次ガロア域（GF(2)）において定義される。非バイナリ線形ブロックコードに対し、生成多項式  $g(x)$  は、 $q^m$  次のガロア域（GF( $q^m$ )）において定義される。 $q$  は、素数である。リード・ソロモン（Reed Solomon (RS)）エンコーダは、非バイナリ線形ブロックコードの分類に該当する。

30

**【0006】**

10ギガビット毎秒のエンコーダに対し、達成可能な最大線形速度は、10.09ギガビット/秒である。1回に单一の入力を処理するシリアル入力を用いてこのような線形速度を達成する場合、1.109GHz (= 11.09 / m) で動作するクロッキングが必要とする。パリティディジットを計算する際に複雑なロジックが関与されるため、シリアル入力を用いてこのような高線形速度を維持することは、非常に困難である。

40

**【発明の概要】****【課題を解決するための手段】****【0007】**

概要

いくつかの実施形態によれば、 $K$  桁のメッセージの  $L$  桁の部分を、 $P$  個のパリティディジットを有する  $N$  桁の符号化メッセージに並列符号化するためのエンコーダモジュールは、 $K$  桁のメッセージの  $L$  桁の部分を受信するように構成された入力と、 $N$  桁の符号化メッセージを出力するように構成された出力と含み、エンコーダモジュールの入力は、その出力に連結される。また、エンコーダモジュールは、順次連結された  $P / L$  個のパリティシフトレジスタを含み、パリティシフトレジスタのうち最初のパリティシフトレジスタの入

50

力が、エンコーダモジュールの入力に連結され、最後のパリティシフトレジスタの出力が、エンコーダモジュールの出力に連結され、パリティシフトレジスタの各々が、 $L$ 個のパリティディジットを格納するように構成される。さらに、エンコーダモジュールは、 $P / L$ 個のパリティ生成モジュールを備えるフィードバック回路を含み、パリティ生成モジュールの各々は、スイッチによって、パリティシフトレジスタのうち対応する1つのパリティシフトレジスタの入力に連結されかつ最初のパリティシフトレジスタの出力に連結され、パリティ生成モジュールの各々は、対応するスイッチが閉合されているときに、最初のパリティシフトレジスタの入力に転送される $L$ 個のパリティディジットを生成するように構成される。

## 【0008】

10

他の実施形態によれば、 $K$ 桁のメッセージの $L$ 桁の部分を、 $P$ 個のパリティディジットを有する $N$ 桁の符号化メッセージに並列符号化するためのエンコーダモジュールは、 $K$ 桁のメッセージの $L$ 桁の部分を受信するように構成された入力と、 $N$ 桁の符号化メッセージを出力するように構成された出力と含み、エンコーダモジュールの入力は、その出力に連結される。また、エンコーダモジュールは、入力および出力に連結された $P / L$ 段の遅延器と、順次連結された $P / L$ 個のパリティシフトレジスタとを含み、パリティシフトレジスタのうち最初のパリティシフトレジスタの入力が、エンコーダモジュールの入力に連結され、パリティシフトレジスタのうち最後のパリティシフトレジスタの出力が、エンコーダモジュールの出力に連結され、パリティシフトレジスタの各々が、 $L$ 個のパリティディジットを格納するように構成される。さらに、エンコーダモジュールは、 $P / L$ 個のパリティ生成モジュールを備えるフィードバック回路を含み、パリティ生成モジュールの各々は、スイッチによって、パリティシフトレジスタのうち対応する1つのパリティシフトレジスタの入力に連結されかつ最初のパリティシフトレジスタの出力に連結され、パリティ生成モジュールの各々は、対応するスイッチが閉合されているときに、最初のパリティシフトレジスタの入力に転送される $L$ 個のパリティディジットを生成するように構成される。

## 【0009】

20

他の局面および特徴ならびにさらなる局面および特徴は、以下の実施形態の詳細な説明を読めば明白になるであろう。

## 【0010】

30

図面は、実施形態の設計および効用を示している。図面において、同様の要素が共通の参照番号を付して参照される。これらの図面は、必ずしも一定の縮尺で描かれていない。上記のおよび他の利点および目的の達成をより明白に理解するために、添付の図面に例示されている実施形態のより具体的な説明を提供する。これらの図面は、代表的な実施形態のみを示すものであり、特許請求の範囲を限定するものとみなされるべきではない。

## 【図面の簡単な説明】

## 【0011】

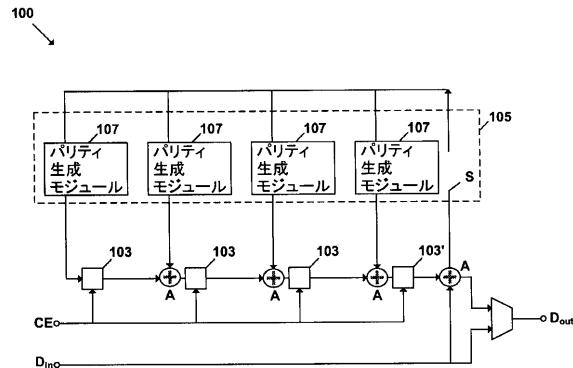

【図1】非バイナリ線形ブロックコードを直列符号化するための直列エンコーダモジュールを示す図である。

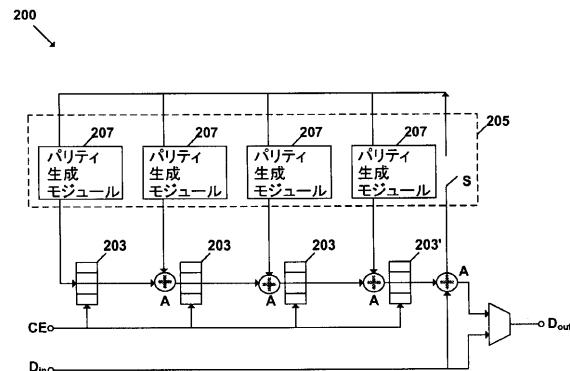

【図2】非バイナリ線形ブロックコードの並列符号化を実行するためのエンコーダモジュールを示す図である。

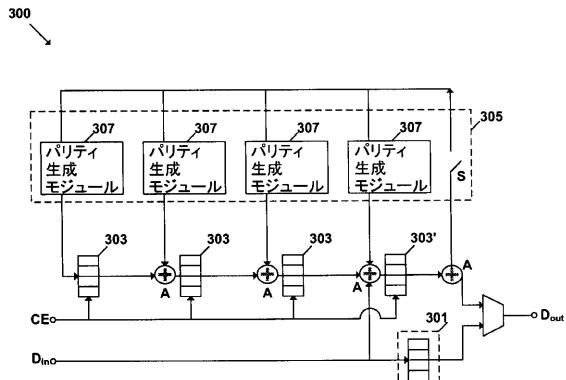

【図3】いくつかの実施形態に従った、非バイナリ線形ブロックコードの並列符号化を実行するためのエンコーダモジュールを示す図である。

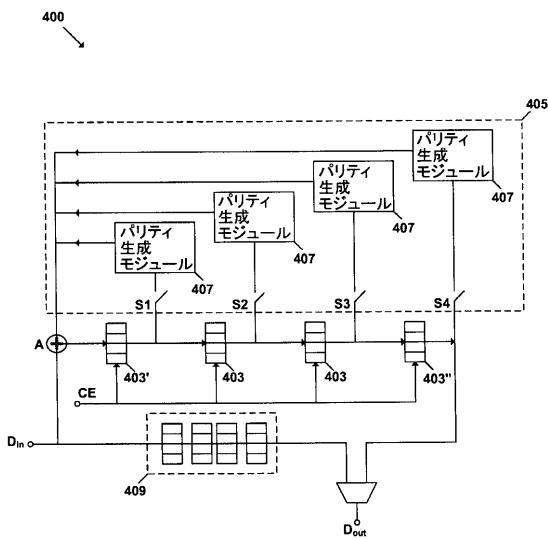

【図4】いくつかの実施形態に従った、減少されたファンアウトを有する非線形ブロックコードの並列符号化を実行するためのエンコーダモジュールを示す図である。

## 【発明を実施するための形態】

## 【0012】

## 詳細な説明

以下、図面を参照してさまざまな実施形態を説明する。注意すべきことは、図面が縮尺通りに描かれておらず、類似構造の要素または機能が図面の全体において同様の参照番号

40

50

によって示されることである。なお、図面は、実施形態の説明を容易にすることを意図していることに注意すべきである。図面は、本発明の網羅的な説明または本発明の特許請求の範囲に対する限定を意図するものではない。また、図示された実施形態は、示された局面または利点をすべて備える必要がない。特定の実施形態に関連して説明した局面または利点は、必ずしもその実施形態に限定されるものではなく、図示されていなくとも、任意の他の実施形態に実施することができる。また、本明細書において、「いくつかの実施形態」または「他の実施形態」を言及する場合、実施形態に関連して説明された特定の特徴、構造、材料または特性が少なくとも 1 つの実施形態に含まれることを意味する。したがって、本明細書において、さまざまな箇所に現れる「いくつかの実施形態において」または「他の実施形態において」などの表現は、必ずしも同じ実施形態を指すではない。

10

## 【0013】

線形ブロックコードは、 $k$  桁のメッセージディジットがエンコーダモジュールによって  $n$  桁のディジットに符号化されたコードであり、 $(n, k)$  によって表記される。このように、エンコーダによって、 $n - k$  桁の冗長ディジットが  $k$  桁のメッセージディジット（たとえば、データブロック）に追加される。 $n - k$  桁の冗長ディジットは、パリティディジットとも呼ばれている。系統的符号化が実行される場合、 $n$  桁の符号化ディジットは、単に  $k$  桁のメッセージディジット（たとえば、データブロック）の後方に  $n - k$  桁パリティディジットが追加されたものである。パリティディジットは、ガロア域 ( $G F$ ) において定義された生成多項式  $g(x)$  に基づき計算される。線形ブロックコードについて、生成多項式  $g(x)$  は、二次ガロア域 ( $G F(2^m)$ ) において定義される。非バイナリ線形ブロックコードについて、生成多項式  $g(x)$  は、 $q^m$  次のガロア域 ( $G F(q^m)$ ) において定義される。 $q$  は、素数である。

20

## 【0014】

例示のために、以下は、 $2^{10}$  次のガロア域 ( $G F(2^{10})$ ) において定義された生成多項式に関連して説明する。しかしながら、重要なのは、非線形ブロックコードを並列符号化するための方法およびシステムは、任意次数のガロア域において定義された生成多項式を包含するように拡張されてもよいということに留意すべきである。

## 【0015】

符号化される  $K$  桁のメッセージは、次のメッセージ多項式で表される。 $m_{N-K}$  は、 $2^m$  次のガロア域における桁数に対応する。

30

## 【0016】

## 【数1】

$$m(x) = \sum_{i=1}^K m_{i-1} x^{K-i} \quad (1)$$

## 【0017】

$N$  は、符号化されたメッセージの長さを表し、 $P$  は、パリティディジットの長さ ( $P = N - K$ ) を表す。生成多項式は、 $2^m$  次のガロア域において定義された  $g(x)$  で表される。

## 【0018】

40

$n$  桁の符号化メッセージは、以下の多項式で表される。式中、 $p(x)$  の係数は、パリティディジットであり、 $c(x)$  の係数は、最終に符号化されたディジットである。

## 【0019】

## 【数2】

$$p(x) = (x^P m(x))_{g(x)} \quad (2)$$

$$c(x) = x^P m(x) + p(x) \quad (3)$$

## 【0020】

$(\ )_{g(x)}$  は、多項式  $g(x)$  に対するモジュロ演算を示す。

50

$p(x)$  の計算は、以下のように展開することができる。

【0 0 2 1】

【数3】

$$p(x) = \left( x^P \sum_{i=1}^K m_{i-1} x^{K-i} \right)_{g(x)} = \left( \sum_{i=1}^K x^P m_{i-1} x^{K-i} \right)_{g(x)}$$

(4)

$$= \left( x^{K-1} x^P m_0 \right)_{g(x)} + \left( x^{K-2} x^P m_1 \right)_{g(x)} + \left( x^{K-3} x^P m_2 \right)_{g(x)} + \left( x^{K-4} x^P m_3 \right)_{g(x)} + \dots$$

10

【0 0 2 2】

$[a(x)b(x)]_{g(x)} = ([a(x)]_{g(x)}[b(x)]_{g(x)})_{g(x)}$  のため、式(4)を以下のような再帰式に書き換えることができる。

【0 0 2 3】

【数4】

$$\begin{aligned} p(x) &= \\ &\left( x^{K-2} \left( x[x^P m_0]_{g(x)} + x^P m_1 \right)_{g(x)} \right)_{g(x)} + \left( x^{K-3} x^P m_2 \right)_{g(x)} + \left( x^{K-4} x^P m_3 \right)_{g(x)} + \dots \quad (5) \\ &= \left( x^{K-3} \left[ x \left( x[x^P m_0]_{g(x)} + x^P m_1 \right)_{g(x)} + x^P m_2 \right]_{g(x)} \right)_{g(x)} + \left( x^{K-4} x^P m_3 \right)_{g(x)} + \dots \end{aligned}$$

20

【0 0 2 4】

以下の擬似コードで示されるように、上記の再帰式を実行することができる。

【0 0 2 5】

【数5】

for i= 1:K

30

parityv= parityt; % parity は、パリティ係数を含む配列に対応する

feedback= (m(i)+parityt(n-k)) \* g(x); % m(i)は、入力されたメッセージのディジットである

parityt(1)= feedback(1);

parityt(2:n-k)= feedback(2:n-k)+parityv(1:n-k-1);

end;

40

【0 0 2 6】

説明したアルゴリズムは、図1に示された直列エンコーダモジュールを用いて実行することができる。図1は、非バイナリ線形ブロックコードを直列符号化するための直列エンコーダモジュール100を示す。直列エンコーダモジュール100は、K桁のメッセージのために、任意P個のパリティディジットを生成するように構成することができる。例示のために、図1の直列エンコーダモジュール100は、K桁のメッセージのために、4個のパリティディジットを生成するように構成されている。

【0 0 2 7】

直列エンコーダモジュール100は、入力D<sub>in</sub>と、出力D<sub>out</sub>と、4つの1桁パリティシフトレジスタ103 / 103と、4つのパリティ生成モジュール107を備える

50

フィードバック回路 105 とを含む。図 1 の直列エンコーダモジュール 100 は、4 つのパリティ生成モジュール（たとえば、ガロア域乗算器）107 および 4 つのパリティシフトレジスタ 103 / 103 のみを含むが、直列エンコーダモジュールとしては、任意 P 個のパリティシフトレジスタと、生成される P 個のパリティディジットに対応する任意 P 個のパリティ生成モジュールとを含んでもよい。

#### 【0028】

エンコーダモジュール 100 の入力  $D_{in}$  は、K 桁のメッセージをシリアル入力として受信するように構成される。直列エンコーダモジュール 100 の出力  $D_{out}$  は、P 個のパリティディジットを有する N 桁の符号化メッセージを出力するように構成される。以下で詳細に説明するように、フィードバック回路 105 のパリティ生成モジュール 107 は、パリティシフトレジスタ 103 / 103 に格納されるパリティディジットを生成するように構成される。10

#### 【0029】

4 つのパリティシフトレジスタ 103 / 103 は、1 つのパリティシフトレジスタ 103 / 103 の出力が（次のパリティシフトレジスタが存在する場合に）次のパリティシフトレジスタ 103 / 103 の入力に連結されるように、順次連結されている。各パリティシフトレジスタ 103 / 103 は、各パリティ生成モジュール 107 に対応しており、各パリティ生成モジュール 107 は、対応するパリティシフトレジスタ 103 / 103 の入力に連結される。加算器モジュール A が、複数のソース（たとえば、1 つのパリティ生成モジュールおよび先行するパリティシフトレジスタ）に連結された各パリティシフトレジスタ 103 / 103 に関連されてもよい。加算器モジュール A は、パリティシフトレジスタ 103 / 103 の入力で受信したデータを格納するために、データの合併を容易にする。20 4 つのパリティシフトレジスタ 103 / 103 の出力は、エンコーダモジュール 100 の入力  $D_{in}$  に連結されかつフィードバック回路 105 の各パリティ生成モジュール 107 の出力に連結される。最後のパリティシフトレジスタ 103 の出力はさらに、マルチプレクサを介してエンコーダモジュール 100 の出力  $D_{out}$  に連結される。追加的な加算器モジュール A は、最後のパリティシフトレジスタ 103 の出力に関連されてもよい。この追加の加算器モジュール A は、最後のパリティシフトレジスタ 103 の出力で受信したデータをフィードバック回路 105 のパリティ生成モジュール 107 に送信するために、データの合併を容易にする。30 同様に、エンコーダモジュール 100 の入力  $D_{in}$  は、マルチプレクサを介してエンコーダモジュール 100 の出力  $D_{out}$  に連結される。

#### 【0030】

フィードバック回路 105 は、スイッチ S をさらに含む。スイッチ S が閉合されると、フィードバック回路 105 が作動され、パリティ生成モジュール 107 が能動的にパリティディジットを生成する。スイッチ S が開放されると、フィードバック回路 105 の動作が停止され、パリティ生成モジュール 107 がパリティディジットを生成しなくなる。

#### 【0031】

最初の K 個（たとえば、メッセージディジットの数）クロックサイクルにおいて、フィードバック回路 105 のスイッチ S は、閉合されている。最初の K 個クロックサイクルの各クロックサイクルにおいて、K 桁のメッセージのディジットは、エンコーダモジュール 100 の入力  $D_{in}$  で直列入力として受信され、最後のパリティシフトレジスタ 103 の出力に転送され、その後フィードバック回路 105 の各パリティ生成モジュール 107 に転送される。フィードバック回路 105 の各パリティ生成モジュール 107 は、対応するパリティシフトレジスタ 103, 103 に格納される単一のパリティディジットを生成するように構成されている。各パリティ生成モジュール 107 は、再帰式（5）および上記の擬似コードに従って、K 桁のメッセージの各ディジットのために、パリティディジットを生成するように構成されている。各クロックサイクルにおいて、各パリティ生成モジュール 107 によって生成されたパリティディジットは、各対応するパリティシフトレジスタ 103 / 103 に格納されているデータと合併され、パリティディジットの最新4050

セットを形成する。

**【0032】**

また、最初のK個クロックサイクルの各クロックサイクルにおいて、各パリティシフトレジスタ103, 103は、(次のパリティシフトレジスタが存在する場合に)次のパリティシフトレジスタに格納されたデータを送信する。最後のパリティシフトレジスタ103は、格納されたデータをフィードバック回路105の各パリティ生成モジュール107に送信する。各クロックサイクルにおいて、K桁のメッセージの新たなディジットが受信されると、パリティシフトレジスタ103/103に格納される新たなパリティデイジットがパリティ生成モジュール107により生成されるので、パリティシフトレジスタ103/103に格納されたパリティデイジットが更新される。上述したように、各クロックサイクルにおいて、新たに生成されたパリティデイジットは、対応するパリティシフトレジスタ103/103に格納されているデータと合併され、パリティデイジットの最新セットを形成する。

10

**【0033】**

同時に、最初のK個クロックサイクルにおいて、エンコーダモジュール100の入力D<sub>i n</sub>で受信したK桁のメッセージの各ディジットは、マルチプレクサを介してエンコーダモジュール100の出力D<sub>o u t</sub>に転送され、よってエンコーダモジュール100により出力される最初のK個のディジットがK桁のメッセージとなる。

**【0034】**

K+1～N個のクロックサイクルにおいて、フィードバック回路のスイッチSは、開放され、パリティシフトレジスタ103/103に格納されている最終パリティデイジット値が、エンコーダモジュール100の出力D<sub>o u t</sub>に送信される。パリティシフトレジスタ103/103に格納されている最終パリティデイジット値は、各パリティシフトレジスタ103/103に連結された制御信号C Eに応じて出力される。たとえば、K+1クロックサイクルにおいて、最後のパリティシフトレジスタ103に格納されたパリティデイジットは、マルチプレクサを介してエンコーダモジュール100の出力D<sub>o u t</sub>に送信されることができ、残りの各パリティシフトレジスタ103に格納されたパリティデイジットは、各々の加算器モジュールを介して次のパリティシフトレジスタ103に送信されることもできる。この動作は、エンコーダモジュール100がすべてのパリティデイジットを出力するまで、第N個のクロックサイクルまで継続する。このようにして、エンコーダモジュール100は、最初のK個のディジットがK桁のメッセージデイジットでありかつ最後のP個のディジットがパリティデイジットであるN桁の符号化メッセージを出力する。

20

30

**【0035】**

しかしながら、図1のエンコーダモジュールが動作してK桁のメッセージをP個のパリティデイジットを有するN桁の符号化メッセージに符号化するときに、いくつかの欠点がある。エンコーダモジュールが直列動作するので、高線形速度を達成するために、エンコーダモジュールが非常に高い周波数で動作しなければならない。しかしながら、パリティ生成モジュールの構成に関連するロジックが複雑であるため、符号化処理にさまざまなエラーを導入することなくおよび追加のコストなくでは、このような高い周波数を達成することができない。

40

**【0036】**

非バイナリ線形ブロックコードの並列符号化を実行するエンコーダモジュールの1つの提案は、図2に示されている。図1の直列エンコーダモジュール100は、各クロックサイクルにおいて、K桁のメッセージの単一のディジットしか処理できない。これに対し、図2のエンコーダモジュール200は、各クロックサイクルにおいて、複数のディジット(L)を処理することができる。エンコーダモジュール200は、N桁の符号化メッセージを形成するために、K桁のメッセージに対し任意P個のパリティデイジットを生成するように構成されてもよい。そのK桁のメッセージは、L桁の並列入力として受信され、そのN桁の符号化メッセージは、L桁の並列出力として出力される。しかしながら、例示の

50

ため、図2のエンコーダモジュール200は、N桁の符号化メッセージを形成するために、K桁のメッセージに対し16個のパリティディジット(すなわち、P=16)を生成するように構成されている。そのK桁のメッセージは、4桁の並列入力(すなわち、L=4)として受信され、そのN桁の符号化メッセージは、4桁の並列出力として出力される。KがLの整数倍でない場合には、メッセージの全体長さがLの倍数になるように、メッセージの先頭にゼロを挿入する。

#### 【0037】

エンコーダモジュール200は、入力D<sub>i\_n</sub>と、出力D<sub>o\_u\_t</sub>と、4つの4桁パリティシフトレジスタ203/203と、4つのパリティ生成モジュール207を備えるフィードバック回路205とを含む。図2のエンコーダモジュール200は、4つのパリティ生成モジュール207および4つの4桁パリティシフトレジスタ203/203のみを含むが、エンコーダモジュール200は、任意P/L個のL桁パリティシフトレジスタと、生成されるP個のパリティディジットに対応する任意P/L個のパリティ生成モジュールと、受信されるL桁の並列入力とを含んでもよい。10

#### 【0038】

エンコーダモジュール200の入力D<sub>i\_n</sub>は、K桁のメッセージを4桁の並列入力として受信するように構成される。エンコーダモジュール200の出力D<sub>o\_u\_t</sub>は、16個のパリティディジットを有するN桁の符号化メッセージを4桁の並列出力として出力するように構成される。以下で詳細に説明するように、フィードバック回路205のパリティ生成モジュール207は各々、4桁パリティシフトレジスタ203/203に格納される4つのパリティディジットを生成するように構成される。20

#### 【0039】

4つのパリティシフトレジスタ203/203は、1つのパリティシフトレジスタ203/203の出力が(次のパリティシフトレジスタが存在する場合に)次のパリティシフトレジスタ203/203の入力に連結されるように、順次連結されている。各4桁パリティシフトレジスタ203/203は、各パリティ生成モジュール207に対応しており、各パリティ生成モジュール207は、対応するパリティシフトレジスタ203/203の入力に連結される。加算器モジュールAが、複数のソース(たとえば、1つのパリティ生成モジュールおよび先行するパリティシフトレジスタ)に連結された各パリティシフトレジスタ203/203の入力に関連されてもよい。加算器モジュールAは、パリティシフトレジスタ203/203の入力で受信したデータを格納するために、データの合併を容易にする。4つの4桁パリティシフトレジスタ203/203のうち最後のパリティシフトレジスタ203の出力は、エンコーダモジュールの入力D<sub>i\_n</sub>に連結されかつフィードバック回路205の各パリティ生成モジュール207の出力に連結される。最後のパリティシフトレジスタ203の出力は、さらに、マルチプレクサを介してエンコーダモジュール200の出力D<sub>o\_u\_t</sub>に連結される。追加の加算器モジュールAは、最後のパリティシフトレジスタ203の出力に関連されてもよい。追加の加算器モジュールAは、最後のパリティシフトレジスタ203の出力で受信したデータをフィードバック回路205のパリティ生成モジュール207に送信するために、データの合併を容易にする。同様に、エンコーダモジュール200の入力D<sub>i\_n</sub>は、マルチプレクサを介してエンコーダモジュール200の出力D<sub>o\_u\_t</sub>に連結される。3040

#### 【0040】

フィードバック回路205は、スイッチSをさらに含む。スイッチSが閉合されると、フィードバック回路205が作動され、パリティ生成モジュール207が能動的にパリティディジットを生成する。スイッチSが開放されると、フィードバック回路205の動作が停止され、パリティ生成モジュール207がパリティディジットを生成しなくなる。

#### 【0041】

図1の直列エンコーダモジュール100は、それぞれ単一のディジットを格納するパリティシフトレジスタ103/103を含む。これに対して、図2のエンコーダモジュール200は、1回に4つのディジットを格納する4桁パリティシフトレジスタ203/250

03 を含む。同様に、図1のフィードバック回路105のパリティ生成モジュール107は、1回に単一のメッセージディジットを処理する。これに対して、図2のフィードバック回路のパリティ生成モジュールは、1回に4つのメッセージディジットを処理する。

【0042】

非線形ブロックコードの並列符号化をサポートするために、パリティディジットを生成するための再帰式(5)は、L個のディジットの同時処理をサポートするように拡張することができる。修正された再帰式は、以下である。

【0043】

【数6】

$$\begin{aligned}

p(x) &= \left( x^P \sum_{i=1}^K m_{i-1} x^{K-i} \right)_{g(x)} \quad (6) \\

&= \left( x^P \sum_{i=0}^{K-1} \sum_{r=1}^L m_{i+L+r-1} x^{K-i+L-r} \right)_{g(x)} \\

&= \left( \sum_{i=0}^{K-1} x^{K-(i+1)*L} \left[ x^P \sum_{r=1}^L m_{i+L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} \\

&= \left( x^{K-L} \left[ x^P \sum_{r=1}^L m_{r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \quad 20 \\

&\quad \left( x^{K-2L} \left[ x^P \sum_{r=1}^L m_{L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \\

&\quad \left( x^{K-3L} \left[ x^P \sum_{r=1}^L m_{2L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \quad 30 \\

&\quad \left( x^{K-4L} \left[ x^P \sum_{r=1}^L m_{3L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \dots \\

&= \left( x^{K-2L} \left[ x^L \left[ x^P \sum_{r=1}^L m_{r-1} x^{L-r} \right]_{g(x)} \right]_{g(x)} + \right. \\

&\quad x^{Pr=1L} m_{L+r-1} x^{L-r} g(x) g(x) + \\

&\quad \left. \left( x^{K-3L} \left[ x^P \sum_{r=1}^L m_{2L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \right. \quad 40 \\

&\quad \left( x^{K-4L} \left[ x^P \sum_{r=1}^L m_{3L+r-1} x^{L-r} \right]_{g(x)} \right)_{g(x)} + \dots \\

&= \left[ x^{K-3L} \left( x^L \left[ x^L \left[ x^P \sum_{r=1}^L m_{r-1} x^{L-r} \right]_{g(x)} \right]_{g(x)} + x^P \sum_{r=1}^L m_{L+r-1} x^{L-r} \right]_{g(x)} + \right. \\

&\quad x^{Pr=1L} m_{2L+r-1} x^{L-r} g(x) g(x) + x^{K-4L} x^{Pr=1L} m_{3L+r-1} x^{L-r} g(x) g(x) + \dots \quad (7)

\end{aligned}$$

【0045】

これによって、フィードバック回路の各パリティ生成モジュールは、以下の擬似コード

によって定義された  $P \times L$  パリティ行列 (P M A T) を用いて、1回に  $L$  個のパリティディジットを生成することができる。P M A T の各  $L$  行は、1つのパリティ生成モジュールを形成する。

【 0 0 4 6 】

【 数 8 】

%eye (L) の余数を決定する

```

msg = gf(eye(L),m);

residue_mat = [msg zeros(L,P)];

for row_index = 1:L

for col_index = 1:L

residue_mat(row_index,:) = residue_mat(row_index,:)+...

[gf(zeros(1,col_index-1),m)

residue_mat(row_index,col_index)*g(x) ...

gf(zeros(1,L-col_index),m)];

end

end

PMAT = (residue_mat(:,L+1:end)).';

```

10

20

【 0 0 4 7 】

上記の再帰式 (7) は、以下の擬似コードに示されたように実行することができる。

【 0 0 4 8 】

【 数 9 】

msg\_padded = [gf(zeros(1,num\_zeros\_to\_pad),m) msg]; %ゼロパディングは、メッセージ

の長さがブロック長さ  $L$  の倍数であることを保証する

for i = 1 : (k / L)

%パリティを次に入るメッセージと合併する

u(i) = msg\_padded((i-1)\*L + (1:L));

feedback = (PMAT\*( (fliplr(lfsr\_state(P-L+1:P)) +u(i)).'))';

lfsr\_state = [gf(zeros(1,L),m) lfsr\_state(1:P-L)]+...

fliplr(feedback);

end

30

40

【 0 0 4 9 】

最初の  $K / L$  個のクロックサイクルにおいて、フィードバック回路 205 のスイッチ S は、閉合されている。K 枠のメッセージの各 4 枠の部分は、エンコーダモジュール 200 の入力  $D_{i,n}$  で並列入力として受信され、最後のパリティシフトレジスタ 203 の出力に転送され、その後フィードバック回路 205 の各パリティ生成モジュール 207 に転送される。フィードバック回路 205 の各パリティ生成モジュール 207 は、対応する 4 枠パリティシフトレジスタ 203 / 203 に格納される 4 つのパリティディジット（たとえば、 $L$  個のパリティディジット）を生成するように構成されている。各パリティ生成モジュール 207 は、再帰式 (7)、P M A T 行列および上記の擬似コードに従って、K 枠のメッセージの各  $L$  枠の部分に対しパリティディジットを生成するように構成されている

50

。各クロックサイクルにおいて、各パリティ生成モジュール 207 によって生成されたパリティディジットは、各対応するパリティシフトレジスタ 203 / 203 に格納されているデータと合併され、パリティディジットの最新セットを形成する。

#### 【0050】

また、最初の  $K / L$  個のクロックサイクルの各クロックサイクルにおいて、各パリティシフトレジスタ 203, 203 は、格納されたデータを（次のパリティシフトレジスタが存在する場合に）次のパリティシフトレジスタ 203 / 203 に転送する。最後のパリティシフトレジスタ 203 は、格納されたデータをフィードバック回路 205 の各パリティ生成モジュール 207 に送信する。各クロックサイクルにおいて、 $K$  桁のメッセージの新たな  $L$  桁の部分が受信されると、対応するパリティシフトレジスタ 203 / 203 10 に格納される新たなパリティディジットがパリティ生成モジュール 207 に生成されるので、パリティシフトレジスタ 203 / 203 に格納されたパリティディジットが更新される。上述したように、各クロックサイクルにおいて、新たに生成されたパリティディジットは、対応するパリティシフトレジスタ 203 / 203 に格納されているデータと合併され、パリティディジットの最新セットを形成する。

#### 【0051】

同時に、最初の  $K / L$  個のクロックサイクルにおいて、エンコーダモジュール 200 の入力  $D_{in}$  で受信した  $K$  桁のメッセージの各 4 桁の部分は、マルチプレクサを介してエンコーダモジュール 200 の出力  $D_{out}$  に転送されるため、エンコーダモジュール 200 により出力される最初の  $K$  個のディジットは、 $K$  桁のメッセージの 4 桁の並列出力となる 20 。

#### 【0052】

$(K / L) + 1 \sim N / L$  個のクロックサイクルにおいて、フィードバック回路のスイッチ S は、開放され、パリティシフトレジスタ 203 / 203 に格納されている最終パリティディジット値が、エンコーダモジュール 200 の出力  $D_{out}$  に送信される。パリティシフトレジスタ 203 / 203 に格納されている最終パリティディジット値は、各パリティシフトレジスタ 203 / 203 に連結された制御信号 C\_E に応じて出力される。たとえば、 $(K / L) + 1$  クロックサイクルにおいて、最後のパリティシフトレジスタ 203 に格納された 4 つのパリティディジットは、マルチプレクサを介してエンコーダモジュール 200 の出力  $D_{out}$  に送信されることができ、残りの各パリティシフトレジスタ 203 に格納された 4 つのパリティディジットは、各々の加算器モジュールを介して次のパリティシフトレジスタ 203 に送信されることもできる。この動作は、エンコーダモジュール 200 がすべてのパリティディジットを出力するまで、第  $(N / L)$  個のクロックサイクルまで継続する。このようにして、エンコーダモジュール 200 は、最初の  $K$  個のディジットが  $K$  桁のメッセージのディジットでありかつ最後の  $P$  個のディジットがパリティディジットである  $N$  桁の符号化メッセージを出力する。 30

#### 【0053】

P M A T 行列を用いたパリティディジットの生成は、XOR の和として効率よく計算することができる。単一のメッセージディジットがパリティ生成モジュール（たとえば、直列符号化）により処理されかつ GF( $q^m$ ) ガロア域に定義された生成多項式  $g(x)$  がパリティディジットの生成に使用される場合、その行列の乗算は、最大  $m - 1$  個の XOR が必要とする。 $L$  個のメッセージディジットがパリティ生成モジュールにより同時に処理されかつ GF( $q^m$ ) ガロア域に定義された生成多項式  $g(x)$  がパリティディジットの生成に使用される場合、その行列の乗算は、最大  $mL - 1$  個の XOR が必要とする。 40

#### 【0054】

しかしながら、図 2 のエンコーダモジュール 200 にとって、各パリティ生成モジュール 207 が最後のパリティシフトレジスタ 203 に連結された加算器モジュールを介してエンコーダモジュール 200 の入力  $D_{in}$  および最後のパリティシフトレジスタ 203 の出力に連結されているため、フィードバック回路 205 の各パリティ生成モジュール 207 は、受信した  $K$  桁のメッセージの 4 桁の部分に対し行列乗算を実行するだけでは 50

なく、さらに最後のパリティシフトレジスタ 203 の出力に対し行列乗算を実行する。したがって、各パリティ生成モジュール 207 を実行するために必要とされた X OR は、 $mL - 1$  個ではなく、 $2mL - 1$  個となる。フィードバック回路は、P および m に応じて急速に成長する  $P * m$  のような経路を含むことに留意することも重要である。したがって、各パリティ生成モジュールによるパリティディジットの生成は、K 衔のメッセージを N 衔の符号化メッセージに符号化することのできる速度を制限する臨界経路を形成し得る。また、図 2 の各パリティ生成モジュール 207 を実行するために必要とされた追加な計算ロジックは、ハードウェアリソースの需要増加をもたらすこともあり得る。

#### 【0055】

パリティ生成モジュールを実行するために必要とされた計算ロジックを減少するために、図 2 のエンコーダモジュール 200 を修正することができる。図 3 は、いくつかの実施形態に従った、非バイナリ線形ブロックコードの並列符号化を実行するエンコーダモジュール 300 を示す。図 3 のエンコーダモジュール 300 は、パリティ生成モジュールを実行するために必要とされた計算ロジックを減少することによって、図 2 のエンコーダモジュール 200 に必要とされた  $2mL - 1$  個の X OR に対して、パリティ生成モジュールを実行するために必要とされた X OR が  $mL - 1$  個に減少される。

#### 【0056】

図 2 のエンコーダモジュールとよく似て、図 3 のエンコーダモジュール 300 は、各クロックサイクルにおいて、K 衔のメッセージの複数のディジット (L) を処理することができる。エンコーダモジュール 300 は、N 衔の符号化メッセージを形成するために、K 衔のメッセージに対し任意 P 個のパリティディジットを生成するように構成されてもよい。K 衔のメッセージは、L 衔の並列入力として受信され、N 衔の符号化メッセージは、L 衔の並列出力として出力される。しかしながら、例示のため、図 3 のエンコーダモジュール 300 は、N 衔の符号化メッセージを形成するために、K 衔のメッセージに対し 16 個のパリティディジット (すなわち、 $P = 16$ ) を生成するように構成される。K 衔のメッセージは、4 衔の並列入力 (すなわち、 $L = 4$ ) として受信され、N 衔の符号化メッセージは、4 衔の並列出力として出力される。K が L の整数倍でない場合には、メッセージの全体長さが L の倍数になるように、メッセージの先頭にゼロを挿入する。

#### 【0057】

エンコーダモジュール 300 は、入力  $D_{in}$  と、出力  $D_{out}$  と、4 衔の入力シフトレジスタ 301 と、4 つの 4 衔パリティシフトレジスタ 303 / 303 と、4 つのパリティ生成モジュール 307 を備えるフィードバック回路 305 とを含む。図 3 のエンコーダモジュール 300 は、4 つのパリティ生成モジュール 307 および 4 つの 4 衔パリティシフトレジスタ 303 / 303 のみを含むが、エンコーダモジュール 300 は、任意 P / L 個の L 衔パリティシフトレジスタと、生成される P 個のパリティディジットに対応する任意 P / L 個のパリティ生成モジュールと、受信された L 衔の並列入力とを含んでもよい。

#### 【0058】

エンコーダモジュール 300 の入力  $D_{in}$  は、K 衔のメッセージを 4 衔の並列入力として受信するように構成される。エンコーダモジュール 300 の出力  $D_{out}$  は、16 個のパリティディジットを有する N 衔の符号化メッセージを 4 衔の並列出力として出力するように構成される。以下で詳細に説明するように、フィードバック回路 305 のパリティ生成モジュール 307 は各々、対応する 4 衔パリティシフトレジスタ 303 / 303 に格納される 4 つのパリティディジットを 1 回に生成するように構成される。

#### 【0059】

入力シフトレジスタ 301 の入力は、エンコーダモジュール 300 の入力  $D_{in}$  に連結され、入力シフトレジスタ 301 の出力は、マルチプレクサを介して、エンコーダモジュール 300 の出力  $D_{out}$  に連結される。

#### 【0060】

4 つの 4 衔パリティシフトレジスタ 303 / 303 は、1 つのパリティシフトレジス

10

20

30

40

50

タ 3 0 3 / 3 0 3 の出力が（次のパリティシフトレジスタが存在する場合に）次のパリティシフトレジスタ 3 0 3 / 3 0 3 の入力に連結されるように、順次連結されている。各 4 桁パリティシフトレジスタ 3 0 3 / 3 0 3 は、各パリティ生成モジュール 3 0 7 に対応しており、各パリティ生成モジュール 3 0 7 は、対応するパリティシフトレジスタ 3 0 3 / 3 0 3 の入力に連結される。4 つの 4 桁パリティシフトレジスタ 3 0 3 / 3 0 3 のうち最後のパリティシフトレジスタ 3 0 3 の入力は、エンコーダモジュール 3 0 0 の入力  $D_{in}$  に連結され、最後のパリティシフトレジスタ 3 0 3 の出力は、フィードバック回路 3 0 9 の各パリティ生成モジュール 3 0 7 に連結される。加算器モジュール A が、複数のソース（たとえば、パリティ生成モジュール 3 0 7、先行するパリティシフトレジスタ 3 0 3、およびエンコーダモジュール 3 0 0 の入力  $D_{in}$ ）に連結された各パリティシフトレジスタ 3 0 3 / 3 0 3 の入力に関連されてもよい。加算器モジュール A は、パリティシフトレジスタ 3 0 3 / 3 0 3 の入力で受信したデータを格納するために、データの合併を容易にする。追加の加算器モジュール A は、最後のパリティシフトレジスタ 3 0 3 の出力に関連されてもよい。追加の加算器モジュール A は、最後のパリティシフトレジスタ 3 0 3 の出力で受信したデータをフィードバック回路 3 0 5 のパリティ生成モジュール 3 0 7 に送信するために、データの合併を容易にする。最後のパリティシフトレジスタ 3 0 3 の出力は、さらに、マルチプレクサを介してエンコーダモジュール 3 0 0 の出力  $D_{out}$  に連結される。

【0061】

フィードバック回路 3 0 5 は、スイッチ S をさらに含む。スイッチ S が閉合されると、フィードバック回路 3 0 5 が作動され、パリティ生成モジュール 3 0 7 が能動的にパリティディジットを生成する。スイッチ S が開放されると、フィードバック回路 3 0 5 の動作が停止され、パリティ生成モジュール 3 0 7 がパリティディジットを生成しなくなる。

【0062】

最初の K / L 個のクロックサイクルにおいて、フィードバック回路 3 0 5 のスイッチ S は、閉合されている。第 1 のクロックサイクルにおいて、K 桁のメッセージの各 4 桁の部分は、エンコーダモジュール 3 0 0 の入力  $D_{in}$  で並列入力として受信され、最後のパリティシフトレジスタ 3 0 3 の出力と入力シフトレジスタ 3 0 1 の入力との両方に転送される。第 2 のクロックサイクルにおいて、最後のパリティシフトレジスタ 3 0 3 からの K 桁のメッセージの 4 桁の部分は、フィードバック回路 3 0 5 の各パリティ生成モジュール 3 0 7 に出力され、よって、各パリティ生成モジュール 3 0 7 は、対応するパリティシフトレジスタ 3 0 3 / 3 0 3 に送信されかつ格納される 4 つのパリティディジットを生成する。各パリティ生成モジュール 3 0 7 は、以下の擬似コードに従って、K 桁のメッセージの各ディジットに対しパリティディジットを生成するように構成されている。

【0063】

## 【数10】

`msg_padded = [gf(zeros(1,num_zeros_to_pad),m) msg];` %ゼロパディングは、メッセージの長さがブロック長さLの倍数であることを保証する

`msg_padded = [msg_padded gf(zeros(1,L),m)];` %パリティ数字を計算するために、ゼロをメッセージに加える

`for i = 1:(k/L)`

`feedback = (PMAT*((fliplr(lfsr_state(P-L+1:P)))).');`

10

%パリティを次に入るメッセージと合併する

`lfsr_state = [gf(zeros(1,L),m) lfsr_state(1:P-L)]+...`

`fliplr(feedback);`

`u(i) = msg_padded((i-1)*L + (1:L));`

`lfsr_state(P-L+1:P)=lfsr_state(P-L+1:P)+fliplr(u(i));`

`end`

## 【0064】

20

以下に示すように、上記の擬似コード用の式は、上記の式(4)を再整理することによって、式(8)を生成することができる。

## 【0065】

## 【数11】

$$p(x) = 0 + (m_0 x^{k-1} x^p)_{g(x)} + (m_1 x^{k-2} x^p)_{g(x)} + (m_2 x^{k-3} x^p)_{g(x)} + \dots + (m_{k-1} x^p)_{g(x)} + 0$$

$$0 = x^{k-1} x (0 + m_0 x^{p-1})_{g(x)} + (m_1 x^{k-2} x^p)_{g(x)} + (m_2 x^{k-3} x^p)_{g(x)} + \dots + (m_{k-1} x^p)_{g(x)} + 0$$

30

$$0 = x^{k-2} x \left[ x (0 + m_0 x^{p-1})_{g(x)} + m_1 x^{p-1} \right]_{g(x)} + (m_2 x^{k-3} x^p)_{g(x)} + \dots + (m_{k-1} x^p)_{g(x)} + 0$$

$$0 = x^{k-3} x \left\{ x \left[ x (0 + m_0 x^{p-1})_{g(x)} + m_1 x^{p-1} \right]_{g(x)} + m_2 x^{p-1} \right\} + \dots + (m_{k-1} x^p)_{g(x)}$$

$$p(x) = \left[ x \left\{ x \left[ \dots \right]_{g(x)} + m_{k-1} x^{p-1} \right\}_{g(x)} + 0 \right]_{g(x)} \quad (8)$$

## 【0066】

40

(4)に示された式は直列エンコーダモジュールに適用するが、当該式はエンコーダモジュールの並列実行にも適用できる。これは、エンコーダモジュールの入力で受信されたK桁のメッセージのL桁の部分が最後のパリティシフトレジスタの入力に入力されるべき、K桁のメッセージにゼロを加えるべきであることを示唆する。

## 【0067】

また、第2のクロックサイクルにおいて、K桁のメッセージの4桁の部分は、入力シフトレジスタ301から、マルチプレクサを介してエンコーダモジュール300の出力D<sub>u t</sub>に出力される。この動作は、K桁のメッセージのすべての4桁の部分が受信されるまで継続する。

## 【0068】

50

さらに、最初の  $K / L$  個のクロックサイクルの各クロックサイクルにおいて、各パリティシフトレジスタ 303 / 303 は、格納されたデータを（次のパリティシフトレジスタが存在する場合に）次のパリティシフトレジスタ 303 / 303 に転送する。最後のパリティシフトレジスタ 303 は、格納されたデータをフィードバック回路の各パリティ生成モジュール 307 に送信する。各クロックサイクルにおいて、 $K$  衍のメッセージの新たな  $L$  衍の部分が受信されると、対応するパリティシフトレジスタ 303 / 303 に格納される新たなパリティディジットがパリティ生成モジュール 307 に生成されるので、パリティシフトレジスタ 303 / 303 に格納されたパリティディジットが更新される。各クロックサイクルにおいて、新たに生成されたパリティディジットは、対応するパリティシフトレジスタ 303 / 303 に格納されているデータと合併され、パリティディジットの最新セットを形成する。

#### 【0069】

$(K / L) + 1$  クロックサイクルにおいて、エンコーダモジュール 300 の入力  $D_{in}$  は、ゼロ入力を受信する。このゼロ入力によって、エンコーダモジュール 300 がフィードバック回路 305 のスイッチ S を開放する。このクロックサイクルにおいて、入力シフトレジスタ 301 に格納された  $K$  衍のメッセージの最後の 4 衍の部分は、エンコーダモジュールの出力  $D_{out}$  に出力され、また、最後のパリティシフトレジスタ 303 に格納された  $K$  衍のメッセージの最後の 4 衍の部分は、フィードバック回路 305 の各パリティ生成モジュール 307 に出力され、フィードバック回路 305 のスイッチ S が開放される前に対応するパリティディジットを生成する。

#### 【0070】

$((K / L) + 2)$  クロックサイクル～ $((N / L) + 1)$  クロックサイクルの間に、フィードバック回路 305 のスイッチ S は、開放に維持され、パリティシフトレジスタ 303 / 303 に格納された最終パリティディジット値は、エンコーダモジュール 300 の出力  $D_{out}$  に出力される。これらのパリティディジットは、パリティシフトレジスタ 303 / 303 の各々に連結された制御信号 C\_E に応じて出力される。たとえば、 $(K / L) + 2$  クロックサイクルにおいて、最後のパリティシフトレジスタ 303 に格納された 4 つのパリティディジットは、マルチプレクサを介してエンコーダモジュール 300 の出力  $D_{out}$  に送信することができ、残りの各パリティシフトレジスタ 303 に格納された 4 つのパリティディジットは、次のパリティシフトレジスタ 303 / 303 に送信されることもできる。

#### 【0071】

最後のパリティシフトレジスタ 303 の出力をエンコーダモジュール 300 の入力  $D_{in}$  に連結するではなく、最後のパリティシフトレジスタ 303 の入力をエンコーダモジュール 300 の入力  $D_{in}$  に連結することによって、各パリティ生成モジュール 307 によって実行される行列乗算の複雑さが低減される。行列乗算は、所定のクロック周期において受信された  $K$  衍のメッセージの 4 衍の部分および最後のパリティシフトレジスタ 303 の出力の両方に対して実行されるではなく、所定のクロック周期において最後のパリティシフトレジスタ 303 の出力のみに対して実行される。したがって、各パリティ生成モジュール 307 を実行するために必要とされた X\_O\_R は、 $2mL - 1$  個ではなく、 $mL - 1$  個のみになる。これによって、 $K$  衍のメッセージを  $N$  衍の符号化メッセージに符号化する速度を増加するとともに、ハードウェアリソースの需要を減少することもできる。

#### 【0072】

図 3 のエンコーダモジュール 300 はさらに、ファンアウトを改善するために修正されてもよい。ファンアウトは、論理ゲート出力が接続されるゲート入力の数を指す。論理ゲート出力が接続されるゲート入力の数が減少されると、ファンアウトも減少される。図 4 は、いくつかの実施形態に従った、減少されたファンアウトを有する非線形ブロックコードの並列符号化を実施するためのエンコーダモジュールを示す。

#### 【0073】

10

20

30

40

50

図3のエンコーダモジュールとよく似て、図4のエンコーダモジュール400は、各クロックサイクルにおいて、K桁のメッセージの複数のディジット(L)を処理することができる。エンコーダモジュール400は、N桁の符号化メッセージを形成するために、K桁のメッセージに対し任意P個のパリティディジットを生成するように構成されてもよい。そのK桁のメッセージは、L桁の並列入力として受信され、そのN桁の符号化メッセージは、L桁の並列出力として出力される。しかしながら、例示のため、図4のエンコーダモジュール400は、N桁の符号化メッセージを形成するために、K桁のメッセージに対し16個のパリティディジット(すなわち、 $P = 16$ )を生成するように構成される。そのK桁のメッセージは、4桁の並列入力(すなわち、 $L = 4$ )として受信され、そのN桁の符号化メッセージは、4桁の並列出力として出力される。KがLの整数倍でない場合には、メッセージの全体長さがLの倍数になるように、メッセージの先頭にゼロを挿入する。

10

#### 【0074】

エンコーダモジュール400は、入力D<sub>in</sub>と、出力D<sub>out</sub>と、4段遅延器409と、4つの4桁パリティシフトレジスタ403/403/403と、4つのパリティ生成モジュール407を備えるフィードバック回路405とを含む。図4のエンコーダモジュール400は、4つのパリティ生成モジュール407および4つの4桁パリティシフトレジスタ403/403/403のみを含むが、エンコーダモジュール400は、任意P/L個のL桁パリティシフトレジスタと、生成されるP個のパリティ数字および受信されるL桁並列入力に対応する任意P/L個のパリティ生成モジュールとを含んでもよい。

20

#### 【0075】

エンコーダモジュール400の入力D<sub>in</sub>は、K桁のメッセージを4桁の並列入力として受信するように構成される。エンコーダモジュール400の出力D<sub>out</sub>は、16個のパリティディジットを有するN桁の符号化メッセージを4桁の並列出力として出力するように構成される。以下で詳細に説明するように、フィードバック回路405のパリティ生成モジュール407は、4桁パリティシフトレジスタに格納されるパリティディジットを生成するように構成される。

#### 【0076】

4つの4桁パリティシフトレジスタ403/403/403は、1つのパリティシフトレジスタ403/403/403の出力が(次のパリティシフトレジスタが存在する場合に)次のパリティシフトレジスタ403/403/403の入力に連結されるように、順次連結されている。各4桁パリティシフトレジスタ403/403/403は、各パリティ生成モジュール407に対応しており、各パリティ生成モジュール407は、対応するパリティシフトレジスタ403/403/403の入力に連結される。最初のパリティシフトレジスタ403の入力は、エンコーダモジュール400の入力D<sub>in</sub>に連結されかつフィードバック回路の各パリティ生成モジュール407に連結される。加算器モジュールAが、複数のソース(たとえば、パリティ生成モジュール407およびエンコーダモジュール400の入力D<sub>in</sub>)に連結された最初のパリティシフトレジスタの入力に関連されてもよい。加算器モジュールAは、最初のパリティシフトレジスタ403の入力で受信したデータを格納するために、データの合併を容易にする。

30

4つの4桁パリティシフトレジスタ403/403/403のうち最後のパリティシフトレジスタ403の入力は、さらに、マルチプレクサを介してエンコーダモジュール400の出力D<sub>out</sub>に連結される。

40

#### 【0077】

4段遅延器409は、エンコーダモジュール400の入力D<sub>in</sub>に連結され、かつ、マルチプレクサを介してエンコーダモジュール400の出力D<sub>out</sub>に連結されている。

#### 【0078】

フィードバック回路405は、4つのスイッチS1, S2, S3, S4をさらに含む。各スイッチS1, S2, S3, S4は、パリティ生成モジュール407に対応している。

50

スイッチ S 1 , S 2 , S 3 , S 4 が閉合されると、フィードバック回路 405 のパリティ生成モジュール 407 が作動され、パリティディジットを生成する。スイッチ S 1 , S 2 , S 3 , S 4 が開放されると、フィードバック回路 405 のパリティ生成モジュール 407 の動作が停止され、パリティディジットを生成しなくなる。

## 【0079】

最初の K / L 個のクロックサイクルにおいて、フィードバック回路 405 の各スイッチ S 1 , S 2 , S 3 , S 4 は、閉合されている。最初の (K / L) 個のクロックサイクルの各クロックサイクルにおいて、K 桁のメッセージの 4 衔の部分は、エンコーダモジュール 400 の入力 D<sub>i,n</sub> で受信され、最初のパリティシフトレジスタ 403 の出力転送される。同時に、各パリティシフトレジスタ 403 / 403 / 403 は、格納されたデータを対応するパリティ生成モジュール 407 および(次のパリティシフトレジスタが存在する場合に)次のパリティシフトレジスタ 403 / 403 / 403 に転送する。各パリティ生成モジュール 407 は、最初のパリティシフトレジスタ 403 にフィードバックされるパリティディジットを生成する。フィードバック回路 405 のパリティ生成モジュール 407 により生成された新たなパリティディジットが最初のパリティシフトレジスタ 403 にフィードバックされるため、各パリティシフトレジスタ 403 / 403 / 403 に格納されたデータは、クロックサイクル毎に更新される。各パリティ生成モジュール 407 は、擬似コード (L = 4, P = 16) に従って、K 桁のメッセージの各ディジットに対しパリティディジットを生成するように構成されている。10

## 【0080】

## 【数12】

```

for i = 1:(k/L)

u(i) = msg_padded((i-1)*L + (1:L));

parity_temp = PMAT(1:4,:)*(shift_reg_state_0)+...

PMAT(5:8,:)*(shift_reg_state_1)+...

PMAT(9:12,:)*(shift_reg_state_2)+...

PMAT(13:16,:)*(shift_reg_state_3);30

shift_reg_state_3 = shift_reg_state_2;

shift_reg_state_2 = shift_reg_state_1;

shift_reg_state_1 = shift_reg_state_0;

shift_reg_state_0 = parity_temp+u(i);

end

```

## 【0081】

20

30

## 【数13】

```

%ゼロ挿入をしてパリティビットを計算する。

%以下の演算が終了後のシフトレジスタは、パリティディジットを含む。

clr = [0 0 0 0];%スイッチ S1, S2, S3, S4 と同様である

for i = 1:L

u(i) = gf(zeros(1,L),m);

parity_temp = PMAT(1:4,:)*(shift_reg_state_0)*(1-clr(1))+...

10

PMAT(5:8,:)*(shift_reg_state_1)*(1-clr(2))+...

PMAT(9:12,:)*(shift_reg_state_2)*(1-clr(3))+...

PMAT(13:16,:)*(shift_reg_state_3)*(1-clr(4));

shift_reg_state_3 = shift_reg_state_2;

shift_reg_state_2 = shift_reg_state_1;

shift_reg_state_1 = shift_reg_state_0;

shift_reg_state_0 = parity_temp+u(i);

20

clr = [1 clr(1:3)];

end

```

## 【0082】

パリティシフトレジスタ $403/403/403$ に格納されたデータは、パリティディジットを形成する。擬似コードは、上記の微分式(8)と同様の方法で得られてもよい。任意所定のサイクルにおいて、すべてのP個のパリティディジットではなく、L個のパリティディジットのみが生成される。すべてのP個のパリティディジットは、P/L個のクロックサイクルに亘って生成される。

## 【0083】

同時に、最初のK/L個のクロックサイクルの各クロックサイクルにおいて、エンコーダモジュール $400$ の入力 $D_{in}$ で受信したK桁のメッセージの4桁の部分は、マルチブレクサを介してエンコーダモジュール $400$ の出力 $D_{out}$ に転送される前に4段遅延器 $409$ を通るため、エンコーダモジュール $400$ により出力される最初のK個のディジットは、K桁のメッセージの4桁の並列出力となる。

## 【0084】

$((K/L)+1) \sim ((K/L)+(P/L))$ 個のクロックサイクルの各クロックサイクルにおいて、エンコーダモジュール $400$ の入力 $D_{in}$ は、ゼロ入力を受信する。各ゼロ入力によって、エンコーダモジュール $400$ は、フィードバック回路 $405$ のスイッチ $S1, S2, S3, S4$ を順次開放する。また、各クロックサイクルにおいて、各パリティシフトレジスタ $403/403/403$ は、格納されたデータを(対応するスイッチが閉合されている)パリティ生成モジュール $407$ に送信する。対応するパリティ生成モジュール $407$ は、最初のパリティシフトレジスタ $403$ に転送されるパリティディジットを生成する。この動作は、フィードバック回路 $405$ のスイッチ $S1, S2, S3, S4$ がすべて開放されるまで継続する。

## 【0085】

$((K/L)+(P/L)) \sim ((N/L)+(P/L))$ 個のクロックサイクルの各クロックサイクルにおいて、すべてのスイッチ $S1, S2, S3, S4$ は、開放に維持され、パリティシフトレジスタ $403/403/403$ に格納されたパリティディジットを生成する。

10

20

30

40

50

トは、パリティシフトレジスタ403 / 403 / 403の各々に連結された制御信号CEに応じて出力される。たとえば、(K/L)+(P/L)クロックサイクルにおいて、最後のパリティシフトレジスタ403に格納された4つのパリティディジットは、マルチプレクサを介してエンコーダモジュール400の出力D<sub>out</sub>に送信されることができ、残りの各パリティシフトレジスタ403 / 403に格納された4つのパリティディジットは、次のパリティシフトレジスタ403 / 403に送信されることもできる。

### 【0086】

K桁のメッセージの各L桁の部分を各パリティ生成モジュール407に伝送するではなく、K桁のメッセージの各L桁の部分を最初のパリティシフトレジスタ403に伝送することによって、エンコーダモジュール400の入力D<sub>in</sub>の高ファンアウトが回避され得る。また、パリティ生成モジュール407が(P/L個の)異なるシフトレジスタ403 / 403 / 403から供給されるため、図2のエンコーダモジュール200および図3のエンコーダモジュール300に比べて、いずれかのシフトレジスタ403 / 403 / 403のファンアウトは、(P/L)の倍数で減少される。ファンアウトの減少は、高い最大周波数を達成することが可能にしながら、ルーティングアルゴリズムに与える過度負荷を低減する。

### 【0087】

特定の実施形態が図示されおよび説明されてきたが、これらは請求される発明を限定する意図なく、当業者なら誰でも、本発明の精神および範囲を逸脱すること無く本発明にさまざまな変更や修正を加えることが可能であることは明らかである。したがって、明細書および図面は、限定的な意味ではなく例示的ものであるとみなされるべきである。請求される発明は、代替物、変形物および等価物を包含することが意図される。

【図1】

【図2】

FIG. 1

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

---

フロントページの続き

(72)発明者 ターン , ハイ - ジョ

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、ロジック・ドライブ、2100

審査官 岡 裕之

(56)参考文献 米国特許第04777635(US,A)

米国特許第04293951(US,A)

米国特許第06493845(US,B1)

特開2011-217138(JP,A)

特開2004-208282(JP,A)

特開2001-94440(JP,A)

特表2002-522943(JP,A)

MATSUSHIMA, T.K. et al., Parallel Architecture For High-Speed Reed-Solomon Codec , Telecommunications Symposium, 1998. ITS '98 Proceedings. SBT/IEEE International (Volume:2), IEEE, 1998年 8月, pp.468-473

QINGSHENG HU et al., 10Gb/s RS-BCH Concatenated Codec with Parallel Strategies for Fiber Communications , Communications, Circuits and Systems (ICCCAS), 2010 International Conference on , IEEE, 2010年 7月, pp.303-307

(58)調査した分野(Int.Cl. , DB名)

H03M 13/00 - 13/53

CiNii, IEEE Xplore