(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4579012号

(P4579012)

(45) 発行日 平成22年11月10日(2010.11.10)

(24) 登録日 平成22年9月3日(2010.9.3)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

H01L 29/786 (2006.01)G02F 1/1368

H01L 29/78 619A

請求項の数 8 (全 11 頁)

(21) 出願番号 特願2005-58886 (P2005-58886)

(22) 出願日 平成17年3月3日 (2005.3.3)

(65) 公開番号 特開2006-243344 (P2006-243344A)

(43) 公開日 平成18年9月14日 (2006.9.14)

審査請求日 平成19年3月2日 (2007.3.2)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 110000338

特許業務法人原謙三國際特許事務所

(72) 発明者 美崎 克紀

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

審査官 福田 知喜

最終頁に続く

(54) 【発明の名称】 液晶表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

(a) 絶縁性透明基板上方に、動作半導体層とコンタクト用の低抵抗半導体層とを含む積層を成膜する工程と、

(b) 前記積層上に島状の第1マスクパターンを形成する工程と、

(c) 前記第1マスクパターンをエッチングマスクとして、前記積層を島状にパターニングする工程と、

(d) 前記第1マスクパターンから露出した前記積層の外周側壁を酸化して側壁酸化膜を形成する工程であって、該工程がオゾン水を用いた酸化、または高压酸化で行われ、前記第1マスクパターンを側壁酸化膜よりも後退させない工程と、

(e) 前記第1マスクパターンを除去し、外周側壁にのみ前記側壁酸化膜が形成された島状積層を露出する工程と、

(f) 前記工程(e)の後、前記島状積層を覆って、電極/配線層を堆積する工程と、

(g) 前記電極/配線層上に配線形状の第2マスクパターンを形成する工程と、

(h) 前記第2マスクパターンをエッチングマスクとして前記電極/配線層をパターニングする工程と、

(i) 前記第2マスクパターンをエッチングマスクとして前記低抵抗半導体層の全厚さと前記動作半導体層の一部厚さとをパターニングする工程と、

(j) 前記第2マスクパターンを除去し、前記動作半導体層の上で分離された前記低抵抗半導体層と前記低抵抗半導体層に電気的に接続された電極/配線層を残す工程と、

10

20

を含む液晶表示装置の製造方法。

【請求項 2】

前記工程 ( i ) がドライエッティングで行われる請求項1記載の液晶表示装置の製造方法

。

【請求項 3】

前記工程 ( i ) が、前記第 2 マスクパターン外の領域では、前記側壁酸化膜に接する領域を含めて、前記低抵抗半導体層を完全に除去する請求項1又は2記載の液晶表示装置の製造方法。

【請求項 4】

( k ) 前記工程 ( i ) の後、前記電極/配線層を覆って、絶縁保護膜を形成する工程と、10

( l ) 前記電極/配線層の所定領域上で前記絶縁保護膜にコンタクト孔を形成する工程と、

、

( m ) 前記絶縁保護膜上に透明電極層を形成し、画素電極状にパターニングする工程と、

、

をさらに含む請求項1 ~ 3のいずれか 1 項記載の液晶表示装置の製造方法。

【請求項 5】

( x ) 前記工程 ( a ) 前に、前記絶縁性透明基板上にゲートバスライン、補助容量バスラインを形成する工程と、

( y ) 前記ゲートバスライン、補助容量バスラインを覆って、ゲート絶縁層を成膜する工程と、20

をさらに含む請求項1 ~ 4のいずれか 1 項記載の液晶表示装置の製造方法。

【請求項 6】

前記第 1 マスクパターン、第 2 マスクパターンが共にレジストパターンである請求項1 ~ 5のいずれか 1 項記載の液晶表示装置の製造方法。

【請求項 7】

前記工程 ( d ) が、オゾン濃度 3 ~ 5 p p m のオゾン水で行われる請求項1 ~ 6のいずれか 1 項記載の液晶表示装置の製造方法。

【請求項 8】

前記工程 ( d ) が、温度 100 ~ 250 、霧囲気圧力 1 . 5 ~ 2 . 5 M P a 、水蒸気を含む霧囲気中の高圧酸化で行われる請求項1 ~ 6のいずれか 1 項記載の液晶表示装置の製造方法。30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置の製造方法に関し、特にアクティブマトリックス基板を用いた液晶表示装置の製造方法に関する。

【背景技術】

【0002】

多数の画素を行列上に配列して表示を行う液晶表示装置において、画素数が多くデュードイー比が低い場合には、画素毎に薄膜トランジスタ ( T F T ) などのスイッチング素子を形成したアクティブマトリックス基板が多く用いられる。40

【0003】

画素電極は、T F T を介して信号電圧を供給される。信号電圧の保持特性を高めるため、補助容量も形成される。例えば、ゲートバスラインと平行に補助容量バスラインが形成され、画素電極との間に容量を形成する。

【0004】

T F T のオフ抵抗が無限大で、補助容量にもリークがなければ、一旦補助容量に蓄積された信号電圧は、書き換えられるまで保持される。T F T にリーク電流が生じると、保持された信号電圧は徐々に減少する。良好な画質を実現するためにはT F T のリークは少なければ少ないほどよい。50

## 【0005】

【特許文献1】特表2000-501569号公報

【特許文献2】特開2000-332254号公報

【特許文献3】特開2003-188183号公報

【特許文献4】特開2004-165688号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

本発明の目的は、製造されるTFTのリークが少なく、プロセスマージンの大きな液晶表示装置の製造方法を提供することである。

10

## 【課題を解決するための手段】

## 【0007】

本発明の1観点によれば、

(a) 絶縁性透明基板上方に、動作半導体層とコンタクト用の低抵抗半導体層とを含む積層を成膜する工程と、

(b) 前記積層上に島状の第1マスクパターンを形成する工程と、

(c) 前記第1マスクパターンをエッチングマスクとして、前記積層を島状にパターニングする工程と、

(d) 前記第1マスクパターンから露出した前記積層の外周側壁を酸化して側壁酸化膜を形成する工程であって、該工程がオゾン水を用いた酸化、または高压酸化で行われ、前記第1マスクパターンを側壁酸化膜よりも後退させない工程と、

20

(e) 前記第1マスクパターンを除去し、外周側壁にのみ前記側壁酸化膜が形成された島状積層を露出する工程と、

(f) 前記工程(e)の後、前記島状積層を覆って、電極/配線層を堆積する工程と、

(g) 前記電極/配線層上に配線形状の第2マスクパターンを形成する工程と、

(h) 前記第2マスクパターンをエッチングマスクとして前記電極/配線層をパターニングする工程と、

(i) 前記第2マスクパターンをエッチングマスクとして前記低抵抗半導体層の全厚さと前記動作半導体層の一部厚さとをパターニングする工程と、

(j) 前記第2マスクパターンを除去し、前記動作半導体層の上で分離された前記低抵抗半導体層と前記低抵抗半導体層に電気的に接続された電極/配線層を残す工程と、

30

を含む液晶表示装置の製造方法

が提供される。

## 【発明の効果】

## 【0008】

マスクパターンを側壁酸化膜よりも後退させずに側壁酸化を行うので、積層上面に酸化膜が形成されず、低抵抗半導体層の除去が容易になる。動作半導体層を残すプロセスのマージンが増加する。

## 【発明を実施するための最良の形態】

## 【0009】

40

以下、図面を参照して本発明者行った研究、解析、解決を説明する。

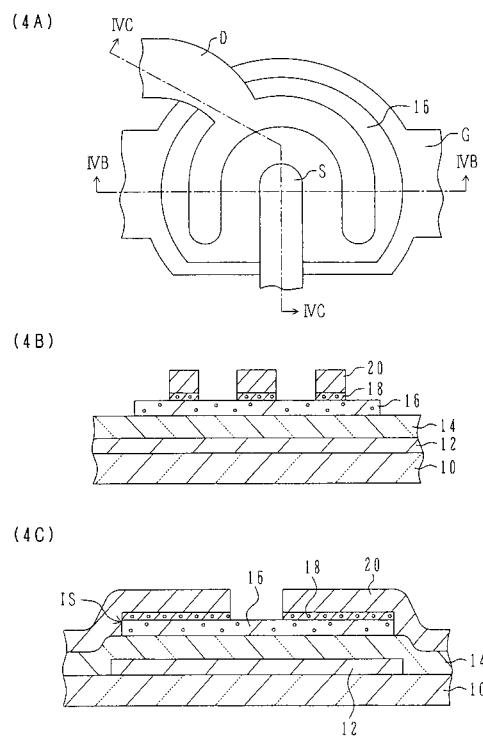

## 【0010】

図4Aは、考察したTFTの構成を概略的に示す平面図である。ゲートバスラインGが横方向に延在し、ゲート絶縁膜で覆われている。ゲート絶縁膜上、ゲートバスライン上方にTFTの動作半導体層となる島状半導体層16が下方を切り欠いた円形状に配置されている。ソース電極Sが下方から島状半導体層16の中央部に延び、ソース電極Sの周囲を一定距離を介してドレイン電極Dが取り囲んでいる。

## 【0011】

図4B、4Cは、図4AのIVB-IVB線、IVC-IVC線に沿う断面図である。ガラス基板10の上にゲートバスラインGを構成する配線層12が形成され、ゲート絶縁

50

膜14で覆われている。ゲート絶縁膜14上にTFTの動作半導体層を構成するアモルファスシリコン層16が形成され、その上にオーミックコンタクトを形成するための低抵抗のn<sup>+</sup>型アモルファスシリコン層18が形成されている。n<sup>+</sup>型アモルファスシリコン層18の上に配線層20が形成され、ソース電極、ドレイン電極を構成する。n<sup>+</sup>型アモルファスシリコン層18は、アモルファスシリコン層16と同一形状にパターニングされた後、配線層20と同一形状にパターニングされている。

#### 【0012】

このTFTは、ゲートバスラインGをパターニングした後、ゲート絶縁膜14、シリコン層16, 18を積層し、シリコン層16, 18をパターニングし、配線層20を堆積し、配線層20とシリコン層18をパターニングすることによって形成できる。ホトリソグラフィの回数は3回と少ない。また島状積層外ではシリコン層16, 18が除去され、配線容量を低く出来る。n<sup>+</sup>型アモルファスシリコン層18をソース側とドレイン側とに分離し、且つアモルファスシリコン層16を所望の厚さ残すためには時間で制御したコントロールエッチを必要とする。

#### 【0013】

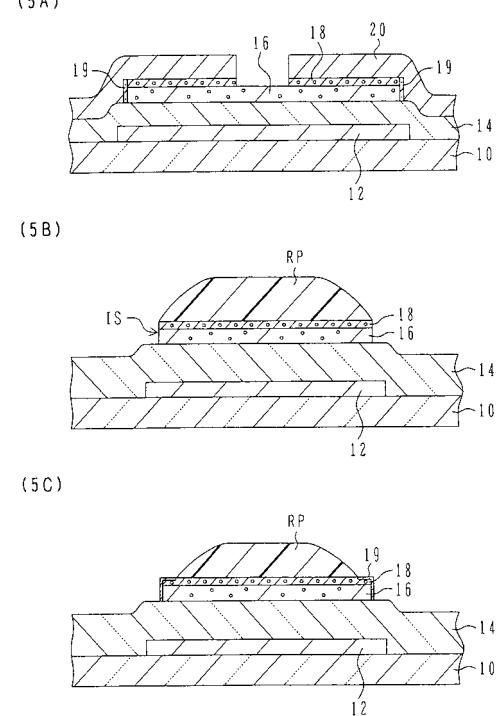

図4A-4Cに示すTFTは、ソースS-ドレインD間にリーク電流が流れることが判った。シリコン層16, 18の側壁に配線層20が接し、ショットキコンタクトを形成していることがリークに寄与していることが推察された。そこで、シリコン層16, 18の側壁を酸化して酸化膜を形成することを考えた。

#### 【0014】

図5Aが、検討した構成である。図4Cと比較すると、シリコン層16, 18の外周の側壁に酸化膜19を形成し、半導体層16, 18の側壁を配線20から電気的に分離している点が異なる。

#### 【0015】

図5Bは、シリコン層16, 18のパターニング工程を示す。n<sup>+</sup>型アモルファスシリコン層18の上に島状のパターンを有するレジストパターンRPを形成し、シリコン層16, 18をエッチングしてパターニングする。パターニングを終了した時点で、シリコン層16, 18の側壁は露出し、上面はレジストパターンRPで覆われている。そこで、露出しているシリコン表面を酸化すれば、図5Aの構造を得られると考えた。

#### 【0016】

そこで、酸素プラズマ中でアッシングを行って、シリコン層16, 18の側壁を酸化した。ところが、アッシングを行ってもリーク電流は消滅しなかった。

#### 【0017】

図5Cは、本発明者が考察した、レジストパターンRPによって上面を覆われたシリコン層16, 18の側壁をアッシングで酸化する状態を示す。アッシングは、シリコン層16, 18の側壁を酸化するが、レジストパターンRPもアッシングして縮小させる。レジストパターンRPの端部は後退して、シリコン層18の上面外周部が露出する。露出したシリコン表面は酸化され、側壁のみでなく上面外周部も酸化されてしまう。シリコン層18の外周部は酸化シリコン層19で覆われた状態となる。

#### 【0018】

配線層のエッチングに続いて、シリコン層のエッチングを行うとき、酸化シリコン層のエッチングレートは低い。酸化シリコン層19のない部分ではn<sup>+</sup>型アモルファスシリコン層18が完全にエッチングされても、酸化シリコン層19で覆われている部分、又は覆われていた部分では、n<sup>+</sup>型アモルファスシリコン層18が残る可能性が大きい。酸化シリコン層19は島状半導体層の外周に沿って形成されるので、外周に沿ってリークパスが形成されてしまう。

#### 【0019】

オーバーエッチング量を増加して、n<sup>+</sup>型アモルファスシリコン層18を完全にエッチングすることも可能であろう。しかし、そうするとアモルファスシリコン層16に対するエッチング量も増加してしまい、所望の厚さのアモルファスシリコン層16を残すプロセ

10

20

30

40

50

スマージンは狭くなってしまうであろう。

**【0020】**

以下、本発明の実施例による液晶表示装置の製造方法を説明する。

**【0021】**

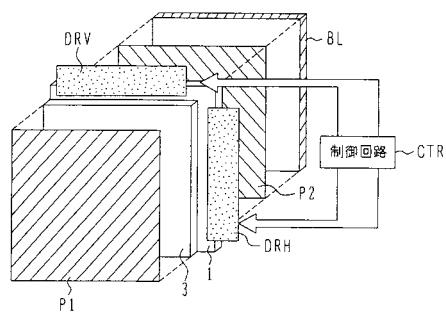

図1Aは、液晶表示装置の構成を概略的に示す斜視図である。TFT基板1と対向基板3とが対向し、その間に液晶層を挟持する。TFT基板1及び対向基板3の外側には、1対の偏光板P1、P2が配置される。偏光板P2の後側には、バックライトユニットBLも配置されている。制御回路CTRから、液晶表示装置の水平ドライバDRH及び垂直ドライバDRVに制御信号が送られる。

**【0022】**

10

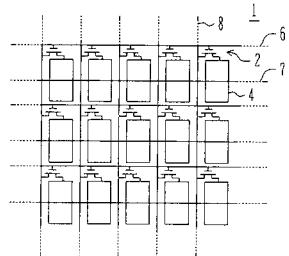

図1Bは、TFT基板1の構成を概略的に示す。TFT基板1の表面には、複数のゲートバスライン6が水平方向に並列に配置され、複数のドレインバスライン8が垂直方向に平行に配置されている。隣接するゲートバスライン6と隣接するドレインバスライン8に囲まれる領域が1画素の領域となる。ゲートバスライン6とドレインバスライン8の各交点には、薄膜トランジスタ(TFT)2が接続されている。TFT2の一方の電流端子は、画素電極4に接続されている。画素電極4に重なるように、補助容量バスライン7がゲートバスライン6と平行に配置されている。対向基板3の上には、例えばカラーフィルタ層と共に通電極が形成されている。以下、TFT基板についてさらに説明する。

**【0023】**

20

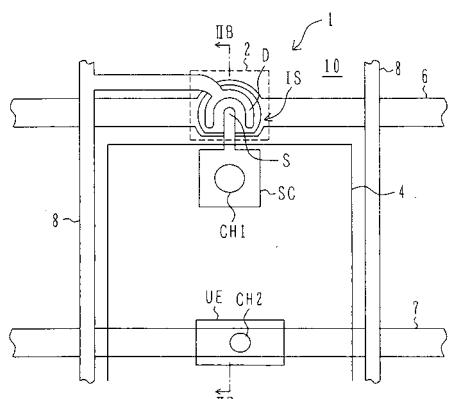

図2Aは、TFT基板の1部を拡大して示す平面図である。ガラス基板10上にゲートバスライン6、補助容量バスライン7が並列に形成されており、その上を覆ってゲート絶縁膜がガラス基板上に形成されている。ゲートバスライン6上方で、ゲート絶縁膜上に動作半導体層の島状領域ISが形成されている。ソースSは、動作半導体層ISの中心部から下方に延在し、幅を広げてソースコンタクト領域SCを形成している。補助容量バスライン7上方においては、ゲート絶縁膜上に補助容量の上部電極UEが形成される。ごみ付着などによる歩留まりを考慮した時、薄膜トランジスタTFT、ソースコンタクト領域SC、上部電極UEは、ドレインバスライン8間の中央部に配置するのが好ましい。

ドレインDは、ソースSの先端を囲むように形成され、動作半導体層IS外に引き出され、ドレインバスライン8に接続されている。ソースS、ドレインDを覆うように保護絶縁膜が形成され、ソースコンタクト領域SC及び補助容量の上部電極UE上にコンタクト孔CH1、CH2が形成される。

30

**【0024】**

保護絶縁膜上に透明電極4が形成され、パターニングされて画素電極を形成する。画素電極4は、コンタクト孔CH1、CH2を介してソースコンタクト領域SC及び補助容量の上部電極UEに接続される。

**【0025】**

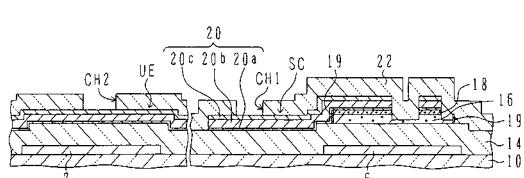

図2Bは、図2A中IIIB-IIIB線に沿う断面図を示す。ガラス基板10上にA1合金層とTi合金層の積層等の金属層で形成されたゲートバスライン6、補助容量バスライン7が形成される。ゲートバスライン6、補助容量バスライン7を覆って、ガラス基板10上に窒化シリコン膜等のゲート絶縁膜14が形成される。ゲートバスライン6上方においては、動作半導体層を構成するアモルファスシリコン層16とオーミックコンタクト形成用低抵抗半導体層である低抵抗アモルファスシリコン層18が積層され、同一島状形状にパターニングされている。低抵抗シリコン層18上に、Mo等の第1配線層20a、A1等の第2配線層20b、Mo等の第3配線層20cの積層からなる電極/配線層20が形成され、配線形状にパターニングされている。

40

動作半導体層16上方においては、電極/配線層20がソースS側とドレインD側が分離されるようにエッチングされ、その下の低抵抗半導体層18もソースS側とドレインD側が分離されるようにエッチングされている。電極/配線層20は、島状半導体層外にも延在し、ソースコンタクト領域SCを形成している。補助容量バスライン7上方においても、電極/配線層20により補助容量の上部電極UEが形成されている。

50

半導体積層 16、18 の外周側壁上には酸化シリコン膜 19 が形成されている。低抵抗半導体層 18 がエッチングされた外周部分においては、エッチングレートの低い酸化膜 19 が垂直に立ったフェンス状に残っている。しかしながら、低抵抗半導体層 18 の上面には酸化シリコン膜 19 が形成されていないため、酸化シリコン膜 19 に接する部分においても、低抵抗半導体層 18 のエッチングが完全に行なわれ、リークパスは残されていない。

#### 【0026】

電極 / 配線層 20 を覆うように窒化シリコン層などの保護絶縁膜 22 が形成され、ソースコンタクト領域 S C、補助容量の上部電極 U E 上にコンタクト孔 C H 1、C H 2 が形成されている。この上に透明電極を形成し、パターニングすると、ソース S 及び補助容量の上部電極 U E に接続された画素電極 4 (図 2 A) が形成される。

10

#### 【0027】

以下、図 2 A、2 B に示す液晶表示装置の製造方法を説明する。

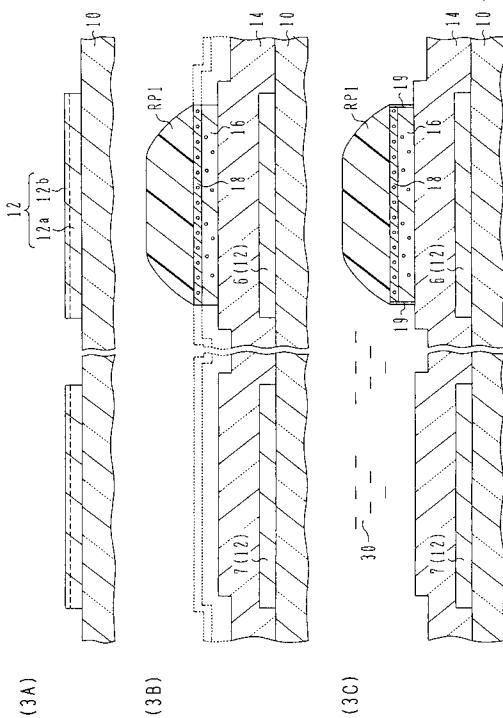

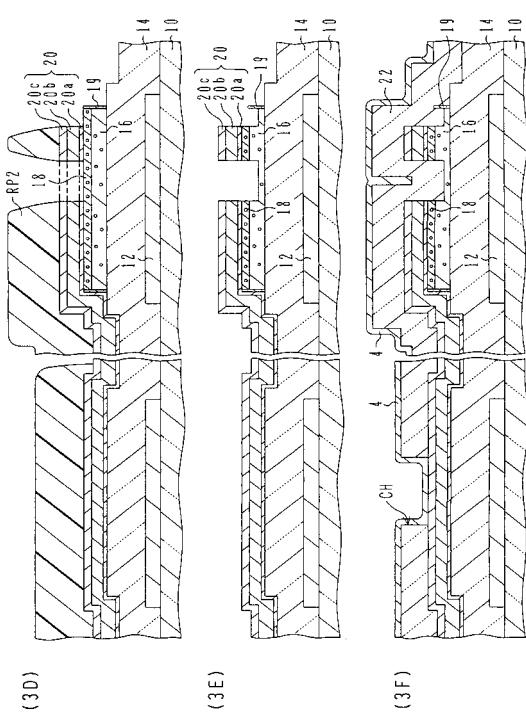

#### 【0028】

図 3 A に示すように、ガラス基板 10 の上に、必要に応じて酸化シリコン等の保護絶縁膜を形成した後、例えば厚さ 130 nm のアルミニウム (アルミニウム合金を含む) 層 12 a と厚さ 70 nm のチタン (チタン合金を含む) 膜 12 b を順にスパッタリングして、全面に厚さ 200 nm の金属膜 12 を成膜する。上層の高融点金属としては、チタンの他に、クロム (Cr)、モリブデン (Mo)、タンタル (Ta)、タンゲステン (W) (又はそれらの合金) を用いることもできる。下層の主導電膜としてアルミニウム合金を用いる場合、アルミニウムにネオジウム (Nd)、珪素 (Si)、銅 (Cu)、チタン (Ti)、タンゲステン (W)、タンタル (Ta)、スカンジウム (Sc) 等を 1 つ又は複数含む材料を用いることができる。

20

次に全面にレジスト層を塗布し、露光現像してゲートバスライン、補助容量バスラインの形状を有するレジストパターンを形成する。このレジストパターンをエッチングマスクとし、塩素系ガス (塩素を含むガス) を用いたドライエッチングを行い、ゲートバスライン及び補助容量バスラインをパターニングする。なお、ガラス基板端部においては、接続端子部分も同時に形成する。

#### 【0029】

図 3 B に示すように、ゲートバスライン 6、補助容量バスライン 7 を覆ってガラス基板 10 上に例えば厚さ約 400 nm の窒化シリコン膜 14 をプラズマ CVD により成膜する。この窒化シリコン膜がゲート絶縁膜を構成する。次に動作半導体層を構成する高抵抗アモルファスシリコン層 16 を厚さ約 130 nm プラズマ CVD によりゲート絶縁膜 14 全面上に成膜する。さらに、オーミックコンタクト形成用の低抵抗 n<sup>+</sup>型アモルファスシリコン層 18 を厚さ約 30 nm プラズマ CVD によりアモルファスシリコン層 16 上に成膜する。

30

#### 【0030】

次に、スピニコートによりホトレジスト層を全面に塗布し、上方から露光、現像することにより、ゲートバスライン 6 上方に島状のレジストパターン R P 1 を形成する。このレジストパターン R P 1 をエッチングマスクとし、低抵抗アモルファスシリコン層 18 及び高抵抗アモルファスシリコン層 16 をフッ素系ガス (フッ素を含むガス) を用いたドライエッチングよりパターニングする。ゲートバスライン 6 上方の所定領域にのみ島状に積層シリコン層が残る。

40

#### 【0031】

図 3 C に示すように、オゾン濃度 3 ~ 5 ppm のオゾン水 30 を流量 10 ~ 15 リットル / min で流し、15 ~ 40 で 30 秒 ~ 300 秒、例えば常温で 60 秒 ~ 180 秒 オゾン水処理を行い、レジストパターン R P 1 外に露出した積層シリコン層 16、18 の側壁を酸化し、酸化シリコン層 19 を形成する。

#### 【0032】

なお、オゾン水による酸化に代え、温度 100 ~ 250 、雰囲気圧力 1.5 ~ 2.5 MPa、例えば 2 MPa、水蒸気を含む雰囲気中で 30 分 ~ 120 分、例えば 60 分の

50

高圧酸化を行なってシリコン積層の側壁上に酸化シリコン膜を形成してもよい。これらの酸化法は、レジストパターンをほとんど後退させないため、積層シリコン層の側壁は酸化されるが、上面はほとんど酸化されない。その後レジストパターン R P 1 は剥離液で除去する。

#### 【 0 0 3 3 】

図 3 D に示すように、パターニングされたシリコン積層を覆って基板全面上に例えれば厚さ 2 0 n m のモリブデン層 2 0 a 、厚さ 2 0 0 n m のアルミニウム層 2 0 b 、厚さ 4 0 n m のモリブデン層 2 0 c をスパッタリングで積層する。このようにして、厚さ 2 6 0 n m の電極 / 配線層 2 0 が形成される。なお、高融点金属層として Mo の他に Cr 、 Ta 、 W 等を用いることもできる。合金を用いてもよいことはゲートバスライン、補助容量バスラインと同様である。10

#### 【 0 0 3 4 】

次に、基板全面上にホトレジスト層を塗布し、上面より露光、現像して配線(ソース / ドレインを含む)形状のレジストパターン R P 2 を形成する。このレジストパターン R P 2 をエッチングマスクとし、先ず酢酸、硝酸、磷酸の混合液を用いたウェットエッチングを施して電極 / 配線層 2 0 をエッチングし、配線、ソース電極 S 、ドレイン電極 D をパターニングする。

#### 【 0 0 3 5 】

次に、同じレジストパターン R P 2 をエッチングマスクとし、フッ素系ガスを用いたドライエッチングによりオーミックコンタクト形成用の低抵抗シリコン層 1 8 をエッチングする。低抵抗シリコン層 1 8 を完全にエッチングするためにオーバーエッチングを行なうと、動作半導体層を構成する高抵抗シリコン層 1 6 も若干エッチングされる。酸化シリコン層 1 9 は、基板法線方向に垂直に立つフェンス上に形成されているため、エッチングの妨げとならず、酸化シリコン層 1 9 に接しているシリコン層もエッチングされ、低抵抗シリコン層 1 8 は完全にエッチングできる。その後レジストパターン R P 2 は剥離液で除去する。20

#### 【 0 0 3 6 】

図 3 E は、エッチングが終了し、レジストパターン R P 2 を除去した状態を示す断面図である。右側に示す酸化シリコン層 1 9 は、フェンス上に残っていても、その側面には低抵抗シリコン層 1 8 は残存せず、リークパスの発生が防止される。30

#### 【 0 0 3 7 】

図 3 F に示すように、パターニングした電極 / 配線層 2 0 を覆って基板全面上に、保護絶縁膜として厚さ約 3 0 0 n m の窒化シリコン層 2 2 をプラズマ C V D により成膜する。窒化シリコン層 2 2 上にレジストパターンを形成し、ソースコンタクト領域 S C 、補助容量の上部電極 U E 上にコンタクト孔 C H を形成する。

#### 【 0 0 3 8 】

その後、透明電極としてインジウム錫酸化物 ( I T O ) 膜 4 を厚さ約 7 0 n m スパッタリング等によりアモルファス相で成膜する。 I T O 膜 4 上にレジストパターンを形成し、蔥酸系エッチャントを用いたウェットエッチングにより画素電極 4 をパターニングする。この画素電極 4 は、コンタクト孔 C H を介してソース電極及び補助容量の上部電極と電気的に接続される。その後 1 5 0 ~ 2 3 0 、例えば 2 0 0 で熱処理を行ない、 I T O 膜 4 を結晶化させる。40

#### 【 0 0 3 9 】

その後、必要に応じて基板全面上に配向膜等を成膜する。カラーフィルタ基板は、公知の方法で形成できる。その他、液晶表示装置の構成及び製造方法として特許文献 3 , 4 の実施の態様に開示されたような公知の技術を種々採用することができる。

シリコン積層の側壁を酸化するマスクパターンは、酸化中シリコン積層側壁から後退しないようにすることが重要である。レジストパターンを用いる場合は、上述の実施例のように、オゾン水酸化又は高圧酸化を行なうことが好ましい。

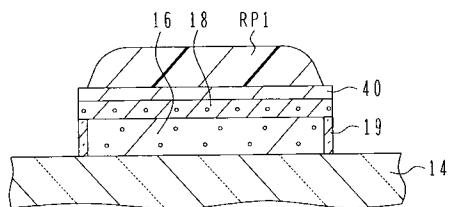

図 6 に示すように、レジストパターン R P 1 の下にさらに T I N 膜等のマスク層 4 0 を形50

成してもよい。レジストパターン R P 1 が酸化工程で後退しても、シリコン層 1 8 の表面はマスク層 4 0 で覆われた状態を保つ。側壁酸化がより容易になるであろう。このマスク層は、レジスト除去と共に、又はレジスト除去に続いて選択性欲除去できることが好ましい。

#### 【 0 0 4 0 】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組合せ等が可能なことは当業者に自明であろう。

#### 【 図面の簡単な説明 】

#### 【 0 0 4 1 】

【図 1】液晶表示装置の構成を示す斜視図及び平面図である。

10

【図 2】図 1 に示す液晶表示装置の T F T 基板の拡大平面図及び断面図である。

【図 3 - 1】図1、図 2 に示す T F T 基板の製造方法を説明するための断面図である。

【図 3 - 2】図1、図 2 に示す T F T 基板の製造方法を説明するための断面図である。

【図 4】本発明者による研究、解析を説明するための平面図及び断面図である。

【図 5】本発明者による検討を説明するための断面図である。

【図 6】液晶表示装置の製造方法の変形例を示す断面図である。

#### 【 符号の説明 】

#### 【 0 0 4 2 】

1 T F T 基板

20

2 T F T

3 対向基板

4 画素電極

6 ゲートバスライン

7 補助容量バスライン

8 ドレインバスライン

10 ガラス基板

12 ( ゲートバスライン用 ) 配線層

30

14 ゲート絶縁膜

16 動作半導体層

18 ( オーミックコンタクト用 ) 低抵抗半導体層

19 酸化シリコン膜

20 ( ソース / ドレイン用 ) 配線層

22 保護絶縁膜

30 オゾン水

40 マスク層

C H コンタクト孔

S ソース

D ドレイン

G ゲート

【図1】

(1A)

(1B)

1:TFT基板

2:TFT

4:画素電極

6:ゲートバスライン

7:補助容量バスライン

8:ドレインバスライン

【図2】

(2A)

(2B)

【図3-1】

【図3-2】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開平02-043739(JP,A)

特開平10-256155(JP,A)

特開2003-045801(JP,A)

特開2005-039026(JP,A)

特開平06-314698(JP,A)

特開平08-107212(JP,A)

特開平08-064835(JP,A)

特開平01-259565(JP,A)

国際公開第97/013177(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

H 01 L 29 / 786