(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6286228号

(P6286228)

(45) 発行日 平成30年2月28日(2018.2.28)

(24) 登録日 平成30年2月9日(2018.2.9)

(51) Int.Cl.

G 11 C 13/00 (2006.01)

F 1

G 11 C 13/00 340

請求項の数 15 (全 11 頁)

(21) 出願番号 特願2014-32846 (P2014-32846)

(22) 出願日 平成26年2月24日 (2014.2.24)

(65) 公開番号 特開2014-164793 (P2014-164793A)

(43) 公開日 平成26年9月8日 (2014.9.8)

審査請求日 平成29年2月23日 (2017.2.23)

(31) 優先権主張番号 13/776,886

(32) 優先日 平成25年2月26日 (2013.2.26)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

Seagate Technology

LLC

アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブールバード、10200

10200 South De Anza Blvd Cupertino CA

95014 United States of America

(74) 代理人 110001195

特許業務法人深見特許事務所

最終頁に続く

(54) 【発明の名称】 抵抗ベースのメモリの抵抗シフトおよび／またはノイズを予測するための転送機能を用いた方法

および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

方法であって、

抵抗ベースの不揮発性メモリの複数の領域の1つにおいて、既知のデータパターンを記憶する参照メモリブロックを読み取ることと、

2つ以上の作業負荷指標に応答して、前記参照メモリブロックの読み取りに基づいて、前記抵抗ベースの不揮発性メモリの前記領域の抵抗シフトを予測する転送機能を判定することと、

前記抵抗ベースの不揮発性メモリの動作の間、前記2つ以上の作業負荷指標を測定することと、

前記2つ以上の作業負荷指標を、前記転送機能に適用することと、

前記参照メモリブロックから分離しつつ前記複数の領域内で、メモリセルに影響するプログラム動作および読み取り動作の少なくとも1つのために使用されるしきい値抵抗をシフトするために、前記転送機能の結果を適用することとを含む、方法。

## 【請求項 2】

前記2つ以上の作業負荷指標は、保持時間、読み取りサイクル数、書き込みサイクル数、近隣データ値、および温度の少なくとも2つを含む、請求項1に記載の方法。

## 【請求項 3】

前記参照メモリブロックの前記読み取りは、前記抵抗ベースの不揮発性メモリの他のメモリブロックよりも高い分解能で、前記参照メモリブロックの前記値を読み取ることを含

む、請求項2に記載の方法。

**【請求項 4】**

前記転送機能は、前記参照メモリブロックについて検出されたノイズマージンの分布を用いて判定される、請求項2または請求項3に記載の方法。

**【請求項 5】**

前記抵抗ベースの不揮発性メモリは、相変化メモリおよび抵抗ランダムアクセスメモリの少なくとも1つを含む、請求項1から請求項4のいずれか1項に記載の方法。

**【請求項 6】**

請求項1から請求項5のいずれか1項に記載の前記方法を実行するために、プロセッサによって実行可能な命令を記憶する、非一時的コンピュータ可読媒体。 10

**【請求項 7】**

装置であって、

抵抗ベースの不揮発性メモリと連結されるように構成されるコントローラを備え、

前記コントローラは、

前記抵抗ベースの不揮発性メモリの複数の領域の1つにおいて、既知のデータパターンを記憶する参照メモリブロックを読み取ることと、

2つ以上の作業負荷指標に応答して、前記参照メモリブロックの読み取りに基づいて、前記抵抗ベースの不揮発性メモリの前記領域の抵抗シフトを予測する転送機能を判定することと、

前記抵抗ベースの不揮発性メモリの動作の間、前記2つ以上の作業負荷指標を測定することと、 20

前記転送機能に前記2つ以上の作業負荷指標を適用することと、

前記参照メモリブロックから分離しあつ前記複数の領域内で、メモリセルに影響するプログラム動作および読み取り動作の少なくとも1つのために使用されるしきい値抵抗をシフトするために前記転送機能の結果を適用することと、

を前記装置に実行させるように構成される、装置。

**【請求項 8】**

前記既知のデータパターンは、事前決定されたパターンを含む、請求項7に記載の装置。 30

**【請求項 9】**

前記既知のデータパターンは、信頼性をもって検索可能であることを確認するために余分の注意をもって記憶されたユーザデータを含む、請求項7に記載の装置。

**【請求項 10】**

前記既知のデータパターンは、一連のデータを生成するためのカウンタあるいはアルゴリズムの使用および前記参照メモリブロックのアドレスの少なくとも一方に基づいて導出可能なデータを含む、請求項7に記載の装置。

**【請求項 11】**

装置であって、

抵抗ベースの不揮発性メモリと連結されるように構成されるコントローラを備え、

前記コントローラは、

前記抵抗ベースの不揮発性メモリの複数の領域の1つにおいて、既知のデータパターンを記憶する参照メモリブロックを読み取ることと、

2つ以上の作業負荷指標に応答して、前記参照メモリブロックの読み取りに基づいて、前記抵抗ベースの不揮発性メモリの前記領域の抵抗ノイズ変化を予測する転送機能を判定することと、

前記抵抗ベースの不揮発性メモリの動作の間、前記2つ以上の作業負荷指標を測定することと、 40

前記転送機能に前記2つ以上の作業負荷指標を適用することと、

前記参照メモリブロックから分離しあつ前記複数の領域内で、メモリセルに影響するプログラム動作および読み取り動作の少なくとも1つのために使用されるしきい値抵抗を 50

判定するために前記転送機能の結果を適用することと、

を前記装置に実行させるように構成される、装置。

**【請求項 1 2】**

前記 2 つ以上の作業負荷指標は、保持時間、読み取りサイクル数、書き込みサイクル数、近隣データ値、および温度の少なくとも 2 つを含む、請求項 7 から請求項 1 1 のいずれか 1 項に記載の装置。

**【請求項 1 3】**

前記参照メモリブロックの前記読み取りは、前記抵抗ベースの不揮発性メモリの他のメモリブロックよりも高い分解能で前記参照メモリブロックの前記値を読み取ることを含む、請求項 7 から請求項 1 2 のいずれか 1 項に記載の装置。 10

**【請求項 1 4】**

前記転送機能は、前記参照メモリブロックについて検出されるノイズマージンの分布を用いて判定される、請求項 7 から請求項 1 3 のいずれか 1 項に記載の装置。

**【請求項 1 5】**

前記抵抗ベースの不揮発性メモリは、相変化メモリおよび抵抗ランダムアクセスメモリの少なくとも 1 つを備える、請求項 7 から請求項 1 4 のいずれか 1 項に記載の装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、抵抗ベースのメモリの抵抗シフトおよび / またはノイズを予測するための転送機能を用いた方法および装置に関する。 20

**【発明の概要】**

**【課題を解決するための手段】**

**【0 0 0 2】**

本開示は、抵抗ベースのメモリの抵抗シフトを予測する転送機能を用いることに関する。 1 つの実施形態では、方法および装置が、抵抗ベースの不揮発性メモリのメモリセルに影響する 2 つ以上の作業負荷指標を測定することを容易にする。 2 つ以上の作業負荷指標が、2 つ以上の作業負荷指標に基づいて抵抗シフトおよび / または抵抗ノイズ変化を予測する転送機能に適用される。 転送機能の結果が、メモリセルに影響するプログラム動作および読み取り動作の少なくとも 1 つのために用いられるしきい値抵抗をシフトおよび / または判定するために適用される。 メモリセルのエラー率はその結果として削減される。 30

**【0 0 0 3】**

これらおよびさまざまな実施形態の他の特徴および様様は、以下の詳細な論議および付随図面を考慮して理解され得るであろう。

**【0 0 0 4】**

以下の図においては、複数の図中で類似 / 同一構成要素を識別するために同一参照番号が使用される。

**【図面の簡単な説明】**

**【0 0 0 5】**

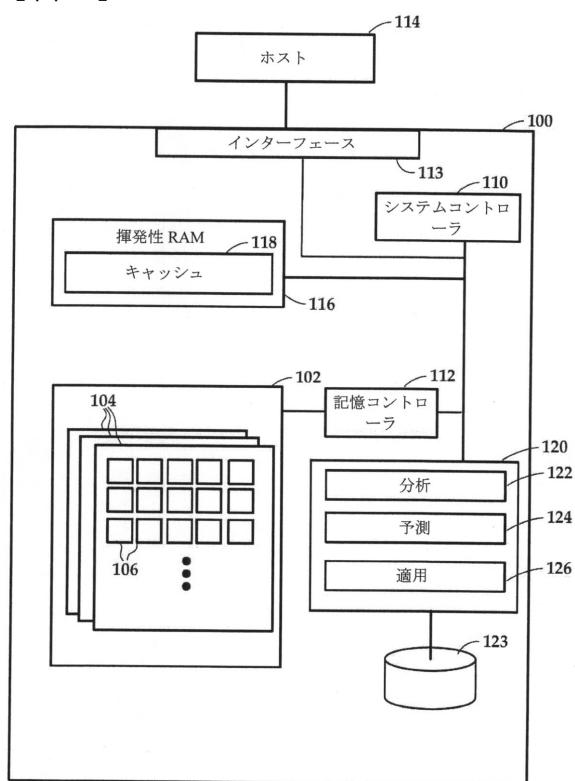

**【図 1】** 実施形態例に従う装置の構成図である。

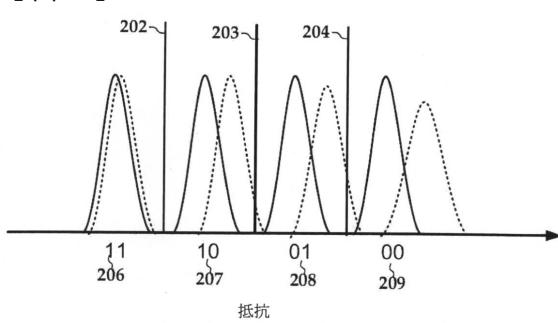

**【図 2】** 実施形態例に従う多重レベルメモリコールにおける抵抗シフトを図解する構成図である。

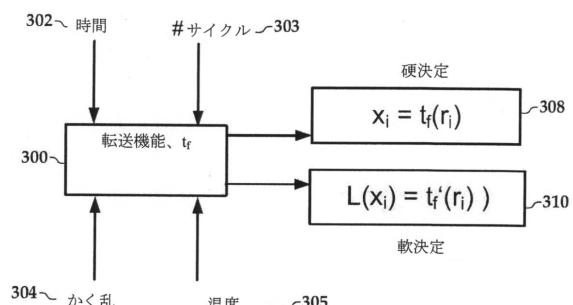

**【図 3】** 実施形態例に従う転送機能を図解する構成図である。

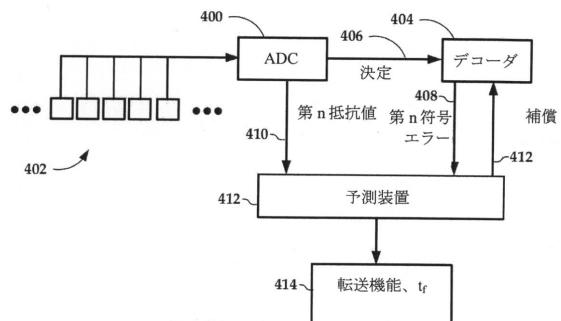

**【図 4】** 実施形態例に従う抵抗シフトを予測するための読み取りエラーの使用を図解する構成図である。

**【図 5】** 実施形態例に従う多重レベルメモリコールにおけるノイズマージンを図解する構成図である。

**【図 6】** 実施形態例に従う抵抗シフトを判定するための参照セルの使用を図解する構成図である。

**【図 7】** 実施形態例に従う方法を図解するフローチャートである。 50

【図8】実施形態例に従う方法を図解するフローチャートである。

【発明を実施するための形態】

【0006】

さまざまな実施形態例の以下の記述において、本明細書の一部を形成する付随図に対して参照が行われ、さまざまな実施形態例が図解によって示されている。本明細書中の請求項の範囲から逸脱することなく構造上および動作上の変更をなしうるために他の実施形態も利用可能であることが理解されるであろう。

【0007】

本開示は、抵抗ベースのメモリを用いる永続的データ記憶装置に概して関する。概して、抵抗ベースのメモリは永続的に変更可能な抵抗値を備えるセルを使用してデータを記憶する。多数の要因がセルの抵抗値における短期および長期シフトを生じ得、データが読み戻される時にビットエラーにつながる。抵抗ドリフトの予測、見積もり、および補償を行い、それによってビットエラー率を削減するために使用可能な装置および方法が以下に記述される。

10

【0008】

図1において、構成図が実施形態例に従うデータ記憶装置100を図解する。この装置100はソリッドステートメモリの任意の組み合わせを利用するソリッドステートドライブ(SSD)(あるいはその副構成要素)として構成し得る。装置100の特徴は、ソリッドステートメモリおよび磁気ディスクの組み合わせを使用するハイブリッドドライブ等のハードドライブ装置の他のタイプに適応し得る。装置100の特徴は、標準ハードドライブデータインターフェースを利用しない特殊用途ソリッドステートおよび/またはディスクデータ記憶装置(あるいはその副構成要素)にも適用し得る。

20

【0009】

装置100は、装置100の不揮発性メモリの一部あるいはすべてを含む1つ以上のメモリユニット102を含み得る。メモリユニット102は、1つ以上の各分散物理ユニット104、例えばメモリチップ、を含み得る。物理ユニット104のそれぞれの中で、メモリはより小さいブロック106にグループ化され得る。この例では単一メモリユニット102が示されているが、本明細書中で記述される概念はそれぞれ異なる媒体タイプのより多くのユニットを有する装置において採用し得る。

30

【0010】

装置100は、ホストインターフェース113を介してホスト114から受信される要求に対する役務を容易化する1つ以上のシステムコントローラ110を含み得る。システムコントローラ110は、論理アドレスを参照するホスト114からの読み取りあるいは書き込み要求を概して受信する。システムコントローラ110は論理アドレスを物理アドレスに翻訳し、メモリユニット102の適切な物理アドレスでそれぞれの読み取りあるいは書き込み動作を実施する。システムコントローラ110はメモリユニット102に影響する動作を実施するように記憶コントローラ112に指図する。

【0011】

記憶コントローラ112は、メモリユニット102に読み取りおよび書き込みを実施するための信号を適用する特殊コントローラである。記憶コントローラ112は、信号をメモリブロック106に、そして読み取りデータをブロック106から適用するために使用される、アナログ-デジタルコンバータ(ADC)およびデジタル-アナログコンバータ(DAC)を含み得る。記憶コントローラ112はエンコーダおよびデコーダを含み得、あるいは暗号化/復号化を別ユニット(図示されない)によって実施し得る。多重メモリユニット102が使用される場合は、特定メモリタイプに適切な読み取り/書き込み動作を実施するために、多重記憶コントローラ112を採用し得る。

40

【0012】

装置100は、特に、不揮発性メモリユニット102、103のための揮発性キャッシュ118のために使用され得る揮発性ランダムアクセスメモリ(RAM)116を含み得る。概して、揮発性キャッシュ118は階層的メモリ構造であり、不揮発性メモリ102

50

の各部分を反映するが、不揮発性メモリ 102 よりも迅速に読み取りおよび／または書き込み可能である。いくつかの状況については、例えば、短期間に読み取り／書き込み活動の反復に遭遇するデータについては、揮発性キャッシュ 118 は性能を上げる。

#### 【0013】

前述のとおり、メモリユニット 102 は、例えば、R e R A M あるいは P C M といった抵抗メモリを含む。抵抗メモリは、信号のセルへの適用によってシフトされ得る事前決定抵抗を概して示すメモリ要素（例えば、セル）を使用する。例えば、P C M セルは特定電圧の適用時に、アモルフォス、結晶、および中間状態と変化し（そして再び戻る）、そして抵抗はこれらの状態間で測定可能なように異なる。R R A M（登録商標）セルは、適切な電圧の適用によって、導電性経路の形成／除去が可能な誘電体を含み、これは導電体を通して検出される可変抵抗に帰結する。10

#### 【0014】

抵抗メモリセルは 1 ビット以上のデータを記憶し得る。1 ビットが各セルに記憶された場合、記憶されたデータの値は、セルの抵抗レベルを測定し、それが定義済みしきい値より上であるか下であるかを判定することによって判定される。同様にして、多重ビットは、セルあたり 2 以上のしきい値を定義し、検出することによって記憶可能である。多重ビットセルはより大きな記憶密度に帰結し得るが、より細かく抵抗測定を見定める必要があるために、エラーをより生じやすい。抵抗メモリセルが 1 ビットあるいは 2 ビット以上を記憶するかは、特定のセルがプログラミング電圧、近隣活動、時間の経過、および他の使用／環境要因に対してどのように応答するかの敏感な違いになり得る。20

#### 【0015】

抵抗メモリセルは、製造差異の理由によりプログラミング電圧に応答して相違を示し得る。いくつかの相違は、繰り返しプログラミングによるものと説明可能であり、例えば、第 1 レベルへのプログラミング、抵抗への読み返し、および目標抵抗が読み返されるまでの後のプログラミングレベルについて同じことを行うことである。しかしながら、例えば、熱影響により、プログラミング直後にセルがドリフトするいくつかのケースがあり得、そしてそのようなドリフトは各セル間で変化し得る。メモリセルの抵抗レベルはより長期にわたり数多くの要因によりシフトし得、例えば、温度、材料破壊、サイクル数、保持時間、読み取り／書き込みかく乱、近隣データ、等である。セルは、ノイズレベルの増加等の刺激に応答して他の変化と遭遇し得る。30

#### 【0016】

抵抗メモリセルの抵抗シフトおよび／またはノイズレベル増加は、信頼性減少を生じ得、例えば、追加工業訂正方策あるいは冗長性を要求する。これらのシフトは耐久性にも影響し、例えば、長期間記憶されたデータは重大なビットエラー率（B E R）を示し、および／または読み取り不能となる。これらのエラーは、メモリセルが 2 ビット以上記憶するように使用されたときにより一層著しくなり得る。抵抗のシフトおよび／またはノイズの増加を補償するための数多くの方法が存在し、適合エラー訂正コード、プログラムおよび読み取り挙動の修正、特定データ記憶形式の使用、および媒体の能動的管理を含む。

#### 【0017】

本開示は、ビットエラー率（B E R）を削減するための、抵抗ドリフトおよび／またはノイズレベルの予測、見積もり、および補償のための方法、システム、および装置に関する。抵抗のシフトおよびノイズレベルの増加の衝撃は、シフト／ノイズの予測および見積もり、ならびにその後の適切な最良しきい値の補償によって最小化可能である。図 1 で示されるように、記憶装置 100 は抵抗ベースの不揮発性メモリにおける B E R の削減を容易化する機能モジュール 120 を含む。分析モジュール 122 は、メモリユニット 102 の特定場所からの読み取りあるいはそこへの書き込み時に、データを集める。分析モジュール 122 は、A D C 値、ノイズマージン、ビットエラー等のデータを取得するために記憶コントローラ 112 とのインターフェースを取り得、このデータはデータベース 123 に記憶し得る。40

#### 【0018】

予測モジュール 124 は、メモリユニット 102 のいくつかあるいはすべての現在の状態について予測を行うために、分析モジュール 122 によって集められたデータを相互に関連付ける。相互に関連付けられたデータは、急いで判定し、あるいは定期的間隔でデータベース 123 に記憶し得る。アプリケーションモジュール 126 は、装置 100 の性能を改善するために、相互に関連付けられた予測データを適用する。アプリケーションモジュール 126 は分析モジュール 122 および / または予測モジュール 124 によって判定される 2 つ以上の作業負荷指標を見て、転送機能を判定する。転送機能は、データの読み返し、期待された抵抗シフトの補償、および性能改善、例えば B E R の低減、のときに記憶コントローラ 112 によって適用可能である。

## 【0019】

10

ここで図 2 を参照すると、図は実施形態例に従う多重レベル抵抗メモリセルの抵抗シフト例を図解する。水平軸は、セルの個体数から測定される抵抗値を表現する。しきい値 202 ~ 204 は 4 つの領域 206 ~ 209 を定義し、それぞれはセル内に記憶されるデータ符号と関連付けられている。実線で描かれた 4 つの分布は、最良分布（例えば、最小 B E R に帰結する）を表現し、そして点線で描かれた 4 つの分布は、全プログラムレベルでの抵抗シフトの効果を表現する。このケースでは、シフトは抵抗の平均的増加として帰結するが、他方向におけるシフトも可能である。この例は 2 - ビット / セル MLC メモリに関するものであるが、概念は、セルあたりより多くのあるいはより少ないビットを記憶するセルについても等しく適用可能である。

## 【0020】

20

抵抗のシフトを予測 / 見積るために使用可能な多数の方法が存在する。それらのアプローチは、まとめて、あるいは個々に使用可能である。図 3 の構成図に示されるように、実施形態例に従う多変量劣化 / 転送機能を使用可能である。転送機能 300 は、時間 302（例えば、保持時間 および / または 使用合計時間）、サイクル数 303、かく乱 304（例えば、近隣読み取り / 書き込み、近隣データ）、および温度 305 等のパラメータに基づいて計算可能である。これら入力値 302 ~ 305 は現行および / または歴史的（例えば、蓄積値）であり得る。

## 【0021】

転送機能 300 は、希望出力のタイプにより、多数の形式をとり得る。ブロック 308 によって示されるように、転送機能 300 は硬決定値を提供（あるいは提供時に使用）し、機能  $t_f(r)$  は、例えば図 2 に示されるような、入力 302 ~ 305 のいくつかの組み合わせに基づくシフトしきい値に基づく符号値  $\times_i$  ならびにベースライン値等、を提供する。ブロック 310 に示されるように、転送機能 300 は機能  $t_f(r)$  のログ見込率等の軟決定値を提供し得る（あるいは提供時に使用され得る）。これらの機能 308、310 においては、値  $r$  はセルから測定された抵抗の値を表し、 $\times$  はセル内に記憶されたデータの値を表す。

30

## 【0022】

転送機能 300 は、抵抗シフト（例えば、ノイズ偏差）の代わりに、あるいはそれに加えて、抵抗メモリセルのノイズレベル（例えば、変化）を予測するためにも使用し得る。例えば、図 3 を再び参照すると、等しくシフトされた分布の代わりに、分布は不均等にシフトされ、および / またはシフトされない場合もあり、分布それ自体はより幅が広くて（例えば、より大きな標準偏差を有する）ランダムノイズの増加を表示している。その様な偏差が予測可能である限り、図 3 に示されるように、それらはデータの暗号化を支援するために使用可能である。本明細書中に記述される方法および装置は転送機能を利用し、2 つ以上の作業負荷指標に応答する抵抗ノイズ変化を予測し、そして転送機能を用いてビットエラー率を改善することが可能であることが理解されるであろう。

40

## 【0023】

ここで図 4 を参照すると、構成図は、実施形態例に従う転送機能を形成するための入力の測定に関連する概念を図解する。ADC 400 は、メモリセル 402 から抵抗値を読み取るように構成される。デコーダ 404 は ADC 400 からのデータを使用し（軟あるいは

50

は硬決定値 406 として)、セル 402 に記憶されるデータを復号化する。デコーダ 404 はデータの復号化時にエラー訂正を適用し、これが 1 つ以上の符号エラー 408 の判定に帰結し得る。現行データの状態 406 から入手される軟情報を使用してメモリの状態を予測可能である。

#### 【0024】

予測構成要素 412 は抵抗シフトを予測するために符号エラー 408 および / または軟情報 406 を使用可能である。例えば、符号 - A 符号 - B エラー 対 符号 - B 符号 - A エラーの測定は抵抗値のシフトおよび / またはノイズレベルを見積もり可能である。ADC 400 は例えば異なるしきい値を用いて、実抵抗値 410 を提供し得る。ADC 400 は、より細かい分解能のしきい値および / または多重読み取りによりサンプルデータ 410 を提供するように構成し得る。ADC は、異なるしきい値で多重回数実行することにより、単一しきい値からエミュレートも可能である。10

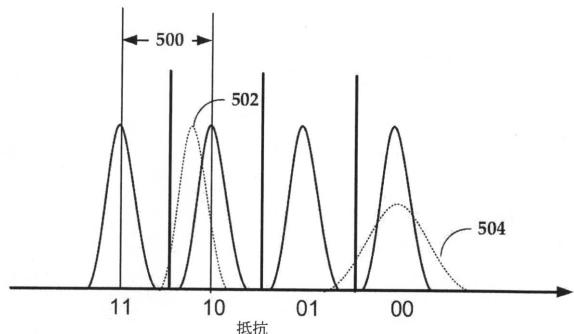

#### 【0025】

ノイズマージンの分布を使用して、抵抗シフトを見積もり可能である。メモリセルのノイズマージンは、ノイズによって状態変化が誘発される前に、メモリセル上に課すことが可能なノイズ量を概して言う。多重レベルセルに関するノイズマージン例は、図 5 に示されている。値 500 はノイズマージンに比例している。例えば、近隣抵抗値分布の平均間の距離 500 が大きくなれば、ノイズマージンは大きくなる。ノイズマージンの減少は、抵抗シフトの暗示となり得、シフトされた分布 502 によって示されるとおりである。ノイズマージンの減少もノイズ増加の暗示となり得、点線で描かれるシフトされた分布 504 に示されるとおりである。分布 504 の平均値は依然としておよそわずかであるが、標準偏差が大きくなると、ノイズが記憶値の変化を生じるであろう見込みの増加に帰結する。20

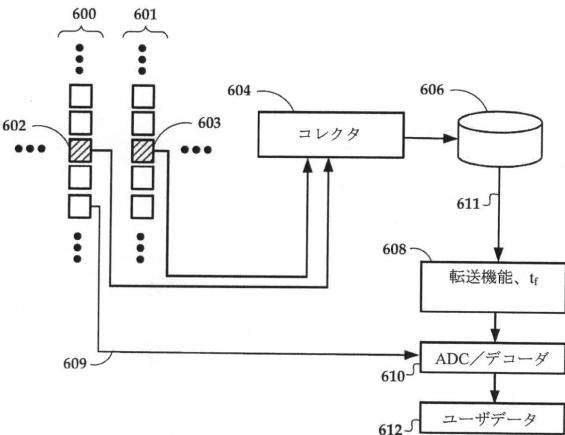

#### 【0026】

ここで図 6 を参照すると、構成図が、実施形態例に従う既知データセットの使用を図解している。領域 600、601 は、レイヤ、チップ等のメモリの異なる領域を表す。ブロック 602、603 は領域 600、601 内のメモリ場所（例えば、個々のセル、セルグループ、ページ、等）を表す。ブロック 602、603 は、各領域 600、601 における抵抗シフトを特徴づけるために使用可能な既知データを記憶する。ブロック 602、603 内の既知データは、事前決定パターン、どこでも探索可能なデータ、導出可能なデータ（例えば、一連のデータを生成するためにカウンタあるいはアルゴリズムを使用し、セルのアドレスに基づく）、および / または信頼性をもって検索可能であることを確認するために注意をもって記憶されたユーザデータ（例えば、通常の ECC 暗号化より大きいおよび / または冗長的）を含み得る。30

#### 【0027】

コレクタモジュール 604 はブロック 602、603 からデータを読み取り、ブロック内の抵抗シフトの現行量を判定する。コレクタモジュール 604 は、実行時、カレンダ時刻、保持時間等に基づいて、反復してこの動作を実施できる。動作は、いくつかのシステム事象（例えば、ビットエラー率のしきい値）に応答して、および / またはユーザ要求に応答して実施し得る。コレクタモジュール 604 は図 4 に示され、記述されているよう 40 に、ADC およびデコーダからのデータを使用し、抵抗シフトの見積もりを判定し得る。参照メモリブロック 602、604 の値は、他のメモリブロックより高い分解能で読み取り得る（例えば、ADC 内に組み込まれたハードウェアサポートを介して）。

#### 【0028】

抵抗シフトデータ 606 を使用してその後の読み取りにおけるエラーを低くすることが可能である。例えば、領域 600 からの読み取り要求 609 に応答し、抵抗シフトおよび / またはノイズデータ 611 はデータベースから入手され、ユーザデータ 612 を入手するために ADC および / またはデコーダを介して（ともにブロック 610 として表現される）適用され得る転送機能 608 を形成するために使用される。抵抗シフトおよび / またはノイズデータ 611 はメモリの参照ブロックあるいは他のブロックについて検出される50

ノイズマージンの分布をも含み得る。

**【0029】**

転送機能 608 に入力されるデータ 611 は、セルあるいは、保持時間、読み取りサイクル回数、書き込みサイクル回数、近隣データ値、および温度等の、要求 609 を介して読み取られるセル特定の作業負荷指標をも含み得る。これらの作業負荷指標はデータベース 606 上にあるいはいずれかに記憶され得る。例えば、作業負荷指標は、特定事象、影響を受けるセルおよび / または近隣セルの読み込み / 書き込みサイクル、経過時間、等が生じたときに増分されるカウンタを介して追跡され得る。ハードウェアサポートの使用は、抵抗追跡を自動化するために使用され得る。

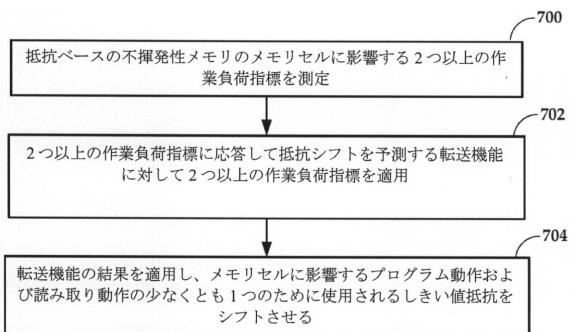

**【0030】**

ここで図 7 を参照すると、フローチャートが実施形態例に従う方法を図解する。この方法は影響する抵抗ベースの不揮発性メモリのメモリセル 2つ以上の作業負荷指標を測定すること 700 を含む。2つ以上の作業負荷指標は、2つ以上の作業負荷指標に基づいて抵抗シフトを予測する転送機能に対して適用される 702。転送機能の結果は、メモリセルに影響するプログラム動作および読み取り動作の少なくとも 1つのために使用されるしきい値抵抗をシフトさせるために適用される 704。このシフトはメモリセルのエラー率を削減する。

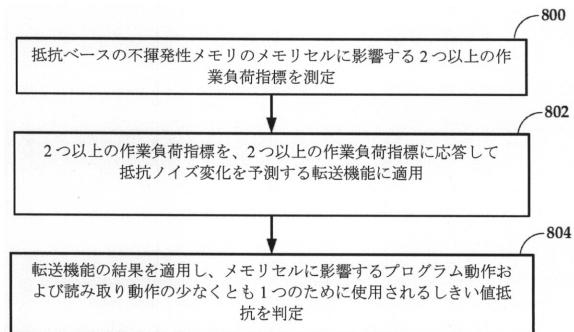

**【0031】**

ここで図 8 を参照すると、フローチャートは実施形態例に従う方法を図解する。この方法は、抵抗ベースの不揮発性メモリのメモリセルに影響する 2つ以上の作業負荷指標を測定すること 800 を含む。2つ以上の作業負荷指標は 2つ以上の作業負荷指標に応答して抵抗ノイズ変化を予測する転送機能に対して適用される 802。転送機能の結果は、メモリセルに影響するプログラム動作および読み取り動作の少なくとも 1つのために使用されるしきい値抵抗を判定するために適用される 804。このしきい値機能はメモリセルのエラー率を削減する。

**【0032】**

図 7 および 8 の方法において、抵抗ベースの不揮発性メモリは、相変化メモリおよび / または抵抗ランダムアクセスメモリを含み得る。2つ以上の作業負荷指標は、保持時間、読み取りサイクル数、書き込みサイクル数、近隣データ値、および温度の少なくとも 2つを含み得る。転送機能は、抵抗ベースの不揮発性メモリの参考メモリブロックの読み取りに応答して判定し得る。この参考メモリブロックは既知データパターンを記憶する。その様なケースでは、参考メモリブロックの読み取りは、抵抗ベースの不揮発性メモリの他のメモリブロックより高い分解能で、参考メモリブロックの値を読み取ることを含み得る。そのようなケースでは、転送機能は、参考メモリブロックについて検出されるノイズマージンの分布を用いて判定され得る。

**【0033】**

上述のさまざまな実施形態は、特定結果を提供するために相互作用する回路および / またはソフトウェアモジュールを用いて実施され得る。コンピュータ技術における当業者は、当該技術において一般的に知られる知識を用いて、モジュールレベルにおいてあるいは全体として、記述されるそのような機能を容易に実装可能である。例えば、本明細書中に図解されるフローチャートは、プロセッサによる実行のために、論理回路あるいはコンピュータ可読命令 / コードを創生するために使用し得る。そのような命令はコンピュータ可読媒体上に記憶可能で、従来技術で知られているように、実行のためにプロセッサへ転送し得る。上に示される構造および手順は、上述のように、データ記憶装置におけるキャッシング管理を容易化するために使用可能な実施形態例の代表に過ぎない。

**【0034】**

実施形態例の上記記述は、図解および記述の目的のために提供されたものである。それらは排他的であったり、あるいは発明概念を開示される形式に精密に限定する意図はない。前述の教示に照らして、多数の修正および変種が可能である。開示された実施形態の任意のあるいはすべての特徴は、個々にあるいは任意の組み合わせによって適用可能であり

10

20

30

40

50

、限定を意味するものではなく、純粹に図解である。範囲はこの詳細記述によって限定されるものではなく、本明細書付属の請求項によって判定されることが意図されている。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

---

フロントページの続き

(72)発明者 アラ・パタポウシャン

アメリカ合衆国、01748 マサチューセッツ州、ホプキントン、ライフォード・ロード、5

(72)発明者 ライアン・ジェイムズ・ゴス

アメリカ合衆国、55372 ミネソタ州、プライアー・レイク、ポンズエッジ・レーン、508

8

(72)発明者 アントワーヌ・クエール

アメリカ合衆国、55124 ミネソタ州、アップル・バレー、ドウェラーズ・ウェイ、1557

8

審査官 後藤 彰

(56)参考文献 特開2010-055699(JP, A)

国際公開第2007/034542(WO, A1)

特開2004-273110(JP, A)

特開2004-185745(JP, A)

特開2008-171543(JP, A)

特開2012-094234(JP, A)

特表2012-518862(JP, A)

米国特許出願公開第2010/0214829(US, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 13/00