## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-190951 (P2006-190951A)

(43) 公開日 平成18年7月20日(2006.7.20)

(51) Int.C1.

$\mathbf{F}$  L

テーマコード (参考)

HO1L 33/00

(2006, 01)

HO1L 33/00

N

5FO41

審査請求 有 請求項の数 28 〇L (全 18 頁)

(21) 出願番号 特願2005-195643 (P2005-195643)

(22) 出願日 平成17年7月5日 (2005.7.5)

(31) 優先権主張番号 093141222

(32) 優先日 平成16年12月29日 (2004.12.29)

(33) 優先権主張国 台湾 (TW)

(71) 出願人 390023582

財団法人工業技術研究院

INDUSTRIAL TECHNOLO GY RESEARCH INSTITU

ΤE

台灣新竹縣竹東鎮中興路四段195號 195 Chung Hsing Rd. , Sec. 4, Chutung, Hsin -Chu, Taiwan R. O. C

(74)代理人 100082418

弁理士 山口 朔生

(72) 発明者 陳明鴻

台湾新竹県竹東鎮中興路四段195號

(72) 発明者 温士逸

台灣新竹県竹東鎮中興路四段195號

最終頁に続く

(54) 【発明の名称】発光ダイオードパッケージ及びその製造プロセス

## (57)【要約】 (修正有)

【課題】容易な製造プロセスで放熱性が良好な発光ダイオード用パッケージを提供する。

【解決手段】発光ダイオード(LED)パッケージ及びその製造プロセスは、二つのシリコンベース材料とそれらの間に介在される絶縁層を備えるシリコン・オン・インシュレータ(SOI)基板を含む。シリコン・オン・インシュレータ基板を正極と負極の接触面に分割するために、シリコン・オン・インシュレータ基板の二つのシリコンベース材料は、各々エッチングされて反射キャビティと絶縁トレンチを形成する。次に、複数の金属ラインが、前記二つのシリコンベース材料を電気的に接続するために形成され、それによって、LEDチップが反射キャビティにマウントされ金属ラインによってシリコン・オン・インシュレータ基板の対応する電極に電気的に接続することが出来る。

【効果】このように、熱抵抗と熱分散の特性が改良されてプロセスが簡単化される。

【選択図】 図3D

## 【特許請求の範囲】

## 【請求項1】

発光ダイオード(LED)パッケージを製造するプロセスであって、

第1のシリコンベース材料と、第2のシリコンベース材料と、前記シリコンベース材料 同士間に介在される絶縁層とを含むシリコン・オン・インシュレータ(SOI)基板を提供するステップと、

シリコン・オン・インシュレータ基板の第1のシリコンベース材料と第2のシリコンベース材料を各々エッチングし、反射キャビティと絶縁トレンチを形成するステップと、を備え、前記絶縁トレンチは、シリコン・オン・インシュレータ基板を正極と負極の接触面に分割し、

シリコン・オン・インシュレータ基板上に複数の金属ラインを形成するステップと、

シリコン・オン・インシュレータの反射キャビティ上にLEDチップをマウントするステップと、備え、LEDチップの正極と負極が金属ラインによってシリコン・オン・インシュレータ基板の対応する電極に電気的に接続する、ことを特徴とする発光ダイオードパッケージ製造プロセス。

## 【請求項2】

前記第1のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、請求項1に記載のプロセス。

### 【請求項3】

前記第2のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、請求項1に記載のプロセス。

## 【請求項4】

前記シリコン・オン・インシュレータ基板は、As、Sb及びPで重ドープされ且つ 0.1 / cmよりも小さな抵抗値を有するNタイプ及びPタイプである前記第 1 のシリコンベース材料及び第 2 のシリコンベース材料よりなる、請求項 1 に記載のプロセス。

## 【請求項5】

前記金属ラインは、Ag、Au、Cu、Al、Pt、Cr、Ni及び上記元素よりなる合金よりなる群から選択される材料よりなる、請求項1に記載のプロセス。

## 【請求項6】

前記反射キャビティは、〈100〉結晶方位を有する前記第1のシリコンベース材料をエッチングすることによって傾斜面が形成される、請求項1に記載のプロセス。

## 【請求項7】

前記反射キャビティは、エッチングのために < 100 > 結晶方位を有する前記第1のシリコンベース材料をドライエッチング又は選択することによって垂直面が形成される、請求項1に記載のプロセス。

## 【請求項8】

前記LEDチップをマウントするステップ後、カプセル化エポキシを使用して前記反射 キャビティを被覆し充填するステップを更に備える、請求項1に記載のプロセス。

## 【請求頂9】

前記カプセル化エポキシは、少なくとも一つのレンズを形成する、請求項 8 に記載のプ 40 ロセス。

## 【請求項10】

前記絶縁トレンチを形成するステップは、絶縁トレンチを強化するためにシリコン・オン・インシュレータ基板を酸化することによって前記絶縁トレンチに酸化層を形成するステップを更に備える、請求項 1 に記載のプロセス。

## 【請求項11】

前記絶縁トレンチは、一つよりも多い、請求項10に記載のプロセス。

## 【請求項12】

前記LEDチップは、一つよりも多い、請求項11に記載のプロセス。

## 【請求項13】

50

10

20

20

30

50

前記絶縁トレンチに酸化層を形成するステップは、前記絶縁トレンチを介して伝導性ビアを形成するステップを更に備える、請求項12に記載のプロセス。

## 【請求項14】

前記LEDチップは、前記伝導性ビアを介して直列、並列又は並直列に互いに接続される、請求項13に記載のプロセス。

## 【請求項15】

発光ダイオード(LED)パッケージであって、

第1のシリコンベース材料と、第2のシリコンベース材料と、前記シリコンベース材料 同士間に介在される絶縁層とを含むシリコン・オン・インシュレータ基板を備え、第1の シリコンベース材料上に反射キャビティがマウントされ、反射キャビティの底部がシリコ ン・オン・インシュレータ基板を正極と負極に分割するための絶縁トレンチを有すると共 にシリコン・オン・インシュレータ基板が複数の金属ラインを有し、

反射キャビティにあるLEDチップを備え、LEDチップの正極と負極が金属ラインによって各々シリコン・オン・インシュレータ基板の対応する電極に電気的に接続することを特徴とする発光ダイオードパッケージ。

## 【請求項16】

前記第1のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、請求項15に記載のパッケージ。

### 【請求項17】

前記第2のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、請求項15に記載のパッケージ。

#### 【請求項18】

前記シリコン・オン・インシュレータ基板は、As、Sb及びPで重ドープされ且つ 0.1 / cmよりも小さな抵抗値を有するNタイプ及びPタイプである前記第 1 のシリコンベース材料及び第 2 のシリコンベース材料を含む、請求項 1 5 に記載のパッケージ。

## 【請求項19】

前記金属ラインは、Ag、Au、Cu、Al、Pt、Cr、Ni及び上記元素よりなる合金よりなる群から選択される材料よりなる、請求項15に記載のパッケージ。

## 【請求項20】

前記反射キャビティは、〈100〉結晶方位を有する前記第1のシリコンベース材料をエッチングすることによって傾斜面が形成される、請求項15に記載のパッケージ。

## 【請求項21】

前記反射キャビティは、エッチングのために < 100 > 結晶方位を有する前記第1のシリコンベース材料をドライエッチング又は選択することによって垂直面が形成される、請求項15記載のパッケージ。

## 【請求項22】

前記反射キャビティを被覆し充填するカプセル化エポキシを更に備える、請求項 1 5 に記載のパッケージ。

## 【請求項23】

前記カプセル化エポキシは、少なくとも一つのレンズを形成する、請求項 2 2 に記載の 40 パッケージ。

## 【請求項24】

前記絶縁トレンチの強化のために前記絶縁トレンチに酸化層を更に備える請求項15に記載のパッケージ。

## 【請求項25】

前記絶縁トレンチは、一つよりも多い、請求項24に記載のパッケージ。

## 【請求項26】

前記LEDチップは、一つよりも多い、請求項25に記載のパッケージ。

## 【請求項27】

前記絶縁トレンチに伝導性ビアを更に備える、請求項26に記載のパッケージ。

## 【請求項28】

前記LEDチップは、前記導電性ビアを介して直列、並列又は並直列接続で互いに接続 する、請求項27に記載のパッケージ。

【発明の詳細な説明】

## 【技術分野】

## [00001]

本発明は、発光ダイオード(LED)パッケージ及びその製造プロセスに係わり、特に 、 基 板 と し て シ リ コ ン ・ オ ン ・ イ ン シ ュ レ ー タ を 使 用 す る 発 光 ダ イ オ ー ド パ ッ ケ ー ジ 及 び その製造プロセスに関する。

## 【背景技術】

## [0002]

従来のSMDLED(表面実装型デバイスLED)パッケージは、リードフレームタイ プと回路ボードタイプの二つのタイプを含む。リードフレームタイプでは、金属フレーム と熱抵抗プラスチックを使用してLEDチップを固定するために使用される、ベース形成 用モールディングを射出する。回路ボードタイプでは、基板として複合回路ボードを使用 し、次にチップ固定、ワイヤボンディング、シールドのステップを続ける。二つのタイプ は、共に、低熱抵抗のような欠点があり、その結果、特に、SMD LEDと他の回路ボ ードとの接合に高温炉処理(約250乃至300 )を必要とする場合に、SMD LE Dの欠陥を引き起こす。他の欠点は、低熱分散である。特に、高電力LEDの場合、LE Dの動作中に熱が蓄積する。温度上昇は、発光効率及びLEDの品質に影響を及ぼす。更 に、従来のSMDLED製造において、SMD LEDをスケールダウンしながら、反射 キャビティを製造することは困難である。

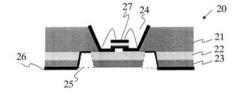

## [0003]

従来の技術では、LEDをパッケージ化するプロセスを提供している。図1に示される ように、従来の技術は、パッケージ基板としてシリコン基板を使用している。シリコン基 板 8 の前面は、キャビティをエッチングするためのスペクトル結晶方位を有し、シリコン 基 板 8 の 背 面 は 、 ス ル ー ホ ー ル 電 極 1 3 を 形 成 す る た め に 使 用 さ れ る 。 絶 縁 層 1 5 、 反 射 層16、及び電極層17と18が形成された後に、LEDチップ3を付着するためのベー スが形成される。LEDプロセスは、チップ固定、ワイヤボンディング、シーリング及び カッティングのプロセス後、完了される。この技術は、良好な熱抵抗、反射キャビティ製 造の容易さ及び良好な熱分散の利点を有し、それによって、SMDLEDパッケージング の従来のプロセスが改良される。しかしながら、この技術では、絶縁層を成長するために 複数の炉プロセスが必要であり、そのため、この技術を複雑なものにしている。このよう に、熱抵抗及び熱除去特性を改良し、且つ反射キャビティ製造における問題を解決するL EDパッケージングのより簡単なプロセスが必要である。

## 【発明の開示】

【発明が解決しようとする課題】

## [0004]

本発明の目的は、シリコン・オン・インシュレータ(SOI)を基板として形成し、反 射キャビティをシリコン・オン・インシュレータ(SOI)基板上に形成してLEDを配 する、発光ダイオード(LED)パッケージ及びその製造プロセスを提供することである S O I 基 板 上 の 絶 縁 層 に よ っ て 絶 縁 が 行 わ れ る 。 従 っ て 、 絶 縁 層 を 成 長 さ せ る 更 な る 炉 プロセスを必要とはしない。このように、良好な熱抵抗、反射キャビティ製造の容易さ、 良好な熱分散、及びより容易な処理である利点が達成される。

## 【課題を解決するための手段】

## [00005]

上記目的を達成するために、発光ダイオード(LED)パッケージを製造するプロセス が開示される。最初に、シリコン・オン・インシュレータ(SOI)基板が提供される。 シ リ コ ン ・ オ ン ・ イ ン シ ュ レ ー 夕 基 板 は 、 第 1 の シ リ コ ン べ ー ス 材 料 と 、 第 2 の シ リ コ ン ベース材料と、これらのシリコンベース材料同士間に介在される絶縁層とを含む。次に、

10

20

30

40

30

40

50

シリコン・オン・インシュレータ基板の第1のシリコンベース材料と第2のシリコンベース材料とは、エッチングされて、各々、反射キャビティと絶縁トレンチを形成する。絶縁トレンチは、シリコン・オン・インシュレータ基板を正極と負極の接触面に分割する。次に、複数組の金属ラインがシリコン・オン・インシュレータ基板上に形成され、且つLEDチップが反射キャビティにマウントされる。LEDチップの正極と負極は、金属ラインによってシリコン・オン・インシュレータ基板の対応する電極に電気的に接続する。

[0006]

上記目的を達成するために、開示された発光ダイオード(LED)パッケージは、第1のシリコンベース材料と、第2のシリコンベース材料と、これらのシリコンベース材料同士間に介在される絶縁層とを含むシリコン・オン・インシュレータ基板を備え、反射キャビティが、第1のシリコンベース材料上にマウントされ、絶縁トレンチが、反射キャビティの底部に配置され、この絶縁トレンチが、この基板を正極と負極の接触面に分割し、シリコン・オン・インシュレータ基板上には複数の金属ラインがあり、且つこの発光ダイオードパッケージは、LEDチップを備え、このチップは、反射キャビティ上にあり、LEDチップの正極と負極が、金属ラインによってシリコン・オン・インシュレータ基板の対応する電極に各々電気的に接続する。

[0007]

本願の第1発明は、発光ダイオード(LED)パッケージを製造するプロセスであって、第1のシリコンベース材料と、第2のシリコンベース材料と、前記シリコンベース材料に、第1のシリコンベース材料と、前記シリコンベース材料には、シリコン・オン・インシュレータ(SOI)基板を提供するステップと、シリコン・オン・インシュレータ基板の第1のシリコンベース材料を各々エッチングし、反射キャビティと絶縁トレンチを形成するステップと、を備え、前記絶縁トレンチは、シリコン・オン・インシュレータ基板上に複数の金属ラインを形成するステップと、シリコン・オン・インシュレータの反射キャビティ上にLEDチップをマウントするステップと、備え、LEDチップの正極と負極が金属ラインによってシリコン・オン・インシュレータ基板の対応する電極に電気的に接続する、ことを特徴とする発光ダイオードパッケージ製造プロセスを提供する。

本願の第2発明は、前記第1のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、第1発明に記載のプロセスを提供する。

本願の第3発明は、前記第2のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、第1発明に記載のプロセスを提供する。

本願の第4発明は前記シリコン・オン・インシュレータ基板は、As、Sb及びPで重ドープされ且つ0.1 / cmよりも小さな抵抗値を有するNタイプ及びPタイプである前記第1のシリコンベース材料及び第2のシリコンベース材料よりなる、第1発明に記載のプロセスを提供する。

本願の第5発明は、前記金属ラインは、Ag、Au、Cu、Al、Pt、Cr、Ni及び上記元素よりなる合金よりなる群から選択される材料よりなる、第1発明に記載のプロセスを提供する。

本願の第6発明は、前記反射キャビティは、<100>結晶方位を有する前記第1のシリコンベース材料をエッチングすることによって傾斜面が形成される、第1発明に記載のプロセスを提供する。

本願の第7発明は、前記反射キャビティは、エッチングのために<100>結晶方位を有する前記第1のシリコンベース材料をドライエッチング又は選択することによって垂直面が形成される、請求項1に記載のプロセスを提供する。

本願の第8発明は、前記LEDチップをマウントするステップ後、カプセル化エポキシを使用して前記反射キャビティを被覆し充填するステップを更に備える、第1発明に記載のプロセスを提供する。

本願の第9発明は、前記カプセル化エポキシは、少なくとも一つのレンズを形成する、 、請求項1に記載のプロセスを提供する。第8発明に記載のプロセスを提供する。 本願の第10発明は、前記絶縁トレンチを形成するステップは、絶縁トレンチを強化するためにシリコン・オン・インシュレータ基板を酸化することによって前記絶縁トレンチに酸化層を形成するステップを更に備える、第1発明に記載のプロセスを提供する。

本願の第11発明は、前記絶縁トレンチは、一つよりも多い、第10発明に記載のプロセスを提供する。

本願の第12発明は、前記LEDチップは、一つよりも多い、第11発明に記載のプロセスを提供する。

本願の第13発明は、前記絶縁トレンチに酸化層を形成するステップは、前記絶縁トレンチを介して伝導性ビアを形成するステップを更に備える、第12発明に記載のプロセスを提供する。

本願の第14発明は、前記 L E D チップは、前記伝導性ビアを介して直列、並列又は並直列に互いに接続される、第13発明に記載のプロセスを提供する。

## [00008]

本願の第15発明は、発光ダイオード(LED)パッケージであって、第1のシリコンベース材料と、第2のシリコンベース材料と、前記シリコンベース材料同士間に介在される絶縁層とを含むシリコン・オン・インシュレータ基板を備え、第1のシリコンベース材料上に反射キャビティがマウントされ、反射キャビティの底部がシリコン・オン・インシュレータ基板を正極と負極に分割するための絶縁トレンチを有すると共にシリコン・オン・インシュレータ基板が複数の金属ラインを有し、反射キャビティにあるLEDチップを備え、LEDチップの正極と負極が金属ラインによって各々シリコン・オン・インシュレータ基板の対応する電極に電気的に接続することを特徴とする発光ダイオードパッケージを提供する。

本願の第16発明は、前記第1のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、第15発明に記載のパッケージを提供する。

本願の第17発明は、前記第2のシリコンベース材料は、低抵抗半導体又は高抵抗半導体である、第15発明に記載のパッケージを提供する。

本願の第18発明は、前記シリコン・オン・インシュレータ基板は、As、Sb及びPで重ドープされ且つ0.1 / c mよりも小さな抵抗値を有するNタイプ及びPタイプである前記第1のシリコンベース材料及び第2のシリコンベース材料を含む、第15発明に記載のパッケージを提供する。

本願の第19発明は、前記金属ラインは、Ag、Au、Cu、Al、Pt、Cr、Ni及び上記元素よりなる合金よりなる群から選択される材料よりなる、第15発明に記載のパッケージを提供する。

本願の第20発明は、前記反射キャビティは、<100>結晶方位を有する前記第1のシリコンベース材料をエッチングすることによって傾斜面が形成される、第15発明に記載のパッケージを提供する。

本願の第21発明は、前記反射キャビティは、エッチングのために<100 > 結晶方位を有する前記第1のシリコンベース材料をドライエッチング又は選択することによって垂直面が形成される、第15発明に記載のパッケージを提供する。

本願の第22発明は、前記反射キャビティを被覆し充填するカプセル化エポキシを更に備える、第15発明に記載のパッケージを提供する。

本願の第 2 3 発明は、前記カプセル化エポキシは、少なくとも一つのレンズを形成する、第 2 2 発明に記載のパッケージを提供する。

本願の第24発明は、前記絶縁トレンチの強化のために前記絶縁トレンチに酸化層を更に備える、第15発明に記載のパッケージを提供する。

本願の第25発明は、前記絶縁トレンチは、一つよりも多い、第24発明に記載のパッケージを提供する。

本願の第26発明は、前記LEDチップは、一つよりも多い、第25発明に記載のパッケージを提供する。

本願の第27発明は、前記絶縁トレンチに伝導性ビアを更に備える、第26発明に記載

10

20

30

40

20

30

40

50

のパッケージを提供する。

本願の第28発明は、前記LEDチップは、前記導電性ビアを介して直列、並列又は並直列接続で互いに接続する、第27発明に記載のパッケージを提供する。

## 【発明の効果】

## [0009]

従って、絶縁層を成長させる更なる炉プロセスを必要とはしない。このように、良好な熱抵抗、反射キャビティ製造の容易さ、良好な熱分散、及びより容易な処理である利点が達成される。

### 【発明を実施するための最良の形態】

#### [0010]

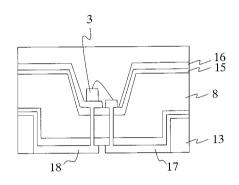

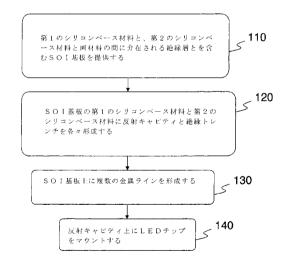

本発明の第1の実施の形態のフロー図である図2を参照する。このプロセスは、以下のステップを含む。最初に、第1のシリコンベース材料、第2のシリコンベース材料、及びそれらの間の絶縁層を含むシリコン・オン・インシュレータ(SOI)基板が、提供される(ステップ110)。次に、反射キャビティと絶縁トレンチが第1のシリコンベース材料と第2のシリコンベース材料をLEDチップに電気的に接続するために、金属ラインが、SOI基板上に形成される(ステップ130)。次に、LEDチップが、反射キャビティ上に配されてSOI基板の電極に電気的に接続し、これらの電極は、金属ラインによって外部に接続するために使用される(ステップ140)。

## [0011]

本発明のより詳細な記述のために、本発明の第1の実施の形態が、以下で記述される。 プロセスの予想横断面図である図3A乃至図3Dを参照する。

## [0012]

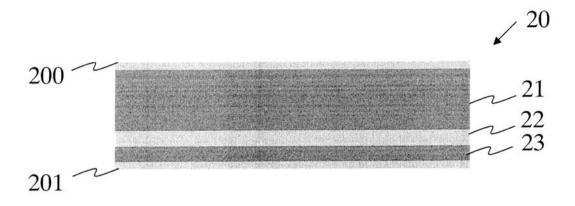

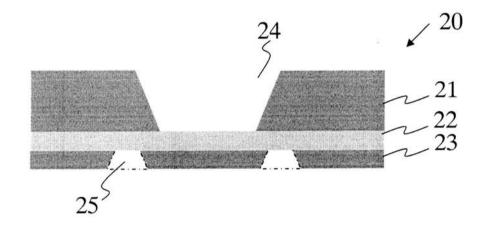

図3 Aに示されるように、最初に、第1のシリコンベース材料21、第2のシリコンベース材料23、及び両者の間の絶縁層22を有するシリコン・オン・インシュレータ(SOI)基板20が提供される。SOI基板20が炉内に置かれて第1のシリコンベース材料21と第2のシリコンベース材料23上にシリコン酸化物層200と201を形成する。シリコン酸化物層200と201は、ウエットエッチングのためのマスクとして使用される。次に、フォトレジストが、SOI基板20の二つの側(両側)に位置されるシリコン酸化物層200と201上に被覆され、フォトレジストをパターン形成してエッチング領域を形成するためにフォトリソグラフィープロセスが実行される。

## [0013]

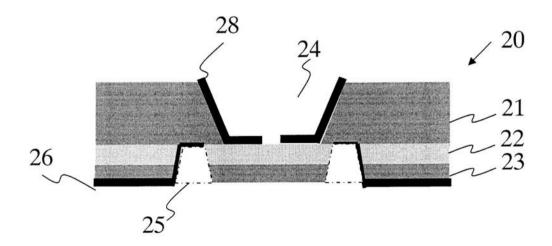

図3 Bに示されるように、シリコン基板用の異方性エッチング溶液(例えば、KOH,TMAH及びEDP)を使用してSOI基板20の第1のシリコンベース材料21をエッチングすることによって、傾斜面を有する反射キャビティ24が形成される。SOI基板20の第2のシリコンベース材料23をエッチングすることによって、正極と負極の接触面を形成する絶縁トレンチ25が形成される。本実施の形態において選択された、SOI基板20の第1のシリコンベース材料21と第2のシリコンベース材料23は、エッチングし反射キャビティ24を形成するために<100>結晶化方位有する。次に、第1のシリコンベース材料21と第2のシリコンベース材料23上のシリコン酸化物層200と201は、RIEで除去される。

## [0014]

図3 Cに示されるように、LEDチップを第1のシリコンベース材料21に電気的に接続するために、蒸着プロセス又はスパッタリングプロセスによって、SOI基板20の第1のシリコンベース材料21上に金属ライン28が形成される。また、第1のシリコンベース材料21と第2のシリコンベース材料23との間の電気接続のために、SOI基板20の第2のシリコンベース材料23及び外部に接続する正極と負極上に金属ライン26が形成される。

## [0015]

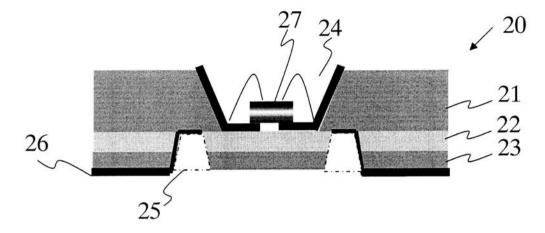

図3Dに示されるように、LEDチップ27は、反射キャビティ24上に配置され、ワ

30

40

50

イヤボンディングによって第 1 のシリコンベース材料上の金属ライン 2 8 に接続され、このワイヤボンディングは、送信のために、金属ライン 2 6 によって S O I 基板 2 0 の正極と負極に接続する L E D チップ 2 7 の正極と負極を造る。

## [0016]

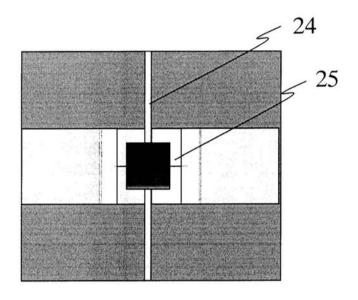

本実施の形態において、たった4回のフォトリソグラフィープロセスが使用される。完成されたLEDパッケージが図3Dに示される。図3Dの平面図である図3Eを図3Dと共に参照する。図面に従って、この図面には、SOI基板20とLEDチップ27が含まれる。SOI基板20は、第1のシリコンベース材料21、第2のシリコンベース材料23、及び両者の間の絶縁層22を有する。第1のシリコンベース材料21及び第2のシリコンベース材料23上には、各々、反射キャビティ24と絶縁トレンチ25がある。絶縁トレンチ25は、SOI基板20を正極と負極のための接触面に分割する。LEDチップとSOI基板20の第1のシリコンベース材料21と第2のシリコンベース材料23との間の電気接続のために、金属ライン26が形成される。LEDチップ27は、反射キャビティ24に配置され、且つ正極と負極が金属ライン26によってSOI基板20の対応する電極に接続される。

## [0017]

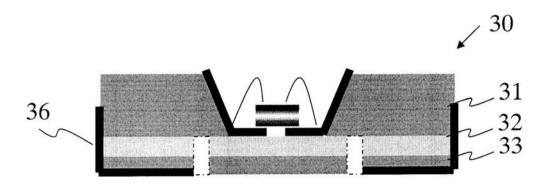

本実施の形態において提供されるLEDパッケージは、両面低抵抗SOI基板又は片面 低抵抗SOI基板を使用することが出来る。即ち、電気インピーダンスを調節及び整合す る た め に 、 第 1 の シ リ コ ン ベ ー ス 材 料 2 1 が 低 抵 抗 を 有 し 、 第 2 の シ リ コ ン ベ ー ス 材 料 が 高抵抗を有する。絶縁層22は、これら二つのシリコンベース材料同士間にあり、LED チップ 2 7 の正極と負極とSOI基板 2 0 の電極との間の電気接続のより短いルートを提 供するために、絶縁トレンチ25は、内側に金属ライン26を有する。SOI基板20の 正極と負極は、外部との電気接続のためである。図4は、本発明の第2の実施の形態を示 す。この実施の形態は、両面低抵抗SOI基板30又は片面低抵抗SOI基板30を使用 することが出来る。即ち、第1のシリコンベース材料31は、低抵抗を有し、第2のシリ コンベース材料 3 3 は、高抵抗を有し、絶縁層 3 2 は、これら二つの材料の間に介在され る。 S O I 基 板 は、より低 N 抵 抗 値 を 有 す る の で 、 金 属 ラ イ ン 2 6 は 、 S O I 基 板 3 0 の 側部に沿って配置されることが出来る。更に、SOI基板は、両面低抵抗SOI基板であ っても良いし、片面低抵抗SOI基板であってもよい。例えば、SOI基板は、砒素、ア ン チ モ ン 及 び リ ン が 重 ド ー プ さ れ た N タ イ プ 又 は P タ イ プ の N ず れ で あ っ て も よ く 、 0 . 1 / c m 未 満 の 抵 抗 を 有 す る 第 1 の シ リ コ ン ベ ー ス 材 料 と 第 2 の シ リ コ ン ベ ー ス 材 料 を 有する。金属ラインの材料は、Ag、Au、Cu、Al、Pt、Pd、Cr、Ni、又は それらの金属の合金である。

## [0018]

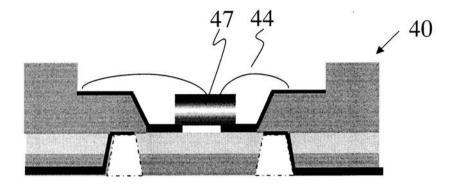

図 5 は、本発明の第 3 の実施の形態を示す。反射キャビティ 4 4 は、二段階の深さを有する。反射キャビティ 4 4 の上層は、LEDチップ 4 7 をSOI基板 4 0 の電極へより容易にワイヤボンディングするためである。

## [0019]

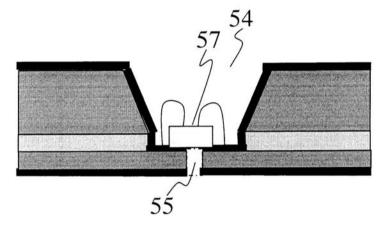

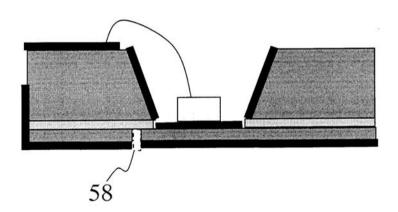

図6Aは、本発明の第4の実施の形態を示す。絶縁トレンチ55は、反射キャビティ5 4の底部の中心に配される。LEDチップ57は、そのトレンチの上に置かれる。このような構造は、壊れ易いので、本実施の形態における絶縁トレンチ58の位置は、図6Bに示されるように、外部により近くされる。

## [0020]

本発明の第5の実施の形態のプロセスフローの横断面図である図7A乃至図7Cを参照する。図面に従い、本発明のLEDパッケージを製造するプロセスは、絶縁トレンチに酸化物層を有することによって強化された構造体を形成出来る。

## [0021]

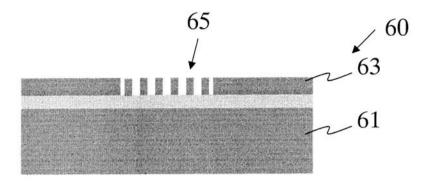

強化構造体を製造するプロセスは、以下に記述される。第1に、SOI基板60の第2のシリコンベース材料63上にマトリックス状に幾つかの絶縁トレンチ65を形成するた

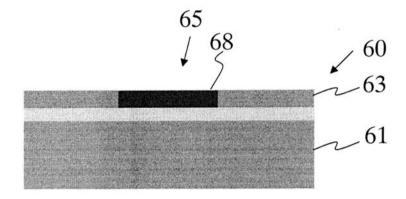

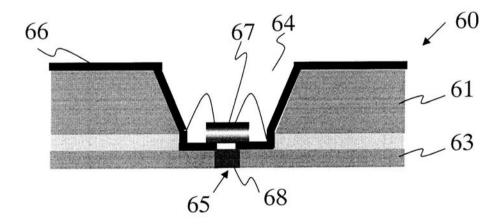

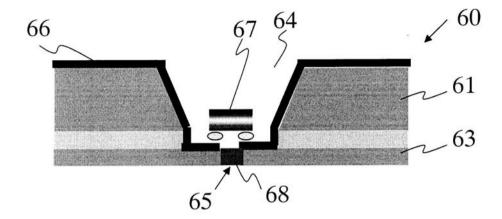

めに、フォトグラフィー及び反応性イオンエッチング(RIE)方法が使用される(図7Aに示される)。次に、SOI基板60は、炉に配され、強化のために、酸化処理されて酸化物層68を成長する。絶縁トレンチ65の不必要な酸化物層68が除去されて、酸化物層68を有する絶縁層65の強化構造体を完成する(図7Bに示される)。同時に、フォトグラフィーとエッチング方法は、第1のシリコンベース材料61上に反射キャビティ64を形成するために使用され得る。次に、金属ライン66は、SOI基板60の両側に形成される。最後に、LEDチップ67は、反射キャビティ64に配され、ワイヤボンディングによってSOI基板60上の金属ライン66に接続される(図7Cに示される)。

[ 0 0 2 2 ]

図 7 D に示されるように、LEDチップ 6 7 は、反射キャビティ 6 4 にマウントされ、フリップチップ方法によって電気接続される。

[ 0 0 2 3 ]

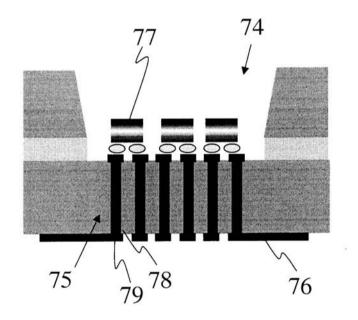

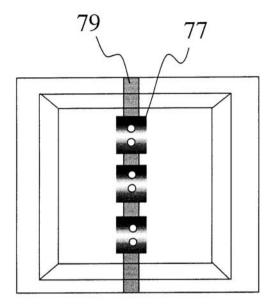

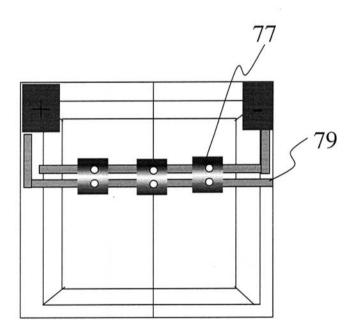

更に、本発明の第6の実施の形態のLEDパッケージを示す図8を参照する。フリップチップ方法によって反射キャビティ74にマウントされる幾つかのLEDチップ77がある。LEDチップは、最初に、絶縁トレンチ75に酸化物層78を形成し、次に、対応する金属ライン76を形成することによって互いに接続する。更に、伝導性ビア79の種々の設計に従い、LEDチップは、直列(図9Aに示される)、並列(図9Bに示される)又は並直列接続部を有することが出来る。

[0024]

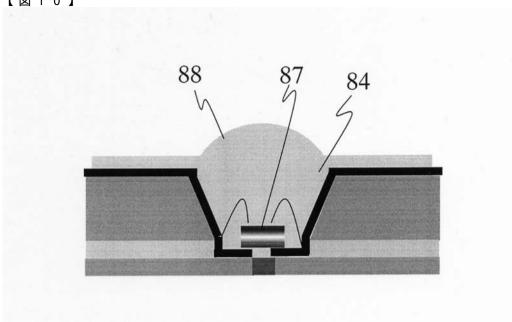

本発明の第7の実施の形態のLEDパッケージを示す図10を参照する。この実施の形態は、LEDチップ87を被覆し反射キャビティ84の全体を充填するためのカプセル化エポキシ88を更に含む。熱が提供された後に、カプセル化エポキシ88が固化して凸状構造になる。本発明の反射キャビティ84は、充填が容易である。

[ 0 0 2 5 ]

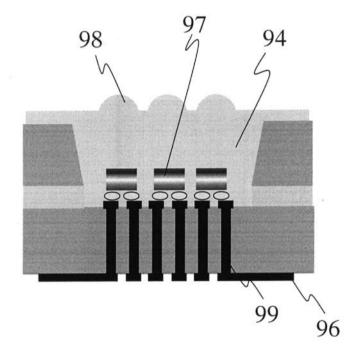

図11は、本発明の第8の実施の形態を示す。この実施の形態において、カプセル化エポキシ98は、反射キャビティ94に幾つかの凸状構造部になるように形成される。これらが直列のLEDチップ97と組合されると、LEDデバイス全体の輝度が改良される。LEDチップ97は、伝導性ビア99と金属ライン96の配置によって直列接続にマウントされる。

[0026]

概説すれば、LEDパッケージとその製造プロセスは、以下の利点を備える。まず、高温抵抗を良好な熱分散を有するSOI基板をパッケージボードとして使用することは、パッケージの信頼性を向上する。更に、基板上に絶縁層を形成する必要が無くなる。このように、このプロセスは、簡単化され、且つLEDチップの直並列接続が容易に達成される。従って、本発明は、駆動回路との統合が容易である、スケールダウンが容易である、大量生産が容易である、及び市場での競合性にとって有利であるとの利点を更に備える。

[0027]

本発明が特定の実施の形態を参照して記述されたが、この記述は、制限する意味に解釈されることを意味しない。開示された実施の形態の種々の変更並びに代替の実施の形態は、当業者には明白である。従って、本発明の範囲内に入る全ての変更を添付の請求項がカバーすることが意図されている。

【図面の簡単な説明】

[0028]

- 【図1】従来のSMDLEDデバイスパッケージを示す図である。

- 【図2】本発明の第1の実施の形態に従うフロー図である。

- 【図3 A】本発明の第1の実施の形態に従うプロセスフローを示す横断面図である。

- 【図3B】本発明の第1の実施の形態に従うプロセスフローを示す横断面図である。

- 【図3C】本発明の第1の実施の形態に従うプロセスフローを示す横断面図である。

- 【図3D】本発明の第1の実施の形態に従うプロセスフローを示す横断面図である。

- 【図3E】図3Dに示されるプロセスフローにおける平面図である。

30

20

50

- 【図4】本発明のLEDパッケージの第2の実施の形態を示す図である。

- 【図5】本発明のLEDパッケージの第3の実施の形態を示す図である。

- 【図6A】本発明のLEDパッケージの第4の実施の形態を示す図である。

- 【図6B】本発明のLEDパッケージの第4の実施の形態に従う第2のシリコンベース材料の側部近くに配置される絶縁トレンチを示す図である。

- 【図7A】本発明の第5の実施の形態に従うプロセスフローを示す横断面図である。

- 【図7B】本発明の第5の実施の形態に従うプロセスフローを示す横断面図である。

- 【図7C】本発明の第5の実施の形態に従うプロセスフローを示す横断面図である。

- 【図7D】本発明の第5の実施の形態に従うフリップチップ方法によってマウントされた LEDチップを示す図である。

- 【図8】本発明のLEDパッケージの第6の実施の形態を示す図である。

- 【図9A】本発明のLEDパッケージの第6の実施の形態に従う、直列接続を示す図である。

- 【図9B】本発明のLEDパッケージの第6の実施の形態に従う、並列接続を示す図である。

- 【 図 1 0 】 本 発 明 の L E D パ ッ ケ ー ジ の 第 7 の 実 施 の 形 態 を 示 す 図 で あ る 。

- 【図11】本発明のLEDパッケージの第8の実施の形態を示す図である。

## 【図1】

## 【図2】

# 【図3A】

【図3B】

【図3C】

# 【図3D】

# 【図3E】

【図4】

# 【図5】

# 【図6A】

# 【図 6 B】

## 【図7A】

## 【図7B】

# 【図7C】

# 【図7D】

# 【図8】

# 【図9A】

## 【図9B】

【図10】

【図11】

## フロントページの続き

(72)発明者 郭武政

台湾新竹県竹東鎮中興路四段195號

(72)発明者 陳炳儒

台湾新竹県竹東鎮中興路四段195號

(72)発明者 翁瑞坪

台湾新竹県竹東鎮中興路四段195號

(72)発明者 李孝文

台湾新竹県竹東鎮中興路四段195號

F ターム(参考) 5F041 AA33 AA42 DA04 DA07 DA09 DA12 DA13 DA19 DA20 DA32

DA35 DA36 DA44 DA57 DA72 DA77 DB09