### **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6:

(11) International Publication Number:

WO 96/31947

H03F 3/45

A2 (43) International Publication Date:

10 October 1996 (10.10.96)

(21) International Application Number:

PCT/FI96/00179

(22) International Filing Date:

2 April 1996 (02.04.96)

(30) Priority Data:

951623

5 April 1995 (05.04.95)

FI

(71) Applicant (for all designated States except US): NOKIA TELECOMMUNICATIONS OY [FI/FI]; Mäkkylän puistotie 1, FIN-02600 Espoo (FI).

(72) Inventor; and

(75) Inventor/Applicant (for US only): DEKKER, André [NL/FI]; Urpiaisentie 13, FIN-90540 Oulu (FI).

(74) Agent: OY KOLSTER AB; Iso Roobertinkatu 23, P.O. Box 148, FIN-00121 Helsinki (FI). (81) Designated States: AL, AM, AT, AU, AZ, BB, BG, BR, BY, CA, CH, CN, CZ, DE, DK, EE, ES, FI, GB, GE, HU, IS, JP, KE, KG, KP, KR, KZ, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, TJ, TM, TR, TT, UA, UG, US, UZ, VN, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

#### **Published**

Without international search report and to be republished upon receipt of that report.

(54) Title: OFFSET-COMPENSATED LINEAR RF DETECTOR

#### (57) Abstract

A known linear RF detector comprises a detector part having a detector diode (D1a) biased with a bias current ( $I_b$ ), and a linearizer part having an operation amplifier (OA1) and a diode in its feedback path. The major drawback of the known detector concerns the output offset voltages, the values of which can be predicted only if the diodes are matched diodes and have the same temperature. Because of this, the detector part and the linearizer part cannot be placed on different circuit boards. The invention solves the problem by placing a transistor circuit ( $Q_{3a}$ ,  $Q_{2a}$ ) in the feedback path such that it generates an offset voltage at the output of the operation amplifier, the voltage being the sum of the base-emitter voltages of the transistors of the circuit. Further, a second transistor circuit ( $Q_{3b}$ ,  $Q_{2b}$ ) is arranged at the output of the operation amplifier such that it generates a voltage at the output of the operation amplifier that compensates for the sum of the base-emitter voltages of the transistor circuit. The voltages thus cancel each other and the output offset voltage of the detector is zero.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM       | Armenia                  | GB       | United Kingdom               | MW  | Malawi                   |

|----------|--------------------------|----------|------------------------------|-----|--------------------------|

| AT       | Austria                  | GE       | Georgia                      | MX  | Mexico                   |

| AU       | Australia                | GN       | Guinea                       | NE  | Niger                    |

| BB       | Barbados                 | GR       | Greece                       | NL  | Netherlands              |

| BE       | Belgium                  | HU       | Hungary                      | NO  | Norway                   |

| BF       | Burkina Faso             | IE       | Ireland                      | NZ  | New Zealand              |

| BG       | Bulgaria                 | IT       | Italy                        | PL  | Poland                   |

| BJ       | Benin                    | JP       | Japan                        | PT  | Portugal                 |

| BR       | Brazil                   | KE       | Kenya                        | RO  | Romania                  |

| BY       | Belarus                  | KG       | Kyrgystan                    | RU  | Russian Federation       |

| CA       | Canada                   | KP       | Democratic People's Republic | SD  | Sudan                    |

| CF       | Central African Republic |          | of Korea                     | SE  | Sweden                   |

| CG       | Congo                    | KR       | Republic of Korea            | SG  | Singapore                |

| CH       | Switzerland              | KZ       | Kazakhstan                   | SI  | Slovenia                 |

| CI       | Côte d'Ivoire            | LI       | Liechtenstein                | SK  | Slovakia                 |

|          | Cameroon                 | LK       | Sri Lanka                    | SN  | Senegal                  |

| CM       | China                    | LR       | Liberia                      | SZ  | Swaziland                |

| CN<br>CS | Czechoslovakia           | LT       | Lithuania                    | TD  | Chad                     |

|          | Czech Republic           | LU       | Luxembourg                   | TG  | Togo                     |

| CZ       | •                        | LV       | Latvia                       | TJ  | Tajikistan               |

| DE       | Germany                  | MC       | Monaco                       | TT  | Trinidad and Tobago      |

| DK       | Denmark                  | MD       | Republic of Moldova          | UA  | Ukraine                  |

| EE       | Estonia                  | MG       | Madagascar                   | UG  | Uganda                   |

| ES       | Spain                    | ML       | Mali                         | US  | United States of America |

| FI       | Finland                  | MN       | Mongolia                     | UZ  | Uzbekistan               |

| FR       | France                   | MR<br>MR | Mauritania                   | VN  | Viet Nam                 |

| GA       | Gabon                    | MK       | IVIQUI Natita                | ••• |                          |

1

### Offset-compensated linear RF detector

5

15

20

25

30

35

The invention relates to a linear RF detector comprising a detector part having a detector diode biased with bias current, and a linearizer part having an operation amplifier to the inverting input of which is connected both the output of the detector part and the feedback path coming from the output of the operation amplifier.

In a typical embodiment of the detector, the level of a received radio signal is detected, but the detector is also used for detecting the level of a transmitted radio signal. This application relates to the latter kind of detector.

Requirements set for an RF detector include good linearity, high speed and zero output voltage when the input voltage is zero. Accuracy of detection should not suffer if the detector part and the linearizer part are placed on different circuit boards.

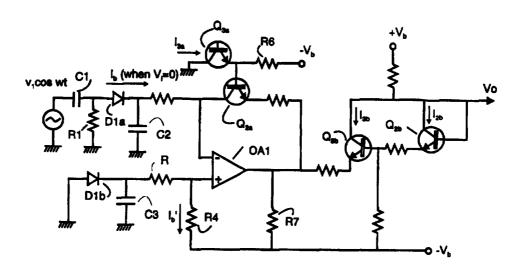

A known detector is shown in fig. 1. It meets all the other requirements except that the output offset voltage is not zero but depends on the differences in temperature of the detector part and the linearizer part. The detector part comprises a detector diode D1, a capacitor C and a resistor  $R_{\text{o}}$ , and the linearizer part comprises an operation amplifier OA1 having a diode D2 and a resistor R in its feedback path. The signal whose level is to be detected is represented by generator  $V_i cos\omega t$ , where  $V_i$  is the amplitude to be detected.  $V_k$  is a direct-current voltage used for biasing diode D1. Starting from the universal diode current equation  $\mathbf{I}_{\text{D}}\text{=}\mathbf{I}_{\text{S}}(\text{T})e^{\text{Vd/Vt}},$  where  $\mathbf{V}_{\text{T}}$  is a voltage proportional to absolute temperature and  $\mathbf{I}_{\mathbf{s}}(\mathbf{T})$  is a saturation current of the diode, it is possible to show that when diode D1 has a temperature T1, whereby the saturation current is

5

10

15

20

2

$I_{si}(T1)$ , and diode D2 has a temperature T2, whereby the saturation current is  $I_{s2}(T2)$ , the output voltage  $V_o$  of the detector is represented by formula (1):

$$V_o = -f(V_i; V_{T1}) - V_k - V_{T1} \ln\left(\frac{I_{s1}(T1)}{I_{c2}(T2)}\right) - \frac{T1 - T2}{T2} V_{D2}$$

(1)

The first term of the formula is the desired part depending on the RF input voltage. The second term is a constant offset voltage, and the third term is a varying offset voltage depending on the temperatures and device matching of the diodes. The fourth term, where  $V_{D2}$  is a voltage over diode D2, generates both a temperature-dependent offset voltage and an error in that part of the output voltage which depends on amplitude  $V_i$ . The part of output voltage  $V_0$  that is dependent on voltage  $V_i$  is given by a non-linear function f, where  $I_0$  and  $I_1$  are Bessel functions, and is obtained from formula (2)

$$f(V_{i}; V_{T}) = V_{T} \ln \left( I_{0} \left( \frac{V_{i}}{V_{T}} \right) \right) + \begin{cases} v_{4}V_{T} \left( \frac{V_{i}}{V_{T}} \right)^{2}, & V_{i} < V_{T} \\ V_{i} - V_{T}(0, 92 + v_{2} \ln \left( V_{i} \middle/ V_{T} \right)), & V_{i} > V_{T} \end{cases}$$

$$\frac{df}{dV_{i}} = \frac{I_{1}(V_{i} \middle/ V_{T})}{I_{0}(V_{i} \middle/ V_{T})} + \begin{cases} v_{2} \frac{V_{i}}{V_{T}}, & V_{i} < V_{T} \\ 1, & V_{i} > V_{T} \end{cases}$$

(2)

The prior art detector circuit illustrated by fig. 1 has several advantages. First, according to formula (2) the diode bias current  $I_b$  has theoretically, i.e. if the diode functions as an ideal diode, no effect on the part  $f(V_i,\ V_{T1})$  of the output voltage  $V_o$  that is dependent on the input voltage. The bias current will have to be set at a large enough value to enable fast charge/discharge

5

10

15

20

25

30

35

3

of the circuit capacitances. But on the other hand, although according to the simplified theory the performance of the circuit is not critical with respect to the bias current of the diode, there are, however, secondary influences, and so the bias current will have to be within a certain range. Second, resistor  $R_{\scriptscriptstyle 0}$  does not affect the output voltage in the transfer of the input voltage. Third, the detector is fast, if  $\boldsymbol{R}_{\!\scriptscriptstyle 0}$  and  $\boldsymbol{C}$ are sufficiently small. The fourth advantage is that the linear dynamic range of the detector is about 50 dB. The lowest input level to a  $50\Omega$  impedance is -20 dBm (sensitivity  $dV_0/dV_i$  has dropped to half of its nominal value) and the highest input level is +30 dBm, depending on the break down voltage of diode D1 and supply voltage of the operation amplifier.

The main disadvantage of the above-described known detector circuit concerns the output offset voltages, the values of which are predictable only if diodes D1 and D2 are matched devices and have the same temperature, so they should preferably be on the same silicon chip. However, it is often advantageous to place the detector and the linearizing amplifier on different circuit boards. It should also be noted that if diodes D1 and D2 are in the same package, RF energy will easily leak through diode D2 into the linearizing amplifier disturbing its operation. This is difficult to prevent, since D2 is in the feedback path of a fast amplifier, in the vicinity of which no filtering is allowed.

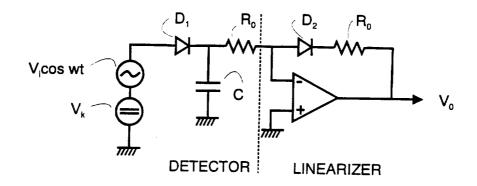

A way of eliminating the offset voltage in a circuit according to fig. 1 is shown in fig. 2. In the figure, offset compensation is used outside the feedback path of the linearizing amplifier. Diodes Dla and D2a are matched devices and have the same temperature, and they are preferably in the same package. Biasing voltage  $V_{\bf k}$  is obtained by the use of a diode D2 that is similar

5

10

15

20

25

30

35

4

to diodes D1a and D1b. This makes the bias current independent of the forward voltage and the temperature of the diodes. The offset voltage of matched diodes D1a and D1b at the output of the first operation amplifier OA1 is  $2*V_k$ . The non-inverting amplification of the latter operation amplifier OA2 is 2 and the inverting amplification is 1, so the final offset at output V is  $2*V_k - 1*2V_k = 0$ .

The circuit of fig. 2 has exactly the same drawbacks as the circuit of fig. 1: the detector and the linearizing amplifier must be placed on the same circuit board, which raises EMC (Electro-Magnetic Compatibility) problems when the RF input level is high (more than 10 dBm). The RF energy leaks through diode Dlb into linearizer OA1 and is rectified in the p-n junctions of diode Dlb and/or of the operation amplifiers. It is almost impossible to arrange an effective lowpass filter in the vicinity of Dlb, because the diode is in the feedback path of a fast amplifier. An extra operation amplifier reduces the speed of the detector and raises the price, especially since the detector must be fast.

The object of the present invention is to provide a linear detector circuit that does not have the drawbacks involved in the offset voltages of the known detector. The object is thus to provide a detector whose output offset voltages have been eliminated and in which the detector and the linearizing amplifier may have different temperatures and which does not involve RF leakage into the linearizing amplifier.

The object is achieved with the detector circuit disclosed in claim 1.

By the use of a transistor instead of a diode in the feedback path of the linearizing amplifier in accordance with the invention, the output offset voltage is rendered independent of the biasing voltage of the 5

10

15

20

25

detector diode. The detector part and the linearizer part can thus be made physically separate. In the feedback path, two transistors are connected such that the sum of their base-emitter voltages is essentially the same as the output offset voltage. At the output, one transistor circuit is preferably in a darlington configuration such that it generates an output voltage that compensates for the offset voltage generated by the transistor in the feedback path. When the voltage of the transistor circuit is added to or subtracted from the output voltage of the linearizing amplifier, the result is thus a zero offset voltage.

In the following the invention will be described in greater detail by means of a preferred embodiment of the invention with reference to the attached drawings, in which

- fig. 1 shows a known linearizing detector,

- fig. 2 illustrates a known compensation method,

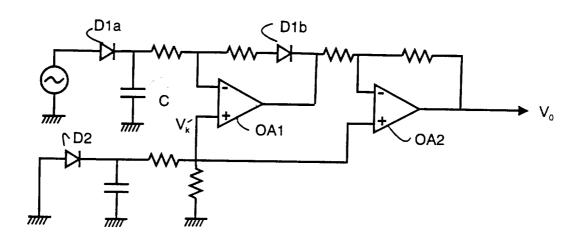

- fig. 3 illustrates a compensation principle according to the invention,

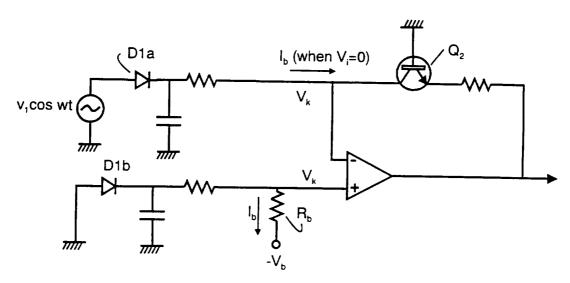

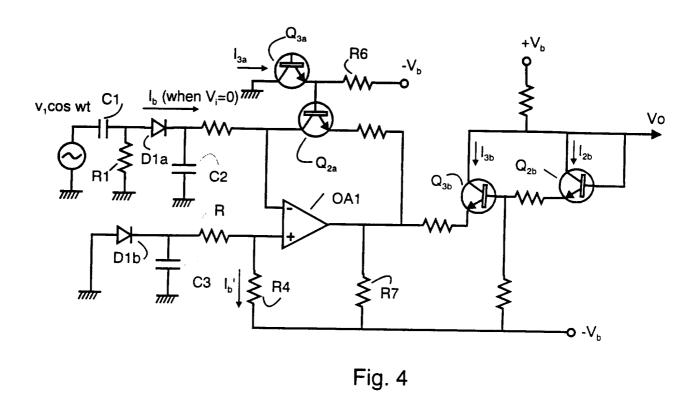

- fig. 4 illustrates compensation of offset voltages,

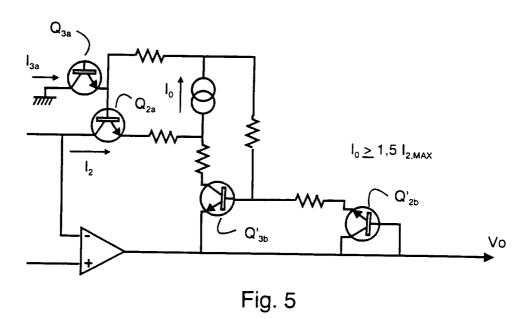

- fig. 5 illustrates compensation of offset voltages in a feedback path,

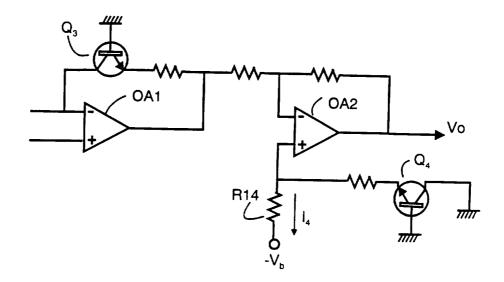

- fig. 6 illustrates compensation of the offset voltage by an operation amplifier,

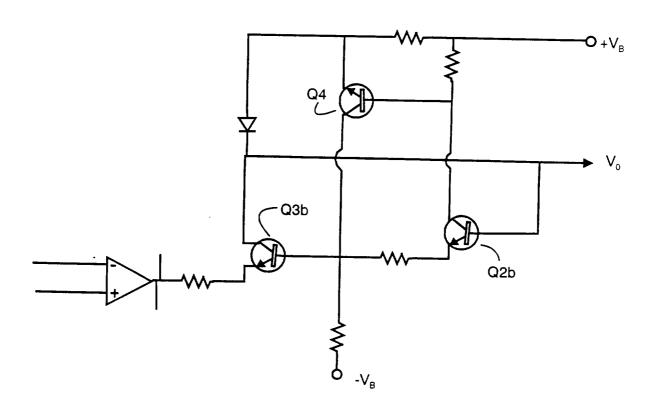

- fig. 7 illustrates a modification of the compensation of the offset voltage.

- Fig. 3 illustrates the principle of the invention in a simplified form. In practice, the circuit will have to be supplemented with the values stated below. When the linear detector according to the invention as shown in fig. 3 is compared with the prior art detector shown in fig. 1, two differences appear: first, biasing voltage source V<sub>k</sub> has been transferred to

6

the non-inverting input of the amplifier, so that the RF voltage source can be grounded directly. In addition, diode Dlb, which is preferably identical to and located on the same silicon chip as detector diode Dla (diode D1 in fig. 1), is used for transferring voltage V, such that bias current Ib becomes independent of the device and temperature. A suitable value for the bias current is e.g. 50μA. Second, diode D2 of fig. 1 in the feedback path of the operation amplifier has been replaced with transistor  $Q_2$ , fig. 3. The replacement is possible since the collector current vs. base-emitter current of the transistor obeys the same law as the current vs. voltage of the diode. When transistor  $Q_2$  is used in the feedback path, the reference level of output voltage Vo is earth (= base voltage of the transistor) instead of direct current  $V_k$  that affects at the inputs of the amplifier.

In reality, the circuit of fig. 3 does not, however, function in exactly the way described above, for the collector voltage of the transistor is lower than the base voltage by voltage  $V_k$ . The base voltage must thus be dropped. This is implemented by adding transistor  $Q_{3a}$  to the base circuit of transistor  $Q_2$  as shown in fig. 4. The drop in the base voltage is the base-emitter voltage of the added transistor Qa, which is operated with collector current I3a. The current is obtained by connecting the emitter of the added transistor Q1, through resistor R6 to negative voltage source -V<sub>R</sub>. This renders the output offset voltage of operation amplifier OA1 equal to the base-emitter voltages of said transistors, one of the latter voltages corresponding to collector current I, and the other to collector current  $I_{3a}$ . Mathematically, this can be expressed by formula (3), in which subindex s represents saturation current:

30

5

10

15

20

25

5

25

30

7

$$V_{ofs} = -V_T \ln\left(\frac{I_{3a}}{I_{s3a}}\right) - V_T \ln\left(\frac{I_b}{I_{s2a}}\right) = -V_T \ln\left(\frac{I_{3a}I_b}{I_{s2a}I_{s2a}}\right)$$

(3)

The offset voltage is eliminated by raising the output voltage by an equal amount. This is performed by using the base-emitter voltage of darlington transistors  $Q_{2b}$ ,  $Q_{3b}$  having collector currents  $I_{2b}$  and  $I_{3b}$  so that formula (4) holds true:

$$\frac{I_{3a}I_b}{I_{83a}I_{82a}} = \frac{I_{3b}I_{2b}}{I_{63b}I_{62b}} \tag{4}$$

To realize this, matched transistor pairs  $Q_{2a}$  and  $Q_{2b}$ , and  $Q_{3a}$  and  $Q_{3b}$ , respectively, are used so that  $I_{a2a} = I_{a2b}$  and  $I_{a2b} = I_{a3b}$ . The compensation condition of the output offset voltage of linearizing amplifier OA1 thus becomes:

$$I_{s3a} I_b = I_{s3b} I_{2b}$$

In principle, any combination of  $I_{2b}$  and  $I_{3b}$  can be used as long as the product of the currents is the right value. Although the above transistors do not accurately obey the exponential law, but are still matched pairs, the values  $I_{2b} = I_b$  and  $I_{3b} = I_{3a}$  compensate for the output offset voltage.

The resistor values of fig. 4 will not be discussed here. Determining of these values is obvious to a person skilled in the art. Resistors connected to supply voltage sources  $-V_B$  and  $+V_B$  can be replaced with current sources. Components Dla and Rl can be interchanged without affecting the operation of the circuit, so that a diode pair with a common anode can be used. In that case, however, most of the RF current will flow through capacitor C2, whereby it must be of a low loss type and grounded as directly as possible. Resistor  $R_7$ , which connects the output of the operation

5

10

15

20

25

30

35

8

amplifier to supply voltage  $-V_{\text{B}}$ , is not essential to the operation of the circuit but can be used for reducing dissipation of the operation amplifier.

The circuit of fig. 4 according to the invention gives a negative output voltage  $V_0$ . A positive output voltage is obtained by inverting the diodes, replacing the NPN transistors with PNP transistors, and changing the polarities of supply voltages  $-V_B$  and  $+V_B$ .

The above circuit will function sufficiently well in most applications, although it has some minor defects. If necessary, most of the defects can be eliminated by adding to circuit complexity. The error caused by the different temperatures of the detector and the linearizer part in that part of the output voltage which is dependent on the input voltage is not eliminated. The error, however, is zero when the input voltage is zero, and at most it is in the order of dozens of millivolts when the input voltage is high.

The diode bias current  $I_b$  and currents  $I_{3a}$  and  $I_{2b}$  are derived from the negative voltage, whereas the compensating current  $I_{3b}$  is obtained from the positive voltage. This increases the sensitivity to nonsymmetrical supply voltage variations.

The ratio of the collector current of transistor  $Q_{2b}$  to diode bias current  $I_b$  is not very well defined and is dependent on the temperature due to imperfect matching of diodes  $D_{1a}$  and  $D_{1b}$ , input offset voltage of the operation amplifier, and the temperature and device dependencies of the current gain of transistor  $Q_{3b}$ . If the resulting output offset voltage is too high, it can be eliminated by tuning, e.g. by making resistor R4 adjustable.

It is to be understood that the above description and the accompanying figures are intended only to illustrate the present invention. It is obvious

to a person skilled in the art that the invention can be varied and modified in many ways without deviating from the scope and spirit of the invention disclosed in the attached claims. Various alternatives are thus possible if the output impedance is to be zero. In the circuit of fig. 4, the output impedance is not zero. This, however, does not produce an offset error when the load is grounded, but only a small gain error. Fig. 5 shows a preferred embodiment of the invention where the output impedance is zero. In it, the offset compensating part has been transferred to the feedback path of the linearizing amplifier. The drawback is that the circuit has high complexity and that the consumption of current increases.

Fig. 6 shows another embodiment of the invention where the output impedance is zero. Another operation amplifier OA2 is used therein. This embodiment utilizes a usually undesired characteristic of the simplest possible differential operation amplifier: non-inverting amplification is twice as great as the inverting amplification. Only one transistor  $Q_4$  is thus needed to simulate the base-emitter voltage of two transistors.

Fig. 7 shows yet another embodiment, in which the defect of the circuit of fig. 4 is taken into account, i.e. the defect that the circuit does not function correctly if current amplification of transistor  $Q_{3b}$  is too small. The base current of transistor  $Q_{3b}$  thus forms too large a part of current  $I_{2b}$ . The problem can be solved by turning transistor  $Q_{2b}$  into a 'super emitter follower' by adding one PNP transistor  $Q_4$ .

10

#### Claims:

l. A linear RF detector comprising a detector part having a detector diode (Dla) biased with bias current ( $I_b$ ), and a linearizer part having an operation amplifier (OA1) to the inverting input of which is connected both the output of the detector part and the feedback path coming from the output of the operation amplifier, c h a r a c t e r i z e d by

10

5

the feedback path comprising a first transistor circuit  $(Q_{3a}, Q_{2a})$  in which the base of one transistor  $(Q_{3a})$  is grounded, the circuit being connected such that the transistor circuit generates an offset voltage at the output of the operation amplifier, the voltage being the sum of the base-emitter voltages of the transistors of the circuit;

15

20

the output of the operation amplifier being connected to a second transistor circuit  $(Q_{3b},\ Q_{2b})$  such that it generates a voltage at the output of the operation amplifier that compensates for the sum of the base-emitter voltages of the transistor circuit, whereby said voltages cancel each other and the output offset voltage of the detector is zero.

25

2. An RF detector according to claim 1, c h a r a c t e r i z e d by the first transistor circuit comprising a first transistor  $(Q_{3a})$  whose base is grounded and a second transistor  $(Q_{2a})$  whose base is connected to the emitter of the first transistor  $(Q_{3a})$  and whose collector current flows in the feedback path.

30

3. An RF detector according to claim 1, c h a r a c t e r i z e d by the second transistor circuit comprising a third transistor  $(Q_{3b})$  in a darlington configuration and a fourth transistor  $(Q_{2b})$  connected such that the output voltage of the detector is obtained from the collectors, the emitter of the

35

5

10

15

20

third transistor  $(Q_{3b})$  being operationally connected to the output of the operation amplifier (OA1).

4. An RF detector according to claims 2 and 3, c h a r a c t e r i z e d in that the transistor circuits are designed such that

$I_{3a} I_b = I_{3b} I_{2b}$

holds true,  $I_{2b}$  and  $I_{3b}$  being the base currents of the transistors in the second transistor circuit,  $I_b$  being the bias current of the detector diode and  $I_{3a}$  being the collector current of the first transistor in the first transistor circuit.

- 5. An RF detector according to claim 1, c h a r a c t e r i z e d in that the biasing voltage source  $(V_k)$  is connected to the non-inverting input of the operation amplifier (OA1) through a diode (D1b) that is similar to the detector diode (D1a).

- 6. An RF detector according to claim 1, characterized in that said second transistor circuit is connected to the output of the operation amplifier such that it is located in the feedback path.

Fig. 1

Fig. 2

Fig. 3

Fig. 6

Fig. 7