(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7089144号

(P7089144)

(45)発行日 令和4年6月22日(2022.6.22)

(24)登録日 令和4年6月14日(2022.6.14)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78  | 3 0 1 D |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/06  | 3 0 1 F |

| H 01 L | 29/06 (2006.01)  | H 01 L | 27/088 | B       |

| H 01 L | 21/8234(2006.01) | H 01 L | 27/088 | C       |

| H 01 L | 27/088(2006.01)  | H 01 L | 27/088 | 3 3 1 A |

F I

請求項の数 6 (全19頁)

(21)出願番号 特願2018-538593(P2018-538593)

(86)(22)出願日 平成29年1月23日(2017.1.23)

(65)公表番号 特表2019-503085(P2019-503085

A)

(43)公表日 平成31年1月31日(2019.1.31)

(86)国際出願番号 PCT/US2017/014581

(87)国際公開番号 WO2017/127813

(87)国際公開日 平成29年7月27日(2017.7.27)

審査請求日 令和2年1月20日(2020.1.20)

(31)優先権主張番号 15/003,776

(32)優先日 平成28年1月21日(2016.1.21)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 7 5 2 6 5

- 5 4 7 4 ダラス メイル ステイション

3 9 9 9 ピーオーボックス 6 5 5 4 7 4

(74)代理人 100098497

弁理士 片寄 恒三

ヘンリー リツツマン エドワーズ

アメリカ合衆国 7 5 0 4 4 テキサス州

ガーランド, バリーバニオン サークル

7 0 5

(72)発明者 ピンホワ フー

アメリカ合衆国 7 5 0 2 4 テキサス州

ブレイノ, スターテン アイランド ド

最終頁に続く

(54)【発明の名称】 側壁誘電体を備えるフィールド緩和酸化物に自己整合されるドリフト領域注入

## (57)【特許請求の範囲】

## 【請求項1】

集積回路であって、

半導体材料を含む基板と、

前記基板の頂部表面に配置されるフィールド酸化物と、

フィールドプレートタイプ電界効果トランジスタ(FET)であって、

前記基板の前記頂部表面に配置される二酸化シリコンのフィールド緩和酸化物であって、

前記フィールド緩和酸化物の横方向端部にバーズピーク構造を有し、前記フィールド酸化物よりも薄い、前記フィールド緩和酸化物と、

前記フィールド緩和酸化物の下の前記基板において配置されるドリフト領域であって、第1の導電型を有し、前記フィールド緩和酸化物の相対する端部から等しい横方向距離だけ前記フィールド緩和酸化物を超えて横方向に延在する、前記ドリフト領域と、

前記フィールド緩和酸化物の直ぐ下の前記基板において配置されて前記フィールド緩和酸化物と前記ドリフト領域との間に位置する電荷調整領域であって、前記第1の導電型と反対の第2の導電型を有する、前記電荷調整領域と、

前記基板において配置されるボディであって、前記第2の導電型を有し、前記基板の前記頂部表面において前記ドリフト領域と接する、前記ボディと、

前記フィールド緩和酸化物の近隣の前記基板の前記頂部表面において配置されるゲート誘電体層であって、前記フィールド緩和酸化物の厚さが前記ゲート誘電体層の厚さの少なくとも2倍である、前記ゲート誘電体層と、

前記ゲート誘電体層の上に配置されるゲートであって、前記ボディの一部の上と、前記ボディと前記フィールド緩和酸化物との間の前記ドリフト領域の部分の上とに延在する、前記ゲートと、

前記フィールド緩和酸化物の直ぐ上に配置されるフィールドプレートと、

を含む、前記フィールドプレートタイプFETと、

を含む、集積回路。

【請求項2】

請求項1に記載の集積回路であって、

前記ゲートが、前記フィールドプレートを提供するように前記フィールド緩和酸化物の上を途中まで延在する、集積回路。

10

【請求項3】

請求項1に記載の集積回路であって、

前記フィールドプレートが前記ゲートから電気的に絶縁される、集積回路。

【請求項4】

請求項1に記載の集積回路であって、

前記ドリフト領域がn型であり、前記ドリフト領域が、前記フィールド緩和酸化物の直ぐ下の砒素拡散された領域と、前記砒素拡散された領域の下の燐拡散された領域とを含み、前記砒素拡散された領域のn型ドーパントの大部分が砒素であり、前記燐拡散された領域のn型ドーパントの大部分が燐である、集積回路。

【請求項5】

請求項1に記載の集積回路であって、

前記ドリフト領域が、100ナノメートル～200ナノメートルの距離だけ前記フィールド緩和酸化物を横方向に超えて前記ゲートの下を延在する、集積回路。

20

【請求項6】

請求項1に記載の集積回路であって、

前記基板において配置されるドリフト領域を含むプレーナFETであって、前記プレーナFETの前記ドリフト領域が前記第1の導電型を有し、前記プレーナFETの前記ドリフト領域が前記フィールドプレートタイプFETの前記ドリフト領域と実質的に等しいドーパント分布を有し、前記プレーナFETにはフィールド緩和酸化物がない、前記プレーナFETを更に含む、集積回路。

30

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、概して集積回路に関し、より詳細には集積回路における電界効果トランジスタに関する。

【背景技術】

【0002】

集積回路の中には、高電圧動作を可能にするためにドリフト領域を備える電界効果トランジスタ(FET)を含むものがある。これらの集積回路が次世代の製品に合わせて縮小する場合、これらのFETにおける低電力消費を維持しながらインダクタなどの外部受動構成要素の大きさを低減するために、これらのFETのスイッチング周波数を高くする要望がある。そのためには、FETのスイッチング寄生及びオン状態比抵抗(面積正規化オン状態抵抗)を同時に低減することが必要となる。

40

【0003】

ドレイン電圧を高くした動作を可能にするために、FETは、高ドレイン電圧状態下で欠乏するドリフト領域を採用し、そのため、FETが、オン状態の間、通電を維持しながら電圧を遮断することができる。高電圧FETは、ドリフト領域のためのフィールドプレートとして働くように、フィールド酸化物の上をゲートが延在する状態で形成される傾向がある。遺憾ながら、250ナノメートルノードやそれ以下のノードなどの高度な製造ノードにおけるフィールド酸化物は、通常、シャロートレンチ分離(STI)プロセスによっ

50

て形成され、このようなFETにおけるゲート拡張フィールドプレートの下のフィールド緩和 (field relief) 酸化物として最適に用いるには概して厚過ぎる。

【発明の概要】

【0004】

説明する例において、集積回路が、フィールドプレートタイプFETを含み、集積回路の基板の頂部表面の上に酸化物マスクの層を形成して、フィールドプレートタイプFETのためのエリアを覆うことによって形成される。第1の開口が酸化物マスクの層に形成されて、フィールドプレートタイプFETのドリフト領域のためのエリアを露出させる。第1の開口の下の基板にドーパントが注入される。続いて、酸化物マスクの層上に第1の開口の横方向境界に沿って誘電体側壁が形成される。第1の開口の誘電体側壁によって露出されるエリアにおける基板の頂部表面においてフィールド緩和酸化物の層が形成される。注入されたドーパントは、基板において拡散されてドリフト領域を形成し、フィールド緩和酸化物の層を超えて横方向に延在する。フィールド緩和酸化物の層が形成された後、誘電体側壁及び酸化物マスクの層が除去される。フィールドプレートタイプFETのゲートが、フィールドプレートタイプFETのボディの上に形成されて、近隣のドリフト領域の上に延在する。ゲートの近隣のフィールド緩和酸化物の直ぐ上にフィールドプレートが形成される。

10

【図面の簡単な説明】

【0005】

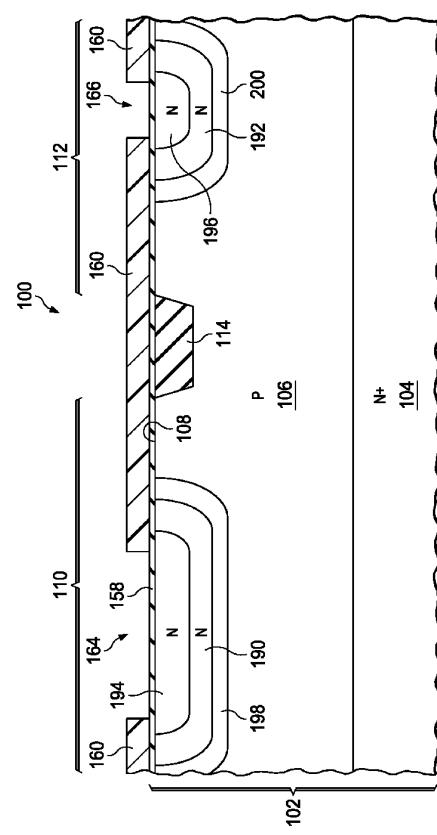

【図1】フィールドプレートタイプFETを含む例示の集積回路の断面である。

20

【0006】

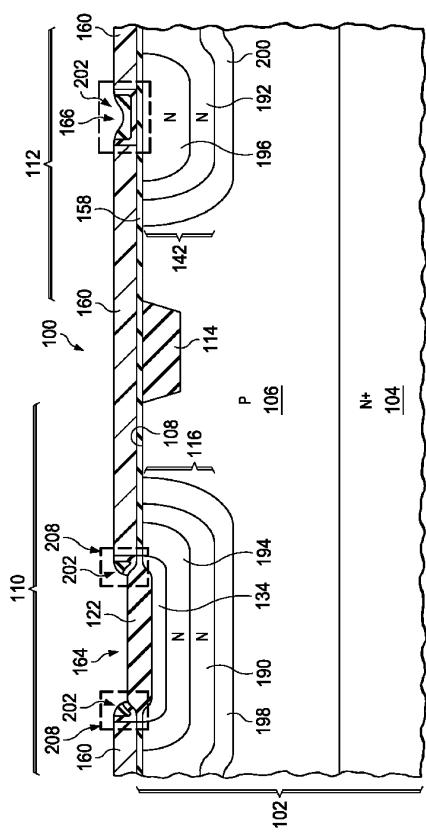

【図2A】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2B】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2C】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2D】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2E】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2F】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2G】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2H】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2I】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

30

【図2J】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図2K】図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【0007】

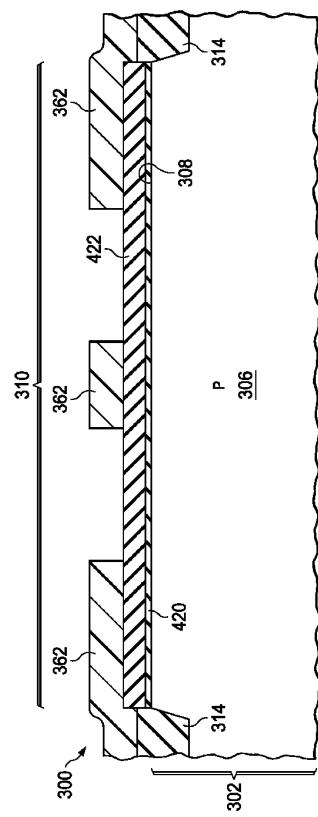

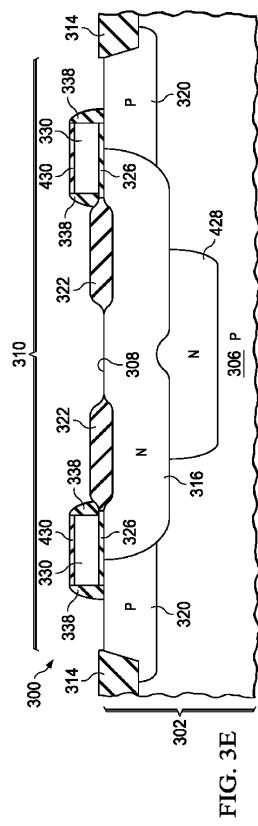

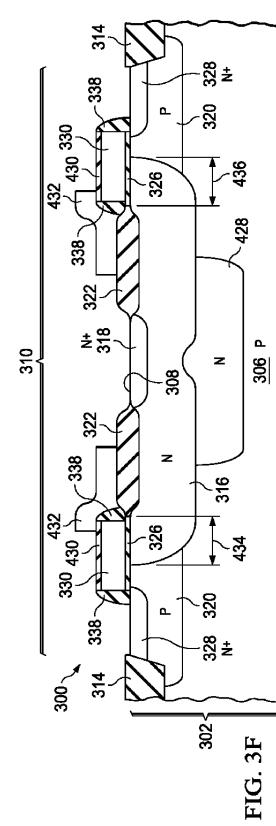

【図3A】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

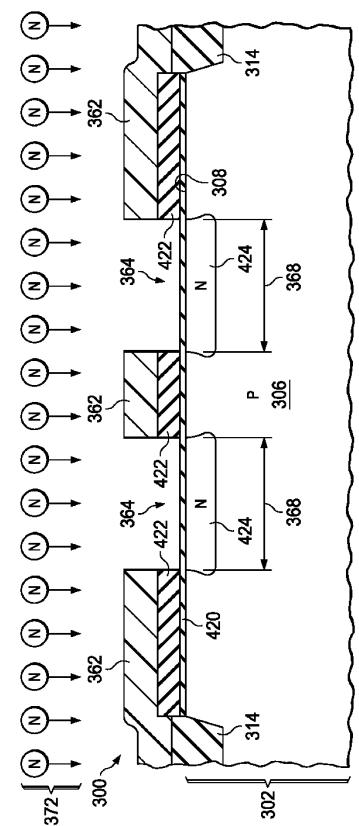

【図3B】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

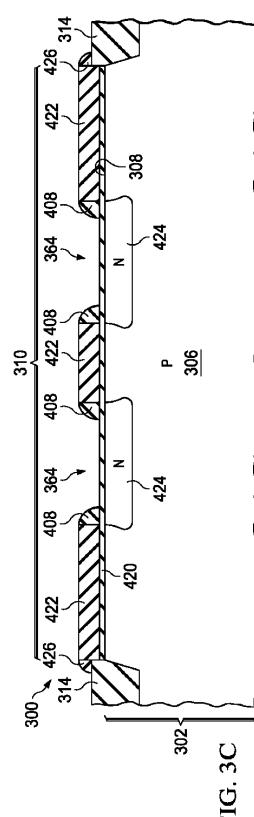

【図3C】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

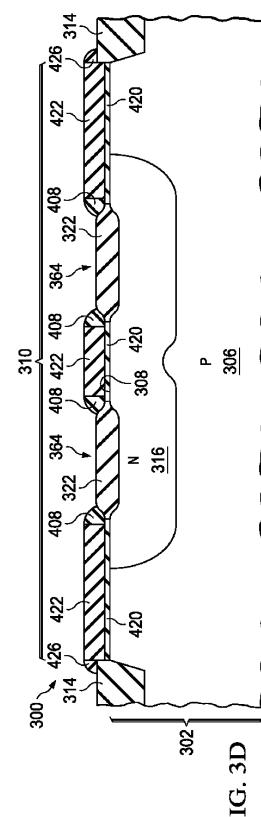

【図3D】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

40

【図3E】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【図3F】フィールドプレートタイプFETを含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。

【例示実施形態の詳細な説明】

【0008】

図面は一定の縮尺で描かれておらず、説明を図示するために提供されている。例示の実施形態は、行為又は事象の図示する順によって限定されるものではなく、行為の中には異なる順で、及び／又は、他の行為又は事象と同時に起こり得るものもある。また、例示の実

50

施形態に従った方法論を実装するために、図示する行為又は事象のすべてが必要とされるわけではない。

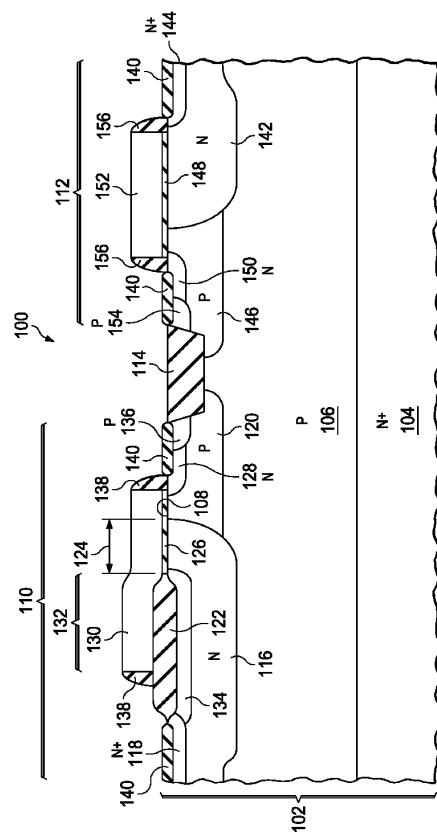

【0009】

図1は、フィールドプレートタイプFETを含む例示の集積回路の断面図である。この例では、nチャネルフィールドプレートタイプFETを説明する。ドーパントの極性を適切に変更することで、類似のpチャネルフィールドプレートタイプFETを説明し得る。集積回路100は基板102を含み、基板102は、場合によっては、重くドープされたn型埋込層104、及びn型埋込層104の上のp型層106を備える。p型層106は基板102の頂部表面108まで延在する。集積回路100は、nチャネルフィールドプレートタイプFET110を含む。集積回路100は、任意選択で、プレーナFET112も含み得る。フィールドプレートタイプFET110及びプレーナFET112などの集積回路100の構成要素は、フィールド酸化物114によって横方向に分離され得る。フィールド酸化物114は、図1に示すようなSTI構造、又は局所酸化シリコン(LOCOS)構造を有し得る。

【0010】

フィールドプレートタイプFET110は、基板102に配置されるn型ドリフト領域116を含む。ドリフト領域116は、フィールドプレートタイプFET110のn型ドレインコンタクト領域118からp型ボディ120まで延在する。例えば、ドリフト領域116の平均ドーパント密度は、 $1 \times 10^{16} \text{ cm}^{-3} \sim 1 \times 10^{16} \text{ cm}^{-3}$ とし得る。フィールドプレートタイプFET110の降伏電圧及び比抵抗の所望の値を提供するため、ドリフト領域116は、重くドープされる頂部及び軽くドープされる底部を有し得る。ドリフト領域116の上にフィールド緩和酸化物122の層が配置される。フィールド緩和酸化物122は、フィールド緩和酸化物122の横方向端部において先細りのプロファイルを有し、これは通常、バーズビーク(bird's beak)と称される。フィールド緩和酸化物112はフィールド酸化物114より薄い。ドリフト領域116は、フィールド緩和酸化物122を超えて横方向距離124延在してボディ120に近接する。例えば、横方向距離124は100ナノメートル～200ナノメートルとし得る。この距離により、有利にも、フィールドプレートタイプFET110の比抵抗及びゲート-ドレイン容量の所望の低い値が提供される。フィールドプレートタイプFET110のゲート誘電体層126が、基板102の頂部表面108において配置され、フィールドプレートタイプFET110のフィールド緩和酸化物122からn型ソース128まで延在して、ドリフト領域116の反対にあるボディ120に接する。ゲート誘電体層126は、フィールド緩和酸化物122を超えて延在するドリフト領域116の部分の上、及びボディ120のドリフト領域116とソース128との間の部分の上に配置される。フィールド緩和酸化物122は、ゲート誘電体層126の少なくとも2倍の厚みである。フィールドプレートタイプFET110はゲート130を含む。ゲート130は、ゲート誘電体層126の上に配置され、ソース128から、ボディ120のドリフト領域116とソース128との間の部分の上、及びフィールド緩和酸化物122を超えて延在するドリフト領域116の部分の上に延在する。この例では、ドリフト領域116の一部の上にフィールドプレート132を提供するため、ゲート130はフィールド緩和酸化物122の上を途中まで延在する。この例の代替バージョンにおいて、ゲート130からの別の構造要素によってフィールドプレートが提供されてもよい。フィールド緩和酸化物122の厚さは、フィールドプレートタイプFET110の動作の間ドリフト領域116において電界の所望の最大値を提供するように選択され得る。

【0011】

フィールドプレートタイプFET110は、場合によっては、フィールド緩和酸化物122の直ぐ下の基板に配置される任意選択の電荷調整領域134を含み得る。電荷調整領域134は、フィールド緩和酸化物122と実質的に整合される。この例の1つのバージョンでは、電荷調整領域134における正味ドーパント密度が電荷調整領域134の下のドリフト領域116より高くなるように、電荷調整領域134におけるドーパントを燐及び

10

20

30

40

50

/又は砒素などのn型とし得る。この例のこのバージョンでは、電荷調整領域134はドリフト領域116の一部とみなし得る。この例の別のバージョンでは、電荷調整領域134における正味ドーパント密度が電荷調整領域134の下のドリフト領域116より低いがn型のままであるように、電荷調整領域134におけるドーパントを、ドリフト領域116のn型ドーパントをカウンタードープせずに補償する、ボロン、ガリウム、及び/又はインジウムなどのp型とし得る。この例のこのバージョンでも、電荷調整領域134はドリフト領域116の一部とみなし得る。この例のさらなるバージョンにおいて、電荷調整領域134における正味ドーパント密度がp型に変換されるように、電荷調整領域134におけるドーパントを、ドリフト領域116のn型ドーパントをカウンタードープするp型とし得る。この例のこのバージョンでは、電荷調整領域134はドリフト領域116とは別個とみなし得る。電荷調整領域134におけるドーパント極性及び密度は、フィールドプレートタイプFET110について降伏電圧及び比抵抗の所望の値を提供するように選択され得る。

#### 【0012】

フィールドプレートタイプFET110はまた、基板102においてボディ120に配置されるp型ボディコンタクト領域136を含み得る。ゲート側壁スペーサ138が、ゲート130の側部表面上に配置され得る。金属シリサイド140が、ドレインコンタクト領域118並びにソース128及びボディコンタクト領域136上に配置され得る。フィールドプレートタイプFET110は、ドレインコンタクト領域118がフィールド緩和酸化物122によって囲まれ、フィールド緩和酸化物122がボディ120及びソース128によって囲まれる、ドレイン中心構成を有し得る。フィールドプレートタイプFET110の他の構成もこの例の範囲に含まれる。

#### 【0013】

プレーナFET112は、基板102に配置されるn型ドリフト領域142を含む。ドリフト領域142は、プレーナFET112のn型ドレインコンタクト領域144からp型ボディ146まで延在する。プレーナFET112には、フィールドプレートタイプFET110のフィールド緩和酸化物122に類似するフィールド緩和酸化物の層がない。プレーナFET112には、フィールドプレートタイプFET110の電荷調整領域134に類似する電荷調整領域もない。プレーナFET112のドリフト領域142は、フィールドプレートタイプFET110のドリフト領域116と同時に形成される結果、ドリフト領域116に類似するドーパント分布及び種を有する。

#### 【0014】

プレーナFET112のゲート誘電体層148が、基板102の頂部表面108において配置され、ドレインコンタクト領域144からプレーナFET112のドリフト領域142からn型ソース150まで延在して、ドリフト領域142とは反対にあるボディ146に接する。ゲート誘電体層148は、ドリフト領域142のドレインコンタクト領域144とボディ146の間の部分の上、及びボディ146のドリフト領域142とソース150の間の部分の上に配置される。プレーナFET112はゲート152を含み、ゲート152は、ゲート誘電体層148の上に配置され、ソース150からドレインコンタクト領域144近傍の位置まで延在する。

#### 【0015】

プレーナFET112は、ボディ146における基板102において配置されるp型ボディコンタクト領域154も含み得る。ゲート側壁スペーサ156が、ゲート152の側部表面上に配置され得る。金属シリサイド140は、フィールドプレートタイプFET110上に存在する場合、ドレインコンタクト領域144並びにソース150及びボディコンタクト領域154上に配置され得る。プレーナFET112は、ドレイン中心構成又は他の構成を有し得る。

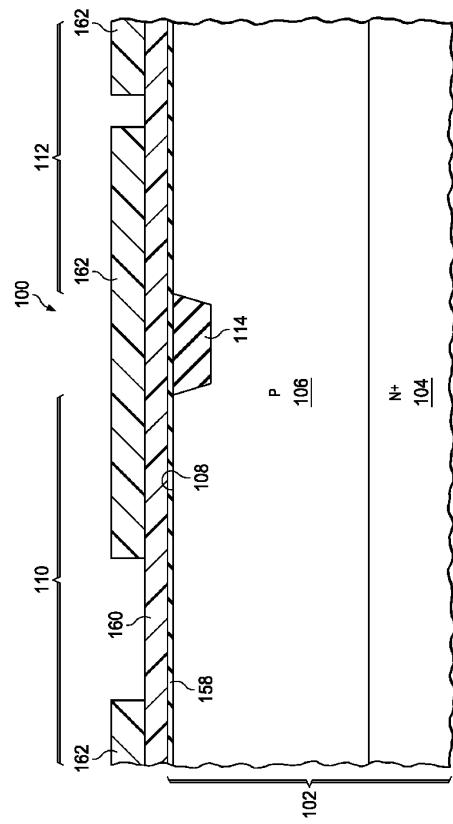

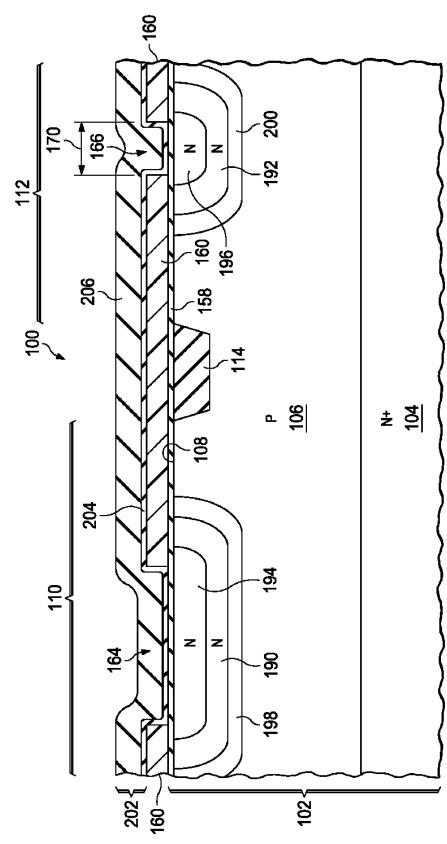

#### 【0016】

図2A～図2Kは、図1の集積回路の断面であり、例示の形成方法の連続的段階で示す。図2Aを参照すると、基板102は、場合によっては頂部表面上にエピタキシャル層を備

10

20

30

40

50

える、p型シリコンウェハで開始し、アンチモンなどのn型ドーパントを $1 \times 10^{15} \text{ cm}^{-2} \sim 1 \times 10^{16} \text{ cm}^{-2}$ のドーズ量で注入することによってn型埋込層104を形成することによって形成され得る。熱駆動プロセスにより、ウェハを加熱して、注入されたn型ドーパントを活性化し拡散させる。インサイチュp型ドーピングを用いるエピタキシャルプロセスによって、p型層106がウェハ上に形成される。例えば、エピタキシャル形成される材料は4ミクロン～6ミクロンの厚さとし得、これは、有利にも図1の比較的浅いドリフト領域116によって可能であり、これは、ドリフト領域116に対する図1のフィールド緩和酸化物122の自己整合性によって可能とされる。n型ドーパントがエピタキシャル成長材料中に途中まで拡散し、そのため、n型埋込層104が元のシリコンウェハとエピタキシャル成長材料との境界に重なる。例えば、p型層106の平均バルク抵抗率は $1 \text{ cm} \sim 10 \text{ cm}$ である。任意選択のp型埋込層が、2メガ電子ボルト(MeV)～3MeVなどのエネルギーでボロンを注入することによってp型層106において形成され得る。

#### 【0017】

フィールド酸化物114は、STIプロセス又はLOCOSプロセスなどによって、基板102の頂部表面108において形成される。例示のSTIプロセスは、基板102の上に、窒化シリコンの化学機械研磨(CMP)停止層及びSTIパッド酸化物の層を形成することを含む。CMP停止層及びSTIパッド酸化物を介して基板102内に分離トレンチがエッチングされる。分離トレンチは、オルトケイ酸テトラエチル(TEOS)を用いるプラズマエンハンスト化学気相成長(PECVD)プロセス、高密度プラズマ(HDP)プロセス、TEOS及びオゾンを用いる高アスペクト比プロセス(HARP)、シランを用いる常圧化学気相成長(APCVD)プロセス、又はジクロロシランを用いる準常圧化学気相成長(SACVD)プロセスを用いて、二酸化シリコンで充填される。酸化物CMPプロセスによって、CMP停止層の上から過剰な二酸化シリコンが除去される。続いてCMP停止層が除去され、フィールド酸化物114が残る。例示のLOCOSプロセスは、基板102の上のLOCOSパッド酸化物の層の上に窒化シリコンマスク層を形成することを含む。フィールド酸化物114のためのエリアにおいて窒化シリコンマスク層が除去され、LOCOSパッド酸化物が露出される。窒化シリコンマスク層によって露出されたエリアに熱酸化によって二酸化シリコンが形成され、フィールド酸化物114が形成される。続いて窒化シリコンマスク層が除去されて、適所にフィールド酸化物114を残す。

#### 【0018】

パッド酸化物158の層が基板102の頂部表面108に形成される。例えば、パッド酸化物158は、5ナノメートル～25ナノメートルの厚さとし得、熱酸化によって、又はいくつかの化学気相成長(CVD)プロセスの任意のものによって形成され得る。パッド酸化物158の層の上に酸化物マスク160の層が形成される。例えば、酸化物マスク160の層は、ジクロロシラン及びアンモニアを用いる低圧化学気相成長(LPCVD)プロセスによって形成される窒化シリコンを含み得る。或いは、酸化物マスク160の層内の窒化シリコンは、ビス(3級ブチルアミノ)シラン(BTBA)の分解によって形成され得る。酸化物シリコン160の層を形成するための他のプロセスもこの例の範囲に含まれる。例えば、酸化物マスク160の層は、図1のフィールド緩和酸化物122の厚さの約1～2倍とし得る。

#### 【0019】

エッチングマスク162が、酸化物マスク160の層の上に形成され、フィールドプレートタイプFET110のためのエリアにおいて図1のフィールド緩和酸化物122のためのエリアを露出させ、かつ、プレーナFET112のためのエリアにおいて図1のドリフト領域142を注入するためのエリアを露出させる。エッチングマスク162は、光リソグラフィプロセスによって形成されるフォトレジストを含み得、アモルファスカーボンなどのハードマスク材料を含み得、有機底部反射防止コーティング(BARC)などの反射防止層を含み得る。フィールドプレートタイプFET110のためのエリアにおけるフィ

10

20

30

40

50

ールド緩和酸化物 122 のための露出エリアは、酸化物マスク 160 の層をエッティングした後、エッティングされたエリアの中央部分が誘電体側壁の形成後に空のままであるよう、充分に広い横寸法を有する。プレーナ FET 112 のためのエリアにおけるドリフト領域 142 を注入するための露出エリアは、酸化物マスク 160 の層をエッティングした後、ドリフト領域 142 を注入するための露出エリアが、誘電体側壁を形成するために用いられる誘電体材料によって遮蔽されたままであるように充分に狭い幅を有する。

#### 【0020】

図 2B を参照すると、エッティングマスク 152 によって露出されたエリアにおいて酸化物マスク 160 の層が除去され、パッド酸化物 158 の層を露出させる。エッティングマスク 152 によって露出されたエリアにおけるパッド酸化物 158 の部分も除去され得る。フィールドプレートタイプ FET 110 のためのエリアにおける酸化物マスク 160 の層を除去することによって、酸化物マスク 160 の層に第 1 の開口 164 が形成される。プレーナ FET 112 のためのエリアにおける酸化物マスク 160 の層を除去することによって、酸化物マスク 160 の層に第 2 の開口 166 が形成される。第 1 の開口 164 の横方向寸法は、誘電体側壁の形成後に第 1 の開口 164 の中央部分が空のままであるように充分に幅広い。例えば、厚さが 80 ナノメートル～100 ナノメートルであるコンフォーマル層の堆積によって誘電体側壁が形成されるこの例の或るバージョンにおいて、横方向寸法 168 は約 350 ナノメートルよりも大きい。第 2 の開口 166 の幅 170 は、誘電体側壁を形成するために用いられる誘電体材料によって第 2 の開口 166 が遮蔽されたままであるように充分に狭い。第 2 の開口における誘電体材料の量を所望の値とするために、第 2 の開口 166 の幅 170 は、第 1 の開口 164 内に誘電体側壁を形成するためにその後形成される誘電体層の厚さの 2.5 倍未満とし得る。例えば、厚さが約 80 ナノメートルであるコンフォーマル層の堆積によって誘電体側壁が形成される上述の例のバージョンでは、幅 170 は約 200 ナノメートル未満である。酸化物マスク 160 の層は、リン酸水溶液などのウェットエッティングによって除去され得、このウェットエッティングによって図 2B に示すようにエッティングマスク 162 がアンダーカットされる。或いは、酸化物マスク 160 の層は、フッ素ラジカルを用いるプラズマエッティングによって除去されてもよく、この場合、アンダーカット量が少なくなり得る。エッティングマスク 162 は、任意選択で、酸化物マスク 160 の層をエッティングした後に除去されてもよいし、後続のイオン注入ステップにおいて付加的な停止材料を提供するために適所に残されてもよい。

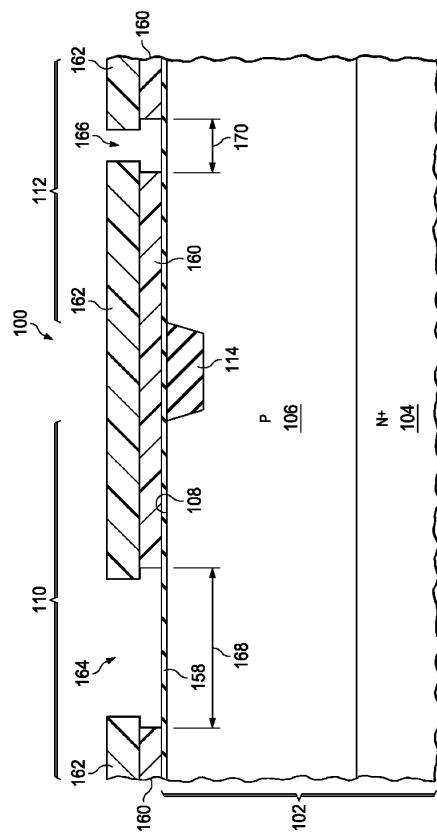

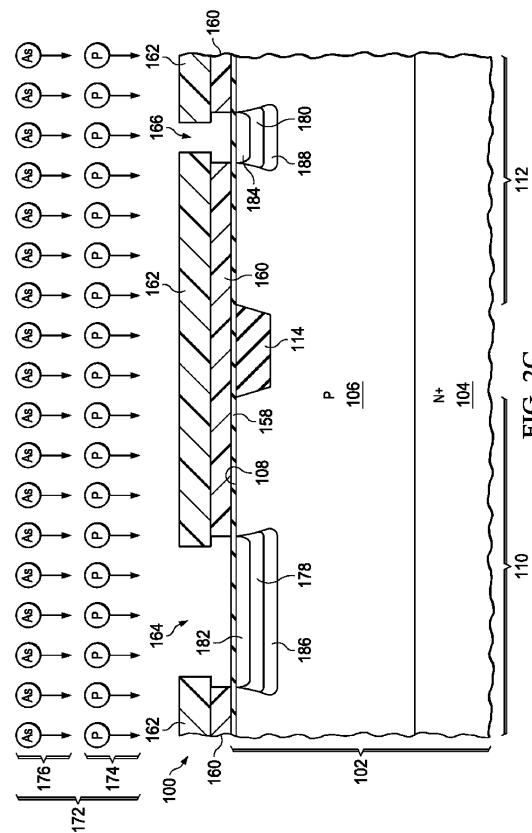

#### 【0021】

図 2C を参照すると、酸化物マスク 160 の層を除去することによって露出されたエリアにおける基板 102 に n 型ドーパント 172 が注入される。このエリアは、フィールドプレートタイプ FET 110 のためのエリアにおける第 1 の開口 164、及びプレーナ FET 112 のためのエリアにおける第 2 の開口 166 を含み、有利にも、その後形成される図 1 のドリフト領域 116 が、その後形成される図 1 のフィールド緩和酸化物 122 に自己整合する。例えば、n 型ドーパント 172 は、 $1 \times 10^{12} \text{ cm}^{-2} \sim 4 \times 10^{12} \text{ cm}^{-2}$  のドーズ量、150 キロ電子ボルト (keV) ~ 225 keV のエネルギーで注入され得る燐 174、及び、 $2 \times 10^{12} \text{ cm}^{-2} \sim 6 \times 10^{12} \text{ cm}^{-2}$  のドーズ量、100 keV ~ 150 keV のエネルギーで注入され得る砒素 176 を有し得る。注入された燐 174 は、第 1 開口 164 の下に第 1 燐注入領域 178 を、及び第 2 開口 166 の下に第 2 燐注入領域 180 を形成する。同様に、注入された砒素 176 は、第 1 開口 164 の下に第 1 砒素注入領域 182 を、及び第 2 開口 166 の下に第 2 砒素注入領域 184 を形成する。フィールドプレートタイプ FET 110 において図 1 のドリフト領域 116 に、及びプレーナ FET 112 において図 1 のドリフト領域 142 に斜めの接合が設けられるように、第 1 燐注入領域 178 及び第 2 燐注入領域 180 は、有利にも、第 1 砒素注入領域 182 及び第 2 砒素注入領域 184 よりも深い。任意選択で、n 型ドーパント 172 の燐ドーパントは深いドーズの燐も含み得、この深いドーズの燐は、第 1 の燐注入領域 178 の下の基板 102 において第 1 のディープ補償注入領域 186 を形成し、第 2 の燐注入領域 180 の下の基板 102 において第 2 のディープ補償注入領域 188 を形成する。

10

20

30

40

50

この深いドーズの燐は、p型層106をn型にカウンタードープせずに、正味ドーパント密度を下げるよう、p型層106を補償することを意図するものである。n型ドーパント172が注入された後、エッティングマスク162の残りの部分があれば、その部分が除去される。

【0022】

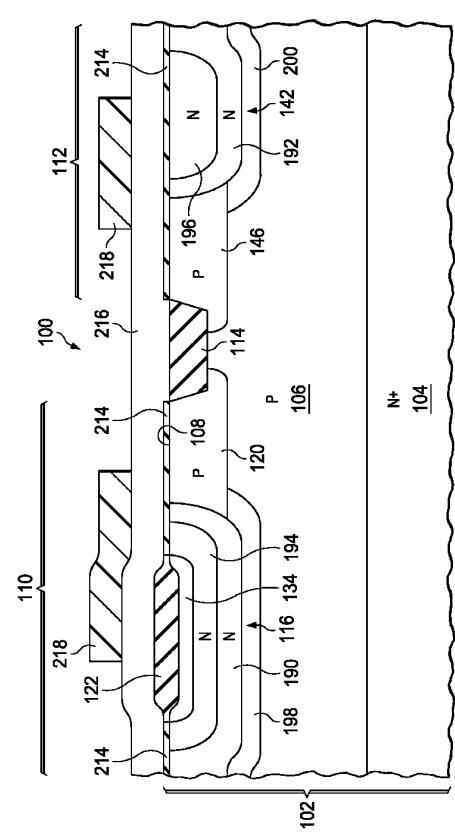

図2Dを参照すると、図2Cの注入されたn型ドーパント172を活性化及び拡散する任意選択の熱駆動動作が実施され得る。例えば、熱駆動動作は、約900～1050で30分～60分の傾斜ファーネスアニールを含み得る。図2Cの第1燐注入領域178における燐ドーパントは、第1開口164の下に第1燐拡散領域190を形成し、図2Cの第2燐注入領域180における燐ドーパントは、第2開口166の下に第2燐拡散領域192を形成する。同様に、図2Cの第1砒素注入領域182における砒素ドーパントは、第1開口164の下に第1砒素拡散領域194を形成し、図2Cの第2砒素注入領域184における砒素ドーパントは、第2開口166の下に第2砒素拡散領域196を形成する。第1燐拡散領域190及び第2燐拡散領域192は、有利にも、第1砒素拡散領域194及び第2砒素拡散領域196よりも深い。第1のディープ補償注入領域186及び第2のディープ補償注入領域188が図2Cを参照して説明したように形成される場合、任意選択の熱駆動動作が、図2Cの第1のディープ補償注入領域186における燐ドーパントを拡散及び活性化して、第1の燐拡散領域190の下及び周りの基板102において第1の補償領域198を形成し、図2Cの第2のディープ補償注入領域188における燐ドーパントを拡散及び活性化して、第2の燐拡散領域192の下及び周りの基板102における第2の補償領域200を形成する。任意選択の熱駆動動作の代わりに、図1のフィールド緩和酸化物122を形成するために、注入されたn型ドーパント172は、後続の熱酸化動作の間に活性化及び拡散され得る。

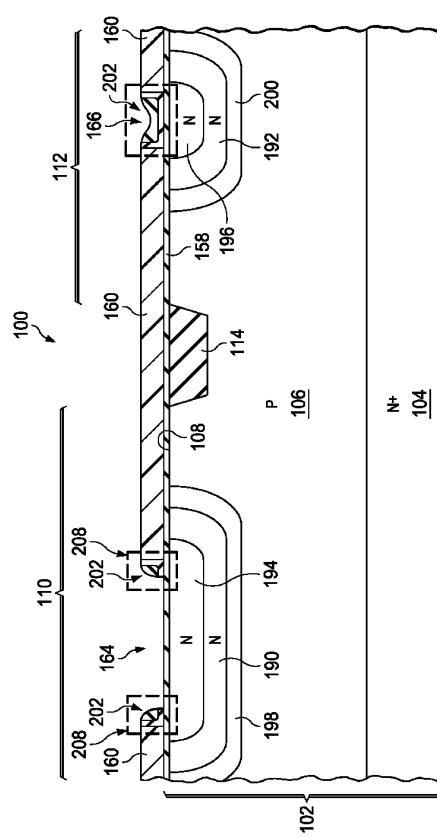

【0023】

図2Eを参照すると、コンフォーマル誘電体層202が、酸化物マスク160の上、及び、フィールドプレートタイプFET110のためのエリアにおける第1の開口164内、及びブレーナFET112のためのエリアにおける第2の開口166内に形成される。コンフォーマル誘電体層202は、誘電体材料の単一層を含んでもよいし、2つ以上の副層を含んでもよい。コンフォーマル誘電体層202は、窒化シリコン、二酸化シリコン、及び/又は他の誘電体材料を含み得る。図2Eに示すこの例のこのバージョンにおいて、コンフォーマル誘電体層202は、酸化物マスク160の層上及びパッド酸化物158上に形成される窒化シリコンの薄層204、並びに二酸化シリコンの薄層204上に形成される窒化シリコンの層206を含み得る。コンフォーマル誘電体層202の厚さは、酸化物マスク160の層の横方向端部上の第1の開口164におけるその後形成される誘電体側壁の所望の幅を提供するように、及び、第2の開口166を遮蔽するように選択される。例えば、コンフォーマル誘電体層202の厚さは、75ナノメートル～90ナノメートル幅の誘電体側壁が得られるように、80ナノメートル～100ナノメートルとし得る。第2の開口166の幅170が制限される結果、第2の開口166の中央におけるコンフォーマル誘電体層202は、第1の開口164の中央におけるコンフォーマル誘電体層202より厚い。コンフォーマル誘電体層202の窒化シリコンは、LPCVDプロセス、又はBTBASの分解によって形成され得る。コンフォーマル誘電体層202の二酸化シリコンは、TEOSの分解によって形成され得る。

【0024】

図2Fを参照すると、第1の開口164の中央部分からコンフォーマル誘電体層202を除去する異方性エッティングプロセスが実施されて、コンフォーマル誘電体層202の誘電体材料が残されて、酸化物マスク160の層の横方向の端部上の第1の開口164において誘電体側壁208が形成される。例えば、誘電体側壁208の幅は、第1の開口164の中央に形成されるコンフォーマル誘電体層202の厚さの50パーセント～90パーセントとし得る。異方性エッティングは、誘電体材料の連続部分が第2の開口166においてパッド酸化物158を覆うように、第2の開口166からコンフォーマル誘電体層202

10

20

30

40

50

の誘電体材料を全部は除去しない。

【0025】

図2Gを参照すると、誘電体側壁208及び酸化物マスク160の層を注入マスクとして用いて、電荷調整ドーパント210を基板102に注入する任意選択の電荷調整注入動作が実施され得る。注入された電荷調整ドーパント210は、第1の開口164の直ぐ下の基板102において電荷調整注入領域212を形成し、電荷調整注入領域212の横方向の広がりが誘電体側壁208によって画定され、有利にも、その後形成される図1の電荷調整領域134を、その後形成される図1のフィールド緩和酸化物122に自己整合する。第2の開口166に残るコンフォーマル誘電体層202の誘電体材料は、第2の開口166の下の基板102から電荷調整ドーパント210を遮蔽する。この例の1つのバージョンにおいて、電荷調整ドーパント210は、燐及び/又は砒素などのn型ドーパントとし得る。この例の別のバージョンでは、電荷調整ドーパント210は、ボロン、ガリウム、及び/又はインジウムなどのp型ドーパントとし得る。例えば、電荷調整ドーパント210のドーズ量は、 $1 \times 10^{10} \text{ cm}^{-2} \sim 1 \times 10^{12} \text{ cm}^{-2}$ とし得る。電荷調整ドーパント210は、注入されたドーパントのピークが、パッド酸化物158の下の基板102内に25ナノメートル～100ナノメートルにくるように、充分なエネルギーで注入され得る。

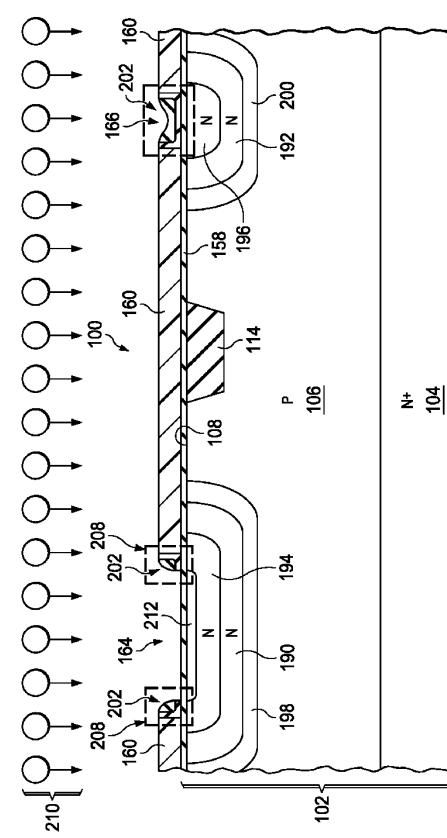

【0026】

図2Hを参照すると、フィールド緩和酸化物122が、フィールドプレートタイプFET110のためのエリアにおける第1の開口164において熱酸化によって形成される。誘電体側壁208及び酸化物マスク160の層の特性が、フィールド緩和酸化物122の横方向の縁におけるテーパプロファイル、すなわちバーズピーク、の長さ及び形状に影響を及ぼす。プレーナFET112のためのエリアにおける第2の開口166においては熱酸化は生じない。これは、第2の開口166に残るコンフォーマル誘電体層202の誘電体材料が熱酸化プロセスの酸化雰囲気を遮蔽するからである。例示のファーネス熱酸化プロセスは、2パーセント～10パーセントの酸素雰囲気で、45分～90分の時間期間でファーネスの温度を約1000まで傾斜上昇させること、雰囲気中の酸素を80パーセント～95パーセントの酸素に増加させながら、10分～20分の時間期間ファーネスの温度を約1000に維持すること、雰囲気中の酸素を80パーセント～95パーセントの酸素に維持し、この雰囲気に塩化水素ガスを添加しながら、60分～120分の時間期間ファーネスの温度を約1000に維持すること、塩化水素がない状態で、雰囲気中の酸素を80パーセント～95パーセントの酸素に維持しながら、ファーネスの温度を30分～90分の時間期間、約1000に維持すること、及び窒素雰囲気においてファーネスの温度を傾斜下降させることを含み得る。熱酸化プロセスのこの温度プロファイルにより、図2Gの電荷調整注入領域212における注入されたドーパントが拡散及び活性化されて、電荷調整領域134が形成される。また、熱酸化プロセスのこの温度プロファイルは、第1の燐拡散領域190、第2の燐拡散領域192、第1の砒素拡散領域194、及び第2の砒素拡散領域196のn型ドーパント、並びに、存在する場合は第1の補償領域198及び第2の補償領域200のn型ドーパント、をさらに拡散する。第1の砒素拡散領域194におけるn型ドーパントの大部分は砒素であり、第1の燐拡散領域190におけるn型ドーパントの大部分は燐である。同様に、第2の砒素拡散領域196におけるn型ドーパントの大部分は砒素であり、第2の燐拡散領域192におけるn型ドーパントの大部分は燐である。第1の燐拡散領域190及び第1の砒素拡散領域194は、フィールドプレートタイプFET110のドリフト領域116を提供する。同様に、第2の燐拡散領域192及び第2の砒素拡散領域196は、プレーナFET112のドリフト領域142を提供する。第1の補償領域198及び第2の補償領域200はp型であり、その正味ドーパント密度は、下にあるp型層106よりも低い。第1の補償領域198及び第2の補償領域200は、有利にも、それぞれ、フィールドプレートタイプFET110及びプレーナFET112のためのドレイン接合容量を低減させる。その後、酸化物マスク160の層、誘電体側壁208、及び第2の開口166に残るコンフォーマル誘電体層202の

10

20

30

40

50

誘電体側材料が除去される。窒化シリコンは、磷酸の水溶液によって除去され得る。二酸化シリコンは、バッファされた希釈フッ化水素酸の水溶液によって除去され得る。

【0027】

図2Iを参照すると、フィールドプレートタイプFET110のp型ボディ120及びプレーナFET112のp型ボディ146が、場合によっては同時に、形成される。ボディ120及びボディ146は、p型ドーパントの所望の分布が得られるように、ボロンなどのp型ドーパントを一又は複数のエネルギーで注入することによって形成され得る。例示の注入動作は、 $1 \times 10^{14} \text{ cm}^{-2} \sim 3 \times 10^{14} \text{ cm}^{-2}$ のドーズ量で、 $80 \text{ keV} \sim 150 \text{ keV}$ のエネルギーでのボロンの第1の注入、並びに $1 \times 10^{13} \text{ cm}^{-2} \sim 3 \times 10^{13} \text{ cm}^{-2}$ のドーズ量で $30 \text{ keV} \sim 450 \text{ keV}$ のエネルギーでのボロンの第2の注入を含み得る。1000で30秒間の高速熱アニールなどの後続のアニールプロセスにより、注入されたボロンが活性化及び拡散される。

10

【0028】

ゲート誘電体材料214の層が、フィールドプレートタイプFET110及びプレーナFET112のためのエリアを含めて、基板102の頂部表面108における露出された半導体材料上に形成される。ゲート誘電体材料214の層は、熱酸化によって形成される二酸化シリコン、及び/又は、CVDプロセスによって形成される酸化ハフニウム又は酸化ジルコニウムを含み得、窒素含有プラズマへの露出によって導入される窒素原子を含み得る。ゲート誘電体材料214の層の厚さは、フィールドプレートタイプFET110及びプレーナFET112の動作電圧を反映する。ゲート材料216の層が、ゲート誘電体材料214の層及びフィールド緩和酸化物122の上に形成される。例えば、ゲート材料216の層は、場合によってはn型ドーパントがドープされた状態で、本明細書でポリシリコンと称する多結晶シリコンを含み得る。ゲート材料216の層における窒化チタンなどの他のゲート材料も、この例の範囲内に含まれる。例えば、ゲート材料216の層におけるポリシリコンは、 $300 \text{ ナノメートル} \sim 800 \text{ ナノメートル}$ の厚さとし得る。

20

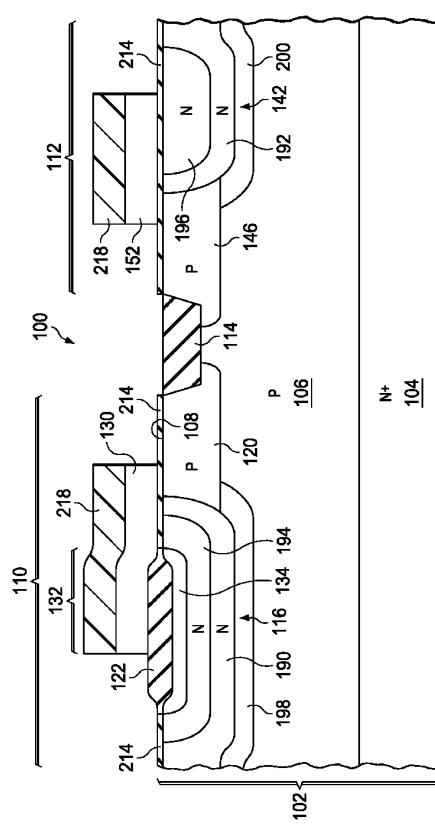

【0029】

フィールドプレートタイプFET110の図1のゲート130及びプレーナFET112の図1のゲート152のためのエリアを覆うように、ゲート材料216の層の上にゲートマスク218が形成される。この例では、ゲートマスク218は、フィールド緩和酸化物122の上を途中まで延在して、図1のフィールドプレート132のためのエリアを覆う。ゲートマスク218は、光リソグラフィプロセスによって形成されるフォトレジストを含み得る。ゲートマスク218は、窒化シリコン及び/又はアモルファスカーボンなどのハードマスク材料の層も含み得る。また、ゲートマスク218は、BARCの層などの反射防止材料の層を含み得る。

30

【0030】

図2Jを参照すると、フィールドプレートタイプFET110のゲート130を形成し、プレーナFET112のゲート152を形成するため、ゲートマスク218によって露出された図2Iのゲート材料216の層を除去するゲートエッチングプロセスが実施される。例えば、このゲートエッチングプロセスは、フッ素ラジカルを用いる反応性イオンエッチング(RIE)プロセスとし得る。ゲートマスク218は、ゲートエッチングプロセスによって腐食され得る。ゲート130及び152が形成された後、残りのゲートマスク218が除去される。

40

【0031】

図2Kを参照すると、図2Jのゲート誘電体材料214の層が、フィールドプレートタイプFET110のゲート誘電体層126、及びプレーナFET112のゲート誘電体層148を提供する。場合によっては窒化シリコン及び/又は二酸化シリコンの2つ以上の副層を含む、側壁材料のコンフォーマル層をゲート130及び基板102の頂部表面108の上に形成することによって、フィールドプレートタイプFET110のゲート130の側部表面上にゲート側壁スペーサ138が形成され得る。その後、RIEプロセスなどの異方性エッチングにより、ゲート130及び基板102の頂部表面から側壁材料の層が除

50

去されて、ゲート側壁スペーサ 138 が適所に残る。プレーナ FET 112 のゲート 152 上のゲート側壁スペーサ 156 は、フィールドプレートタイプ FET 110 のゲート側壁スペーサ 138 と同様に、場合によってはそれと同時に、形成され得る。

【0032】

フィールドプレートタイプ FET 110 の n 型ソース 128 及び n 型ドレインコンタクト領域 118 が、燐及び砒素などの n 型ドーパントを、例えば  $1 \times 10^{14} \text{ cm}^{-2} \sim 5 \times 10^{15} \text{ cm}^{-2}$  のドーズ量で、ゲート 130 及びフィールド緩和酸化物 122 の近隣の基板 102 に注入することによって形成され得る。その後、注入されたドーパントを活性化するため、スパイクアニール又はフラッシュアニールなどのアニール動作が続く。ゲート側壁スペーサ 138 を形成する前に、ゲート 130 の下を途中まで延在するソース 128 の n 型ドレイン拡張部が、ゲート 130 に近隣の基板に n 型ドーパントを注入することによって形成され得る。プレーナ FET 112 の n 型ソース 150 及び n 型ドレインコンタクト領域 144 は、フィールドプレートタイプ FET 110 のソース 128 及びドレインコンタクト領域 118 と同様に、場合によってはそれと同時に、形成され得る。

10

【0033】

フィールドプレートタイプ FET 110 のボディ 120 における p 型ボディコンタクト領域 136 が、例えば  $1 \times 10^{14} \text{ cm}^{-2} \sim 5 \times 10^{15} \text{ cm}^{-2}$  のドーズ量で、基板 102 に p 型ドーパント（例えばボロン）を注入することによって形成され得る。その後、注入されたドーパントを活性化するため、スパイクアニール又はフラッシュアニールなどのアニール動作が続く。プレーナ FET 112 のボディ 146 における p 型ボディコンタクト領域 136 は、フィールドプレートタイプ FET 110 のボディ 120 におけるボディコンタクト領域 136 と同様に、場合によってはそれと同時に、形成され得る。

20

【0034】

フィールド緩和酸化物 122 に自己整合されるようにドリフト領域 116 を形成することにより、ゲート 130 がドリフト領域 116 に重なる横方向距離 124 が所望の小さな値になり、有利にも、低ゲート - ドレイン容量を提供する。また、この自己整合構成により、デバイス毎に制御可能な横方向距離 124 が提供され得、整合誤差と称することもある、不可避な光リソグラフィ整合ばらつきによる望まれない変動は生じない。

【0035】

図 3A ~ 図 3F は、フィールドプレートタイプ FET を含む別の例示の集積回路の断面であり、例示の形成方法の連続的段階で示す。この例では、n チャネルフィールドプレートタイプ FET を説明する。ドーパントの極性を適切に変更することで、類似の p チャネルフィールドプレートタイプを説明し得る。図 3A を参照すると、集積回路 300 が、p 型層 306 を備える基板 302 を含み、p 型層 306 は基板 302 の頂部表面 308 まで延在する。p 型層 306 は、半導体ウェハ上のエピタキシャル層とし得、又はバルクシリコンウェハの頂部とし得る。集積回路 300 は、この例では対照的なドレイン中心構成を有する、n チャネルフィールドプレートタイプ FET 310 を含む。集積回路 300 は、任意選択で、図 3A ~ 図 3F には示さないプレーナ FET も含み得る。この例では、集積回路 300 は、フィールドプレートタイプ FET 310 のためのエリアの周りにフィールド緩和酸化物 314 を含む。フィールド酸化物 314 は、図 2A を参照して説明したように、STI プロセスによって形成される。この STI プロセスは、基板 302 の頂部表面 308 の上の STI パッド酸化物 420 の層、及び STI パッド酸化物 420 の層の上の窒化シリコンの CMP 停止層 422 を用いる。この例では、フィールド酸化物 314 を形成した後、STI パッド酸化物 420 の層及び CMP 停止層 422 は、除去されず、フィールドプレートタイプ FET 310 を形成するために用いられる。

30

40

【0036】

STI パッド酸化物 420 の層、及び CMP 停止層 422 は、フィールドプレートタイプ FET 310 のためのエリアにわたって延在する。フィールドプレートタイプ FET 310 のためのエリアにおいてその後形成されるフィールド緩和酸化物のためのエリアを露出させる CMP 停止層 422 の上に、エッティングマスク 362 が形成される。エッティングマ

50

スク 3 6 2 は、図 2 A を参照して説明したように形成され得る。フィールド緩和酸化物のための露出エリアの横方向寸法は、C M P 停止層 4 2 2 をエッティングした後、エッティングされたエリアの中央部分が誘電体側壁の形成後に空のまま残るよう、充分に幅広い。

【 0 0 3 7 】

図 3 B を参照すると、エッティングマスク 3 6 2 によって露出されたエリアにおいて C M P 停止層 4 2 2 が除去されて、S T I パッド酸化物 4 2 0 の層が露出され、C M P 停止層 4 2 2 に開口 3 6 4 が形成される。開口 3 6 4 の横方向寸法 3 6 8 は、誘電体側壁の形成後、開口 3 6 4 の中央部分が空のままであるよう、充分に幅広い。C M P 停止層 4 2 2 は、図 3 B に示すように、アンダーカットが極めて小さくなり得るフッ素ラジカルを用いるプラズマエッティングによって除去され得る。或いは、C M P 停止層 4 2 2 は、図 2 B を参考して説明したように、ウェットエッティングによって除去され得る。

10

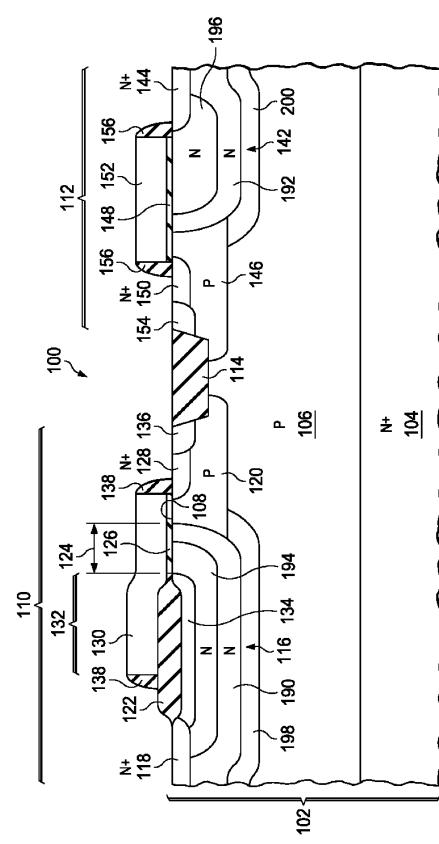

【 0 0 3 8 】

n 型ドーパント 3 7 2 が、フィールドプレートタイプ F E T 3 1 0 のためのエリアにおける開口 3 6 4 を含めて、C M P 停止層 4 2 2 を除去することによって露出されたエリアにおいて基板 3 0 2 に注入され、有利にも、その後形成されるドリフト領域を、その後形成されるフィールド緩和酸化物に自己整合させる。例えば、n 型ドーパント 3 7 2 は、図 2 C を参考して説明したように燐及び砒素を含み得る。注入された n 型ドーパント 3 7 2 は、開口 3 6 4 の下にドリフト注入領域 4 2 4 を形成する。エッティングマスク 3 6 2 の残りの部分はすべて、n 型ドーパント 3 7 2 が注入された後、除去される。

20

【 0 0 3 9 】

図 3 C を参照すると、図 2 E 及び図 2 F を参考して説明したように、C M P 停止層 4 2 2 の横方向端部上の開口 3 6 4 に誘電体側壁 4 0 8 が形成される。開口 3 6 4 内の誘電体側壁 4 0 8 と同時に、C M P 停止層 4 2 2 の横方向端部上でフィールド酸化物 3 1 4 の上に付加的な側壁 4 2 6 が形成され得る。開口 3 6 4 の中央部分は、誘電体側壁 4 0 8 が形成された後、空になる。

【 0 0 4 0 】

図 3 D を参考すると、フィールドプレートタイプ F E T 3 1 0 のためのエリアにおける開口 3 6 4 にフィールド緩和酸化物 3 2 2 が熱酸化によって形成される。誘電体側壁 4 0 8 及び C M P 停止層 4 2 2 の特性がフィールド緩和酸化物 3 2 2 の横方向端部の長さ及び形状に影響を及ぼす。フィールド緩和酸化物 3 2 2 は、図 2 H を参考して説明したようにファーネス熱酸化プロセスによって形成され得る。熱酸化プロセスの温度プロファイルにより、図 3 C のドリフト注入領域 4 2 4 における注入された n 型ドーパントが拡散され活性化されて、フィールドプレートタイプ F E T 3 1 0 のドリフト領域 3 1 6 が形成される。その後、C M P 停止層 4 2 2 、誘電体側壁 4 0 8 、及び付加的な側壁 4 2 6 が除去される。

30

【 0 0 4 1 】

図 3 E を参考すると、フィールド緩和酸化物 3 2 2 に対して中央に位置するドリフト領域 3 1 6 の下の基板 3 0 2 において、n 型ウェル 4 2 8 が任意選択で形成され得る。n 型ウェル 4 2 8 は、有利にも、フィールドプレートタイプ F E T 3 1 0 のドレイン抵抗を低減し得、フィールドプレートタイプ F E T 3 1 0 のドレインの中央部分を流れる電流を広げさせ得、信頼性が改善される。n 型ウェル 4 2 8 は、集積回路 3 0 0 の論理回路内の p チャネル金属酸化物半導体 ( P M O S ) ランジスタの下の他の n 型ウェルと同時に形成され得る。ドリフト領域 3 1 6 に接する基板 3 0 2 において、フィールドプレートタイプ F E T 3 1 0 の p 型ボディ 3 2 0 が形成される。ボディ 3 2 0 は、図 2 I を参考して説明したように、ボロンなどの p 型ドーパントを注入することによって形成され得る。後続のアーチルプロセスにより、注入されたボロンが活性化され拡散する。

40

【 0 0 4 2 】

図 3 D の S T I パッド酸化物 4 2 0 の層が除去される。フィールド緩和酸化物 3 2 2 に近隣の基板 3 0 2 の頂部表面 3 0 8 において、ゲート誘電体層 3 2 6 が形成される。ゲート誘電体層 3 2 6 は、図 2 I を参考して説明したように形成され得る。フィールドプレートタイプ F E T 3 1 0 のゲート 3 3 0 が、フィールド緩和酸化物 3 2 2 の近傍から、ボディ

50

320の途中まで重なって延在して、ゲート誘電体層326の上に形成される。ゲート330は、ドリフト領域の、フィールド緩和酸化物322とボディ320との間の部分の上に延在する。ゲート330は、図2I及び図2Jを参照して説明したように形成され得る。

【0043】

図2Kを参照して例えれば説明したように、ゲート330の側部表面上にゲート側壁スペーサ338が形成される。この例では、ゲート330の頂部表面の上に、誘電体材料のゲートキャップ430が形成される。ゲートキャップ430及びゲート側壁スペーサ338は、ゲート330の頂部表面と横方向の面とを電気的に絶縁する。ゲートキャップ430は、例えば、ゲートマスクを形成しゲートエッチングを実施する前にゲート材料の層の上に誘電体層を形成することなどによって、形成され得る。

10

【0044】

図3Fを参照すると、フィールド緩和酸化物322の2つの対向部分間のドリフト領域316内の基板302において、n型ドレインコンタクト領域318が形成される。ドレインコンタクト領域318と反対のゲート330の近隣の基板302において、n型ソース328が形成される。ドレインコンタクト領域318及びソース328は、図2Kを参照して説明したように形成され得、同時に形成され得る。ゲート側壁スペーサ338が形成される前に、ゲート330の下を途中まで延在する、ソース328のn型ドレイン拡張部が形成され得る。

【0045】

この例では、フィールドプレート432がフィールド緩和酸化物322の一部の直ぐ上に形成され、ゲート330まで延在する。フィールドプレート432は、ゲート330から電気的に絶縁される。フィールドプレート432は、ゲート330及びフィールド緩和酸化物322の上に、ポリシリコン又は窒化チタンなどの導電材料の層を形成すること、フィールドプレート432のためのエリアを覆うために導電材料の層の上にエッチングマスクを形成すること、及び、フィールドプレート432を画定するためのエッチングプロセスを実施することによって形成され得る。集積回路300は、ゲート330及びフィールドプレート432に別々のバイアス電圧を印加するように構成され得る。ゲート330と電気的に絶縁され、別々にバイアスされ得るようにフィールドプレート432を形成することによって、フィールドプレートを提供するためにゲートに重なるフィールド緩和酸化物を備える類似のフィールドプレートタイプFETと比較して、有利にも、フィールドプレートタイプFET310の動作の間のドリフト領域316における電界が低減され得る。

20

【0046】

ドリフト領域316は、フィールドプレートタイプFET310の第1の側で第1の横方向距離434、フィールド緩和酸化物322を超えて延在し、第1の側と反対の第2の側で第2の横方向距離436、フィールド緩和酸化物322を超えて延在する。ドリフト領域316がフィールド緩和酸化物322と自己整合されるように形成される結果、第1の横方向距離434が第2の横方向距離436と実質的に等しくなり、これは、有利にも、フィールドプレートタイプFET310を通じて均一な電流分布を提供する。また、フィールド緩和酸化物322と自己整合されるようにドリフト領域316を形成することによって、有利にも、デバイス毎に制御可能な第1の横方向距離434及び第2の横方向距離436が所望の狭い範囲内の値になり、その際、整合誤差と称することもある不可避な光リソグラフィ整合のばらつきによる望まれない変動は生じない。

30

【0047】

特許請求の範囲内で、説明した実施形態において改変が可能であり、他の実施形態が可能である。

40

50

【図面】

【図 1】

FIG. 1

## 【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図2C】

FIG. 2C

【図 2 D】

FIG. 2D

【図 2 E】

FIG. 2E

10

20

30

40

【図 2 F】

FIG. 2F

【図 2 G】

FIG. 2G

50

【図 2 H】

FIG. 2H

【図 2 I】

FIG. 2I

10

20

30

40

【図 2 J】

FIG. 2J

【図 2 K】

FIG. 2K

50

【図3A】

FIG. 3A

【図3B】

FIG. 3B

### 【図3C】

FIG. 3C

【図3D】

FIG. 3D

【図3E】

### 【図3F】

---

フロントページの続き

ライブ 4313

(72)発明者 ジェームズ ロバート トッド

アメリカ合衆国 75025 テキサス州 プレイノ, ワースランド ドライブ 7712

審査官 綿引 隆

(56)参考文献 特開平10-050997 (JP, A)

米国特許出願公開第2010/0102388 (US, A1)

特開平07-078990 (JP, A)

米国特許第04795716 (US, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/336

H01L 21/8234

H01L 27/088

H01L 29/78