(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4987607号

(P4987607)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.CI.

H03K 19/0185 (2006.01)

F 1

H03K 19/00 101D

請求項の数 12 (全 16 頁)

(21) 出願番号 特願2007-193516 (P2007-193516)

(22) 出願日 平成19年7月25日 (2007.7.25)

(65) 公開番号 特開2009-33329 (P2009-33329A)

(43) 公開日 平成21年2月12日 (2009.2.12)

審査請求日 平成22年4月19日 (2010.4.19)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100080816

弁理士 加藤 朝道

(72) 発明者 久家 弘之

神奈川県川崎市中原区小杉町 1 丁目 403

番 53 NECマイクロシステム株式会社

内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】 レベルシフト回路

## (57) 【特許請求の範囲】

## 【請求項 1】

接地と第1の電源電圧間の振幅レベルである入力信号を、接地と第2の電源電圧間の振幅レベルである出力信号に変換するレベルシフト回路であって、

前記入力信号の立ち上がりで第1のパルス信号を立ち上げ、前記入力信号の立ち下がりで前記第1のパルス信号と同極性の第2のパルス信号を立ち上げる、前記第1の電源電圧で動作する入力部と、

前記第1のパルス信号の信号レベルを前記第2の電源電圧の振幅レベルに変換する第1のレベル変換回路と、前記第2のパルス信号の信号レベルを前記第2の電源電圧の振幅レベルに変換する第2のレベル変換回路とを含むレベルシフト部と、

前記レベル変換された第1および第2のパルス信号に対応して駆動され、前記出力信号を生成する、前記第2の電源電圧で動作する出力部と、

前記生成された出力信号のレベルを保持する、前記第2の電源電圧で動作する保持部と、

を備え、

前記入力部は、前記第1のパルス信号を前記出力信号の立ち上がりに応じて立ち下げ、前記第2のパルス信号を前記出力信号の立ち下がりに応じて立ち下げるよう構成されることを特徴とするレベルシフト回路。

## 【請求項 2】

前記入力部は、前記入力信号と前記出力信号との論理レベルの一致不一致を判断して不

一致である時に、前記入力信号の立ち上がりエッジに対応して前記第1のパルス信号を立ち上げ、かつ前記入力信号の立ち下がりエッジに対応して前記第2のパルス信号を立ち上げるように構成され、

前記出力部は、前記第1および第2のパルス信号の立ち上がりタイミングに対応して前記出力信号の論理レベルが遷移するように構成されることを特徴とする請求項1記載のレベルシフト回路。

#### 【請求項3】

前記第1および第2のレベル変換回路のそれぞれは、

ゲートにそれぞれ前記第1および第2のパルス信号を供給し、ソースを第1の電源に接続し、ドレインからレベル変換されたパルス信号を出力する第1導電型トランジスタと

10

ゲートを前記第1導電型トランジスタのゲートに接続し、ドレインを前記第1導電型トランジスタのドレインに接続し、ソースをトランジスタ接続群を介して第2の電源に接続する第1の第2導電型トランジスタと、

を備え、

前記トランジスタ接続群は、1乃至2以上の第2導電型のトランジスタで構成されることを特徴とする請求項1記載のレベルシフト回路。

#### 【請求項4】

前記トランジスタ接続群は、ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第2の第2導電型トランジスタであることを特徴とする請求項3記載のレベルシフト回路。

20

#### 【請求項5】

前記トランジスタ接続群は、

ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第1の第2導電型トランジスタのソースに接続する第2の第2導電型トランジスタと、

ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第2の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第3の第2導電型トランジスタと、

からなることを特徴とする請求項3記載のレベルシフト回路。

30

#### 【請求項6】

前記トランジスタ接続群は、

ゲートに前記第1導電型トランジスタのドレインの反転信号を供給し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第2の第2導電型トランジスタと、

ゲートに前記出力信号に係る信号を供給し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第3の第2導電型トランジスタと、

からなり、

前記トランジスタ接続群が前記第1のレベル変換回路に含まれる場合、前記第3の第2導電型トランジスタのゲートは、前記出力信号の反転信号が供給され、

40

前記トランジスタ接続群が前記第2のレベル変換回路に含まれる場合、前記第3の第2導電型トランジスタのゲートは、前記出力信号が供給されることを特徴とする請求項3記載のレベルシフト回路。

#### 【請求項7】

入力信号の立ち上がりで第1のパルス信号を生成し、該入力信号の立ち下がりで該第1のパルス信号と同極性の第2のパルス信号を生成する入力部と、

前記第1のパルス信号の信号レベルを変換する第1のレベル変換回路と、前記第2のパルス信号の信号レベルを変換する第2のレベル変換回路とを含むレベルシフト部と、

前記レベル変換された第1および第2のパルス信号に対応して駆動され、出力信号を生

50

成する出力部と、

前記生成された出力信号のレベルを保持する保持部と、

を備え、

前記入力部は、前記生成した第1および第2のパルス信号を前記出力信号によって立ち下げるように構成されることを特徴とするレベルシフト回路。

**【請求項8】**

前記入力部は、前記入力信号と前記出力信号との論理レベルの一致不一致を判断して不一致である時に、前記入力信号の立ち上がりエッジに対応して前記第1のパルス信号を生成し、かつ前記入力信号の立ち下がりエッジに対応して前記第2のパルス信号を生成するように構成され、

10

前記出力部は、前記第1および第2のパルス信号の生成タイミングに対応して前記出力信号の論理レベルが遷移するように構成されることを特徴とする請求項7記載のレベルシフト回路。

**【請求項9】**

前記第1および第2のレベル変換回路のそれぞれは、

ゲートにそれぞれ前記第1および第2のパルス信号を供給し、ソースを第1の電源に接続し、ドレインからレベル変換されたパルス信号を出力する第1導電型トランジスタと、

ゲートを前記第1導電型トランジスタのゲートに接続し、ドレインを前記第1導電型トランジスタのドレインに接続し、ソースをトランジスタ接続群を介して第2の電源に接続する第1の第2導電型トランジスタと、

20

を備え、

前記トランジスタ接続群は、1乃至2以上の第2導電型のトランジスタで構成されることを特徴とする請求項7記載のレベルシフト回路。

**【請求項10】**

前記トランジスタ接続群は、ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第2の第2導電型トランジスタであることを特徴とする請求項9記載のレベルシフト回路。

**【請求項11】**

30

前記トランジスタ接続群は、

ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第1の第2導電型トランジスタのソースに接続する第2の第2導電型トランジスタと、

ゲートを前記第1導電型トランジスタのゲートまたは接地に接続し、ドレインを前記第2の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第3の第2導電型トランジスタと、

からなることを特徴とする請求項9記載のレベルシフト回路。

**【請求項12】**

前記トランジスタ接続群は、

ゲートに前記第1導電型トランジスタのドレインの反転信号を供給し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第2の第2導電型トランジスタと、

40

ゲートに前記出力信号に係る信号を供給し、ドレインを前記第1の第2導電型トランジスタのソースに接続し、ソースを前記第2の電源に接続する第3の第2導電型トランジスタと、

からなり、

前記トランジスタ接続群が前記第1のレベル変換回路に含まれる場合、前記第3の第2導電型トランジスタのゲートは、前記出力信号の反転信号が供給され、

前記トランジスタ接続群が前記第2のレベル変換回路に含まれる場合、前記第3の第2導電型トランジスタのゲートは、前記出力信号が供給されることを特徴とする請求項9記

50

載のレベルシフト回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源電圧の異なる回路間でインターフェースとして機能するレベルシフト回路に関する。

【背景技術】

【0002】

モバイル製品等で低消費電力化のために半導体装置の内部コア電圧の低電圧対応が必須である。I/Oバッファにおいては、内部コア電圧とI/O電圧間でのレベルシフトが不可欠である。このようなI/Oバッファに適用可能なレベルシフト回路が特許文献1に開示されている。

10

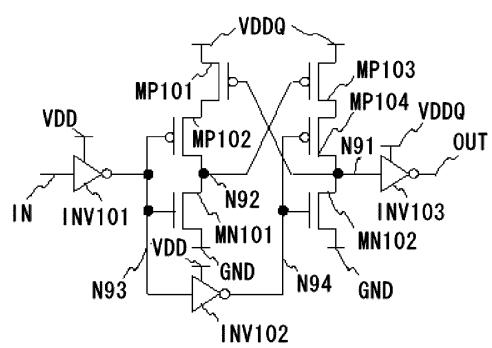

【0003】

図8は、特許文献1のレベルシフト回路の回路図である。図8において、レベルシフト回路は、PMOSトランジスタMP101、MP102、MP103、MP104、NMOSトランジスタMN101、MN102、インバータINV101、INV102、INV103から構成される。PMOSトランジスタMP101は、ソースを電源VDDQに接続し、ゲートを複掛け部の出力ノードN91を接続する。PMOSトランジスタMP102は、ソースをPMOSトランジスタMP101のドレインに接続し、ゲートをインバータINV101の出力であるノードN93に接続する。NMOSトランジスタMN101は、ソースを接地し、ドレインをPMOSトランジスタMP102のドレインであるノードN92に接続し、ゲートをインバータINV101の出力であるノードN93に接続する。

20

【0004】

PMOSトランジスタMP103は、ソースを電源VDDQに接続し、ゲートをノードN92に接続する。PMOSトランジスタMP104は、ソースをPMOSトランジスタMP103のドレインに接続し、ゲートをインバータINV102の出力であるノードN94に接続する。NMOSトランジスタMN102は、ソースを接地し、ドレインをPMOSトランジスタMP104のドレインである複掛け部の出力ノードN91に接続し、ゲートをノードN94に接続する。

30

【0005】

インバータINV101は、入力を入力端子INに接続し、電源電圧はVDDである。インバータINV102は、入力をインバータINV101の出力であるノードN93に接続し、電源電圧はVDDである。インバータINV103は、入力を複掛け部の出力ノードN91に接続し、出力を出力端子OUTに接続し、電源電圧はVDDQである。

【0006】

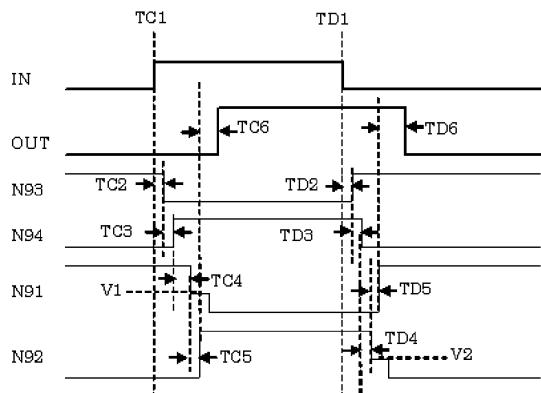

図9は、図8のレベルシフト回路のタイミングチャートである。まず、ノードINが立ち上がった時に関して動作を説明する。また、VDD=1.2V、VDDQ=1.8Vとして以下説明を行う。

40

【0007】

時刻TC1において、ノードINが立ち上るとインバータINV101によって信号が反転し、インバータINV101の遅延時間TC2後にノードN93が立ち下がる。従って、NMOSトランジスタMN101、PMOSトランジスタMP102のゲートには立ち下がり信号が与えられる。また、インバータINV102で再度信号が反転してインバータINV102の遅延時間TC3後にノードN94は立ち上がる。従って、NMOSトランジスタMN102、PMOSトランジスタMP104のゲートには、立ち上がり信号が与えられる。この時、NMOSトランジスタMN102がオンする為、遅延時間TC4後にノードN91の電圧は低下する。

【0008】

しかしながら、PMOSトランジスタMP104の入力信号であるゲートにはVDD=

50

1 . 2 V のレベルまでしか上昇せず、PMOSトランジスタMP104は完全なオフ状態とはならない。したがって、ノードN91の電圧は、PMOSトランジスタMP103、MP104とNMOSトランジスタMN102とのオン抵抗の分圧電圧であるV1まで引き下がることになる。これに伴い、遅延時間TC5後にPMOSトランジスタMP101がオン状態となり、この時NMOSトランジスタMN101とPMOSトランジスタMP102のゲートには、立ち下がり信号が入力されている。したがって、NMOSトランジスタMN101はオフ、PMOSトランジスタMP102はオン状態となり、ノードN92の電圧は、VDDQ = 1 . 8 V レベルまで上昇する。これに伴いPMOSトランジスタMP103は、完全なオフ状態となりノードN91は0 Vまで引き下がり、インバータINV103の遅延時間TC6後、出力端子OUTは立ち上がる。

10

#### 【0009】

次に、ノードINが立ち下がった時に關して動作を説明する。時刻TD1において、ノードINが立ち下がるとインバータINV101によって信号が反転し、ノードN93がインバータINV101の遅延時間TD2後に立ち上がる。従って、NMOSトランジスタMN101、PMOSトランジスタMP102のゲートには、立ち上がり信号が与えられる。また、インバータINV102で再度信号が反転してインバータINV102の遅延時間TD3後にノードN94は立ち下がる。従って、NMOSトランジスタMN102、PMOSトランジスタMP104のゲートには、立ち下がり信号が与えられる。この時、NMOSトランジスタMN101がオンする為、遅延時間TD4後にノードN92の電圧は低下する。

20

#### 【0010】

しかしながら、PMOSトランジスタMP102の入力信号であるゲートは、VDD = 1 . 2 V のレベルまでしか上昇せず、PMOSトランジスタMP102は、完全なオフ状態とはならない。したがって、ノードN92の電圧は、PMOSトランジスタMP101、MP102とNMOSトランジスタMN101とのオン抵抗の分圧電圧であるV2まで引き下がることになる。それに伴い、遅延時間TD5後にPMOSトランジスタMP103がオン状態となり、この時NMOSトランジスタMN102とPMOSトランジスタMP104のゲートには、立ち下がり信号が入力されている。したがって、NMOSトランジスタMN102はオフ、PMOSトランジスタMP104はオン状態となり、ノードN91の電圧は、VDDQ = 1 . 8 V レベルまで上昇する。それに伴いPMOSトランジスタMP101は、完全なオフ状態となりノードN92は0 Vまで引き下がり、インバータINV103の遅延時間TD6後、出力端子OUTは立ち下がる。

30

#### 【0011】

なお、関連する技術として、特許文献2には、貫通電流を流さず、消費電力を少なくできるレベルシフタが記載されている。

#### 【0012】

また、関連する技術として、特許文献3には、レベル変換にラッチ構造を採用せずに低消費電力で、かつ高速動作するレベルシフト回路が記載されている。

#### 【0013】

【特許文献1】米国特許第4845381号明細書

40

【特許文献2】特開2004-363740号公報

【特許文献3】特開2004-7821号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

ところで、図8のレベルシフト回路において、時刻TD1以降、ノードN92の電圧が充分低くなることによってノードN91は、立ち上がる。ノードN92の電圧は、PMOSトランジスタMP101、MP102とNMOSトランジスタMN101とのオン抵抗の分圧値である。したがって、NMOSトランジスタMN101のオン抵抗が大きくなると、ノードN92の電圧は、充分に低い電圧まで下がらなくなり、ノードN91が立ち上

50

がらないという状態が生じる。VDDの低下、つまりNMOSトランジスタMN101のゲート電圧の低下は、NMOSトランジスタMN101のオン抵抗が大きくなる要因である。したがって、VDDが低くなるほどノードN91の立ち上がり特性が悪化する。この回路は左右対称であるので、ノードN92の立ち上がり特性に関しても同様なことがいえる。

#### 【0015】

そこで、NMOSトランジスタMN101、MN102のWサイズを大きくすることと、VDDが低い時でもレベルシフトを行うことが可能であると考えられる。すなわち、NMOSトランジスタMN101、MN102のWサイズを大きくすればオン抵抗が小さくなる。これにより、VDDが低くなつてもノードN91、N92の電圧を充分に低くすることができるるのでレベルシフト動作可能となる。10

#### 【0016】

しかしながら、この方法には、弊害がある。それは、PMOSトランジスタMP101、MP102、MP103、MP104のWサイズを大きくすることが出来ず、ノードN91、N92の立ち上がり特性が悪くなってしまうことである。PMOSトランジスタMP101、MP102、MP103、MP104のWサイズを大きくできないのは、大きくなるとノードN91、N92の電圧が高くなってしまうからである。

#### 【0017】

一方、NMOSトランジスタMN101、MN102は、Wサイズを大きくしているので、ノードN91、N92の立ち下がり特性は、良化する。したがって、低電圧でも動作するようなトランジスタのディメンジョンを採用すると、立ち上がり／立ち下がりのバランスが悪くなる。このため、回路のジッタ特性が悪化し、レベルシフトの高速動作が出来なくなる。例えば、昨今のメモリインターフェース規格であるDDR2バッファの場合、数十psのジッタの変動が、特性に影響されることが知られており、立ち上がり／立ち下がりのバランスが悪くなり数十psの差が生じた場合には、そのままジッタの悪化につながることになる。20

#### 【0018】

以上の問題は、ノードINが立ち上がった時と立ち下がった時とで、動作に関するトランジスタが異なり、各トランジスタに能力差があることによって生じている。これらの欠点を補う回路として、立ち上がり時も立ち下がり時も、動作するトランジスタが、出来るだけ同じ種類でかつ同じサイズのものでレベルシフト動作をさせることが望ましい。この目的に合った回路として、本来の目的とは異なるが、特許文献2の技術を適用することができる。しかしながら、特許文献2の回路を、本発明で解決しようとしている低電圧動作特性の改善に適用した場合、コンデンサによる動作であるため、周囲からの外部ノイズに弱く、信頼性上、誤動作による回路の不安定さが生じてしまう。また、ノイズ対策でガードリングなど設ければ部品点数が増えてしまう。また、この回路のコンデンサをLSIチップ上に配置することは、通常のロジック素子を配置する面積に比べ、数十倍の面積を有し、ロックサイズ増大の懸念が考えられる。30

#### 【課題を解決するための手段】

#### 【0019】

本発明の1つのアспектに係るレベルシフト回路は、接地と第1の電源電圧間の振幅レベルである入力信号を、接地と第2の電源電圧間の振幅レベルである出力信号に変換するレベルシフト回路であって、入力信号の立ち上がりで第1のパルス信号を立ち上げ、入力信号の立ち下がりで第1のパルス信号と同極性の第2のパルス信号を立ち上げる、第1の電源電圧で動作する入力部と、第1のパルス信号の信号レベルを第2の電源電圧の振幅レベルに変換する第1のレベル変換回路と、第2のパルス信号の信号レベルを第2の電源電圧の振幅レベルに変換する第2のレベル変換回路とを含むレベルシフト部と、レベル変換された第1および第2のパルス信号に対応して駆動され、出力信号を生成する、第2の電源電圧で動作する出力部と、生成された出力信号のレベルを保持する、第2の電源電圧で動作する保持部と、を備え、入力部は、第1のパルス信号を出力信号の立ち上がりに応4050

じて立ち下げる、第2のパルス信号を出力信号の立ち下がりに応じて立ち下げるよう構成される。

本発明の他のアスペクトに係るレベルシフト回路は、入力信号の立ち上がりで第1のパルス信号を生成し、入力信号の立ち下がりで第1のパルス信号と同極性の第2のパルス信号を生成する入力部と、第1のパルス信号の信号レベルを変換する第1のレベル変換回路と、第2のパルス信号の信号レベルを変換する第2のレベル変換回路とを含むレベルシフト部と、レベル変換された第1および第2のパルス信号に対応して駆動され、出力信号を生成する出力部と、生成された出力信号のレベルを保持する保持部と、を備え、入力部は、生成した第1および第2のパルス信号を出力信号によって立ち下げるよう構成される。

10

### 【発明の効果】

#### 【0020】

本発明によれば、第1のおよび第2のパルス信号の信号レベルを第1および第2のレベル変換回路によって変換し出力信号を生成するので、出力信号における立ち上がりと立下がりの遅延時間のバランスを良くすることができる。したがって、レベルシフトを高速に動作させることができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

本発明の実施形態に係るレベルシフト回路は、入力部と、レベルシフト部と、出力部と、保持部と、を備える。入力部は、入力信号の立ち上がりで第1のパルス信号を生成し、入力信号の立ち下がりで第1のパルス信号と同極性の第2のパルス信号を生成し、生成した第1および第2のパルス信号を出力信号によって立ち下げる。レベルシフト部は、第1のパルス信号の信号レベルを変換する第1のレベル変換回路と、第2のパルス信号の信号レベルを変換する第2のレベル変換回路とを含む。出力部は、レベル変換された第1および第2のパルス信号に対応して駆動され、出力信号を生成する。保持部は、生成された出力信号のレベルを保持する。

20

#### 【0022】

本発明のレベルシフト回路において、入力部は、入力信号と出力信号との論理レベルの一一致不一致を判断して不一致である時に、入力信号の立ち上がりエッジに対応して第1のパルス信号を生成し、かつ入力信号の立ち下がりエッジに対応して第2のパルス信号を生成するように構成され、出力部は、第1および第2のパルス信号の生成タイミングに対応して出力信号の論理レベルが遷移するように構成されることが好ましい。

30

#### 【0023】

本発明のレベルシフト回路において、第1および第2のレベル変換回路のそれぞれは、ゲートにそれぞれ第1および第2のパルス信号を供給し、ソースを第1の電源に接続し、ドレインからレベル変換されたパルス信号を出力する第1導電型トランジスタと、ゲートを第1導電型トランジスタのゲートに接続し、ドレインを第1導電型トランジスタのドレインに接続し、ソースをトランジスタ接続群を介して第2の電源に接続する第1の第2導電型トランジスタと、を備え、トランジスタ接続群は、1乃至2以上の第2導電型のトランジスタで構成されることが好ましい。

40

#### 【0024】

本発明のレベルシフト回路において、トランジスタ接続群は、ゲートを第1導電型トランジスタのゲートまたは接地に接続し、ドレインを第1の第2導電型トランジスタのソースに接続し、ソースを第2の電源に接続する第2の第2導電型トランジスタであってもよい。

#### 【0025】

本発明のレベルシフト回路において、トランジスタ接続群は、ゲートを第1導電型トランジスタのゲートまたは接地に接続し、ドレインを第1の第2導電型トランジスタのソースに接続する第2の第2導電型トランジスタと、ゲートを第1導電型トランジスタのゲートまたは接地に接続し、ドレインを第2の第2導電型トランジスタのソースに接続し、ソ

50

ースを第2の電源に接続する第3の第2導電型トランジスタと、からなっていてもよい。

【0026】

本発明のレベルシフト回路において、トランジスタ接続群は、ゲートに第1導電型トランジスタのドレインの反転信号を供給し、ドレインを第1の第2導電型トランジスタのソースに接続し、ソースを第2の電源に接続する第2の第2導電型トランジスタと、ゲートに出力信号に係る信号を供給し、ドレインを第1の第2導電型トランジスタのソースに接続し、ソースを第2の電源に接続する第3の第2導電型トランジスタと、からなり、トランジスタ接続群が第1のレベル変換回路に含まれる場合、第3の第2導電型トランジスタのゲートは、出力信号の反転信号が供給され、トランジスタ接続群が第2のレベル変換回路に含まれる場合、第3の第2導電型トランジスタのゲートは、出力信号が供給されるようにしてよい。 10

【0027】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0028】

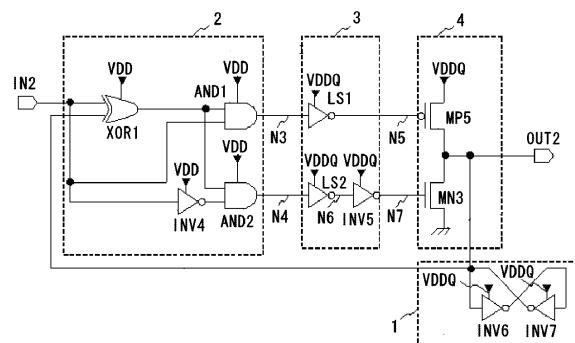

図1は、本発明の第1の実施例に係るレベルシフト回路の回路図である。図1において、レベルシフト回路は、保持回路1、入力部2、レベルシフト部3、出力反転部4を備える。入力部2の電源は、低電圧側の電源VDDから供給され、保持回路1、レベルシフト部3、出力反転部4のそれぞれの電源は、高電圧側の電源VDDQから供給される。 20

【0029】

入力部2は、排他論理回路XOR1、AND回路AND1、AND2及びインバータ回路INV4を備え、全て電源VDDに接続される。排他論理回路XOR1は、2つの入力端をそれぞれノードIN2とノードOUT2に接続し、出力端をAND回路AND1、AND2のそれぞれの一方の入力端に接続する。AND回路AND1は、他方の入力端をノードIN2に接続し、出力端をノードN3に接続する。また、AND回路AND2は、他方の入力端をインバータ回路INV4を介してノードIN2に接続し、出力端をノードN4に接続する。

【0030】

図2は、入力部2における入出力の真理値表である。入力部2の入出力間の論理は、図2に示すように、ノードIN2、OUT2の論理が一致している時に、ノードN3、N4が共に「0」となる。また、ノードIN2、OUT2の論理が不一致で、かつノードIN2が「1」の時は、ノードN3のみが「1」となる。さらに、ノードIN2、OUT2の論理が不一致で、かつノードIN2が「0」の時は、ノードN4のみが「1」となる。入力部2の回路は、図2に示す真理値表の論理を出力する回路であれば、図1の回路に限定されず、他の回路構成であっても良い。 30

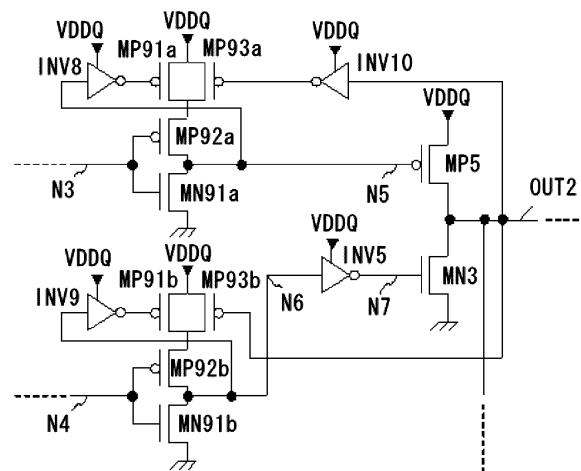

【0031】

レベルシフト部3は、レベル変換回路LS1、LS2及びインバータ回路INV5を備え、全て電源VDDQに接続される。レベル変換回路LS1は、入力端をAND回路AND1の出力であるノードN3に接続し、出力端をノードN5に接続する。レベル変換回路LS2は、入力端をAND回路AND2の出力であるノードN4にし、出力端をインバータ回路INV5を介してノードN7に接続する。 40

【0032】

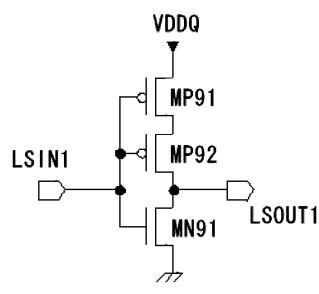

図3は、レベル変換回路LS1、LS2の回路図である。レベル変換回路LS1、LS2は、PchトランジスタMP91、MP92及びNchトランジスタMN91で構成されており、全てのトランジスタのゲートは、入力端LSIN1に接続される。PchトランジスタMP92及びNchトランジスタMN91のドレインは、出力端LSOUT1に接続される。また、PchトランジスタMP91のドレインは、PchトランジスタMP92のソースに接続され、PchトランジスタMP91のソースは、VDDQに接続され、NchトランジスタMN91のソースは、GNDに接続されている。 50

【0033】

このような構成のレベル変換回路は、入力端 L S I N 1 に与えられる V D D - 接地間の電位のパルス信号を、接地（正確には接地に近い電位） - V D D Q 間の電位のパルス信号にレベル変換して出力端 L S O U T 1 に出力する。

#### 【 0 0 3 4 】

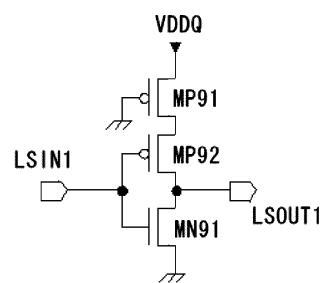

また、図 4 は、レベル変換回路 L S 1、L S 2 の他の例を示す回路図である。図 4 に示すように、図 3 における P c h トランジスタ M P 9 1 のゲート入力を「0」レベルにクランプ（接地）しても同様の動作をさせることができる。

#### 【 0 0 3 5 】

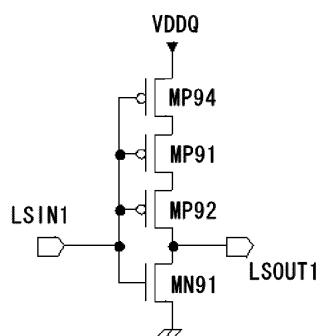

さらに、図 5 は、レベル変換回路 L S 1、L S 2 のさらに他の例を示す回路図である。

図 5 に示すように、図 3 における P c h トランジスタ M P 9 1 と電源 V D D Q の間に、ゲートを入力端 L S I N 1 に接続する P c h トランジスタ M P 9 4 を追加するなどして総積み段数を変えても同様の動作をさせることができる。また、図 5 において、P c h トランジスタ M P 9 1、M P 9 4 のいずれか一方、または双方のゲートを「0」レベルにクランプ（接地）してもよい。

#### 【 0 0 3 6 】

出力反転部 4 は、P c h トランジスタ M P 5 及び N c h トランジスタ M N 3 を備える。

N c h トランジスタ M N 3 は、ゲートをインバータ回路 I N V 5 の出力であるノード N 7 に接続し、ソースを G N D に接続し、ドレインをノード O U T 2 に接続する。また、P c h トランジスタ M P 5 は、ゲートをレベル変換回路 L S 1 の出力であるノード N 5 に接続し、ソースを電源 V D D Q に接続し、ドレインをノード O U T 2 に接続する。

#### 【 0 0 3 7 】

保持回路 1 は、電源 V D D Q に接続されたインバータ回路 I N V 6、I N V 7 を備える。

インバータ回路 I N V 6 は、入力端をノード O U T 2 に接続し、出力端をインバータ回路 I N V 7 の入力端に接続する。インバータ回路 I N V 7 は、出力端をノード O U T 2 に接続する。

#### 【 0 0 3 8 】

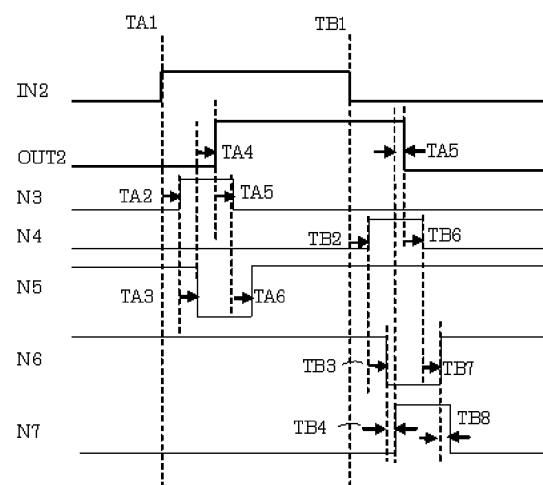

次に、レベルシフト回路の動作について説明する。図 6 は、本発明の第 1 の実施例に係るレベルシフト回路の動作を表すタイミングチャートである。ここでは、ローレベルを「0」、ハイレベルを「1」として表す。

#### 【 0 0 3 9 】

初期状態において、I N 2 = 「0」、O U T 2 = 「0」であり、ノード N 3、N 4 は、「0」となっている。この時、ノード N 5 の電圧レベルは、V D D Q であるので、V D D Q の電圧がゲートに印加されている P c h トランジスタ M P 5 はオフ状態である。また、ノード N 6 の電圧レベルは、ノード N 5 と同様 V D D Q であり、ノード N 7 の電圧は、インバータ回路 I N V 5 によって反転され「0」レベルである。したがって、「0」レベルの電圧がゲートに印加されている N c h トランジスタ M N 3 はオフ状態である。出力 O U T 2 の電圧は、保持回路 1 によって「0」レベルに保持されている。

#### 【 0 0 4 0 】

時刻 T A 1において、入力 I N 2 が立ち上ると、図 2 の真理値表に示すようにノード N 3 が入力回路 2 の遅延時間 T A 2 後に立ち上がる（「1」になる）。つまり、ノード N 3 の電圧レベルが V D D となり、V D D の電圧がゲートに印加されているレベル変換回路 L S 1 の N c h トランジスタ M N 9 1 がオンする。この結果、レベル変換回路 L S 1 の遅延時間 T A 3 後、ノード N 5 の電圧が引き下げられ、P c h トランジスタ M P 5 がオン状態となる。P c h トランジスタ M P 5 がオン状態になると、出力 O U T 2 の電圧は、出力反転部 4 の遅延時間 T A 4 後、引き上げられ、保持回路 1 の状態（出力 O U T 2 のレベル）が V D D Q レベルへと反転する。

#### 【 0 0 4 1 】

出力 O U T 2 が V D D Q レベル（「1」レベル）となると、図 2 の真理値表に示すようにノード N 3 は、入力回路 2 の遅延時間 T A 5 後に「0」レベルとなる。それに伴い、レベル変換回路 L S 1 の N c h トランジスタ M N 9 1 が、レベルシフト部 3 の遅延時間 T A

10

20

30

40

50

6後にオフする。この結果、ノードN5がVDDQレベルとなり、PchトランジスタMP5がオフ状態となる。このオフ状態において、出力OUT2の電圧は、保持回路1において「1」レベルに保持される。

#### 【0042】

時刻TB1において、入力IN2が立ち下がると、図2の真理値表に示すようにノードN4が入力回路2の遅延時間TB2後に立ち上がる（「1」になる）。つまり、ノードN4の電圧レベルがVDDとなり、VDDの電圧がゲートに印加されているレベル変換回路LS2のNchトランジスタMN91がオンする。この結果、レベル変換回路LS2の遅延時間TB3後、ノードN6の電圧が引き下げられ、ノードN7の電圧がインバータ回路INV5によってインバータ回路INV5の遅延時間TB4後に反転されVDDQレベルとなる。したがって、NchトランジスタMN3がオン状態となる。NchトランジスタMN3がオン状態になると、出力OUT2の電圧は、出力反転部4の遅延時間TB5後、引き下げられ、保持回路1が「0」レベルへと反転する。10

#### 【0043】

出力OUT2が「0」レベルとなると、図2の真理値表に示すようにノードN4は、入力回路2の遅延時間TB6後に「0」レベルとなる。それに伴い、レベル変換回路LS2のNchトランジスタMN91が、レベルシフト部3の遅延時間TB7後にオフして、ノードN6がVDDQレベルとなる。この結果、ノードN7の電圧がインバータ回路INV5によって反転されてインバータ回路INV5の遅延時間TB8後に「0」レベルとなり、NchトランジスタMN3がオフ状態となる。このオフ状態で出力OUT2の電圧は、保持回路1において「0」レベルに保持される。20

#### 【0044】

ここで、VDDの電圧が低くなてもレベル変換回路LS1、LS2を動作させるには、入力端LSIN1の電圧がVDDとなった時に、NchトランジスタMN91のオン抵抗がPchトランジスタMP91、MP92のオン抵抗に対して充分小さくなるようにトランジスタのディメンジョンを設定する必要がある。VDDがNchトランジスタMN91の閾値電圧程度まで低くなても、NchトランジスタMN91のオン抵抗がPchトランジスタMP91、MP92のオン抵抗に対して小さくなるようなディメンジョンに設定し、出力端LSOUT1の電圧を引き下げることができれば、レベル変換回路LS1、LS2は動作可能である。30

#### 【0045】

従来の回路では、このようなディメンジョンの設定をした場合に立ち上がり動作が悪化するので、立ち上がり／立ち下がりの遅延時間のバランスが悪化することは前述の通りである。これに対し、本発明のレベルシフト回路によれば、以下の効果を奏する。

#### 【0046】

前述の通り、出力OUT2が立ち上がる時は、レベル変換回路LS1のみが動作し、出力OUT2が立ち下がる時は、レベル変換回路LS2のみが動作する。レベル変換回路LS1、LS2は、入力IN2の論理値を出力OUT2に伝達する際、両者とも立ち下がりで動作する。レベル変換回路LS1、LS2が立ち上がり動作するのは、出力OUT2の論理が決定した後にPchトランジスタMP5またはNchトランジスタMN3をオフ状態にする時のみであって、入力IN2から出力OUT2への遅延時間には影響を与えない。40

#### 【0047】

つまり、低電圧でも動作するようにレベル変換回路LS1、LS2におけるトランジスタのディメンジョンを設定しても、立ち下がり動作でしか入力IN2の論理を出力OUT2に伝達せず、レベル変換回路LS1、LS2の立ち上がり動作の悪化は、遅延時間に影響を与えない。したがって、立ち上がり／立ち下がりの遅延時間のバランスは悪化しないことになる。

#### 【実施例2】

#### 【0048】

10

20

30

40

50

図7は、本発明の第2の実施例に係るレベルシフト回路の主要部の回路図である。図7に示すレベルシフト回路は、図1のレベルシフト部3及び出力反転部4の部分に対して変更を加えたものであり、変更部分のみを示している。他の部分は、図1と同じに構成される。図7に示すレベルシフト回路は、図3のレベル変換回路LS1、LS2に対して、PchトランジスタMP93a、MP93b、インバータ回路INV8、INV9、INV10を追加している。インバータ回路INV8、INV9、INV10は、全て電源VDDQに接続されている。なお、NchトランジスタMN91a、MN91bは、図3のNchトランジスタMN91と同等であり、PchトランジスタMP92a、MP92bは、図3のPchトランジスタMP92と同等である。

## 【0049】

10

また、図3のPchトランジスタMP91の代わりにPchトランジスタMP91a、MP91bをそれぞれ備え、PchトランジスタMP91a、MP91bのゲートの接続先を変更している。PchトランジスタMP91aのゲートは、ノードN5の反転信号を出力するインバータ回路INV8の出力に接続される。また、PchトランジスタMP91bのゲートは、ノードN6の反転信号を出力するインバータ回路INV9の出力に接続される。

## 【0050】

20

PchトランジスタMP93aは、ゲートを出力OUT2の反転信号を出力するインバータ回路INV10の出力に接続し、ドレインをPchトランジスタMP92aのソースに接続し、ソースをVDDQに接続する。PchトランジスタMP93bは、ゲートを出力OUT2に接続し、ドレインをPchトランジスタMP92bのソースに接続し、ソースをVDDQに接続する。

## 【0051】

30

まず始めにノードN4が立ち上がる場合(図6の時刻TB1以降)について説明する。ノードN4が立ち上がるということは、実施例1で前述したように出力OUT2が立ち下がるということである。したがって、出力OUT2の初期電圧レベルはVDDQである。出力OUT2がゲートに接続されているPchトランジスタMP93bは、この時オフ状態である。また、ノードN4が立ち上がるということは、ノードN6が立ち下がるということである。したがって、ノードN6の電圧レベルはVDDQである。ノードN6の反転信号がゲートに接続されているMP91bは、この時オン状態である。

## 【0052】

ノードN4が立ち上がってNchトランジスタMN91bがオン状態となると、PchトランジスタMP93bはオフ状態である。したがって、ノードN6の電圧は、PchトランジスタMP91b、MP92bとNchトランジスタMN91bとで分圧された電圧となる。この時、PchトランジスタMP91bのオン抵抗が大きいほどノードN6の電圧を低くすることができる。但し、PchトランジスタMP91bがオン状態のままであると、ノードN6の立ち上がり特性が悪くなる。立ち上がり特性の悪化は、入力IN2から出力OUT2までの遅延時間に影響を与えないが、レベルシフト動作期間が長くなることを意味する。

## 【0053】

40

本実施例は、この動作期間を短くする工夫を行っている。PchトランジスタMP91bは、初期状態(図6の時刻TB1)でオンしているが、ノードN6が立ち下がるとオフ状態となる。その後、出力OUT2が立ち下がると、PchトランジスタMP93bがオンする。PchトランジスタMP93bのオン抵抗をPchトランジスタMP91bに対して小さくなるようにトランジスタのディメンジョンを設定しておく。この設定によって、ノードN4が立ち下がってノードN6が立ち上がる際、PchトランジスタMP91bで引き上げるよりも高速で動作することができる。

## 【0054】

なお、以上の説明では、ノードN4に係る経路について説明したが、ノードN3に係る経路についても、同様の構成で動作する。ただし、PchトランジスタMP91aに対し

50

てオン抵抗が小さくなるように設定される PchトランジスタMP93aは、出力OUT2をインバータ回路INV10を介してゲートに与えられ、出力OUT2が立ち上ると、オンするように動作する。

#### 【0055】

以上のように立ち下がり時と立ち上がり時でオン抵抗を切り替える回路構成とすることで、レベルシフトの動作期間を短くすることができる。レベルシフトの動作期間が終了しないと入力IN2における信号の次の遷移を行うことができない。したがって、レベルシフトの動作期間を短くすることは、レベルシフト回路をより高い周波数で動作させる上で効果的である。

#### 【0056】

また、PchトランジスタMP91a、MP91bのオン抵抗を極端に大きくすることも可能であるので、その分だけNchトランジスタMN91a、MN91bのオン抵抗も大きくすることができます。つまり、NchトランジスタMN91a、MN91bのWサイズを小さくできることになる。また、VDDの電圧レベルが低くなることによるNchトランジスタMN91a、MN91bのオン抵抗増大に対する耐性も高まる。このため、レベルシフト回路は、より低電圧で動作しやすくなる。

#### 【0057】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示（請求の範囲を含む）の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

#### 【図面の簡単な説明】

#### 【0058】

【図1】本発明の第1の実施例に係るレベルシフト回路の回路図である。

【図2】入力部における入出力の真理値表である。

【図3】レベル変換回路LS1、LS2の回路図である。

【図4】レベル変換回路LS1、LS2の他の例を示す回路図である。

【図5】レベル変換回路LS1、LS2のさらに他の例を示す回路図である。

【図6】本発明の第1の実施例に係るレベルシフト回路の動作を表すタイミングチャートである。

【図7】本発明の第2の実施例に係るレベルシフト回路の主要部の回路図である。

【図8】特許文献1のレベルシフト回路の回路図である。

【図9】特許文献1のレベルシフト回路のタイミングチャートである。

#### 【符号の説明】

#### 【0059】

1 保持回路

2 入力部

3 レベルシフト部

4 出力反転部

AND1、AND2 AND回路

IN2、N3、N4、N5、N6、N7、OUT2 ノード

INV4～INV10 インバータ回路

LS1、LS2 レベル変換回路

L SIN1 入力端

L SOUT1 出力端

MN3、MN91、MN91a、MN91b Nchトランジスタ

MP5、MP91、MP91a、MP91b、MP92、MP92a、MP92b、MP

93a、MP93b、MP94 Pchトランジスタ

10

20

30

40

50

VDD、VDDQ 電源

XOR1 排他論理和回路

【図1】

【図2】

| 入力  |      | 出力 |    |

|-----|------|----|----|

| IN2 | OUT2 | N3 | N4 |

| 0   | 0    | 0  | 0  |

| 1   | 0    | 1  | 0  |

| 1   | 1    | 0  | 0  |

| 0   | 1    | 0  | 1  |

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2002-135107(JP,A)

特開2004-007821(JP,A)

特開2004-112310(JP,A)

特開2003-133941(JP,A)

特開平08-307236(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096

H01L27/04