(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3813689号

(P3813689)

(45) 発行日 平成18年8月23日(2006.8.23)

(24) 登録日 平成18年6月9日(2006.6.9)

(51) Int.C1.

F 1

|             |              |                  |             |             |

|-------------|--------------|------------------|-------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b> |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> |

| <b>H04N</b> | <b>5/46</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> |

| <b>H04N</b> | <b>5/66</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> |

請求項の数 18 (全 29 頁) 最終頁に続く

|              |                       |                |                                 |

|--------------|-----------------------|----------------|---------------------------------|

| (21) 出願番号    | 特願平9-122254           | (73) 特許権者      | 000003078                       |

| (22) 出願日     | 平成9年5月13日(1997.5.13)  | 株式会社東芝         |                                 |

| (65) 公開番号    | 特開平10-97230           | 東京都港区芝浦一丁目1番1号 |                                 |

| (43) 公開日     | 平成10年4月14日(1998.4.14) | (74) 代理人       | 100064285                       |

| 審査請求日        | 平成16年4月14日(2004.4.14) | 弁理士 佐藤 一雄      |                                 |

| (31) 優先権主張番号 | 特願平8-182318           | (74) 代理人       | 100073379                       |

| (32) 優先日     | 平成8年7月11日(1996.7.11)  | 弁理士 佐藤 政光      |                                 |

| (33) 優先権主張国  | 日本国(JP)               | (74) 代理人       | 100088889                       |

|              |                       | 弁理士 橋谷 英俊      |                                 |

|              |                       | (74) 代理人       | 100082991                       |

|              |                       | 弁理士 佐藤 泰和      |                                 |

|              |                       | (72) 発明者       | 森山直己                            |

|              |                       |                | 神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内 |

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項1】

マトリクス状に配置された複数の画素電極と、各画素電極に対応して設けられたスイッチ素子と、前記画素電極のうち同じ行方向に配置された画素電極に対応するスイッチ素子を共通接続して同時に開閉動作させる制御信号を送るための走査線と、前記画素電極のうち同じ列方向に配置された画素電極に、対応するスイッチ素子を介して映像信号を送るための映像信号線と、前記複数の画素電極に対向配置された対向電極と、を有する表示パネル部と、

映像信号バスラインを介して送られてくる映像データを受信する前に受信した、一水平走査毎に発生されるリセット信号に応じた第1のタイミング信号を生成し、この第1のタイミング信号に基づいて、前記リセット信号に同期して送られてくる非表示データを選択し、この選択した非表示データを全ての前記映像信号線に送出し、その後、送られてくる前記映像データを、第2のタイミング信号に基づいて選択し、この選択した映像データを前記第2のタイミング信号に対応する前記映像信号線に送出する映像信号線駆動回路と、を備えていることを特徴とする表示装置。

## 【請求項2】

請求項1記載の表示装置を駆動する駆動方法であって、前記非表示データを一水平帰線期間中に書き込み、前記映像データを一水平走査期間中に書き込むことを特徴とする表示装置の駆動方法。

## 【請求項3】

前記一水平帰線期間中に書き込まれる前記非表示データの信号の極性が、同一水平画素ライン中の表示領域に前記水平走査期間中に書き込まれる前記映像データの信号の極性と同一であることを特徴とする請求項2記載の表示装置の駆動方法。

【請求項4】

前記非表示データの表示には、前記映像データの表示に用いられる画素電極と対向電極との間の電位差の領域外の電位差が用いられることを特徴とする請求項2記載の表示装置の駆動方法。

【請求項5】

前記映像信号線駆動回路は、nビットのアドレス信号と前記リセット信号とに基づいて前記第1または第2のタイミング信号を出力する論理回路と、この論理回路の出力に基づいて前記映像データ又は非表示データを選択する選択回路と、

を備えていることを特徴とする請求項1記載の表示装置。

【請求項6】

前記映像信号線駆動回路は、

nビットのアドレス信号に基づいて前記第1または第2のタイミング信号を出力する論理回路と、

前記第1のタイミング信号に基づいて前記非表示データを選択する第1の選択回路と、

前記第2のタイミング信号に基づいて前記映像データを選択する第2の選択回路と、

を備えていることを特徴とする請求項1記載の表示装置。

【請求項7】

前記映像信号線駆動回路は、

継続接続された複数のフリップフロップからなり、スタートパルスを受信し、このスタートパルスをクロック信号に同期して後段のフリップフロップに順次転送するシフトレジスタ回路と、このシフトレジスタ回路の各段のフリップフロップの出力と前記リセット信号とに基づいて前記第1または第2のタイミング信号を出力するリセット回路とを有する論理回路と、

前記第1または第2のタイミング信号に基づいて前記映像データまたは前記非表示データを選択する選択回路と、

を備えていることを特徴とする請求項1記載の表示装置。

【請求項8】

前記シフトレジスタ回路の所定の段のフリップフロップと次段のフリップフロップとの間に設けられ、表示される画面のアスペクト比に応じて、前記所定の段のフリップフロップの出力を選択するか、または初段のフリップフロップに入力されるスタートパルスをバイパスしたパルス信号を選択するように接続を切換え、この選択した信号を前記次段のフリップフロップに送出する切換手段を備えていることを特徴とする請求項7記載の表示装置。

【請求項9】

前記切換手段が前記バイパスされたパルス信号を選択するように接続を切換えた場合には、前記初段乃至前記所定の段のフリップフロップを含む複数段のフリップフロップの出力に基づいた前記第2のタイミング信号を出力しないようにする手段を前記論理回路は更に備えていることを特徴とする請求項8記載の表示装置。

【請求項10】

リセット信号を受信しない場合は第1期間で走査線を選択し、リセット信号を受信した場合は前記第1期間とは異なる第2期間で走査線を選択する論理回路と、前記論理回路の出力に基づいて選択された走査線に前記制御信号を供給するバッファアンプ回路と、を有する走査線駆動回路部を更に備えていることを特徴とする請求項1乃至9のいずれかに記載の表示装置。

【請求項11】

前記論理回路は、mビットのアドレス信号と前記リセット信号に基づいて走査線を選択することを特徴とする請求項10記載の表示装置。

10

20

30

40

50

**【請求項 12】**

前記論理回路は、

継続接続された複数のフリップフロップからなり、スタートパルスを受信し、このスタートパルスをクロック信号に同期して後段のフリップフロップに順次転送するシフトレジスタ回路と、このシフトレジスタ回路の各段のフリップフロップの出力と前記リセット信号とに基づいて前記走査線を選択するための信号を出力するリセット回路とを有する、

ことを特徴とする請求項10記載の表示装置。

**【請求項 13】**

前記シフトレジスタ回路の所定の段のフリップフロップと次段のフリップフロップとの間に設けられ、表示される画面のアスペクト比に応じて、前記所定の段のフリップフロップの出力を選択するか、または初段のフリップフロップに入力されるスタートパルスをバイパスしたパルス信号を選択するように接続を切換え、この選択した信号を前記次段のフリップフロップに送出する切換手段を備えていることを特徴とする請求項12記載の表示装置。10

**【請求項 14】**

前記切換手段が前記バイパスされたパルス信号を選択するように接続を切換えた場合には、前記初段乃至前記所定の段のフリップフロップを含む複数段のフリップフロップの出力に基づいた前記走査線を選択するための信号を出力しないようにする手段を前記論理回路は更に備えていることを特徴とする請求項13記載の表示装置。

**【請求項 15】**

前記表示パネル部は、前記画素電極、前記スイッチ素子、前記走査線、および前記映像信号線が形成されたアレイ基板と、前記対向電極が形成された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、を備えていることを特徴とする請求項1, 5, 6, 7, 8, 9のいずれかに記載の表示装置。20

**【請求項 16】**

前記映像信号線駆動回路は前記アレイ基板上に形成されていることを特徴とする請求項15記載の表示装置。

**【請求項 17】**

前記表示パネル部は、前記画素電極、前記スイッチ素子、前記走査線、および前記映像信号線が形成されたアレイ基板と、前記対向電極が形成された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、を備えていることを特徴とする請求項10, 11, 12, 13, 14のいずれかに記載の表示装置。30

**【請求項 18】**

前記走査線駆動回路は前記アレイ基板上に形成されていることを特徴とする請求項17記載の表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、表示装置およびその駆動方法に関する。

**【0002】****【従来の技術】**

近年、液晶表示装置は、軽量かつ低消費電力を達成するフラットパネルディスプレイとして注目を集めている。中でも、各表示画素毎に薄膜トランジスタ（以下、TFTと称する）等のスイッチ素子が設けられてなるアクティブマトリクス型の液晶表示装置は、クロストークのない高精細な表示画像が得られることから、TV用をはじめOA用等の各種ディスプレイとして利用されている。近年では、表示画面の大型化の要求から、このような液晶表示装置を投射型として用いる試みが成されている。

**【0003】**

このようなアクティブマトリクス型の表示装置を投射型として用いる場合、小型化、低価格化、低消費電力化を達成する上で、光学系の小型化が必須であり、これにともない液晶40

50

表示装置自体を3インチ程度の小型に形成する必要がある。

【0004】

そこで、このような表示装置においては、各表示画素を駆動するための駆動回路部を表示画素部と同一基板上に一体的に形成することが試みられている。

【0005】

【発明が解決しようとする課題】

アスペクト比16:9の画素数の表示装置にアスペクト比4:3のコンピュータの映像信号を表示させるなど、表示装置が複数の映像規格に対応することが重要になってきている。この場合、映像信号の水平帰線期間も含めた水平画素数の設定が、表示パネルの一水平画素ラインを構成する表示画素数よりも少ない場合が考えられる。このようなとき、対応する映像信号が無い表示画素には非表示データを表示させることになる。駆動回路側の対応の方法として、フレームメモリを使って映像信号の駆動周波数を変えて、非表示データをあらかじめ映像信号の水平走査期間に埋め込むことが考えられるが、この方法はコストがかかる。

10

【0006】

別の方法として、表示データとは別に非表示データを用意して、映像規格に合わせて表示装置側で画素毎に表示データと非表示データを選択し表示させることが考えられる。表示装置にこのような動作をさせる場合、SID 93 DIGEST p. 383 - p. 386 "A 1.9-in, 1.5-Mpixel Driver Fully-Integrated Poly-Si TFT-LCD for HDTV Project on" 等に示されるようなシフトレジスタを主体に構成された駆動回路では、シフトレジスタが順次信号を転送する形態であるが故に、映像信号規格に合わせて表示パネルの中で駆動する信号線を切り替えることが難しい。

20

【0007】

本発明は上記事情を考慮してなされたものであって、非表示領域の非表示データの表示を容易に行うことのできる表示装置およびその駆動方法を提供することを目的とする。

【0008】

【課題を解決するための手段】

本発明の第1の態様の表示装置は、マトリクス状に配置された複数の画素電極と、各画素電極に対応して設けられたスイッチ素子と、前記画素電極のうち同じ行方向に配置された画素電極に対応するスイッチ素子を共通接続して同時に開閉動作させる制御信号を送るための走査線と、前記画素電極のうち同じ列方向に配置された画素電極に、対応するスイッチ素子を介して映像信号を送るための映像信号線と、前記複数の画素電極に対向配置された対向配置された対向電極と、を有する表示パネル部と、映像データを受信する前に受信したリセット信号に応じた第1のタイミング信号を生成し、この第1のタイミング信号に基づいて、前記リセット信号に同期して送られてくる非表示データを選択し、この選択した非表示データを前記第1のタイミング信号に対応する前記映像信号線に送出し、その後、送られてくる前記映像データを、第2のタイミング信号に基づいて選択し、この選択した映像データを前記第2のタイミング信号に対応する前記映像信号線に送出する映像信号線駆動回路と、を備えていることを特徴とする。

30

【0009】

また、前記映像信号線駆動回路は、nビットのアドレス信号と前記リセット信号とに基づいて前記第1または第2のタイミング信号を出力する論理回路と、この論理回路の出力に基づいて前記映像データ又は非表示データを選択する選択回路と、を備えているように構成しても良い。

40

【0010】

また、前記映像信号線駆動回路は、nビットのアドレス信号に基づいて前記第1または第2のタイミング信号を出力する論理回路と、前記第1のタイミング信号に基づいて前記非表示データを選択する第1の選択回路と、前記第2のタイミング信号に基づいて前記映像データを選択する第2の選択回路と、を備えているように構成しても良い。

50

## 【0011】

また、前記映像信号線駆動回路は、縦続接続された複数のフリップフロップからなり、スタートパルスを受信し、このスタートパルスをクロック信号に同期して後段のフリップフロップに順次転送するシフトレジスタ回路と、このシフトレジスタ回路の各段のフリップフロップの出力と前記リセット信号とに基づいて前記第1または第2のタイミング信号を出力するリセット回路とを有する論理回路と、前記第1または第2のタイミング信号に基づいて前記映像データまたは前記非表示データを選択する選択回路と、を備えているように構成しても良い。

## 【0012】

また、前記シフトレジスタ回路の所定の段のフリップフロップと次段のフリップフロップとの間に設けられ、表示される画面のアスペクト比に応じて、前記所定の段のフリップフロップの出力を選択するか、または初段のフリップフロップに入力されるスタートパルスをバイパスしたパルス信号を選択するように接続を切換え、この選択した信号を前記次段のフリップフロップに送出する切換手段を備えているように構成しても良い。

10

## 【0013】

また、前記切換手段が前記バイパスされたパルス信号を選択するように接続を切換えた場合には、前記初段乃至前記所定の段のフリップフロップを含む複数段のフリップフロップの出力に基づいた前記第2のタイミング信号を出力しないようにする手段を前記論理回路は更に備えているように構成しても良い。

## 【0014】

20

また、前記表示パネル部は、前記画素電極、前記スイッチ素子、前記走査線、および前記映像信号線が形成されたアレイ基板と、前記対向電極が形成された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、を備えているように構成しても良い。

## 【0015】

また、前記映像信号線駆動回路は前記アレイ基板上に形成することが可能である。

## 【0016】

また本発明の第2の態様の表示装置は、マトリクス状に配置された複数の画素電極と、各画素電極に対応して設けられたスイッチ素子と、前記画素電極のうち同じ行方向に配置された画素電極に対応するスイッチ素子を共通接続して同時に開閉動作させる制御信号を送るための走査線と、前記画素電極のうち同じ列方向に配置された画素電極に、対応するスイッチ素子を介して映像信号を送るための映像信号線と、前記画素電極に対向配置された対向電極と、を有する表示パネル部と、リセット信号を受信しない場合は第1のタイミングで走査線を選択し、リセット信号を受信した場合は前記第1のタイミングとは異なる第2のタイミングで走査線を選択する論理回路と、前記論理回路の出力に基づいて選択された走査線に走査電位を供給するバッファアンプ部と、を有する走査線駆動回路部と、を備えていることを特徴とする。

30

## 【0017】

また、前記論理回路は、mビットのアドレス信号と前記リセット信号に基づいて走査線を選択するように構成しても良い。

40

## 【0018】

また、前記論理回路は、縦続接続された複数のフリップフロップからなり、スタートパルスを受信し、このスタートパルスをクロック信号に同期して後段のフリップフロップに順次転送するシフトレジスタ回路と、このシフトレジスタ回路の各段のフリップフロップの出力と前記リセット信号とに基づいて前記走査線を選択するための信号を出力するリセット回路とを有するように構成しても良い。

## 【0019】

また、前記シフトレジスタ回路の所定の段のフリップフロップと次段のフリップフロップとの間に設けられ、表示される画面のアスペクト比に応じて、前記所定の段のフリップフロップの出力を選択するか、または初段のフリップフロップに入力されるスタートパルス

50

をバイパスしたパルス信号を選択するように接続を切換え、この選択した信号を前記次段のフリップフロップに送出する切換手段を備えているように構成しても良い。

【0020】

また、前記切換手段が前記バイパスされたパルス信号を選択するように接続を切換えた場合には、前記初段乃至前記所定の段のフリップフロップを含む複数段のフリップフロップの出力に基づいた前記走査線を選択するための信号を出力しないようにする手段を前記論理回路は更に備えているように構成することができる。

【0021】

また、前記表示パネル部は、前記画素電極、前記スイッチ素子、前記走査線、および前記映像信号線が形成されたアレイ基板と、前記対向電極が形成された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、を備えているように構成しても良い。

10

【0022】

また、前記走査線駆動回路は前記アレイ基板上に形成することが可能である。

【0023】

また本発明の第3の態様の駆動方法は、非表示データを一水平帰線期間中に書き込み、映像データを一水平走査期間中に書き込むことを特徴とする。

【0024】

また、前記一水平帰線期間中に書き込まれる前記非表示データの信号の極性が、同一水平画素ライン中の表示領域に前記水平走査期間中に書き込まれる前記映像データの信号の極性と同一であっても良い。

20

【0025】

また、前記非表示データの表示には、前記映像データの表示に用いられる画素電極と対向電極との間の電位差の領域外の電位差を用いても良い。

【0026】

また本発明の第4の態様の駆動方法は、複数の表示画素から成る水平画素ラインが複数本配列されて成る表示パネルに映像データに基づく表示画像を形成する表示装置の駆動方法において、前記映像データの垂直帰線期間を含めた一垂直走査期間の水平画素ライン数の設定が表示パネルの水平画素ライン数よりも少ない場合、前記映像データに対応しない複数の水平画素ラインに同時に非表示データを第1期間で書き込むと共に、前記映像データをそれに対応する少なくとも一本の前記水平画素ラインに、前記第1期間と異なる第2期間で書き込むことを特徴とする。

30

【0027】

また、前記第1期間が一垂直帰線期間で、前記第2期間が垂直走査期間であることが好ましい。

【0028】

【発明の実施の態様】

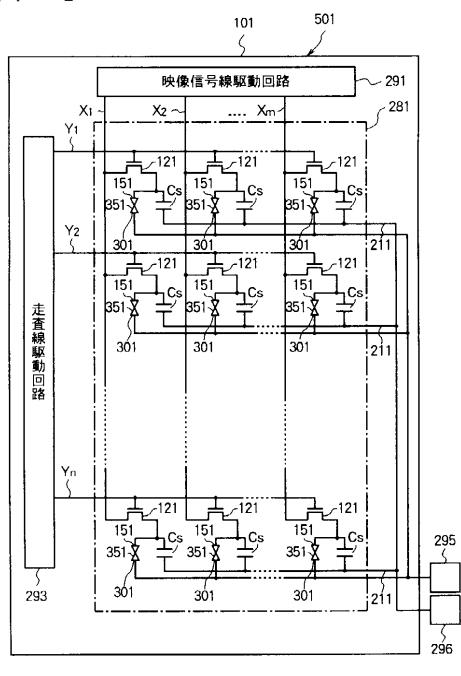

本発明による表示装置の第1の実施の形態の構成を図1に示す。この実施の形態の表示装置501は液晶表示装置であって投射型EDTV(Extended Definition TeleVision)に用いられ、図1に示すように対角3インチの表示領域281を備えている。

40

【0029】

この液晶表示装置501は、マトリクスアレイ基板101と対向基板(図示せず)との間にポリイミドからなる配向膜を介してTN型の液晶層351が保持された構成となっている。

【0030】

図1に示すように、マトリクスアレイ基板101は、表示領域281とその周辺部分に映像信号線駆動回路291および走査線駆動回路293を一体的に備えている。対向電極駆動回路295と画素電位保持容量線駆動回路296はマトリクスアレイ基板101の外部に設置される。表示領域281には、映像信号線駆動回路291に接続され、互いに略平行に所定の間隔を隔て配置されるm本の映像信号線X<sub>1</sub>...X<sub>m</sub>と、走査線駆動回路293

50

に接続され、映像信号線  $X_i$  ( $i = 1, \dots, m$ ) と略直交して配置される  $n$  本の走査線  $Y_1, \dots, Y_n$  が設けられている。

【0031】

一方各走査線  $Y_j$  ( $j = 1, \dots, n$ ) と各映像信号線  $X_i$  ( $i = 1, \dots, m$ ) との交点部分には  $n$  チャネルの TFT121 が配置され、この TFT121 を介して ITO (Indium Tin Oxide) からなる画素電極 151 が配置されている。なお、TFT121 は対応する映像信号線  $X_i$  ( $i = 1, \dots, m$ ) に接続されている。また、画素電極 151 には、画素電位を保持する保持容量線 211 が各画素電極 151 に対して走査線  $Y_j$  ( $j = 1, \dots, n$ ) と略平行に配置されている。

【0032】

上記対向基板は、透明なガラス基板上に、ITO からなり対向電極駆動回路 295 に電気的に接続されるように形成された対向電極 301 と、その上に配置される配向膜とを備えるように構成されている。また図示しないが、クロム (Cr) 等の金属からなる遮光層が不必要な光、例えば TFT121 へ入射する光を遮光するように配置されている。

【0033】

映像信号に基づき画素表示を行う場合、走査線駆動回路 293 は走査線  $Y_1$ 、走査線  $Y_2$ 、…走査線  $Y_n$  に順次ゲートON電圧  $V_g$  を出力する。このゲートON電圧  $V_g$  を受けて各 TFT121 のドレイン・ソース間は導通し、これにより映像信号線  $X_i$  ( $i = 1, \dots, m$ ) からの映像信号  $V_s$  が対応する TFT121 を介して各画素電極 151 に導かれる。これにより、上記対向電極と画素電極 151 との間の電位差が液晶層 351 に印加され、この電位差に基づいて表示が成されると共に、画素電極 151 と保持容量線 211 との間にも電荷が保持される。そしてこの電荷が保持されることにより液晶層 351 に保持される電荷の変動を補って各フィールド期間、表示画像を維持する。

【0034】

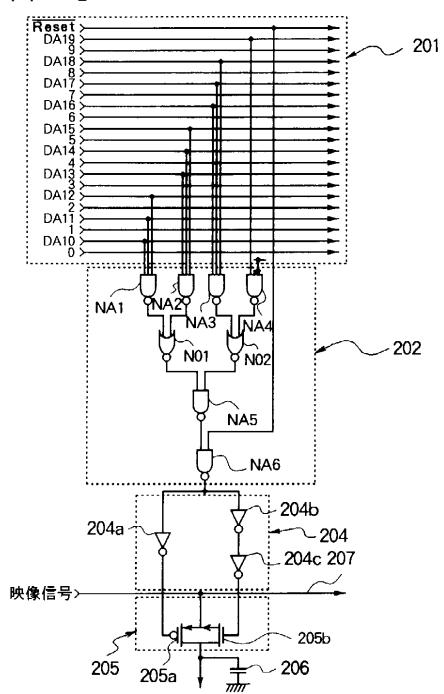

次に図 2 を参照してこの実施の形態の液晶表示装置 501 の映像信号線駆動回路 291 の構成を説明する。この映像信号線駆動回路 291 は、図 2 に示すように、マトリクス配線部 201 と、論理回路 202 と、この論理回路 202 に接続されるバッファアンプ回路 204 と、このバッファアンプ回路 204 に接続される映像信号選択回路 205 と、この映像信号選択回路 205 に接続される保持容量 206 とを備えている。なお、論理回路 202、バッファアンプ回路 204、映像信号選択回路 205、および保持容量 206 は各映像信号線毎に設けられる。

【0035】

マトリクス配線部は、映像信号線  $X_i$  ( $i = 1, \dots, m$ ) を選択するためのアドレス信号を例えば  $A_0 \dots A_9$  ( $A_i$  ( $i = 0, \dots, 9$ ) は 0 または 1 の値を有する) とすると、21 本の配線を有する。21 本の配線のうち 1 本の配線にはリセット信号が入力され、残りの 20 本の配線にはアドレス信号の 10 ビット  $A_0 \sim A_9$  の各々の数値の  $D_0 \sim D_9$  と、これらの 10 ビット  $A_0 \sim A_9$  を各々反転した数値  $D_{10} \sim D_{19}$  とが入力される。

【0036】

論理回路 202 は 3 入力 NAND ゲート NA1, NA2, NA3, NA4 と、2 入力 NAND ゲート NA5, NA6 と 2 入力ノアゲート NO1, NO2 を備えている。3 入力 NAND ゲート NA1, NA2, NA3, NA4 にはデジタル数値信号 DA0 ~ DA9 か、その反転デジタル数値信号 DA10 ~ DA19 が各ビット毎に 1 種類ずつ入力される。3 入力 NAND ゲート NA1, NA2 の出力はノアゲート NO1 の入力端に接続され、 NAND ゲート NA3, NA4 の出力はノアゲート NO2 の入力に接続される。ノアゲート NO1, NO2 の出力は NAND ゲート NA5 の入力に接続される。 NAND ゲート NA5 の出力とリセット信号が NAND ゲート NA6 の入力に接続される。論理回路 203 の最終段の NAND ゲート NA6 の出力がサンプリングパルスになる。 NAND ゲート NA6 の出力はバッファアンプ回路 204 に接続されている。

【0037】

バッファアンプ回路 204 は、3 個のバッファ 204a, 204b, 204c を有してい

10

20

30

40

50

る。 NANDゲート N A 6 の出力はバッファ 2 0 4 a によって反転増幅され、この反転増幅された信号は、映像信号選択回路 2 0 5 を構成するトランスファゲートの p チャネル T F T 2 0 5 a のゲートに入力される。

【 0 0 3 8 】

また NANDゲート N A 6 の出力は、直列に接続されたバッファ 2 0 4 b , 2 0 4 c からなる増幅回路によって増幅され、この増幅された信号は映像信号選択回路 2 0 5 を構成するトランスファゲートの n チャネル T F T 2 0 5 b のゲートに入力される。なお、 T F T 2 0 5 a , 2 0 5 b からなるトランスファゲートは映像信号を選択するのに用いられる。

【 0 0 3 9 】

このトランスファゲートのドレインは映像信号バスライン 2 0 7 に接続され、論理回路 2 0 2 からのサンプリングパルスが O N 期間の間、映像信号がサンプリングされる。トランスファゲートのソースは、対応する映像信号線に接続されているとともに映像信号選択回路 2 0 5 により選択された映像信号を保持する保持容量 2 0 6 にも接続されている。 10

【 0 0 4 0 】

次に図 2 を参照して、映像信号線駆動回路 2 9 1 の動作について説明する。各マトリクス配線部 2 0 1 では 3 入力 NANDゲート N A 1 , N A 2 , N A 3 , N A 4 に接続される数値信号線の組み合わせがそれぞれ異なっている。

【 0 0 4 1 】

NANDゲート N A 1 にはデジタル数値信号 D A 0 かその反転信号 D A 1 0 のどちらかと、デジタル数値信号 D A 1 かその反転信号 D A 1 1 のどちらかと、デジタル数値信号 D A 2 かその反転信号 D A 1 2 のどちらかとが入力されている。NANDゲート N A 2 にはデジタル数値信号 D A 3 かその反転信号 D A 1 3 のどちらかと、デジタル数値信号 D A 4 かその反転信号 D A 1 4 のどちらかと、デジタル数値信号 D A 5 かその反転信号 D A 1 5 のどちらかとが入力されている。NANDゲート N A 3 にはデジタル数値信号 D A 6 かその反転信号 D A 1 6 のどちらかと、デジタル数値信号 D A 7 かその反転信号 D A 1 7 のどちらかと、デジタル数値信号 D A 8 かその反転信号 D A 1 8 のどちらかとが入力されている。NANDゲート N A 4 の入力うち、1 入力はデジタル数値信号 D A 9 かその反転信号 D A 1 9 のどちらかが入力され、他の 2 入力には常に「 H 」レベルの信号が入力されている。NANDゲート N A 6 の片方の入力は全てがリセット信号線と接続されている。 20

【 0 0 4 2 】

このように構成された映像信号線駆動回路 2 9 1 においては、NANDゲート N A 1 , N A 2 , N A 3 , N A 4 の全ての入力が「 H 」レベルになったときだけデコーダ（論理回路） 2 0 2 の NANDゲート N A 5 は「 L 」レベルの信号を出力する。この場合において、表示領域の映像信号データを書き込むときはリセット信号は「 H 」レベルになっているため、論理回路 2 0 2 の最終段の NANDゲート N A 6 からサンプリングパルスがバッファアンプ回路 2 0 4 に出力される。これにより映像信号選択回路 2 0 5 によって映像信号が選択され、出力される。 30

【 0 0 4 3 】

これに対して非表示データを書き込むとき、リセット信号は「 L 」レベルとなるため、このときの NANDゲート N A 1 , N A 2 , N A 3 , N A 4 の入力に関わらず、全ての論理回路 2 0 2 の最終段の NANDゲート N A 6 からサンプリングパルスがバッファアンプ回路 2 0 4 に出力される。 40

【 0 0 4 4 】

リセット信号が「 L 」レベルになるのに同期して映像信号バスライン 2 0 7 から必要な非表示データを供給することにより、全ての映像信号選択回路 2 0 5 から非表示映像信号が出力される。

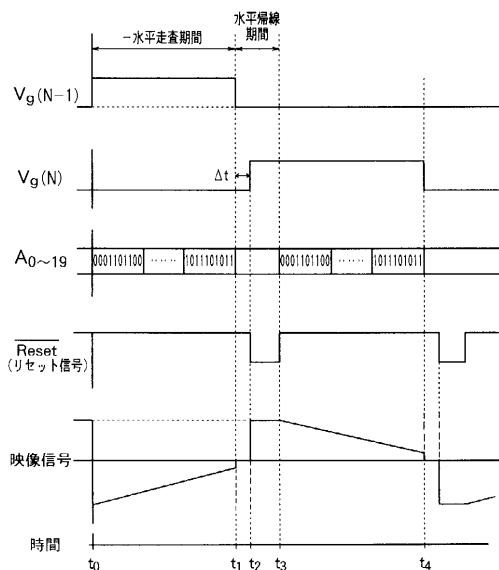

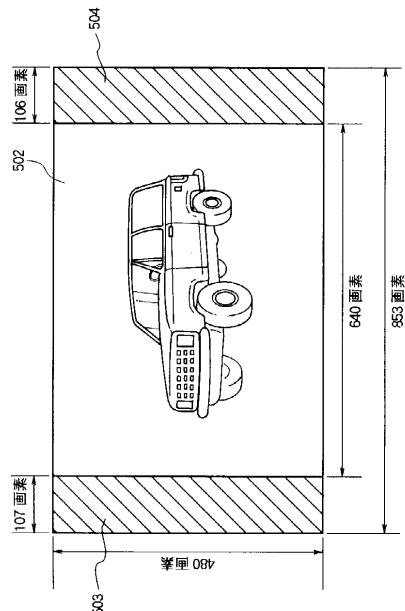

【 0 0 4 5 】

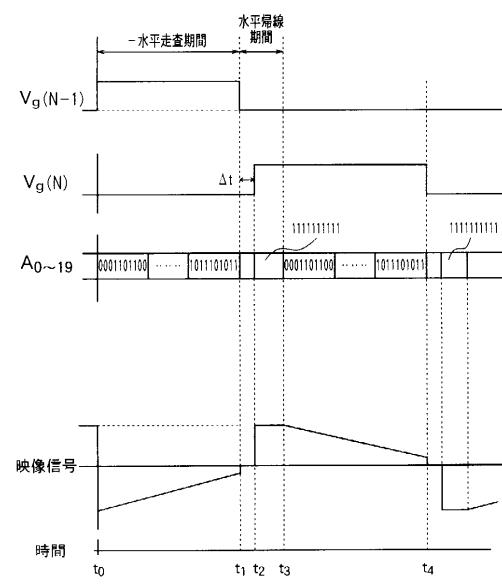

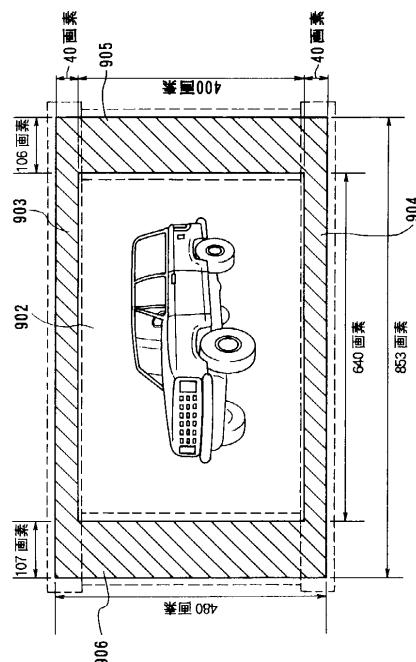

今、表示画面が図 4 に示すように、 6 4 0 × 4 8 0 画素からなる表示領域 5 0 2 と、 1 0 7 × 4 8 0 画素からなる非表示領域 5 0 3 と、 1 0 6 × 4 8 0 画素からなる非表示領域 5 0 4 とから構成される場合を例にとって本実施の形態の液晶表示装置の動作を図 3 を参照 50

して説明する。この場合の液晶表示装置は 853 本の映像信号線と 480 本の走査線を有している。

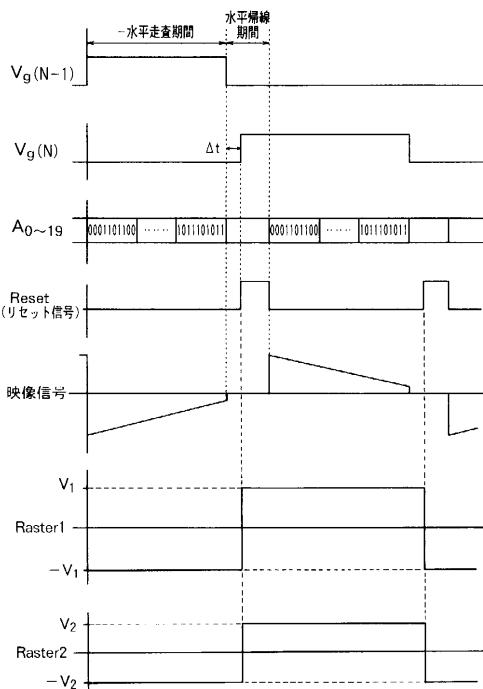

【0046】

時刻  $t_0$  において、 $N - 1$  番目の走査線  $Y_{N-1}$  に走査線駆動回路 293 から「H」レベルの電圧  $Vg(N - 1)$  が output されており、このためこの走査線  $Y_{N-1}$  に接続された TFT 121 は ON となっている。このとき、108 番目の映像信号線  $X_{108}$  から 747 番目の映像信号線  $X_{747}$  に接続された論理回路 202 が順次サンプリングパルスを出力する様なアドレス信号が、映像信号線駆動回路 291 のマトリクス配線部 201 に送られる。すると映像信号線駆動回路 291 から映像信号線  $X_{108}, \dots, X_{747}$  に映像信号が順次送られ、走査線  $Y_{N-1}$  に接続されている TFT 121 を介して、対応する画素電極 151 に映像信号データが書き込まれる（図 3 に示す一水平走査期間の間）。これにより図 4 に示す表示領域 502 中の上から  $N - 1$  行目の画素に表示データが表示されることになる。

【0047】

そして、走査線  $Y_{N-1}$  の電圧  $Vg(N - 1)$  が「L」レベルとなった時（時刻  $t_1$ ）から所定時間  $t$  経過すると、 $N$  番目の走査線  $Y_N$  の電位  $Vg(N)$  が「H」レベルになるとともにリセット信号が「L」レベルとなる（図 3 に示す時刻  $t_2$  参照）。 $N$  番目の走査線  $Y_N$  の電位  $Vg(N)$  が「H」レベルになったことにより、この走査線  $Y_N$  に接続された TFT 121 は ON となっている。このとき、リセット信号を「L」レベルにするとともに映像信号バスライン 207 に非表示データ、例えば黒表示の電位を供給すると、走査線  $Y_N$  に接続された TFT 121 を介して  $m$  ( $= 853$ ) 個の画素電極 151 に非表示データの映像信号が書き込まれる。

【0048】

時刻  $t_3$  において水平帰線期間が終了してリセット信号が「H」レベルになると、上述したと同様にして 108 番目の映像信号線  $X_{108}$  から 747 番目の映像信号線  $X_{747}$  に接続された論理回路 202 が順次サンプリングパルスを出力する様なアドレス信号が映像信号線駆動回路 291 のマトリクス配線部 201 に送られる。すると、映像信号線駆動回路 291 から映像信号線  $X_{108}, \dots, X_{747}$  に映像信号が順次送られ、走査線  $Y_N$  に接続されている TFT 121 を介して、対応する画素電極 151 に映像信号データが書き込まれる。

【0049】

したがって、表示画面の上から  $N$  行目の画素に対応する画素電極のうち、非表示領域 503, 504 の画素に対応する画素電極 151 には非表示データ、例えば黒表示の電位が書き込まれ、表示領域 502 の画素に対応する画素電極 151 には表示データが書き込まれる。

【0050】

これにより、表示領域 502 には表示データが表示され、非表示領域 503, 504 には非表示データ、上述の場合は「黒色」が表示されることになる。

【0051】

なお、図 3 に示す  $t$  は  $Y_{N-1}$  行目の走査線で制御される TFT 121 の OFF するタイミングが走査線の時定数の影響で遅れ、 $Y_N$  行に書き込むべき映像信号を  $Y_{N-1}$  行目の画素電極 151 が保持してしまうのを防ぐためのものである。

【0052】

以上説明したように本実施の形態の表示装置によれば、リセット信号を変化させるだけで、水平帰線期間に非表示領域の信号線に非表示データを書き込むことが可能となり、非表示領域の非表示データの表示を容易に行うことができる。

【0053】

なお、上記実施の形態の液晶表示装置において、非表示データとして同フレームで画素電極に書き込む映像信号と同極性の信号を指定して、水平帰線期間中にあらかじめ書き込んでおくこと、すなわちプリチャージすることにより表示データの十分な書き込みを行うことが可能となり、高コントラストの表示を得ることができる。

【0054】

10

20

30

40

50

また、本実施の形態においては、リセット信号によって一水平画素全てに対して非表示データの書き込みを行っているので、駆動回路によって表示画面上の水平方向で任意に表示領域を選択した場合に、選択されなかった領域の表示画素には、既に非表示データが保持される。このため映像信号に手を加えることなしに表示領域を任意に選択することができる。

#### 【0055】

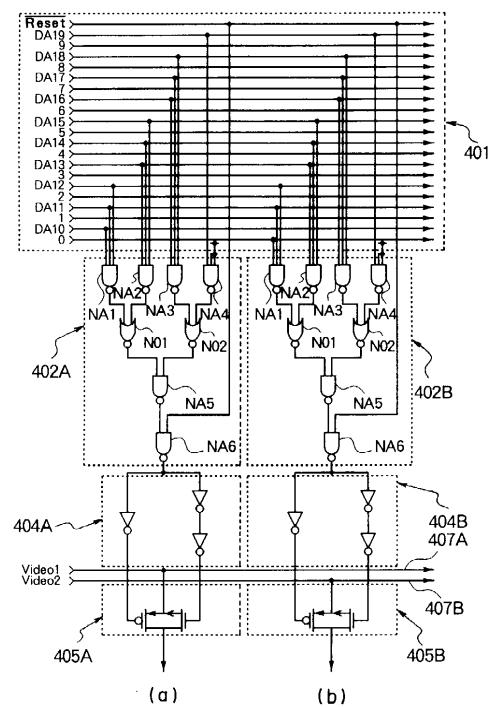

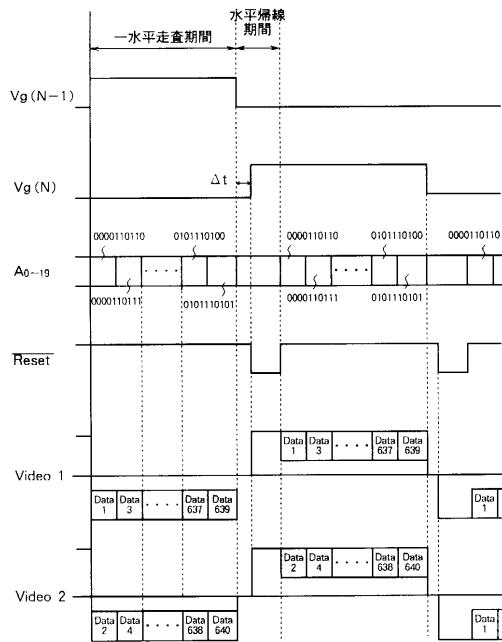

次に本発明による表示装置の第2の実施の形態の構成を図5および図6を参照して説明する。この実施の形態の表示装置は、図1乃至図2に示す第1の実施の形態の液晶表示装置において、映像信号線駆動回路291の構成を図5に示す構成の映像信号線駆動回路に置換えるとともに映像信号バスライン207の代わりに映像信号バスライン407A, 407Bを設けたものである。 10

#### 【0056】

この図5示す映像信号線駆動回路は、マトリクス配線部401と、2種類の駆動部とを備えており、一方の駆動部は表示領域の映像信号線を駆動するのに用いられ、他方の駆動部は非表示領域の映像信号線を駆動するのに用いられる。

#### 【0057】

上記一方の駆動部は図5(a)に示すように表示領域の各映像信号線毎に設けられ、論理回路402Aと、この論理回路402Aの出力を受けるバッファアンプ回路404Aと、このバッファアンプ回路404Aの出力に基づいて映像信号を選択する映像信号選択回路405Aとを備えている。また上記他方の駆動部は図5(b)に示すように非表示領域の各映像信号線毎に設けられ、論理回路402Bと、この論理回路402Bの出力を受けるバッファアンプ回路404Bと、このバッファアンプ回路404Bの出力に基づいて映像信号を選択する映像信号選択回路405Bとを備えている。 20

#### 【0058】

マトリクス配線部401は図2に示すマトリクス配線部201と同一の構成となっている。また論理回路402A, 402Bは図2に示す論理回路202と同一の構成となっている。バッファアンプ回路404A, 404Bは図2に示すバッファアンプ回路204と同一の構成となっている。なお、マトリクス配線部401と論理回路402Aは、駆動する映像信号線のアドレスがマトリクス配線部401Aに入力されているときに上記駆動する映像信号線に映像データが送出されるように接続される。また、マトリクス配線部401と論理回路402Bとの接続も同様である。なお、図5においては映像信号選択回路に接続されるべき保持容量は図示されていない。 30

#### 【0059】

そして、バッファアンプ回路404Aは論理回路402Aの出力を増幅および反転増幅し、バッファアンプ回路404Bは論理回路402Bの出力を増幅および反転増幅する。また、映像信号選択回路405は、2個のトランスマルチплексор 405A, 405Bを有している。トランスマルチплексор 405Aはバッファアンプ回路404Aの出力に基づいて映像信号バスライン407Aを介して送られてくる映像信号Video1を選択し、トランスマルチплексор 405Bはバッファアンプ回路404Bの出力に基づいて映像信号バスライン407Bを介して送られてくる映像信号Video2を選択する。 40

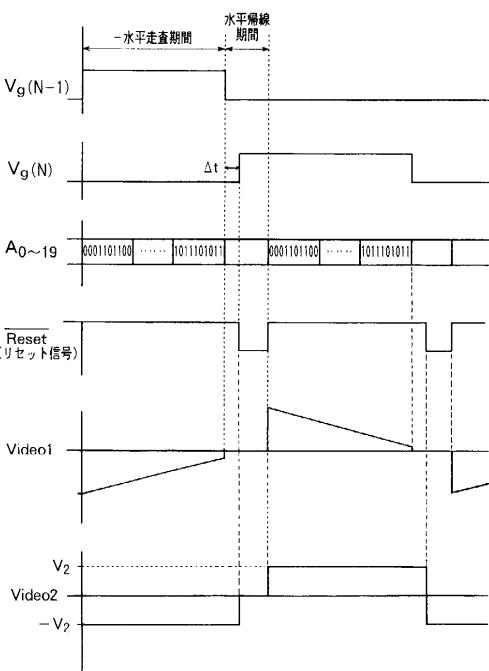

#### 【0060】

このような構成とすることにより、表示パネル内の非表示データの内容に対応して、TF T121の入力配線(映像信号線)の接続を前もって映像信号バスライン407Aと映像信号バスライン407Bとに振り分けておけば、図6に示すように映像信号に非表示データを挿入する必要がなくなる。また水平帰線期間に同時に別の表示データを書き込むことも可能となり、一水平画素ライン内で表示領域へのプリチャージの為の電圧と非表示領域への非表示データの電圧を別に設定することができる。例えば図4に示すような表示画像の場合は、表示領域502に対応する信号線に映像信号Video1が入力するように接続し、非表示領域503と非表示領域504に対応する信号線に映像信号Video2が入力するように接続する。非表示データを表示しない場合には映像信号Video1と映 50

像信号 Video 2 は全く同じであるが、非表示データを表示する場合には映像信号 Video 1 はそのままで、映像信号 Video 2 は非表示データとなる。なお、プリチャージ用電圧を設定して入力したい時は図 7 に示すように映像信号 Video 1 の水平帰線期間の電圧を  $\pm V_1$  に設定する。

【 0 0 6 1 】

この第 2 の実施の形態の液晶表示装置も第 1 の実施の形態と同様の効果を奏することは云うまでもない。

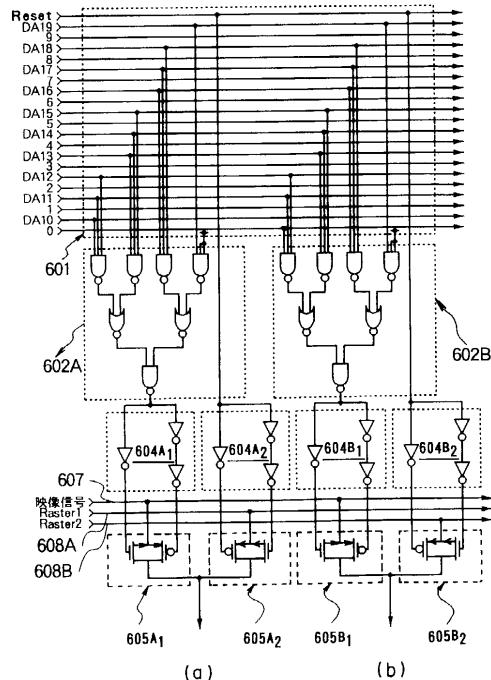

【 0 0 6 2 】

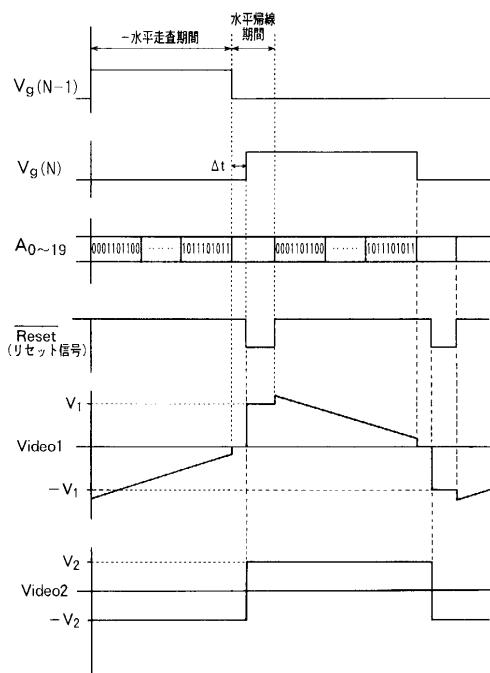

次に、本発明による表示装置の第 3 の実施の形態の構成を図 8 および図 9 を参照して説明する。この実施の形態の表示装置は、図 1 乃至図 2 に示す第 1 の実施の形態の液晶表示装置において、映像信号線駆動回路 291 の構成を図 8 に示す構成の映像信号線駆動回路に置き換えるとともに映像信号バスライン 207 の代わりに映像信号バスライン 607 およびラスタ信号バスライン 608A, 608B を設けたものである。

10

【 0 0 6 3 】

この図 8 に示す映像信号線駆動回路はマトリクス配線部 601 と、2 種類の駆動部とを備えている。2 種類の駆動部のうちの一方の駆動部は図 8 (a) に示すように駆動する信号線毎に設けられ、論理回路 602A と、バッファアンプ回路 604A<sub>1</sub>, 604A<sub>2</sub> と、トランスマジックゲートからなる映像信号選択回路 605A<sub>1</sub>, 605A<sub>2</sub> とを備えている。また他方の駆動部は図 8 (b) に示すように駆動する信号線毎に設けられ、論理回路 602B と、バッファアンプ回路 604B<sub>1</sub>, 604B<sub>2</sub> と、トランスマジックゲートからなる映像信号選択回路 605B<sub>1</sub>, 605B<sub>2</sub> とを備えている。なお、図 8 においては保持容量は図示されていない。

20

【 0 0 6 4 】

マトリクス配線部 601 は図 2 に示すマトリクス配線部 201 と同一の構成となっている。論理回路 602A, 602B は各々図 2 に示す論理回路 202 から NAND ゲート N A 6 を削除したものである。バッファアンプ回路 604A<sub>1</sub>, 604B<sub>1</sub>, 604C<sub>1</sub>, 604D<sub>2</sub> は各々、図 2 に示すバッファアンプ回路 204 と同一の構成を有している。そしてバッファアンプ回路 604A<sub>1</sub> は論理回路 602A の出力を増幅および反転増幅し、バッファアンプ回路 604B<sub>1</sub> は論理回路 602B の出力を増幅および反転増幅する。また、バッファアンプ回路 604A<sub>2</sub>, 604A<sub>3</sub> は各々リセット信号（本実施の形態においては正値論理）を増幅および反転増幅する。

30

【 0 0 6 5 】

トランスマジックゲート 605A<sub>1</sub> はバッファアンプ回路 604A<sub>1</sub> の出力に基づいて映像信号バスライン 607 を介して送られてくる映像信号を選択し、トランスマジックゲート 605B<sub>1</sub> はバッファアンプ回路 604B<sub>1</sub> の出力に基づいて映像信号バスライン 607 を介して送られてくる映像信号を選択する。またトランスマジックゲート 605A<sub>2</sub> は、バッファアンプ回路 604A<sub>2</sub> の出力に基づいて、ラスタ信号バスライン 608A を介して送られてくるラスタ信号 Raster 1 を選択し、トランスマジックゲート 605B<sub>2</sub> はバッファアンプ回路 604B<sub>2</sub> の出力に基づいて、ラスタ信号バスライン 608B を介して送られてくるラスタ信号 Raster 2 を選択する。

40

【 0 0 6 6 】

このような構成とすることにより、非表示データあるいはプリチャージ用電圧を表わすラスタ信号 Raster 1, Raster 2 を表示データを表わす映像信号と別に入力することが可能となり、図 9 に示すように映像信号の水平帰線期間のデータを修正する必要がなくなる。またラスタ信号 Raster 1 とラスタ信号 Raster 2 を別の配線で供給することで第 2 の実施の形態と同様に一水平画素ライン内で非表示データとプリチャージ用電圧を別々に設定して入力できる。

【 0 0 6 7 】

この第 3 の実施の形態の表示装置も第 1 の実施の形態の表示装置と同様の効果を奏することも云うまでもない。

50

## 【0068】

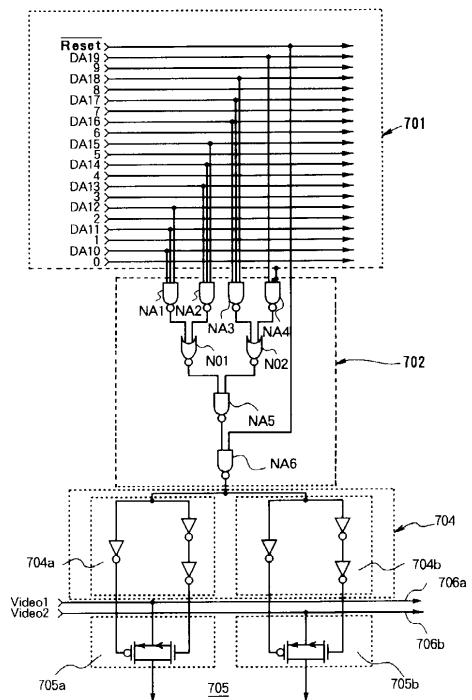

本発明による表示装置の第1、2、3の実施の形態について以上説明したが、これらは各映像信号線毎に論理回路が設置された例である。これに対して本発明の第4の実施の形態のように、1つの論理回路で複数の映像信号線を同時に駆動することができる。この第4の実施の形態について図10、11を参照して説明する。この実施の形態の表示装置は図1乃至図2に示す第1の実施の形態の液晶表示装置において、バッファアンプ回路及び映像信号選択回路を図10に示すバッファアンプ部704及び映像信号選択回路部705に置き換えたものである。バッファアンプ部704は2個のバッファアンプ回路704a、704bを有しており、映像信号選択回路部705はトランスファゲートからなる映像信号選択回路705a及びトランスファゲートからなる映像信号選択回路705bを有している。10

## 【0069】

論理回路702から出力されたサンプリングパルスが2個のバッファアンプ704a、704bに入力される。これらのバッファアンプ回路704a、704bはサンプリングパルスを増幅、反転増幅してそれぞれトランスファゲート705a、705bに入力する。トランスファゲート705aは映像信号バスライン706aを介して送られてくる映像信号Video1を選択し、トランスファゲート705bは映像信号バスライン706bを介して送られてくる映像信号Video2を選択する。そして図11に示すように映像信号バスライン706aには奇数番目の映像信号線に書き込む映像信号を供給し、映像信号バスライン706bには偶数番目の映像信号線に書き込む映像信号を供給する。但し図11の映像信号Video1、2の波形は、奇数番目、或は偶数番目の映像信号線に対応した信号の内容を図示するのは難しいため模式的表現をとっている。20

## 【0070】

そして第1の実施の形態と同様に NANDゲートNA1、NA2、NA3、NA4に入力するデジタル数値信号が全て「H」になった時だけ論理回路702からサンプリングパルスが出力されて映像信号が選択、出力される。またリセット信号が「L」レベルになるのに同期して映像信号バスライン706a、706bから必要な非表示データを供給することにより、映像信号線全てに対応する映像信号選択回路部705から非表示映像信号が出力される。なお、この第4の実施の形態ではデジタル入力信号D0～D19の周波数及び映像信号の周波数が第1の実施の形態の半分で第1の実施の形態と同様の表示を行うことができる。またこの駆動法を用いることでトランスファゲートの映像信号の十分な書き込みが可能になる。本発明の第4の実施の形態は第1の実施の形態だけではなく、第2、3の実施の形態にも適用できることは言うまでもない。30

## 【0071】

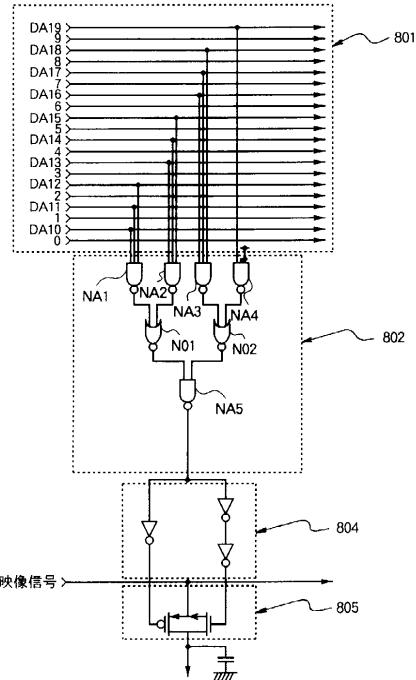

なお、以上説明した実施の形態ではリセット信号に基づいて非表示データを選択したが本発明の第5の実施の形態のようにリセット信号に基づいて非表示データを選択する回路がない場合でも非表示データを表示することが可能である。この第5の実施の形態の表示装置を図12、13を参照して説明する。

## 【0072】

この第5の実施の形態の表示装置の映像信号線駆動回路291の構成を図12に示す。この実施の形態の映像信号線駆動回路は、図12に示すようにマトリクス配線部801と、論理回路802と、バッファアンプ回路804と、映像信号選択回路805とを備えている。マトリクス配線部801は図2に示す第1の実施の形態のマトリクス配線部201からリセット信号用の配線を削除したものである。また論理回路802は図2に示す第1の実施の形態の論理回路202から最終段のNANDゲートNA6を削除したものである。なお、バッファアンプ回路804および映像信号選択回路805は図2に示す第1の実施の形態のバッファアンプ回路204および映像信号選択回路205と各々同一の構成となっている。40

## 【0073】

図13に示すように非表示データを選択、出力する時はNANDゲートNA1、NA2、N50

A3, NA4に入力するデジタル数値信号DAY0～DAY19を全て「H」とし、これに同期させて映像信号バスラインに非表示データを供給する。これにより全ての映像信号線に対して非表示データを書き込むことができる。

【0074】

以上述べた実施の形態の表示装置においては、図4に示すように表示画面の左右に非表示領域がある場合について説明した。本発明の表示装置の第6の実施の形態のように、表示画面の上下に非表示領域がある場合にも非表示データの表示を容易に行うことができる。この第6の実施の形態の表示装置を図14乃至図16を参照して説明する。

【0075】

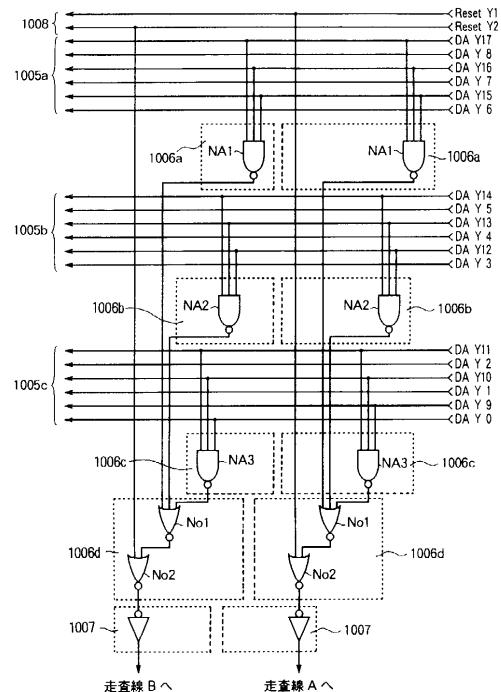

この第6の実施の形態の表示装置は、第1乃至第4のいずれかの実施の形態の表示装置において、走査線駆動回路293が図15に示すような構成を有しているものである。そして図14に示す表示画面を容易に表示することが可能となる。

10

【0076】

図14において表示データ表示領域902では、走査線駆動回路293は走査線Y<sub>1</sub>、走査線Y<sub>2</sub>、…走査線Y<sub>n</sub>に順次ゲートON電圧Vgを出力する。それに対し上下の非表示データ表示領域903、904での非表示データの書き込みでは、走査線駆動回路293は非表示領域の走査線全てに対して同時にゲートON電圧Vgを出力する。

【0077】

この実施の形態にかかる走査線駆動回路293は、図15に示すように、マトリクス配線部1005a, 1005b, 1005cと、リセット信号配線部1008とを有し、更に各走査線毎に設けられた論理回路1006a, 1006b, 1006c, 1006dおよびバッファアンプ回路1007を有している。

20

【0078】

今、走査線Y<sub>j</sub> (j = 1, … n)を選択するためのアドレス信号をA<sub>0</sub> … A<sub>8</sub> (A<sub>i</sub> (i = 0, … 8)は0または1の値を有する)とすると、マトリクス配線部1005a, 1005b, 1005c全体で18本の配線を有する。この18本の配線にはアドレス信号の9ビットA<sub>0</sub> … A<sub>8</sub>の各々の数値DAY0～DAY8と、これらの10ビットA<sub>0</sub> … A<sub>8</sub>を各々反転した数値DAY9～DAY17とが入力される。

【0079】

マトリクス配線部1005aは、数値DAY6～DAY8が入力される3本の配線と、数値DAY15～DAY17が入力される3本の配線とからなり、マトリクス配線部1005bは、数値DAY3～DAY5が入力される3本の配線と、数値DAY12～DAY14が入力される3本の配線とからなり、マトリクス配線部1005cは、数値DAY0～DAY2が入力される3本の配線と、数値DAY9～DAY11が入力される3本の配線とからなっている。

30

【0080】

またリセット信号配線部1008はリセット信号ResetY1が入力される配線とリセット信号ResetY2が入力される配線とを有している。

【0081】

論理回路1006a, 1006b, 1006cはそれぞれ3入力 NANDゲートNA1, NA2, NA3から成る。論理回路部1006dはそれぞれ2入力ノアゲートNO1, NO2から成る。NANDゲートNA1は数値信号DAY6かDAY15のどちらかと、数値信号DAY7かDAY16のどちらかと、数値信号DAY8かDAY17のどちらかが入力されている。NANDゲートNA2は数値信号DAY3かDAY12のどちらかと、数値信号DAY4かDAY13のどちらかと、数値信号DAY5かDAY14のどちらかが入力されている。NANDゲートNA3は数値信号DAY0かDAY9のどちらかと、数値信号DAY1かDAY10のどちらかと、数値信号DAY2かDAY11のどちらかが入力されている。ノアゲートNO1にはNANDゲートNA1, NA2, NA3の出力が入力される。異なる走査線に対しては3入力 NANDゲートNA1, NA2, NA3に接続される数値信号の組み合わせがそれぞれ異なっている。

40

50

## 【0082】

ノアゲートNO2には2入力のノアゲートでノアゲートNO1の出力とリセット信号が入力され、演算結果がバッファアンプ回路1007を介して走査線に送出される。またリセット信号配線部1008では表示領域の走査線Aを選択する論理回路1006dにはリセット信号ResetY1が入力され、非表示領域の走査線Bを選択する論理回路1006dにはリセット信号ResetY2が入力される。以上のように接続された NANDゲートNA1, NA2, NA3の全ての入力が「H」になった時あるいはリセット信号が「H」になったときデコーダのノアゲートNO2は「L」を出力する。

## 【0083】

ここで表示パネルの上下に非表示データを表示しない場合は、リセット信号ResetY1、ResetY2はともに常に「L」になっているため、走査信号駆動回路293は垂直走査期間にだけ順次走査電圧を順次出力する。これに対し表示パネルの上下非表示データを表示する場合はリセット信号ResetY1は常に「L」、リセット信号ResetY2は垂直走査期間は「L」、垂直帰線期間に「H」になる(図16参照)。これにより垂直帰線期間には、リセット信号ResetY2が入力された全ての論理回路1006dには NANDゲートNA1, NA2, NA3, NA4の入力に関わらず同時にサンプリングパルスをバッファアンプ回路1007に対して出力し走査電圧が出力される(図16参照)。これに合わせ映像信号線駆動回路291は垂直走査期間の間、非表示データを出力することにより複数の水平画素ラインに非表示データの書き込みが行われる。

## 【0084】

上記実施の形態でリセット信号ResetY1は常に「L」であるため、リセット信号ResetY1とノアゲートNO2の入力を設定しない回路も可能であるが、本実施の形態では各段での動作速度に差が出ないように、すべての段にノアゲートNO2が設定された回路とした。

## 【0085】

前述した水平帰線期間に左右の非表示データを書き込むと同時に、上記した駆動回路と駆動方法を用いて上下にも非表示データを表示した表示画面例を図14に示す。853×480個の表示画素を持つ表示装置で640×400画素の表示領域902でコンピュータの映像信号に基づく表示を行い、残りの表示領域903, 904, 905, 906には非表示データを表示させる。

## 【0086】

なおリセット信号を上記の2種類よりも多く設定することで更に多くの垂直画素数の映像信号規格に対応できるようになることは言うまでもない。

## 【0087】

上記第1乃至第6の実施の形態においては、映像信号線駆動回路291および走査線駆動回路293の論理回路としてはデコーダが用いられていたがシフトレジスタを用いることもできる。映像信号線駆動回路の論理回路にシフトレジスタを用いた場合を第7の実施の形態として説明する。

## 【0088】

本発明による表示装置の第7の実施の形態を図17乃至図19を参照して説明する。この実施の形態の表示装置は図1に示す液晶表示装置において、映像信号線駆動回路291を図19に示す構成の映像信号線駆動回路に置換えたものである。

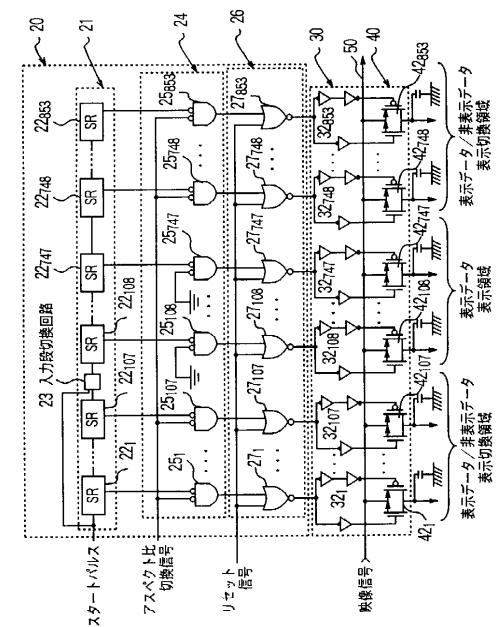

## 【0089】

この図19に示す映像信号線駆動回路は、論理回路20と、バッファアンプ部30と、映像信号選択回路40とを備えている。論理回路20はスタートパルス、アスペクト比切換信号、およびリセット信号に基づいて映像信号バスライン50から映像データまたは非表示データを取り出すためのタイミング信号を順次発生するものであって、水平シフトレジスタ回路21と、アスペクト比切換回路24と、リセット回路26とを備えている。

## 【0090】

今、本実施の形態の表示装置の表示領域281の横の画素数と縦の画素が図4に示すよう

10

20

30

40

50

に  $853 \times 480$  である場合、すなわちアスペクト比が 16:9 である場合を考える。この場合、シフトレジスタ回路 21 は上記横の画素数に対応して設けられた 853 個の例えれば D 型フリップフロップ  $22_1, \dots 22_{853}$  と、入力段切換回路 23 とを備えている。853 個のフリップフロップ  $22_1, \dots 22_{853}$  は縦続接続されている。

#### 【0091】

そして上記表示領域に図 4 に示すように表示画面 502 の始まりとなる横の画素に対応するフリップフロップ  $22_{108}$  と、このフリップフロップ  $22_{108}$  の前段のフリップフロップ  $22_{107}$  との間に入力段切換回路 23 が設けられている。外部からのスタートパルスがフリップフロップ  $22_1$  に入力されると、図示しないクロックパルスに同期して上記スタートパルスは後段のフリップフロップ  $22_2$  に転送されるとともにシフトレジスタ回路 21 の出力であるタイミング信号がアスペクト比切換回路 24 に送られる。これが各段のフリップフロップで順次繰り返される。フリップフロップ  $22_{107}$  の出力は入力段切換回路 23 に送られる。

#### 【0092】

入力段切換回路 23 は、表示領域 281 にアスペクト比 16:9 の表示画面を表示する場合には、フリップフロップ  $22_{107}$  の出力を選択し、アスペクト比 4:3 の表示画面を表示する場合には、バイパスされたスタートパルスを選択して次段のフリップフロップ  $22_{108}$  に送出する。フリップフロップ  $22_{108}$  は入力段切換回路 23 の出力（スタートパルス）を、上記クロックパルスに同期して後段のフリップフロップ  $22_{109}$  に転送するとともにアスペクト比切換回路 24 に送る。これが各段のフリップフロップで繰りかえされ、スタートパルスが順次、後段のフリップフロップに転送されるとともにアスペクト比切換回路 24 に送出される。

#### 【0093】

アスペクト比切換回路 24 は 853 個の NOR 回路  $25_1, \dots 25_{853}$  を有している。NOR 回路  $25_i$  ( $i = 1, \dots 107, 748, \dots 853$ ) はアスペクト比切換信号とフリップフロップ  $22_i$  の出力に基づいて NOR 演算を行い演算結果をリセット回路 26 に送出する。NOR 回路  $25_i$  ( $i = 108, \dots 747$ ) はアスペクト比切換信号と、「L」レベルの信号に基づいて NOR 演算を行い、演算結果をリセット回路 26 に送出する。

#### 【0094】

リセット回路 26 は 853 個の NOR 回路  $27_1, \dots 27_{853}$  を有している。NOR 回路  $27_i$  ( $i = 1, \dots 853$ ) はアスペクト比切換回路 24 の NOR 回路  $25_i$  の出力と、リセット信号に基づいて NOR 演算を行い、演算結果をバッファアンプ部 30 に送出する。

#### 【0095】

バッファアンプ部 30 は 853 個のバッファアンプ回路  $32_1, \dots 32_{853}$  を有している。また映像信号選択回路 40 は 853 個のトランスマッピングゲート  $42_1, \dots 42_{853}$  を備えている。バッファアンプ回路  $32_i$  ( $i = 1, \dots 853$ ) は、NOR 回路  $27_i$  の出力を増幅および反転増幅し、トランスマッピングゲート  $42_i$  を構成する p チャネル TFT および n チャネル TFT のゲートに各々入力される。このトランスマッピングゲート  $42_i$  ( $i = 1, \dots 853$ ) が ON となっている期間の間、映像信号バスラインを介して送られてくる映像データまたは非表示データがサンプリングされ、対応する映像信号線  $X_i$  ( $i = 1, \dots 853$ ) に送られる。

#### 【0096】

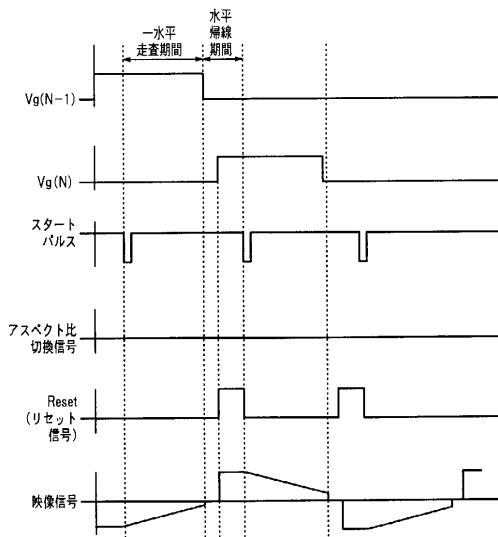

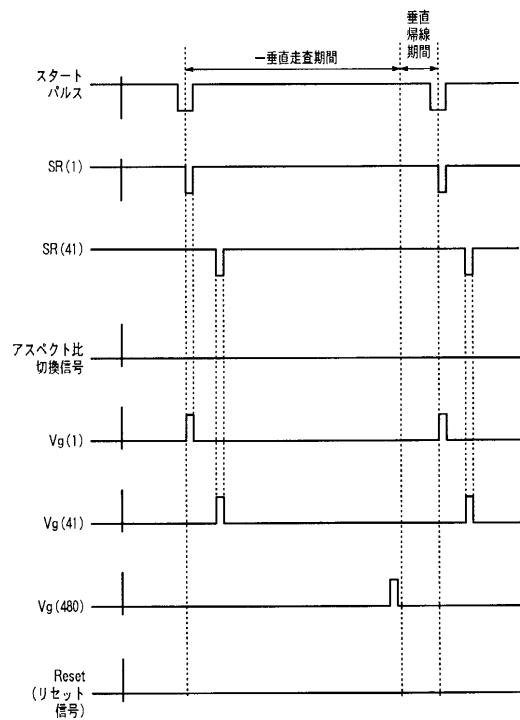

この実施の形態の表示装置の動作を図 18 および図 19 を参照して説明する。図 18 はアスペクト比が 16:9 の表示画面を表示する場合のタイミングチャートであり、図 19 はアスペクト比が 4:3 の表示画面を表示する場合のタイミングチャートである。

#### 【0097】

アスペクト比が 16:9 の表示画面を表示する場合は、アスペクト比切換信号は「L」レベルに設定される。そして入力段切換回路 23 によってフリップフロップ  $22_{107}$  の出力

10

20

20

30

40

50

が選択されてフリップフロップ 22<sub>108</sub> に送られるように接続が切換られている。したがって一水平走査期間の開始時に外部から水平シフトレジスタ回路 21 に入力されたスタートパルスはクロック信号に同期してフリップフロップ 22<sub>1</sub> , ... 22<sub>853</sub> に順次転送されるとともに、これらの各フリップフロップ 22<sub>i</sub> (i = 1, ... 853) からアスペクト比切換回路 24 の対応する NOR 回路 25<sub>i</sub> にタイミング信号が送出される。なお、スタートパルスおよびタイミング信号は、この実施の形態においては図 18 に示すように負論理となっているとともにリセット信号は正論理となっている。各フリップフロップ 22<sub>i</sub> (i = 1, ... 853) からタイミング信号が対応する NOR 回路 25<sub>i</sub> に送られると、NOR 回路 25<sub>i</sub> から「H」レベルの信号が出力されてリセット回路 26 の対応する NOR 回路 27<sub>i</sub> に送信される。

10

#### 【0098】

上記一水平走査期間中はリセット信号は「L」レベルに設定されているので NOR 回路 25<sub>i</sub> の出力が「H」の時だけ NOR 回路 27<sub>i</sub> (i = 1, ... 853) から「L」レベルの信号が出力され、バッファアンプ回路 32<sub>i</sub> を介して対応するトランスファゲート 42<sub>i</sub> が ON する。これによりトランスファゲート 42<sub>i</sub> (i = 1, ... 853) によって映像信号バスライン 50 から映像データが対応する映像信号線 X<sub>i</sub> 取り込まれる（図 18 参照）。このようにして一水平走査期間中に映像信号線 X<sub>1</sub> , ... X<sub>853</sub> に映像データが順次取り込まれる。

#### 【0099】

またこの実施の形態においては、水平帰線期間のある期間にリセット信号が「H」レベルとなるため（図 18 参照）、リセット回路 26 の各 NOR 回路 27<sub>i</sub> (i = 1, ... 853) から「L」レベルの信号が出力され、全てのトランスファゲート 42<sub>i</sub> , ... 42<sub>853</sub> が ON となる。このとき映像信号バスライン 50 に非表示データ、例えば黒表示の電位を供給すると、この非表示データはトランスファゲート 42<sub>i</sub> (i = 1, ... 853) を介して対応する映像信号線 X<sub>i</sub> 送られる。そして第 1 の実施の形態の場合と同様に走査線駆動回路 293 によって現在選択されている走査線に接続された TFT121 を介して 853 個の画素電極に上記非表示データが書き込まれる。

20

#### 【0100】

一方、アスペクト比が 4 : 3 表示画面を表示する場合は、図 19 に示すようにアスペクト比切換信号は「H」レベルに固定される。したがってアスペクト比切換回路 24 の NOR 回路 25<sub>1</sub> ~ 25<sub>107</sub> および NOR 回路 25<sub>748</sub> ~ 25<sub>853</sub> の出力は各々、常に「L」レベルとなっている。水平帰線期間のある期間にリセット信号は「H」レベルとなるから（図 19 参照）、アスペクト比が 16 : 9 の場合と同様に、走査線駆動回路 293 によって現在選択されている走査線に接続された TFT121 を介して 853 個の画素電極に非表示データを書き込むことが可能となる。

30

#### 【0101】

そして一水平走査期間においては、上記の通り NOR 回路 25<sub>1</sub> ~ 25<sub>107</sub> および NOR 回路 25<sub>748</sub> ~ 25<sub>853</sub> の出力は常に「L」レベルであり、図 19 に示すようにリセット信号は「L」レベルであるから、リセット回路 26 の NOR 回路 27<sub>1</sub> ~ 27<sub>107</sub> および NOR 回路 27<sub>748</sub> ~ 27<sub>853</sub> の出力は、各々「H」レベルとなる。このため、一水平走査期間内ではトランスファゲート 42<sub>1</sub> ~ 42<sub>107</sub> およびトランスファゲート 42<sub>748</sub> ~ 42<sub>853</sub> は ON せず、対応する映像信号線 X<sub>1</sub> ~ 27<sub>107</sub> および X<sub>748</sub> ~ X<sub>853</sub> に TFT121 を介して接続された画素電極には、映像データが書き込まれない。上記画素電極は、水平帰線期間に書き込まれたデータを保持している。

40

#### 【0102】

また、一水平走査期間中に外部から送出されてくるスタートパルスはフリップフロップ 22<sub>1</sub> に入力されるとともに入力段切換回路 23 を介してフリップフロップ 22<sub>108</sub> に入力される。そしてクロック信号に同期してフリップフロップ 22<sub>1</sub> からフリップフロップ 22<sub>107</sub> まで、スタートパルスが順次転送されるとともに、フリップフロップ 22<sub>108</sub> から最終段のフリップフロップ 22<sub>853</sub> までスタートパルスが順次転送される。なお、フリッ

50

フリップフロップ<sub>107</sub> の出力は入力段切換回路 23 によってフリップフロップ 22<sub>108</sub> には送られない。

【0103】

そして上記クロック信号に同期して各段のフリップフロップ 22<sub>i</sub> (i = 1, ..., 853) からスタートパルスが出力されるとともに対応する NOR 回路 25<sub>i</sub> にタイミング信号が送出される。

【0104】

このように一水平走査期間中に各 NOR 回路 25<sub>i</sub> (i = 1, ..., 853) にはタイミング信号が送出されるが、前述したようにトランスマルチエクスル 42<sub>1</sub> ~ 42<sub>107</sub> およびトランスマルチエクスル 42<sub>748</sub> ~ 42<sub>853</sub> は ON しない。

10

【0105】

これに対してトランスマルチエクスル 42<sub>108</sub> ~ 42<sub>747</sub> はアスペクト比 16 : 9 の場合と同様に上記タイミング信号に応じて ON するから、映像データを取り込むことが可能となる。したがって映像信号線 X<sub>i</sub> (i = 108, ..., 747) に、 TFT121 を介して接続された画素電極には映像データが書き込まれることになり、例えば図 4 に示すように表示領域 502 には映像データが表示され、非表示領域 503, 504 には非表示データが表示されることになる。

【0106】

なおこの第 7 の実施の形態においては第 1 の実施の形態の映像信号線駆動回路 291 の論理回路としてデコーダの代わりにシフトレジスタを用いたが、第 2、第 4 および第 5 の実施の形態の映像信号線駆動回路の論理回路としてデコーダの代わりにシフトレジスタを用いることが可能であることは言うまでもない。

20

【0107】

なお、本実施の形態においては、映像データと非表示データとを選択するためのスイッチは共用のアナログスイッチを用いているため、映像信号線駆動回路は小さくすることが可能となり、映像信号線駆動回路が設けられる、表示画面の周囲の額縁と呼ばれる領域を小さくすることができる。また、映像信号線駆動回路を表示領域の両側から設けて両側から駆動することができ、より高精細化することができる。

【0108】

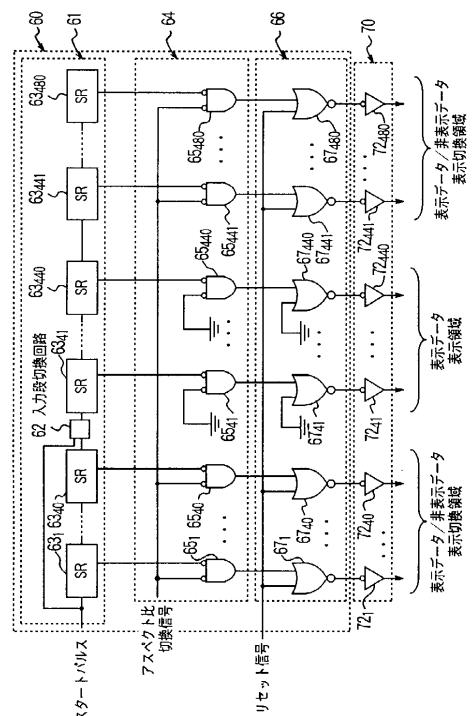

次に走査線駆動回路 293 の論理回路としてシフトレジスタを用いた場合を第 8 の実施の形態として説明する。

30

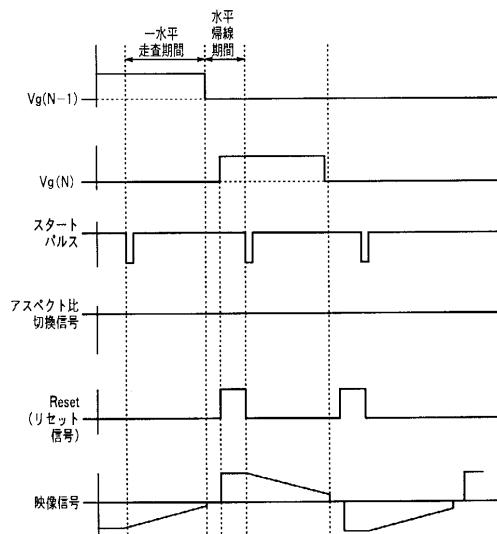

【0109】

本発明による表示装置の第 8 の実施の形態を図 20 乃至図 22 を参照して説明する。この第 8 の実施の形態の表示装置は、例えば第 7 の実施の形態の表示装置において走査線駆動回路 293 の論理回路にシフトレジスタを用いたものである。この走査線駆動回路 293 は、論理回路 60 と、バッファアンプ回路 70 とを備えている。

【0110】

論理回路 60 は、スタートパルス、アスペクト比切換信号、およびリセット信号に基づいて走査線を選択するためのタイミング信号を順次発生するものであって、シフトレジスタ回路 61 と、アスペクト比切換回路 64 と、リセット回路 66 とを備えている。

40

【0111】

今、本実施の形態の表示装置の表示領域 281 (図 1 参照) の横の画素数と縦の画素数が図 14 に示すように 853 × 480 である場合、すなわちアスペクト比が 16 : 9 である場合を考える。この場合、シフトレジスタ回路 61 は上記縦の画素数に対応して設けられた 480 個の例えば D 型のフリップフロップ 63<sub>1</sub>, ..., 63<sub>480</sub> と、入力段切換回路 62 とを備えている。480 個のフリップフロップ 63<sub>1</sub>, ..., 63<sub>480</sub> は縦続接続されている。

【0112】

そして上記表示領域 281 に、図 14 に示すようにアスペクト比が 8 : 5 の表示画面 902 を表示するときに、この表示画面 902 の始まりとなる縦の画素に対応するフリップフ

50

ロップ 6 3<sub>41</sub> とこの前段のフリップフロップ 6 3<sub>40</sub> との間に入力段切換回路 6 2 が設けられている。

【 0 1 1 3 】

外部から送られてくるスタートパルスがフリップフロップ 6 3<sub>1</sub> に入力されると、図示しないクロックパルスに同期して上記スタートパルスは順次後段のフリップフロップに転送されるとともに、各段のフリップフロップ 6 3<sub>i</sub> ( i = 1, ... 4 0 ) からタイミング信号がアスペクト比切換回路 6 4 に順次送出される。

【 0 1 1 4 】

入力段切換回路 6 2 は、表示領域 2 8 1 ( 図 1 参照 ) に図 1 4 に示すようなアスペクト比が 8 : 5 の表示画面 9 0 2 を表示する場合には、バイパスされたスタートパルスを選択し、図 4 に示すようなアスペクト比が 4 : 3 の表示画面 5 0 2 を表示する場合にはフリップフロップ 6 3<sub>40</sub> の出力を選択して次段のフリップフロップ 6 3<sub>41</sub> に送出する。

10

【 0 1 1 5 】

フリップフロップ 6 3<sub>41</sub> は入力段切換回路 6 2 の出力を、上記クロックパルスに同期して後段のフリップフロップ 6 3<sub>42</sub> ( 図示せず ) に転送するとともにアスペクト比切換回路 6 4 に送る。これが以後の各段のフリップフロップで繰り返され、スタートパルスが順次後段のフリップフロップに転送されるとともにアスペクト比切換回路 6 4 に送出される。

【 0 1 1 6 】

アスペクト比切換回路 6 4 は 4 8 0 個の N O R 回路 6 5<sub>1</sub>, ... 6 5<sub>480</sub> を有している。 N O R 回路 6 5<sub>i</sub> ( i = 1, ... 4 0, 4 1 1, ... 4 8 0 ) はアスペクト比切換信号とフリップフロップ 6 3<sub>i</sub> の出力とに基づいて N O R 演算を行い、演算結果をリセット回路 6 6 に送出する。また N O R 回路 6 5<sub>i</sub> ( i = 4 1, ... 4 4 0 ) はフリップフロップ 6 3<sub>i</sub> の出力と、「 L 」レベルの信号とに基づいて N O R 演算を行い、演算結果をリセット回路 6 6 に送出する。

20

【 0 1 1 7 】

リセット回路 6 6 は、4 8 0 個の N O R 回路 6 7<sub>1</sub>, ... 6 7<sub>480</sub> を有している。 N O R 回路 6 7<sub>i</sub> ( i = 1, ... 4 0, 4 1 1, ... 4 8 0 ) はアスペクト比切換回路 6 4 の N O R 回路 6 5<sub>i</sub> の出力と、リセット信号とに基づいて N O R 演算を行い、演算結果をバッファアンプ回路 7 0 に送出する。また N O R 回路 6 7<sub>i</sub> ( i = 4 1, ... 4 4 0 ) は N O R 回路 6 5<sub>i</sub> の出力と、「 L 」レベルの信号とに基づいて N O R 演算を行い、演算結果をバッファアンプ回路 7 0 に送出する。

30

【 0 1 1 8 】

バッファアンプ回路 7 0 は、4 8 0 個のバッファアンプ 7 2<sub>1</sub>, ... 7 2<sub>480</sub> を有している。バッファアンプ 7 2<sub>i</sub> ( i = 1, ... 4 8 0 ) はリセット回路 6 6 の N O R 回路 6 7<sub>i</sub> の反転出力を增幅し、対応する走査線 Y<sub>i</sub> に送出する。

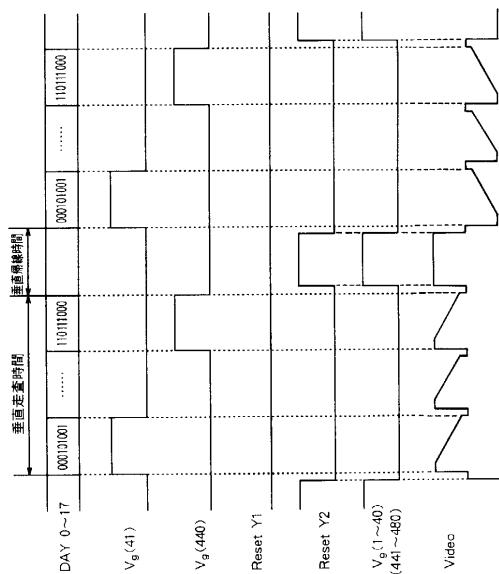

【 0 1 1 9 】

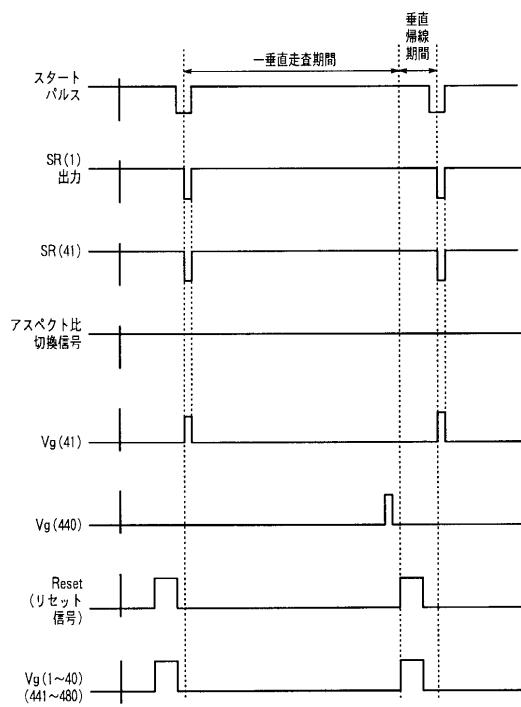

この第 8 の実施の形態の動作を図 2 1 および図 2 2 を参照して説明する。図 2 1 はアスペクト比が 4 : 3 の表示画面を表示する場合のタイミングチャートであり、図 2 2 はアスペクト比が 8 : 5 の表示画面を表示する場合のタイミングチャートである。

【 0 1 2 0 】

40

アスペクト比が 4 : 3 の表示画面を表示する場合は、アスペクト比切換信号およびリセット信号 ( 本実施例では正論理 ) は「 L 」レベルに設定されている。そして入力切換回路 2 3 によってフリップフロップ 6 3<sub>40</sub> の出力が選択されてフリップフロップ 6 3<sub>41</sub> に送られるように接続が切換えられる。

【 0 1 2 1 】

したがって一垂直走査期間の開始時に外部からシフトレジスタ回路 6 1 に入力されたスタートパルスはクロック信号に同期してフリップフロップ 6 3<sub>1</sub>, ... 6 3<sub>480</sub> に順次転送されるとともに、これらの各フリップフロップ 6 3<sub>i</sub> ( i = 1, ... 4 8 0 ) からアスペクト比切換回路 6 4 の対応する N O R 回路 6 5<sub>i</sub> に「 L 」レベルのタイミングパルス信号 S R ( i ) が送出される ( 図 2 1 参照 )。すると N O R 回路 6 5<sub>i</sub> ( i = 1, ... 4 8 0 ) から

50

「H」レベルのパルス信号が出力され、これによりリセット回路66のNOR回路67<sub>i</sub>から「L」レベルのパルス信号が出力され、更に対応するバッファアンプ72<sub>i</sub>から「H」レベルのパルス信号Vg(i)が出力される。

【0122】

以上により一垂直走査期間に全走査線で順次書き込みが行われ、図4に示すアスペクト比が4:3の表示画面502が表示されることになる。

【0123】

アスペクト比が8:5の表示画面を表示する場合は、図22に示すようにアスペクト比切換信号は「H」レベルに設定されるとともに、リセット信号は垂直帰線期間中の所定期間だけ「H」レベルにされる。そして入力段切換回路23によってバイパスされたスタートパルスが選択されてフリップフロップ63<sub>41</sub>に送られるように接続が切換えられる。 10

【0124】

したがって一垂直走査期間の開始時に外部からシフトレジスタ回路61に入力されたスタートパルスはクロック信号に同期してフリップフロップ63<sub>1</sub>...63<sub>41</sub>とフリップフロップ63<sub>41</sub>...63<sub>480</sub>、それそれで順次転送されるとともに、これらの各フリップフロップ63<sub>i</sub>(i=1,...480)からアスペクト比切換回路64の対応するNOR回路65<sub>i</sub>に「L」レベルのタイミングパルス信号SR(i)が出力される(図22参照)。

【0125】

するとNOR回路65<sub>i</sub>(i=1,...480)から「H」レベルのパルス信号が出力される。しかし、アスペクト比切換信号が「H」レベルに設定されているため、他のNOR回路65<sub>i</sub>(i=1,...40,441,...480)の出力は「L」レベルに固定されたままとなっている。 20

【0126】

したがってリセット回路66のNOR回路67<sub>i</sub>(i=1,...40,441,...480)の出力は一垂直走査期間中、「H」レベルに固定されるが、表示データ表示領域のNOR回路67<sub>i</sub>(i=41,...441)の出力は、アスペクト比切換回路64の対応するNOR回路65<sub>i</sub>からパルス信号を受信したときに「L」レベルのパルス信号を出力する。

【0127】

これにより表示切換領域903,904(図14参照)のバッファアンプ72<sub>i</sub>(i=1,...40,441,...480)の出力は一垂直走査期間中、「L」レベルに固定され、表示切換領域の走査線は選択されない。しかし、データ表示領域のバッファアンプ72<sub>i</sub>(i=41,...440)からは、選択するためのタイミングパルス信号Vg(i)が順次出力され、一垂直走査期間中に対応する走査線Y<sub>i</sub>が順次走査される。これにより図14に示すように、表示データ表示領域902にのみ映像データの書き込みが行われる。 30

【0128】

また垂直帰線期間の所定期間にリセット信号が「H」レベルになることにより、表示切換領域903,904のNOR回路67<sub>i</sub>(i=1,...40,441,...480)の出力は垂直帰線期間の所定期間中、「L」レベルになる。なおこのとき表示領域のNOR回路67<sub>i</sub>(i=41,...441)の出力は「H」レベルである。

【0129】

したがって、表示切換領域のバッファアンプの出力は「H」レベルとなるから、この表示切換領域の走査線Y<sub>i</sub>(i=1,...40,441,...480)は、上記所期間中、常時選択されており、これらの走査線に接続された全てのTFTはONとなる。また表示領域のバッファアンプの出力は「L」レベルとなるから表示領域の走査線Y<sub>i</sub>(i=41...440)に接続された全てのTFTは、上期期間中常時OFFとなる。 40

【0130】

以上説明したように本実施の形態の表示装置によれば、非表示領域の非表示データの表示を容易に行うことができる。

【0131】

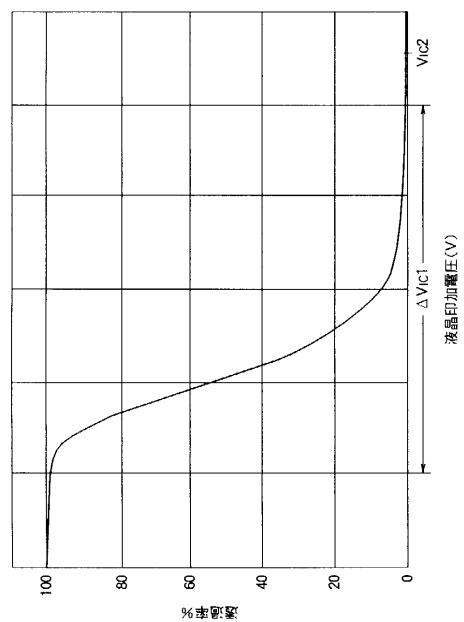

なお、上記第1乃至第8の実施の形態において図23に示すように、非表示データの書き 50

込みの際に液晶に印加する電圧を、表示データを表示する際に液晶に印加する電圧領域  $V_{Lc1}$  より大きな電圧  $V_{Lc2}$  にすることでフリッカ見えにくくすることもできる。

【0132】

また上記実施の形態では非表示データを黒表示としたが白でも中間調でもよい。

【0133】

なお上記実施の形態においては表示装置は液晶表示装置であったが、他の表示装置にも本発明を適用できることは云うまでもない。

【0134】

【発明の効果】

以上述べたように本発明によれば、非表示領域の非表示データの表示を容易に行なうことができる。 10

【図面の簡単な説明】

【図1】本発明による表示装置の第1の実施の形態の構成を示す構成図。

【図2】第1の実施の形態の表示装置にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図3】第1の実施の形態の表示装置の駆動タイミングを示す図。

【図4】本発明の表示装置によって表示される表示画像の一例を示す図。

【図5】本発明による表示装置の第2の実施の形態にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図6】第2の実施の形態の表示装置の駆動タイミングを示す図。 20

【図7】第2の実施の形態の表示装置の他の駆動タイミングを示す図。

【図8】本発明による表示装置の第3の実施の形態にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図9】第3の実施の形態の表示装置の駆動タイミングを示す図。

【図10】本発明による表示装置の第4の実施の形態にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図11】第4の実施の形態の表示装置の駆動タイミングを示す図。

【図12】本発明による表示装置の第5の実施の形態にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図13】第5の実施の形態の表示装置の駆動タイミングを示す図。 30

【図14】本発明の表示装置によって表示される表示画像の一例を示す図。

【図15】本発明による表示装置の第6の実施の形態にかかる走査線駆動回路の一具体例の構成を示す図。

【図16】第6の実施の形態の表示装置の駆動タイミングを示す図。

【図17】第7の実施の形態にかかる映像信号線駆動回路の一具体例の構成を示す図。

【図18】第7の実施の形態の表示装置の一駆動方法を説明するタイミングチャート。

【図19】第7の実施の形態の表示装置の他の駆動方法を説明するタイミングチャート。

【図20】第8の実施の形態にかかる走査線駆動回路の一具体例の構成を示す図。

【図21】第8の実施の形態の表示装置の一駆動方法を説明するタイミングチャート。

【図22】第8の実施の形態の表示装置の他の駆動方法を説明するタイミングチャート。 40

【図23】液晶印加電圧と光透過率との関係を示すグラフ。

【符号の説明】

20 論理回路

21 水平シフトレジスタ回路

21<sub>i</sub> (i = 1, ..., 8 5 3) フリップフロップ

23 入力段切換回路

24 アスペクト比切換回路

25<sub>i</sub> (i = 1, ..., 8 5 3) NOR回路

26 リセット回路

27<sub>i</sub> (i = 1, ..., 8 5 3) NOR回路

|                                       |                                                |    |

|---------------------------------------|------------------------------------------------|----|

| 3 0                                   | バッファアンプ部                                       |    |

| 3 2                                   | <sub>i</sub> ( i = 1 , ... 8 5 3 ) NOR 回路      |    |

| 4 0                                   | 映像信号選択回路                                       |    |

| 4 2                                   | <sub>i</sub> ( i = 1 , ... 8 5 3 ) トランスマジックゲート |    |

| 6 0                                   | 論理回路                                           |    |

| 6 1                                   | シフトレジスタ回路                                      |    |

| 6 3                                   | <sub>i</sub> ( i = 1 , ... 4 8 0 ) フリップフロップ    |    |

| 6 4                                   | アスペクト比切換回路                                     |    |

| 6 5                                   | <sub>i</sub> ( i = 1 , ... 4 8 0 ) NOR 回路      |    |

| 6 6                                   | リセット回路                                         | 10 |

| 6 7                                   | <sub>i</sub> ( i = 1 , ... 4 8 0 ) NOR 回路      |    |

| 7 0                                   | バッファアンプ回路                                      |    |

| 7 2                                   | <sub>i</sub> ( i = 1 , ... 4 8 0 ) バッファアンプ     |    |

| 1 0 1                                 | マトリクスアレイ基板                                     |    |

| 1 2 1                                 | TFT                                            |    |

| 1 5 1                                 | 画素電極                                           |    |

| 2 0 1                                 | マトリクス配線部                                       |    |

| 2 0 2                                 | 論理回路                                           |    |

| 2 0 4                                 | バッファアンプ回路                                      |    |

| 2 0 5                                 | 映像信号選択回路                                       | 20 |

| 2 0 6                                 | 保持容量                                           |    |

| 2 0 7                                 | 映像信号バスライン                                      |    |

| 2 1 1                                 | 保持容量線                                          |    |

| 2 8 1                                 | 表示領域                                           |    |

| 2 9 1                                 | 映像信号線駆動回路                                      |    |

| 2 9 3                                 | 走査線駆動回路                                        |    |

| 2 9 5                                 | 対向電極駆動回路                                       |    |

| 2 9 6                                 | 画素電位保持容量線駆動回路                                  |    |

| 3 0 1                                 | 対向電極                                           |    |

| 3 5 1                                 | 液晶層                                            | 30 |

| 4 0 1                                 | マトリクス配線部                                       |    |

| 4 0 2 A , 4 0 2 B                     | 論理回路                                           |    |

| 4 0 4 A , 4 0 4 B                     | バッファアンプ回路                                      |    |

| 4 0 5 A , 4 0 5 B                     | 映像信号選択回路 ( トランスマジックゲート )                       |    |

| 4 0 7 A , 4 0 7 B                     | 映像信号バスライン                                      |    |

| 5 0 1                                 | 液晶表示装置                                         |    |

| 5 0 2                                 | 表示領域                                           |    |

| 5 0 3                                 | 非表示領域                                          |    |

| 5 0 4                                 | 非表示領域                                          |    |

| 6 0 1                                 | マトリクス配線部                                       | 40 |

| 6 0 2 A , 6 0 2 B                     | 論理回路                                           |    |

| 6 0 4 A , 6 0 4 B                     | バッファアンプ回路                                      |    |

| 6 0 5 A , 6 0 5 B , 6 0 5 C , 6 0 5 D | 映像信号選択回路 ( トランスマジックゲート )                       |    |

| 6 0 7                                 | 映像信号バスライン                                      |    |

| 6 0 8 A , 6 0 8 B                     | ラスタ信号バスライン                                     |    |

| 7 0 1                                 | マトリクス配線部                                       |    |

| 7 0 2                                 | 論理回路                                           |    |

| 7 0 4                                 | バッファアンプ部                                       |    |

| 7 0 4 a , 7 0 4 b                     | バッファアンプ回路                                      |    |

| 7 0 5                                 | 映像信号選択回路部                                      | 50 |

705a, 705b トランスファゲート

801 マトリクス配線部

802 論理回路

804 バッファアンプ回路

805 映像信号選択回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

【 図 1 6 】

【 図 1 7 】

【 図 1 8 】

【図19】

【図20】

【図21】

【図22】

【図 2 3】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 2 F 1/133 5 5 0

H 0 4 N 5/46

H 0 4 N 5/66 1 0 2 B

(72)発明者 増 田 陽 一

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

審査官 橋本 直明

(56)参考文献 特開平08-079663 (JP, A)

特開平07-020816 (JP, A)

特開平05-260418 (JP, A)

特開平04-165329 (JP, A)

特開平08-122748 (JP, A)

特開平04-016982 (JP, A)

特開平07-298171 (JP, A)

特開平03-219288 (JP, A)

特開平04-078823 (JP, A)

特開平04-204628 (JP, A)

特開平07-140933 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/36

G02F 1/133

G09G 3/20

H04N 5/46

H04N 5/66