(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5215356号

(P5215356)

(45) 発行日 平成25年6月19日(2013.6.19)

(24) 登録日 平成25年3月8日(2013.3.8)

(51) Int.Cl.

HO3K 19/0185 (2006.01)

F 1

HO3K 19/00 101D

請求項の数 7 (全 34 頁)

(21) 出願番号 特願2010-159588 (P2010-159588)

(22) 出願日 平成22年7月14日 (2010.7.14)

(65) 公開番号 特開2012-23533 (P2012-23533A)

(43) 公開日 平成24年2月2日 (2012.2.2)

審査請求日 平成24年6月25日 (2012.6.25)

(73) 特許権者 396023993

株式会社半導体理工学研究センター

神奈川県横浜市港北区新横浜3丁目17番

地2 友泉新横浜ビル6階

(74) 代理人 100101454

弁理士 山田 卓二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100125874

弁理士 川端 純市

(72) 発明者 廣瀬 哲也

兵庫県神戸市灘区六甲台町1-1 国立大

学法人神戸大学内

最終頁に続く

(54) 【発明の名称】 レベルコンバータ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の信号レベルを有するデジタル信号である入力信号を、上記第1の信号レベルよりも高い第2の信号レベルを有する出力信号に変換するレベルコンバータ回路において、上記入力信号を増幅して上記出力信号に出力する増幅回路と、

上記入力信号の信号レベルが変化するとき上記増幅回路に流れる動作電流に対応する制御電流を生成する電流生成回路と、

上記電流生成回路によって生成された制御電流を検出して、上記増幅回路の動作電流が上記検出した制御電流に対応するように制御する電流検出回路とを備え、

上記電流生成回路は、上記電流検出回路と接地との間に挿入されかつ直列に接続された第1及び第2のnMOSトランジスタを備え、

上記第1のnMOSトランジスタは上記入力信号に応答して動作しつつ上記第2のnMOSトランジスタは上記入力信号の反転信号に応答して動作するように構成され、

上記レベルコンバータ回路は、

上記第1及び第2のnMOSトランジスタのしきい値電圧を上記レベルコンバータ回路に比較して低下させて、上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第1及び第2のnMOSトランジスタの基板電位を変化させる制御回路をさらに備えたことを特徴とするレベルコンバータ回路。

## 【請求項 2】

第1の信号レベルを有するデジタル信号である入力信号を、上記第1の信号レベルより

10

20

も高い第2の信号レベルを有する出力信号に変換するレベルコンバータ回路において、

上記入力信号を増幅して上記出力信号に出力する増幅回路と、

上記入力信号の信号レベルが変化するとき上記増幅回路に流れる動作電流に対応する制御電流を生成する電流生成回路と、

上記電流生成回路によって生成された制御電流を検出して、上記増幅回路の動作電流が上記検出した制御電流に対応するように制御する電流検出回路とを備え、

上記電流生成回路は、上記電流検出回路と接地との間に挿入されかつ直列に接続された第1及び第2のnMOSトランジスタを備え、

上記第1のnMOSトランジスタは上記入力信号に応答して動作しつつ上記第2のnMOSトランジスタは上記入力信号の反転信号に応答して動作するように構成され、10

上記レベルコンバータ回路は、

上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第1及び第2のnMOSトランジスタに対してそれぞれ並列に、別のnMOSトランジスタを接続したことを特徴とするレベルコンバータ回路。

**【請求項3】**

上記電流生成回路はさらに、

上記入力信号の信号レベルが変化しないときであって上記入力信号がハイレベルでありかつ上記出力信号がローレベルであるときに、上記出力信号がハイレベルとなるように補正するための上記制御電流を生成する立ち上がり電流生成回路と、20

上記入力信号の信号レベルが変化しないときであって上記入力信号がローレベルでありかつ上記出力信号がハイレベルであるときに、上記出力信号がローレベルとなるように補正するための上記制御電流を生成する立ち下がり電流生成回路と

のうちの少なくとも1つを備えたことを特徴とする請求項1又は2記載のレベルコンバータ回路。

**【請求項4】**

上記立ち上がり電流生成回路は、

電圧源と接地との間に挿入されかつ所定のノードを介して直列に接続された、pMOSトランジスタ及び第3のnMOSトランジスタと、

上記電流検出回路と接地との間に挿入されかつ直列に接続された第4及び第5のnMOSトランジスタとを備え、30

上記pMOSトランジスタは上記出力信号に応答して動作し、上記第3のnMOSトランジスタは上記入力信号に応答して動作し、上記第4のnMOSトランジスタは上記入力信号に応答して動作し、かつ上記第5のnMOSトランジスタは上記ノードの信号レベルに応答して動作するように構成されたことを特徴とする請求項3記載のレベルコンバータ回路。

**【請求項5】**

上記立ち下がり電流生成回路は、

上記電流検出回路と接地との間に挿入されかつ直列に接続された第6及び第7のnMOSトランジスタとを備え、

上記第6のnMOSトランジスタは上記入力信号の反転信号に応答して動作し、かつ上記第7のnMOSトランジスタは上記出力信号に応答して動作するように構成されたことを特徴とする請求項3記載のレベルコンバータ回路。40

**【請求項6】**

上記増幅回路は、差動増幅回路と、ソース接地増幅回路とを備えたことを特徴とする請求項1乃至5のうちのいずれか1つに記載のレベルコンバータ回路。

**【請求項7】**

上記ソース接地増幅回路は、プッシュプル型ソース接地増幅回路であることを特徴とする請求項6記載のレベルコンバータ回路。

**【発明の詳細な説明】**

**【技術分野】**

10

20

30

40

50

## 【0001】

本発明は、デジタル信号の信号レベルを、第1の電圧レベルから、上記第1の電圧レベルよりも高い第2の電圧レベルに変換するためのレベルコンバータ回路に関する。

## 【背景技術】

## 【0002】

L S I の消費電力を削減する最も有効な手法として、電源電圧の低減が挙げられる。特に、近年の L S I においては、回路ブロック毎に最適な電源電圧を供給する手法が採用されるため、各回路ブロック間の電源電圧が異なる場合がある。したがって、このような信号レベルの異なる回路間にはレベルコンバータ回路が必要となる。これまで、様々なレベルコンバータ回路が報告してきた。既存の回路は、ラッチ構成を基本としたレベルコンバータ回路が一般的である。しかし、これらのレベルコンバータ回路は、回路間の電源電圧の差電圧が大きな場合、低電源電圧によって駆動されるトランジスタの駆動力が極めて小さくなり、安定したレベル変換動作が保証されない課題がある。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

【特許文献1】特開平06-311014号公報。

【特許文献2】特開2006-135384号公報。

【特許文献3】特開2007-180671号公報。

20

## 【非特許文献】

## 【0004】

【非特許文献1】S. Henzler, "Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies", Springer, October 2006.

【非特許文献2】Y. Kanno, H. Mizuno, K. Tanaka, and T. Watanabe, "Level converters with high immunity to power-supply bouncing for high-speed sub-1-V LSIs", Digest of Technical Papers of 2000 Symposium on VLSI Circuits, pp. 202-203, June 2000.

【非特許文献3】I. J. Chang, J. J. Kim, and K. Roy, "Robust level converter design for sub-threshold logic", in Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED), pp. 14-19, October 2006.

30

【非特許文献4】O-S. Kwon and K.-S. Min, "Fast-delay and low-power level shifter for low-voltage applications", IEICE Transactions on Electronics, Volume E90-C, number 7, pp. 1540-1543, July 2007.

【非特許文献5】H. Shao and C.-Y. Tsui, "Low energy level converter design for sub-V<sub>th</sub> logics", in Proceedings of Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 107-108, January 2009.

【非特許文献6】Y.-S. Lin and D. M. Sylvester, "Single stage static level shifter design for subthreshold to I/O Voltage conversion", in Proceeding of the 13th International Symposium on Low Power Electronics and Design (ISLPED), pp. 197-200, August 2008.

40

【非特許文献7】F. Ishihara, F. Shikh, and B. Nikolic, "Level conversion for dual-supply systems", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Volume 12, Issue 2, pp. 185-195, February 2004.

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

これまで、C M O S ( C o m p l e m e n t a r y M e t a l O x i d e S e m i c o n d u c t o r ) 半導体集積回路の低消費電力化は、デバイス素子の微細化及びそれに伴う電源電圧の低減によって実現してきた。デジタル回路の消費電力は電源電圧の2乗で表されることから、電源電圧の低減は低消費電力化に極めて有効な手法である。近

50

年のLSIにおいては、回路ブロック毎に最適な電源電圧を供給する手法が採用されるため、回路ブロック間の電源電圧が異なる設計がなされる（非特許文献1参照。）。したがって、信号レベルの異なる回路間には、レベルコンバータ回路が必要となる。

#### 【0006】

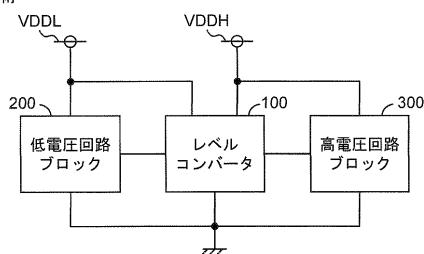

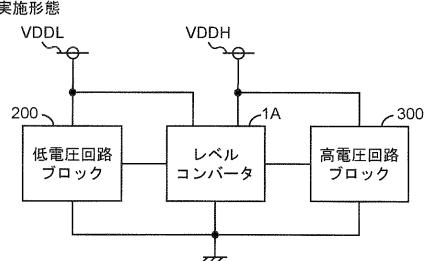

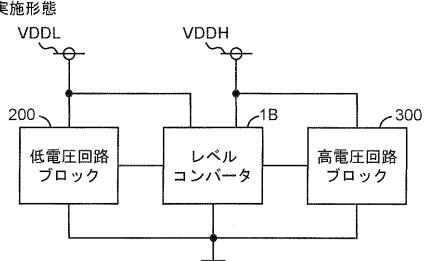

図1は、従来技術に係るレベルコンバータ回路100の応用例を示すブロック図である。図1において、レベルコンバータ回路100は、低電源電圧VDDL（例えば0.4Vである。）が供給される低電圧回路ブロック200からの信号の信号レベルを変換して、高電源電圧VDDH（例えば3Vである。）が供給される高電圧回路ブロック300に出力する。低電圧回路ブロック200からレベルコンバータ回路100に入力される入力信号INは、ハイレベル又はローレベルを有する2値信号であり、ハイレベルの電位は低電源電圧VDDLであり、ローレベルの電位は接地電位である。また、レベルコンバータ回路100によって高電圧回路ブロック300に出力される出力信号OUTは、ハイレベル又はローレベルを有する2値信号であり、ハイレベルの電位は高電源電圧VDDHであり、ローレベルの電位は接地電位である。以下、低電源電圧VDDLの電圧レベルを第1のハイレベルといい、高電源電圧VDDHの電圧レベルを第2のハイレベルという。また、低電源電圧VDDLを有する電圧源を低電圧源といい、高電源電圧VDDHを有する電圧源を高電圧源という。

#### 【0007】

これまで、様々なレベルコンバータ回路が報告してきた。多くのレベルコンバータ回路は、クロスカップル接続されたpチャネルMOSFET（Metal Oxide Semiconductor Field Effect Transistor）（以下、pMOSトランジスタという。）からなるラッチ回路と、nチャネルMOSFET（以下、nMOSトランジスタという。）とを備えて構成される。しかし、これらのレベルコンバータ回路のnMOSトランジスタは低電源電圧で駆動されることになるため、pMOSトランジスタとnMOSトランジスタとの間の駆動力を考慮した回路設計が極めて重要になる。ラッチ回路を基本にしたレベルコンバータ回路では、pMOSトランジスタをクロスカップル接続させてポジティブフィードバック回路を構成するので、出力信号を反転させるためにnMOSトランジスタのチャネル幅を大きく設計してnMOSトランジスタの駆動力を高める手法、及びクロスカップル接続されたpMOSトランジスタの駆動力を低くする手法など、様々な改善策が試みられている（非特許文献2乃至7、及び特許文献1乃至3参照。）。しかし、電源電圧の低電圧化が進み電源電圧間の差電圧が大きくなると、これらの設計手法では安定したレベル変換動作を保証することが困難になる。

#### 【0008】

最初に、従来技術に係るレベルコンバータ回路であるクロスカップル接続型レベルコンバータ回路について説明し、その課題について述べる。

#### 【0009】

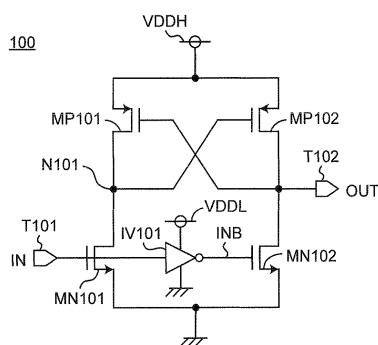

図2は、従来技術に係るクロスカップル型レベルコンバータ回路100の構成を示す回路図である。レベルコンバータ回路100は、入力信号IN及び入力信号INBがそれぞれゲートに入力されたnMOSトランジスタ（MN101, MN102）とクロスカップル接続されたpMOSトランジスタ（MP101, MP102）とで構成される。ここで入力信号INと入力信号INBとは、相補関係である。入力信号INが第1のハイレベルになると、入力信号INB及びノードN101の電圧はローレベルとなる。これにより、pMOSトランジスタMP102を介して端子T102が充電されて、レベルコンバータ回路100は第2のハイレベルである出力信号OUTを出力する。一方、入力信号INがローレベルになると、入力信号INBは第1のハイレベルとなる。nMOSトランジスタMN102は端子T102を放電して、レベルコンバータ回路100はローレベルの出力信号OUTを出力する。

#### 【0010】

しかし、従来技術に係るレベルコンバータ回路100には、端子T102を充電する電流と放電する電流との間に大きな差があると正常に動作しない課題がある。これは、電源

10

20

30

40

50

電圧間（高電源電圧VDDHと低電源電圧VDDLとの間）の差電圧が大きくなると特に顕著になる。例えば、入力信号INが第1のハイレベルからロー・レベルになったとき、nMOSトランジスタMN102は低電圧源の低電源電圧VDDLで駆動される。このとき、pMOSトランジスタMP102を流れる電流が、nMOSトランジスタMN102を流れる電流よりも多くなると、出力信号OUTの論理（信号レベル）は反転せず、第2のハイレベルが保持される。すなわち、入力信号INがロー・レベルであるにも関わらず、出力信号OUTは第2のハイレベルのままとなり、レベルコンバータ回路100が正常に動作しない。

【0011】

従来技術に係るレベルコンバータ回路100において安定動作を保証するためには、nMOSトランジスタMN102を流れる電流量とpMOSトランジスタMP102を流れる電流量とをバランスさせる必要がある。このために、nMOSトランジスタMN102及びpMOSトランジスタMP102のチャネル幅及びしきい値電圧を適切に設定する必要がある。しかし、pMOSトランジスタMP102のゲートに入力される電圧の振幅は、接地電圧から高電源電圧VDDHと広い一方、nMOSトランジスタMN102のゲートに入力される電圧の振幅は接地電圧から低電源電圧VDDLと狭い。すなわち、従来技術に係るレベルコンバータ回路100は、高電源電圧VDDHと低電源電圧VDDLとの間の電圧差が大きくなると、nMOSトランジスタMN102を流れる電流量とpMOSトランジスタMP102を流れる電流量とのバランスを取ることが困難となる。さらに、プロセスバラツキ及び温度変化によってnMOSトランジスタMN102及びpMOSトランジスタMP102を流れる電流量が変化すると、レベルコンバータ回路100は安定して動作しない。

【0012】

これらの問題点を改善するためのレベルコンバータ回路が提案されている（非特許文献2乃至7、及び特許文献1乃至3参照。）。しかし、これらのレベルコンバータ回路の多くがクロスカップル接続を基本とし、nMOSトランジスタ及びpMOSトランジスタを流れる電流のバランスを取りやすくした回路構成を実現しているが、上記の課題を解決したものとはいえない。

【0013】

本発明の目的は以上の問題点を解決し、従来技術に比較して、回路ブロック間の電源電圧の差電圧が大きい場合でも安定に動作可能であり、かつ低消費電力で動作するレベルコンバータ回路を提供することにある。

【課題を解決するための手段】

【0014】

本発明に係るレベルコンバータ回路は、第1の信号レベルを有するデジタル信号である入力信号を、上記第1の信号レベルよりも高い第2の信号レベルを有する出力信号に変換するレベルコンバータ回路において、

上記入力信号を增幅して上記出力信号に出力する增幅回路と、

上記入力信号の信号レベルが変化するとき上記增幅回路に流れる動作電流に対応する制御電流を生成する電流生成回路と、

上記電流生成回路によって生成された制御電流を検出して、上記增幅回路の動作電流が上記検出した制御電流に対応するように制御する電流検出回路とを備え、

上記電流生成回路は、上記電流検出回路と接地との間に挿入されかつ直列に接続された第1及び第2のnMOSトランジスタを備え、

上記第1のnMOSトランジスタは上記入力信号に応答して動作しかつ上記第2のnMOSトランジスタは上記入力信号の反転信号に応答して動作するように構成されたことを特徴とする。

【0015】

また、上記レベルコンバータ回路は、上記第1及び第2のnMOSトランジスタのしきい値電圧を上記レベルコンバータ回路に比較して低下させて、上記制御電流を上記レベル

10

20

30

40

50

コンバータ回路に比較して増加させるように、上記第1及び第2のnMOSトランジスタの基板電位を変化させる制御回路をさらに備えたことを特徴とする。

【 0 0 1 6 】

さらに、上記レベルコンバータ回路は、上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第1及び第2のnMOSトランジスタに対してそれぞれ並列に、別のnMOSトランジスタを接続したことを特徴とする。

【 0 0 1 7 】

またさらに、上記レベルコンバータ回路において、上記電流生成回路はさらに、

上記入力信号の信号レベルが変化しないときであって上記入力信号がハイレベルでありかつ上記出力信号がローレベルであるときに、上記出力信号がハイレベルとなるように補正するための上記制御電流を生成する立ち上がり電流生成回路と、

上記入力信号の信号レベルが変化しないときであって上記入力信号がローレベルでありかつ上記出力信号がハイレベルであるときに、上記出力信号がローレベルとなるように補正するための上記制御電流を生成する立ち下がり電流生成回路と

のうちの少なくとも1つを備えたことを特徴とする。

【 0 0 1 8 】

また、上記レベルコンバータ回路において、上記立ち上がり電流生成回路は、

電圧源と接地との間に挿入されかつ所定のノードを介して直列に接続された、p M O S トランジスタ及び第3のn M O S トランジスタと、

上記電流検出回路と接地との間に挿入されかつ直列に接続された第4及び第5のnMOSトランジスタとを備え、

上記 p M O S トランジスタは上記出力信号に応答して動作し、上記第 3 の n M O S トランジスタは上記入力信号に応答して動作し、上記第 4 の n M O S トランジスタは上記入力信号に応答して動作し、かつ上記第 5 の n M O S トランジスタは上記ノードの信号レベルに応答して動作するように構成されたことを特徴とする。

〔 0 0 1 9 〕

さらに、上記レベルコンバータ回路において、上記立ち下がり電流生成回路は、

上記電流検出回路と接地との間に挿入されかつ直列に接続された第 6 及び第 7 の n M O S トランジスタとを備え、

上記第6のnMOSトランジスタは上記入力信号の反転信号に応答して動作し、かつ上記第7のnMOSトランジスタは上記出力信号に応答して動作するように構成されたことを特徴とする。

〔 0 0 2 0 〕

またさらに、上記レベルコンバータ回路において、上記增幅回路は、差動增幅回路と、ソース接地増幅回路とを備えたことを特徴とする。

【 0 0 2 1 】

ここで、上記レベルコンバータ回路において、上記ソース接地增幅回路は、プッシュプル型ソース接地增幅回路であることを特徴とする。

## 【発明の効果】

【 0 0 2 2 】

本発明に係るレベルコンバータ回路によれば、電流生成回路によって生成される電流に応する電流を增幅回路に印加して、信号レベルを変換するので、第1の信号レベルと第2の信号レベルとの間の差が大きい場合でも、レベルコンバータ回路は安定に動作する。また、電流生成回路は、入力信号の信号レベルが変化するときのみ制御電流を生成し、入力信号の信号レベルが変化しないときは制御電流を生成しないので、レベルコンバータ回路は低消費電力で動作する。

[ 0 0 2 3 ]

Sトランジスタの基板電位を変化させる制御回路をさらに備えるので、レベルコンバータ回路が上記レベルコンバータ回路に比較して高速に動作する。

【0024】

またさらに、本発明に係るレベルコンバータ回路によれば、上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第1及び第2のnMOSトランジスタに対してそれぞれ並列に、別のnMOSトランジスタを接続するので、レベルコンバータ回路が上記レベルコンバータ回路に比較して高速に動作する。

【0025】

またさらに、本発明に係るレベルコンバータ回路によれば、入力信号と入力信号の反転信号とがともにハイレベルである期間が存在しない場合にも、立ち上がり電流生成回路又は立ち下がり電流生成回路が制御電流を生成するので、レベルコンバータ回路は正常に動作する。さらに、外部ノイズ等の外乱により出力信号の信号レベルが変化する場合にも、立ち上がり電流生成回路又は立ち下がり電流生成回路が制御電流を生成するので、レベルコンバータ回路は正常に動作する。

【図面の簡単な説明】

【0026】

【図1】従来技術に係るレベルコンバータ回路100の応用例を示すブロック図である。

【図2】従来技術に係るクロスカップル型レベルコンバータ回路100の構成を示す回路図である。

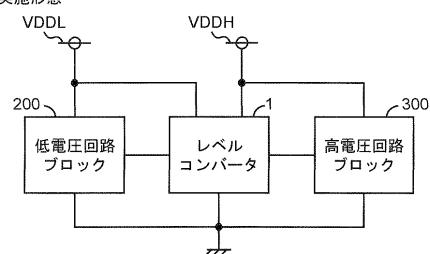

【図3A】本発明の第1の実施形態に係るレベルコンバータ回路1の応用例を示すブロック図である。

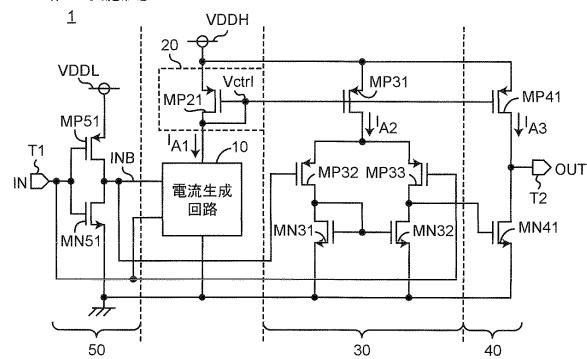

【図3B】本発明の第1の実施形態に係るレベルコンバータ回路1の構成を示すブロック図である。

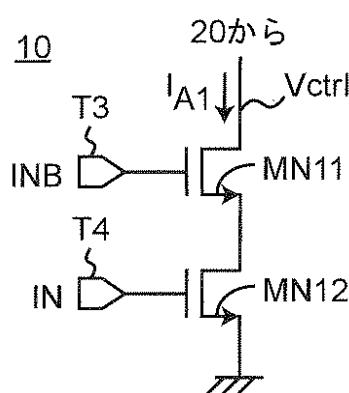

【図4】図3Bの電流生成回路10の構成を示すブロック図である。

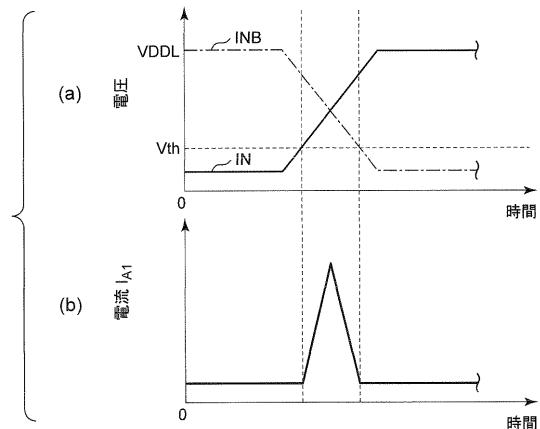

【図5】図4の電流生成回路10に入力される入力信号IN及び入力信号INBの電圧と、電流生成回路10によって生成される電流IA1との間のタイミングを示すタイミング図であり、(a)は入力信号IN及び入力信号INBの電圧を示し、(b)は電流IA1を示す。

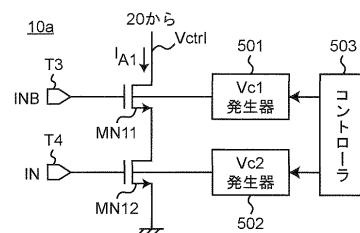

【図6】図4の電流生成回路10の第1の変形例である電流生成回路10aの構成を示す回路図である。

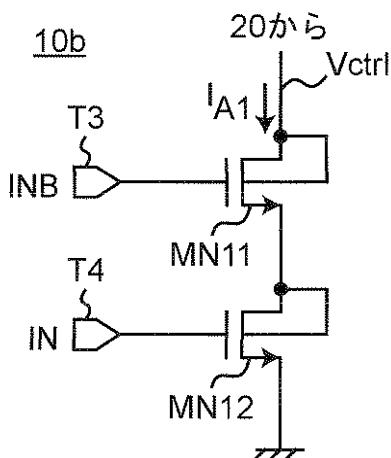

【図7】図4の電流生成回路10の第2の変形例である電流生成回路10bの構成を示す回路図である。

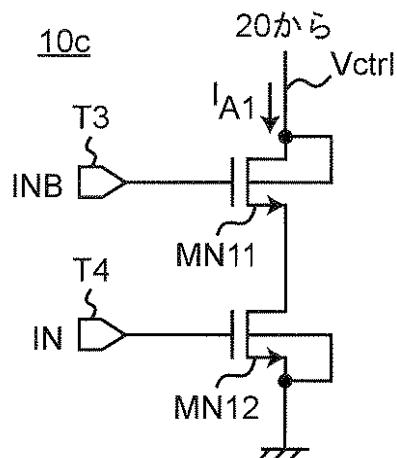

【図8】図4の電流生成回路10の第3の変形例である電流生成回路10cの構成を示す回路図である。

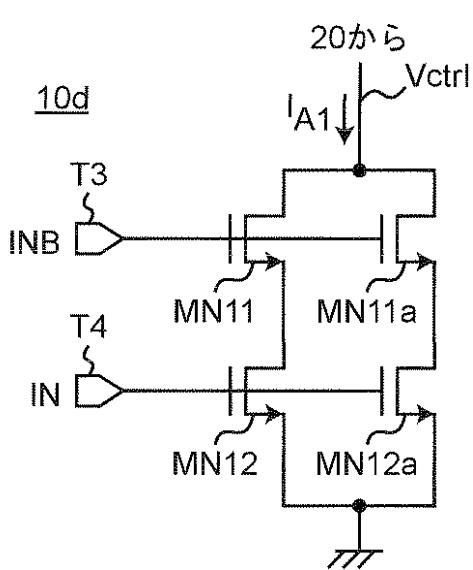

【図9】図4の電流生成回路10の第4の変形例である電流生成回路10dの構成を示す回路図である。

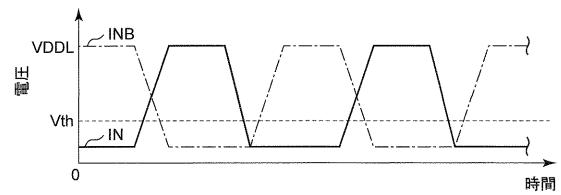

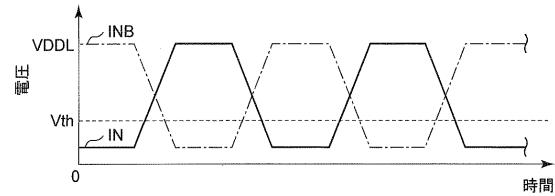

【図10A】図3Bのレベルコンバータ回路1への理想的な入力信号IN, INBの波形を示すグラフである。

【図10B】図3Bのレベルコンバータ回路1への非理想的な入力信号IN, INBの波形を示すグラフである。

【図11A】本発明の第2の実施形態に係るレベルコンバータ回路1Aの応用例を示すブロック図である。

【図11B】本発明の第2の実施形態に係るレベルコンバータ回路1Aの構成を示すブロック図である。

【図12】図11Bの電流生成回路10Aの構成を示す回路図である。

【図13A】本発明の第3の実施形態に係るレベルコンバータ回路1Bの応用例を示すブロック図である。

【図13B】本発明の第3の実施形態に係るレベルコンバータ回路1Bの構成を示すブロック図である。

【図14】図4の電流生成回路10によって生成されるピーク電流の低電源電圧VDDL

10

20

30

40

50

への依存性を示すグラフである。

【図15】図3Bの電流 $I_{A2}$ ,  $I_{A3}$ の周波数応答特性を示すグラフである。

【図16】(a)は図3Bのレベルコンバータ回路1への入力信号INの波形及び図3Bのレベルコンバータ回路1からの出力信号OUTの波形を示すグラフであり、(b)は図4の電流生成回路10によって生成される電流 $I_{A1}$ の波形を示すグラフである。

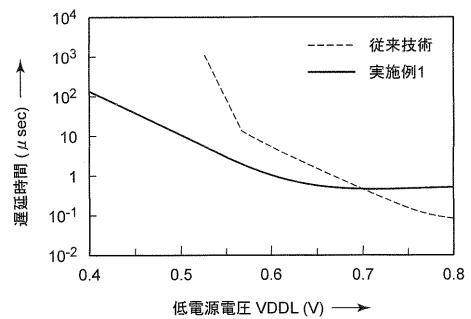

【図17】低電源電圧VDDLの電圧値に対する図3Bのレベルコンバータ回路1及び従来技術に係るレベルコンバータ回路100の遅延時間を示すグラフである。

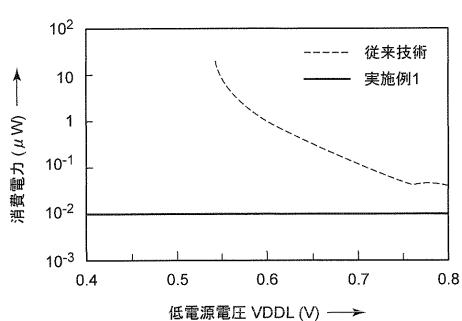

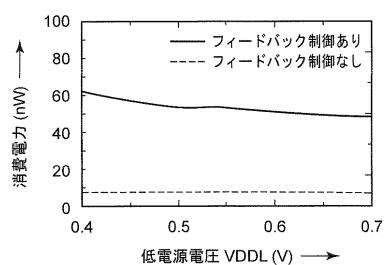

【図18】低電源電圧VDDLの電圧値に対する図3Bのレベルコンバータ回路1及び従来技術に係るレベルコンバータ回路100の消費電力を示すグラフである。

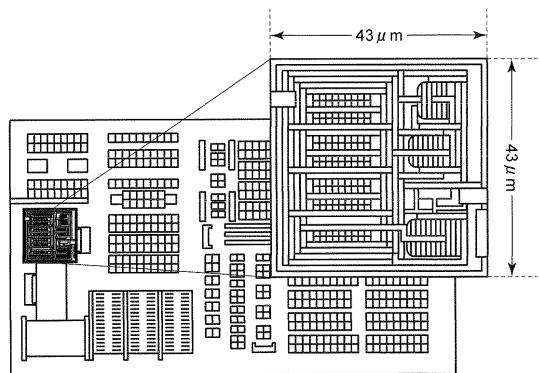

【図19】図3Bのレベルコンバータ回路1についての試作チップの写真である。

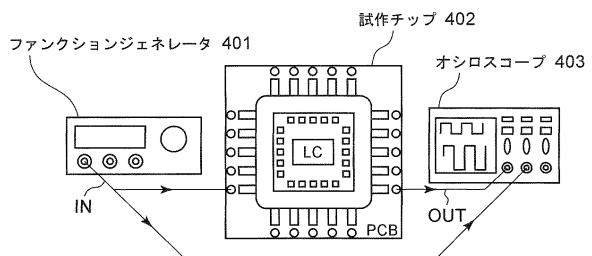

【図20】図19の試作チップの動作を測定するための測定環境を示すブロック図である。

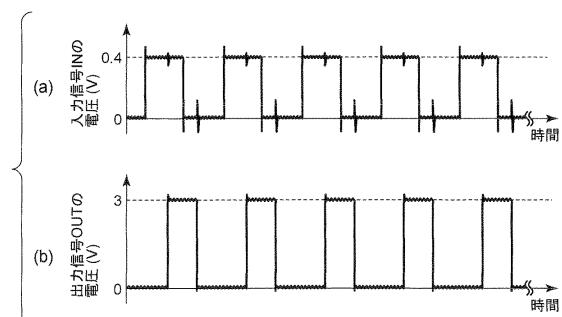

【図21】(a)は図20の測定環境において、試作チップ402への入力信号INの波形を示すグラフであり、(b)は図20の測定環境において、試作チップからの出力信号OUTの波形を示すグラフである。

【図22】図19の試作チップのシム(Simoo)プロットを示す図である。

【図23】低電源電圧VDDLの電圧値に対する図19の試作チップの消費電力を示すグラフである。

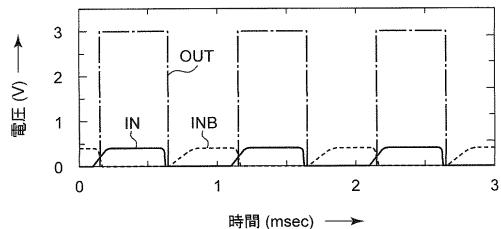

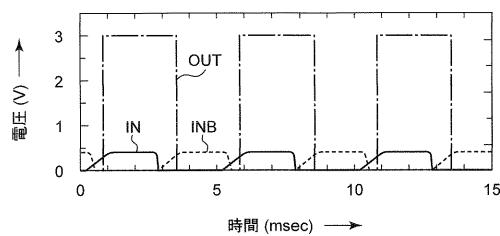

【図24】図11Bのレベルコンバータ回路1Aへの入力信号IN, INBの波形及び図11Bのレベルコンバータ回路1Aからの出力信号OUTの波形を示すグラフである。

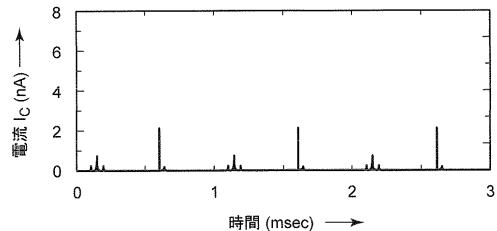

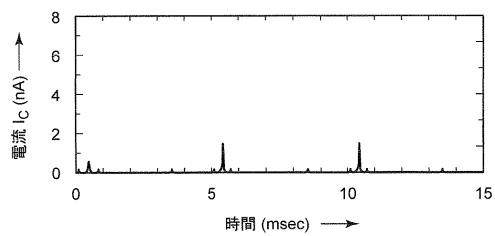

【図25】図12の変化時電流生成回路11によって生成される電流 $I_c$ の波形を示すグラフである。

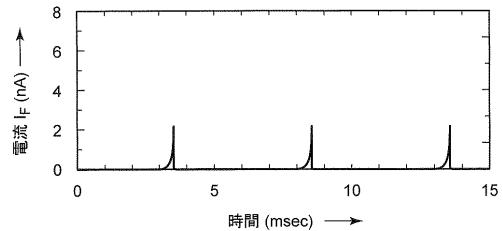

【図26】図12の立ち下がり電流生成回路13によって生成される電流 $I_F$ の波形を示すグラフである。

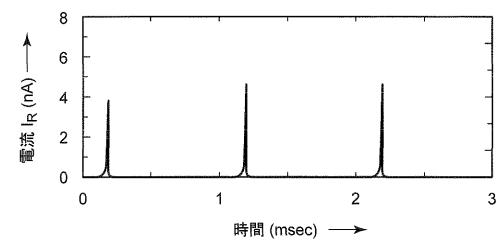

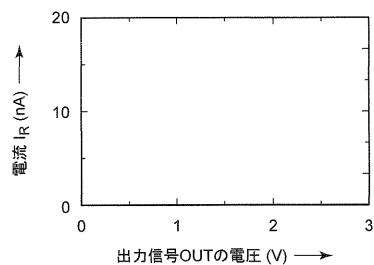

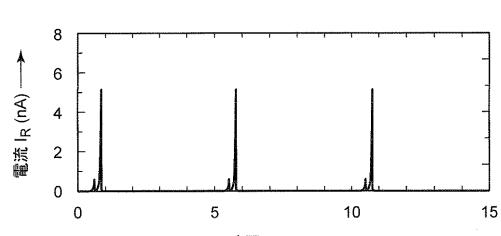

【図27】図12の立ち上がり電流生成回路12によって生成される電流 $I_R$ の波形を示すグラフである。

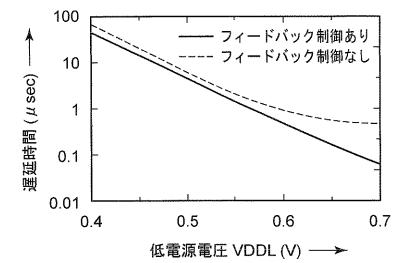

【図28】低電源電圧VDDLの電圧値に対する図11Bのレベルコンバータ回路1A及び図3Bのレベルコンバータ回路1の遅延時間を示すグラフである。

【図29】低電源電圧VDDLの電圧値に対する図11Bのレベルコンバータ回路1A及び図3Bのレベルコンバータ回路1の消費電力を示すグラフである。

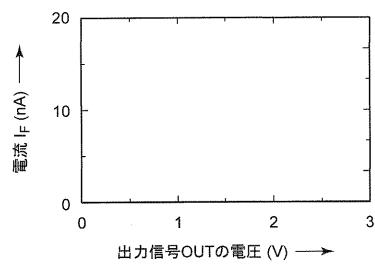

【図30A】図12の電流生成回路10Aにおいて、入力信号INを第1のハイレベルに固定し、入力信号INBをローレベルに固定し、出力信号OUTを0Vから3Vに変化させた場合に生成される電流 $I_F$ を示すグラフである。

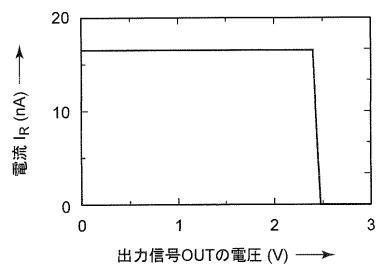

【図30B】図12の電流生成回路10Aにおいて、入力信号INを第1のハイレベルに固定し、入力信号INBをローレベルに固定し、出力信号OUTを0Vから3Vに変化させた場合に生成される電流 $I_R$ を示すグラフである。

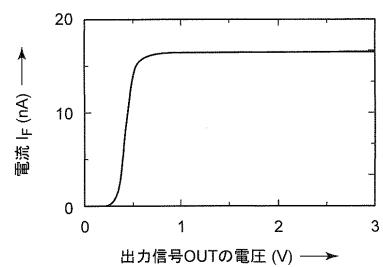

【図31A】図12の電流生成回路10Aにおいて、入力信号INをローレベルに固定し、入力信号INBを第1のハイレベルに固定し、出力信号OUTを0Vから3Vに変化させた場合に生成される電流 $I_F$ を示すグラフである。

【図31B】図12の電流生成回路10Aにおいて、入力信号INをローレベルに固定し、入力信号INBを第1のハイレベルに固定し、出力信号OUTを0Vから3Vに変化させた場合に生成される電流 $I_R$ を示すグラフである。

【図32】図13Bのレベルコンバータ回路1Bへの入力信号IN, INBの波形及び図13Bのレベルコンバータ回路1Bからの出力信号OUTの波形を示すグラフである。

【図33】図12の変化時電流生成回路11によって生成される電流 $I_c$ の波形を示すグラフである。

【図34】図12の立ち下がり電流生成回路13によって生成される電流 $I_F$ の波形を示すグラフである。

【図35】図12の立ち上がり電流生成回路12によって生成される電流 $I_R$ の波形を示すグラフである。

10

20

30

40

50

## 【発明を実施するための形態】

## 【0027】

## 第1の実施形態。

図3Aは、本発明の第1の実施形態に係るレベルコンバータ回路1の応用例を示すプロック図である。図3Aにおいて、レベルコンバータ回路1は、低電源電圧VDDL(例えば0.4Vである。)が供給される低電圧回路ブロック200からの信号の信号レベルを変換して、高電源電圧VDDH(例えば3Vである。)が供給される高電圧回路ブロック300に出力する。低電圧回路ブロック200からレベルコンバータ回路1に入力される入力信号INは、ハイレベル又はローレベルを有する2値信号であり、ハイレベルの電位は低電源電圧VDDLであり、ローレベルの電位は接地電位である。また、レベルコンバータ回路1によって高電圧回路ブロック300に出力される出力信号OUTは、ハイレベル又はローレベルを有する2値信号であり、ハイレベルの電位は高電源電圧VDDHであり、ローレベルの電位は接地電位である。以下、低電源電圧VDDLの電圧レベルを第1のハイレベルといい、高電源電圧VDDHの電圧レベルを第2のハイレベルという。また、低電源電圧VDDLを有する電圧源を低電圧源といい、高電源電圧VDDHを有する電圧源を高電圧源という。

## 【0028】

図3Bは、本発明の第1の実施形態に係るレベルコンバータ回路1の構成を示すプロック図である。図3Bにおいて、レベルコンバータ回路1は、電流生成回路10と、電流検出回路20と、差動增幅回路30と、ソース接地增幅回路40と、前処理回路50と、端子T1, T2とを備えて構成される。

## 【0029】

第1の実施形態に係るレベルコンバータ回路1は、第1のハイレベルを有するデジタル信号である入力信号INを、第1のハイレベルよりも高い第2のハイレベルを有する出力信号OUTに変換するレベルコンバータ回路1において、

入力信号INを増幅して出力信号OUTに出力する差動增幅回路30及びソース接地增幅回路40と、

入力信号INの電圧が変化するとき差動增幅回路30及びソース接地增幅回路40のそれぞれに流れる動作電流IA2, IA3に対応する制御電流IA1を生成する電流生成回路10と、

電流生成回路10によって生成された制御電流IA1を検出して、差動增幅回路30及びソース接地增幅回路40のそれぞれの動作電流IA2, IA3が制御電流IA1に対応するように制御する電流検出回路20とを備え、

電流生成回路10は、電流検出回路20と接地との間に挿入されかつ直列に接続されたnMOSトランジスタMN11, MN12を備え、

nMOSトランジスタMN11は入力信号INに応答して動作しつかtnMOSトランジスタMN12は入力信号INの反転信号INBに応答して動作するように構成されたことを特徴とする。

## 【0030】

前処理回路50は、pMOSトランジスタMP51と、nMOSトランジスタMN51とを備えて構成される。pMOSトランジスタMP51のソースは、低電圧源に接続される。pMOSトランジスタMP51のゲート及びnMOSトランジスタMN51のゲートは、端子T1に接続され、低電圧回路ブロック200からの入力信号INは当該ゲートに入力される。pMOSトランジスタMP51のドレインは、nMOSトランジスタMN51のドレインに接続される。nMOSトランジスタMN51のソースは接地される。pMOSトランジスタMP51とnMOSトランジスタMN51とは、直列に接続されてインバータを構成しており、当該インバータは入力信号INを反転した信号INB(以下、入力信号INBともいう。)を電流生成回路10及び差動增幅回路30に出力する。

## 【0031】

電流生成回路10は、詳細後述するように、電流検出回路20、前処理回路50、及び

端子 T 1 に接続され、その回路の接地部は接地される。

【 0 0 3 2 】

電流検出回路 2 0 は、p MOS トランジスタ MP 2 1 を備えて構成される。p MOS トランジスタ MP 2 1 のソースは、高電圧源に接続され、p MOS トランジスタ MP 2 1 のゲートは、p MOS トランジスタ MP 3 1 のゲート及び p MOS トランジスタ MP 4 1 のゲートに接続されるとともに、p MOS トランジスタ MP 2 1 のドレインに接続される。p MOS トランジスタ MP 2 1 のドレインは、電流生成回路 1 0 に接続される。p MOS トランジスタ MP 2 1 , MP 3 1 , MP 4 1 は、カレントミラー回路を構成する。

【 0 0 3 3 】

差動増幅回路 3 0 は、p MOS トランジスタ MP 3 1 , MP 3 2 , MP 3 3 と、n MOS トランジスタ MN 3 1 , MN 3 2 を備えて構成される。p MOS トランジスタ MP 3 1 のソースは、高電圧源に接続され、p MOS トランジスタ MP 3 1 のドレインは、p MOS トランジスタ MP 3 2 のソース及び p MOS トランジスタ MP 3 3 のソースに接続される。p MOS トランジスタ MP 3 2 のゲートは、前処理回路 5 0 に接続され、入力信号 IN B は当該ゲートに入力される。p MOS トランジスタ MP 3 2 のドレインは、n MOS トランジスタ MN 3 1 のドレインに接続される。p MOS トランジスタ MP 3 3 のゲートは、端子 T 1 に接続され、入力信号 IN は当該ゲートに入力される。p MOS トランジスタ MP 3 3 のドレインは、n MOS トランジスタ MN 3 2 のドレインに接続される。n MOS トランジスタ MN 3 1 のゲートは、n MOS トランジスタ MN 3 1 のドレイン及び n MOS トランジスタ MN 3 2 のゲートに接続される。n MOS トランジスタ MN 3 1 のソース及び n MOS トランジスタ MN 3 2 のソースは接地される。

【 0 0 3 4 】

ソース接地増幅回路 4 0 は、p MOS トランジスタ MP 4 1 と、n MOS トランジスタ MN 4 1 を備えて構成される。p MOS トランジスタ MP 4 1 のソースは、高電圧源に接続され、p MOS トランジスタ MP 4 1 のドレインは、n MOS トランジスタ MN 4 1 のドレインに接続される。n MOS トランジスタ MN 4 1 のゲートは、p MOS トランジスタ MP 3 3 のドレインと n MOS トランジスタ MN 3 2 のドレインとの接続点に接続され、n MOS トランジスタ MN 4 1 のソースは接地される。p MOS トランジスタ MP 4 1 のドレインと n MOS トランジスタ MN 4 1 のドレインとの接続点は、端子 T 2 に接続される。ここで、差動増幅回路 3 0 とソース接地増幅回路 4 0 とは、2 段増幅回路を構成する。

【 0 0 3 5 】

レベルコンバータ回路 1 では、入力信号 IN が p MOS トランジスタ MP 3 3 のゲートに入力され、入力信号 IN B が p MOS トランジスタ MP 3 2 のゲートに入力される。レベルコンバータ回路 1 の特徴は、入力信号 IN 及び入力信号 IN B を利用した電流生成回路 1 0 にある。電流生成回路 1 0 は、入力信号 IN の信号レベルが変化する期間のみ電流  $I_{A1}$  ( 制御電流  $I_{A1}$  ともいう。 ) を生成する。電流検出回路 2 0 は、電流  $I_{A1}$  を検出して制御電圧  $V_{ctr1}$  を発生し、差動増幅回路 3 0 に流れる電流  $I_{A2}$  ( 動作電流  $I_{A2}$  ともいう。 ) 及びソース接地増幅回路 4 0 に流れる電流  $I_{A3}$  ( 動作電流  $I_{A3}$  ともいう。 ) が、電流  $I_{A1}$  に対応するようにカレントミラー回路を介して制御する。差動増幅回路 3 0 及びソース接地増幅回路 4 0 は、それぞれ対応する電流  $I_{A2}$  ,  $I_{A3}$  が供給されると、小振幅の入力信号 IN を大振幅の出力信号 OUT に増幅して出力することによりレベル変換を実行する。以下、レベルコンバータ回路 1 の動作を詳細に説明する。

【 0 0 3 6 】

レベルコンバータ回路 1 は、差動増幅回路 3 0 及びソース接地増幅回路 4 0 を備えて構成される 2 段増幅回路と、電流生成回路 1 0 と、電流検出回路 2 0 と、前処理回路 5 0 とを備えて構成される。電流生成回路 1 0 によって生成される電流  $I_{A1}$  に対応する電流  $I_{A2}$  及び  $I_{A3}$  がそれぞれ差動増幅回路 3 0 及びソース接地増幅回路 4 0 に供給される場合を考える。入力信号 IN の電圧が入力信号 IN B の電圧よりも高い場合、出力信号 OUT は第 2 のハイレベルとなる。一方、入力信号 IN の電圧が入力信号 IN B の電圧よりも

低い場合、出力信号 OUT はローレベルとなる。入力信号 IN と入力信号 INB とは、第 1 のハイレベル又はローレベルの相補関係であることから、入力信号 IN がローレベルから第 1 のハイレベルになったとき、入力信号 INB は第 1 のハイレベルからローレベルとなり、出力信号 OUT はローレベルから第 2 のハイレベルまで上昇する。

【 0 0 3 7 】

ここで、端子 T 2 に対する充放電電流に注目する。出力信号 OUT の論理（信号レベル）は、p MOS トランジスタ MP 4 1 及び n MOS トランジスタ MN 4 1 を流れる充放電電流によって端子 T 2 が充放電されることによって決定される。充放電を担う p MOS トランジスタ MP 4 1 及び n MOS トランジスタ MN 4 1 のゲート電圧は、電流生成回路 1 0 によって生成される電流  $I_{A1}$  によって決定されるため、p MOS トランジスタ MP 4 1 及び n MOS トランジスタ MN 4 1 に流れる電流量のバランスを緻密に調整する必要がない。すなわち、レベルコンバータ回路 1 は、図 2 に示す従来技術に係るレベルコンバータ回路 1 0 0 と比較して、高電源電圧 VDDH と低電源電圧 VDDL との間の電圧差、プロセスバラツキ、及び温度変化に対して耐性を有する。

【 0 0 3 8 】

差動增幅回路 3 0 及びソース接地增幅回路 4 0 は通常、基準電流源回路から生成される電流を利用して動作する。しかしながら、定常的に電流が流れることは消費電力を増大させるので好ましくない。一般に、レベルコンバータ回路 1 は、入力信号 IN の電圧が変化するときのみ高速に動作することが求められる。すなわち、入力信号 IN の電圧が変化するときのみ差動增幅回路 3 0 及びソース接地增幅回路 4 0 に流れる電流を生成し、入力信号 IN の電圧が変化しないときには電流を生成しないようにすることで、レベルコンバータ回路 1 0 の低消費電力化を実現することができる。このための電流生成回路 1 0 を考えた。

【 0 0 3 9 】

図 4 は、図 3 B の電流生成回路 1 0 の構成を示すブロック図である。電流生成回路 1 0 は、n MOS トランジスタ MN 1 1, MN 1 2 を備えて構成される。n MOS トランジスタ MN 1 1 のドレインは、電流検出回路 2 0 に接続され、n MOS トランジスタ MN 1 1 のゲートは、端子 T 3 に接続される。端子 T 3 には、前処理回路 5 0 から入力信号 INB が入力される。n MOS トランジスタ MN 1 1 のソースは、n MOS トランジスタ MN 1 2 のドレインに接続される。n MOS トランジスタ MN 1 2 のゲートは、端子 T 4 に接続される。端子 T 4 は、端子 T 1 に接続され、入力信号 IN が端子 T 4 に入力される。n MOS トランジスタ MN 1 2 のソースは接地される。なお、電流生成回路 1 0 は、入力信号 IN が端子 T 3 に入力され、かつ入力信号 INB が端子 T 4 に入力されるように構成されてもよい。

【 0 0 4 0 】

図 4 において、電流生成回路 1 0 では、2 つの n MOS トランジスタ MN 1 1, MN 1 2 を縦続接続し、n MOS トランジスタ MN 1 1 のゲートに入力信号 INB を印加し、n MOS トランジスタ MN 1 2 のゲートに入力信号 IN を印加する。このとき、入力信号 INB, IN の信号レベルは、有限の遅延時間で変化するため、入力信号 INB, IN がともに有限の電圧を有する期間が存在する。この期間において、n MOS トランジスタ MN 1 1 は入力信号 INB に応答して動作し、n MOS トランジスタ MN 1 2 は入力信号 IN に応答して動作して、電流  $I_{A1}$  を生成する。

【 0 0 4 1 】

図 5 は、図 4 の電流生成回路 1 0 に入力される入力信号 IN 及び入力信号 INB の電圧と、電流生成回路 1 0 によって生成される電流  $I_{A1}$  との間のタイミングを示すタイミング図であり、図 5 ( a ) は入力信号 IN 及び入力信号 INB の電圧を示し、図 5 ( b ) は電流  $I_{A1}$  を示す。入力信号 IN の電圧が変化すると、前処理回路 5 0 を介して入力信号 INB の電圧が反転する。このとき、入力信号 IN, INB の信号レベルが変化する期間には、入力信号 IN, INB の電圧がともに、しきい値電圧 Vth を超える期間が存在し、当該期間において n MOS トランジスタ MN 1 1, MN 1 2 がオン状態となり、入力信

10

20

30

40

50

号のいずれか一方がローレベルになるまで電流  $I_{A_1}$  が生成される。この電流  $I_{A_1}$  に対応する電流  $I_{A_2}$ ,  $I_{A_3}$  が差動増幅回路 30 及びソース接地増幅回路 40 に印加されて、レベル変換動作が実行される。入力信号 IN の電圧が変化しないとき、レベルコンバータ回路 1 は、nMOS ランジスタ MN11, MN12 を流れるリーク電流のみで動作する。したがって、この電流生成回路 10 を利用することで、レベルコンバータ回路 1 は、低消費電力で信号レベル変換動作を実現することができる。

#### 【0042】

入力信号 IN が変化してから出力信号 OUT が変化するまでの遅延時間は、電流生成回路 10 によって生成される電流  $I_{A_1}$  に依存する。したがって、縦続接続した 2 つの nMOS ランジスタ MN11, MN12 のランジスタサイズ若しくはしきい値電圧を調整する、又は差動増幅回路 30 及びソース接地増幅回路 40 のカレントミラー比を調整することで、上記遅延時間を制御することができる。

10

#### 【0043】

以上説明したように、第 1 の実施形態によれば、電流生成回路 10 によって生成される電流  $I_{A_1}$  に対応する電流  $I_{A_2}$ ,  $I_{A_3}$  をそれぞれ差動増幅回路 30 及びソース接地増幅回路 40 に印加して、信号レベルを変換するので、低電源電圧 VDDL と高電源電圧 VDDH との間の差電圧が大きい場合でも、レベルコンバータ回路 1 は安定に動作する。また、電流生成回路 10 は、入力信号 IN の電圧が変化するときのみ電流  $I_{A_1}$  を生成し、入力信号 IN の電圧が変化しないときは電流  $I_{A_1}$  を生成しないので、レベルコンバータ回路 1 は低消費電力で動作する。

20

#### 【0044】

図 6 は、図 4 の電流生成回路 10 の第 1 の変形例である電流生成回路 10a の構成を示す回路図である。図 6 の電流生成回路 10a は、図 4 の電流生成回路 10 と比較して、電圧  $V_{c1}$  を発生する  $V_{c1}$  発生器（電圧発生器）501 と、電圧  $V_{c2}$  を発生する  $V_{c2}$  発生器（電圧発生器）502 と、コントローラ 503 とをさらに備える点が異なる。nMOS ランジスタ MN11 の基板電位（ウェル電位）は、 $V_{c1}$  発生器 501 によって発生される電圧  $V_{c1}$  に設定され、nMOS ランジスタ MN12 の基板電位は、 $V_{c2}$  発生器 502 によって発生される電圧  $V_{c2}$  に設定される。コントローラ 503 は、nMOS ランジスタ MN11, MN12 のしきい値電圧がそれぞれ電流生成回路 10 における nMOS ランジスタ MN11, MN12 のしきい値電圧よりも低下するように、 $V_{c1}$  発生器 501 及び  $V_{c2}$  発生器 502 によって発生される電圧  $V_{c1}$ ,  $V_{c2}$  を制御する。これにより、電流生成回路 10a によって生成される電流  $I_{A_1}$  が電流生成回路 10 によって生成される電流  $I_{A_1}$  よりも増加し、レベルコンバータ回路 1 が高速に動作するようになる。

30

#### 【0045】

図 7 は、図 4 の電流生成回路 10 の第 2 の変形例である電流生成回路 10b の構成を示す回路図である。図 7 の電流生成回路 10b は、図 4 の電流生成回路 10 と比較して、nMOS ランジスタ MN11 の基板電位が、nMOS ランジスタ MN11 のドレインの電圧と同一の電圧に設定され、nMOS ランジスタ MN12 の基板電位が、nMOS ランジスタ MN12 のドレインの電圧と同一の電圧に設定されている点が異なる。これにより、nMOS ランジスタ MN11, MN12 のしきい値電圧がそれぞれ電流生成回路 10 における nMOS ランジスタ MN11, MN12 のしきい値電圧よりも低下して、電流生成回路 10b によって生成される電流  $I_{A_1}$  が電流生成回路 10 によって生成される電流  $I_{A_1}$  よりも増加し、レベルコンバータ回路 1 が高速に動作するようになる。

40

#### 【0046】

図 8 は、図 4 の電流生成回路 10 の第 3 の変形例である電流生成回路 10c の構成を示す回路図である。図 8 の電流生成回路 10c は、図 4 の電流生成回路 10 と比較して、nMOS ランジスタ MN11 の基板電位が、nMOS ランジスタ MN11 のドレインの電圧と同一の電圧に設定され、nMOS ランジスタ MN12 の基板電位が、nMOS ランジスタ MN12 のソースの電圧と同一の電圧に設定されている点が異なる。これによ

50

り、nMOSトランジスタMN1\_1のしきい値電圧がそれぞれ電流生成回路10におけるnMOSトランジスタMN1\_1のしきい値電圧よりも低下して、電流生成回路10cによって生成される電流 $I_{A_1}$ が電流生成回路10によって生成される電流 $I_{A_1}$ よりも増加し、レベルコンバータ回路1が高速に動作するようになる。

#### 【0047】

図9は、図4の電流生成回路10の第4の変形例である電流生成回路10dの構成を示す回路図である。図9の電流生成回路10dは、図4の電流生成回路10と比較して、nMOSトランジスタMN1\_1a, MN1\_2aをさらに備える点が異なる。nMOSトランジスタMN1\_1aのドレインは、電流検出回路20に接続され、nMOSトランジスタMN1\_1aのゲートは、端子T3に接続され、入力信号INBは当該ゲートに入力される。nMOSトランジスタMN1\_1aのソースは、nMOSトランジスタMN1\_2aのドレインに接続される。nMOSトランジスタMN1\_2aのゲートは、端子T4に接続され、入力信号INは当該ゲートに入力される。nMOSトランジスタMN1\_2aのソースは接地される。

#### 【0048】

図9において、nMOSトランジスタMN1\_1a, MN1\_2aは、図4のnMOSトランジスタMN1\_1, MN1\_2と同様に接続されるように構成される。これによって、電流生成回路10dにおいて電流が流れる経路が、電流生成回路10において電流が流れる経路よりも増加するので、電流生成回路10dによって生成される電流 $I_{A_1}$ が電流生成回路10によって生成される電流 $I_{A_1}$ よりも増加し、レベルコンバータ回路1が高速に動作するようになる。

#### 【0049】

なお、電流生成回路10のnMOSトランジスタMN1\_1, MN1\_2に対して、ゲート幅を大きくする、トランジスタのサイズを大きくする、又はチャネル幅を大きくしてもよく、これによって、電流生成回路10によって生成される電流 $I_{A_1}$ が増加し、レベルコンバータ回路1が高速に動作するようになる。

#### 【0050】

第2の実施形態。

レベルコンバータ回路1の動作は、入力信号INの波形に強く依存する課題がある。また、レベルコンバータ回路1は、回路動作の特性上、ノイズ耐性に課題がある。すなわち、次の2つの課題がある。

課題A：入力信号INの波形と入力信号INBの波形との間に電圧の重なり、すなわち入力信号IN及び入力信号INBがともに第1のハイレベルである期間がない場合、電流生成回路10が電流 $I_{A_1}$ を生成しない。

課題B：出力信号OUTの論理確定後、電流生成回路10は動作せず、レベルコンバータ回路1はリーク電流で動作する。このため、レベルコンバータ回路1はノイズ等の外乱に弱い可能性がある。

以下では、課題A及び課題Bのそれぞれについて説明する。

#### 【0051】

まず、課題Aについて説明する。図10Aは、図3Bのレベルコンバータ回路1への理想的な入力信号IN, INBの波形を示すグラフであり、図10Bは、図3Bのレベルコンバータ回路1への非理想的な入力信号IN, INBの波形を示すグラフである。レベルコンバータ回路1は、入力信号INと入力信号INBとの論理が重なった電圧領域を、縦続接続したnMOSトランジスタMN1\_1, MN1\_2で検出し、電流 $I_{A_1}$ を生成して動作する。図10Aより明らかなように、理想的な入力信号IN, INBの波形の場合には、入力信号IN及び入力信号INBの論理が変化する期間において、入力信号IN, INBがともに有限の電圧を有する期間、すなわちともに第1のハイレベルである期間が存在する。nMOSトランジスタMN1\_1, MN1\_2がこの期間の間オン状態となりし、レベルコンバータ回路1を動作させるための電流 $I_{A_1}$ を生成する。一方、図10Bに示す非理想的な入力信号IN, INBの波形の場合は、入力信号INの立ち上がりでは入力信号

10

20

30

40

50

I N と入力信号 I N B との波形が重なるが、入力信号 I N の立ち下がりでは入力信号 I N と入力信号 I N B との波形は重ならない。これは、入力信号 I N の立ち下がりにおいて、電流生成回路 1 0 が十分な電流  $I_{A1}$  を生成できないことを意味しており、レベルコンバータ回路 1 が安定に動作することを保証することができない課題がある。

【 0 0 5 2 】

次に、課題 B について説明する。レベルコンバータ回路 1 では、出力信号 O U T の論理が切り替わるときのみ電流生成回路 1 0 が動作して、電流  $I_{A1}$  を生成する。この電流  $I_{A1}$  に対応する電流  $I_{A2}$ ,  $I_{A3}$  によって差動増幅回路 3 0 及びソース接地増幅回路 4 0 が動作し、レベル変換動作を実現する。しかし、出力信号 O U T の論理が切り替わった後を考えると、端子 T 2 はフローティング状態となり、ノイズ等の外乱の影響を受けやすい課題がある。すなわち、レベルコンバータ回路 1 が第 2 のハイレベルである出力信号 O U T を出力すべき期間において、ノイズなどの影響によって出力信号 O U T が第 2 のハイレベルから低下したとしても、これを補正することができない課題がある。また、レベルコンバータ回路 1 がローレベルである出力信号 O U T を出力すべき期間において、ノイズなどの影響によって出力信号 O U T がローレベルから上昇したとしても、これを補正することができない課題がある。

【 0 0 5 3 】

第 2 の実施形態に係るレベルコンバータ回路 1 A は、上記の課題 A, B を解決する。レベルコンバータ回路 1 A は、レベルコンバータ回路 1 を基本構造とし、これにフィードバック制御方式を導入することで上記の課題 A, B を解決する。

【 0 0 5 4 】

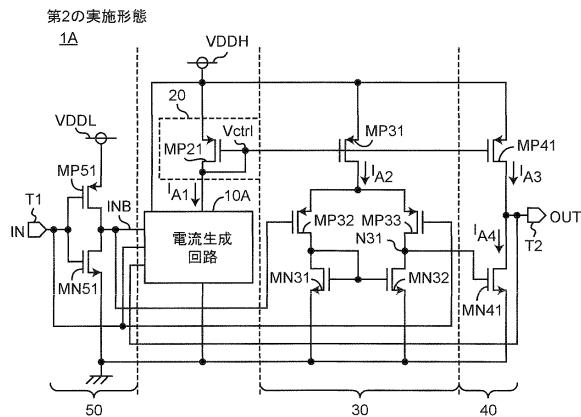

図 1 1 A は、本発明の第 2 の実施形態に係るレベルコンバータ回路 1 A の応用例を示すブロック図である。図 1 1 A において、レベルコンバータ回路 1 A は、低電源電圧 V D D L ( 例えは 0 . 4 V である。 ) が供給される低電圧回路ブロック 2 0 0 からの信号の信号レベルを変換して、高電源電圧 V D D H ( 例えは 3 V である。 ) が供給される高電圧回路ブロック 3 0 0 に出力する。以下、入力信号 I N , I N B 、第 1 のハイレベル、第 2 のハイレベル、低電圧源、及び高電圧源はそれぞれ、第 1 の実施形態で説明した入力信号 I N , I N B 、第 1 のハイレベル、第 2 のハイレベル、低電圧源、及び高電圧源と同様である。

【 0 0 5 5 】

図 1 1 B は、本発明の第 2 の実施形態に係るレベルコンバータ回路 1 A の構成を示すブロック図である。図 1 1 B において、レベルコンバータ回路 1 A は、第 1 の実施形態に係るレベルコンバータ回路 1 と比較して、電流生成回路 1 0 に代えて電流生成回路 1 0 A を備える点が異なり、その他の構成要素は、レベルコンバータ回路 1 と同様であり、その説明を省略する。図 1 1 B に示すように、電流生成回路 1 0 A には、出力信号 O U T が入力されて、フィードバック制御が実行される。

【 0 0 5 6 】

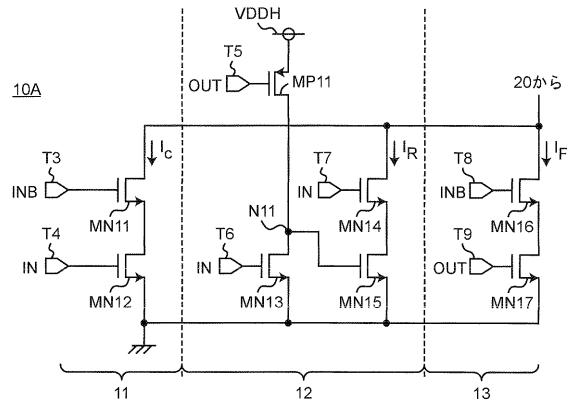

図 1 2 は、図 1 1 B の電流生成回路 1 0 A の構成を示す回路図である。電流生成回路 1 0 A は、変化時 ( C H A N G E ) 電流生成回路 1 1 と、立ち上がり ( R I S E ) 電流生成回路 1 2 と、立ち下がり ( F A L L ) 電流生成回路 1 3 とを備えて構成される。

【 0 0 5 7 】

変化時電流生成回路 1 1 は、図 4 の電流生成回路 1 0 と同様の構成であり、同様に動作する。立ち上がり電流生成回路 1 2 は、入力信号 I N の立ち上がり ( R I S E ) をモニタし、立ち下がり電流生成回路 1 3 は、入力信号 I N の立ち下がり ( F A L L ) をモニタする。ここで、変化時電流生成回路 1 1 によって生成される電流を電流  $I_c$  ( 制御電流  $I_c$  ともいう。 ) とし、立ち上がり電流生成回路 1 2 によって生成される電流を電流  $I_R$  ( 制御電流  $I_R$  ともいう。 ) とし、立ち下がり電流生成回路 1 3 によって生成される電流を電流  $I_F$  ( 制御電流  $I_F$  ともいう。 ) とする。以下、立ち上がり電流生成回路 1 2 、及び立ち下がり電流生成回路 1 3 について説明する。

【 0 0 5 8 】

10

20

30

40

50

立ち上がり電流生成回路 12 は、 pMOSトランジスタ MP11 と、 nMOSトランジスタ MN13, MN14, MN15 と、端子 T5, T6, T7 とを備えて構成される。 pMOSトランジスタ MP11 のソースは高電圧源に接続され、 pMOSトランジスタ MP11 のゲートは、端子 T5 に接続され、出力信号 OUT は当該ゲートに入力される。 pMOSトランジスタ MP11 のドレインは、 nMOSトランジスタ MN13 のゲートは、端子 T6 に接続され、入力信号 IN は当該ゲートに入力される。 nMOSトランジスタ MN13 のソースは接地される。また、 pMOSトランジスタ MP11 のドレインと nMOSトランジスタ MN13 のドレインとの接続点をノード N11 という。 nMOSトランジスタ MN14 のドレインは、電流検出回路 20 に接続され、 nMOSトランジスタ MN14 のゲートは、端子 T7 に接続され、入力信号 IN は当該ゲートに入力される。 nMOSトランジスタ MN14 のソースは、 nMOSトランジスタ MN15 のドレインに接続される。 nMOSトランジスタ MN15 のゲートはノード N11 に接続され、 nMOSトランジスタ MN15 のソースは接地される。ここで、端子 T5 は端子 T2 に接続されており、端子 T6 及び端子 T7 は端子 T1 に接続されている。10

#### 【0059】

立ち上がり電流生成回路 12 は、2段構成で実現される。1段目の回路では、 pMOSトランジスタ MP11 が出力信号 OUT をモニタし、 nMOSトランジスタ MN13 が入力信号 IN をモニタする。2段目の回路では、 nMOSトランジスタ MN14, MN15 を継続接続し、 nMOSトランジスタ MN15 は、ノード N11 の電圧をモニタし、 nMOSトランジスタ MN14 は、入力信号 IN をモニタする。この回路構成により、 pMOSトランジスタ MP11 は、出力信号 OUT に応答して動作し、 nMOSトランジスタ MN13, MN14 は入力信号 IN に応答して動作し、 nMOSトランジスタ MN15 は、ノード N11 の電圧に応答して動作する。また、立ち上がり電流生成回路 12 は、入力信号 IN が第1のハイレベルかつ出力信号 OUT がローレベルのときにのみ動作して、出力信号 OUT が第2のハイレベルとなるように補正するための電流  $I_R$  を生成する。20

#### 【0060】

入力信号 IN が第1のハイレベルであり、かつ出力信号 OUT が第2のハイレベルのとき、ノード N11 の電圧はローレベルとなる。このため、 nMOSトランジスタ MN15 はオフ状態となり、2段目の回路は電流  $I_R$  を生成しない。一方、入力信号 IN が第1のハイレベルであり、かつ出力信号 OUT がローレベルのとき、すなわち入力信号 IN と出力信号 OUT との論理が不一致のとき、ノード N11 の電圧はハイレベルとなって nMOSトランジスタ MN15 がオン状態となり、2段目の回路は電流  $I_R$  を生成する。電流  $I_R$  の電流量は、入力信号 IN の電圧、すなわち低電源電圧 VDDL によって規定される。30

#### 【0061】

立ち下がり電流生成回路 13 は、 nMOSトランジスタ MN16, MN17 と、端子 T8, T9 とを備えて構成される。 nMOSトランジスタ MN16 のドレインは、電流検出回路 20 に接続され、 nMOSトランジスタ MN16 のゲートは、端子 T8 に接続され、入力信号 INB は当該ゲートに入力される。 nMOSトランジスタ MN16 のソースは、 nMOSトランジスタ MN17 のドレインに接続される。 nMOSトランジスタ MN17 のゲートは、端子 T9 に接続され、出力信号 OUT は当該ゲートに入力される。 nMOSトランジスタ MN17 のソースは接地される。ここで、端子 T8 には前処理回路 50 から入力信号 INB が入力されており、端子 T9 は端子 T2 に接続されている。40

#### 【0062】

立ち下がり電流生成回路 13 は、1段構成で実現される。 nMOSトランジスタ MN16, MN17 が継続接続され、 nMOSトランジスタ MN17 は出力信号 OUT をモニタし、 nMOSトランジスタ MN16 は入力信号 INB をモニタする。この回路構成により、 nMOSトランジスタ MN16 は、入力信号 INB に応答して動作し、 nMOSトランジスタ MN17 は、出力信号 OUT に応答して動作する。また、立ち下がり電流生成回路 13 は入力信号 IN がローレベル（このとき、入力信号 INB は第1のハイレベルである50

。) かつ出力信号 OUT が第 2 のハイレベルのときにのみ動作して、出力信号 OUT がローレベルとなるように補正するための電流  $I_F$  を生成する。

【 0 0 6 3 】

入力信号 IN がローレベルであり、かつ出力信号 OUT がローレベルのとき、立ち下がり電流生成回路 13 は動作しない。入力信号 IN がローレベルであり、かつ出力信号 OUT が第 2 のハイレベルのとき、すなわち入力信号 IN と出力信号 OUT との論理が不一致のとき、立ち下がり電流生成回路 13 は電流  $I_F$  を生成する。電流  $I_F$  の電流量は、入力信号 INB の電圧、すなわち低電源電圧 VDDL によって規定される。

【 0 0 6 4 】

まず、入力信号 IN が第 1 のハイレベル（入力信号 INB がローレベル）の場合の電流生成回路 10A の動作について以下説明する。まず、出力信号 OUT が第 2 のハイレベルのときについて説明する。このとき、入力信号 IN と出力信号 OUT との論理は一致する。変化時電流生成回路 11 は、nMOS ランジスタ MN11 がオフ状態であるので、電流  $I_C$  を生成しない。また、立ち上がり電流生成回路 12 のノード N11 の電圧は、pMOS ランジスタ MP11 がオフ状態でありかつ nMOS ランジスタ MN13 がオン状態であるので、接地電圧まで低下する。nMOS ランジスタ MN15 は、ノード N11 の電圧に応答してオフ状態となる。したがって、立ち上がり電流生成回路 12 は、電流  $I_R$  を生成しない。さらに、立ち下がり電流生成回路 13 は、nMOS ランジスタ MN16 がオフ状態であるので、電流  $I_F$  を生成しない。したがって、入力信号 IN が第 1 のハイレベルであり、かつ出力信号 OUT が第 2 のハイレベルであるときは、電流生成回路 10A は電流を生成しない。

【 0 0 6 5 】

次に、出力信号 OUT がローレベルのときについて説明する。このとき、入力信号 IN と出力信号 OUT との論理は一致しない。変化時電流生成回路 11 は、nMOS ランジスタ MN11 がオフ状態であるので、電流  $I_C$  を生成しない。また、立ち上がり電流生成回路 12 において、pMOS ランジスタ MP11 がオン状態となり、ノード N11 の電圧は高電源電圧 VDDH まで上昇する。nMOS ランジスタ MN15 は、ノード N11 の電圧に応答してオン状態となり、これによって電流  $I_R$  が生成される。さらに、立ち下がり電流生成回路 13 は、nMOS ランジスタ MN16 がオフ状態であるので、電流  $I_F$  を生成しない。したがって、入力信号 IN が第 1 のハイレベルであり、かつ出力信号 OUT がローレベルであるときは、電流生成回路 10A は電流  $I_R$  を生成する。

【 0 0 6 6 】

次いで、入力信号 IN がローレベル（入力信号 INB が第 1 のハイレベル）の場合の電流生成回路 10A の動作について以下説明する。まず、出力信号 OUT がローレベルのときについて説明する。このとき、入力信号 IN と出力信号 OUT との論理は一致する。変化時電流生成回路 11 は、nMOS ランジスタ MN12 がオフ状態であるので、電流  $I_C$  を生成しない。また、立ち上がり電流生成回路 12 において、ノード N11 の電圧は、pMOS ランジスタ MP11 がオン状態でありかつ nMOS ランジスタ MN13 がオフ状態であるので、高電源電圧 VDDH まで上昇する。nMOS ランジスタ MN15 は、ノード N11 の電圧に応答してオン状態であるが、入力信号 IN がローレベルであるため nMOS ランジスタ MN14 はオフ状態である。したがって、立ち上がり電流生成回路 12 は電流  $I_R$  を生成しない。さらに、立ち下がり電流生成回路 13 は、nMOS ランジスタ MN17 がオフ状態であるので、電流  $I_F$  を生成しない。したがって、入力信号 IN がローレベルであり、かつ出力信号 OUT がローレベルであるときは、電流生成回路 10A は電流を生成しない。

【 0 0 6 7 】

次に、出力信号 OUT が第 2 のハイレベルのときについて説明する。このとき、入力信号 IN と出力信号 OUT との論理は一致しない。変化時電流生成回路 11 は、nMOS ランジスタ MN12 がオフ状態であるので、電流  $I_C$  を生成しない。また、立ち上がり電流生成回路 12 において、pMOS ランジスタ MP11 はオフ状態となり、ノード N1

10

20

30

40

50

1 がフローティング状態となる。しかし、入力信号 IN がローレベルであるので n MOS トランジスタ MN14 がオフ状態となるため、立ち上がり電流生成回路 12 は電流  $I_R$  を生成しない。また、立ち下がり電流生成回路 13 は、n MOS トランジスタ MN16, MN17 がオン状態となるため、電流  $I_F$  を生成する。したがって、入力信号 IN がローレベルであり、かつ出力信号 OUT が第 2 のハイレベルであるときは、電流生成回路 10A は電流  $I_F$  を生成する。

#### 【0068】

さらに、上述したレベルコンバータ回路 1 の課題 A, B に対するレベルコンバータ回路 1A の効果について考察する。

#### 【0069】

まず、課題 A について説明する。入力信号 IN と入力信号 INB とがともに第 1 のハイレベルとなる期間が存在しない場合、電流生成回路 10 は正しく電流を生成することができない。このとき、入力信号 IN と出力信号 OUT との論理は不一致となる場合がある。これに対して、電流生成回路 10A を用いることで論理不一致を解決することができる。すなわち、入力信号 IN が第 1 のハイレベルであり、かつ出力信号 OUT がローレベルである論理不一致が存在する場合には、立ち上がり電流生成回路 12 が電流  $I_R$  を生成する。また、入力信号 IN がローレベルであり、かつ出力信号 OUT が第 2 のハイレベルである論理不一致が存在する場合には、立ち下がり電流生成回路 13 が電流  $I_F$  を生成する。これにより、論理不一致が存在する場合には、電流生成回路 10A によって電流が生成され、正しい論理を出力することを 保証 することができる。

#### 【0070】

これは、レベルコンバータ回路 1A が、図 10B で示した非理想的な入力信号 IN, INB の波形に対応できることを意味する。また、図 10B と異なる非理想的な波形、すなわち、入力信号 IN の立ち上がりにおいて入力信号 IN と入力信号 INB との波形が重ならない場合、及び入力信号 IN の立ち上がり並びに立ち下がりの両方において入力信号 IN と入力信号 INB との波形が重ならない場合においても、レベルコンバータ回路 1A は、正常に動作する。

#### 【0071】

次に、課題 B について説明する。入力信号 IN の論理が第 1 のハイレベルであり、出力信号 OUT の論理が第 2 のハイレベルである場合、すなわち論理がハイレベルで一致している場合を考える。このとき、端子 T2 はリーク電流で充電され、端子 T2 はハイインピーダンス状態となる。このとき、外部ノイズ等の外乱により出力信号 OUT の電圧が低下した場合を考える。出力信号 OUT の電圧が徐々に低下すると、出力信号 OUT をモニタする立ち上がり電流生成回路 12 の p MOS トランジスタ MP11 が出力信号 OUT の電圧の低下に対応した電流を生成し、ノード N11 の電圧が徐々に上昇する。これに応じて、ノード N11 の電圧をモニタする n MOS トランジスタ MN15 は、電流  $I_R$  を生成し始める。上述したように、出力信号 OUT の電圧が低下すると、立ち上がり電流生成回路 12 によって電流  $I_R$  が生成され、出力信号 OUT の電圧の低下を回避するように差動增幅回路 30 及びソース接地增幅回路 40 に電流が供給される。

#### 【0072】

次に、入力信号 IN の論理がローレベルであり、出力信号 OUT の論理がローレベルである場合、すなわち論理がローレベルで一致している場合を考える。このとき、端子 T2 はリーク電流で放電され、端子 T2 はハイインピーダンス状態となる。このとき、外部ノイズ等の外乱により出力信号 OUT の電圧が上昇した場合を考える。出力信号 OUT の電圧が徐々に上昇すると、出力信号 OUT をモニタする立ち下がり電流生成回路 13 の n MOS トランジスタ MN17 が出力信号 OUT の電圧の上昇に対応した電流を生成する。また、n MOS トランジスタ MN16 のゲートには第 1 のハイレベルを有する入力信号 INB が印加されているため、n MOS トランジスタ MN16 はオン状態である。上述したように、出力信号 OUT の電圧が上昇すると、立ち下がり電流生成回路 13 によって電流  $I_F$  が生成され、出力信号 OUT の電圧の上昇を回避するように差動增幅回路 30 及びソ-

10

20

30

40

50

ス接地増幅回路40に電流が供給される。

【0073】

以上説明したように、第2の実施形態によれば、第1の実施形態と同様の作用効果を有する。また、入力信号INと入力信号INBがともに第1のハイレベルである期間が存在しない場合にも、立ち上がり電流生成回路12が電流IRを生成する、又は立ち下がり電流生成回路13が電流IFを生成するので、レベルコンバータ回路1Aは正常に動作する。さらに、外部ノイズ等の外乱により出力信号OUTの電圧が変化する場合にも、立ち上がり電流生成回路12が電流IRを生成する、又は立ち下がり電流生成回路13が電流IFを生成するので、レベルコンバータ回路1Aは正常に動作する。

【0074】

なお、第2の実施形態では、立ち上がり電流生成回路12及び立ち下がり電流生成回路13を備えて電流生成回路10Aを構成したが、本発明はこれに限らず、立ち上がり電流生成回路12又は立ち下がり電流生成回路13のうちのいずれか一方を備えて電流生成回路10Aを構成してもよい。

【0075】

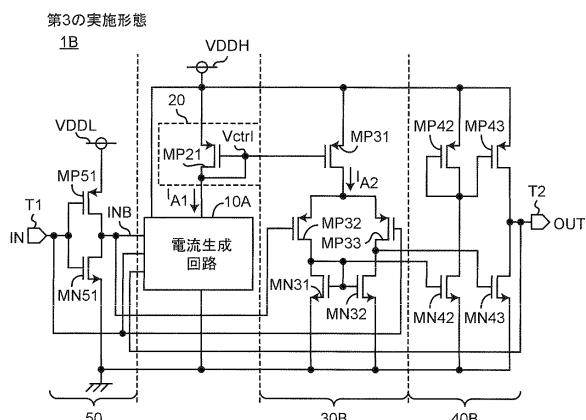

第3の実施形態。

図13Aは、本発明の第3の実施形態に係るレベルコンバータ回路1Bの応用例を示すブロック図である。図13Aにおいて、レベルコンバータ回路1Bは、低電源電圧VDD\_L(例えば0.4Vである。)が供給される低電圧回路ブロック200からの信号の信号レベルを変換して、高電源電圧VDDH(例えば3Vである。)が供給される高電圧回路ブロック300に出力する。以下、入力信号IN, INB、第1のハイレベル、第2のハイレベル、低電圧源、及び高電圧源はそれぞれ、第1の実施形態で説明した入力信号IN, INB、第1のハイレベル、第2のハイレベル、低電圧源、及び高電圧源と同様である。

【0076】

図13Bは、本発明の第3の実施形態に係るレベルコンバータ回路1Bの構成を示すブロック図である。第2の実施形態に係るレベルコンバータ回路1Aでは、電流IFの特性を十分に評価できない課題があった。

【0077】

レベルコンバータ回路1Bは、レベルコンバータ回路1Aと比較して、差動増幅回路30に代えて差動増幅回路30Bを備える点、ソース接地増幅回路40に代えてプッシュプル型ソース接地増幅回路40Bを備える点が異なり、その他の構成要素はレベルコンバータ回路1Aと同様であり、その説明を省略する。

【0078】

差動増幅回路30Bは、差動増幅回路30と比較して、pMOSトランジスタMP32のドレインとnMOSトランジスタMN31のドレインとの接続点がnMOSトランジスタMN42のゲートに接続されている点、及びpMOSトランジスタMP33のドレインとnMOSトランジスタMN32のドレインとの接続点がnMOSトランジスタMN43のゲートに接続されている点が異なり、その他の構成要素及び動作は差動増幅回路30と同様である。

【0079】

プッシュプル型ソース接地増幅回路40Bは、pMOSトランジスタMP42, MP43と、nMOSトランジスタMN42, MN43とを備えて構成される。pMOSトランジスタMP42のソースは高電圧源に接続され、pMOSトランジスタMP42のゲートは、pMOSトランジスタMP42のドレイン及びpMOSトランジスタMP43のゲートに接続される。pMOSトランジスタMP42のドレインは、nMOSトランジスタMN42のドレインに接続される。nMOSトランジスタMN42のゲートは、pMOSトランジスタMP32のドレインとnMOSトランジスタMN31のドレインとの接続点に接続され、nMOSトランジスタMN42のソースは接地される。pMOSトランジスタMP43のソースは高電圧源に接続され、pMOSトランジスタMP43のドレインは、

10

20

30

40

50

nMOSトランジスタMN43のドレインに接続される。nMOSトランジスタMN43のゲートは、pMOSトランジスタMP33のドレインとnMOSトランジスタMN32のドレインとの接続点に接続され、nMOSトランジスタMN43のソースは接地される。pMOSトランジスタMP43のドレインとnMOSトランジスタMN43のドレインとの接続点は、端子T2に接続される。ここで、差動增幅回路30Bとプッシュプル型ソース接地增幅回路40Bとは、2段増幅回路を構成する。

#### 【0080】

プッシュプル型ソース接地增幅回路40Bは、上述したように構成されるので、出力信号OUTの立ち上がり及び立ち下がりの両方において、電流生成回路10Aによって生成される電流に対応した電流によって端子T2を充電及び放電することができる。

10

#### 【0081】

以上説明したように、第3の実施形態によれば、第2の実施形態と同様の作用効果を有する。

#### 【0082】

なお、第1及び第2の実施形態では、差動増幅回路30及びソース接地増幅回路40を備えてレベルコンバータ回路1及びレベルコンバータ回路1Aを構成したが、本発明はこれに限らず、差動増幅回路30B及びプッシュプル型ソース接地増幅回路40Bを備えてレベルコンバータ回路1及びレベルコンバータ回路1Aを構成してもよい。

#### 【実施例1】

#### 【0083】

20

第1の実施形態に係るレベルコンバータ回路1についてのシミュレーション評価（実施例1）について以下説明する。図3Bのレベルコンバータ回路1について、SPICEシミュレーション評価の結果を示す。使用したプロセスは0.35μmCMOSプロセスである。低電源電圧VDDLは0.4~0.8Vとし、また高電源電圧VDDHは3Vとした。

#### 【0084】

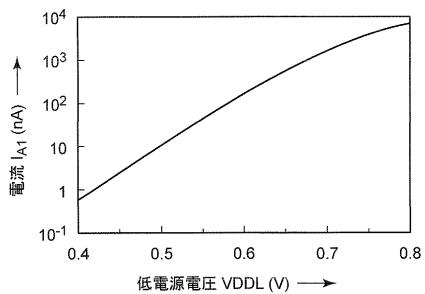

本発明者らは、電流生成回路10のシミュレーション評価を行った。図14は、図4の電流生成回路10によって生成されるピーク電流の低電源電圧VDDLへの依存性を示すグラフである。図14は、低電源電圧VDDLを0.4V~0.8Vに変化させたときに、電流生成回路10によって生成される電流IA1のピーク電流値を示す。低電源電圧VDDLの上昇に従って、ピーク電流は指数関数的に増加することが確認できる。これは、低電源電圧VDDLが低電圧であるときは、電流生成回路10の縦続接続したnMOSトランジスタMN11,MN12がしきい値電圧以下のサブスレッショルド領域で動作し、低電源電圧VDDLが上昇すると、nMOSトランジスタMN11,MN12のゲート電圧が上昇して、nMOSトランジスタMN11,MN12に流れる電流が指数関数的に増加するためである。

30

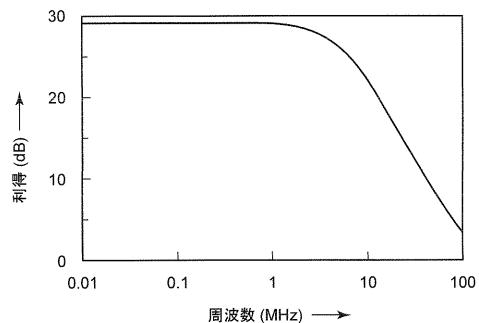

#### 【0085】

電流生成回路10によって生成される電流IA1は、pMOSトランジスタMP21,MP31,MP41を備えて構成されるカレントミラー回路を介して差動増幅回路30及びソース接地増幅回路40に供給される。図5に示すように、電流生成回路10によって生成される電流IA1はパルス電流となるため、カレントミラー回路を介しての電流供給精度の課題がある。そこで、差動増幅回路30に供給される電流IA2及びソース接地増幅回路40に供給される電流IA3の周波数特性を評価した。

40

#### 【0086】

図15は、図3Bの電流IA2,IA3の周波数応答特性を示すグラフである。図15に示すように、カレントミラー回路は、電流IA1の周波数が約2MHz以下の場合、一定の電流利得を維持したまま電流を差動増幅回路30及びソース接地増幅回路40に供給できることがわかる。電流IA1の周波数が2MHzを超えると、カレントミラー回路のローパスフィルタの効果によって電流利得は減少する。すなわち、レベルコンバータ回路1は、数MHz帯域の動作帯域を有する。レベルコンバータ回路1の動作帯域を向上させ

50

るためには、電流生成回路 10 によって生成される電流  $I_{A1}$  の電流量を高める工夫が必要になる。上述した電流生成回路 10 の変形例に係る電流生成回路 10a, 10b, 10c, 10d を用いることによって、電流生成回路 10 によって生成される電流  $I_{A1}$  の電流量を高めることができる。

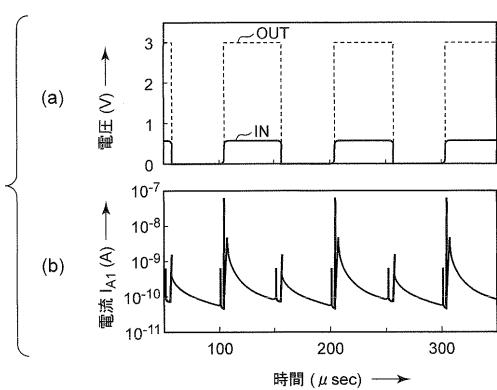

【0087】

本発明者らは、レベルコンバータ回路 1 の動作の一例として、低電源電圧 VDDL を 0.55V、入力信号 IN の周波数を 10 kHz としてシミュレーション評価を行った。図 16 (a) は、図 1 のレベルコンバータ回路 1 への入力信号 IN の波形及び図 1 のレベルコンバータ回路 1 からの出力信号 OUT の波形を示すグラフであり、図 16 (b) は、図 2 の電流生成回路 10 によって生成される電流  $I_{A1}$  の波形を示すグラフである。図 16 (a) に示すように、入力信号 IN の論理に同期して、0 ~ 3V の振幅を有する出力信号 OUT が output される。また、図 16 (b) に示すように、入力信号 IN の論理が反転するときにのみ、大きな電流  $I_{A1}$  が生成される。

【0088】

図 17 は、低電源電圧 VDDL の電圧値に対する図 3B のレベルコンバータ回路 1 及び従来技術に係るレベルコンバータ回路 100 の遅延時間を示すグラフである。図 3B のレベルコンバータ回路 1 の遅延時間を図 2 に示した従来技術に係るレベルコンバータ回路 100 の遅延時間と比較する。従来技術に係るレベルコンバータ回路 100 は、低電源電圧 VDDL が 0.7V 以上のときに、レベルコンバータ回路 1 よりも高速に動作する。しかし、低電源電圧 VDDL が低下するにつれ、レベルコンバータ回路 100 の動作遅延は指數関数的に増大し、低電源電圧 VDDL が約 0.52V 以下になると、レベルコンバータ回路 100 は、動作することができない。これは、従来技術に係るレベルコンバータ回路 100 では、出力信号 OUT の電圧を低下させるために端子 T102 を放電する電流は、低電源電圧 VDDL の電圧に依存するためである。すなわち、低電源電圧 VDDL が低電圧になるほど nMOS ドレイン M102 を流れる電流が減少し、遅延時間が指數関数的に増大する。そして、低電源電圧 VDDL が約 0.52V 以下になると nMOS ドレイン M102 を流れる電流量より pMOS ドレイン MP102 を流れる電流量の方が多くなり、出力信号 OUT の論理は反転することなく、レベルコンバータ回路 100 は動作を停止する。

【0089】

一方、レベルコンバータ回路 1 では、電流生成回路 10 によって生成される電流  $I_{A1}$  の電流量で遅延時間が決定される。低電源電圧 VDDL が 0.65V 付近よりも低い領域では、電流生成回路 10 の nMOS ドレイン MN11, MN12 が、サブスレッショルド領域で動作する。このため、図 14 に示すように、電流  $I_{A1}$  の電流量が低電源電圧 VDDL に対して指數関数的に変化する。これにより、低電源電圧 VDDL の上昇に従って、遅延時間が指數関数的に減少する。また、低電源電圧 VDDL が約 0.65V より高い領域では、遅延時間はほぼ一定となる。これは、低電源電圧 VDDL が 0.65V 以上になると電流生成回路 10 によって生成される電流  $I_{A1}$  は増加するものの、図 15 に示すようにカレントミラー回路のローパスフィルタの効果によって生成される電流  $I_{A1}$  の供給能力が減少する。その結果、差動增幅回路 30 に流れる電流  $I_{A2}$  及びソース接地増幅回路 40 に流れる電流  $I_{A3}$  は増加せず、遅延時間はほぼ一定となる。このことは、図 17 の遅延時間の逆数である周波数が MHz オーダーであることからも図 15 の結果と一致する。レベルコンバータ回路 1 は、電流生成回路 10 によって生成される電流  $I_{A1}$  に對応する電流を用いて、端子 T2 に対する充電及び放電の両方を実行するため、従来技術に係るレベルコンバータ回路 100 が有する問題は発生せず、低電源電圧 VDDL と高電源電圧 VDDH との間の電源電圧の差が大きくなるような低い低電源電圧 VDDL においても安定に動作する。

【0090】

図 18 は、低電源電圧 VDDL の電圧値に対する図 3B のレベルコンバータ回路 1 及び従来技術に係るレベルコンバータ回路 100 の消費電力を示すグラフである。ここでは、

10

20

30

40

50

入力信号INの周波数は1 kHzである。また、図3Bのレベルコンバータ回路1の消費電力を図2に示した従来技術に係るレベルコンバータ回路100の消費電力と比較する。図18より明らかなどおり、レベルコンバータ回路1は、従来技術に係るレベルコンバータ回路100と比較して、低消費電力で動作可能である。従来技術に係るレベルコンバータ回路100は、高電圧源から多量の貫通電流が流れるため消費電力が高くなる。

#### 【0091】

また、図18において、従来技術に係るレベルコンバータ回路100の消費電力が、低電源電圧VDDLの上昇とともに指數関数的に減少していることが確認できる。これは、低電源電圧VDDLで動作するロジック回路の信号波形が原因である。低電源電圧VDDLで動作するロジック回路においては、トランジスタの電流駆動能力が極めて低くなり、信号が緩やかに変化する。そのため、0.55V程度の低電源電圧VDDLでは、信号の遷移時間が長くなり、高電圧源から多量の貫通電流が流れる。一方で、低電源電圧VDDLの上昇とともに、信号は急峻に変化するため、高電圧源からの貫通電流が減少する。

#### 【0092】

一方、レベルコンバータ回路1の消費電力は、低電源電圧VDDLが変化しても、ほぼ変化しない。これは、低電源電圧VDDLの上昇による次の2つの要因に起因する。

(1)電流生成回路10によって生成される電流IA1の増加。

(2)低電源電圧VDDLによって駆動されるロジック回路の信号の遅延改善。

図14に示すとおり、電流生成回路10によって生成される電流IA1が、低電源電圧VDDLの上昇に従って指數関数的に増加する。一方で、低電源電圧VDDLの上昇に従って低電源電圧VDDLで動作するロジック回路の遅延時間は指數関数的に減少する。これら2つの要因により、瞬間に流れる電流IA1は指數関数的に増加するが、電流IA1が流れる時間は指數関数的に短くなるので、最終的に流れる電流IA1の全体量はほぼ変化しない。したがって、レベルコンバータ回路1の消費電力は、低電源電圧VDDLに対する依存性が小さい。

#### 【0093】

表1は、図3Bのレベルコンバータ回路1及び従来技術に係るレベルコンバータ回路100のプロセスバラツキ及び温度変化に対する耐性を示す。表1では、低電源電圧VDDLは0.6Vである。また、表1中のFF, FS, TT, SF, SSは、nMOSトランジスタ及びpMOSトランジスタのコーナーモデルを表し、Pは当該レベルコンバータ回路が正常に動作するパス状態を表し、Fは当該レベルコンバータ回路が正常に動作しないフェイル状態を表す。

#### 【0094】

【表1】

| タイプ                 | 温度 (°C) | プロセスコーナー |    |    |    |    |

|---------------------|---------|----------|----|----|----|----|

|                     |         | FF       | FS | TT | SF | SS |

| 実施例1に係る<br>レベルコンバータ | -20     | P        | P  | P  | P  | P  |

|                     | 40      | P        | P  | P  | P  | P  |

|                     | 100     | P        | P  | P  | P  | P  |

| 従来技術に係る<br>レベルコンバータ | -20     | P        | P  | P  | F  | F  |

|                     | 40      | P        | P  | P  | P  | F  |

|                     | 100     | P        | P  | P  | P  | P  |

## 【0095】

従来技術に係るレベルコンバタ回路100は、プロセスバラツキ及び温度変化によってnMOSトランジスタのしきい値電圧が高くなると、正常に動作しなくなる。これは、遅延時間の低電源電圧VDDLに対する依存性の結果と同様に、nMOSトランジスタMN102を流れる電流がpMOSトランジスタMP102を流れるリーク電流よりも小さくなることで、端子T102が放電されないためである。一方、レベルコンバタ回路1は、プロセスバラツキ及び温度変化に対して安定に動作する。

## 【0096】

本発明者らは、レベルコンバタ回路1の有効性を確認するために、チップを試作した。試作チップの信号波形及び消費電力の測定結果を以下に示す。使用したプロセスは0.35μm 2P-4M CMOSプロセスである。図19に試作チップの写真を示す。回路面積は、43μm × 43μmと小面積である。

## 【0097】

図20は、図19の試作チップの動作を測定するための測定環境を示すブロック図である。図20に示すように、パッケージされた試作チップ402をボード上に実装して測定を行った。ファンクションジェネレータ401を用いて低振幅の入力信号INを生成し、レベルコンバタ回路(試作チップ402)に入力する。ファンクションジェネレータ401からの入力信号IN及びレベルコンバタ回路からの出力信号OUTをオシロスコープ403に入力して評価した。また、高電源電圧VDDHは3Vである。

## 【0098】

図21(a)は、図20の測定環境において、試作チップ402への入力信号INの波形を示すグラフであり、図21(b)は、図20の測定環境において、試作チップからの

10

20

30

40

50

出力信号 OUT の波形を示すグラフである。図 21 は、低電源電圧 VDDL が 0.4V、入力信号 IN の周波数が 10 kHz であるときの入力信号 IN の波形及び出力信号 OUT の波形を示す。0.4V の振幅を有する低振幅の入力信号 IN が、レベルコンバータ回路 1 によって 3V の振幅を有する大振幅の出力信号 OUT にレベル変換されている様子が確認できる。

#### 【0099】

また、図 21 の結果から、入力信号 IN が変化してから、出力信号 OUT が変化するまでの立ち上がり時間と立ち下がり時間が異なることがわかる。その結果、出力信号 OUT のデューティ比が 50% 以下となった。これは、レベルコンバータ回路 1 の特性に起因する。図 3B に示したレベルコンバータ回路 1 の端子 T2 の充放電は、pMOS ドラッグ・スイッチ MP41 及び nMOS ドラッグ・スイッチ MN41 に流れる電流によって行われる。このとき、出力信号 OUT の立ち上がり時間は、pMOS ドラッグ・スイッチ MP41 を流れる電流、すなわち、カレントミラー回路を介して供給される電流生成回路 10 によって生成される電流 IA1 に対応する電流によって決まる。一方、nMOS ドラッグ・スイッチ MN41 を流れる電流は、nMOS ドラッグ・スイッチ MN41 のゲートに印加される電圧によって決まる。nMOS ドラッグ・スイッチ MN41 のゲートの容量を充放電するための時間も、カレントミラー回路を介して供給される電流生成回路 10 によって生成される電流 IA1 に対応する電流によって決まるが、差動增幅回路 30 の回路構成の特性から、pMOS ドラッグ・スイッチ MP41 によって端子 T2 が充電される時間と、nMOS ドラッグ・スイッチ MN41 によって端子 T2 が放電される時間とは異なる。そのため、出力信号 OUT の立ち上がり時間と立ち下がり時間が異なる結果となる。今後は、立ち上がり時間と立ち下がり時間とが等しくなるような回路を構成するなど、デューティ比を 50% に近づける必要がある。

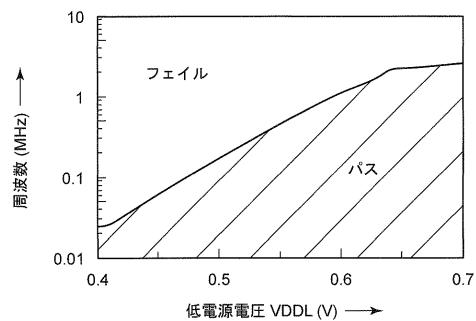

#### 【0100】

図 22 は、図 19 の試作チップのシム (Shmoo) プロットを示す図である。低電源電圧 VDDL に対して、レベルコンバータ回路 1 が動作可能な周波数帯をプロットしている。低電源電圧 VDDL が 0.4V から 0.64V 付近であるとき、動作可能な最大周波数が指数関数的に増加している。これは、低電源電圧 VDDL の上昇に従って電流生成回路 10 によって生成される電流 IA1 が指数関数的に増加するためである。低電源電圧 VDDL が 0.64V を超えると動作可能な周波数は 2MHz 付近からほぼ一定となる。これは、図 17 に示したシミュレーション結果と同様に、カレントミラー回路のローパス・フィルタの効果により、電流生成回路 10 によって生成された電流 IA1 の高周波成分が差動增幅回路 30 及びソース接地增幅回路 40 に供給されず、差動增幅回路 30 及びソース接地增幅回路 40 に流れる電流が制限されるためである。

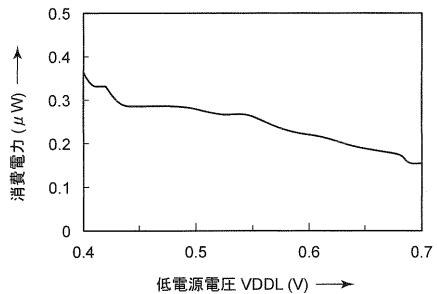

#### 【0101】

図 23 は、低電源電圧 VDDL の電圧値に対する図 19 の試作チップの消費電力を示すグラフである。ここでは、入力信号 IN の周波数は 10 kHz である。試作チップの消費電力は、低電源電圧 VDDL への依存性が小さく、低電源電圧 VDDL の上昇とともに減少している。これは、図 18 のシミュレーション結果と一致する。

#### 【0102】

レベルコンバータ回路 1 は、クロスカップル型レベルコンバータ回路 100 よりも低消費電力で動作し、かつ低電源電圧 VDDL が低電圧であっても安定に動作することから、低電圧動作 LSI に有用である。

#### 【0103】

第 1 の実施形態では、回路ブロック間の電源電圧の差電圧が大きい場合でも安定に動作可能なレベルコンバータ回路 1 を提案した。レベルコンバータ回路 1 は、2 段增幅回路を基本とした回路を構成することで、従来技術に係るレベルコンバータ回路 100 の問題点である充放電部分の電源電圧差依存性を緩和する。さらに、レベルコンバータ回路 1 は入力信号 IN が変化するときのみ電力を消費することから低消費電力で動作することができる。0.35 μm 標準 CMOS プロセスを用いてチップを試作し、測定により動作を確認した。レベルコンバータ回路 1 を用いることで、0.4V 振幅の低電圧信号を 3V 振幅の

高電圧信号に変換することができる。レベルコンバータ回路1は、低消費電力、低電圧動作L S Iに有用である。

【実施例2】

【0104】

第2の実施形態に係るレベルコンバータ回路1Aについてのシミュレーション評価(実施例2)について以下説明する。本発明者らは、レベルコンバータ回路1Aの動作を確認するためのシミュレーション評価を行った。使用したCMOSプロセスは、0.35μm CMOSプロセスである。

【0105】

本発明者らは、レベルコンバータ回路1Aのシミュレーション評価を行った。ここで、低電源電圧VDDLは0.4Vであり、高電源電圧VDDHは3.0Vである。シミュレーションの結果を図24～図27に示す。図24は、図11Bのレベルコンバータ回路1Aへの入力信号IN, INBの波形及び図11Bのレベルコンバータ回路1Aからの出力信号OUTの波形を示すグラフである。図25は、図12の変化時電流生成回路11によって生成される電流Icの波形を示すグラフである。図26は、図12の立ち下がり電流生成回路13によって生成される電流Ifの波形を示すグラフである。図27は、図12の立ち上がり電流生成回路12によって生成される電流Irの波形を示すグラフである。

【0106】

図24に示すように、入力信号INの論理に一致して出力信号OUTがレベル変換されて出力されている。また、入力信号INの立ち上がりと入力信号INBの立ち下がりとにおいては、波形が重なっているが、入力信号INの立ち下がりと入力信号INBの立ち上がりとにおいては、波形が重なっていない。これは、入力信号INの立ち下がりでは電流Icが正しく生成されないことを意味する。

【0107】

図25に示すように、入力信号INの立ち上がり時に、変化時電流生成回路11は、正常に電流Icを生成している(1ナノアンペアオーダーのピーク電流である。)。一方、入力信号INの立ち下がり時には、変化時電流生成回路11は、電流Icを生成しているように見える(2ナノアンペアオーダーのピーク電流である。)。しかし、上述のように、入力信号INの立ち下がりでは、入力信号INと入力信号INBとは重ならないため、変化時電流生成回路11が正常動作しているとはいえない。この電流Icは、出力信号OUTのキックバック現象によって生成された電流であり、変化時電流生成回路11によって生成された電流ではない。

【0108】

しかしながら、レベルコンバータ回路1Aは、所望の動作(すなわち、ローレベルの出力信号OUTを出力する。)を行っている。これは、レベルコンバータ回路1Aのレベル変換動作が、差動增幅回路30及びソース接地增幅回路40における出力信号OUTの立ち上がり時間の遅延時間並びに立ち下がり時間の遅延時間、及び電流生成回路10Aの遅延時間に依存するためである。レベルコンバータ回路1Aの差動增幅回路30及びソース接地增幅回路40では、出力信号OUTの立ち上がり遅延時間はpMOSトランジスタMP41の充電電流IA3で決定され、出力信号OUTの立ち下がり時間はnMOSトランジスタMN41の放電電流IA4で決定される。充電電流IA3は電流生成回路10Aによって生成される電流IA1に依存する一方で、放電電流IA4は電流生成回路10Aによって生成される電流に依存しないことが考えられる。

【0109】

これを図11Bに示す差動增幅回路30及びソース接地增幅回路40の回路図で考える。充電電流IA3は、pMOSトランジスタMP21, MP41で構成されるカレントミラー回路を介して供給される電流生成回路10Aによって生成された電流IA1に対応する電流である。一方、放電電流IA4は、ソース接地增幅回路40のnMOSトランジスタMN41のゲート電圧、すなわち差動增幅回路30のノードN31の電圧に依存する。ノードN31の電圧は、入力信号INがローレベルとなると、ローレベルから第1のハイ

10

20

30

40

50

レベルの近傍電圧に変化する。ノードN31の電圧は、nMOSトランジスタMN41のゲートに印加されるため、出力信号OUTは立ち下がってローレベルとなる。ノードN31の電圧は、電流生成回路10Aによって生成される電流IA1に依存せず、第1のハイレベルの近傍電圧となって出力信号OUTを立ち下げる。すなわち、差動増幅回路30及びソース接地増幅回路40では、出力信号OUTの立ち上がり遅延時間が長く、立ち下がり遅延時間が短い。立ち上がり遅延時間が長いため、入力信号INの立ち上がりにおいて論理不一致が生じ、電流生成回路10Aの立ち上がり電流生成回路12が論理不一致を検出し、電流IRを生成して出力信号OUTの立ち上がりを加速させる。一方、レベルコンバータ回路1Aの差動増幅回路30及びソース接地増幅回路40は、出力信号OUTの立ち下がり時には素早く反応するため、立ち下がり電流生成回路13は動作せずともレベルコンバータ回路1Aはローレベルの出力信号OUTを出力することができる。10

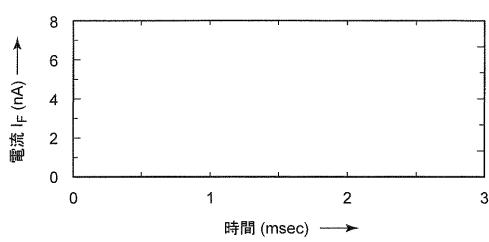

#### 【0110】

図26に示すように、電流IFが生成されていないことが確認できる。これは、上述のように出力信号OUTの立ち下がり遅延時間が短いので、電流生成回路10Aが動作を開始する前に、出力信号OUTがローレベルに立ち下がるからである。一方、出力信号OUTの立ち上がりにおいて、図25に示すように電流ICが生成されているが、出力信号OUTを立ち上げるのに十分な電流量とは言えず、立ち上がり電流生成回路12が論理不一致を検出し、電流IRを生成する。図27に示すように、出力信号OUTの立ち上がりにおいて、電流IRが生成されていることが確認できる。20

#### 【0111】

図28は、低電源電圧VDDLの電圧値に対する図11Bのレベルコンバータ回路1A及び図3Bのレベルコンバータ回路1の遅延時間を示すグラフである。図28において、フィードバック制御を有するレベルコンバータ回路1Aの遅延時間は実線で示され、フィードバック制御を有しないレベルコンバータ回路1の遅延時間は破線で示される。図28に示すように、レベルコンバータ回路1Aの遅延時間は、低電源電圧VDDLの上昇とともに減少することが確認できる。また、レベルコンバータ回路1Aは、レベルコンバータ回路1と比較して、高速に動作することが確認できる。低電源電圧VDDLが約0.55V以下の低電圧では、レベルコンバータ回路1Aはレベルコンバータ回路1よりも数倍程度高速に動作し、低電源電圧VDDLが高くなるにつれて、その差は大きくなることが確認できる。立ち上がり電流生成回路12によって生成される電流IR及び立ち下がり電流生成回路13によって生成される電流IFが差動増幅回路30及びソース接地増幅回路40の動作電流に加算されることが、レベルコンバータ回路1Aの高速動作に繋がっているといえる。30

#### 【0112】

図29は、低電源電圧VDDLの電圧値に対する図11Bのレベルコンバータ回路1A及び図3Bのレベルコンバータ回路1の消費電力を示すグラフである。図29において、フィードバック制御を有するレベルコンバータ回路1Aの消費電力は実線で示され、フィードバック制御を有しないレベルコンバータ回路1の消費電力は破線で示される。レベルコンバータ回路1Aは、レベルコンバータ回路1よりも消費電力が多い。これは、立ち上がり電流生成回路12によって生成される電流IR及び立ち下がり電流生成回路13によって生成される電流IFが、差動増幅回路30及びソース接地増幅回路40の動作電流に加算されるためである。しかし、増加する消費電力は、ナノワットオーダーの微小電力に抑えることができている。40

#### 【0113】

本発明者らは、電流生成回路10Aの特性評価を行うためのシミュレーション評価を行った。ここでは、図12に示す電流生成回路10Aにおいて、以下の2つのシミュレーションを実行した。

シミュレーション1：入力信号INを第1のハイレベルに固定し、入力信号INBをローレベルに固定し、出力信号OUTを0Vから3Vまで変化させて、立ち上がり電流生成回路12によって生成される電流IR及び立ち下がり電流生成回路13によって生成される50

電流  $I_F$  を測定する。

シミュレーション 2：入力信号  $I_N$  をローレベルに固定し、入力信号  $I_N B$  を第 1 のハイレベルに固定し、出力信号  $OUT$  を 0 V から 3 V まで変化させて、立ち上がり電流生成回路 1 2 によって生成される電流  $I_R$  及び立ち下がり電流生成回路 1 3 によって生成される電流  $I_F$  を測定する。

#### 【0114】

まず、シミュレーション 1 の結果について説明する。図 30 A は、図 12 の電流生成回路 10 A において、入力信号  $I_N$  を第 1 のハイレベルに固定し、入力信号  $I_N B$  をローレベルに固定し、出力信号  $OUT$  を 0 V から 3 V に変化させた場合に生成される電流  $I_F$  を示すグラフである。また、図 30 B は、図 12 の電流生成回路 10 A において、入力信号  $I_N$  を第 1 のハイレベルに固定し、入力信号  $I_N B$  をローレベルに固定し、出力信号  $OUT$  を 0 V から 3 V に変化させた場合に生成される電流  $I_R$  を示すグラフである。

10

#### 【0115】

入力信号  $I_N$  が第 1 のハイレベルであり、入力信号  $I_N B$  がローレベルであるため、出力信号  $OUT$  は第 2 のハイレベルであることが理想である。図 30 B に示すように、出力信号  $OUT$  が約 2.4 V 以下の低い電圧である場合、電流  $I_R$  が生成されることが確認できる。この電流  $I_R$  は、出力信号  $OUT$  を上昇させるようにカレントミラー回路を介して差動増幅回路 30 及びソース接地増幅回路 40 に供給される。一方、出力信号  $OUT$  が高い電圧、すなわち第 2 のハイレベルに近い場合、電流  $I_R$  は生成されないことが確認できる。また、このとき、入力信号  $I_N B$  はローレベルであり、出力信号  $OUT$  を立ち下げる必要はないため、図 30 A に示すように電流  $I_F$  は生成されない。電流  $I_R$  の電流量（シミュレーション 1 では約 17 nA である。）は、低電源電圧  $VDD L$  の値（シミュレーション 1 では 0.4 V である。）に依存する。低電源電圧  $VDD L$  が上昇すると、電流  $I_R$  は増大する。

20

#### 【0116】

次に、シミュレーション 2 の結果について説明する。図 31 A は、図 12 の電流生成回路 10 A において、入力信号  $I_N$  をローレベルに固定し、入力信号  $I_N B$  を第 1 のハイレベルに固定し、出力信号  $OUT$  を 0 V から 3 V に変化させた場合に生成される電流  $I_F$  を示すグラフである。また、図 31 B は、図 12 の電流生成回路 10 A において、入力信号  $I_N$  をローレベルに固定し、入力信号  $I_N B$  を第 1 のハイレベルに固定し、出力信号  $OUT$  を 0 V から 3 V に変化させた場合に生成される電流  $I_R$  を示すグラフである。

30

#### 【0117】

入力信号  $I_N$  がローレベルであり、入力信号  $I_N B$  が第 1 のハイレベルであるため、出力信号  $OUT$  はローレベルであることが理想である。図 31 A に示すように、出力信号  $OUT$  が約 0.3 V 以上の高い電圧である場合、電流  $I_F$  が生成されることが確認できる。この電流  $I_F$  は、出力信号  $OUT$  を低下させるようにカレントミラー回路を介して差動増幅回路 30 及びソース接地増幅回路 40 に供給される。一方、出力信号  $OUT$  が低い電圧、すなわちローレベルに近い場合、電流  $I_F$  は生成されないことが確認できる。また、このとき、入力信号  $I_N$  はローレベルであり、出力信号  $OUT$  を立ち上げる必要はないため、図 31 B に示すように電流  $I_R$  は生成されない。電流  $I_F$  の電流量（シミュレーション 2 では約 17 nA である。）は、低電源電圧  $VDD L$  の値（シミュレーション 2 では 0.4 V である。）に依存する。低電源電圧  $VDD L$  が上昇すると、電流  $I_F$  は増大する。

40

#### 【実施例 3】

#### 【0118】

第 3 の実施形態に係るレベルコンバータ回路 1 B についてのシミュレーション評価（実施例 3）について以下説明する。本発明者らは、レベルコンバータ回路 1 B のシミュレーション評価を行った。その結果を図 32 ~ 図 35 に示す。図 32 は、図 13 B のレベルコンバータ回路 1 B への入力信号  $I_N$ 、 $I_N B$  の波形及び図 13 B のレベルコンバータ回路 1 B からの出力信号  $OUT$  の波形を示すグラフである。図 33 は、図 12 の変化時電流生成回路 1 1 によって生成される電流  $I_c$  の波形を示すグラフである。図 34 は、図 12 の

50

立ち下がり電流生成回路 1 3 によって生成される電流  $I_F$  の波形を示すグラフである。図 3 5 は、図 1 2 の立ち上がり電流生成回路 1 2 によって生成される電流  $I_R$  の波形を示すグラフである。

【 0 1 1 9 】

図 3 2 に示すように、入力信号  $I_N$  の論理に一致して出力信号  $O_{UT}$  がレベル変換されて出力されている。また、入力信号  $I_N$  の立ち上がりと入力信号  $I_{NB}$  の立ち下がりとにおいては、波形が重なっているが、入力信号  $I_N$  の立ち下がりと入力信号  $I_{NB}$  の立ち上がりとにおいては、波形が重なっていない。このため、図 3 3 に示すように、入力信号  $I_N$  の立ち上がりでは電流  $I_C$  が生成されるが、入力信号  $I_N$  の立ち下がりでは電流  $I_C$  が生成されない。レベルコンバータ回路 1 B は、レベルコンバータ回路 1 A と比較して、2 段増幅回路の構成を変更したので、電流生成回路 1 0 A が動作を開始する前に出力信号  $O_{UT}$  がローレベルに立ち下がることがなくなり、図 3 4 に示すように、電流  $I_F$  が解析通りに生成されている。また、図 3 5 に示すように、入力信号  $I_N$  の立ち上がりにおいて、電流  $I_R$  が生成されている。上述したように、電流生成回路 1 0 A のすべての回路プロック（変化時電流生成回路 1 1、立ち上がり電流生成回路 1 2、及び立ち下がり電流生成回路 1 3）が解析通りに動作することを確認した。

【 産業上の利用可能性 】

【 0 1 2 0 】

以上詳述したように、本発明に係るレベルコンバータ回路によれば、電流生成回路によって生成される電流に対応する電流を増幅回路に印加して、信号レベルを変換するので、第 1 の信号レベルと第 2 の信号レベルとの間の差が大きい場合でも安定な動作が可能である。また、電流生成回路は、入力信号の信号レベルが変化するときのみ制御電流を生成し、入力信号の信号レベルが変化しないときは制御電流を生成しないので、レベルコンバータ回路は低消費電力で動作する。

【 0 1 2 1 】

また、本発明に係るレベルコンバータ回路によれば、上記第 1 及び第 2 の nMOS トランジスタのしきい値電圧を上記レベルコンバータ回路に比較して低下させて、上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第 1 及び第 2 の nMOS トランジスタの基板電位を変化させる制御回路をさらに備えるので、レベルコンバータ回路が上記レベルコンバータ回路に比較して高速に動作する。

【 0 1 2 2 】

またさらに、本発明に係るレベルコンバータ回路によれば、上記制御電流を上記レベルコンバータ回路に比較して増加させるように、上記第 1 及び第 2 の nMOS トランジスタに対してそれぞれ並列に、別の nMOS トランジスタを接続するので、レベルコンバータ回路が上記レベルコンバータ回路に比較して高速に動作する。

【 0 1 2 3 】

またさらに、本発明に係るレベルコンバータ回路によれば、入力信号と入力信号の反転信号とがともにハイレベルである期間が存在しない場合にも、立ち上がり電流生成回路又は立ち下がり電流生成回路が制御電流を生成するので、レベルコンバータ回路は正常に動作する。さらに、外部ノイズ等の外乱により出力信号の信号レベルが変化する場合にも、立ち上がり電流生成回路又は立ち下がり電流生成回路が制御電流を生成するので、レベルコンバータ回路は正常に動作する。

【 符号の説明 】

【 0 1 2 4 】

1 , 1 A , 1 B , 1 0 0 ... レベルコンバータ回路、

1 0 , 1 0 a , 1 0 b , 1 0 c , 1 0 d , 1 0 A ... 電流生成回路、

1 1 ... 変化時電流生成回路、

1 2 ... 立ち上がり電流生成回路、

1 3 ... 立ち下がり電流生成回路、

2 0 ... 電流検出回路、

10

20

30

40

50

3 0 , 3 0 B ... 差動増幅回路、

4 0 ... ソース接地増幅回路、

4 0 B ... プッシュプル型ソース接地増幅回路、

5 0 ... 前処理回路、

2 0 0 ... 低電圧回路ブロック、

3 0 0 ... 高電圧回路ブロック、

4 0 1 ... ファンクションジェネレータ、

4 0 2 ... 試作チップ、

4 0 3 ... オシロスコープ、

5 0 1 ...  $V_c$  1 発生器、

5 0 2 ...  $V_c$  2 発生器、

5 0 3 ... コントローラ、

I V 1 0 1 ... インバータ、

M N 1 1 ~ M N 1 7 , M N 1 1 a , M N 1 2 a , M N 3 1 , M N 3 2 , M N 4 1 ~ M N 4 3 , M N 5 1 , M N 1 0 1 , M N 1 0 2 ... nMOSトランジスタ、

M P 1 1 , M P 2 1 , M P 3 1 ~ M P 3 3 , M P 4 1 ~ M P 4 3 , M P 5 1 , M P 1 0 1 , M P 1 0 2 ... pMOSトランジスタ、

N 1 1 , N 3 1 , N 1 0 1 ... ノード、

T 1 ~ T 9 , T 1 0 1 , T 1 0 2 ... 端子。

10

【図1】

従来技術

【図2】

従来技術

【図3 A】

第1の実施形態

【図3 B】

第1の実施形態

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10B】

【図11A】

【図10A】

【図11B】

【図13A】

【図12】

【図13B】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図26】

【図27】

【図24】

【図25】

【図28】

【図29】

【図 3 0 A】

【図 3 0 B】

【図 3 1 A】

【図 3 1 B】

【図 3 2】

【図 3 4】

【図 3 3】

【図 3 5】

---

フロントページの続き

(72)発明者 大崎 勇士

兵庫県神戸市灘区六甲台町1-1 国立大学法人神戸大学内

(72)発明者 森 俊彦

神奈川県横浜市港北区新横浜三丁目17番地2 友泉新横浜ビル6階 株式会社半導体理工学研究

センター内

審査官 宮島 郁美

(56)参考文献 特開平04-159814 (JP, A)

特開2002-311063 (JP, A)

特開平11-088136 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096