(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-309767

(P2005-309767A)

(43) 公開日 平成17年11月4日(2005.11.4)

(51) Int.CI.<sup>7</sup>

F 1

テーマコード(参考)

G06F 1/26

G06F 1/00 334B

5B011

G06F 1/24

G06F 1/00 350B

5B054

審査請求 未請求 請求項の数 5 O L (全 10 頁)

(21) 出願番号

特願2004-125833 (P2004-125833)

(22) 出願日

平成16年4月21日 (2004.4.21)

(71) 出願人 501431073

ソニー・エリクソン・モバイルコミュニケーションズ株式会社

東京都港区港南1丁目8番15号 Wビル

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100117514

弁理士 佐々木 敏朗

(72) 発明者

斎藤 正敏

東京都港区港南1丁目8番15号 ソニー・エリクソン・モバイルコミュニケーションズ株式会社内

最終頁に続く

(54) 【発明の名称】電源制御装置、電子機器、及び携帯電話端末

## (57) 【要約】

**【課題】** C P Uのリセット解除とパワーオンのタイミングを、アルミ修正によらずに容易に変更可能にする。

**【解決手段】** 電圧検出器 2 0はバッテリ 1 0からの電源供給の開始を検出する。カウンタ 2 2は、電圧検出器 2 0が電源供給の開始を検出すると、R T Cのクロックのカウントを開始する。比較器 2 6は、MONOS 2 3が記憶しているカウント値Mと、カウンタ 2 2のカウント値を比較し、それらが一致したときC P Uリセット解除信号を出力する。比較器 2 7は、MONOS 2 4が記憶しているカウント値Nと、カウンタ 2 2のカウント値を比較し、それらが一致したとき、C P U 1 2のI / O電源を出力するレギュレータ 3 0をパワーオンさせる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

電源供給の開始を検出する検出手段と、

上記検出手段にて電源供給の開始が検出された後に、C P Uのリセット解除のタイミングとC P UへのI / O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、

上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、

上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを有する

ことを特徴とする電源制御装置。

**【請求項 2】**

請求項 1 記載の電源制御装置であって、

上記不揮発性記憶手段は、上記制御値として、C P Uのリセット解除のタイミングを制御するための第1のカウント値と、C P UへのI / O電源供給のタイミングを制御するための第2のカウント値とを記憶しており、

上記タイミング決定手段は、上記検出手段にて電源供給の開始が検出された後に基準クロックのカウントを開始するカウント手段と、上記不揮発性記憶手段が記憶している第1のカウント値と上記カウント手段からのカウント値とを比較する第1の比較手段と、上記不揮発性記憶手段が記憶している第2のカウント値と上記カウント手段からのカウント値とを比較する第2の比較手段とを備え、上記不揮発性記憶手段の第1のカウント値とカウント手段のカウント値との一致を上記第1の比較手段が検出したタイミングを、上記C P Uのリセット解除のタイミングに決定し、上記不揮発性記憶手段の第2のカウント値とカウント手段のカウント値との一致を上記第2の比較手段が検出したタイミングを、上記C P UへのI / O電源供給のタイミングに決定することを特徴とする電源制御装置。

**【請求項 3】**

請求項 1 又は請求項 2 記載の電源制御装置であって、

上記不揮発性記憶手段は、MONOS型のメモリであることを特徴とする電源制御装置。

**【請求項 4】**

C P Uと、

上記C P Uにより動作制御がなされる他の各構成要素と、

電源供給の開始を検出する検出手段と、上記検出手段にて電源供給の開始が検出された後に、C P Uのリセット解除のタイミングとC P UへのI / O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを備えた電源制御回路と有する

ことを特徴とする電子機器。

**【請求項 5】**

無線電話通信を行うための通信手段と、

少なくとも無線電話通信の制御を行うためのC P Uと、

電源供給の開始を検出する検出手段と、上記検出手段にて電源供給の開始が検出された後に、C P Uのリセット解除のタイミングとC P UへのI / O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを備えた電源制御回路とを有する

ことを特徴とする携帯電話端末。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、電源投入時にC P U（中央処理ユニット）のリセット解除を行った後にそのC P U及びその他の各構成に電源を供給する電源制御装置、その電源制御装置を備えた電子機器及び携帯電話端末に関する。

**【背景技術】****【0002】**

従来より、C P Uにより機器の動作制御等を行う電子機器において、例えばバッテリ装着時や電源コンセントの接続時のような電源投入の際には、パワーマネージメントI CがC P Uのリセット解除とレギュレータのパワーオンの制御を行っている。具体的に説明すると、電源投入時のパワーマネージメントI Cは、その電源投入後の電圧値が、予め定められている所定電圧値以上になったことを検出すると、内蔵遅延回路による所定の設定時間経過後にC P Uのリセット解除を行い、さらにレギュレータをパワーオンさせてC P Uの内部メモリ等へのI / O電源を供給するような制御を行っている。

**【0003】**

なお、特開平9-44468号の公開特許公報（特許文献1）には、マイクロコンピュータの動作開始前に、そのマイクロコンピュータにて管理されるバックアップ用のハード回路の回路形態（ロジック）を設定する制御回路が開示されている。すなわちこの制御回路においては、ハード回路内に回路形態設定用の不揮発性メモリが設けられており、電源投入後にマイクロコンピュータが動作を開始する以前に、その不揮発性メモリの記憶データに従ってハード回路の回路形態を設定するようになされている。したがって、この制御回路によれば、マイクロコンピュータの動作開始前にハード回路の回路形態の設定を終了することができ、システムの誤動作防止と高速処理化を両立させることができとなっている。

**【0004】****【特許文献1】特開平9-44468号公報（第1図）****【発明の開示】****【発明が解決しようとする課題】****【0005】**

ところで、従来のパワーマネージメントI Cの場合、内蔵遅延回路の設定時間は固定時間となされており、当該設定時間を変更するためにはI C内のアルミ配線パターンを修正すること（いわゆるアルミ修正）が必要となっている。したがって、例えばC P Uの仕様が変更されリセット解除とパワーオンのタイミングの変更が必要になった場合には、上記パワーマネージメントI Cについてもアルミ修正等の仕様変更が必要となり、それらは機器のコスト増加と開発期間の長期化の要因の一つになっている。

**【0006】**

なお、特許文献1に記載の技術の場合、マイクロコンピュータのリセット解除前に、バックアップ用のハード回路の回路形態の設定を終了することはできても、マイクロコンピュータのリセット解除とパワーオンのタイミングを変更するような用途には使用できない。

**【0007】**

本発明は、このような実情に鑑みて提案されたものであり、C P Uの仕様が変更されリセット解除とパワーオンのタイミングの変更が必要になったような場合であっても、アルミ修正等によらずに、リセット解除とパワーオンのタイミングを容易に変更可能な電源制御装置、電子機器、及び携帯電話端末を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

本発明の電源制御装置は、電源供給の開始を検出する検出手段と、電源供給の開始が検出された後に、C P Uのリセット解除のタイミングとC P UへのI / O電源供給のタイミングのうち少なくとも一方のタイミングを決定するタイミング決定手段と、決定手段にて

10

20

30

40

50

決定されるタイミングを制御するための制御値を記憶する書き換え可能な不揮発性記憶手段と、不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを有することにより、上述した課題を解決する。

#### 【0009】

ここで、不揮発性記憶手段は、制御値として、C P Uのリセット解除のタイミングを制御するための第1のカウント値と、C P UへのI/O電源供給のタイミングを制御するための第2のカウント値とを記憶しており、タイミング決定手段は、電源供給の開始が検出された後に基準クロックのカウントを開始するカウント手段と、不揮発性記憶手段が記憶している第1のカウント値とカウント手段からのカウント値とを比較する第1の比較手段と、不揮発性記憶手段が記憶している第2のカウント値とカウント手段からのカウント値とを比較する第2の比較手段とを備え、不揮発性記憶手段の第1のカウント値とカウント手段のカウント値との一致を第1の比較手段が検出したタイミングを、C P Uのリセット解除のタイミングに決定し、不揮発性記憶手段の第2のカウント値とカウント手段のカウント値との一致を第2の比較手段が検出したタイミングを、C P UへのI/O電源供給のタイミングに決定する。10

#### 【0010】

また、本発明の電子機器と携帯電話端末は、本発明の電源制御装置を搭載したことにより、上述した課題を解決する。

#### 【0011】

すなわち、本発明においては、C P Uのリセット解除のタイミングとC P UへのI/O電源供給のタイミングのうち少なくとも一方のタイミングを決定するための制御値を、書き換え可能な不揮発性記憶手段に記憶させているため、その不揮発性記憶手段が記憶している制御値を書き換えれば、リセット解除のタイミングとI/O電源供給のタイミングの少なくとも一方のタイミングを任意に変更することができるようになる。20

#### 【発明の効果】

#### 【0012】

本発明によれば、不揮発性記憶手段の制御値を書き換えることで、リセット解除のタイミングとI/O電源供給のタイミングのうち少なくとも一方のタイミングを変更できるため、例えば、C P Uの仕様が変更されてリセット解除とパワーオンのタイミングの変更が必要になったような場合であっても、アルミ修正等によらずに、リセット解除とパワーオンのタイミングを容易に変更可能となっている。30

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、図面を参照しながら、本発明の電源制御装置、電子機器及び携帯電話端末が適用される実施形態について説明する。

#### 【0014】

##### 〔パワーマネージメントI Cの構成〕

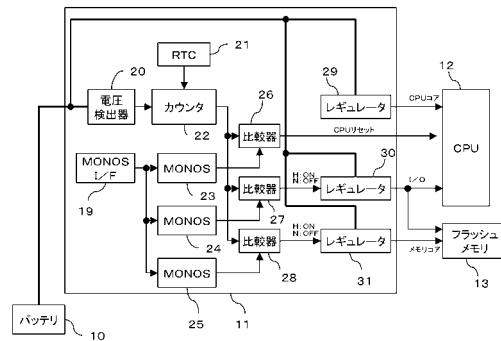

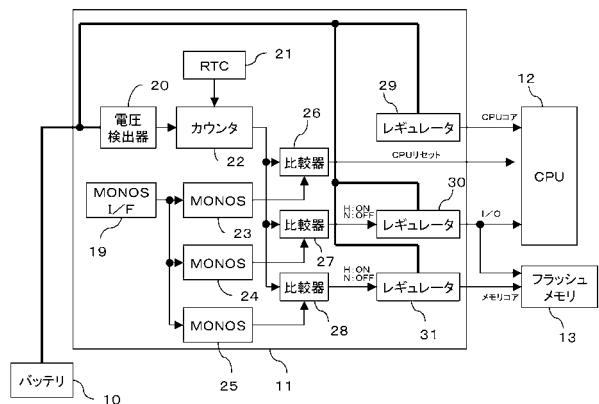

図1には、本発明の電源制御装置の一実施形態であるパワーマネージメントI C 1 1と、バッテリ10の電源が当該パワーマネージメントI C 1 1を介して供給されるC P U 1 2及びフラッシュメモリ13とからなる構成例を示す。また、図2には、図1の各構成要素の動作タイミングチャートを示す。40

#### 【0015】

バッテリ10は、例えば着脱可能な電池であるとする。なお、パワーマネージメントI C 1 1に電源を供給するのは、例えば交流電源を直流電源に変換するA C / D C変換器であっても良い。

#### 【0016】

本実施形態において、上記バッテリ10がパワーマネージメントI C 1 1に接続されると、当該パワーマネージメントI C 1 1の電圧検出器20の入力端子の電圧は、図2の(a)に示すように徐々に上昇することになる。電圧検出器20は、バッテリ10からの電圧値を監視しており、図2の(b)に示すように、当該バッテリ10からの電圧値が所定

の検出電圧に達する前にはL(ロー)レベルとなっており、バッテリ10からの電圧値が所定の検出電圧に達したときH(ハイ)レベルに変化する電圧検出信号を出力する。電圧検出器20からの電圧検出信号はカウンタ22へ送られる。

#### 【0017】

また、第1のレギュレータ29は、上記バッテリ10がパワーマネージメントIC11に接続されると、図2の(c)に示すような所定の電圧のコア電源をCPU12へ供給する。

#### 【0018】

クロック発生器21は、いわゆるRTC(リアルタイムクロック)であり、パワーマネージメントIC11にバッテリ10が接続されると、図2の(d)に示すようにクロック動作を開始する。このクロック発生器21からのクロック信号は、カウンタ22へ送られる。

#### 【0019】

カウンタ22は、図2の(e)に示すように、上記電圧検出器20からの電圧検出信号がHレベルになった後、クロック発生器21からのクロック信号のカウントを開始する。このカウンタ22からのカウント信号は、第1の比較器26、第2の比較器27、第3の比較器28に送られる。

#### 【0020】

第1の比較器26は、書き換え可能な不揮発性メモリである第1のMONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)23が記憶しているカウント値Mと、カウンタ22からのカウント値とを比較し、図2の(f)に示すように、カウンタ22からのカウント値が第1のMONOS23のカウント値Mに達する前にはLレベルとなり、カウンタ22からのカウント値が第1のMONOS23のカウント値Mに達したときにHレベルに変化する比較検出信号を出力する。本実施形態のパワーマネージメントIC11の場合、当該第1の比較器26の比較検出信号がHレベルになったとき、その信号はリセット解除信号としてCPU12へ送られる。すなわち本実施形態において、第1の比較器26の比較検出信号がHレベルになったとき、CPU12のリセット解除が行われる。

#### 【0021】

第2の比較器27は、書き換え可能な不揮発性メモリである第2のMONOS24が記憶しているカウント値N( $N > M$ )と、カウンタ22からのカウント値とを比較し、図2の(g)に示すように、カウンタ22からのカウント値が第2のMONOS24のカウント値Nに達する前にはLレベルとなり、カウンタ22からのカウント値が第2のMONOS24のカウント値Nに達したときにHレベルに変化する比較検出信号を出力する。当該第2の比較器27の比較検出信号がHレベルになったとき、その信号はパワーオン信号として第2のレギュレータ30へ送られる。

#### 【0022】

第2のレギュレータ30は、第2の比較器27からパワーオン信号が供給されると(比較検出信号がHレベルになったとき)、図2の(h)に示すように、所定の電圧のI/O電源をCPU12とフラッシュメモリ13へ供給する。

#### 【0023】

第3の比較器28は、書き換え可能な不揮発性メモリである第3のMONOS25が記憶しているカウント値O( $O > N$ )と、カウンタ22からのカウント値とを比較し、図2の(i)に示すように、カウンタ22からのカウント値が第3のMONOS25のカウント値Oに達する前にはLレベルとなり、カウンタ22からのカウント値が第3のMONOS25のカウント値Oに達したときにHレベルに変化する比較検出信号を出力する。当該第3の比較器28の比較検出信号がHレベルになったとき、その信号はパワーオン信号として第3のレギュレータ31へ送られる。

#### 【0024】

第3のレギュレータ31は、第3の比較器28からパワーオン信号が供給されると(比較検出信号がHレベルになったとき)、図2の(j)に示すように、所定の電圧のコア電

10

20

30

40

50

源をフラッシュメモリ 13 へ供給する。

【0025】

ここで、本実施形態において、第1のMONOS23、第2のMONOS24、第3のMONOS25は、ゲート電極の下の全面にトンネル電流により電子を出し入れすること、或いは、いわゆるホットキャリアを用いて、データを書き換え可能な不揮発性メモリである。本実施形態のパワーマネージメントIC11は、MONOSインターフェイス(I/F)19を介して、上記第1のMONOS23、第2のMONOS24、第3のMONOS25のデータを書き換え可能となっている。

【0026】

したがって、本実施形態のパワーマネージメントIC11において、第1のMONOS23が記憶しているカウント値Mを別の所望の値に書き換えれば、CPUリセット解除のタイミングを所望のタイミングに変更することができ、また、第2のMONOS24が記憶しているカウント値Nを別の所望の値に書き換えれば、CPU12とフラッシュメモリ13へI/O電源を供給するタイミングを所望のタイミングに変更することができ、また、第3のMONOS25が記憶しているカウント値Oを別の所望の値に書き換えれば、フラッシュメモリ13へコア電源を供給するタイミングを所望のタイミングに変更することができる。

【0027】

すなわち、本実施形態のパワーマネージメントIC11によれば、例えばCPU12の仕様が変更されてリセット解除とレギュレータのパワーオンのタイミングの変更が必要になったり、フラッシュメモリの使用が変更されてレギュレータのパワーオンのタイミング変更が必要になった場合であっても、それらCPU12のリセット解除やレギュレータのパワーオンのタイミングを容易に変更可能となっている。

【0028】

なお、上述の図1の例では、第1～第3のMONOS23～25内に、比較器26～28での比較基準となるカウント値を記憶した場合を挙げているが、例えば、第1～第3のMONOS23～25内に、第1の可変カウンタ、第2の可変カウンタ、第3の可変カウンタのそれぞれのカウント設定値を記憶させても良い。この場合のパワーマネージメントICの構成は、図1のカウンタ22を無くし、また、第1～第3の比較器26～28をそれぞれ第1～第3の可変カウンタに代え、それら第1～第3の可変カウンタに対して、RTCのクロックを供給すると共に第1～第3のMONOS23～25からのカウント設定値を供給する構成とすれば良い。すなわちこの例の場合、第1の可変カウンタは、第1のMONOS23により設定されるカウント値Mまでカウントした時点でHレベルとなる信号を出力するものとなされ、第2の可変カウンタは、第2のMONOS24により設定されるカウント値Nまでカウントした時点でHレベルとなる信号を出力するものとなされ、第3の可変カウンタは、第3のMONOS25により設定されるカウント値Oまでカウントした時点でHレベルとなる信号を出力するものとなされる。

【0029】

[本実施形態のパワーマネージメントICの適用例]

本実施形態のパワーマネージメントIC11は、例えばPDA(Personal Digital Assistant)やディジタルカメラ、携帯型や据え置き型のテレビジョン受像機やパーソナルコンピュータ等の各種の電子機器や携帯電話端末等に適用可能である。

【0030】

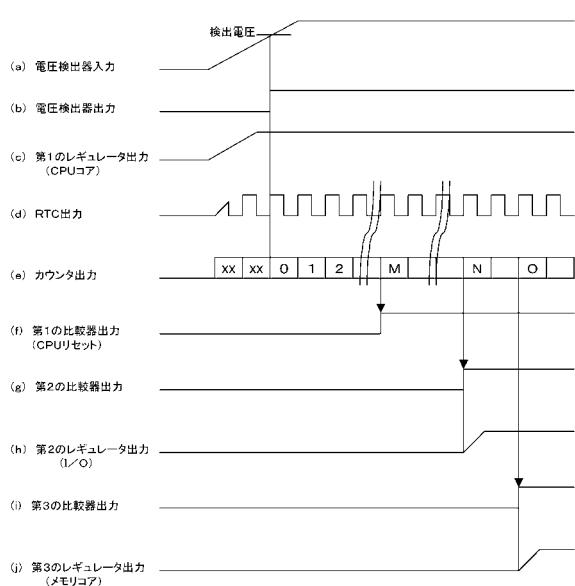

図3には、本実施形態のパワーマネージメントIC11を搭載した携帯電話端末の主要な内部構成を示す。

【0031】

図3において、アンテナ41は、例えば内蔵アンテナであり、信号電波の送受信を行う。RFブロック43は、無線通信を行うための通信回路であり、アンテナ41を介した送受信信号の增幅やレベル調整、RF帯域からベースバンド帯域への周波数変換、或いは、ベースバンド帯域からRF帯域への周波数変換等を行う。

10

20

30

40

50

## 【0032】

D S P (Digital Signal Processor) 47は、信号の変調と復調、スペクトラム拡散と逆拡散、送受信されたデータが通話音声データかそれ以外のデータかの弁別等を行う。なお、通話音声データ以外のデータとは、画像データや、電子メール、プログラムデータ、その他の各種データである。

## 【0033】

受信された通話音声データは、データラインを介してコーデック48へ送られる。コーデック48は、通話音声データを復号化し、その復号化後の音声データをデータラインを介してスピーカ49へ送る。

## 【0034】

スピーカ49は、デジタル／アナログ変換器と増幅器を含み、音声データをデジタル／アナログ変換及び増幅した後、出力する。これにより、通話音声が得られることになる。

## 【0035】

一方、マイクロホン50は、アナログ／デジタル変換器と増幅器を含む。このマイクロホン50を介して入力された通話音声信号は、増幅器により所定のレベルに増幅された後、アナログ／デジタル変換器によりデジタル音声データに変換され、データラインを介してコーデック48へ送られて符号化された後、D S P 47を介してR F ブロック43へ送られる。

## 【0036】

メモリ46は、R O MとR A Mを含む。R O Mは、C P U 12が各部を制御するための制御プログラムや各種の初期設定値、当該携帯電話端末の電話番号、フォントデータ、辞書データ、各種のアプリケーション用のプログラムコード、当該携帯電話端末の識別情報(I D)などを記憶している。このR O Mは、E E P R O Mのような書き換え可能なR O Mを含み、電子メールデータ、ユーザにより設定される電話帳や電子メールアドレス、画像データや着信音データ、文字データ、その他、各種のユーザ設定値等を保存することも可能となされている。なお、図1のフラッシュメモリ13は当該R O Mに含まれていても良い。R A Mは、C P U 12が各種のデータ処理を行う際の作業領域として、随時データを格納する。

## 【0037】

表示部44は、例えば液晶等のディスプレイと、そのディスプレイに画像等を表示させるため駆動回路とを含む。

## 【0038】

操作部45は、携帯電話端末の筐体上に設けられている各種キー・ジョグダイヤルと、それらの操作に応じた操作信号を発生するキー操作信号発生部を有している。

## 【0039】

C P U 12は、制御ラインを介して当該携帯電話端末の各構成要素を制御したり、各種の演算処理を行う。

## 【0040】

パワーマネージメントI C 11は、前述の図1に示した構成を有し、バッテリ10からの電源を各部に供給する。

## 【0041】

その他、図3には図示を省略しているが、本実施形態の携帯電話端末は、音楽の録音や再生を行うための音楽録音再生部、ブラウザ機能、例えば外部メモリ等の外部記憶装置と端末本体とを接続するためのインターフェイス、外部リモートコントローラの接続端子、近距離で様々な情報を無線により通信(赤外線通信等も含む)するための近距離無線通信部、携帯電話端末の現在位置を検出するための測位デバイスであるG P S(Global Positioning System)部などを備えている。

## 【0042】

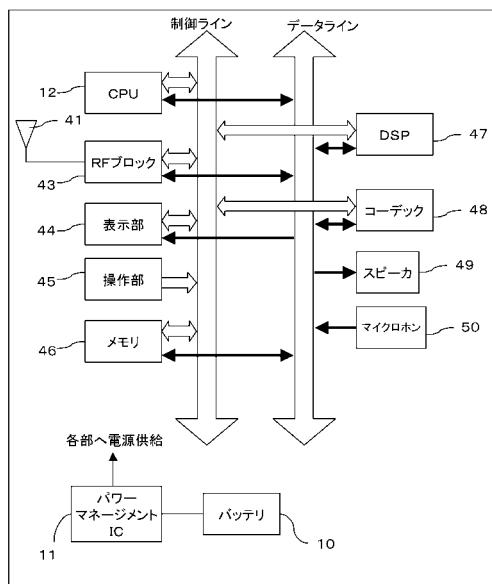

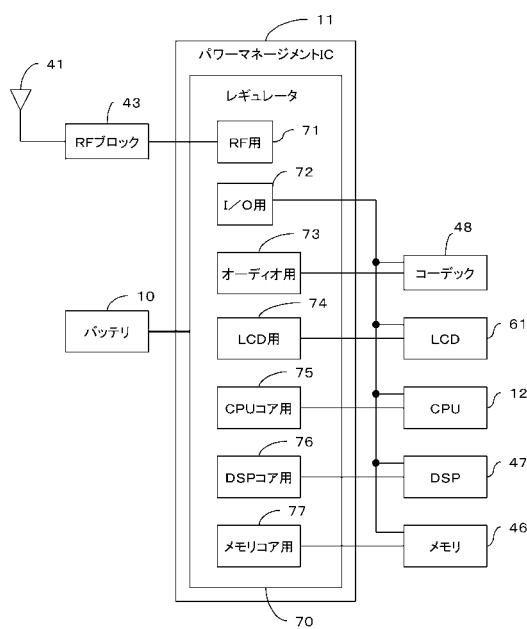

図4には、図3に示した携帯電話端末の各構成要素の中から、本実施形態のパワーマネ

10

20

30

40

50

ージメント I C 1 1 により電源供給がなされる主要な構成要素を抜き出して示す。

【 0 0 4 3 】

この図 4 に示すように、携帯電話端末に適用された場合、パワーマネージメント I C 1 1 内に設けられるレギュレータ 7 0 は、C P U 1 2 へコア電源を供給するための C P U コア用レギュレータ（図 1 の第 1 のレギュレータ 2 9 ）やメモリ 4 6 へコア電源を供給するためのメモリコア用レギュレータ（図 1 の第 3 のレギュレータ 3 1 ）の他に、R F ブロック 4 3 へ電源供給を行うための R F 用レギュレータ 7 1 、コーデック 4 8 へ電源供給を行うためのオーディオ用レギュレータ、表示部 4 4 の L C D 6 1 へ電源供給を行うための L C D 用レギュレータ 7 4 、D S P 4 7 へコア電源を供給するための D S P コア用レギュレータを備えている。また、I / O 電源供給用のレギュレータ（図 1 の第 2 のレギュレータ 3 0 ）は、C P U 1 2 やメモリ 4 6 のみならず、L C D 6 1 やD S P 4 7 へも I / O 電源を供給している。10

【 0 0 4 4 】

そして、この図 4 の例の場合のパワーマネージメント I C 1 1 は、それら各レギュレータへのパワーオンのタイミングを所望のタイミングに設定するための値を記憶した M O N O S を備えていることになる。

【 0 0 4 5 】

なお、上述した実施の形態の説明は、本発明の一例である。このため、本発明は上述した実施の形態に限定されることなく、本発明に係る技術的思想を逸脱しない範囲であれば、設計等に応じて種々の変更が可能であることはもちろんである。20

【 図面の簡単な説明 】

【 0 0 4 6 】

【 図 1 】本発明実施形態のパワーマネージメント I C の内部構成を示すブロック回路図である。

【 図 2 】本実施形態のパワーマネージメント I C の各内部構成要素の動作タイミングチャートである。

【 図 3 】本発明実施の形態のパワーマネージメント I C が搭載された携帯電話端末内部の主要部の構成例を示すブロック回路図である。

【 図 4 】本実施形態の携帯電話端末の各構成要素の中から、本実施形態のパワーマネージメント I C により電源供給がなされる主要な構成要素を抜き出して示すブロック回路図である。30

【 符号の説明 】

【 0 0 4 7 】

1 0 バッテリ、1 1 パワーマネージメント I C 、1 2 C P U 、1 3 フラッシュメモリ、1 9 M O N O S インターフェイス、2 0 電圧検出器、2 1 クロック発生器、2 2 カウンタ、2 3 第 1 の M O N O S 、2 4 第 2 の M O N O S 、2 5 第 3 の M O N O S 、2 6 第 1 の比較器、2 7 第 2 の比較器、2 8 第 3 の比較器、2 9 第 1 のレギュレータ、3 0 第 2 のレギュレータ、3 1 第 3 のレギュレータ、4 1 アンテナ、4 3 R F ブロック、4 4 表示部、4 5 操作部、4 6 メモリ、4 7 D S P 、4 8 コーデック、4 9 スピーカ、5 0 マイクロホン、6 1 L C D 、7 0 レギュレータ、7 1 R F 用レギュレータ、7 2 I / O 用レギュレータ、7 3 オーディオ用レギュレータ、7 4 L C D 用レギュレータ、7 5 C P U コア用レギュレータ、7 6 D S P コア用レギュレータ、7 7 メモリコア用レギュレータ40

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 土山 智令

東京都品川区北品川6丁目7番35号 ソニー株式会社内

Fターム(参考) 5B011 DA06 DC01 EA10 MB11

5B054 AA11 BB01 CC10