(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6067138号

(P6067138)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

HO3M 13/47 (2006.01)

F 1

HO3M 13/47

請求項の数 10 (全 23 頁)

(21) 出願番号 特願2015-553747 (P2015-553747)

(86) (22) 出願日 平成26年1月6日(2014.1.6)

(65) 公表番号 特表2016-504002 (P2016-504002A)

(43) 公表日 平成28年2月8日(2016.2.8)

(86) 國際出願番号 PCT/US2014/010276

(87) 國際公開番号 WO2014/113226

(87) 國際公開日 平成26年7月24日(2014.7.24)

審査請求日 平成27年8月13日(2015.8.13)

(31) 優先権主張番号 13/912,876

(32) 優先日 平成25年6月7日(2013.6.7)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/752,646

(32) 優先日 平成25年1月15日(2013.1.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 391030332

アルカテルルーセント

フランス国、92100・プローニューピ

ャンクール、ルート・ドゥ・ラ・レーヌ・

148/152

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100114915

弁理士 三村 治彦

(74) 代理人 100120363

弁理士 久保田 智樹

(74) 代理人 100125139

弁理士 岡部 洋

最終頁に続く

(54) 【発明の名称】劣化した量子冗長符号化状態のシンドローム

## (57) 【特許請求の範囲】

## 【請求項1】

物理的に処理された量子冗長符号化状態の対応するn個の物理的対象を受け取るn個の入力ポートと、前記物理的に処理された量子冗長符号化状態にある前記n個の物理的対象を出力するn個の出力ポートとを有するデバイスであって、前記n個の物理的対象に前記デバイスを通過させることによって、前記物理的に処理された量子冗長符号化状態のシンドロームのビットを測定するように構成されているデバイスを備えており、

前記デバイスは、前記n個の物理的対象に前記デバイスを前記通過させることによって、前記シンドロームの前記測定されたビットのいくつかに対するパリティ検査ビットを測定するように構成されている、装置。

## 【請求項2】

前記デバイスは、一連の直列接続された測定デバイスを含んでおり、前記測定デバイスは、それぞれが、前記n個の物理的対象を受信および送信するように構成されており、前記シンドロームの前記ビットの中の1つを測定する、または、前記シンドロームの前記測定されたビットのいくつかに対する前記パリティ検査ビットを測定するように構成されている、請求項1に記載の装置。

## 【請求項3】

前記測定デバイスは、それぞれが量子ゲートの量子回路を含む、請求項2に記載の装置。

## 【請求項4】

10

20

前記測定デバイスの真部分集合は、前記シンドロームのそれぞれのビットが前記真部分集合の前記測定デバイスの中の別の1つによって測定されるように、前記シンドロームの前記ビットを測定するように構成されている、請求項2に記載の装置。

【請求項5】

前記シンドロームの前記測定されたビットと前記測定されたパリティ検査ビットとを受け取るように接続されており、前記測定されたパリティ検査ビットと前記シンドロームの前記測定されたビットとに基づいて、前記シンドロームの誤り訂正された値を決定するように構成されているコントローラを更に備えている、請求項4に記載の装置。

【請求項6】

電子コントローラによって生成された前記シンドロームの誤り訂正された値に基づいて、前記物理的に処理された量子冗長符号化状態を誤り訂正するように構成されている誤り訂正モジュールを更に備えている、請求項5に記載の装置。 10

【請求項7】

n量子ビットの物理的状態を受け取り記憶するように接続されている入力レジスタと、1つまたは複数の量子ビットの予めセットされた状態を送信するようにそれが構成されている複数の補助レジスタと、

前記入力レジスタから受け取られた前記物理的状態に基づいて前記予めセットされた状態を変換し、前記物理的状態を出力するように構築されている量子回路と、

それが、前記変換された予めセットされた状態の中の対応する1つを前記量子回路から受け取るように接続され、前記変換された予めセットされた状態の中の前記対応する受け取った1つの1つまたは複数の量子ビットを測定することによって、値を生成するように構成されている複数の検出器と、 20

を備えており、前記量子回路が、前記生成された値が前記物理的状態のシンドロームのビットを測定し、前記生成された値の少なくとも1つが前記シンドロームの前記測定されたビットに対するパリティ検査ビットを測定するように、前記変換された予めセットされた状態を形成するように構成されている、装置。

【請求項8】

前記検出器から前記値を受け取るように構成され、パリティ検査ビットを測定する前記値に基づいて前記シンドロームのビットを測定する前記生成された値の中の1つを誤り訂正するように構成されているコントローラを更に備えている、請求項7に記載の装置。 30

【請求項9】

前記量子回路は、前記変換された予めセットされた状態を直列的に生成するように構成されている、請求項7に記載の装置。

【請求項10】

前記量子回路は、前記予めセットされた状態の中の少なくとも2つを並列的に変換するように構成されている、請求項7に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、2013年1月15日に出願された米国仮特許出願第61/752,646号の利益を主張するものである。 40

【0002】

米国政府は、本発明に関して一括払い方式の実施権(paid-up license)を有しており、更に、情報先端研究プロジェクト活動(IARPA: Intelligence Advanced Research Projects Activity)によって認められた契約第D11PC20165号の条項に規定されているように、限定された状況において、合理的な条件で他者に実施権を付与することを特許権者に要求する権利を有する。

【0003】

本発明は、物理的劣化を経験した可能性のある量子冗長符号化状態(quantum redundant

50

cy coded states) のシンドロームを測定することに関する。

【背景技術】

【0004】

このセクションでは、本発明のよりよい理解を容易にするのに役立ち得る態様について紹介する。従って、このセクションの言説は、その観点から読まれるべきであって、従来技術に何が存在しているのか、または従来技術に何が存在しないのかに関する承認として理解されるべきではない。

【0005】

もつれた (entangled) 量子状態を搬送する情報はいくつかのタイプの物理的処理の間に誤りを生じやすいため、情報がそのようなもつれた量子状態によって搬送される量子コンピュータによって、誤り訂正 (error-correction) が用いられ得る蓋然性が高い。そのような量子コンピュータでは、誤り訂正是、量子安定化群 (stabilizer groups) に基づいて、もつれた量子状態を搬送する情報の量子冗長符号化を含み得る。

10

【0006】

量子冗長符号化は、個々の初期量子状態をコヒーレントに混合、すなわち、状態を搬送する情報と予めセットされた量子状態とをコヒーレントに混合して、対応する量子冗長符号化状態を生成することを含む。このコヒーレントな混合が、典型的には、それぞれの初期量子状態と複数の量子ビットを有する予めセットされた量子状態 (量子ビット) とのエンタングルメントを生じさせる。量子冗長符号化の後で、物理的処理が、量子冗長符号化状態に誤りを生成し得る。この物理的処理は、例えば、量子冗長符号化状態の物理的通信チャネル経由での送信、および / または、量子冗長符号化状態の記憶を含み得る。

20

【0007】

物理的処理の後で、物理的に処理された量子冗長符号化状態に、誤り訂正処理がなされ得る。誤り訂正のプロセスは、典型的には、物理的に処理された量子冗長符号化状態のシンドロームの値を測定することを含む。シンドロームの測定された値は、物理的処理により、対応する量子冗長符号化状態に誤りが生じたかどうかを示す。典型的には、測定された値は、物理的処理によって生じた蓋然性が最も高い誤りを識別するのに用いられる。シンドロームの測定された値が誤りの存在を示す場合には、誤り訂正プロセスが、前記物理的処理によって生じた蓋然性が最も高い誤りを反転させるために、物理的に処理された冗長符号化量子状態に対して量子演算 (quantum operation) の適用を含み得る。適用される量子演算の形態は、物理的に処理された量子冗長符号化状態のシンドロームから決定される。通常は、そのような誤り訂正処理によって訂正可能な誤りの集合は、物理的処理が生じさせる可能性があるすべての誤りの集合の真部分集合 (proper subset) である。

30

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許出願第13/912,654号

【非特許文献】

【0009】

【非特許文献1】Frank Gaitan, Quantum Error Correction and Fault Tolerant Quantum Computing, Taylor & Francis 2008

40

【非特許文献2】Micael A. Nielson and Isaac L. Chuang, Quantum Computation and Quantum Information, Cambridge 2000

【発明の概要】

【0010】

いくつかの実施形態は、例えば劣化したなど、物理的に処理された量子冗長符号化状態のシンドロームの決定が、潜在的な誤りに対してより堅牢であるような装置または方法を提供する。

50

## 【0011】

いくつかの実施形態では、第1の装置は、n個の入力ポートとn個の出力ポートとを有するデバイスを含む。n個の入力ポートは、物理的に処理された量子冗長符号化状態のn個の対応する物理的対象を受け取るように構成されている。n個の出力ポートは、物理的に処理された量子冗長符号化状態にあるn個の物理的対象を出力するように構成されている。このデバイスは、n個の物理的対象を通過させることによって、物理的に処理された量子冗長符号化状態のシンドロームのビットを測定するように構成されている。このデバイスは、n個の物理的対象を通過させることによって、シンドロームの測定されたビットのいくつかに対するパリティ検査ビットを測定するように構成されている。

## 【0012】

第1の装置のいくつかの実施形態では、デバイスは、一連の直列接続された測定デバイスを含み得る。測定デバイスは、それぞれが、n個の物理的対象を受信および送信するように構成されており、シンドロームのビットの中の1つを測定するか、または、シンドロームの測定されたビットのいくつかに対するパリティ検査ビットを測定するように、構成されている。いくつかのそのような実施形態では、測定デバイスの少なくとも1つが、パリティ検査ビットを測定するように構成されている。この段落のいずれの実施形態においても、測定デバイスは、それぞれが、量子ゲートの量子回路を含み得る。この段落のいずれの実施形態においても、測定デバイスの真部分集合は、シンドロームのそれぞれのビットがこの真部分集合の測定デバイスの中の別の1つによって測定されるように、シンドロームのビットを測定するように構成され得る。

10

## 【0013】

第1の装置の上述した実施形態は、どれもが、シンドロームの測定されたビットと測定されたパリティ検査ビットとを受け取るように接続されている電子コントローラを更に含み得る。この電子コントローラは、測定されたパリティ検査ビットとシンドロームの測定されたビットとに基づいて、シンドロームの誤り訂正された値を決定するように構成されている。いくつかのそのような実施形態では、このコントローラは、線形ブロック符号に従って測定デバイスの真部分集合によって測定されたシンドロームを誤り訂正するように、構成され得る。いくつかのそのような実施形態では、第1の装置は、電子コントローラによって生成されたシンドロームの誤り訂正された値に基づいて、物理的に処理された量子冗長符号化状態を誤り訂正するように構成されている誤り訂正モジュールを含み得る。

20

## 【0014】

いくつかの実施形態では、第2の装置は、n量子ビットの物理的状態を受け取り記憶するように接続されている入力レジスタと、複数の補助レジスタと、量子回路と、複数の検出器とを含む。複数の補助レジスタは、それぞれが、1つまたは複数の量子ビットの予めセットされた状態を伝達するように構成されている。量子回路は、入力レジスタから受け取られた物理的状態に基づいて予めセットされた状態を変換し、物理的状態を出力レジスタに出力するように構築されている。複数の検出器は、それぞれが、変換された予めセットされた状態の中の対応する1つを量子回路から受け取るように接続され、変換された予めセットされた状態の中の対応する受け取った1つの1つまたは複数の量子ビットを測定することによって、値を生成するように構成されている。量子回路は、生成された値が物理的状態のシンドロームのビットを測定するように、そして、生成された値の少なくとも1つがシンドロームの測定されたビットに対するパリティ検査ビットを測定するように、変換された状態を形成するように構成されている。

30

## 【0015】

第2の装置のいくつかの実施形態は、検出器から値を受け取るように構成されたコントローラを更に含み得る。このコントローラは、また、パリティ検査ビットを測定する値に基づいてシンドロームのビットを測定する生成された値の中の1つを誤り訂正するように構成され得る。いくつかのそのような実施形態は、出力レジスタから物理的状態を受け取り、受け取られた物理的状態を、電子コントローラによって生成されたシンドロームの誤り訂正された値に基づいて誤り訂正するように構成されている誤り訂正モジュールを、更

40

50

に含み得る。

【0016】

第2の装置のいくつかの実施形態では、量子回路は、変換された量子状態を直列的に生成するように構成されている。

【0017】

第2の装置のいくつかの実施形態では、量子回路は、予めセットされた量子状態の中の少なくとも2つを並列的に変換するように構成されている。

【0018】

別の実施形態では、方法は、冗長符号化された多量子ビット (multi-qubit) 状態を第1のハードウェア・デバイスを通過するように送信して、冗長符号化された多量子ビット状態のシンドロームを測定するステップを含む。この方法は、また、冗長符号化された多量子ビット状態を第2のハードウェア・デバイスを通過するように送信して、シンドロームの測定のために1つまたは複数のパリティ検査ビットを測定するステップも含む。

10

【0019】

この方法のいくつかの実施形態では、冗長符号化された多量子ビット状態を第1のハードウェア・デバイスを通過するように送信する動作は、冗長符号化された多量子ビット状態を量子ゲート回路のシーケンスを通過するように送信することを含み得る。いくつかのそのような実施形態では、冗長符号化された多量子ビット状態を第2のハードウェア・デバイスを通過するように送信する動作は、冗長符号化された多量子ビット状態を量子ゲート回路のシーケンスを通過するように送信することを含み得る。ただし、第1および第2のシーケンスは共通要素を有しない (disjoint)。

20

【0020】

方法の上述した実施形態のいずれも、1つまたは複数のパリティ検査ビットの測定された値に基づいて、シンドロームの複数の測定されたビットの少なくとも1つを訂正することにより、測定されたシンドロームを誤り訂正するステップを更に含み得る。いくつかのそのような実施形態は、測定され誤り訂正されたシンドロームに基づいて、量子回路における冗長符号化された多量子ビット状態を誤り訂正するステップを、更に含み得る。

【0021】

他の実施形態は、発明の概要、図面、および/または発明を実施するための形態に記載されているように、他の装置または装置を動作させる方法に及び得る。

30

【図面の簡単な説明】

【0022】

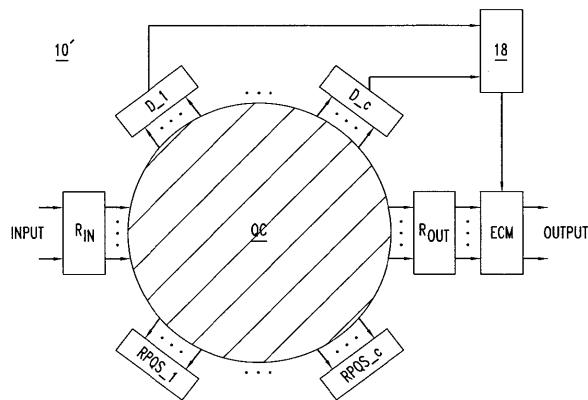

【図1】誤りを生成し得る物理的処理を経験した量子冗長符号化状態のシンドロームを測定するように構成された装置のブロック図である。

【図2】例えば、図1のハードウェア測定デバイスの1つを形成し得る量子回路のブロック図である。

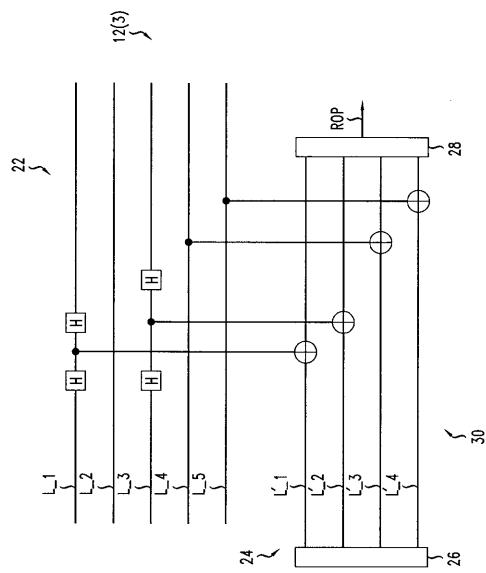

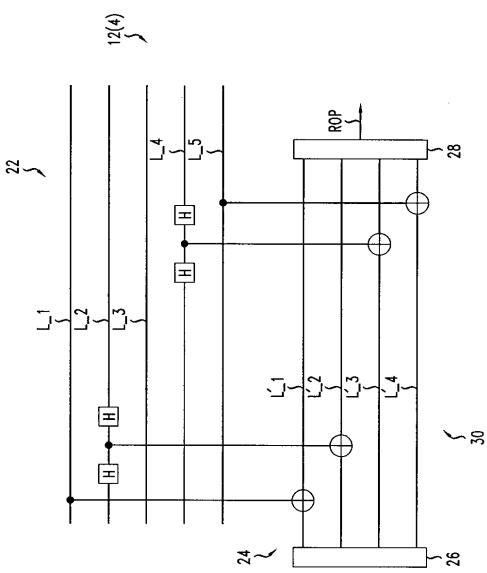

【図3】安定化群Gの基底要素 (basis elements) のための量子回路の実例のブロック図であり、ある量子冗長符号化方式のためのシンドロームのビットを直接的に測定するための図1のハードウェア測定デバイスの実施形態である。

【図4】安定化群Gの基底要素のための量子回路の実例のブロック図であり、ある量子冗長符号化方式のためのシンドロームのビットを直接的に測定するための図1のハードウェア測定デバイスの実施形態である。

40

【図5】安定化群Gの基底要素のための量子回路の実例のブロック図であり、ある量子冗長符号化方式のためのシンドロームのビットを直接的に測定するための図1のハードウェア測定デバイスの実施形態である。

【図6】安定化群Gの基底要素のための量子回路の実例のブロック図であり、ある量子冗長符号化方式のためのシンドロームのビットを直接的に測定するための図1のハードウェア測定デバイスの実施形態である。

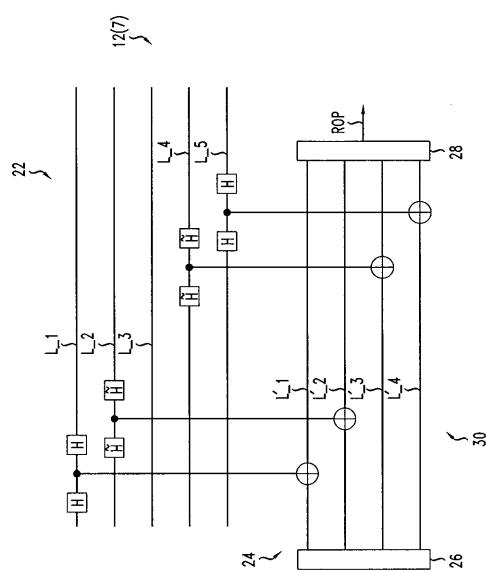

【図7】同じ安定化群Gの非基底要素のための量子回路の実例のブロック図であり、同じ量子冗長符号化方式における測定されたシンドロームのためのパリティ・ビットを直接的

50

に測定するための図 1 のハードウェア測定デバイスの実施形態である。

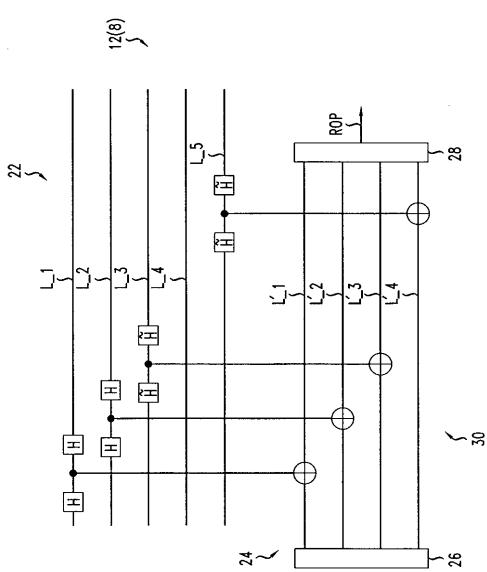

【図 8】同じ安定化群 G の非基底要素のための量子回路の実例のブロック図であり、同じ量子冗長符号化方式における測定されたシンドロームのためのパリティ・ビットを直接的に測定するための図 1 のハードウェア測定デバイスの実施形態である。

【図 9】量子回路と予めセットされた量子状態の集合とを用いて、受け取られた量子冗長符号化状態の測定されたシンドロームの誤り訂正を提供する装置を図解するブロック図である。

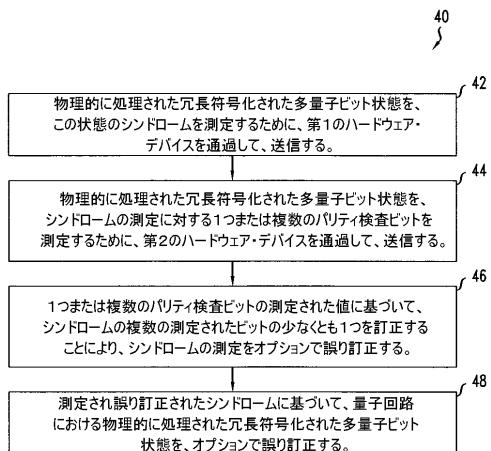

【図 10】例えば図 1 および図 9 の装置において物理的に処理された冗長符号化された多量子ビット状態を取り扱う方法を図解する流れ図である。

【発明を実施するための形態】

10

【0023】

図面および本文では、同様の参照番号が、機能的および / または構造的に同様の要素を指している。

図面では、いくつかの形状の相対的寸法が、そこにおける装置をより明瞭に図解するために誇張されている場合があり得る。

本明細書では、様々な実施形態が、図面と発明を実施するための形態とによってより完全に説明されている。しかし、本発明は様々な形態で実施され得るのであって、図面と発明を実施するための形態とにおいて説明されている特定の実施形態には限定されない。

【0024】

Frank Gaitanによる「Quantum Error Correction and Fault Tolerant Quantum Computing」(Taylor & Francis 2008)ならびにMicahel A. NielsenおよびIsaac L. Chuangによる「Quantum Computation and Quantum Information」(Cambridge 2000)の2つの書籍は、それらの全体を、参照により本明細書に組み入れる。

20

【0025】

2013年1月15日に出願された米国仮特許出願第 61/752,646 号は、その全体を参照により本明細書に組み入れる。

【0026】

30

本明細書では、状態という単語は、特に断らない限り、抽象的な条件ではなく物理的実体 (physical entity) を指す。例えば、物理的対象の n 量子ビット状態 (n-qubit state) とは、例えば、適切に準備された n 個のイオンの集まりなど、物理的対象の物理的実体を指す。状態の物理的実体は、生成され、記憶され、輸送され、または測定され得るのであって、例えば、n 量子ビットの表現を搬送し得る。

【0027】

既に述べたように、物理的に処理された量子冗長符号化状態のシンドロームに基づく誤り訂正方式が、いくつか存在する。シンドロームは、バイナリ値を取る複数成分のベクトルであり、そのベクトルの値は、そのような状態における可能性のある誤りの集合から、例えばそのような状態における最も蓋然性の高い誤りなど、蓋然性の高い特定の誤りを識別する。例えば、シンドロームは、誤りが单一量子ビットの誤り (single qubit errors) であるときには、そのような物理的に処理された量子冗長符号化状態への誤りを識別するのに十分であり得る。すなわち、シンドロームの値は、量子冗長符号化状態の量子ビットの予め選択された数の中の 1 つに誤りがあるという仮定の下で、誤りを識別するのに十分であり得る。シンドロームの決定する値に基づいて、この誤り訂正処理が、物理的に処理された量子冗長符号化状態に量子ゲートの量子回路を通過させることにより、識別された最も蓋然性の高い誤りを反転させ得る。

40

【0028】

物理的に処理された量子冗長符号化状態のシンドロームの値を不正確に識別する決定がなされるときには、誤り訂正のためのこの方式は失敗することが多い。また、シンドロームの値を測定する多くのハードウェア・デバイスは、誤った値を提供する傾向を有してい

50

るが、その理由は、ハードウェア・デバイスが、誤りを生じる傾向を有する初等量子ゲートの量子回路に基づいているからである。よって、シンドロームの決定の信頼性を向上させることで、シンドロームの決定された値に基づく誤り訂正のパフォーマンスを向上させることが可能である。

【0029】

シンドロームの値の決定の信頼性を向上させるためのある方式は、物理的に処理された量子冗長符号化状態に基づいてシンドロームの値の測定の集合を作成するステップと、その状態に対するシンドロームの値をその集合の値の中で最も頻繁に測定されるものであると定義するステップとを含む。例えば、値の中で最も頻繁に測定されるものは、多数決ルールによって決定され得る。多数決ルールによると、決定される値は、ほとんどの時間で、物理的に処理された量子冗長符号化状態に対して測定される値であり得る。本発明の発明者は、この方式がシンドロームの決定における誤りの確率を低下させると考えているが、同時に、本発明の発明者は、この方式が、典型的には、そのような誤りの発生を僅かに低下させるために大量の測定ハードウェアを用いる、とも考えている。

10

【0030】

装置および方法の様々な実施形態が、物理的に処理された量子冗長符号化状態に対するシンドロームの値の決定の信頼性を向上させる。向上した信頼性は、シンドロームの複数回の測定を含む上述の方法によって得られる信頼性よりも高く、および／または、より少ない測定ハードウェアを用いて、シンドロームの複数回の測定を含む方法と同じ信頼性でシンドロームの値を決定することができる。

20

【0031】

図1は、物理的に処理された量子冗長符号化状態のシンドロームを決定するように構成されている装置10を図解している。量子冗長符号化状態はn個の物理的対象を有しており、それらの物理的対象は、それぞれが、情報の対応する単一の測定可能な量子ビットを搬送する。量子冗長符号化状態は、(n-k)個の物理的対象の予め選択された量子状態と情報のk量子ビットを搬送する初期の量子状態とをコヒーレントに混合することによって、生成される。量子冗長符号化状態の以前の物理的処理が、その状態に誤りを生じさせている可能性がある。

【0032】

様々な量子状態において、情報の個々の量子ビットを搬送する物理的対象は、例えば、光子、閉じ込められたイオン、閉じ込められた原子、および／または電荷キャリアの分数量子ホール効果ドロップレットのエッジもしくは他の励起など、様々な形態を取り得る。当業者であれば、どのようにして、そのような物理的対象を作成するか、そのような物理的対象上の情報を量子符号化するか、そのような量子状態をコヒーレントに混合するか、そしてそのような量子状態に記憶されている情報を読み出すかを理解するであろう。そのような機能を実行するように構成されているいくつかのそのような方法および装置が、既に組み入れられたFrank Gaitanによる書籍、および／または、既に組み入れられたMicahel A. Nielsen他による書籍に記載されているであろう。

30

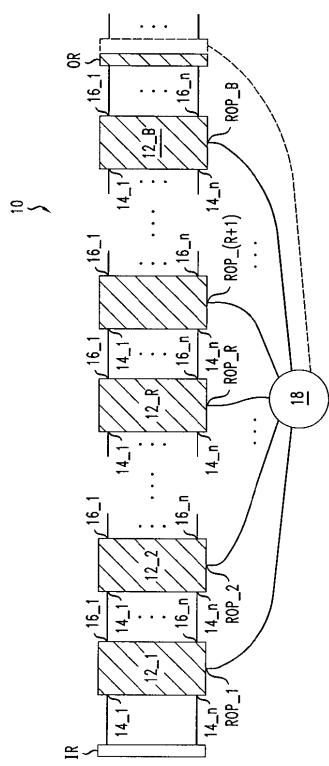

【0033】

図1では、装置10は、ある量子状態のための入力レジスタIRと、ある量子状態のための出力レジスタORとを含む。入力レジスタIRは、n量子ビットの物理的に処理された量子冗長符号化状態のn個の物理的対象を、受け取って記憶することができる。出力レジスタは、装置10における処理の後で、同じ受け取られた状態のn個の物理的対象を記憶し送信するように構成されている。

40

【0034】

装置10は、一連のハードウェア測定デバイス12\_1、…、12\_Bを有している。それぞれのハードウェア測定デバイス12\_1～12\_Bは、n個の入力ポート14\_1～14\_nの第1のアレイと、n個の出力ポート16\_1～16\_nの第2のアレイとを有する。ハードウェア測定デバイスのR番目である12\_Rの中間的な出力ポート16\_1～16\_nは、1対1の態様で、シーケンスにおけるハードウェア測定デバイスの

50

次の1つである $12_{-}(R+1)$ の中間的な入力ポート $14_{-}1 \sim 14_{-}n$ と接続する。このシーケンスは、このシーケンスの第1のハードウェア測定デバイス $12_{-}1$ の入力ポート $14_{-}1 \sim 14_{-}n$ を経由して、入力レジスタIRから物理的に処理された量子冗長符号化状態のn個の物理的対象を受け取り、このシーケンスの最後のハードウェア測定デバイス $12_{-}B$ の出力ポート $16_{-}1 \sim 16_{-}n$ を経由して、出力レジスタORへ前記物理的対象を送信する。

#### 【0035】

このシーケンスでは、それぞれのハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ は、バイナリ値を測定するように構成されており、このバイナリ値は、

a) 装置10によって入力ポート $14_{-}1 \sim 14_{-}n$ において受け取られた、物理的に処理された量子冗長符号化状態のシンドロームの対応するビットか、または

b) ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の中の他のものが測定するように構成されている同じシンドロームに対するパリティ検査ビットか、のいずれかを示す。

ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の1つまたは複数が、シンドロームのパリティ検査ビットを測定し、ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の中の他のものが、シンドロームのビットを測定する。いくつかの実施形態では、パリティ検査ビットのそのような測定は、シンドロームの測定された値の複数のパリティ検査をサポートし得る。いくつかの実施形態では、測定は、シーケンスのハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の少なくとも1つによるシンドロームのそれぞれのビットの測定を含み得る。異なる実施形態では、シンドロームの特定のビットおよび/またはその測定のための特定のパリティ検査ビットの測定は、シーケンスにおける異なる位置に配置されているハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の中のいくつかによって実行され得る。

#### 【0036】

装置10は、また、電子コントローラ18を含むが、この電子コントローラ18は、シンドロームの測定されたビットとその測定されたパリティ検査とを、ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ から受け取るように構成されている。実際に、それぞれのハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ は、結果出力ポートROP\_1 ~ ROP\_Bを有し、そこから、シンドロームのそのようなパリティ検査ビットまたは通常ビットの測定された値がコントローラ18に送信される。電子コントローラ18は、ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の結果出力ポートROP\_1 ~ ROP\_Bから受け取られる測定されたビット値に基づいて、物理的に処理され受け取られた量子冗長符号化状態のシンドロームに対する値を決定する。

#### 【0037】

電子コントローラ18は、シンドロームのビットの前記測定に対する測定され受け取られたパリティ検査ビットに基づいて、シンドロームのビットの受け取られた測定に、誤り訂正を適用する。例えば、誤り訂正された値は、ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の中のいくつかによるシンドロームのそれぞれのビットの直接的な測定と、ハードウェア測定デバイス $12_{-}1 \sim 12_{-}B$ の残りのものによるシンドロームのビットの測定された値に対する1つまたは複数のパリティ検査ビットの直接的な測定とに基づき得る。

#### 【0038】

そのような実施形態では、電子コントローラ18は、また、例えば線形ブロック符号または組織的な線形ブロック符号(systematic linear block code)に基づく線形冗長符号化の誤り訂正を経由して、シンドロームのビットの測定された値を誤り訂正し得る。そのような方法では、電子コントローラ18は、シンドロームを、バイナリ情報ベクトルとして扱い得る。次に、コントローラは、シンドロームを識別するために、シンドロームの測定された値から、すなわち測定されたパリティ検査ビットに基づいて、従来型の技術を適用し得る。シンドロームの測定された値に基づいて、コントローラ18は、例えば単一ビットの誤りなど、シンドロームの測定された値における最も蓋然性の高い誤りなどを識別して、シンドロームの測定された値における誤りを訂正することができる。

#### 【0039】

10

20

30

40

50

装置 10 のいくつかの実施形態では、それぞれのハードウェア測定デバイス 12\_1 ~ 12\_B は、初等量子ゲートの量子回路を含む。ハードウェア測定デバイス 12\_1 ~ 12\_B の中の異なるものにおいては、量子回路が異なり得る。特に、それぞれのハードウェア測定デバイス 12\_1 ~ 12\_B は、シンドロームの対応するビットまたは測定されたシンドロームのパリティ検査ビットを測定するように構成された量子回路を有している。

#### 【0040】

いくつかの実施形態では、それぞれのハードウェア測定デバイス 12\_1 ~ 12\_B は、量子ゲートの対応する量子回路を含む。それぞれの量子回路は、量子冗長符号化方式のための安定化群の要素に対応し、安定化群のその要素が、ハードウェア測定デバイス 12\_1 ~ 12\_B の結果出力ポート ROP\_1 ~ ROP\_B におけるビット出力のタイプを定義する。

#### 【0041】

ハードウェア測定デバイス 12\_1 ~ 12\_B のそのような実施形態の記述は、2つの状態すなわち |0> および |1> を有するスピンとして、量子ビットの表現を経由する単純なものである。そのような表現では、初期量子状態と量子冗長符号化状態とは、多重スピン状態の複素重ね合わせ (complex superpositions) として表現される。それぞれの初期量子状態は、k 個のそのようなスピンの状態の複素重ね合わせである。それぞれの量子冗長符号化状態は、n 個のそのようなスピンの状態の複素重ね合わせである。ここで、p 個のスピンの状態は、基本的な 2 状態スピンの直積空間 (direct product space) における状態である。複素重ね合わせとは、そのような直積状態の和であり、その場合に、和のそれぞれの状態は、複素因数によって重み付けがなされている。

#### 【0042】

このようなスピン表現においては、量子冗長符号化状態の処理は、対応する n スピン状態に対する行列の適用によって表現され得る。それらの行列は、集合 V の  $2 \times 2$  行列の直積の和として書くことができる。集合 V は、 $2 \times 2$  の単位行列および  $2 \times 2$  のパウリ行列、すなわち、I、x、y および z を含む。実際に、量子冗長符号化状態の物理的処理は基本的な誤りを生じ得るが、その基本的な誤りは、V の  $2 \times 2$  行列の n 次元直積空間における演算子 (operator) の作用によって表現可能である。

#### 【0043】

更に、V の  $2 \times 2$  行列と 2 成分のバイナリ・ベクトルとの間には、1 対 1 対応が存在する。この対応は、図 1 のハードウェア測定デバイス 12\_1 ~ 12\_B のための図解されている実施形態の量子回路の記述を簡略化する。対応は、次のように定義される。

$$\begin{aligned} I & < - > 0, 0; \\ x & < - > 1, 0; \\ z & < - > 0, 1; \text{ および} \\ y & < - > 1, 1 \end{aligned}$$

$2 \times 2$  のパウリ行列が次のように定義されることは、広く知られている。

#### 【0044】

##### 【数 1】

$$\sigma_x = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}, \sigma_y = \begin{bmatrix} 0 & -i \\ i & 0 \end{bmatrix}, \text{ および } \sigma_z = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$$

上述した対応は、2 次元のバイナリ・ベクトルの空間から集合 V への関数 U を定義する。関数 U は、次のように定義される。

$$\begin{aligned} U(0, 0) &= I, \\ U(1, 0) &= x, \\ U(0, 1) &= z, \text{ および} \\ U(1, 1) &= y \end{aligned}$$

10

20

30

40

50

関数  $U$  は、基本誤り演算子と  $2^n$  次元バイナリ・ベクトルとの間の対応の単純な記述を提供する。なお、 $2^n$  次元バイナリ・ベクトルとは、それぞれの  $a_{i,j}$  が  $\{0, 1\}$  に含まれる ( $a_{1,1}, a_{1,2}, a_{2,1}, a_{2,2}, \dots, a_{n,1}, a_{n,2}$ ) という形式のベクトルである。それぞれの基本誤り演算子  $E$  は、ある  $2^n$  次元バイナリ・ベクトル ( $a_{1,1}, a_{1,2}, \dots, a_{n,1}, a_{n,2}$ ) に対して、次の形式を有する。

【0045】

【数2】

$$U(a_{11}, a_{12}) \otimes \dots \otimes U(a_{n1}, a_{n2})$$

よって、対応は次のように定義される。

10

【0046】

【数3】

$$E = U(a_{11}, a_{12}) \otimes \dots \otimes U(a_{n1}, a_{n2}) \leftrightarrow (a_{11}, a_{12}, \dots, a_{n1}, a_{n2})$$

この対応を更に例証するために、 $n = 3$  および 4 の場合の 2 つの例が、以下に示されている。

誤り

【0047】

【数4】

$$\sigma_x \otimes I \otimes \sigma_z = U(1, 0) \otimes U(0, 0) \otimes U(0, 1) \leftrightarrow (1, 0, 0, 0, 0, 1)$$

20

誤り

【0048】

【数5】

$$I \otimes \sigma_z \otimes \sigma_x \otimes \sigma_y = U(0, 0) \otimes U(0, 1) \otimes U(1, 0) \otimes U(1, 1) \leftrightarrow (0, 0, 0, 1, 1, 0, 1, 1)$$

上述した対応は、また、基本誤り演算子である安定化群の要素と  $2^n$  次元バイナリ・ベクトルの部分集合との間の対応も与える。特に、量子冗長符号化方式のための安定化群の各要素  $g_i$  は、 $2^n$  次元バイナリ・ベクトル ( $a_{1,1}(i), a_{1,2}(i), \dots, a_{n,1}(i), a_{n,2}(i)$ ) に対応し、これに対する要素  $g_i$  は次の通りである。

30

【0049】

【数6】

$$g_i = U(a_{11}(i), a_{12}(i)) \otimes \dots \otimes U(a_{n1}(i), a_{n2}(i))$$

【0050】

要素  $g_i$  に対応する  $2^n$  次元バイナリ・ベクトル ( $a_{1,1}(i), a_{1,2}(i), \dots, a_{n,1}(i), a_{n,2}(i)$ ) は、また、安定化群の表現を形成する。この表現で、群の演算は、対応する  $2^n$  次元バイナリ・ベクトルのバイナリ加算である。特に、群の要素  $g_m = g_i \times g_i$  は、次の数式によって表現される。

$$(a_{1,1}(m), a_{1,2}(m), \dots, a_{n,1}(m), a_{n,2}(m)) =$$

40

$$(a_{1,1}(i) + a_{1,1}(j), a_{1,2}(i) + a_{1,2}(j), \dots, a_{n,1}(i) + a_{n,1}(j), a_{n,2}(i) + a_{n,2}(j))$$

この表現は、安定化群それ自体がそうであるように、可換 (abelian) である。

【0051】

当業者であれば、選択された量子冗長符号化方式から、安定化群を容易に決定することができるであろう。量子冗長符号化方式とその安定化群との例に関するいくつかの説明は、既に本明細書に組み入れられ Frank Gaitan による書籍および Michael A. Nielsen 他による書籍において見いだされるであろう。

【0052】

安定化群の基底要素は、物理的に処理された量子冗長符号化状態のシンドロームを直接

50

的に測定するのに用いることが可能な初等量子ゲートの量子回路を記述する。安定化群の他の要素は、そのような物理的に処理された量子冗長符号化状態のシンドロームの測定された値に対するパリティ検査ビットを直接的に測定するのに用いることが可能な初等量子ゲートの量子回路を記述する。以下では、そのような量子回路に関する説明は、上述した対応に基づく。

#### 【0053】

特に、安定化群のそれぞれの基底要素  $g_j$  が、物理的に処理された量子冗長符号化状態のシンドロームの対応するビット  $s_j$  を測定するように構成された初等量子ゲートの量子回路を定義する。シンドロームのビット  $s_j$  を測定するために、物理的に処理された量子冗長符号化状態は、安定化群の対応する基底要素  $g_j$  に対する量子回路を通過させられる。よって、シンドロームのそれぞれのビットは、物理的に処理された量子冗長符号化状態に、そのような量子回路の直列配列 (series) を通過させることによって測定され得るが、これは、その直列配列が、安定化群のそれぞれの基底要素に対する少なくとも 1 つのそのような量子回路を含む場合である。

10

#### 【0054】

安定化群の他の要素  $g_q$  は、シンドロームの測定された値のための対応するパリティ検査ビット  $p_q$  を測定するように構成された初等量子ゲートの量子回路を定義する。パリティ検査ビット  $p_q$  を測定するために、物理的に処理された量子冗長符号化状態が、安定化群の対応する要素  $g_q$  に対する量子回路を通過させられる。例えば、シンドロームの測定されたビット  $s_f$  および  $s_h$  に対するパリティ検査ビットを決定するためには、物理的に処理された量子冗長符号化状態が、 $g_q = g_f \times g_h$  に対する量子回路を通過させられる。ここで、 $g_f$  は、シンドロームのビット  $s_f$  を測定するように構成された量子回路に對応する安定化群の基底要素であり、 $g_h$  は、シンドロームのビット  $s_h$  を測定するように構成された量子回路に對応する安定化群の基底要素である。最後に、「 $\times$ 」は、安定化群の乗算である。

20

#### 【0055】

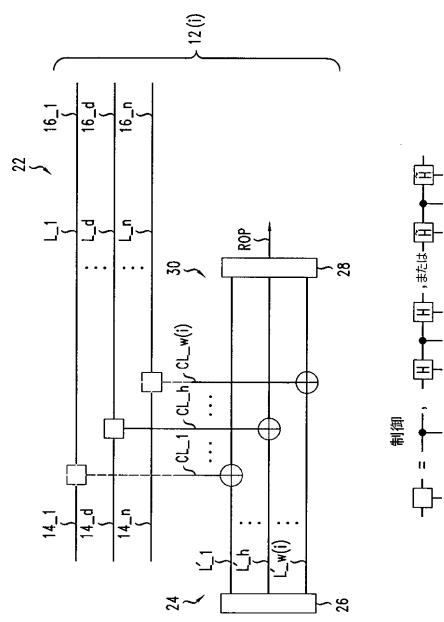

図 2 は、例えば図 1 のハードウェア測定デバイス 12\_1 ~ 12\_B の中の 1 つである、安定化群の要素  $g_i$  に對応する量子回路 12 (i) の実施形態を図解している。要素  $g_i$  は、対応する  $2^n$  次元バイナリ・ベクトル ( $a_{1,1}(i), a_{1,2}(i), \dots, a_{n,1}(i), a_{n,2}(i)$ ) を有しているが、これは整数  $w(i)$  を定義する。特に、整数  $w(i)$  は、インデクス  $f$  のすべての値に対して、(0, 0) と等しくない対 ( $a_{f,1}(i), a_{f,2}(i)$ ) の個数である。整数  $w(i)$  は、後述するように、量子回路 12 (i) のいくつかの性質を定義する。

30

#### 【0056】

量子回路 12 (i) は、量子ビット接続線  $L_1, \dots, L_n$  と、測定部分 24 と、 $w(i)$  個の制御線  $C_{L_1}, \dots, C_{L_w(i)}$  を備えた 1 次物理チャネル 22 を有する。それぞれの接続線  $L_1, \dots, L_n$  は、例えば量子ビットに対して演算を行うために、受け取られた量子状態の量子ビットを、入力ポート  $14_1, \dots, 14_d, \dots, 14_n$  の中の 1 つから、出力ポート  $14_1, \dots, 14_d, \dots, 14_n$  の中の 1 つへ通信する。1 次物理チャネル 22 は、予め選択された量子状態を、2 次物理チャネル 30 を通過して送信することにより、入力ポート  $14_1, \dots, 14_n$  において受け取られた量子状態に対するシンドロームのビットまたはシンドロームの前記測定に対するパリティ検査ビットをその性質が測定する状態が生成されるように、測定部分 24 の 2 次物理チャネル 30 を制御する。

40

#### 【0057】

ここで、例えば線  $L_1 \sim L_n$  および  $L'_1 \sim L'_{w(i)}$  のいずれかである接続線は、状態の量子ビットを入力ポートと出力ポートとの間で転送するための量子ゲートの一部または量子ゲートの直列配列の一部である。

#### 【0058】

測定部は、予め選択された量子状態すなわち  $w(i)$  量子ビットのアンシラ状態 (anci

50

lla state) を記憶する入力レジスタ 26 と、出力測定デバイス 28 と、入力レジスタ 26 と出力測定デバイス 28 との間で予め選択された量子状態の量子ビットを送信するための  $w(i)$  量子ビットの接続線  $L'_1, \dots, L'_w(i)$  を有する 2 次物理チャネル 30 とを含む。2 次物理チャネル 30 の接続線  $L'_1 \sim L'_w(i)$  のそれぞれは、1 次物理チャネル 22 の接続線  $L_1 \sim L_n$  の中の 1 つによって、すなわち、制御線  $CL_1 \sim CL_w(i)$  を経由して、制御される。明瞭にするために、制御構造は、1 次物理チャネル 22 の接続線  $L_d$  上の箱によって、示されている。この箱は、制御線  $CL_h$  を経由して、2 次物理チャネル 30 の接続線  $L'_h$  に接続している。1 次物理チャネル 22 の他の接続線  $L_1 \sim L_n$  は、そのような制御接続が配置され得る位置を示すために、その上に小さな破線による箱を有する。 $n$  本の接続線  $L_1 \sim L_n$  の間で、 $w(i)$  は、小さな破線による箱によって示されている位置において、それらの線の間での相互作用構造を有する。1 次チャネルの  $[n - w(i)]$  本の他の接続線  $L_1 \sim L_n$  の中のいずれも、2 本線の初等量子ゲートに接続していない。

10

#### 【0059】

制御線  $CL_1 \sim CL_w(i)$  は、1 次物理チャネル 22 の接続線  $L_1 \sim L_n$  の中の  $w(i)$  本を 2 次物理チャネル 30 の接続線  $L'_1 \sim L'_w(i)$  に接続する 2 本線の量子ゲートの存在を示している。

#### 【0060】

出力領域 28 は、2 次物理チャネル 30 から受け取られた量子状態の  $w(i)$  量子ビットのそれぞれの値を測定するように構成され、かつ、受け取られた量子状態の  $w(i)$  量子ビットの測定された値の和の測定されたパリティに対する結果信号を送信するように構成されている。この結果信号は、例えば図 1 の結果出力ポート  $ROP_1 \sim ROP_B$  の中の 1 つなどである結果出力ポートに送信される。結果信号は、シンドロームの測定されたビットまたは測定されたシンドロームに対するパリティ検査ビットの値である。

20

#### 【0061】

線  $L_1 \sim L_n$ 、 $L'_1 \sim L'_w(i)$ 、および  $CL_1 \sim CL_w(i)$  と、初等量子ゲートと、レジスタ 26 と、測定領域 28 とを作成し用いるための様々な構造および方法は、本開示に基づいて、当業者によって容易に理解されるであろう。更に、いくつかのこれらの構造および方法に関する説明は、例えば、既に本明細書に組み入れられた Frank Gaitan による書籍および Michael A. Nielsen 他による書籍の一方または両方に提供されているであろう。

30

#### 【0062】

ハードウェア測定デバイスでは、1 次および 2 次物理チャネル 22、30 の線  $L_1 \sim L_n$  および  $L'_1 \sim L'_w(i)$  を結合する初等量子ゲートのパターンは、要素  $g_i$  に対応する  $2n$  次元バイナリ・ベクトル  $(a_{1,1}(i) a_{1,2}(i), \dots, a_{n,1}(i), a_{n,2}(i))$  の形式によって固定されている。例えば、1 次物理チャネル 22 の上から  $d$  番目の線  $L_d$  は、1 つの初等量子ゲートを経由して、2 次物理チャネル 30 の  $h$  番目の線  $L'_h$  に接続している。その初等量子ゲートの形式は、対  $(a_{d,1}(i), a_{d,2}(i))$  の値によって固定されている。この対の様々な値に対して、初等量子ゲートは、次のように定義される。

40

0)  $(a_{d,1}(i), a_{d,2}(i)) = (0, 0)$  の場合には、量子ゲートは、恒等演算子 (identity operator) として作用する。すなわち、量子ゲートは存在しない。

1)  $(a_{d,1}(i), a_{d,2}(i)) = (0, 1)$  の場合には、量子ゲートは、制御 NOT (CNOT) ゲートである。つまり、その制御は、1 次物理チャネル 22 における線  $L_d$  からのものである。

2)  $(a_{d,1}(i), a_{d,2}(i)) = (1, 0)$  の場合には、量子ゲートは、アダマール・ゲート (H)、CNOT ゲート、および H ゲートのシーケンスである。なお、ここで、H ゲートと CNOT ゲートの制御とは、1 次物理チャネル 22 の線  $L_d$  上に存在する。

3)  $(a_{d,1}(i), a_{d,2}(i)) = (1, 1)$  の場合には、量子ゲートは、- /

50

4 の離散的な  $\times$  軸回転ゲート

【0063】

【数7】

$\tilde{H}$

、 CNOT ゲート、および

【0064】

【数8】

$\tilde{H}$

10

のシーケンスである。なお、ここで、

【0065】

【数9】

$\tilde{H}$

と CNOT ゲートの制御とは、1 次物理チャネル 2 2 の線  $L_d$  上に存在する。様々な上述した初等量子ゲートは、次のように動作する。H ゲートは、単一のスピン状態  $|j\rangle$  に対して、すなわち、1 次物理線  $L_d$  の線  $L_d$  上の量子ビットに対して、

$$H|j\rangle = [ |0\rangle + (-1)^j |1\rangle ]$$

に従って動作する。

20

CNOT ゲートは、2 スピン状態  $|i, j\rangle$  に対して、すなわち、 $L_d$  および  $L_h$  の量子ビットに対して、

$$CNOT|i, j\rangle = |i, i+j\rangle$$

に従って動作する。ここで、「+」は、mod 2 での加算を意味する。CNOT ゲートの場合には、制御量子ビット  $i$  は 1 次物理チャネル 2 2 の線  $L_d$  上に存在し、制御量子ビット  $j$  は 2 次物理チャネル 3 0 の線  $L_h$  上に存在する。

【0066】

【数10】

$\tilde{H}$

30

ゲートは、1 次物理チャネル 2 2 の線  $L_d$  の上の单一スピン状態  $|j\rangle$  に対して動作し、

、

【0067】

【数11】

$$\tilde{H}|j\rangle = \exp(-i\pi\sigma_x/4)|j\rangle$$

によって定義される。

【0068】

量子回路では、2 次物理チャネル 3 0 の形式とレジスタ 2 6 における予め選択された量子状態とは、安定化群の要素  $g_i$  と対応する 2  $n$  次元バイナリ・ベクトル ( $a_{1,1}(i)$   $a_{1,2}(i), \dots, a_{n,1}(i), a_{n,2}(i)$ ) によって固定されている。第 1 に、既に述べられたように、2 次物理チャネル 3 0 は、量子ビット接続線  $L_1 \sim L_w(i)$  の  $w(i)$  を、すなわち、この量子回路のそれぞれの 2 状態量子ゲートのための別の線を、有する。最後に、レジスタ 2 6 に記憶されており 2 次物理チャネル 3 0 に送信される予め選択された量子状態は、 $w(i)$  量子ビットのショア量子状態  $|A\rangle$  である。ショア量子状態  $|A\rangle$  は、次の数式によって定義される。

【0069】

40

## 【数12】

$$|A\rangle = 2^{[-w(i)-1]/2} \sum_{A(e)} |A(e)\rangle$$

ここで、量子状態  $A(e)$  の全体に亘る和は、 $w(i)$  個のスピン状態すなわち  $w(i)$  個の量子状態のすべての直積を含み、偶数パリティを有する。

## 【0070】

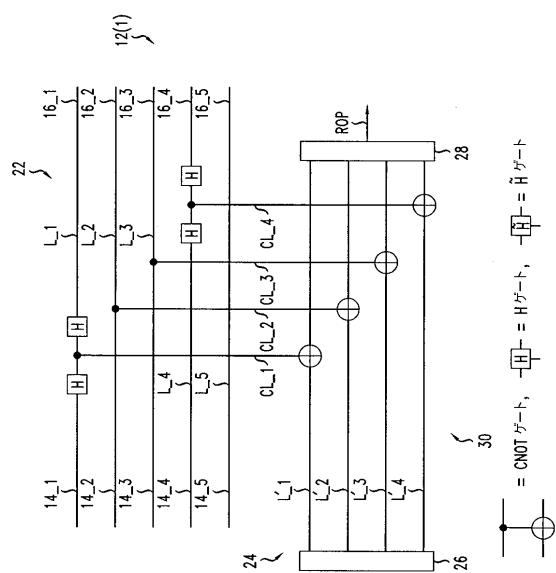

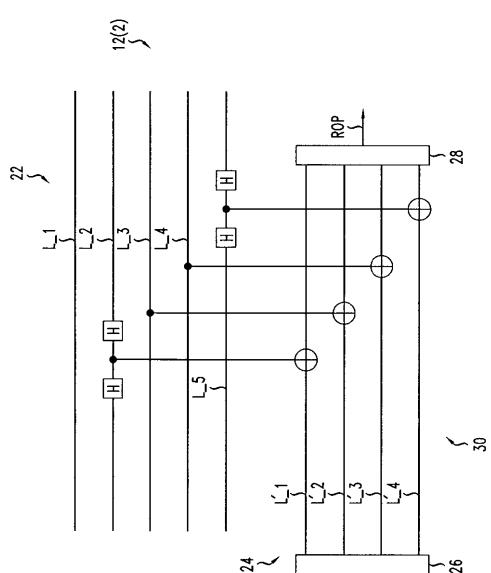

図3、図4、図5、および図6は、 $n = 5$  である場合の量子冗長符号化方式に対する安定化群  $G$  の基底要素  $g_1$ 、 $g_2$ 、 $g_3$ 、および  $g_4$  それぞれに対応する量子回路 12(1)、12(2)、12(3)、および 12(4)を図解している。基底要素  $g_1$ 、 $g_2$ 、 $g_3$ 、および  $g_4$  と 10次元(1D)のバイナリ・ベクトルとの間の対応は、次のように与えられる。

10

$$\begin{aligned} g_1 &<-> (1, 0, 0, 1, 0, 1, 1, 0, 0, 0), \\ g_2 &<-> (0, 0, 1, 0, 0, 1, 0, 1, 1, 0), \\ g_3 &<-> (1, 0, 0, 0, 1, 0, 0, 1, 0, 1), \text{ および} \\ g_4 &<-> (0, 1, 1, 0, 0, 0, 1, 0, 0, 1). \end{aligned}$$

要素  $g_1$ 、 $g_2$ 、 $g_3$ 、および  $g_4$  は、それぞれが、ショア状態が 4 量子ビットを有するように、4に等しいウェイト「 $w(i)$ 」を有する。

## 【0071】

図3は、安定化群の要素  $g_1$  に対応する量子回路 12(1)を図解している。量子回路 12(1)の構造は、10次元のバイナリ・ベクトル(1, 0, 0, 1, 0, 1, 1, 0, 0, 0)から、以下のようにして導かれる。

20

1.  $g_1$  に対する 10次元のバイナリ・ベクトルにおいて、最も左にあるビット対は(1, 0)である。対(1, 0)に対しては、一連のHゲート、CNOTゲート、およびHゲートが、1次物理チャネル22の1番上の線を、2次物理チャネル30の1番上の線に接続する。

2.  $g_1$  に対する 10次元のバイナリ・ベクトルにおいて、第2のビット対は(0, 1)である。対(0, 1)に対しては、CNOTが、1次物理チャネル22の上から2番目の線を、2次物理チャネル30の上から2番目の線に接続する。

3.  $g_1$  に対する 10次元のバイナリ・ベクトルにおいて、第3のビット対は(0, 1)である。対(0, 1)に対しては、CNOTが、1次物理チャネル22の3番目の線を、2次物理チャネル30の3番目の線に接続する。

30

4.  $g_1$  に対する 10次元のバイナリ・ベクトルにおいて、第4のビット対は(1, 0)である。対(1, 0)に対しては、一連のHゲート、CNOTゲート、およびHゲートが、1次物理チャネル22の4番目の線を、2次物理チャネル30の4番目の線に接続する。

5.  $g_1$  に対する 10次元のバイナリ・ベクトルにおいて、第5の、すなわち最も右にあるビット対は(0, 0)である。対(0, 0)に対しては、1次物理チャネル22の一番下の線と2次物理チャネル30との間には接続が存在しない。第5の量子ビットは、この測定には参加しない。

40

## 【0072】

図4、図5、および図6は、それぞれの基底要素  $g_2$ 、 $g_3$ 、および  $g_4$  に対応する量子回路 12(2)、12(3)、および 12(4)は、群の要素  $g_2$ 、 $g_3$ 、および  $g_4$  に対応する 10次元のバイナリ・ベクトルから、群の要素  $g_1$  と対応する 10次元のバイナリ・ベクトルから量子回路 12(1)を上で導いたのと同様の態様で、導かれ得る。

## 【0073】

いくつかの実施形態においては、電子コントローラ18が、線形符号化を用いて、例えば線形ブロック符号化により、シンドロームのビットの測定を誤り訂正するように構成され得る。例えば、上述した実例では、安定化群  $G$  の基底要素  $g_1$ 、 $g_2$ 、 $g_3$ 、および  $g_4$  50

$s_4$  と対応する量子回路  $12(1) \sim 12(4)$  は、物理的に処理された量子冗長符号化状態に対するシンドロームのビット  $s_1, s_2, s_3$ 、および  $s_4$  を測定した。電子コントローラ 18 は、線形ブロック符号化技術により、シンドロームのビット  $s_1, s_2, s_3$ 、および  $s_4$  の測定された値の集合を誤り訂正するように構成され得る。線形ブロック符号化では、パリティ検査ビットは、情報ビットの線形結合 (linear combinations) として定義される。この場合、情報ビットはシンドローム・ビット  $s_1, s_2, s_3$ 、および  $s_4$  である。よって、上述の実例では、このような線形ブロック符号化は、パリティ検査ビット  $p_1 \sim p_8$  を用い得るが、これらは、シンドローム・ビット  $s_1, s_2, s_3$ 、および  $s_4$  の以下の線形結合である。

$$\begin{aligned} p_1 &= s_1 + s_3, \\ p_2 &= s_2 + s_3, \\ p_3 &= s_1 + s_2, \\ p_4 &= s_1 + s_2 + s_4, \\ p_5 &= s_1 + s_3 + s_4, \\ p_6 &= s_3 + s_4, \\ p_7 &= s_1 + s_2 + s_3 + s_4, \\ p_8 &= s_2 + s_4. \end{aligned}$$

10

パリティ検査ビットのこのような選択は線形符号 C に対応し、線形符号 C は次の生成行列を有する。

【0 0 7 4】

20

【数 1 3】

$$\begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 0 & 1 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 1 & 1 & 1 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 & 0 & 0 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 \end{bmatrix} \quad (2)$$

上のパリティ検査ビットは、安定化群の要素と対応する量子回路によって測定されうるが、ここで、安定化群の要素は、基底要素  $g_1, g_2, g_3$ 、および  $g_4$  の積である。例えば、パリティ検査ビット  $p_3$  は  $s_1 + s_2$  と等しいから、 $p_3$  を測定するための量子回路は、安定化群の要素  $g_1 \times g_2$  に対応する。しかし、 $g_1 \times g_2$  に対応する 10 次元のバイナリ・ベクトルは、 $g_1$  および  $g_2$  に対応する 10 次元のバイナリ・ベクトルの和である。よって、 $p_3$  を測定するための量子回路は、次のバイナリ・ベクトルに対応する。

$$(1, 0, 0, 1, 0, 1, 1, 0, 0, 1, 1, 0) + (0, 0, 1, 0, 0, 1, 1, 1, 1, 1, 1, 1)$$

$$= (1, 0, 1, 1, 0, 0, 1, 1, 1, 1, 0, 0)$$

同様に、 $s_2 + s_3$  である  $p_2$  を測定するための量子回路は、 $g_2 \times g_3$  に対応する 10 次元のバイナリ・ベクトルである。よって、 $p_2$  を測定するための量子回路は、次のバイナリ・ベクトルに対応する。

$$(0, 0, 1, 0, 0, 1, 0, 1, 1, 0) + (1, 0, 0, 0, 1, 0, 0, 1, 1, 1) \quad 40$$

$$, (0, 1, 0, 1) = (1, 0, 1, 0, 1, 1, 0, 0, 1, 1)$$

図 7 および図 8 は、 $p_3$  および  $p_2$  をそれぞれ直接的に測定するための量子回路  $12(7)$  および  $12(8)$  をそれぞれ図解している。

【0 0 7 5】

以上の説明に基づいて、当業者であれば、上述したリストにあるパリティ検査ビット  $p_1 \sim p_8$  のそれぞれを直接的に測定するための量子回路を構築することが可能であろう。

【0 0 7 6】

そのような量子回路を含んでいた図 1 の装置 10 の実施形態では、電子コントローラ 18 は、例えば線形 C 符号 (linear C code) に基づいてシンドロームの測定された値を誤り訂正するように、構成され得る。特に、シンドローム・ビット  $s_1 \sim s_4$  とパリティ検

50

査ビット  $p_1 \sim p_8$  との測定された値がすべて正しい場合には、ベクトル ( $s_1, s_2, s_3, s_4, p_1, p_2, p_3, p_4, p_5, p_6, p_7, p_8$ ) が符号 C の符号語 (codeword) である。他方、これらの測定されたビット値の中の 1 つまたは複数が正しくない場合には、このベクトルは符号語ではない。そのような状況では、電子コントローラ 18 は、最も可能性が高い符号語である ( $v_1, v_2, v_3, v_4, v_5, v_6, v_7, v_8, v_9, v_{10}, v_{11}$ ) を C において見つけるように構成され得るし、シンドロームを ( $v_1, v_2, v_3, v_4$ ) として形成するように構成され得る。例えば、電子コントローラ 18 は、ベクトル ( $s_1, s_2, s_3, s_4, p_1, p_2, p_3, p_4, p_5, p_6, p_7, p_8$ ) に最も近い C の符号語を、次のように見いだすように構成され得る。

$v = (v_1, v_2, v_3, v_4, v_5, v_6, v_7, v_8, v_9, v_{10}, v_{11})$  10

$= \arg \min_v \text{dist}(v, (s_1, s_2, s_3, s_4, p_1, p_2, p_3, p_4, p_5, p_6, p_7, p_8))$

なお、ここで、関数  $\text{dist}(v, w)$  は、ベクトル v とベクトル w との間のハミング距離である。

#### 【0077】

他の実施形態では、図 1 の電子コントローラ 18 は、シンドロームの各ビット  $s_j$  に対する復号誤りの確率  $P_j$  と、各ビット  $p_i$  に対する誤り確率  $P_{r_i}$  とを推定し、これらの確率を用いて C の軟判定復号 (soft-decision decoding) を実行し得る。例えば、電子コントローラ 18 は、C のトレリス・ベースの (trellis based) 軟判定復号を実行するように構成され得る。確率  $P_j$  および  $P_{r_i}$  は、例えば、安定化群の対応する要素のバイナリ・ベクトルのハミング・ウェイトに依存し得る。 20

#### 【0078】

図 1 の装置 10 は物理的に処理された量子冗長符号化状態のシンドロームのビットを直列的に測定し、そのシンドロームの測定されたビットの前記集合に対する 1 つまたは複数のパリティ検査ビットを測定するのであるが、前記測定は、異なる態様で実行され得ることもあり得る。実際、他の実施形態は、そのような測定を、並列的な態様で、直列的な態様で、または並列および直列が混合された態様で、実行し得る。

#### 【0079】

図 9 は、図 9 において INPUT と記されている入力において受け取られる n 量子ビットの物理状態のシンドロームの測定されたビットに誤り訂正を適用するように構成されている別の装置 10' を図解している。受け取られた n 量子ビットの物理状態は、k 個の物理的対象の初期量子状態を量子冗長符号化し、その後で、誤りを生じさせる可能性がある態様で n 個の物理的対象の量子冗長符号化状態を物理的に処理することによって、前もって準備されていた。 30

#### 【0080】

装置 10' は、入力レジスタ  $R_{IN}$  と、出力レジスタ  $R_{OUT}$  と、物理的対象の c 個の対応する予めセットされた量子状態のための補助レジスタ  $R_{PQS\_1} \sim R_{PQS\_c}$  と、量子回路 QC と、量子状態の c 個の検出器  $D\_1 \sim D\_c$  と、電子コントローラ 18 を含む。いくつかの実施形態では、この装置は、また、オプションの誤り訂正モジュール ECM も、含み得る。 40

#### 【0081】

図 9 は、構成要素の間の様々な接続を概略的に示している。第 1 に、レジスタ  $R_{IN}$ 、 $R_{OUT}$ 、 $R_{PQS\_1} \sim R_{PQS\_c}$  のポートと量子回路 QC のポートとの間の接続と、そして、検出器  $D\_1 \sim D\_c$  のポートと量子回路 QC のポートとの間の接続とは、矢印付きの線で示されている。第 2 に、電子コントローラ 18 と検出器  $D\_1 \sim D\_c$  との間で信号を送信するための接続と、電子コントローラ 18 とオプションの誤り訂正モジュール ECM との間で信号を送信するための接続とが、矢印付きの線で示されている。

#### 【0082】

入力レジスタ  $R_{IN}$  は、図 9 の INPUT と記された入力において受け取られる n 量子ビットの物理状態を記憶するように接続されている。入力レジスタ  $R_{IN}$  は、受け取られ 50

た  $n$  量子ビットの物理状態を、入力レジスタ  $R_{IN}$  の  $n$  個の出力ポートを経由して、量子回路  $QC$  の  $n$  個の入力ポートに送信する。

【0083】

出力レジスタ  $R_{OUT}$  は、量子回路  $QC$  が入力レジスタ  $R_{IN}$  から以前に受け取っていた  $n$  量子ビットの物理状態を受け取り記憶することができるよう、量子回路  $QC$  の  $n$  個の出力ポートに接続された  $n$  個の入力ポートを有している。出力レジスタ  $R_{IN}$  は、図9において  $OUTPUT$  と記されている出力に、 $n$  量子ビットの物理状態を送信するか、または、前記状態を、そのようなモジュールを有する実施形態におけるオプションの誤り訂正モジュール  $ECM$  に出力する。

【0084】

1つまたは複数の補助レジスタ  $R_{PQS\_1} \sim R_{PQS\_c}$  は、それぞれが、予めセットされた量子状態を記憶し、記憶されている予めセットされた量子状態を、出力ポートを経由して、量子回路  $QC$  の入力ポートの対応する組に送信するように構成されている。

【0085】

量子回路  $QC$  は、予めセットされた量子状態を入力レジスタ  $R_{IN}$  から受け取られた  $n$  量子ビットの物理状態に基づいて変換するよう、受け取られた量子状態を処理するよう構成されている。量子回路  $QC$  は、1つまたは複数の変換された予めセットされた量子状態のそれぞれを、検出器  $D\_1 \sim D\_c$  の中の対応する1つに送信する。量子回路  $QC$  は、入力レジスタ  $R_{IN}$  から受け取られた同じ  $n$  量子ビットの量子状態を、出力レジスタ  $R_{OUT}$  に出力する。例えば、量子回路  $QC$  の内部では、受け取られた  $n$  量子ビットの物理状態は、量子ゲートの制御ノードを動作させる、および／または、量子回路  $QC$  の内部で反転される1つまたは複数の内部変換を受けることがあり得る。

【0086】

それぞれの検出器  $D\_1 \sim D\_c$  は、そこで受け取られた予めセットされ変換された量子状態の量子ビットの値の測定を行う。量子ビットの測定された値に基づいて、検出器は、信号を、電子コントローラ18に送信する。信号は、入力( $INPUT$ )において受け取られた  $n$  量子ビットの量子状態に対するシンドロームの対応するビットの測定された値か、または、シンドロームの測定されたビットに対するパリティ検査ビットの測定された値のいずれかに対応する。検出器  $D\_1 \sim D\_c$  の1つまたは複数が、シンドロームの測定されたビットに対するパリティ検査ビットを測定する。典型的には、検出器  $D\_1 \sim D\_c$  の中の他のものが、シンドロームのビットを測定する。

【0087】

電子コントローラ18は、シンドロームのビットの測定された値、および／または、検出器  $D\_1 \sim D\_c$  からのパリティ検査ビットの測定された値に対する信号を受け取る。測定された値から、電子コントローラ18は、 $INPUT$  と記された入力において受け取られた  $n$  量子ビットの物理状態に対するシンドロームの可能性が高い値を決定する。例えば、電子コントローラ18は、パリティ検査ビットの測定された値に基づいて、シンドロームに対するビットの測定された値を誤り訂正するために、線形冗長符号化の1つまたは複数の技術を適用し得る。電子コントローラ18は、また、制御信号をオプションの誤り訂正モジュール  $ECM$  に送ることがあり、この場合、制御信号は、電子コントローラ18によって決定されたシンドロームの可能性の高い値を示す。

【0088】

オプションである誤り訂正モジュール  $ECM$  は、 $n$  量子ビットの物理状態に対して動作して、そこにある誤りを除去し、誤り訂正された物理状態を、図9では  $OUTPUT$  と記されている出力に送信する。特に、誤り訂正モジュールは、 $n$  量子ビットの物理状態に量子回路を通過させ、そこにあるある誤りを反転させるが、その場合に、誤り反転の形式は、電子コントローラ18から受け取られた制御信号によって示される。このように、誤り訂正は、電子コントローラ18によって決定されたシンドロームの値に基づく。

【0089】

図9では、装置10'は、配列的、直列的、または部分的に並列的で部分的に直列的な

10

20

30

40

50

態様で、様々な予めセットされ変換された量子状態を準備し得る。

【0090】

最後に、受け取られ物理的に処理された量子冗長符号化状態のシンドロームのビットを測定し、シンドロームの測定されたビットの前記集合に対する1つまたは複数のパリティ検査ビットを測定する装置の他の実施形態は、他の量子回路を用いることがあり得る。前記量子回路は、異なるパターンの量子ゲートを有し得るし、および／または、いくつかの異なる量子ゲートを用いることがあり得る。例えば、いくつかのそのような量子回路は、2よりも大きな量子ビットを結合することさえあり得る。

【0091】

図10は、方法40を図解しているが、この方法40は、例えば図1および図9の装置10、10'において、物理的に処理され冗長符号化された多量子ビット状態のシンドロームを測定するステップを含む。

【0092】

方法40は、物理的に処理され冗長符号化された多量子ビット状態を、この物理的に処理され冗長符号化された多量子ビット状態のシンドロームを測定するために、第1のハードウェア・デバイスを通過して送信するステップ(ステップ42)を含む。例えば、ステップ42は、図1のハードウェア測定デバイス12\_1～12\_Bのいくつかにおいて、または、図9の量子回路QCにおいて、実行され得る。例えば、第1のハードウェア測定デバイスは、量子ゲート回路の1つまたは複数の第1のシーケンスを含み得る。

【0093】

方法40は、また、物理的に処理され冗長符号化された多量子ビット状態を、シンドロームの測定に対する1つまたは複数のパリティ検査ビットを測定するために、第2のハードウェア・デバイスを通過して送信するステップ(ステップ44)を含む。例えば、ステップ42は、図1の残りのハードウェア測定デバイス12\_1, …, 12\_Bにおいて、または、図9の量子回路QCの他の部分において、実行され得る。例えば、第2のハードウェア測定デバイスは、量子ゲート回路の1つまたは複数の第2のシーケンスを含み得る。

【0094】

方法40は、オプションとして、1つまたは複数のパリティ検査ビットの測定された値に基づいてシンドロームの複数の測定されたビットの中の少なくとも1つを訂正することにより、測定されたシンドロームを誤り訂正するステップを含み得る(ステップ46)。例えば、測定されたシンドロームのそのような訂正は、図1および図9の電子コントローラ18によって実行され得る。

【0095】

方法40は、オプションとして、測定され誤り訂正されたシンドロームに基づき、量子回路における物理的に処理された冗長符号化された多量子ビット状態を誤り訂正するステップを含み得る。例えば、そのような誤り訂正は、図9の誤り訂正モジュールECMにおいて実行され得る。

【0096】

本明細書に記載されている装置および方法のいくつかの実施形態は、2013年6月7日に同時に出願された米国特許出願第13/912,654号に記載されている方法および／または装置を用い得る。例えば、いくつかの実施形態は、線形ブロック符号が低密度生成行列符号であるように構築されるときに適切であり得る。米国特許出願第13/912,654号は、その全体が、参照によって本明細書に組み入れられる。

【0097】

本明細書では、パリティ検査ビットが、和のパリティがパリティ検査ビットによって検査されるビットの別個の測定を経由して、測定されることはない。例えば、そのようなパリティ検査ビットを測定するように構成された量子回路デバイスが、もつれた(entangled)対象の单一の量子状態に関する測定から、パリティ検査ビットの値を取得し得る。そのような量子回路デバイスが、複数の量子状態の別個の測定からパリティ検査ビットの値

10

20

30

40

50

を取得することはない。なお、この場合、別個の測定とは、パリティ検査ビットの値によってその和がパリティ検査されることが可能であるビットの値を、測定することである。

【0098】

他の実施形態は、本明細書に記載されている装置のいずれかを動作させる様々な方法を含む。

【0099】

本明細書に記載されている電子デバイスは、完全にハードウェアとして、または、特定のソフトウェアを動作させるように構成されたハードウェアとして、実装され得る。後者は、例えば、本明細書に記載された方法のいずれかのステップを遂行するためのマシンを実行させるように、または、そのように実行可能なコマンドのコンピュータ可読なプログラムを実行させるように構成されたコンピュータ・デバイスである。そのようなマシンまたはコンピュータ実行可能なプログラムは、非一時的な態様で、例えば電子メモリ、磁気ハードディスク、または光学的データ記憶ディスクなど、任意の通常のデジタル・データ記憶媒体上に記憶され得る。

10

【0100】

発明を実施するための態様と図面とは、本発明の実施形態を例証しているに過ぎない。本開示に基づいて、当業者が、本明細書に明示的に記載されていないまたは示されていない場合であっても、特許請求の範囲に記載された発明に含まれる他の装置および方法を容易に想到することが可能である、ということが理解されるであろう。更に、本明細書に記載されたすべての実例は、教示する目的だけを有することが原則的に意図されており、特許請求の範囲に記載された発明に対する限定となることなく、解釈されるべきである。更に、原則、態様、および実施形態に関する本明細書におけるすべての言明は、それらの均等物に及ぶことが意図されている。

20

【0101】

本明細書において、要素が特徴Bまたは特徴Cを有する、という記載は、下記の場合1、2、および3のいずれかが真である場合に満足される。場合1では、要素は特徴Bを有するが特徴Cを有していない。場合2では、要素は特徴Cを有するが特徴Bを有していない。場合3では、要素は特徴Bおよび特徴Cの両方を有する。

【図1】

【図2】

【図3】

【図4】

【 図 5 】

## 【 図 6 】

【図7】

【 四 8 】

【図9】

【図10】

---

フロントページの続き

(72)発明者 アシクミン,アレクセイ

アメリカ合衆国 07974-0636 ニュージャージィ,マレイ ヒル,マウンテン アヴェ

ニュー 600-700

審査官 岡 裕之

(56)参考文献 特開2006-345324 (JP, A)

特開2010-233066 (JP, A)

G. Gilbert et al., Logical Zeros for the Seven-Qubit Quantum Error Correction Code, Proceeding of SPIE 8057, Quantum Information and Computation IX, 80570D, 2011年 6月 2日, Vol.8057

古田憲一郎,訂正へのシンドローム情報の反映にユニタリ作用素を用いる量子誤り訂正,電子情報通信学会技術研究報告, 2004年 9月 9日, Vol.104, No.301, pp.31-36, IT2004-37

Alexei Ashikhmin et al., Robust Quantum Error Syndrome Extraction by Classical Coding, 2014 IEEE International Symposium on Information Theory, 2014年 7月 4日, pp. 546-550

(58)調査した分野(Int.Cl., DB名)

H03M 13/47

IEEE Explore

Cini