(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I682692 B

(45)公告日：中華民國 109 (2020) 年 01 月 11 日

(21)申請案號：105114045

(51)Int. Cl. : **H05K1/02 (2006.01)**

**H05K3/28 (2006.01)**(30)優先權：2015/05/11 南韓

2015/10/05 南韓

2016/04/19 南韓(71)申請人：南韓商三星電子股份有限公司 (南韓) SAMSUNG ELECTRONICS CO., LTD. (KR)

南韓

(72)發明人：朴大賢 PARK, DAE HYUN (KR)；金漢 KIM, HAN (KR)；許康憲 HUR, KANG HEON (KR)；高永寬 KO, YOUNG GWAN (KR)；沈正虎 SHIM, JUNG HO (KR)

(74)代理人：葉璟宗；鄭婷文；詹富閔

(56)參考文獻：

TW I343105

審查人員：劉育瑜

申請專利範圍項數：32 項 圖式數：44 共 182 頁

(54)名稱

扇出半導體封裝及其製造方法

(57)摘要

提供扇出半導體封裝及其製造方法。扇出半導體封裝包括：第一連接構件，含貫穿孔；半導體晶片，於貫穿孔中且含主動表面，連接焊墊置於主動表面上且非主動表面相對主動表面；囊封劑，至少囊封第一連接構件及半導體晶片的非主動表面的部分；第二連接構件，於第一連接構件及半導體晶片的主動表面上且含電性連接至連接焊墊的重新分配層，第一連接構件含第一絕緣層、於第一絕緣層的表面上的第一重新分配層、於第一絕緣層且覆蓋第一重新分配層的第二絕緣層及於第二絕緣層上的第二重新分配層，第一重新分配層及第二重新分配層電性連接至連接焊墊。

A fan-out semiconductor package and a method of manufacturing the same are provided. The fan-out semiconductor package includes a first connection member having a through-hole; a semiconductor chip disposed in the through-hole and having an active surface on which a connection pad is disposed and an inactive surface opposing the active surface; an encapsulant encapsulating at least portions of the first connection member and the inactive surface of the semiconductor chip; and a second connection member disposed on the first connection member and the active surface of the semiconductor chip, and including a redistribution layer electrically connected to the connection pad. The first connection member includes a first insulating layer, a first redistribution layer disposed on a surface of the first insulating layer, a second insulating layer disposed on the first insulating layer and covering the first redistribution layer, and a second redistribution layer disposed on the second insulating layer, and the first and second redistribution layers are electrically connected to the connection pad.

指定代表圖：

符號簡單說明：

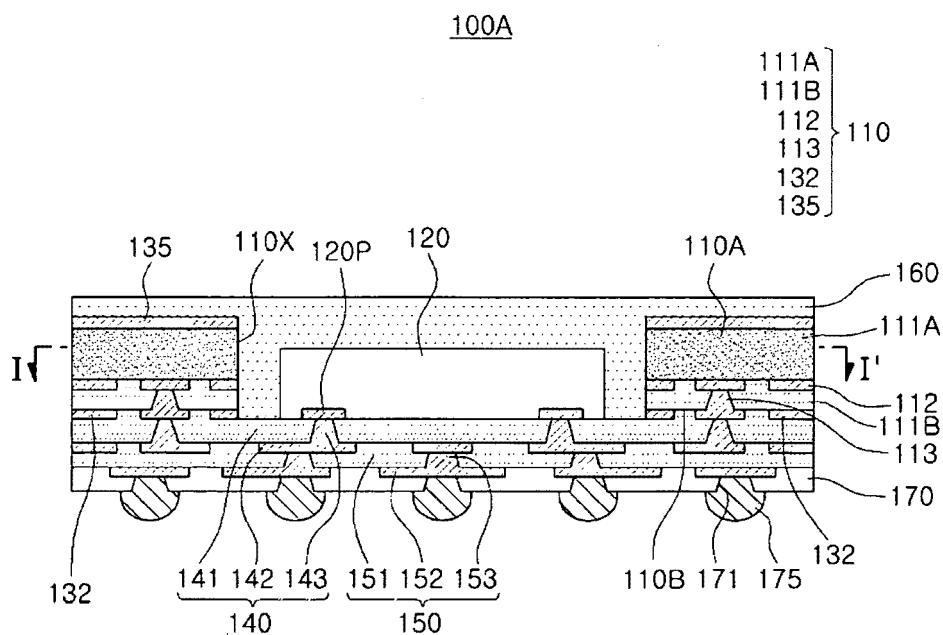

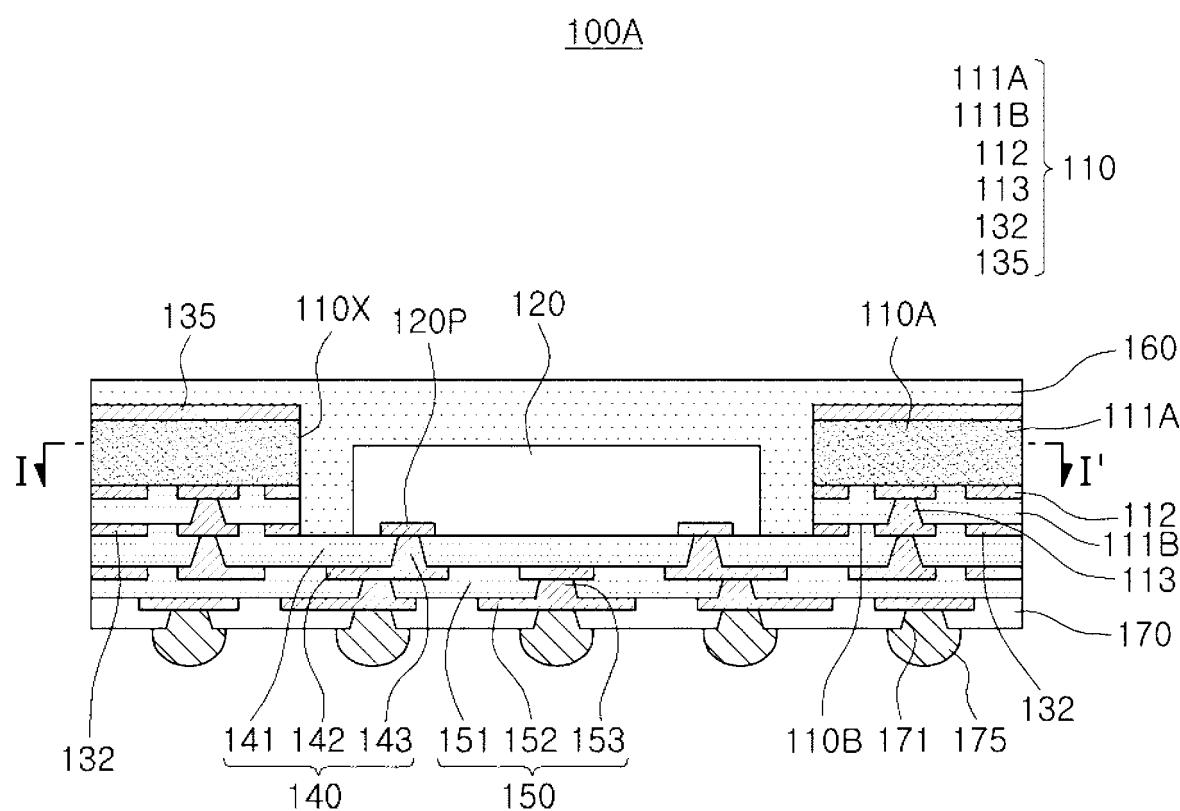

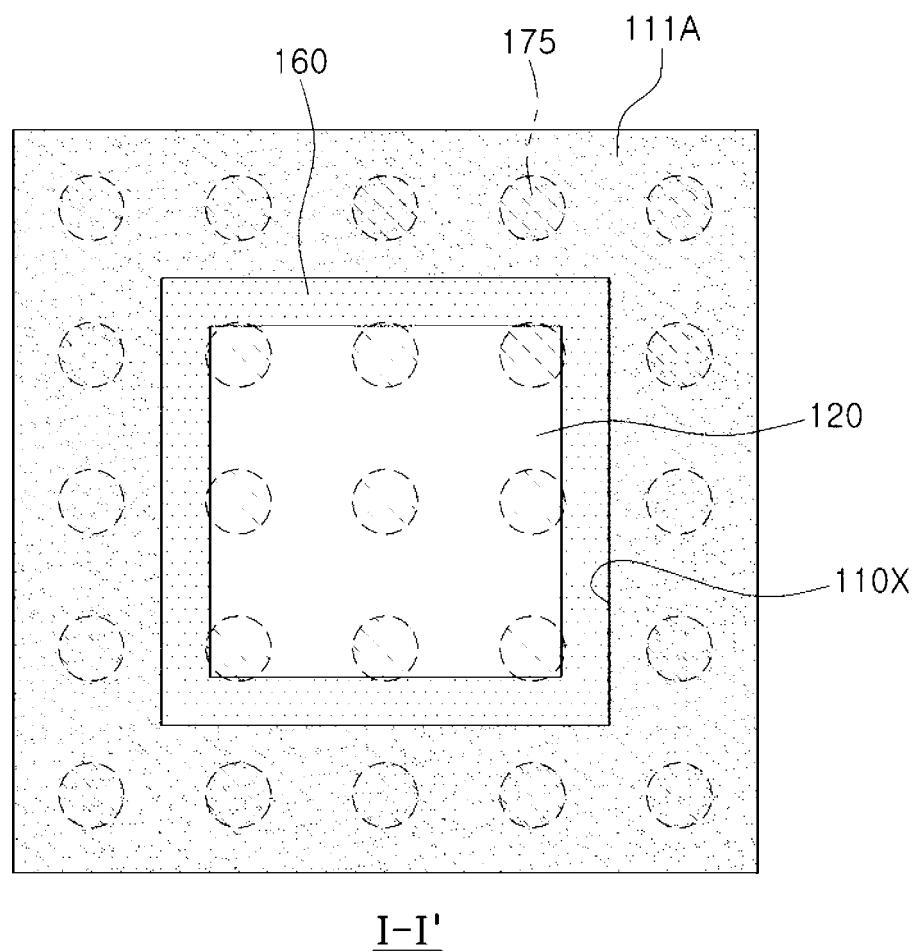

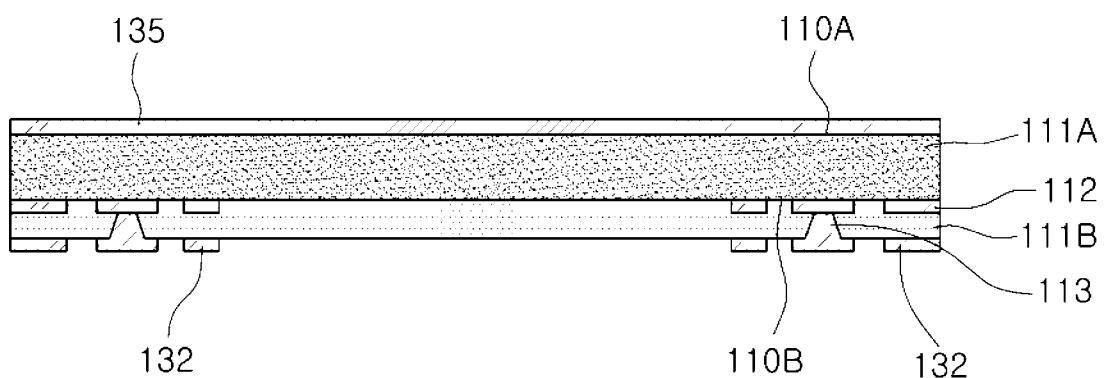

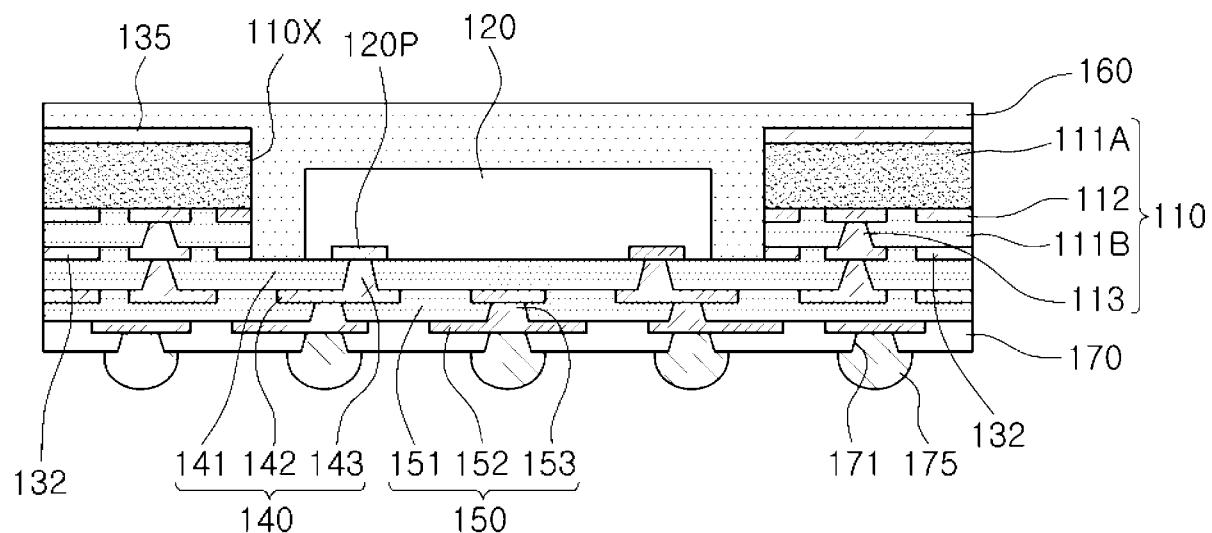

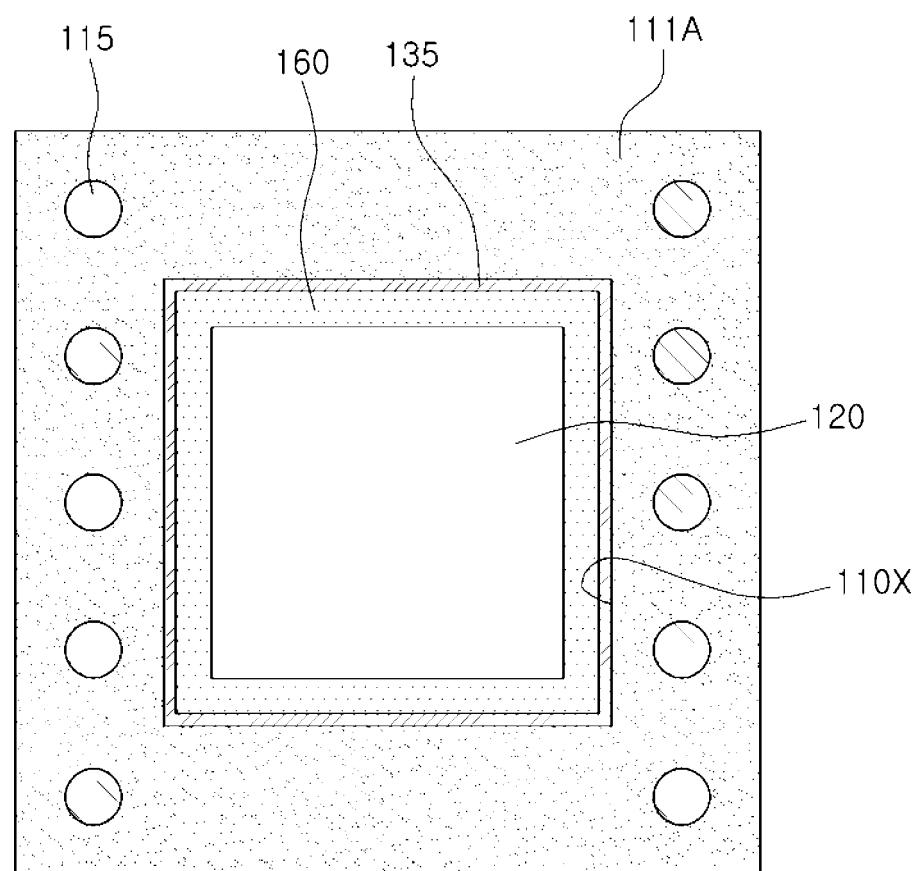

【圖3】

- 100A ··· 電子元件封裝

- 110 ··· 框架

- 110A ··· 上表面

- 110B ··· 下表面

- 110X ··· 貫穿孔

- 111A ··· 第一絕緣層

- 111B ··· 第二絕緣層

- 112 ··· 第一配線層

- 113 ··· 通孔

- 120 ··· 電子元件

- 120P ··· 電極焊墊

- 132 ··· 第二配線層

- 135 ··· 金屬層

- 140 ··· 重新分配部

- 141 ··· 絝緣層

- 142 ··· 配線層

- 143 ··· 通孔

- 150 ··· 重新分配部

- 151 ··· 絝緣層

- 152 ··· 配線層

- 153 ··· 通孔

- 160 ··· 囊封劑

- 170 ··· 保護層

- 171 ··· 第一開口部

- 175 ··· 第一外部連接端子

- I-I' ··· 線

## 【發明圖式】

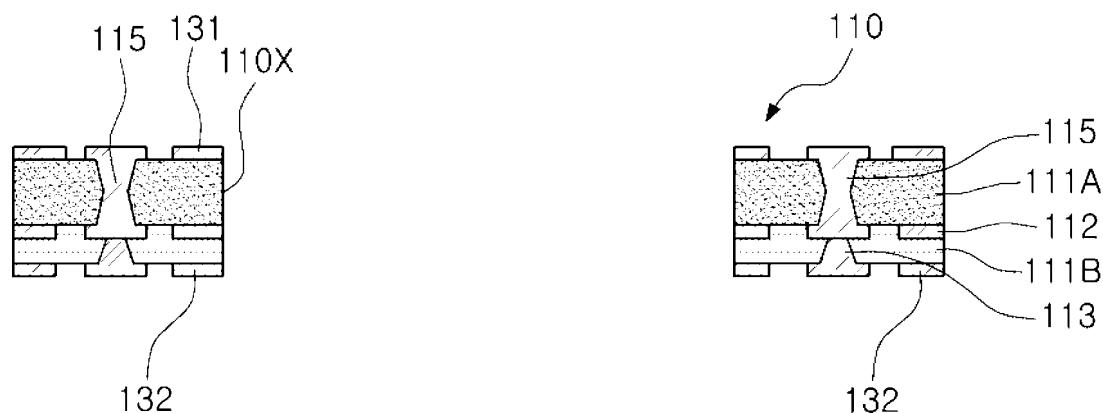

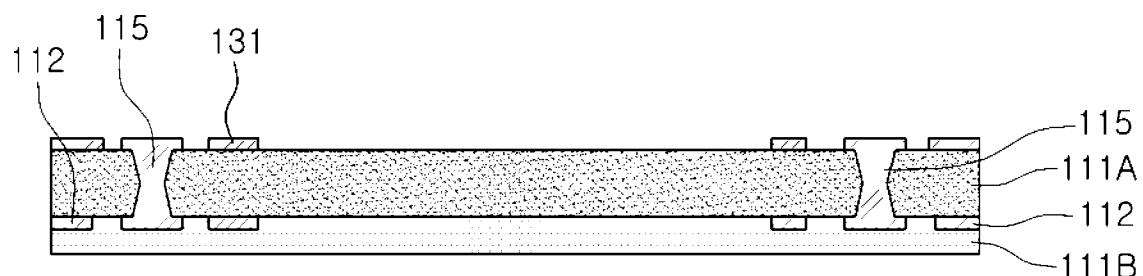

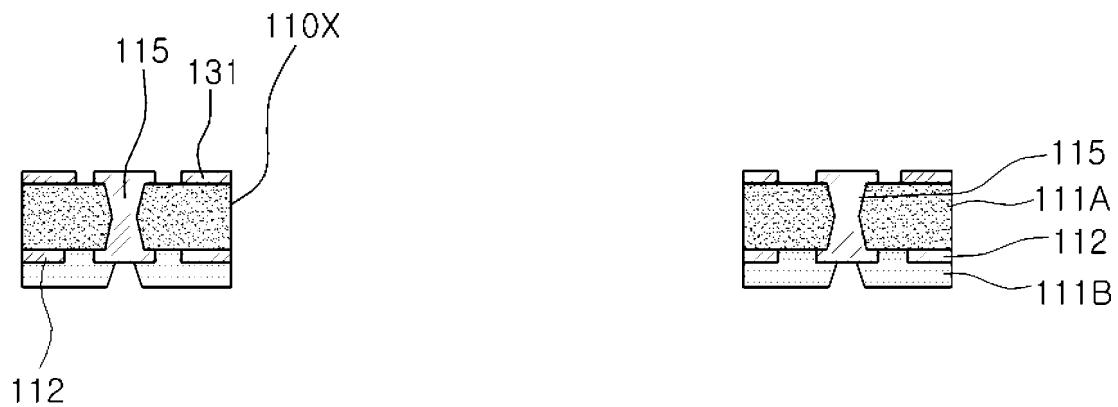

【圖1】

【圖2】

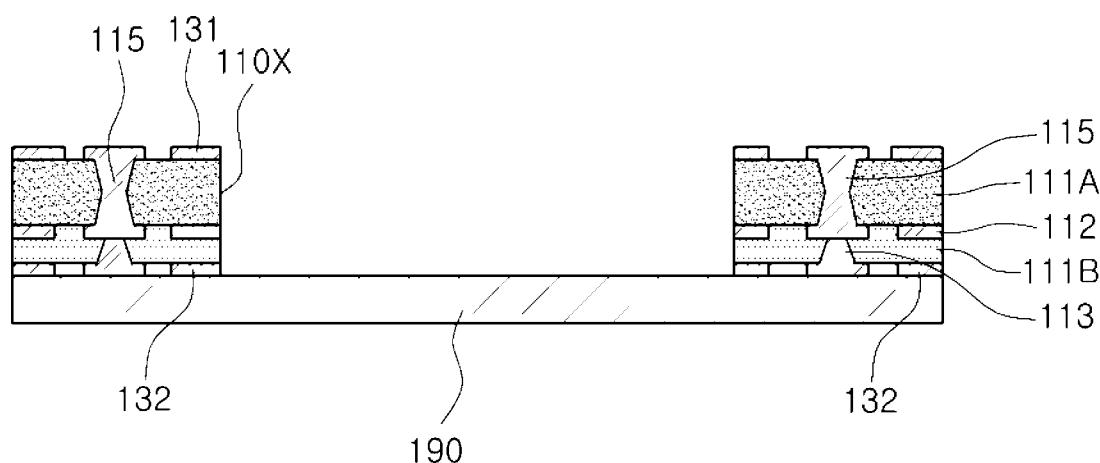

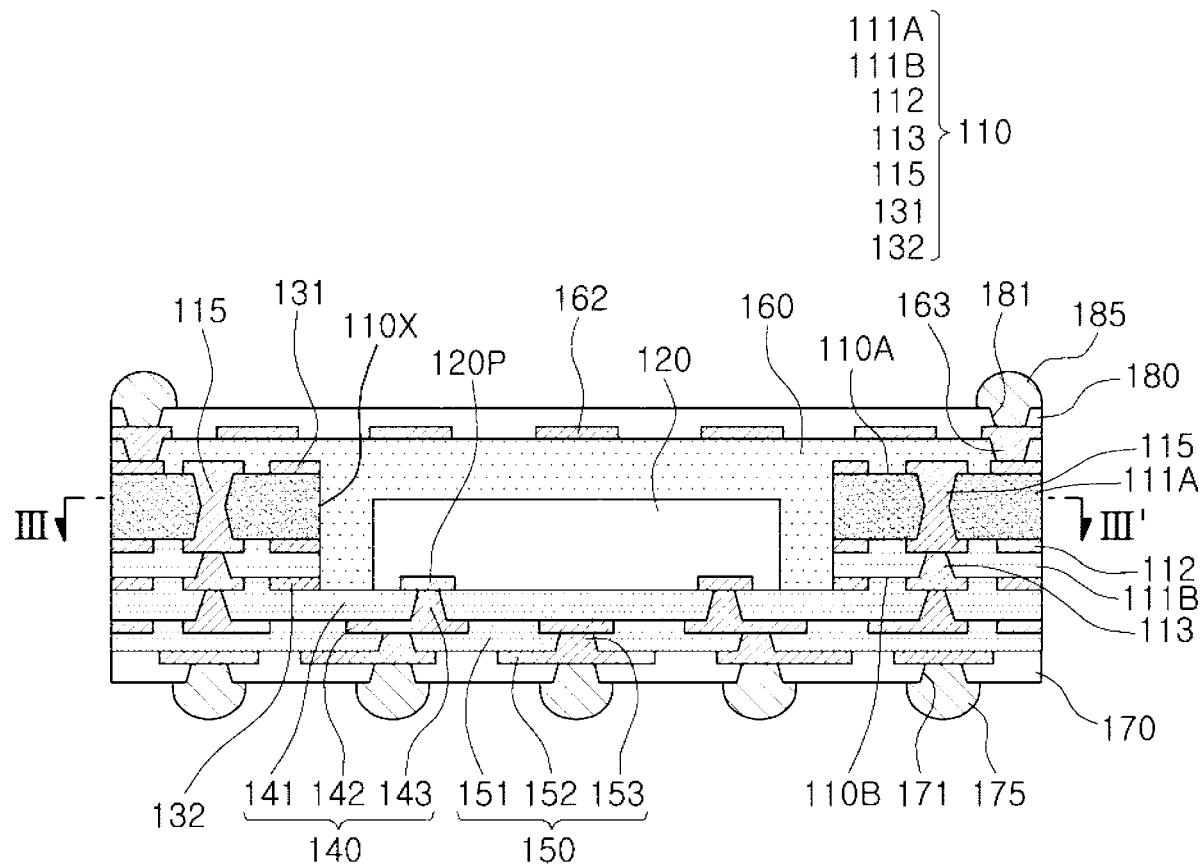

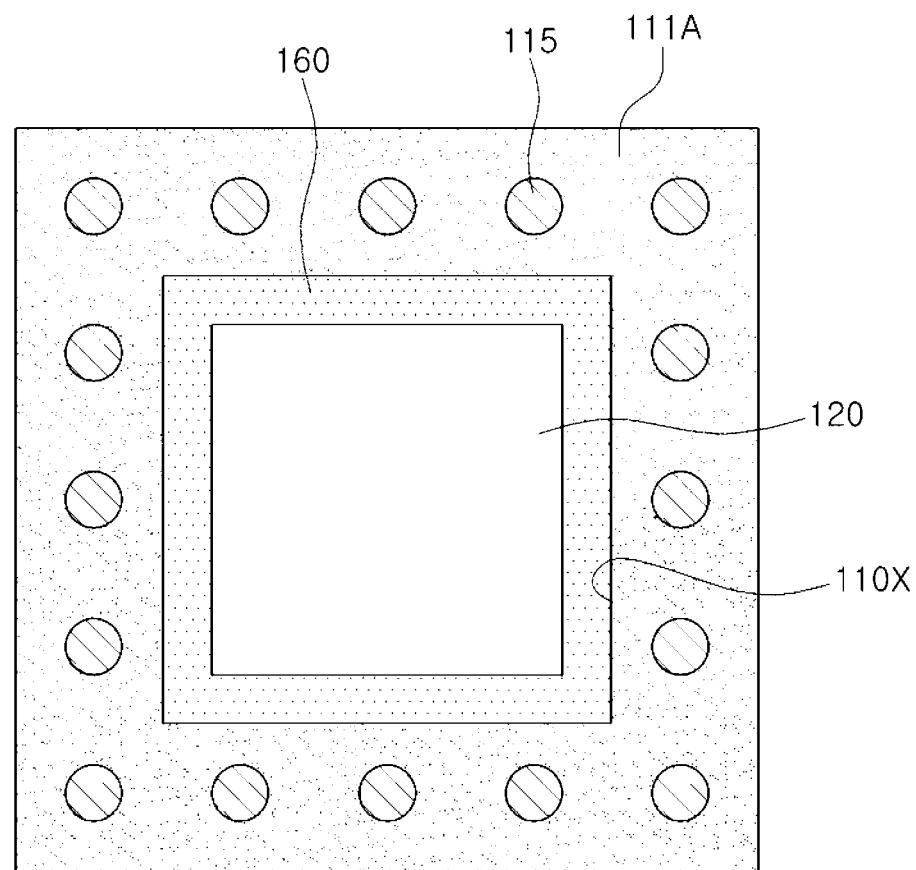

【圖3】

【圖4】

【圖5A】

【圖5B】

【圖5C】

【圖5D】

【圖5E】

【圖5F】

【圖5G】

【圖5H】

【圖5I】

【圖5J】

【圖5K】

【圖5L】

100B

【圖6】

II - II'

【圖7】

【圖8A】

【圖8B】

【圖8C】

【圖8D】

【圖8E】

【圖8F】

【圖8G】

【圖8H】

【圖8I】

【圖8J】

【圖8K】

【圖8L】

(圖8M)

100C

(圖9)

III-III'

【圖10】

【圖11A】

【圖11B】

【圖11C】

【圖11D】

【圖11E】

【圖11F】

【圖11G】

【圖11H】

【圖11I】

【圖11J】

【圖11K】

【圖11L】

【圖11M】

100D

111A

111B

112

113

132

135A

135B

110

【圖12】

IV-IV'

【圖13】

【圖14A】

【圖14B】

【圖14C】

【圖14D】

【圖14E】

【圖14F】

【圖14G】

【圖14H】

【圖14I】

【圖14J】

【圖14K】

【圖14L】

100E

【圖15】

V - V'

【圖16】

【圖17A】

【圖17B】

【圖17C】

【圖17D】

【圖17E】

【圖17F】

【圖17G】

【圖17H】

【圖17I】

【圖17J】

【圖17K】

【圖17L】

【圖17M】

100F

【圖18】

VI-VI'

【圖19】

【圖20A】

【圖20B】

【圖20C】

【圖20D】

【圖20E】

【圖20F】

【圖20G】

【圖20H】

【圖20I】

【圖20J】

【圖20K】

【圖20L】

【圖20M】

【圖21】

【圖22】

100H

111A

111B

112

113

115

131

132

【圖23】

VIII-VIII'

【圖24】

圖25

【圖26】

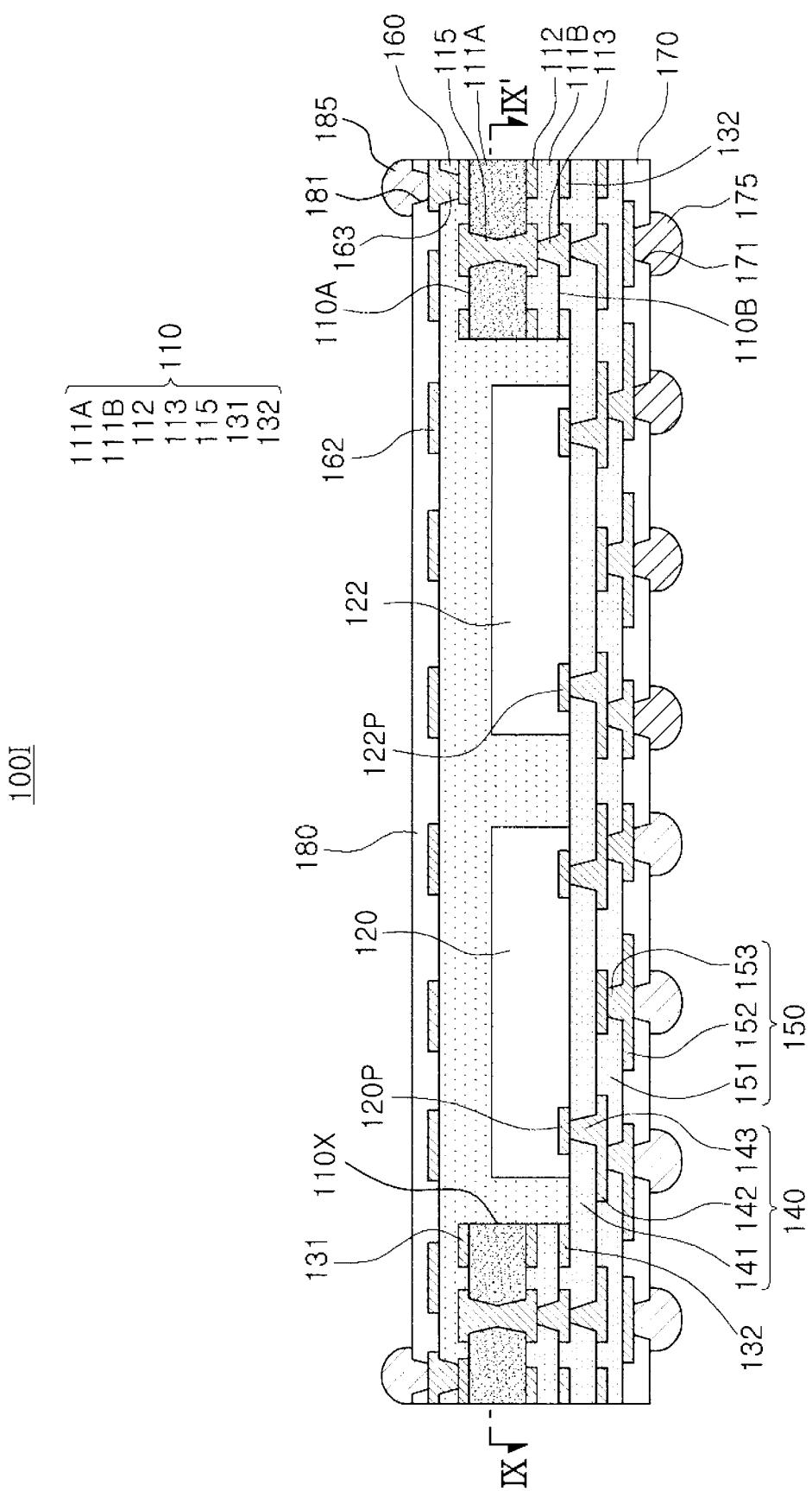

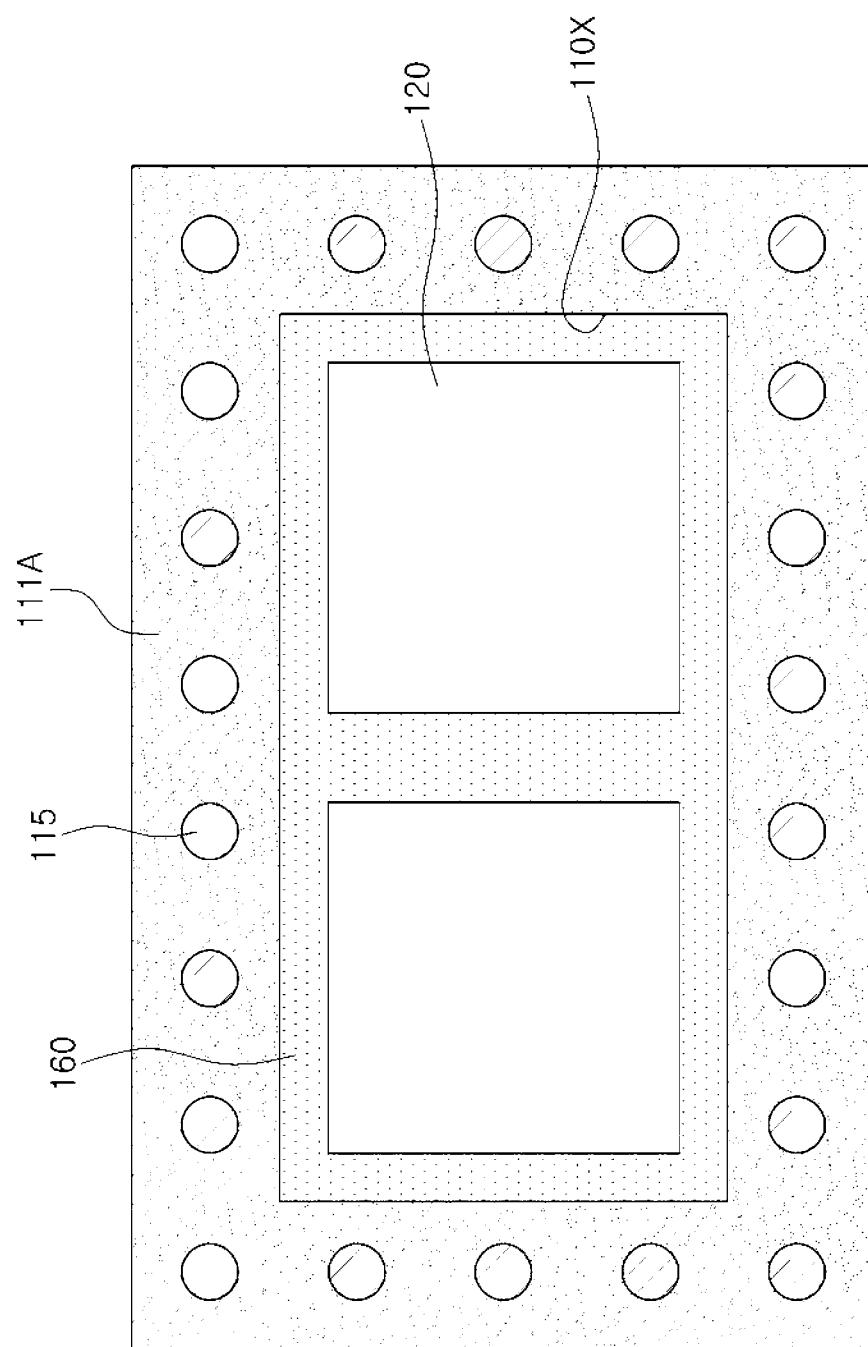

IX-IX'

【圖27】

【圖29】

【圖30】

100L

【圖31】

【圖32】

100M

【圖33】

XIII-XIII'

【圖34】

100N

【圖35】

【圖36】

100P

【圖37】

【圖38】

【圖39】

【圖40】

【圖41】

100R

【圖42】

100S

【圖43】

【圖44】

# 【發明說明書】

【中文發明名稱】扇出半導體封裝及其製造方法

【英文發明名稱】FAN-OUT SEMICONDUCTOR PACKAGE AND

METHOD OF MANUFACTURING THE SAME

[相關申請案的交叉參考]

【0001】本申請案主張於 2015 年 5 月 11 日在韓國智慧財產局提出申請的韓國專利申請案第 10-2015-0065177 號的優先權、於 2015 年 10 月 5 日在韓國智慧財產局提出申請的韓國專利申請案第 10-2015-0139682 號的優先權、及於 2016 年 4 月 19 日在韓國智慧財產局提出申請的韓國專利申請案第 10-2016-0047455 號的優先權，所述韓國專利申請案的揭露內容併入本案供參考。

【技術領域】

【0002】本發明是有關於一種扇出半導體封裝及其製造方法。

【先前技術】

【0003】電子元件封裝被定義成用於將電子元件電性連接至例如電子裝置的主板等印刷電路板（printed circuit board，PCB）、並保護電子元件不受外部衝擊的封裝技術，並且與將電子元件嵌置於例如插板基板（interposer substrate）等印刷電路板中的嵌置技術有所區別。同時，與電子元件相關的技術發展中的當前主要趨勢之一是減小電子元件的尺寸。因而，在封裝領域中，且隨著對緊湊電子元件等的需求的快速增加，已經需要實作具有小的尺寸且

包括多個引腳的電子元件封裝。

**【0004】** 為滿足上述技術需求，所建議的一種封裝技術為利用晶圓上所形成的電子元件的電極焊墊的重新分配配線的晶圓級封裝（wafer level package，WLP）。所述晶圓級封裝的實例包括扇入（fan-in）式晶圓級封裝及扇出（fan-out）式晶圓級封裝。具體而言，扇出式晶圓級封裝具有緊湊的尺寸且有利於實作多個引腳。因而，近來，扇出式晶圓級封裝已得到積極開發。

**【0005】** 同時，由於晶圓級封裝的結構特性，因此重新分配部是在電子元件安置於晶圓上之後被固定。在此種情形中，在安置電子元件之後的製程中發生的缺陷會導致電子元件的良率降低。

### 【發明內容】

**【0006】** 本發明的態樣可提供一種可解決電子元件的良率降低問題的電子元件封裝、其製造方法、及堆疊式封裝（package-on-package）結構。

**【0007】** 根據本發明的態樣，可提供一種可在安置電子元件之前引入能夠執行電子元件的重新分配功能的配線層的新式封裝結構。

**【0008】** 根據本發明的態樣，一種電子元件封裝可包括：框架，具有貫穿孔及一或多個第一配線層；電子元件，安置於所述框架的所述貫穿孔中；以及重新分配部，安置於所述框架及所述電子元件的一側上，其中所述一或多個第一配線層經由所述重新分配部而電性連接至所述電子元件。

105-10-17

**【0009】** 根據本發明的另一態樣，一種電子元件封裝可包括：框架，包括第一絕緣層、安置於所述第一絕緣層下的二或更多個配線層、及安置於所述二或更多個配線層之間的第二絕緣層；電子元件，安置於穿透過所述框架的貫穿孔中；以及重新分配部，電性連接至所述二或更多個配線層及所述電子元件且安置於所述電子元件上，其中所述二或更多個配線層及所述第二絕緣層安置於所述重新分配部與所述第一絕緣層之間。

**【0010】** 根據本發明的另一態樣，一種製造電子元件封裝的方法可包括：藉由製備第一絕緣層、在所述第一絕緣層的一側形成第一配線層、在所述第一絕緣層的一側形成其中嵌置有所述第一配線層的第二絕緣層、以及形成穿透過所述第一絕緣層及所述第二絕緣層的貫穿孔而形成框架；將電子元件安置於所述框架的所述貫穿孔中；以及在所述框架及所述電子元件的一側形成重新分配部，其中所述第一配線層是在所述電子元件的所述安置之前形成。

**【0011】** 根據本發明的另一態樣，一種製造電子元件封裝的方法可包括：製備包括多個絕緣層及多個配線層的框架；形成穿透過整個所述框架的貫穿孔；將所述框架及電子元件貼附至臨時基板上，其中所述電子元件位於所述框架的所述貫穿孔內；藉由將囊封劑至少填充至所述框架的所述貫穿孔中而囊封所述電子元件；將所述臨時基板自所述框架的表面、所述囊封劑的表面及所述電子元件的表面分離；以及將重新分配部形成至所述框架的所述表面、所述囊封劑的所述表面及所述電子元件的所述表面上，且因

105-10-17

此所述重新分配部將所述電子元件電性連接至所述框架的所述多個配線層。

### 【圖式簡單說明】

**【0012】** 藉由結合附圖閱讀以下詳細說明，將更清楚地理解本發明的以上及其他態樣、特徵及優點，在附圖中：

圖 1 是示意性地說明電子裝置系統的實例的方塊圖。

圖 2 是示意性地說明用於電子裝置中的電子元件封裝的實例的圖。

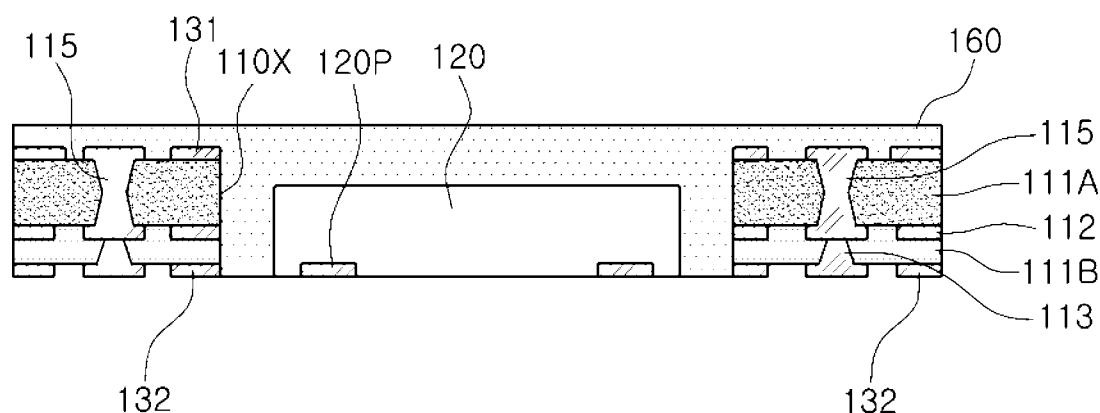

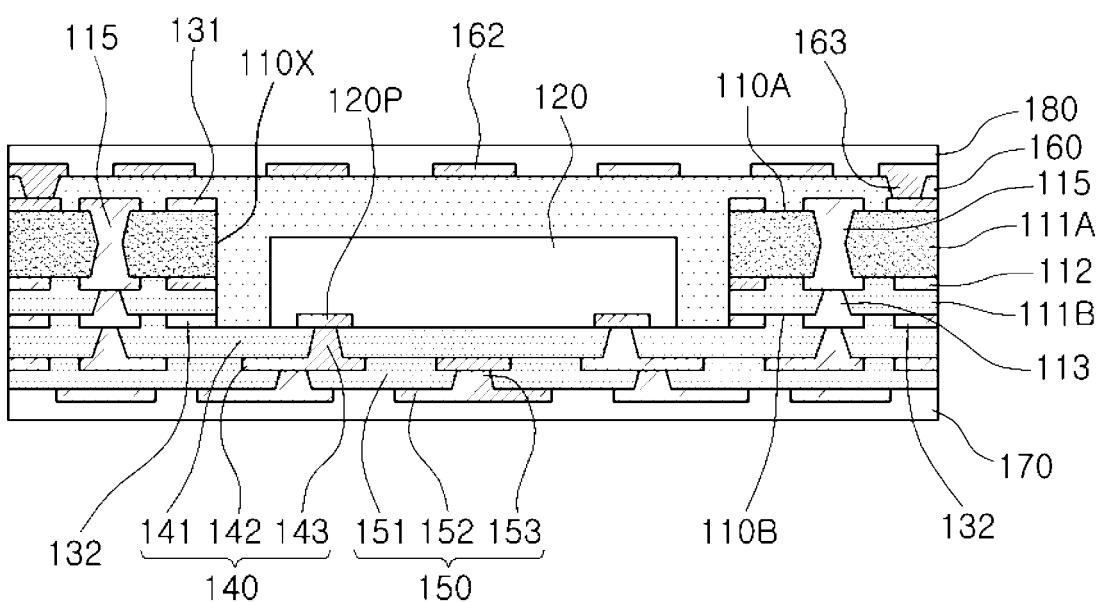

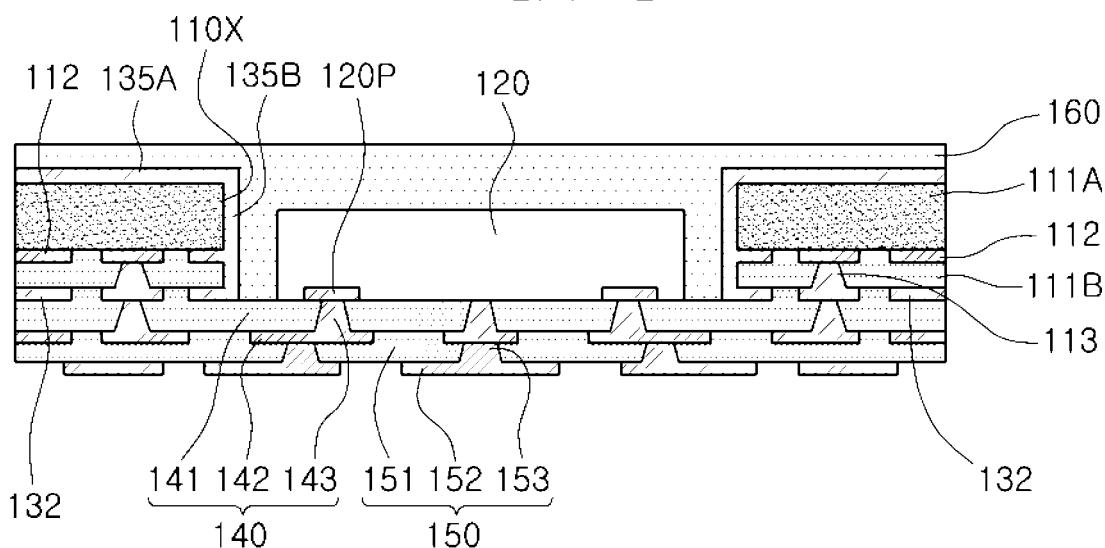

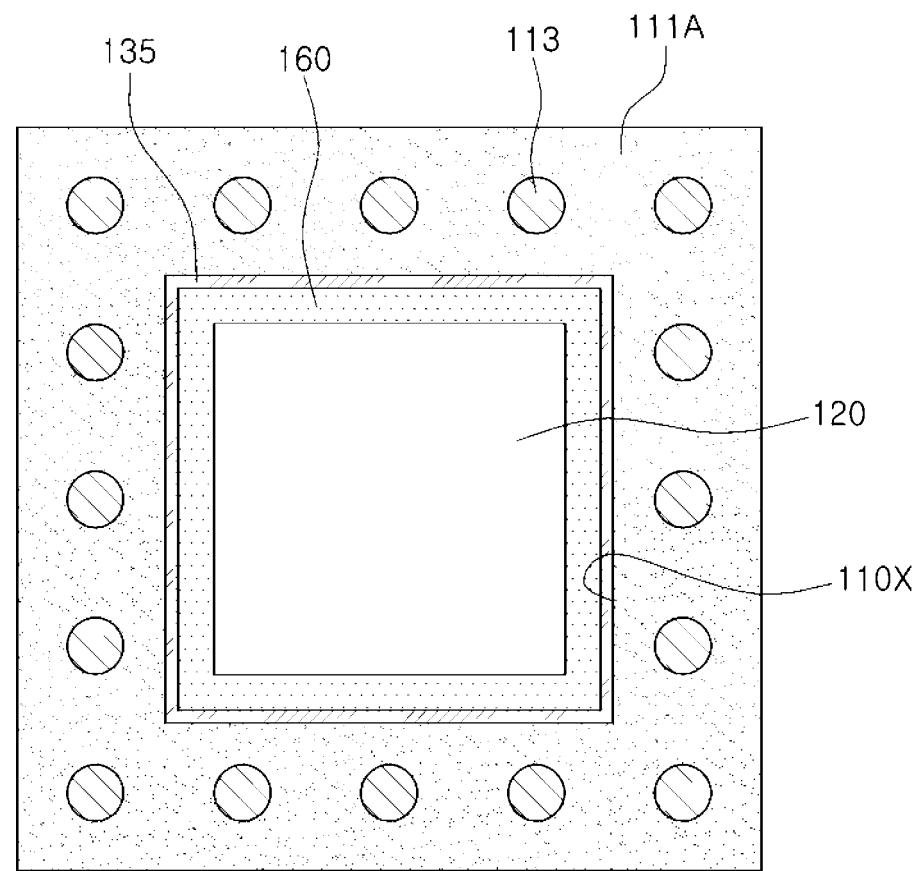

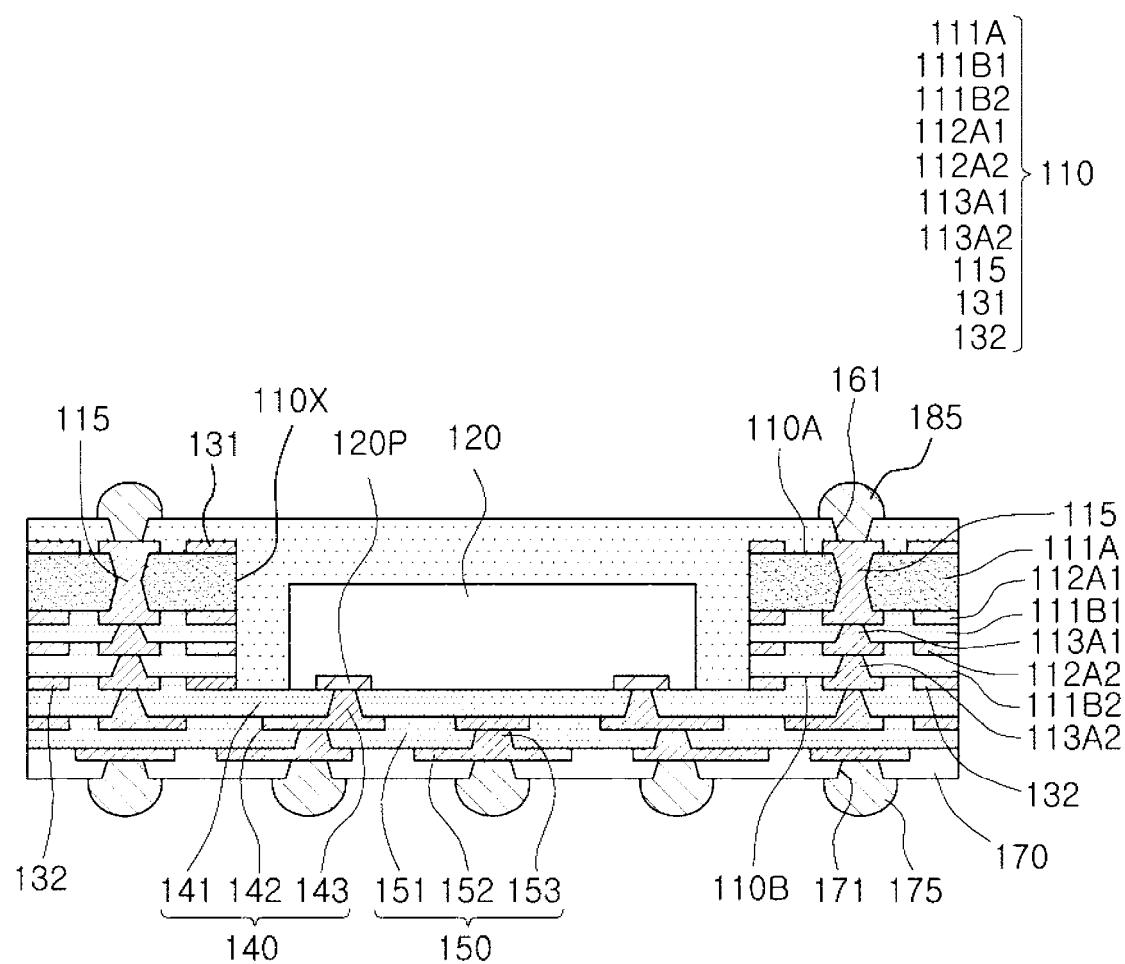

圖 3 是示意性地說明電子元件封裝的實例的剖視圖。

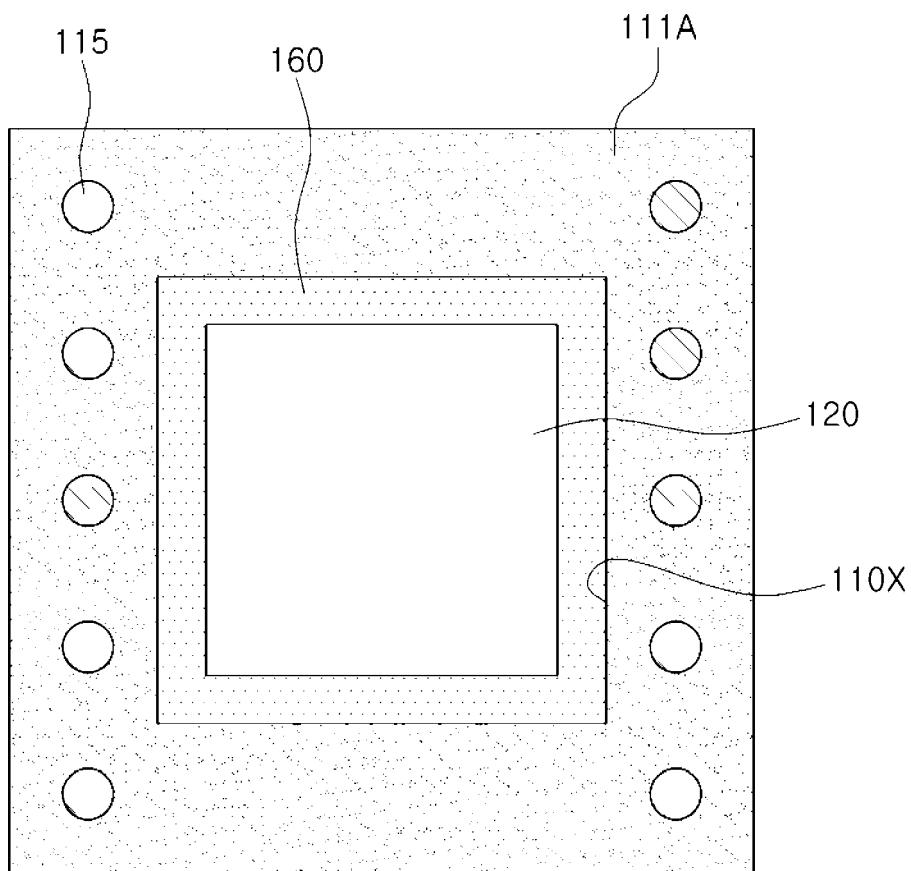

圖 4 是電子元件封裝沿圖 3 所示的線 I-I' 截取的示意性平面圖。

圖 5A 至圖 5L 是說明製造圖 3 所示電子元件封裝的製程的實例的示意圖。

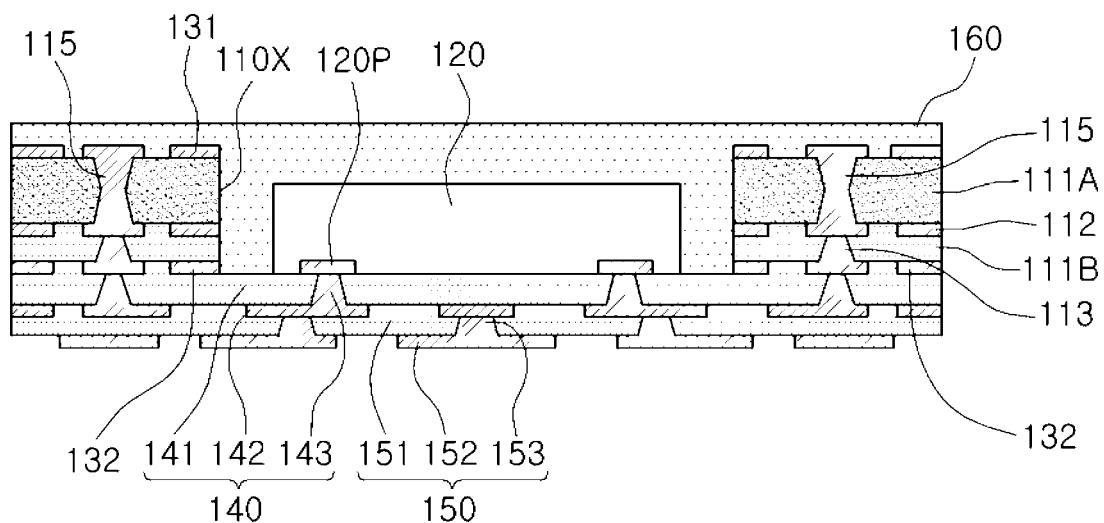

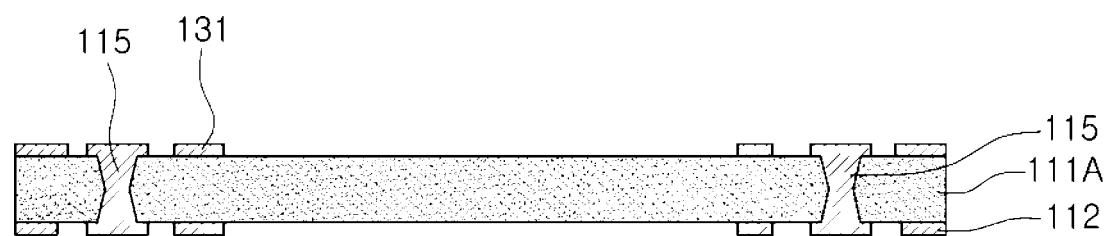

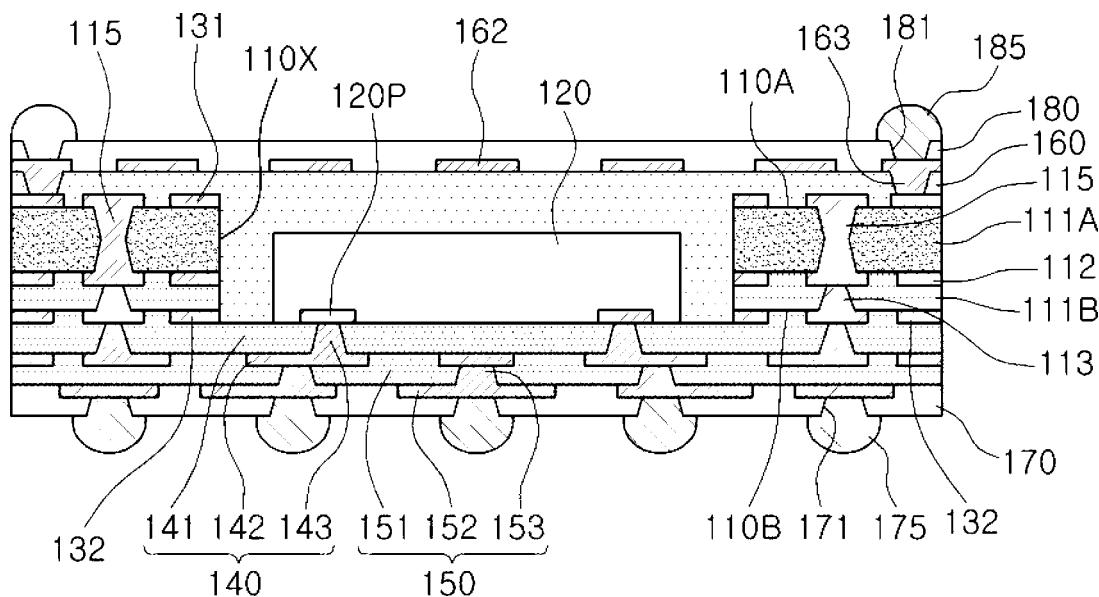

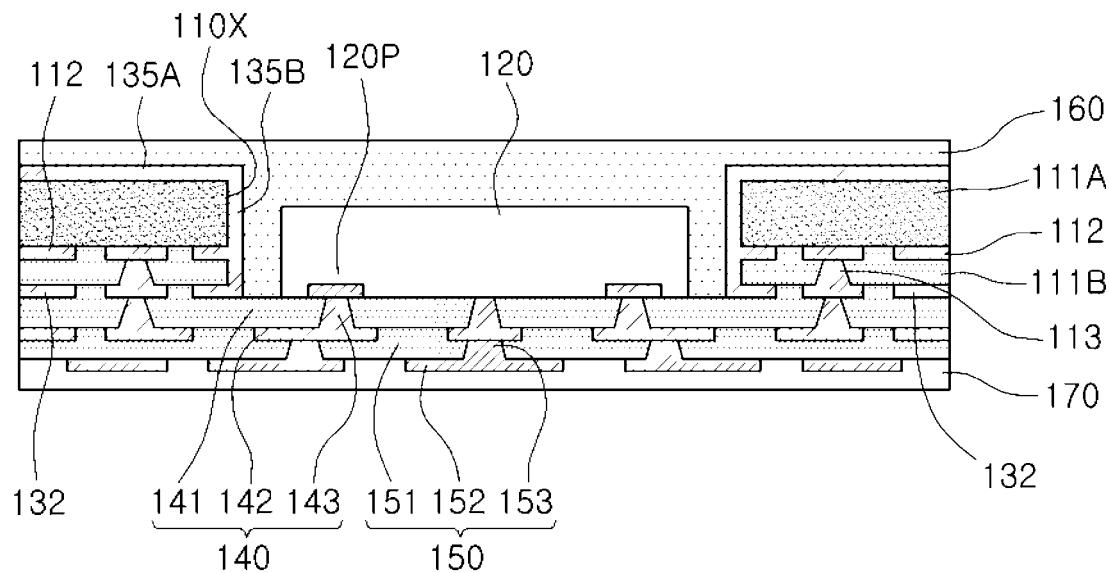

圖 6 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 7 是電子元件封裝沿圖 6 所示的線 II-II' 截取的示意性平面圖。

圖 8A 至圖 8M 是說明製造圖 6 所示電子元件封裝的製程的實例的示意圖。

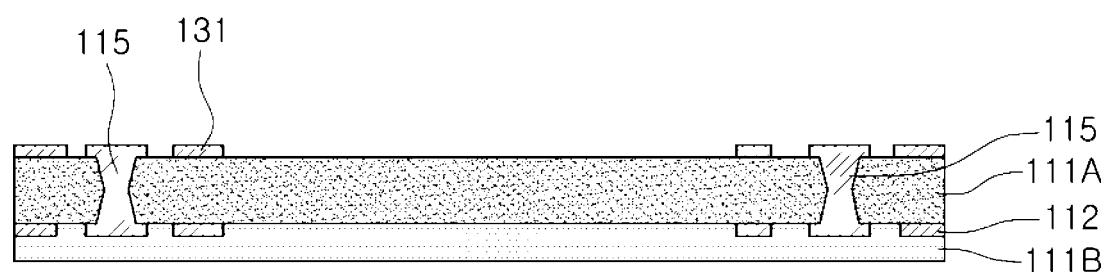

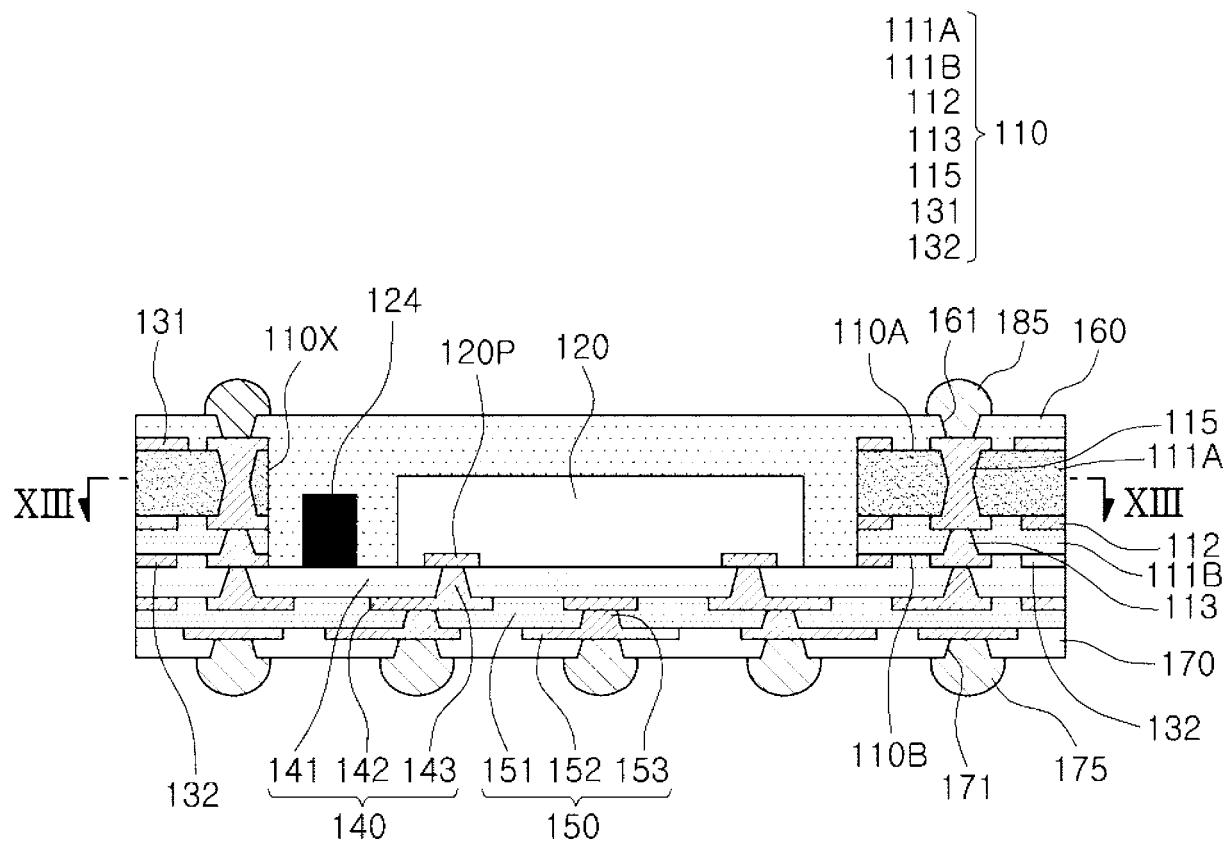

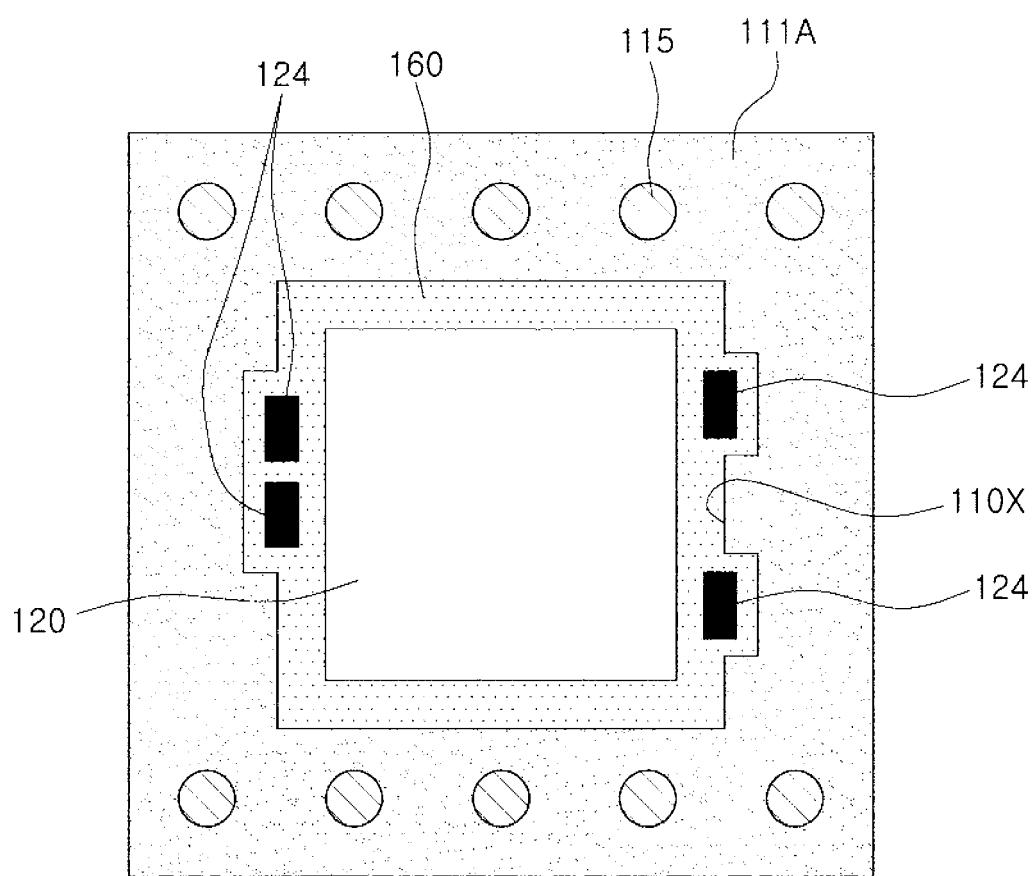

圖 9 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 10 是電子元件封裝沿圖 9 所示的線 III-III' 截取的示意性平面圖。

圖 11A 至圖 11M 是說明製造圖 9 所示電子元件封裝的製程的

實例的示意圖。

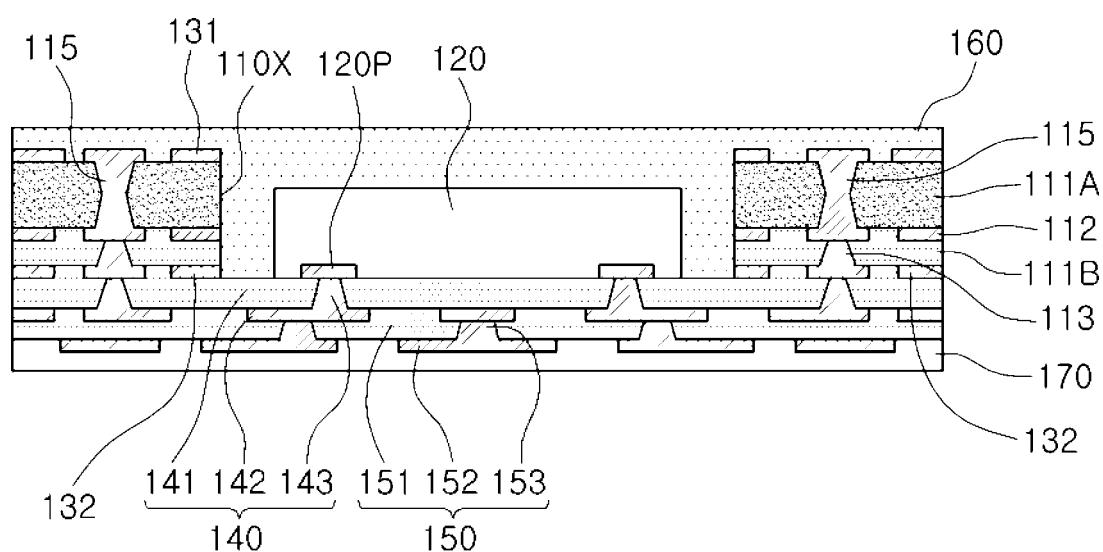

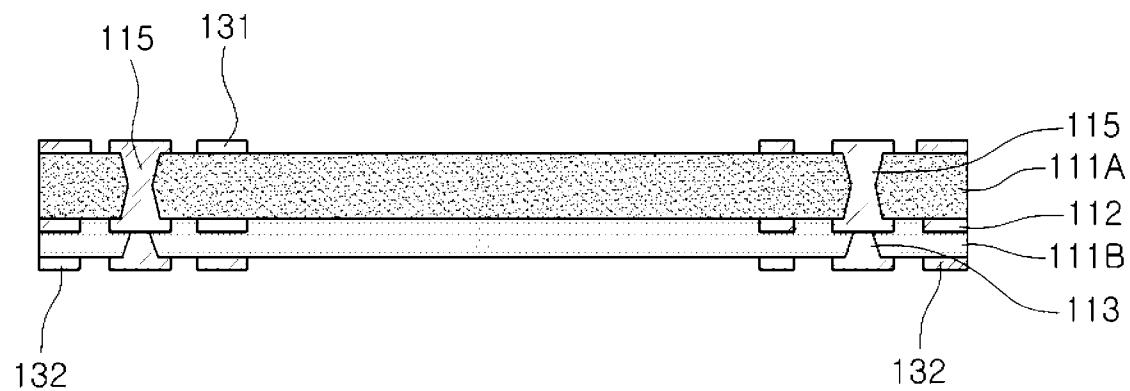

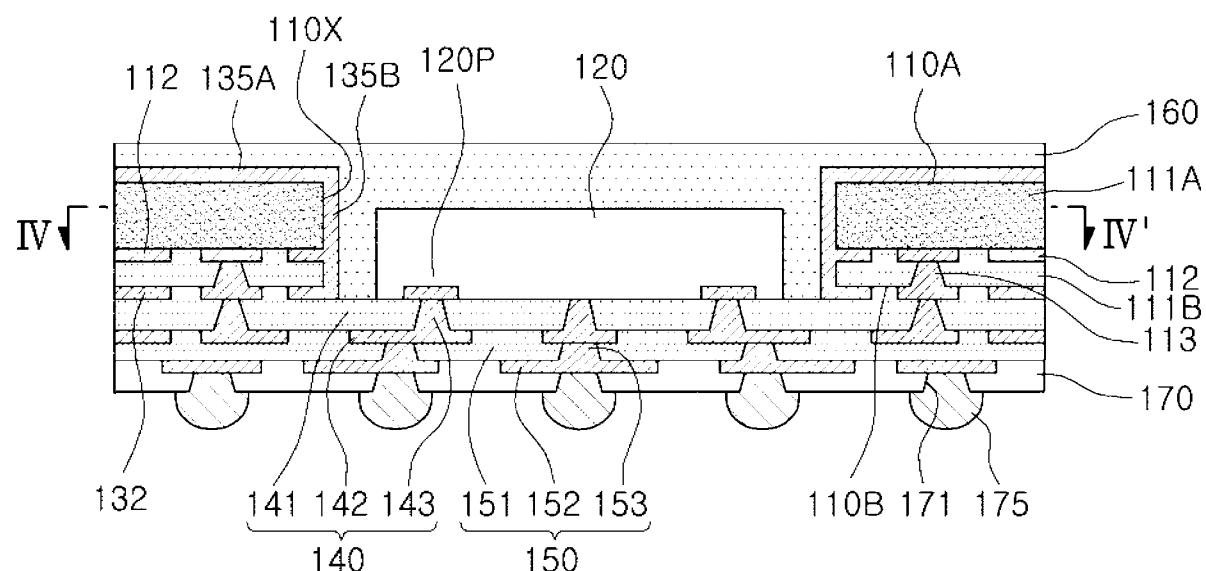

圖 12 是示意性地說明電子元件封裝的另一實例的剖視圖。

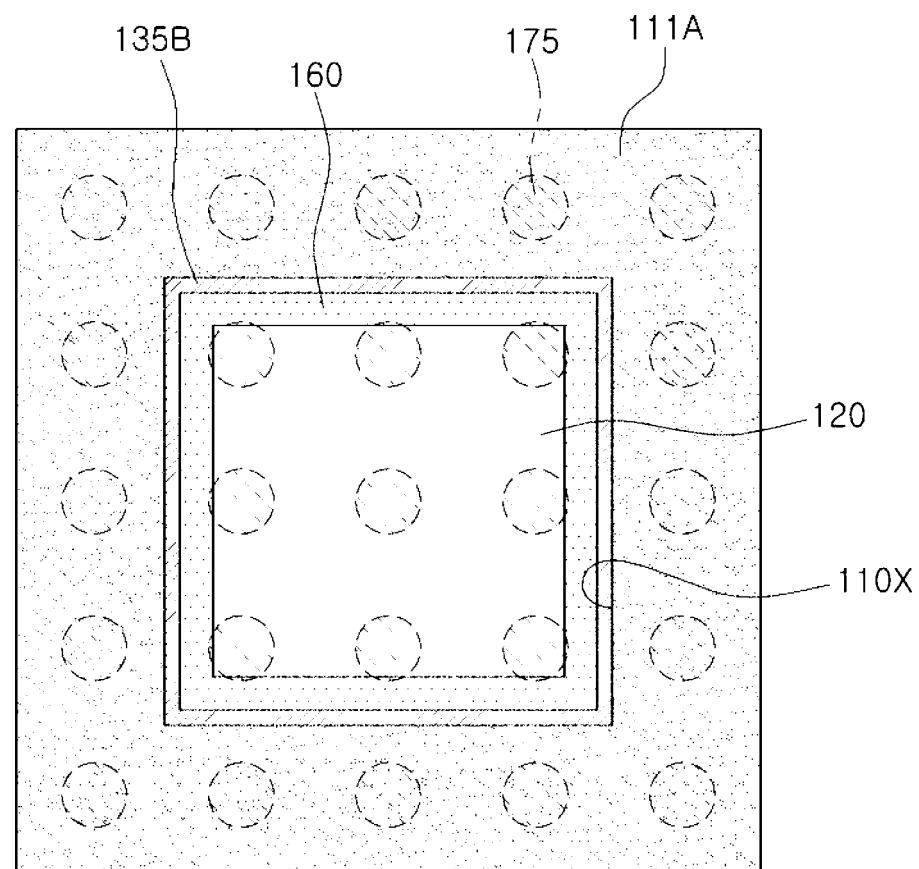

圖 13 是電子元件封裝沿圖 12 所示的線 IV-IV' 截取的示意性平面圖。

圖 14A 至圖 14L 是說明製造圖 12 所示電子元件封裝的製程的實例的示意圖。

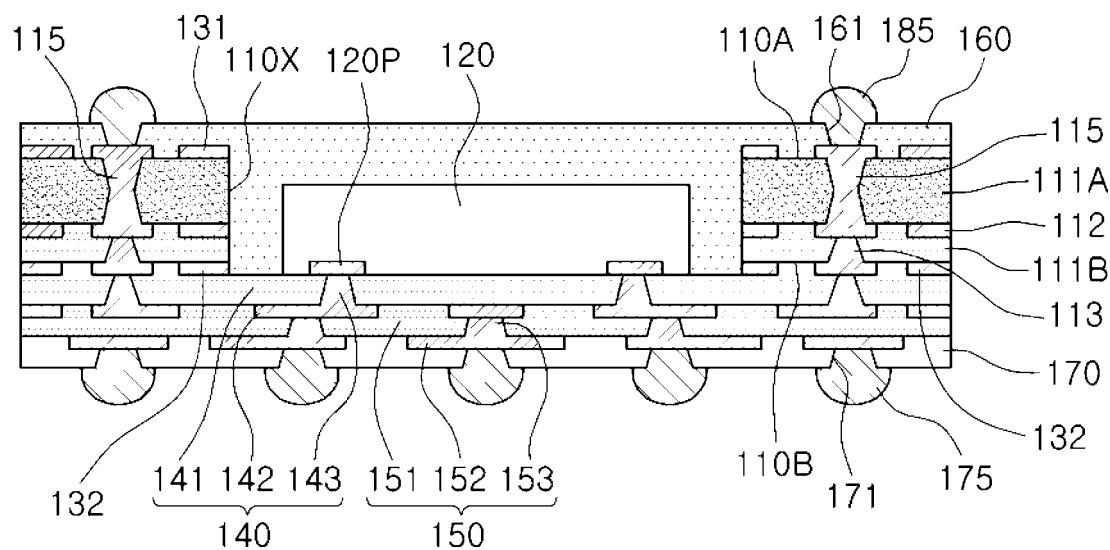

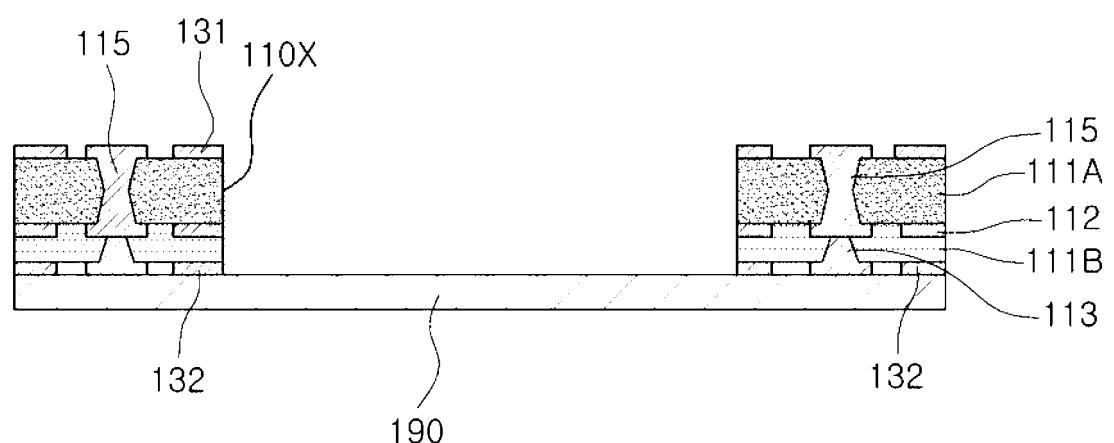

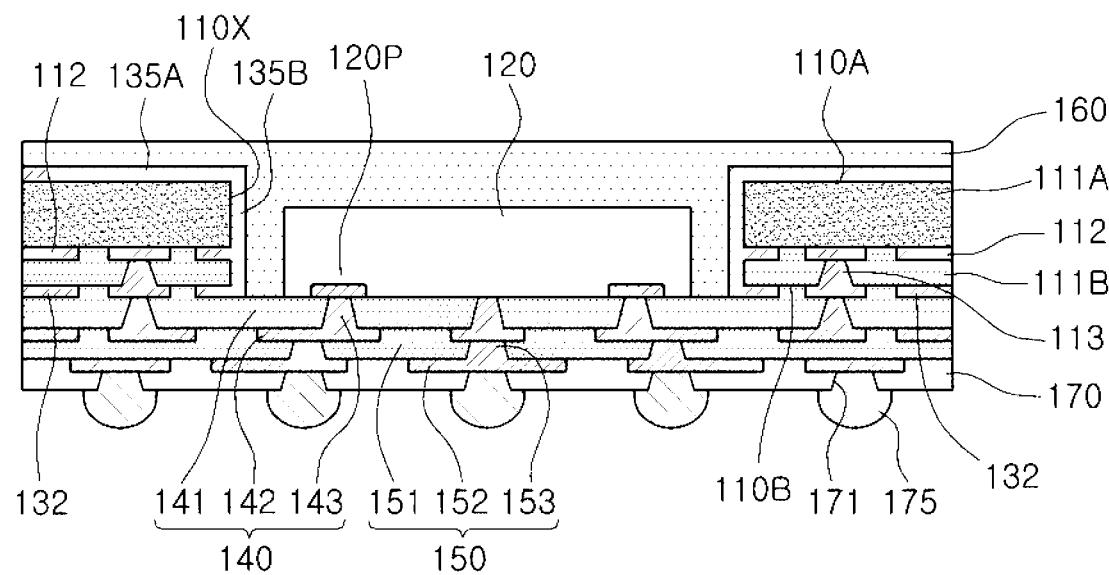

圖 15 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 16 是電子元件封裝沿圖 15 所示的線 V-V' 截取的示意性平面圖。

圖 17A 至圖 17M 是說明製造圖 15 所示電子元件封裝的製程的實例的示意圖。

圖 18 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 19 是電子元件封裝沿圖 18 所示的線 VI-VI' 截取的示意性平面圖。

圖 20A 至圖 20M 是說明製造圖 18 所示電子元件封裝的製程的實例的示意圖。

圖 21 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 22 是電子元件封裝沿圖 21 所示的線 VII-VII' 截取的示意性平面圖。

圖 23 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 24 是電子元件封裝沿圖 23 所示的線 VIII-VIII' 截取的示意性平面圖。

105-10-17

圖 25 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 26 是電子元件封裝沿圖 25 所示的線 IX-IX' 截取的示意性平面圖。

圖 27 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 28 是電子元件封裝沿圖 27 所示的線 X-X' 截取的示意性平面圖。

圖 29 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 30 是電子元件封裝沿圖 29 所示的線 XI-XI' 截取的示意性平面圖。

圖 31 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 32 是電子元件封裝沿圖 31 所示的線 XII-XII' 截取的示意性平面圖。

圖 33 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 34 是電子元件封裝沿圖 33 所示的線 XIII-XIII' 截取的示意性平面圖。

圖 35 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 36 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 37 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 38 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 39 是示意性地說明電子元件封裝的訊號傳遞的實例的圖。

圖 40 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 41 是示意性地說明電子元件封裝的另一實例的剖視圖。

105-10-17

圖 42 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 43 是示意性地說明電子元件封裝的另一實例的剖視圖。

圖 44 是示意性地說明電子元件封裝的另一實例的剖視圖。

## 【實施方式】

**【0013】** 在下文中，將參照附圖對本發明的實施例進行如下闡述。

**【0014】** 然而，本發明可被示例成諸多不同的形式，而不應被視為僅限於本文中所述的具體實施例。確切而言，提供該些實施例是為了使此揭露內容將透徹及完整，並將向熟習此項技術者充分傳達本發明的範圍。

**【0015】** 在本說明書通篇中，應理解，當稱一組件（例如，層、區、或晶圓（基板））位於另一組件「上」、「連接至」、或「耦合至」另一組件時，所述組件可直接位於所述另一組件「上」、直接「連接至」、或直接「耦合至」所述另一組件、抑或其間可存在其他中間組件。相比之下，當稱一組件「直接位於」另一組件「上」、「直接連接至」、或「直接耦合至」另一組件時，其間可不存在中間組件或層。在通篇中相同的編號指代相同的組件。本文中所使用的用語「及/或」包含相關列出項其中一或多個項的任意及所有組合。

**【0016】** 將顯而易見，儘管本文中可能使用「第一」、「第二」、「第三」等用語來闡述各種構件、元件、區、層及/或區段，然而該些構件、元件、區、層及/或區段不應受限於該些用語。該些用語僅用於區分各個構件、元件、區、層或區段。因而，在不背離示例

105-10-17

性實施例的教示內容的條件下，以下所論述的第一構件、元件、區、層或區段可被稱為第二構件、元件、區、層或區段。

**【0017】** 在本文中，為易於說明，可使用例如「在…之上（above）」、「上方的（upper）」、「在…之下（below）」及「下方的（lower）」等空間相對性用語來闡述圖中所示的一個組件相對於另一（其他）組件的關係。應理解，該些空間相對性用語旨在除圖中所繪示定向以外亦囊括裝置在使用或操作中的不同定向。舉例而言，若圖中的裝置被翻轉，則被闡述為在其他組件「之上」或「上方」的組件此時將被定向為在其他組件或特徵「之下」或「下方」。因此，依圖的具體方向而定，用語「在…之上」可囊括上方與下方兩種定向。所述裝置亦可具有其他定向（例如，旋轉90度或處於其他定向），且本文中所用的空間相對性描述語可相應地進行解釋。

**【0018】** 本文所用術語僅用於闡述具體實施例，且本發明並不以其限制。除非上下文中清楚地另外指明，否則本文所用的單數形式「一」及「所述」旨在亦包含複數形式。更應理解，當在本說明書中使用用語「包括（comprises 及/或 comprising）」時，是指明所陳述特徵、整數、步驟、操作、構件、組件及/或其群組的存在，但不排除一或多個其他特徵、整數、步驟、操作、構件、組件及/或其群組的存在或添加。

**【0019】** 在下文中，將參照說明本發明實施例的示意圖來闡述本發明的實施例。在圖式中，可估計會因例如製造技術及/或容差而

105-10-17

造成對所示形狀的修改。因此，本發明的實施例不應被視為僅限於本文中所示區的特定形狀，而是例如包含由製造而引起的形狀變化。以下實施例亦可由其中的一者或其組合構成。

**【0020】** 以下所闡述的本發明的內容可具有多種構型且在本文中可僅提出所需要的構型，但並非僅限於此。

### **【0021】 電子裝置**

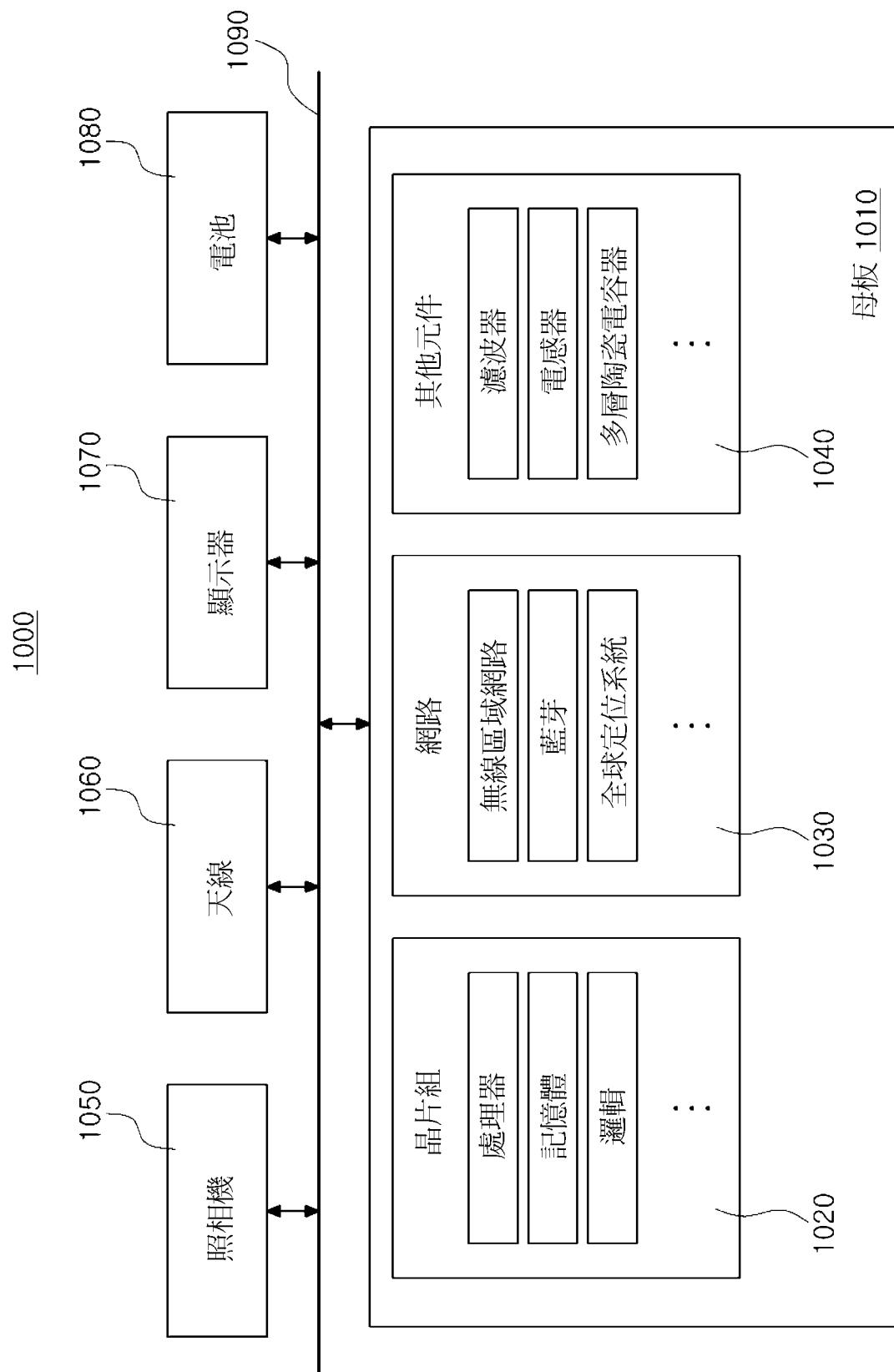

**【0022】** 圖 1 是示意性地說明電子裝置系統的實例的方塊圖。

**【0023】** 參照圖 1，電子裝置 1000 中可容置有母板 1010。晶片相關元件 1020、網路相關元件 1030、其他元件 1040 等可物理地連接至及/或電性連接至母板 1010。該些元件可經由各種訊號線 1090 而連接至以下將闡述的其他元件。

**【0024】** 晶片相關元件 1020 可包括：記憶體晶片，例如揮發性記憶體（例如，動態隨機存取記憶體（dynamic random access memory, DRAM）、非揮發性記憶體（例如，唯讀記憶體（read only memory, ROM））、快閃記憶體等；應用處理器晶片，例如中央處理器（例如，中央處理單元（central processing unit, CPU））、圖形處理器（例如，圖形處理單元（graphic processing unit, GPU））、數位訊號處理器、密碼學處理器（cryptographic processor）、微處理器、微控制器等；邏輯晶片，例如類比 - 數位轉換器（analog-to-digital converter）、應用專用積體電路（application-specific integrated circuit, ASIC）等；以及類似元件。然而，晶片相關元件 1020 並非僅限於此，而是亦可包括其他類型

105-10-17

的晶片相關元件。此外，該些元件 1020 可彼此組合。

**【0025】** 網路相關元件 1030 可包括例如以下協定：無線保真 ( wireless fidelity , Wi-Fi ) ( 電氣及電子工程師學會 ( Institute of Electrical and Electronics Engineers , IEEE ) 802.11 家族等 ) 、全球互通微波存取 ( worldwide interoperability for microwave access , WiMAX )( IEEE 802.16 家族等 ) 、 IEEE 802.20 、長期演進 ( long term evolution , LTE ) 、僅支援資料的演進 ( evolution data only , Ev-DO ) 、高速封包存取 + ( high speed packet access + , HSPA+ ) 、高速下行封包存取 + ( high speed downlink packet access + , HSDPA+ ) 、高速上行封包存取 + ( high speed uplink packet access + , HSUPA+ ) 、增強型資料 GSM 環境 ( enhanced data GSM environment , EDGE ) 、全球行動通訊系統 ( global system for mobile communications , GSM ) 、全球定位系統 ( global positioning system , GPS ) 、通用封包無線電服務 ( general packet radio service , GPRS ) 、分碼多重存取 ( code division multiple access , CDMA ) 、分時多重存取 ( time division multiple access , TDMA ) 、數位增強型無線電訊 ( digital enhanced cordless telecommunications , DECT ) 、藍芽、 3G 協定、 4G 協定、 5G 協定及繼上述協定之後指定的任何其他無線協定及有線協定。然而，網路相關元件 1030 並非僅限於此，且亦可包括多個其他無線標準或協定或者有線標準或協定中的任一者。此外，該些元件 1030 可與上述晶片相關元件 1020 一起相互組合。

**【0026】** 其他元件 1040 可包括高頻電感器、鐵氧體電感器 ( ferrite

105-10-17

inductor)、功率電感器、鐵氧體珠粒、低溫共燒陶瓷 (low temperature co-firing ceramic, LTCC)、電磁干擾 (electromagnetic interference, EMI) 濾波器、多層陶瓷電容器 (multilayer ceramic capacitor, MLCC) 等。然而，其他元件 1040 並非僅限於此，而是亦可包括用於各種其他目的的被動元件等。此外，該些其他元件 1040 可與以上所述晶片相關元件 1020 及/或網路相關元件 1030 一起相互組合。

**【0027】** 依其種類而定，電子裝置 1000 可包括可物理地連接至及/或電性連接至母板 1010 或可不物理地連接至及/或不電性連接至母板 1010 的其他元件。該些其他元件可包括例如照相機 1050、天線 1060、顯示器 1070、電池 1080、音訊編解碼器 (圖中未示出)、視訊編解碼器 (圖中未示出)、功率放大器 (圖中未示出)、羅盤 (圖中未示出)、加速度計 (圖中未示出)、陀螺儀 (圖中未示出)、揚聲器 (圖中未示出)、大容量儲存器 (例如，硬碟驅動機) (圖中未示出)、光碟 (compact disk, CD) (圖中未示出)、數位多功能光碟 (digital versatile disk, DVD) (圖中未示出) 等。然而，該些其他元件並非僅限於此，而是依電子裝置 1000 的類型而定亦可包括用於各種目的的其他元件。

**【0028】** 電子裝置 1000 可為智慧型電話、個人數位助理、數位攝影機、數位照相機 (digital still camera)、網路系統、電腦、監視器、平板電腦 (tablet)、膝上型電腦、隨身型易網機 (netbook)、電視、視訊遊戲機 (video game console)、智慧型手錶等。然而，

105-10-17

電子裝置 1000 並非僅限於此，而是亦可為用於處理資料的任何其他電子裝置。

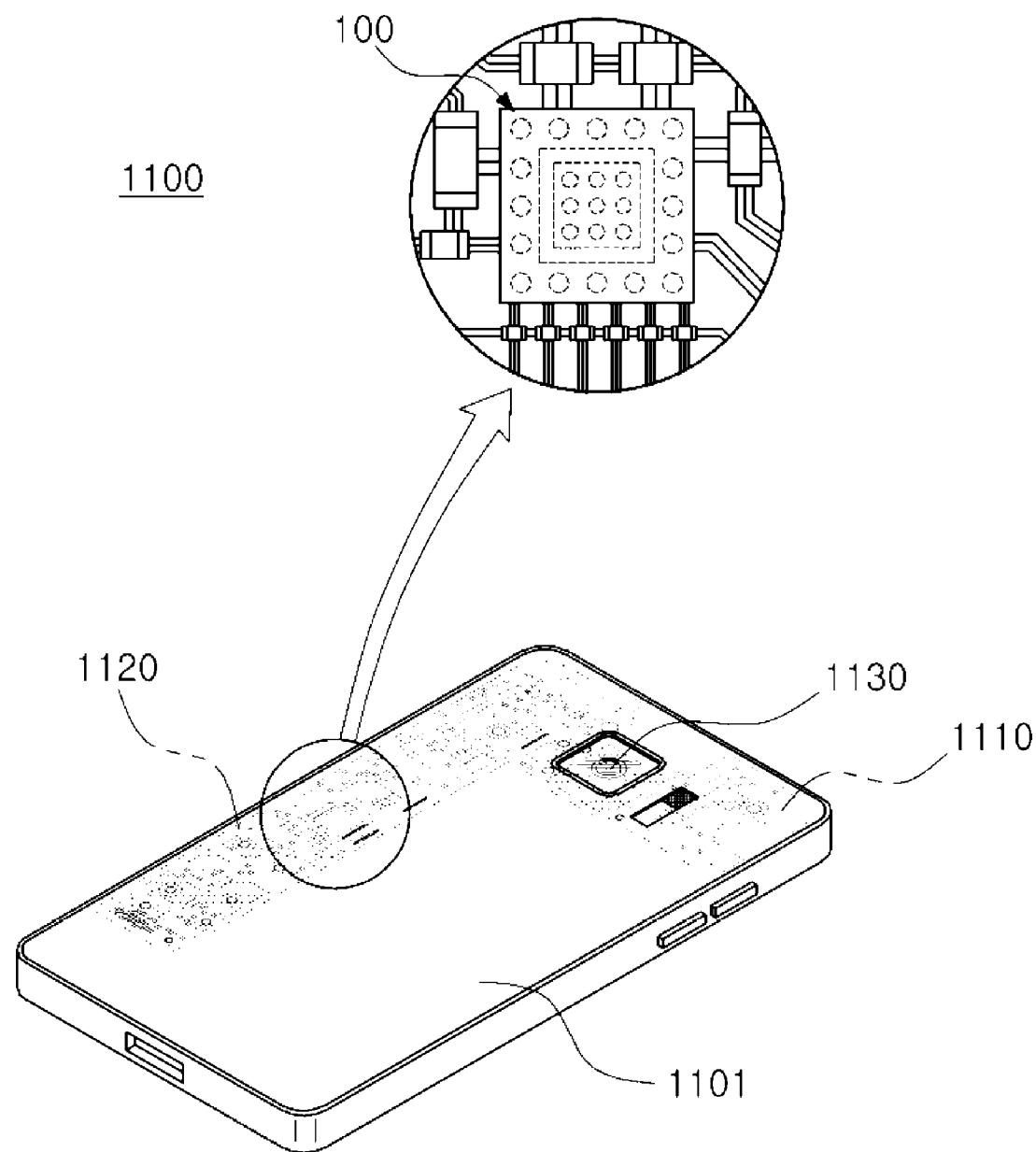

**【0029】** 圖 2 是示意性地說明用於電子裝置中的電子元件封裝的實例的圖。

**【0030】** 所述電子元件封裝可出於各種目的而用於如上所述的各種電子裝置 1000 中。舉例而言，主板 1110 可容置於智慧型電話 1100 的主體 1101 中，且各種電子元件 1120 可物理地連接至及/或電性連接至主板 1110。此外，可物理地連接至及/或電性連接至主板 1110 或可不物理地連接至及/或不電性連接至主板 1110 的另一元件（例如，照相機 1130）可容置於主體 1101 中。此處，電子元件 1120 中的某些電子元件 1120 可為如上所述的晶片相關元件，且電子元件封裝 100 可為例如晶片相關元件中的應用處理器，但並非僅限於此。

### **【0031】 電子元件封裝**

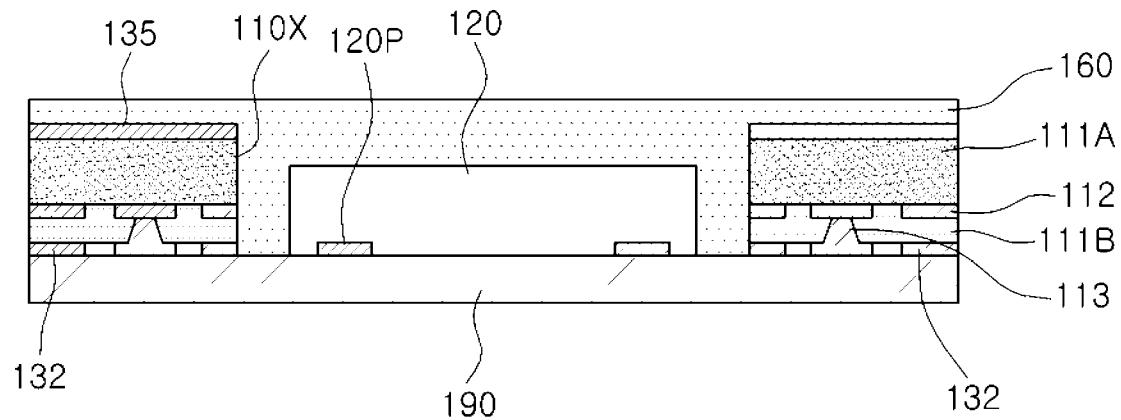

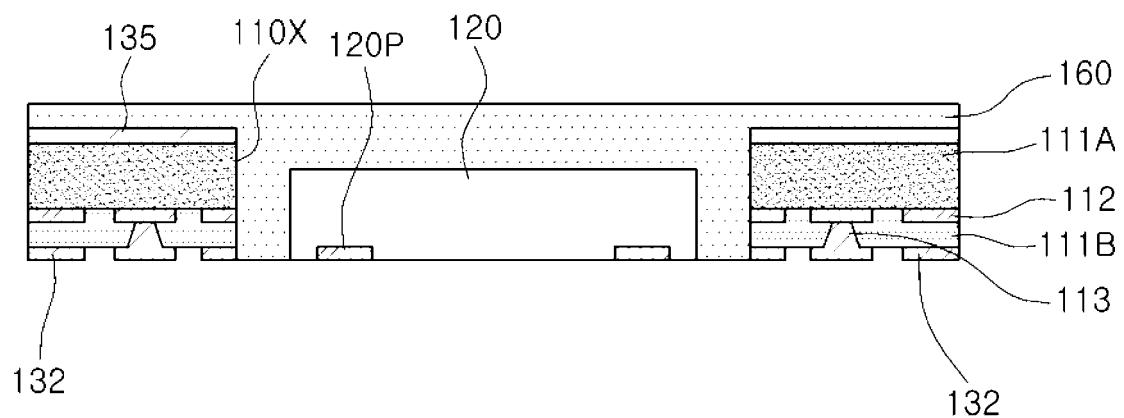

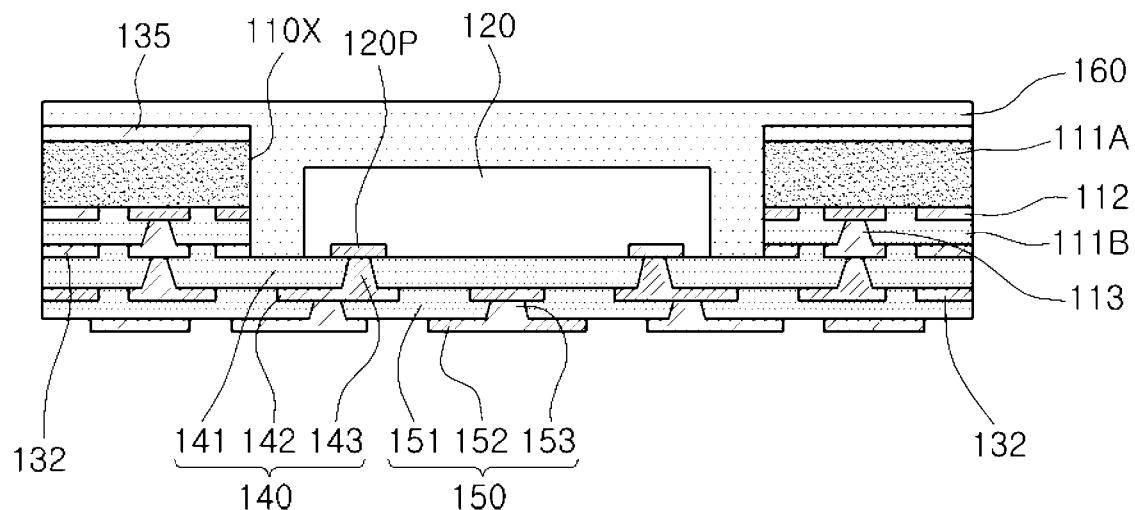

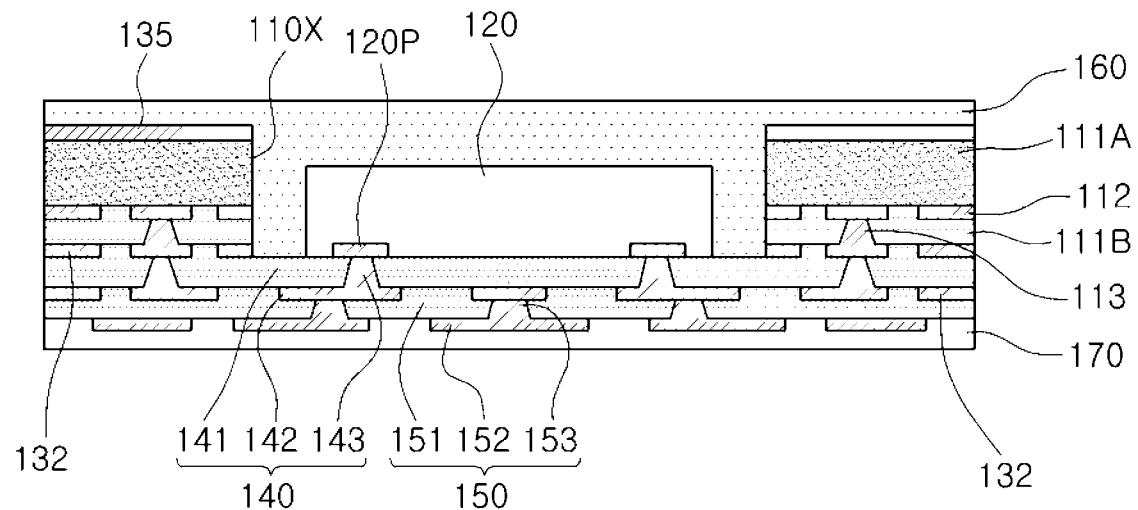

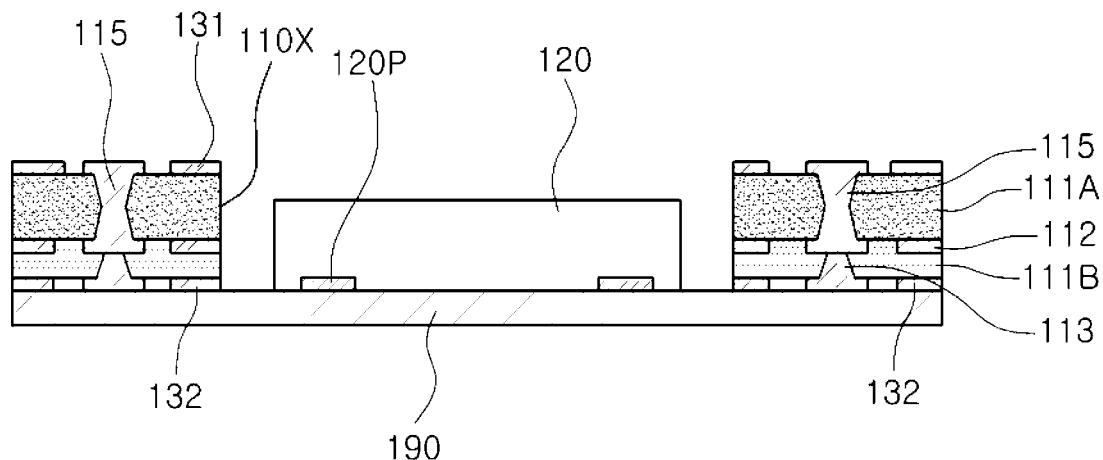

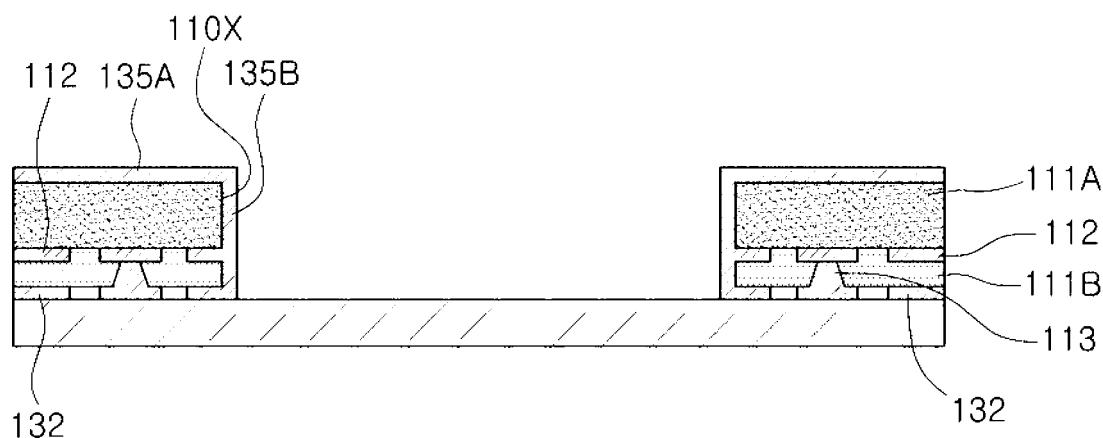

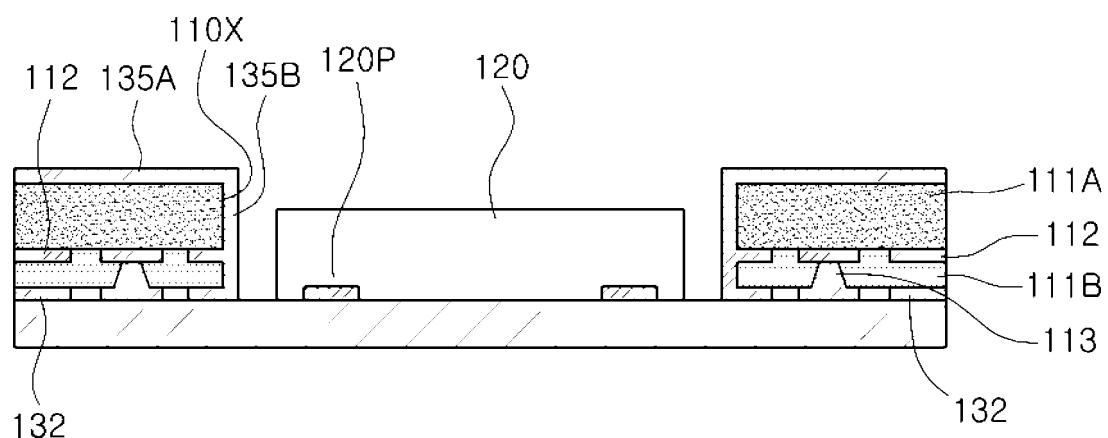

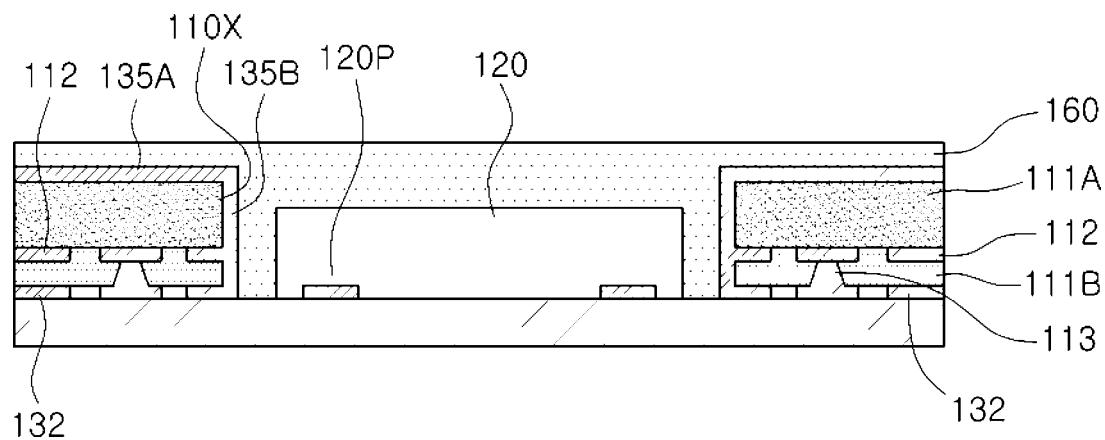

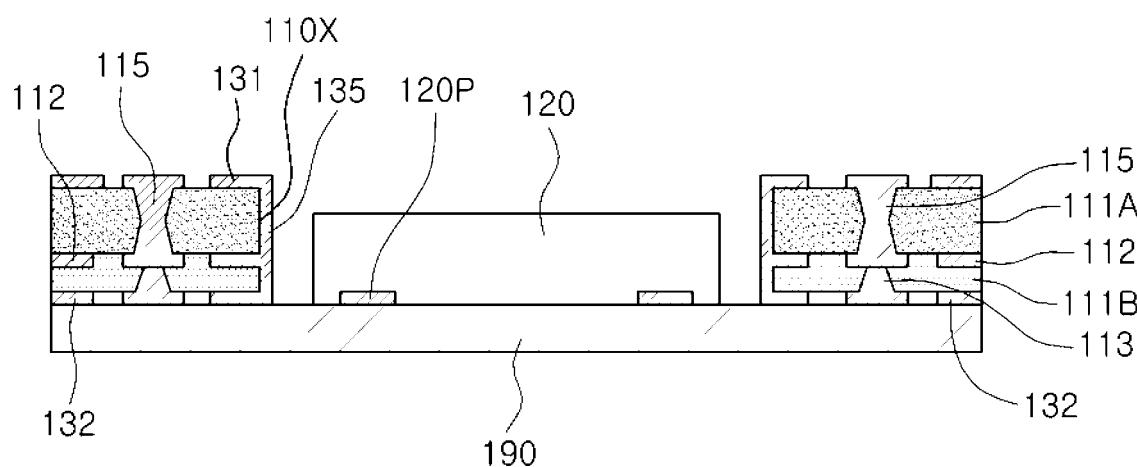

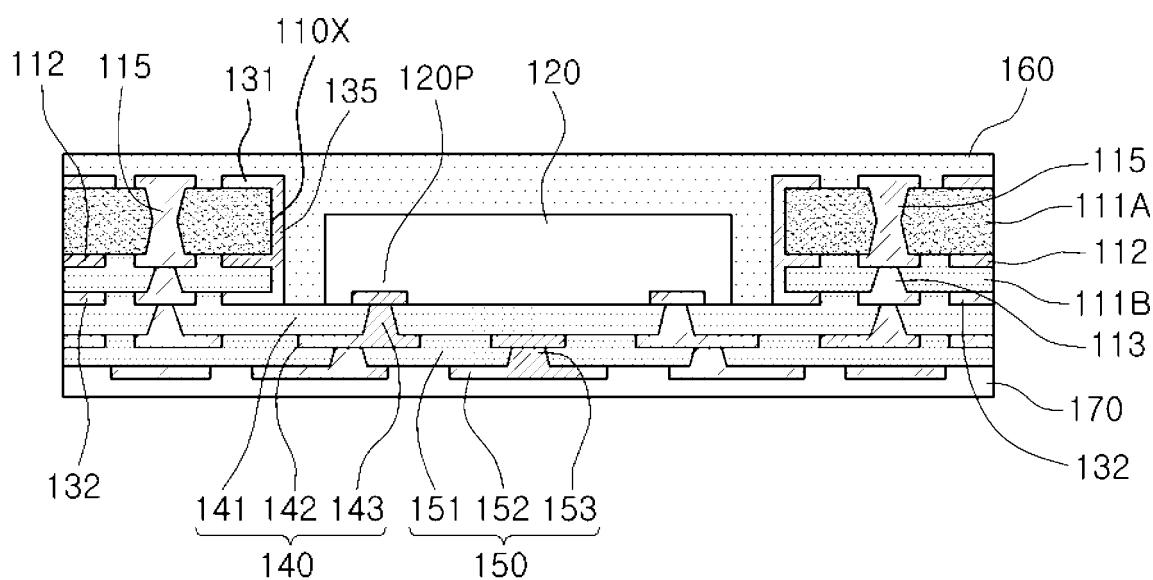

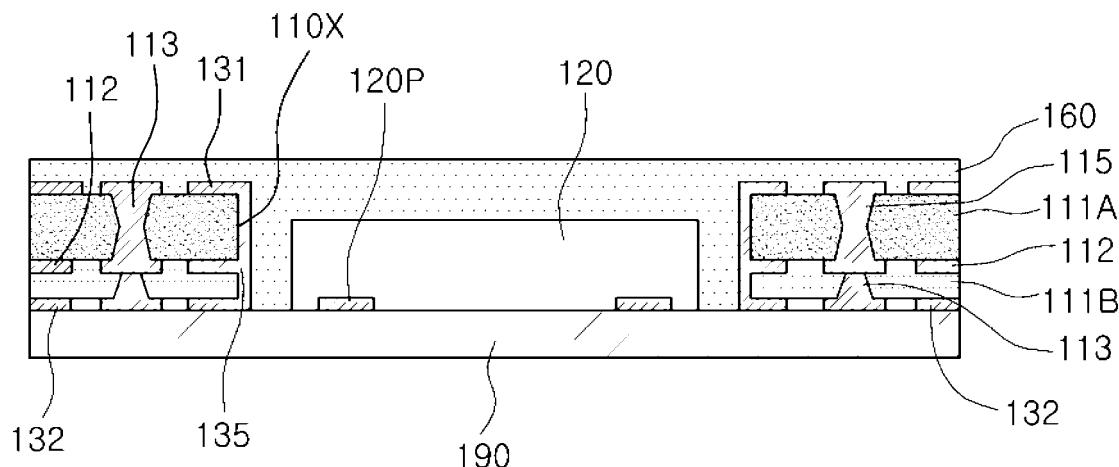

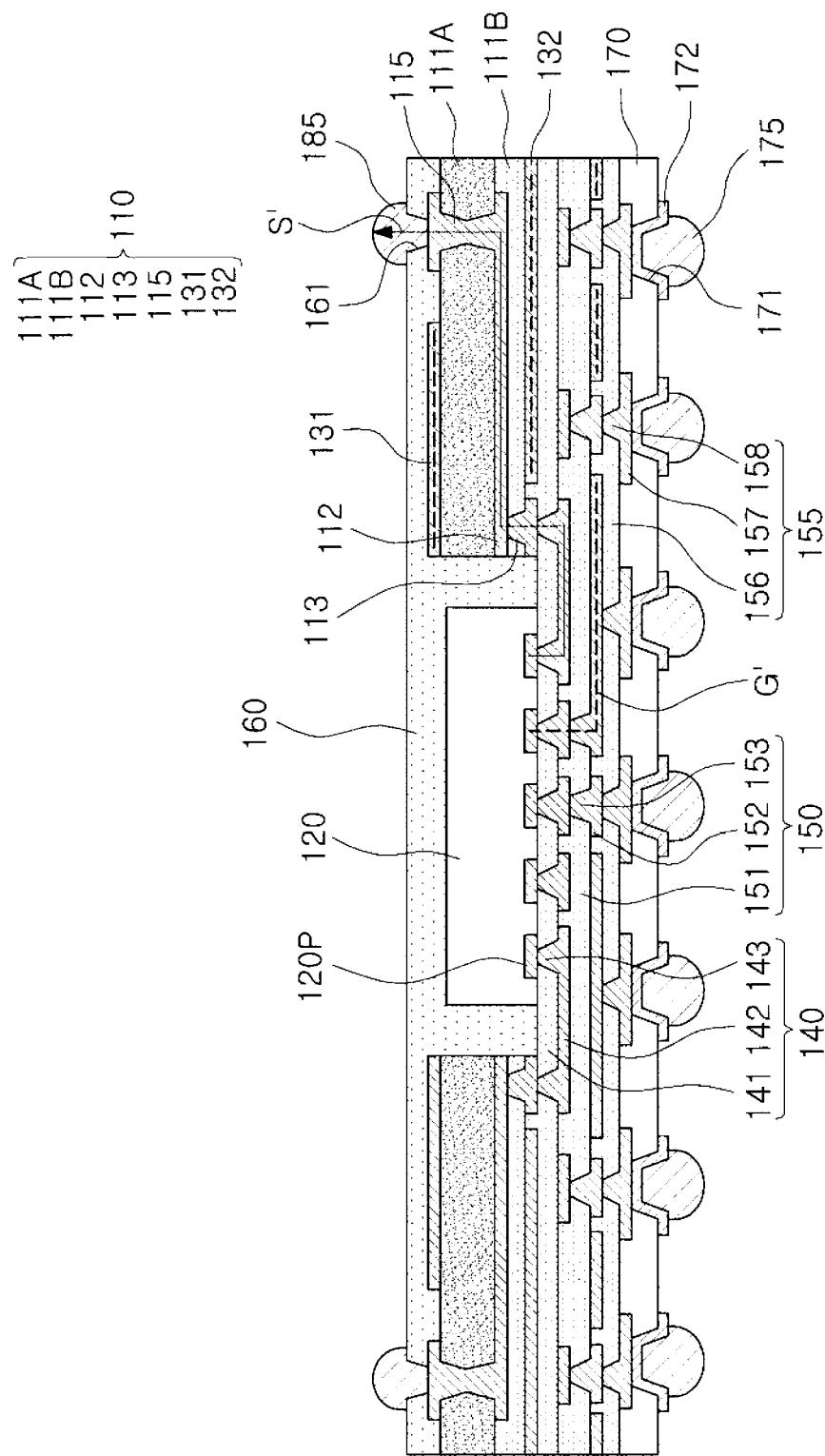

**【0032】** 圖 3 是示意性地說明電子元件封裝的實例的剖視圖。

**【0033】** 圖 4 是電子元件封裝沿圖 3 所示的線 I-I' 截取的示意性平面圖。

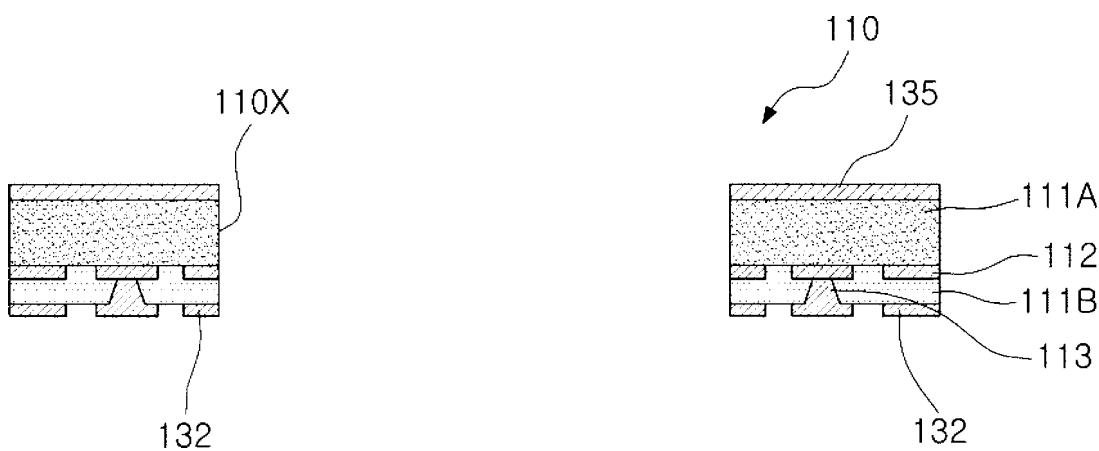

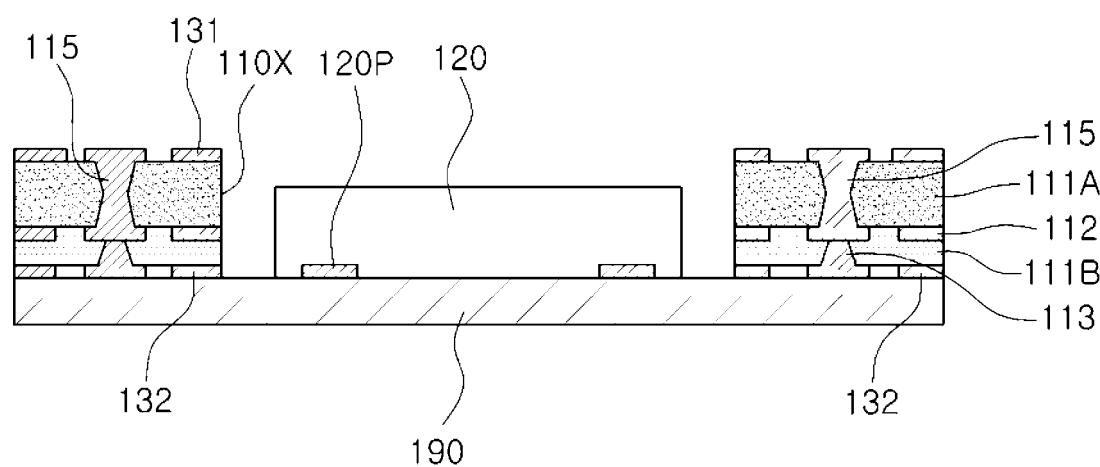

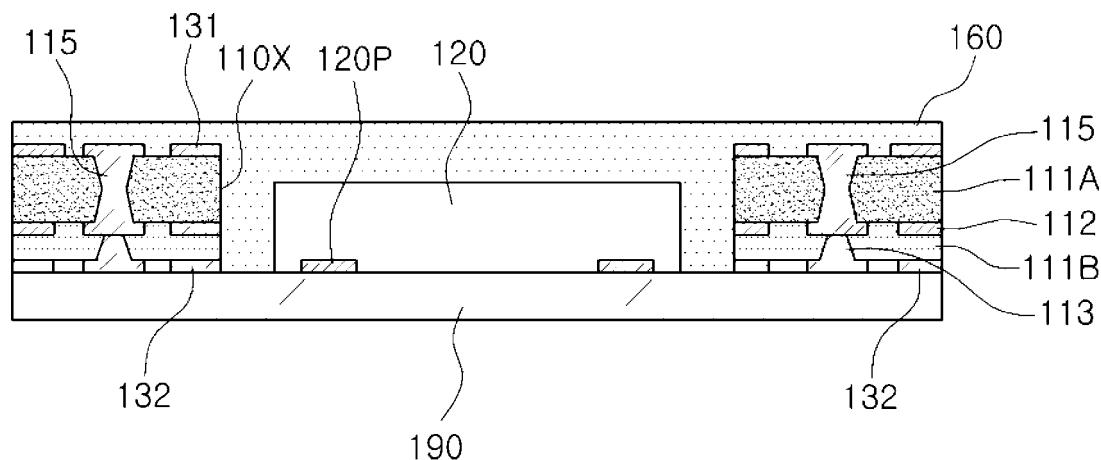

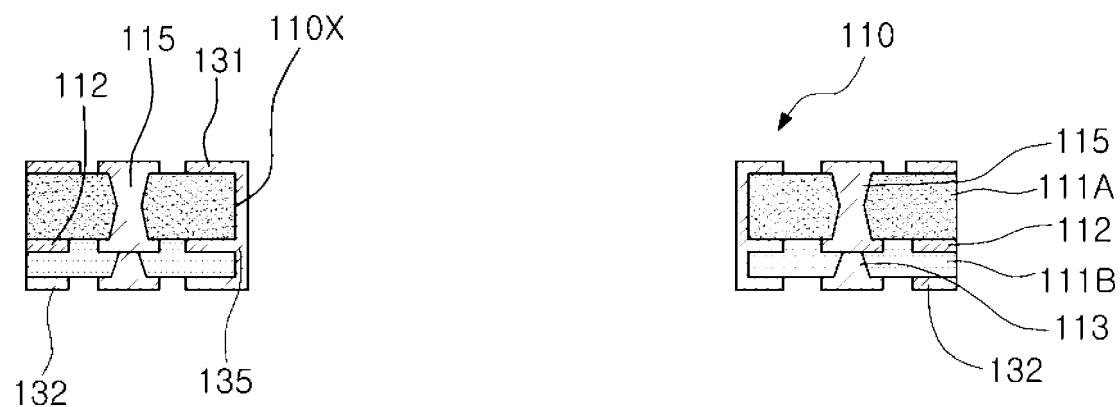

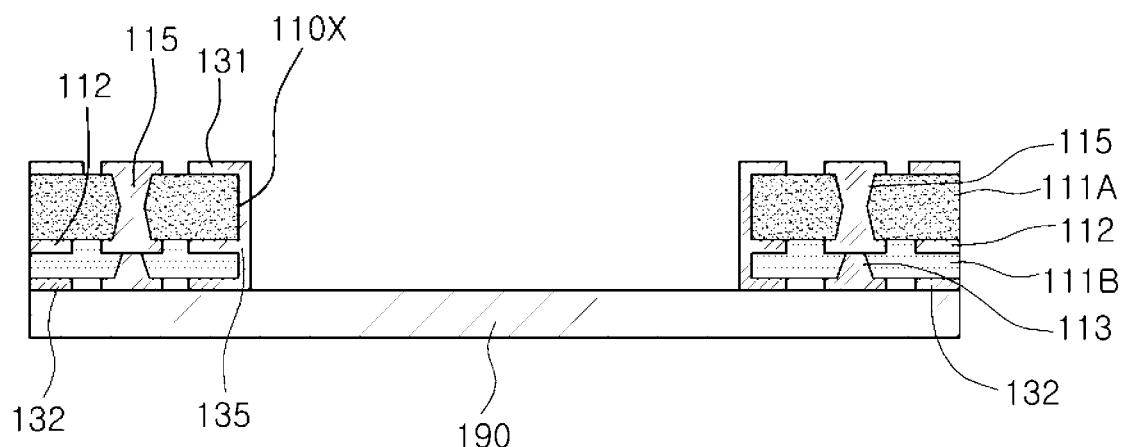

**【0034】** 參照圖 3 及圖 4，根據實例的電子元件封裝 100A 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層

105-10-17

111A 與第二絕緣層 111B 之間的第一配線層 112、安置於第一絕緣層 111A 的上表面上的金屬層 135、安置於第二絕緣層 111B 的下表面上的第二配線層 132、及穿透過第二絕緣層 111B 的通孔 113。貫穿孔 110X 可依序穿透過金屬層 135、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。

**【0035】** 如上所述，近來，已積極地開發出具有小的尺寸且有利於實作多個引腳的扇出式晶圓級封裝。此處，一般而言，晶圓級封裝具有其中電子元件的周圍僅利用例如環氧樹脂模製化合物（epoxy molding compound，EMC）等囊封劑進行模製及封閉的結構，且在所述晶圓級封裝下形成重新分配部以實作電子元件的重新分配。此處，隨著用於實作重新分配部的層的數目增加，將在形成所述重新分配部的製程中發生缺陷的幾率增大，此導致電子元件的良率降低，乃因電子元件一般而言是在重新分配部形成之前安置於所述電子元件封裝中。

**【0036】** 此外，由於電子元件的周圍僅利用囊封劑進行囊封及封閉，因此難以控制因各種原因造成的翹曲、在固定電子元件方面受限、且難以利用囊封區作為路由區，並且因此降低設計的自由度等。

**【0037】** 相反地，在其中在安置電子元件 120 之前將可執行電子元件的重新分配功能的框架 110 引入至用於囊封電子元件 120 的囊封劑 160 中的情形中，如在根據實例的電子元件封裝 100A 中，在安置電子元件 120 之後形成的重新分配部 140 及 150 的層的數

105-10-17

目可減小。因而，可解決其中電子元件 120 的良率因在安置電子元件 120 之後所造成的製程缺陷而降低的問題。

**【0038】** 此外，由於電子元件封裝 100A 的剛性可藉由框架 110 而得到改善，因此可更易於控制翹曲，且由於電子元件 120 安置於框架 110 的貫穿孔 110X 中，因此電子元件 120 可藉由壁面黏合 (wall-surface adhesion) 而更牢固地固定。此外，由於框架 110 的上表面 110A 及下表面 110B 可用作路由區，因此設計的自由度可得到提升。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 3 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於金屬層 135 的上表面下、或者位於與金屬層 135 的上表面相同的位階處或位於金屬層 135 的上表面之上，只要金屬層 135 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0039】** 在下文中，將更詳細地闡述包含於根據實例的電子元件封裝 100A 中的相應元件。

**【0040】** 使用框架 110 的目的可為基本維持電子元件封裝 100A 的剛性。框架 110 可具有用於封閉電子元件 120 的周圍的貫穿孔 110X，且可因電子元件 120 安置於貫穿孔 110X 中而達成對電子元件 120 進行的壁面黏合。框架 110 可包括第一配線層 112 及第二

105-10-17

配線層 132。由於第一配線層 112 及第二配線層 132 是在安置電子元件 120 之前形成，因此其可解決其中電子元件 120 的良率降低的問題。框架 110 可為電子元件封裝 100A 提供更寬的路由區，藉此進一步提升電子元件封裝 100A 的設計的自由度。此外，用於囊封電子元件封裝 100A 中的電子元件 120 的囊封劑 160 的相對平坦的外部表面及電子元件封裝 100A（不包括以下將闡述的第一外部連接端子 175 的突起）的厚度的均勻性可藉由框架 110 而得以確保。

**【0041】** 框架 110 可具有上表面 110A 及與上表面 110A 相對的下表面 110B。第一絕緣層 111A、第二絕緣層 111B 及第一配線層 112 可安置於上表面 110A 與下表面 110B 之間。框架 110 可具有穿透於上表面 110A 與下表面 110B 之間的貫穿孔 110X。第二配線層 132 可安置於框架的下表面 110B 上。框架 110 可包括將第一配線層 112 與第二配線層 132 電性連接至彼此的通孔 113。框架 110 可為一包括安置於上表面 110A 與下表面 110B 之間的元件、及安置於上表面 110A 及下表面 110B 上的元件的概念。作為實例，框架 110 可為一包括第一絕緣層 111A、第二絕緣層 111B、第一配線層 112、第二配線層 132 及通孔 113 的上位概念（upper concept）。貫穿孔 110X 可依序穿透過金屬層 135、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。

**【0042】** 第一絕緣層 111A 可實質上維持電子元件封裝 100A 的剛性且第一絕緣層 111A 的材料並無特別限制，只要其可支撐電子元

105-10-17

件封裝 100A 即可。舉例而言，可使用絕緣材料作為第一絕緣層 111A 的材料。此處，所述絕緣材料可為：熱固性樹脂，例如環氧樹脂；熱塑性樹脂，例如聚醯亞胺樹脂；具有例如浸入於所述熱固性樹脂及所述熱塑性樹脂中的玻璃纖維及/或無機填料等加強材料的樹脂，例如預浸體( pre-preg )、味之素構成膜( Ajinomoto Build up Film, ABF )、FR-4、雙馬來醯亞胺三嗪( Bismaleimide Triazine , BT ) 等。作為另一選擇，可使用具有優異剛性及熱傳導性的金屬作為第一絕緣層 111A 的材料。此處，所述金屬可為 Fe-Ni 系合金。在此種情形中，在所述 Fe-Ni 系合金的表面上亦可形成有鍍 Cu，以確保所述 Fe-Ni 系合金與所述囊封劑、層間絕緣材料等之間的黏合。除上述材料以外，亦可使用玻璃、陶瓷、塑膠等作為第一絕緣層 111A 的材料。第一絕緣層 111A 的厚度並無特別限制，但可依電子元件 120 的厚度來設計。舉例而言，依電子元件 120 的類型而定，第一絕緣層 111A 的厚度可為 100 微米至 500 微米左右。

**【0043】** 第二絕緣層 111B 可為一種用於引入第一配線層 112 及第二配線層 132 的構成層，且第二絕緣層 111B 的材料並無特別限制，只要其為絕緣材料即可。此處，所述絕緣材料可為：熱固性樹脂，例如環氧樹脂；熱塑性樹脂，例如聚醯亞胺樹脂；具有例如浸入於所述熱固性樹脂及所述熱塑性樹脂中的玻璃纖維或無機填料等加強材料的樹脂，例如預浸體、味之素構成膜、FR-4、雙馬來醯亞胺三嗪等。同時，在其中使用例如感光成像介電( photo imagable dielectric , PID )樹脂等感光性絕緣材料作為第二絕緣層

105-10-17

111B 的材料的情形中，第二絕緣層 111B 可被形成為更小的厚度，且可藉由光刻方法而形成通孔洞。因而，通孔的尺寸可減小，且因此可易於實作精細的節距（例如，30 微米或小於 30 微米）。第二絕緣層 111B 的厚度並無特別限制，但依設計特定細節而定可進行各種設計。舉例而言，第二絕緣層 111B 的除第一配線層 112 以外的厚度可為 5 微米至 20 微米左右，且當慮及第一配線層 112 的厚度時，第二絕緣層 111B 的厚度可為 15 微米至 70 微米左右。

**【0044】** 第一絕緣層 111A 及第二絕緣層 111B 可由不同的材料形成。舉例而言，第一絕緣層 111A 可由具有極佳剛性的材料形成，而第二絕緣層 111B 可由感光性絕緣材料形成而無論剛性如何。如上所述，可選擇並使用適宜用作電子元件封裝中的相應第一絕緣層 111A 及第二絕緣層 111B 的材料。舉例而言，第一絕緣層 111A 可具有較第二絕緣層 111B 大的彈性模量。此外，第一絕緣層 111A 可具有較第二絕緣層 111B 大的厚度。相應第一絕緣層 111A 及第二絕緣層 111B 的彈性模量及厚度亦可與相應第一絕緣層 111A 及第二絕緣層 111B 在電子元件封裝中的作用相關，因第一絕緣層 111A 具有相對大的厚度，其可有利於維持電子元件封裝的剛性並固定電子元件 120，且因第二絕緣層 111B 具有減小的厚度，其可有利於減小通孔 113 的尺寸並縮短電性路徑。然而，第一絕緣層 111A 及第二絕緣層 111B 並非僅限於此，而是亦可由相同的材料形成且具有相同的厚度。

**【0045】** 第一配線層 112 可安置於第一絕緣層 111A 與第二絕緣層

105-10-17

111B 之間。舉例而言，第一配線層 112 可安置於第一絕緣層 111A 的下表面上並嵌置於第二絕緣層 111B 中。亦即，第一配線層 112 可安置於框架 110 中。此處，第一配線層 112 安置於框架 110 中的含義為第一配線層 112 安置於框架 110 的上表面 110A 與下表面 110B 之間。依對應層的設計而定，第一配線層 112 可執行各種功能。舉例而言，第一配線層可充當接地 (GND) 圖案、功率 (PWR) 圖案、訊號 (S) 圖案等而作為重新分配圖案。此處，訊號 (S) 圖案可包括除接地 (GND) 圖案、功率 (PWR) 圖案等以外的各種訊號，例如資料訊號等。此外，第一配線層 112 可充當通孔焊墊等而作為焊墊圖案。如上所述，由於第一配線層 112 可執行重新分配功能，因此第一配線層 112 可分擔重新分配部 140 及 150 的重新分配功能。例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作第一配線層 112 的材料。第一配線層 112 的厚度亦無特別限制，但可為例如 10 微米至 50 微米左右。

**【0046】** 第二配線層 132 可安置於第二絕緣層 111B 的下表面 110B 上。亦即，第二配線層 132 可安置於框架 110 之外。此處，第二配線層 132 可安置於框架 110 之外的含義為第二配線層 132 不安置於框架 110 的上表面 110A 與下表面 110B 之間。第二配線層 132 亦可充當重新分配圖案及/或焊墊圖案。舉例而言，第二配線層 132 可充當接地圖案而作為重新分配圖案。此外，第二配線層 132 可充當通孔焊墊等而作為焊墊圖案。由於第二配線層 132 亦是在安

105-10-17

置電子元件 120 之前形成，因此第二配線層 132 可解決其中電子元件 120 的良率降低的問題。金屬層 135 的厚度及第二配線層 132 的厚度並無特別限制，但依設計特定細節而定可進行各種設計。舉例而言，金屬層 135 的厚度及第二配線層 132 的厚度可為 10 微米至 50 微米左右。

**【0047】** 通孔 113 可將形成於不同的層上的第一配線層 112 及第二配線層 132 電性連接至彼此，藉此在電子元件封裝 100A 內形成電性路徑。通孔 113 可穿透過第二絕緣層 111B。例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作通孔 113 的材料。通孔 113 可被完全填充以傳導性材料。作為另一選擇，傳導性材料可沿通孔的壁形成。此外，通孔 113 可具有先前技術中所習知的所有形狀，例如其中通孔的直徑朝下表面變得更小的錐形形狀、其中通孔的直徑朝下表面變得更大的倒錐形形狀、圓柱形形狀等。

**【0048】** 金屬層 135 可安置於框架 110 的上表面 110A 上。金屬層 135 可為用於改善熱輻射特性及/或阻擋電磁波的附加元件，且金屬層 135 的材料並無特別限制，只要其為具有高熱傳導性的金屬即可。舉例而言，金屬層 135 的材料可為銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金，但並非僅限於此。

**【0049】** 電子元件 120 可為各種主動元件（例如，二極體、真空管、電晶體等）或被動元件（例如，電感器、電容器、電阻器等）。

105-10-17

作為另一選擇，電子元件 120 可為指示其中將數百至數百萬個或更多個組件整合於一起的晶片的積體電路（integrated circuit，IC）。若需要，則電子元件 120 可為其中將積體電路以覆晶（flip-chip）形式封裝的電子元件。所述積體電路可為例如中央處理器（例如，中央處理單元）、圖形處理器（例如，圖形處理單元）、數位訊號處理器、密碼學處理器、微處理器、微控制器等應用處理器晶片，但並非僅限於此。

**【0050】** 電子元件 120 可具有在電子元件 120 的下表面上形成的電極焊墊 120P。電極焊墊 120P 可將電子元件 120 電性連接至電子元件封裝內的另一元件或位於所述電子元件封裝之外的元件，且電極焊墊 120P 的材料並無特別限制，只要其為傳導性材料即可。所述傳導性材料可為銅（Cu）、鋁（Al）、銀（Ag）、錫（Sn）、金（Au）、鎳（Ni）、鉛（Pb）、或其合金，但並非僅限於此。電極焊墊 120P 可藉由第一配線層 112、第二配線層 132、重新分配部 140 及 150 等而重新分配。電極焊墊 120P 可具有嵌置形式或突出形式。當電極焊墊 120P 具有嵌置形式時，電子元件 120 的下表面是其最外表面。當電極焊墊 120P 具有突出形式時，電子元件 120 的下表面是其供電極焊墊 120P 自其突出的表面。電子元件 120 的橫截面的厚度並無特別限制，且依電子元件 120 的類型而定可有所變化。舉例而言，在其中所述電子元件為積體電路的情形中，電子元件的厚度可為 100 微米至 480 微米左右，但並非僅限於此。

**【0051】** 在其中電子元件 120 為積體電路的情形中，所述電子元

105-10-17

件可具有主體（未由參考編號表示）、保護層（圖中未示出）、及電極焊墊 120P。所述主體可基於例如主動晶圓而形成。在此種情形中，可使用矽（Si）、鍆（Ge）、砷化鎵（GaAs）等作為主體的基材（basic material）。所述保護層可用於保護主體不受外部因素影響，且可由例如氧化物層、氮化物層等形成，或者可由氧化物層與氮化物層形成的雙層形成。例如銅（Cu）、鋁（Al）、銀（Ag）、錫（Sn）、金（Au）、鎳（Ni）、鉛（Pb）、或其合金等傳導性材料可用作電極焊墊 120P 的材料。其上形成有電極焊墊 120P 的層可變為主動層。

**【0052】** 第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 3 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於金屬層 135 的上表面下、或者位於與金屬層 135 的上表面相同的位階處或位於金屬層 135 的上表面之上，只要金屬層 135 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0053】** 使用重新分配部 140 及 150 的目的可為基本重新分配電子元件 120 的電極焊墊 120P。具有各種功能的數十至數百個電極焊墊 120P 可藉由重新分配部 140 及 150 而重新分配，且依其功能而定，可藉由以下將闡述的第一外部連接端子 175 而物理地連接

105-10-17

至及/或電性連接至外部。重新分配部 140 及 150 可連接至電子元件 120。亦即，重新分配部 140 及 150 可支撐電子元件 120。

**【0054】** 重新分配部 140 及 150 可包括交替地堆疊於一起的重新分配部絕緣層 141 及 151 與重新分配部配線層 142 及 152，以及穿透過重新分配部絕緣層 141 及 151 以藉此分別電性連接至重新分配部配線層 142 及 152 的重新分配部通孔 143 及 153。儘管重新分配部 140 及 150 分別是由多個層形成，然而在根據實例的電子元件封裝 100A 中，重新分配部 140 及 150 並非僅限於此，且依電子元件 120 的類型而定可不同於圖式中所示而分別由單個層形成。作為另一選擇，重新分配部亦可由較所述多個層更多的層形成。

**【0055】** 重新分配部絕緣層 141 及 151 的材料亦無特別限制，只要其為絕緣材料即可，舉例而言，所述絕緣材料為：熱固性樹脂，例如環氧樹脂；熱塑性樹脂，例如聚醯亞胺樹脂；具有例如浸入於所述熱固性樹脂及所述熱塑性樹脂中的玻璃纖維或無機填料等加強材料的樹脂，例如預浸體、味之素構成膜、FR-4、雙馬來醯亞胺三嗪等。在其中使用例如感光成像介電樹脂等感光性絕緣材料作為重新分配部絕緣層 141 及 151 的材料的情形中，重新分配部絕緣層 141 及 151 可被形成為具有減小的厚度，且可易於實作精細節距。若需要，則重新分配部絕緣層 141 及 151 的材料可彼此相同或可彼此不同。重新分配部絕緣層 141 及 151 的厚度亦無特別限制。舉例而言，重新分配部絕緣層 141 及 151 的除重新分配部配線層 142 及 152 以外的厚度可為約 5 微米至 20 微米左右，

105-10-17

且當慮及重新分配部配線層 142 及 152 的厚度時，重新分配部絕緣層 141 及 151 的厚度可為約 15 微米至 70 微米左右。

**【0056】** 重新分配部配線層 142 及 152 亦可充當重新分配圖案及/或焊墊圖案，且例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作重新分配部配線層 142 及 152 的材料。依對應層的設計而定，重新分配部配線層 142 及 152 可執行各種功能。舉例而言，重新分配部配線層 142 及 152 可充當接地 (GND) 圖案、功率 (PWR) 圖案、訊號 (S) 圖案等而作為重新分配圖案。此處，訊號 (S) 圖案可包括除接地 (GND) 圖案、功率 (PWR) 圖案等以外的各種訊號，例如資料訊號等。此外，重新分配部配線層 142 及 152 可充當通孔焊墊、外部連接端子焊墊等而作為焊墊圖案。重新分配部配線層 142 及 152 的厚度亦無特別限制，且可為例如約 10 微米至 50 微米左右。若需要，則可在重新分配部配線層 152 的被暴露出的圖案上形成表面處理層。所述表面處理層並無特別限制，只要其為先前技術中所習知者即可，且可藉由例如電解鍍金、無電鍍金、有機可焊性保護劑 (organic solderability preservative, OSP)、或無電鍍錫、無電鍍銀、無電鍍鎳/置換鍍金 (substituted gold plating)、直接浸金 (direct immersion gold, DIG) 鍍覆、熱空氣焊料均塗 (hot air solder leveling, HASL) 等而形成。

**【0057】** 重新分配部通孔 143 及 153 可將第二配線層 132、重新分配部配線層 142 及 152 與形成於不同的層上的電極焊墊 120P 電性

105-10-17

連接至彼此，藉此在電子元件封裝 100A 內形成電性路徑。例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作重新分配部通孔 143 及 153 的材料。重新分配部通孔 143 及 153 亦可被完全填充以傳導性材料。作為另一選擇，可沿重新分配部通孔 143 及 153 的壁形成傳導性材料。此外，重新分配部通孔 143 及 153 可具有先前技術中所習知的所有形狀，例如其中通孔的直徑朝下表面變得更小的錐形形狀、其中通孔 (via) 的直徑朝下表面變得更大的倒錐形形狀、圓柱形形狀等。

**【0058】** 重新分配部 140 及 150 可將框架 110 與電子元件 120 連接至彼此。此處，框架 110 與電子元件 120 經由重新分配部 140 及 150 而連接至彼此的含義為框架 110 與電子元件 120 彼此間隔開，但重新分配部 140 及 150 連接至框架 110 與電子元件 120 兩者，且因此框架 110 與電子元件 120 經由重新分配部 140 及 150 而連接至彼此。

**【0059】** 框架 110 可經由旁路 (bypass) 而電性連接至電子元件 120。重新分配部 140 及 150 可直接電性連接至電子元件 120。亦即，由於框架 110 位於電子元件的側部部分處，因此其可經由重新分配部 140 及 150 而電性連接至電子元件 120。亦即，框架 110 的第一配線層 112 及第二配線層 132 可經由重新分配部 140 及 150 而電性連接至電子元件 120，且重新分配部 140 及 150 可直接電性連接至電子元件 120。框架 110 的第一配線層 112 及第二配線層

132 可不直接電性連接至電子元件 120。

**【0060】** 使用囊封劑 160 的目的可為保護電子元件 120。為此，囊封劑 160 可囊封框架 110 的及電子元件 120 的至少部分。囊封形式並無特別限制，但可為封閉電子元件 120 的形式。舉例而言，囊封劑 160 可覆蓋電子元件 120，且可設置於框架 110 的貫穿孔 110X 內的其餘空間中。此外，囊封劑 160 亦可覆蓋框架 110。囊封劑 160 可設置於貫穿孔 110X 中，藉此在充當黏合劑的同時用於減少電子元件 120 的屈曲（buckling）。囊封劑 160 可覆蓋電子元件 120 的除電子元件 120 的下表面以外的所有表面。依電子元件 120 的電極焊墊 120P 的突出形式而定，囊封劑 160 可覆蓋電子元件 120 的下表面的僅一部分。

**【0061】** 囊封劑 160 可包括由多個材料形成的多個層。舉例而言，貫穿孔 110X 內的空間可被填充以第一囊封劑，且框架 110 及電子元件 120 可被覆蓋以第二囊封劑。作為另一選擇，可在使用第一囊封劑填充貫穿孔 110X 內的空間的同時以預定厚度覆蓋框架 110 及電子元件 120，且可在第一囊封劑上再次以預定厚度覆蓋第二囊封劑。除上述形式以外，亦可使用各種形式。被填充以囊封劑 160 的貫穿孔 110X 內的空間的間距並無特別限制，且可被熟習此項技術者最佳化。舉例而言，被填充以囊封劑 160 的貫穿孔 110X 內的空間的間距可為約 10 微米至 150 微米左右，但並非僅限於此。

**【0062】** 囊封劑 160 的詳細材料並無特別限制。舉例而言，可使用絕緣材料作為囊封劑 160 的材料。此處，所述絕緣材料可為：

105-10-17

熱固性樹脂，例如環氧樹脂；熱塑性樹脂，例如聚醯亞胺樹脂；具有例如浸入於所述熱固性樹脂及所述熱塑性樹脂中的玻璃纖維及/或無機填料等加強材料的樹脂，例如預浸體、味之素構成膜等。此外，亦可使用例如環氧樹脂模製化合物等習知的模製材料。使用例如玻璃纖維及/或無機填料等絕緣樹脂作為囊封劑 160 的材料可更有效地控制翹曲。

**【0063】** 囊封劑 160 可具有較框架 110 的第一絕緣層 111A 的材料低的彈性模量。舉例而言，囊封劑 160 的彈性模量可為 15 千兆帕 (GPa) 或小於 15 千兆帕，例如為 50 兆帕至 15 千兆帕左右。隨著囊封劑 160 的彈性模量變得相對小，電子元件封裝 100A 的翹曲可藉由對電子元件 120 的屈曲效應 (buckling effect) 及應力分散效應 (stress dispersing effect) 而減少。詳言之，由於囊封劑 160 設置於貫穿孔 110X 的空間中，因此囊封劑 160 可對電子元件 120 具有屈曲效應，且由於囊封劑 160 覆蓋電子元件 120，因此囊封劑 160 可分散並減輕在電子元件 120 中產生的應力。然而，在其中囊封劑 160 的彈性模量過度小的情形中，囊封劑 160 可過度變形，且因此囊封劑 160 可能無法發揮囊封劑的基本作用。所述彈性模量被定義為應力與變形之間的比率，且可藉由 KS M 3001、KS M 527-3、ASTM D882 等中規定的張力試驗來量測。

**【0064】** 若需要，則囊封劑 160 可含有傳導性粒子以阻擋電磁波。舉例而言，所述傳導性粒子可為可阻擋電磁波的任意材料，例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛

105-10-17

(Pb)、焊料等，但並非特別地限定於此。

**【0065】** 根據實例的電子元件封裝 100A 可更包括安置於重新分配部 140 及 150 下的保護層 170。使用保護層 170 的目的可為保護重新分配部 140 及 150 不受外部的物理或化學損害等。保護層 170 可具有第一開口部 171，第一開口部 171 暴露出重新分配部 140 及 150 的重新分配部配線層 152 的至少部分。儘管第一開口部 171 可暴露出重新分配部配線層 152 的上表面的部分，然而在某些情形中第一開口部 171 亦可暴露出重新分配部配線層 152 的側表面。

**【0066】** 保護層 170 的材料並無特別限制。舉例而言，可使用阻焊劑 (solder resist) 作為保護層 170 的材料。此外，可使用與框架 110 的第二絕緣層 111B 及/或重新分配部 140 及 150 的重新分配部絕緣層 141 及 151 相同的材料（例如，同一種感光成像介電樹脂、味之素構成膜等）作為保護層 170 的材料。保護層 170 一般而言為單個層，但若需要，則亦可由多個層形成。使用味之素構成膜作為保護層 170 的材料可有效地提高所述電子元件封裝的可靠性。

**【0067】** 根據實例的電子元件封裝 100A 可更包括安置於保護層 170 的第一開口部 171 中以藉此暴露於外部的第一外部連接端子 175。使用第一外部連接端子 175 的目的可為將電子元件封裝 100A 物理地連接至及/或電性連接至外部。舉例而言，電子元件封裝 100A 可藉由第一外部連接端子 175 而安裝於所述電子元件的主板上。第一外部連接端子 175 可安置於第一開口部 171 中，並可連

105-10-17

接至經由第一開口部 171 而暴露出的重新分配部配線層 152。因而，第一外部連接端子 175 亦可電性連接至電子元件 120。

**【0068】** 第一外部連接端子 175 可由例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、焊料等傳導性材料形成，但並非特別地限定於此。第一外部連接端子 175 可為焊盤 (land)、球、引腳等。第一外部連接端子 175 可由多個層或單個層形成。在其中第一外部連接端子 175 由多個層形成的情形中，第一外部連接端子 175 可含有銅柱及焊料，而在其中第一外部連接端子 175 由單個層形成的情形中，第一外部連接端子 175 可含有錫-銀焊料或銅。然而，此僅為實例，且第一外部連接端子 175 並非僅限於此。

**【0069】** 第一外部連接端子 175 中的至少一者可安置於扇出區中。所述扇出區被定義為除其中安置有所述電子元件的區以外的區。亦即，根據實例的電子元件封裝 100A 可為扇出式封裝。所述扇出式封裝可具有較扇入式封裝高的可靠性、可實作多個 I/O 端子、且可易於執行 3D 互連。此外，由於扇出式封裝相較於球柵陣列 (ball grid array, BGA) 封裝、焊盤柵陣列 (land grid array, LGA) 封裝等而言可無需使用獨立的基板而安裝於所述電子裝置上，因此所述扇出式封裝可被製造成具有減小的厚度，且可具有優異的價格競爭力。

**【0070】** 第一外部連接端子 175 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修

105-10-17

改。舉例而言，依電子元件 120 的電極焊墊 120P 的數目而定，第一外部連接端子 175 的數目可為數十至數千個。然而，第一外部連接端子 175 的數目並非僅限於此，且亦可為幾十至幾千個或更多個、或者幾十至幾千個或更少個。

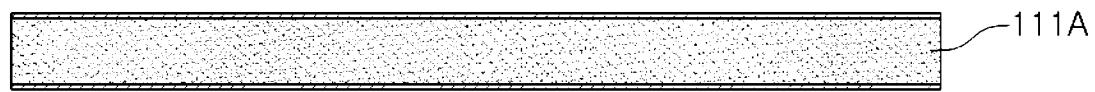

**【0071】** 圖 5A 至圖 5L 是說明製造電子元件封裝 100A 的製程的實例的示意圖。

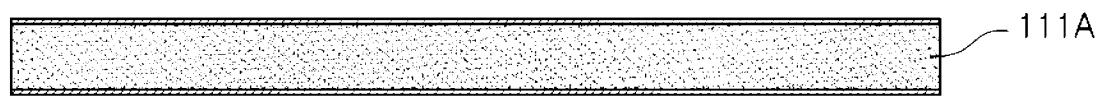

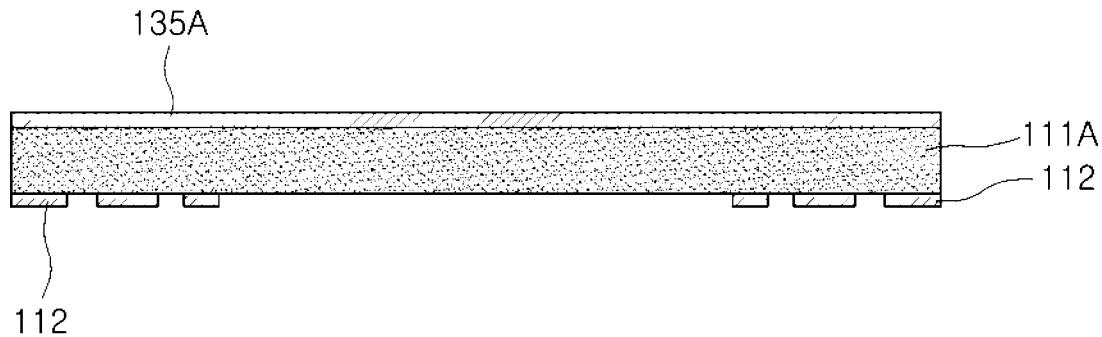

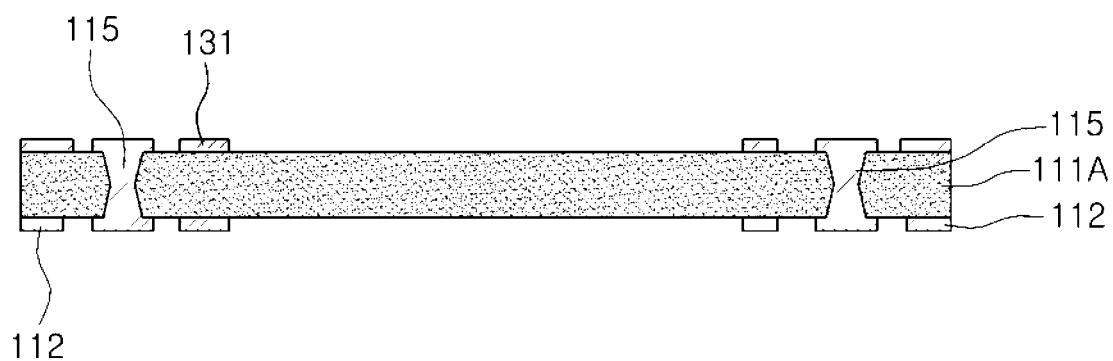

**【0072】** 參照圖 5A，可製備第一絕緣層 111A。可以各種尺寸來製造及使用第一絕緣層 111A，以便於大量生產。亦即，在製備出具有大尺寸的第一絕緣層 111A 之後，可藉由以下將闡述的製程來製造多個電子元件封裝 100A。接著，可藉由鋸切 (sawing) 製程而將所述多個電子元件封裝 100A 分割成獨立的單位封裝。若需要，則可在第一絕緣層 111A 中呈現優異拾取及放置 (pick-and-place, P&P) 的基準標記 (fiducial mark)。由於安裝有電子元件 120 的位置可藉由所述基準標記而更清楚地辨識，因此可提高製造的完整性。例如敷銅積層板 (copper clad laminate, CCL) (未由參考編號表示) 等薄金屬層可形成於第一絕緣層 111A 的上表面及下表面上，並可在後續製程中充當用於形成配線層等的基礎晶種層。

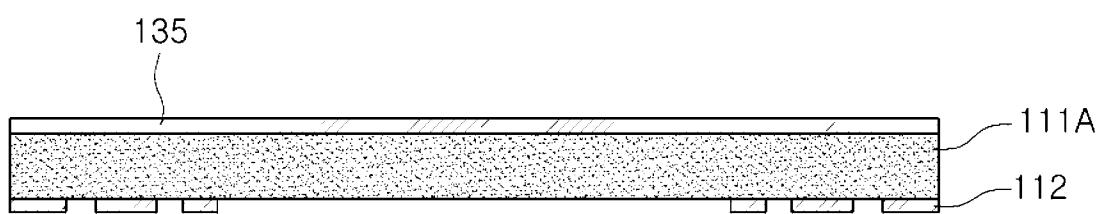

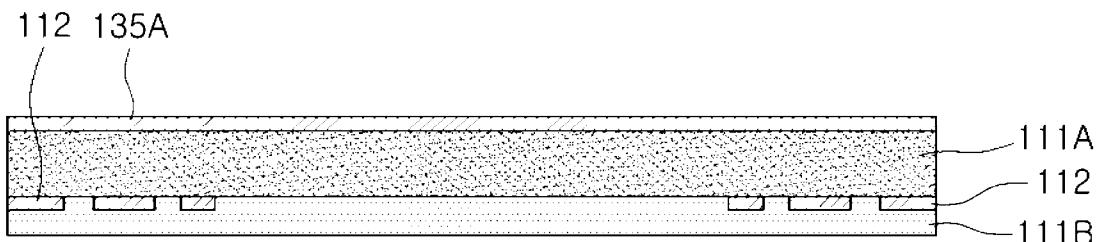

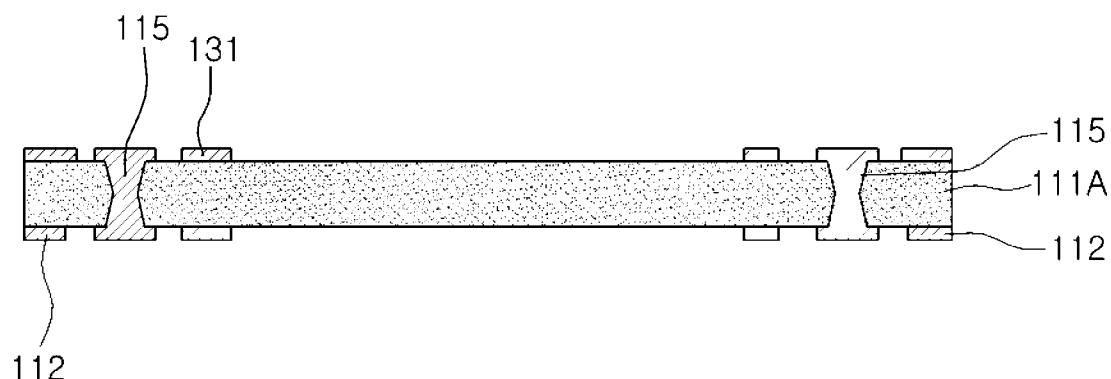

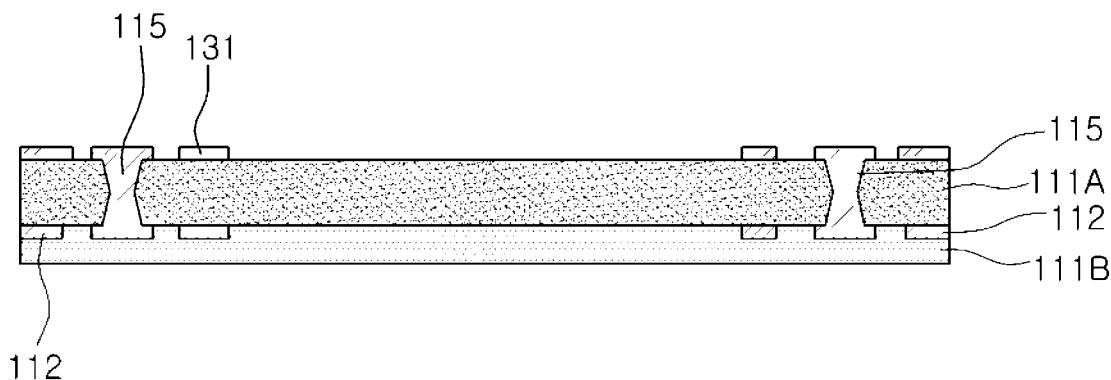

**【0073】** 參照圖 5B，可在第一絕緣層 111A 的上表面及下表面上分別形成金屬層 135 及第一配線層 112。可藉由習知的方法來形成金屬層 135 及第一配線層 112。舉例而言，可使用乾膜圖案 (dry film pattern) 藉由電解鍍銅、無電鍍銅等來形成金屬層 135 及第一配線層 112。更詳言之，可使用例如化學氣相沈積 (chemical vapor

105-10-17

deposition，CVD）、物理氣相沈積（physical vapor deposition，PVD）、濺鍍、減性製程、加性製程、半加性製程（semi-additive process，SAP）、經修改半加性製程（modified semi-additive process，MSAP）等方法來形成金屬層 135 及第一配線層 112，但並非僅限於此。

**【0074】** 參照圖 5C，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。亦可藉由習知的方法來形成第二絕緣層 111B。舉例而言，可藉由將第二絕緣層 111B 的前驅物積層於第一絕緣層 111A 的下表面上並接著硬化所述前驅物的方法、將用於形成第二絕緣層 111B 的材料施加至第一絕緣層 111A 的下表面上並接著硬化所述材料的方法等來形成第二絕緣層 111B，但並非僅限於此。可使用例如以下方法等作為積層所述前驅物的方法：執行在高溫下對前驅物壓製預定時間的熱壓製（hot press）製程、對所述前驅物進行減壓、並且接著將所述前驅物冷卻至室溫、在冷壓製（cold press）製程中冷卻所述前驅物、並且接著分離作業工具。可使用例如利用刮板（squeegee）施加油墨的網版印刷方法、以霧形式施加油墨的噴霧印刷方法等作為施加所述材料的方法。所述硬化製程—其為後置製程—可為使材料乾燥以不被完全硬化從而使用光刻（photolithography）方法等的製程。

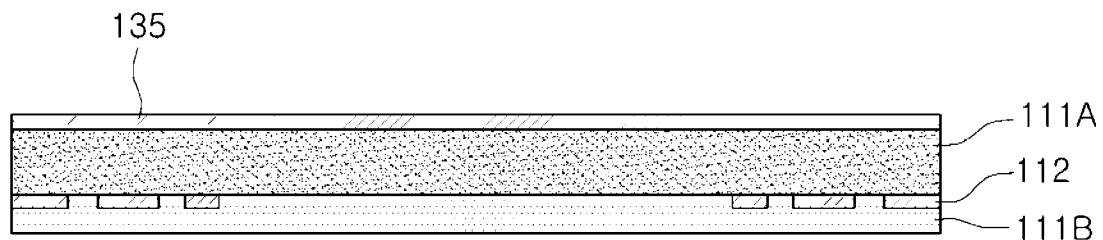

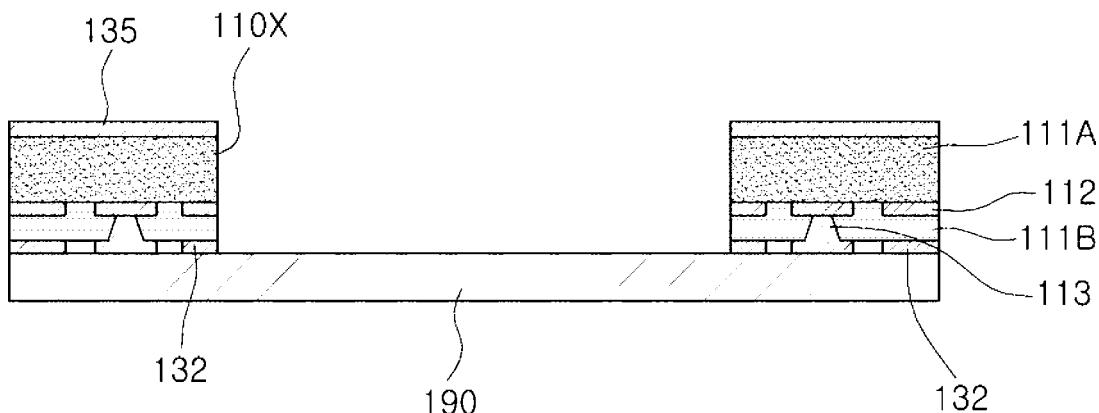

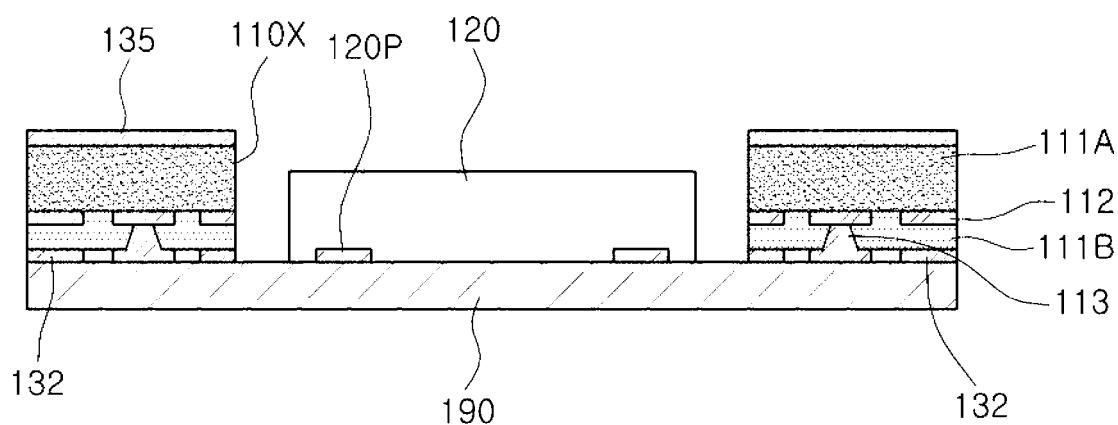

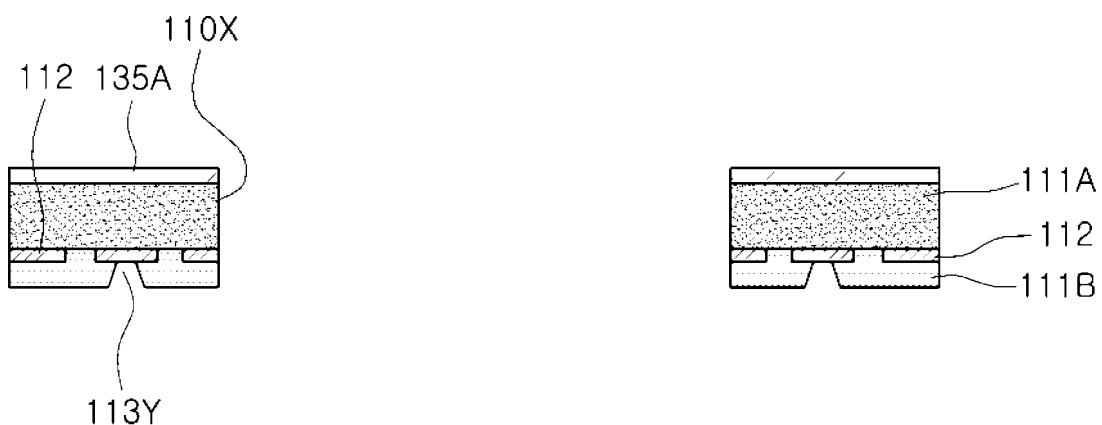

**【0075】** 參照圖 5D，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B 中形成通孔 113。可使用機械鑽孔及/或雷射鑽孔來形成通孔洞（圖中未示出）。此處，所述雷射鑽孔可

105-10-17

為 CO<sub>2</sub> 雷射或 YAG 雷射，但並非僅限於此。在其中使用機械鑽孔及/或雷射鑽孔形成通孔洞（圖中未示出）的情形中，可對通孔洞（via hole）執行除汙製程，以移除通孔洞（圖中未示出）中的樹脂污垢。可使用例如高錳酸鹽方法來執行所述除汙製程。在其中第二絕緣層 111B 含有感光成像介電樹脂等的情形中，亦可藉由光刻方法來形成通孔洞。在通孔洞形成之後，亦可使用乾膜圖案而藉由電解鍍銅、無電鍍銅等來形成第二配線層 132 及通孔 113。更詳言之，可使用例如化學氣相沈積、物理氣相沈積、濺鍍、減性製程、加性製程、半加性製程、經修改半加性製程等方法來形成第二配線層 132 及通孔 113，但並非僅限於此。

**【0076】** 參照圖 5E，可形成穿透過框架 110 的上表面 110A 及下表面 110B 的貫穿孔 110X。形成貫穿孔 110X 的方法亦無特別限制。可藉由例如機械鑽孔及/或雷射鑽孔、使用研磨顆粒的噴砂方法、使用電漿的乾式蝕刻方法等來形成貫穿孔 110X。同樣地，在其中使用機械鑽孔及/或雷射鑽孔來形成貫穿孔 110X 情形中，可執行例如高錳酸鹽方法等除汙製程，以移除貫穿孔 110X 中的樹脂污垢。可根據欲安裝的電子元件 120 的尺寸、形狀、數目等來設計貫穿孔 110X 的尺寸、形狀等。可藉由一系列製程來形成具有貫穿孔 110X 的框架 110。

**【0077】** 參照圖 5F，可將黏合膜 190 貼附至第二配線層 132。可使用可固定第二配線層 132 的任意材料作為黏合膜 190。作為此材料的非限制性實例，可使用此項技術中習知的膠帶等。所述習知

105-10-17

膠帶的實例可包括其黏度被熱處理弱化的熱固性黏合膠帶、其黏度被紫外線輻射弱化的可紫外光固化的黏合膠帶等。

**【0078】** 參照圖 5G，可在貫穿孔 110X 中安置電子元件 120。詳言之，可將電子元件 120 貼附至並安置於經由框架 110 的貫穿孔 110X 而暴露出的黏合膜 190 上。電子元件 120 可被安置成面朝下的形式，從而使電極焊墊 120P 貼附至黏合膜 190。在其中電子元件 120 的電極焊墊 120P 具有嵌置形式的情形中，電子元件 120 的下表面與第二配線層 132 的下表面可實質上彼此共面。舉例而言，電子元件 120 的下表面與第二配線層 132 的下表面之間的距離可小於第二配線層 132 的厚度。在其中電子元件 120 的電極焊墊 120P 具有突出形式的情形中，第二配線層 132 的下表面與電極焊墊 120P 的下表面可實質上彼此共面。舉例而言，第二配線層 132 的下表面與電極焊墊 120P 的下表面之間的距離可小於第二配線層 132 的厚度。

**【0079】** 參照圖 5H，可使用囊封劑 160 對電子元件 120 進行囊封。囊封劑 160 可覆蓋框架 110 及電子元件 120，且可設置於貫穿孔 110X 內的空間中。可藉由習知的方法來形成囊封劑 160。舉例而言，可藉由對囊封劑 160 的前驅物進行積層並接著硬化所述前驅物的方法來形成囊封劑 160。作為另一選擇，可藉由將前體囊封劑施加至黏合膜 190 上以囊封電子元件 120 並接著硬化所述前驅囊封劑的方法來形成囊封劑 160。可藉由所述硬化來固定電子元件 120。可使用例如以下方法等作為積層所述前驅物的方法：執行在

105-10-17

高溫下對前驅物壓製預定時間的熱壓製製程、對所述前驅物進行減壓、並且接著將所述前驅物冷卻至室溫、在冷壓製製程中冷卻所述前驅物、並且接著分離作業工具。可使用例如利用刮板施加油墨的網版印刷方法、以霧形式施加油墨的噴霧印刷方法等作為施加所述前驅囊封劑的方法。

**【0080】** 參照圖 5I，可剝除黏合膜 190。剝除黏合膜 190 的方法並無特別限制，且可為習知的方法。舉例而言，在其中使用其黏度被熱處理弱化的熱固性黏合膠帶、其黏度被紫外線輻射弱化的可紫外光固化黏合膠帶等作為黏合膜 190 的情形中，可在黏合膜 190 的黏度藉由對黏合膜 190 進行的熱處理而弱化之後剝除黏合膜 190，或者可在黏合膜 190 的黏度藉由利用紫外線對黏合膜 190 進行的輻射而弱化之後剝除黏合膜 190。

**【0081】** 參照圖 5J，可在框架 110 及電子元件 120 下首先形成重新分配部絕緣層 141，並可形成重新分配部配線層 142 及重新分配部通孔 143，以形成重新分配部 140。接下來，可在重新分配部絕緣層 141 下再次形成重新分配部絕緣層 151，並可形成重新分配部配線層 152 及重新分配部通孔 153，以形成重新分配部 150。形成重新分配部 140 及 150 的詳細方法相同於上述方法。重新分配部絕緣層 141 與囊封劑 160 之間的介面可和第二配線層 132 的下表面實質上共面。舉例而言，所述介面與第二配線層 132 的下表面之間的距離可小於第二配線層 132 的厚度。依電子元件 120 的電極焊墊 120P 是否突出而定，所述介面可與電子元件 120 的下表面

105-10-17

或電極焊墊 120P 的下表面實質上共面。舉例而言，所述介面與電子元件 120 的下表面或電極焊墊 120P 的下表面之間的距離可小於第二配線層 132 的厚度。所述介面可存在於其中重新分配部絕緣層 141 及囊封劑 160 由不同的材料形成的情形中、或可存在於其中重新分配部絕緣層 141 及囊封劑 160 由相同的材料形成但是以不同的步驟或製程形成的情形中。

**【0082】** 參照圖 5K，可形成安置於重新分配部 140 及 150 下的保護層 170。亦可藉由對保護層 170 的前驅物進行積層並接著硬化所述前驅物的方法、施加用於形成保護層 170 的材料並接著硬化所述材料的方法等來形成保護層 170。可使用例如以下方法等作為積層所述前驅物的方法：執行在高溫下對前驅物壓製預定時間的熱壓製製程、對所述前驅物進行減壓、並且接著將所述前驅物冷卻至室溫、在冷壓製製程中冷卻所述前驅物、並且接著分離作業工具。可使用例如利用刮板施加油墨的網版印刷方法、以霧形式施加油墨的噴霧印刷方法等作為施加所述前驅囊封劑的方法。所述硬化製程—其為後置製程—可為使材料乾燥以不被完全硬化從而使用光刻方法等的製程。

**【0083】** 參照圖 5L，可在保護層 170 中形成第一開口部 171，以暴露出重新分配部配線層 152 的至少部分。可使用機械鑽孔及/或雷射鑽孔來形成第一開口部 171。作為另一選擇，可藉由光刻方法來形成第一開口部 171。在其中使用機械鑽孔及/或雷射鑽孔形成第一開口部 171 的情形中，可利用高錳酸鹽方法等對第一開口部

105-10-17

171 執行除汙製程，以移除樹脂污垢。接著，可形成安置於第一開口部 171 中的第一外部連接端子 175。形成第一外部連接端子 175 的方法並無特別限制。亦即，依第一外部連接端子 175 的結構或形式而定，可藉由先前技術中眾所習知的方法來形成第一外部連接端子 175。可藉由回焊 (reflow) 來固定第一外部連接端子 175，且第一外部連接端子 175 的部分可嵌置於保護層 170 中以增強固定力，且第一外部連接端子 175 的其餘部分可暴露於外部，藉此可提高可靠性。在某些情形中，可僅形成第一開口部 171，且若需要，則可藉由由購買電子元件封裝 100A 的客戶進行的單獨製程而形成第一外部連接端子 175。

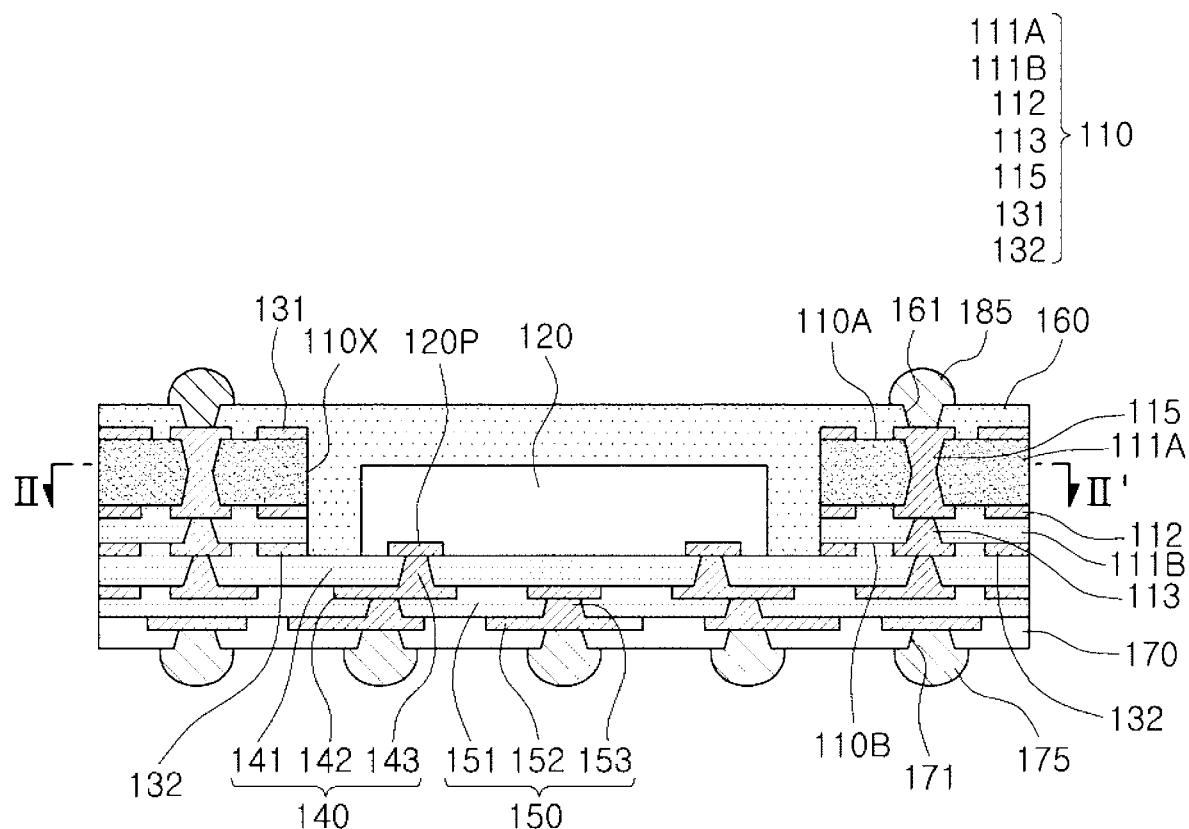

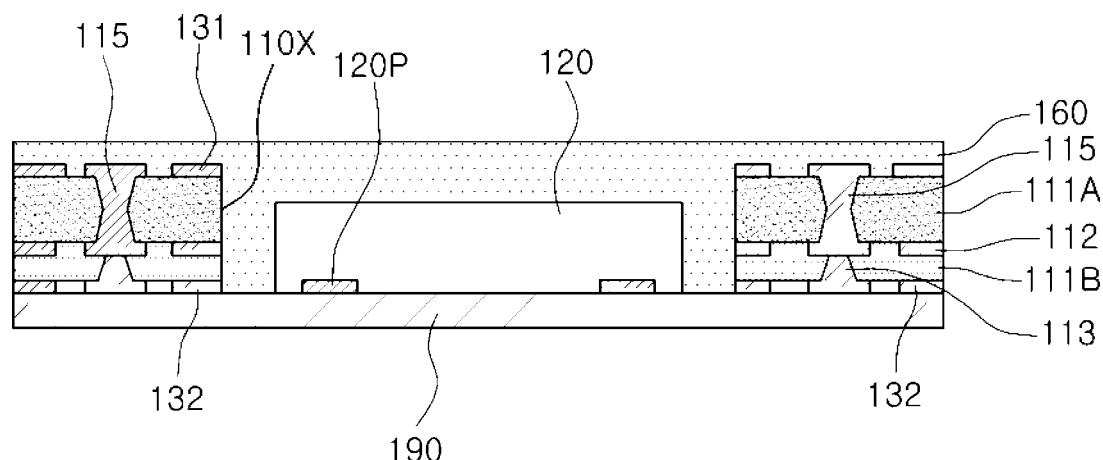

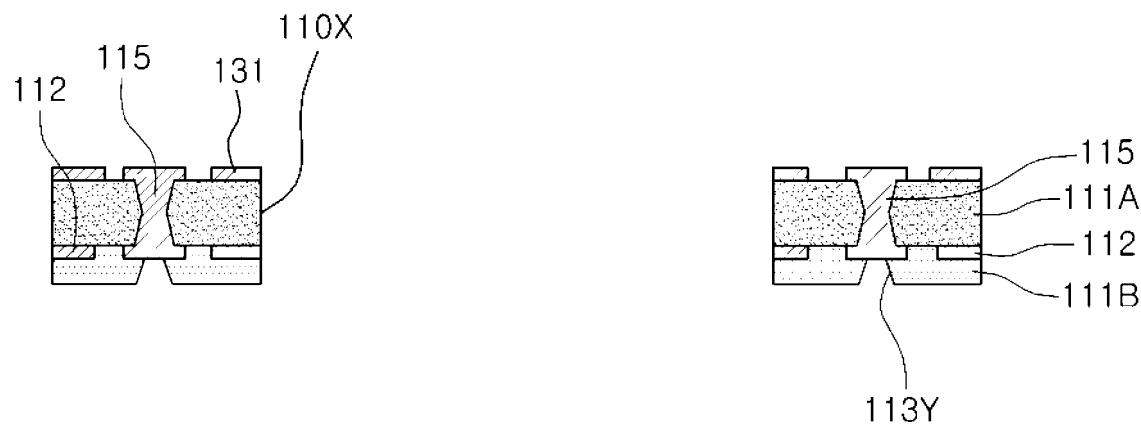

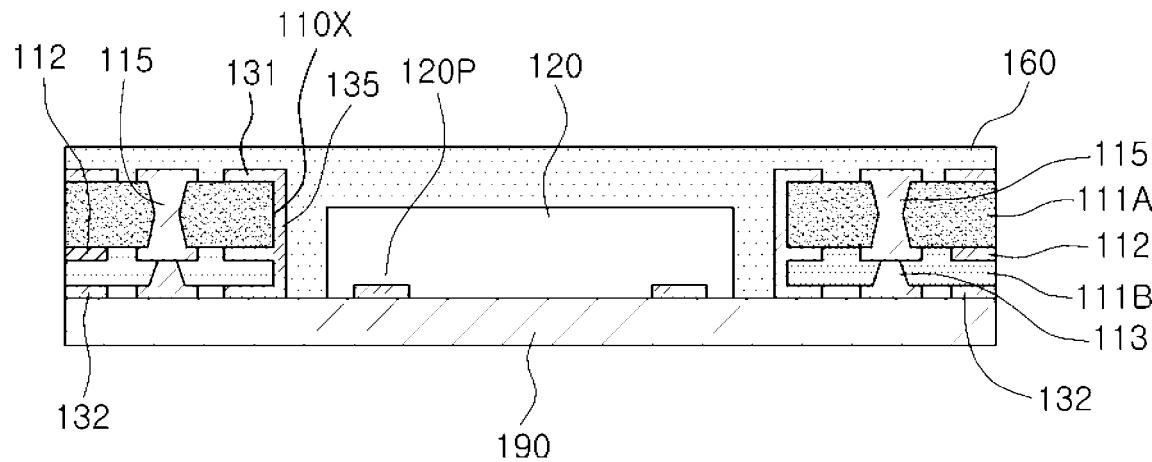

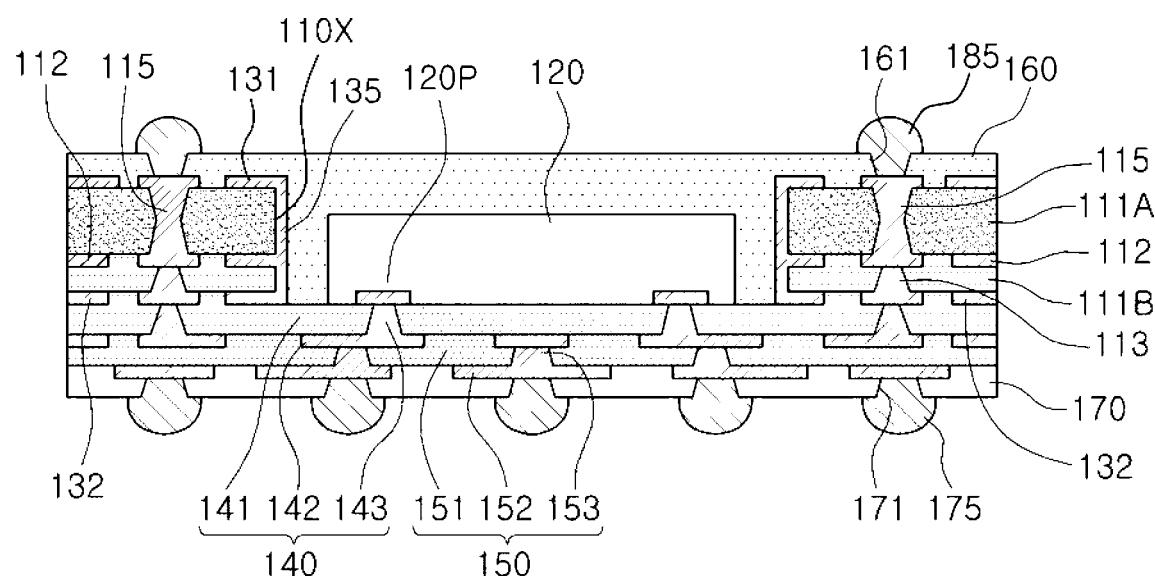

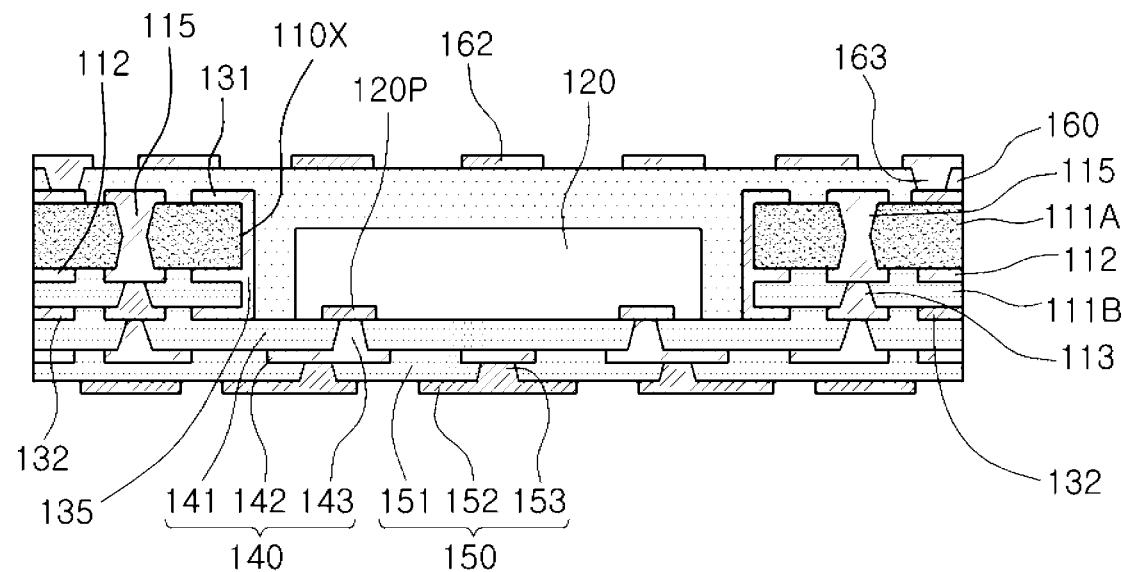

**【0084】** 圖 6 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0085】** 圖 7 是電子元件封裝沿圖 6 所示的線 II-II' 截取的示意性平面圖。

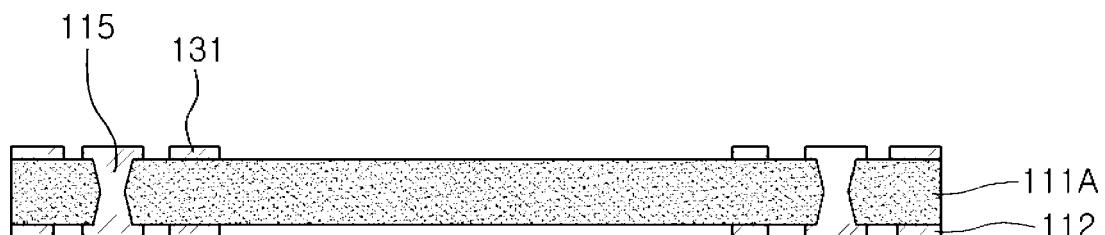

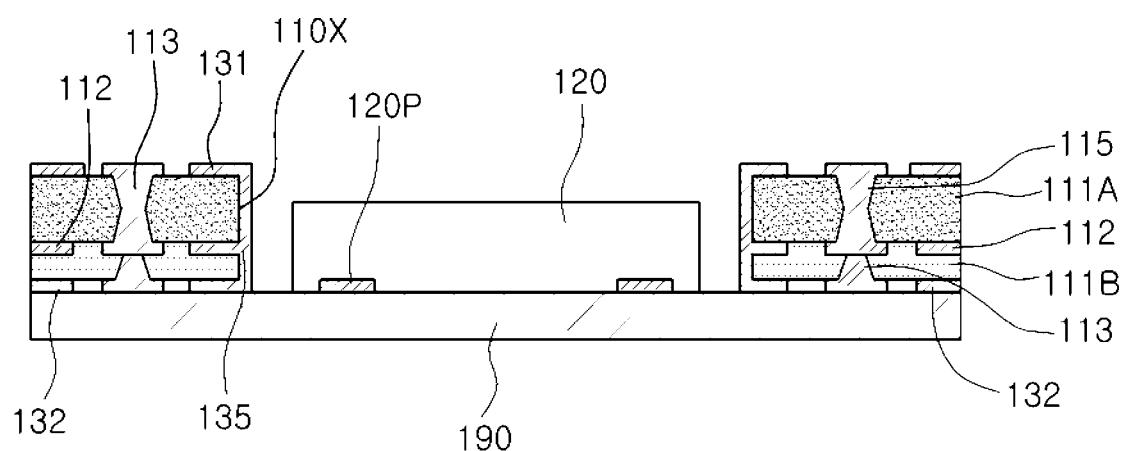

**【0086】** 參照圖 6 及圖 7，根據另一實例的電子元件封裝 100B 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

105-10-17

**【0087】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。每一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 6 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0088】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100B 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0089】** 第二配線層 132 可安置於第二絕緣層 111B 的下表面 110B 上。亦即，第二配線層 132 可安置於框架 110 之外。第三配線層 131 可安置於第一絕緣層 111A 的上表面 110A 上。亦即，第三配線層 131 亦可安置於框架 110 之外。此處，第二配線層 132 或第三配線層 131 安置於框架 110 之外的含義為第二配線層 132 或第三配線層 131 不安置於框架 110 的上表面 110A 與下表面 110B 之間。第三配線層 131 及第二配線層 132 亦可充當重新分配圖案及/或焊墊圖案，且例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金

105-10-17

(Au)、鎳(Ni)、鉛(Pb)、或其合金等傳導性材料可用作第三配線層131的及第二配線層132的材料。第三配線層131及第二配線層132可依對應層的設計而定執行各種功能。舉例而言，第三配線層131及第二配線層132可充當接地(GND)圖案、功率(PWR)圖案、訊號(S)圖案、焊線導引(bond finger, BF)圖案等而作為重新分配圖案。此處，訊號(S)圖案可包括除接地(GND)圖案、功率(PWR)圖案、焊線導引(BF)圖案等以外的各種訊號，例如資料訊號等。此外，第三配線層131及第二配線層132可充當通孔焊墊、內部通孔焊墊、外部連接端子焊墊等而作為焊墊圖案。由於充當內部通孔的焊墊圖案安置於框架110中，因此不需要在重新分配部140及150上形成內部通孔的焊墊，且因而可增大設計面積，藉此可提升設計的自由度。第三配線層131的厚度及第二配線層132的厚度亦無特別限制，且可為例如10微米至50微米左右。若需要，則可在第三配線層131的被暴露出的圖案上進一步形成表面處理層。所述表面處理層可藉由例如電解鍍金、無電鍍金、有機可焊性保護劑、或無電鍍錫、無電鍍銀、無電鍍鎳/置換鍍金、直接浸金鍍覆、熱空氣焊料均塗等來形成。

**【0090】** 穿透過第一絕緣層111A的內部通孔115可用於將安置於不同的層中的第三配線層131及第一配線層112電性連接至彼此，且例如銅(Cu)、鋁(Al)、銀(Ag)、錫(Sn)、金(Au)、鎳(Ni)、鉛(Pb)、或其合金等傳導性材料可用作內部通孔115的材料。內部通孔115可直接連接至在第三配線層131及第一配

105-10-17

線層 112 中充當內部通孔的焊墊的焊墊圖案。內部通孔 115 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修改。舉例而言，依安裝於電子元件封裝 100B 上的另一電子元件封裝的形式而定，內部通孔 115 可僅在第一絕緣層 111A 的如圖 6 及圖 7 中所示的特定區中分散成彼此間隔開或可在第一絕緣層 111A 的整個表面上方分散成彼此間隔開。在其中使用例如 Fe-Ni 系合金等金屬作為第一絕緣層 111A 的材料的情形中，絕緣材料可安置於所述金屬與內部通孔 115 及/或第三配線層 131 及第一配線層 112 之間，以使所述金屬與內部通孔 115 及/或第三配線層 131 及第一配線層 112 之間電性絕緣。內部通孔 115 可具有較通孔 113 大的直徑。內部通孔 115 可具有較通孔 113 大的直徑，但並非僅限於此。依第一絕緣層 111A 而定，內部通孔 115 可具有與通孔 113 實質上相同的形狀、直徑等。

**【0091】** 在根據另一實例的電子元件封裝 100B 中，囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分。此外，根據另一實例的電子元件封裝 100B 可更包括安置於囊封劑 160 的第二開口部 161 中以藉此暴露於外部的第二外部連接端子 185。使用第二外部連接端子 185 的目的可為將電子元件封裝 100B 上的另一電子元件、另一電子元件封裝等物理地連接至及/或電性連接至電子元件封裝 100B。舉例而言，另一電子元件封裝可經由第二外部連接端子 185 而安裝於電子元件封裝 100B 上，且因此可形成堆疊式封裝

105-10-17

結構。第二外部連接端子 185 可安置於囊封劑 160 的第二開口部 161 中，且可連接至經由第二開口部 161 而暴露出的第三配線層 131。因而，第二外部連接端子 185 亦可電性連接至電子元件 120。

**【0092】** 第二外部連接端子 185 可由例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、焊料等傳導性材料形成，但並非特別地限定於此。第二外部連接端子 185 可為焊盤、球、引腳等。第二外部連接端子 185 可由多個層或單個層形成。在其中第二外部連接端子 185 由多個層形成的情形中，第二外部連接端子 185 可含有銅柱及焊料，且在其中第二外部連接端子 185 由單個層形成的情形中，第二外部連接端子 185 可含有錫銀焊料或銅。然而，此僅為實例，且第二外部連接端子 185 並非僅限於此。

**【0093】** 圖 8A 至圖 8M 是說明製造電子元件封裝 100B 的製程的實例的示意圖。

**【0094】** 在對製造電子元件封裝 100B 的製程的實例的說明中，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

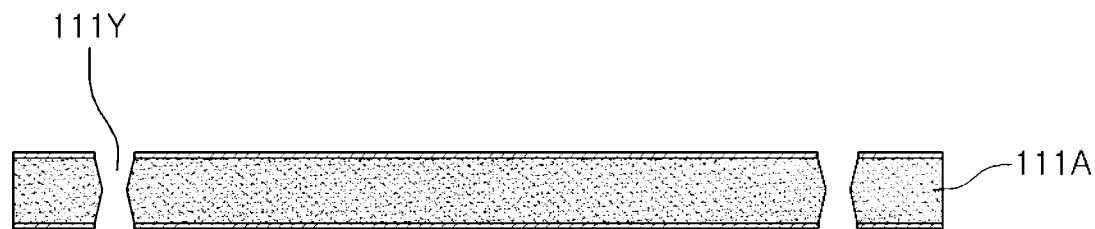

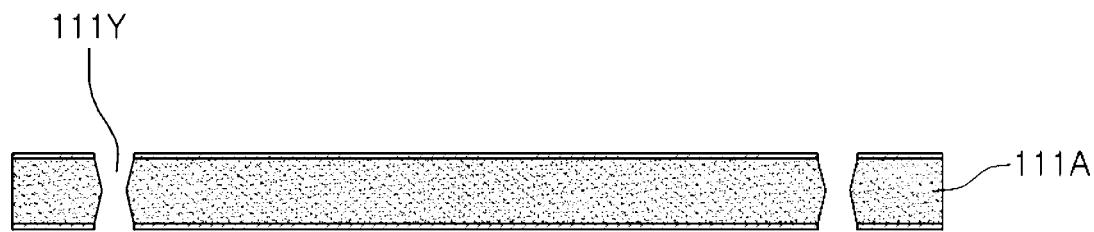

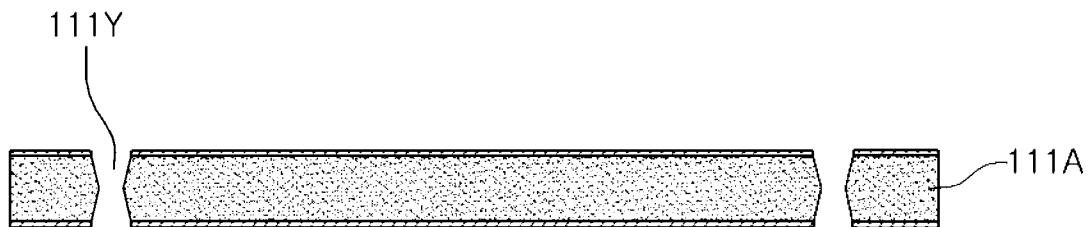

**【0095】** 參照圖 8A，可製備第一絕緣層 111A。參照圖 8B，可形成穿透過第一絕緣層 111A 的上表面及下表面的貫穿孔 111Y。可使用機械鑽孔及/或雷射鑽孔來形成貫穿孔 111Y。此處，所述雷射鑽孔可為 CO<sub>2</sub> 雷射鑽孔或 YAG 雷射鑽孔，但並非僅限於此。在其中使用機械鑽孔及/或雷射鑽孔形成貫穿孔 111Y 的情形中，可對

105-10-17

貫穿孔 111Y 執行除汙製程，以移除貫穿孔 111Y 中的樹脂污垢。可使用例如高錳酸鹽方法來執行所述除汙製程。在某些情形中，亦可藉由光刻方法來形成所述貫穿孔 111Y。參照圖 8C，可在第一絕緣層 111A 的上表面及下表面上分別形成第三配線層 131 及第一配線層 112。此外，可以導性材料填充貫穿孔 111Y，以形成內部通孔 115。亦可藉由習知的方法來形成內部通孔 115。舉例而言，可使用乾膜圖案藉由電解鍍銅、無電鍍銅等來形成內部通孔 115。更詳言之，可使用例如化學氣相沈積、物理氣相沈積、濺鍍、減性製程、加性製程、半加性製程、經修改半加性製程等方法來形成內部通孔 115，但並非僅限於此。參照圖 8D，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。參照圖 8E，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B 中形成通孔 113。參照圖 8F，可形成穿透過第一絕緣層 111A 及第二絕緣層 111B 的貫穿孔 110X。因此，可形成具有貫穿孔 110X 的框架 110。

**【0096】** 參照圖 8G，可將黏合膜 190 貼附至第二配線層 132。參照圖 8H，可在貫穿孔 110X 中安置電子元件 120。參照圖 8I，可使用囊封劑 160 對電子元件 120 進行囊封。參照圖 8J，可剝除黏合膜 190。參照圖 8K，可形成包括重新分配部絕緣層 141、重新分配部配線層 142、及重新分配部通孔 143 的重新分配部 140。接著，可形成包括重新分配部絕緣層 151、重新分配部配線層 152、及重新分配部通孔 153 的重新分配部 150。參照圖 8L，可形成連

105-10-17

接至重新分配部 140 及 150 的保護層 170。參照圖 8M，可形成保護層 170 的第一開口部 171 及安置於第一開口部 171 中的第一外部連接端子 175。此外，可在囊封劑 160 的外表面中形成第二開口部 161 以便暴露出第三配線層 131 的至少部分，且可形成安置於第二開口部 161 中的第二外部連接端子 185。可使用機械鑽孔及/或雷射鑽孔來形成第二開口部 161。作為另一選擇，可藉由光刻方法來形成第二開口部 161。在其中使用機械鑽孔及/或雷射鑽孔形成第二開口部 161 的情形中，可使用高錳酸鹽方法等對第二開口部 161 執行除汙製程，以移除樹脂污垢。依第二外部連接端子 185 的結構或形式而定，可藉由先前技術中眾所習知的方法來形成第二外部連接端子 185。可藉由回焊來固定第二外部連接端子 185，且可將第二外部連接端子 185 的部分嵌置於囊封劑 160 中以增強固定力，且第二外部連接端子 185 的其餘部分可暴露於外部，藉此可提高可靠性。在某些情形中，可僅形成安置於囊封劑 160 的第二開口部 161 中的第二外部連接端子 185，且可在保護層 170 中僅形成第一開口部 171，並且若需要，則可藉由由購買電子元件封裝 100B 的客戶進行的單獨製程形成安置於第一開口部 171 中的第一外部連接端子 175。

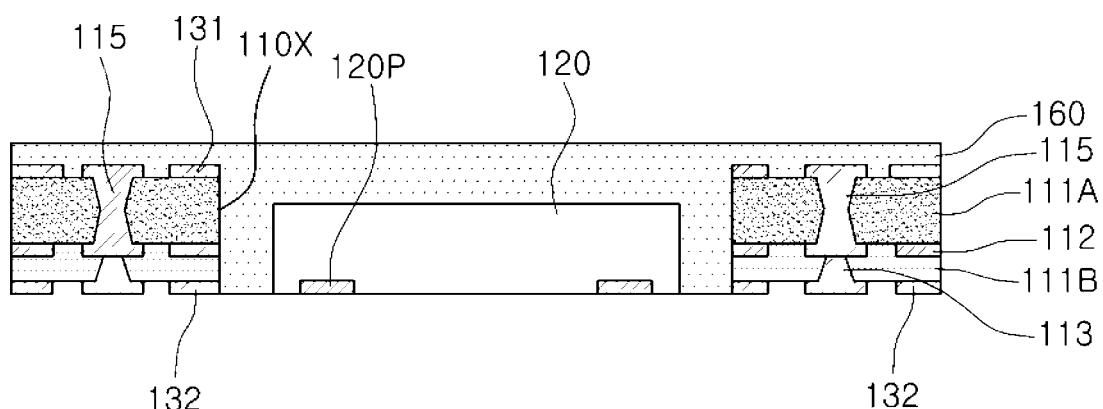

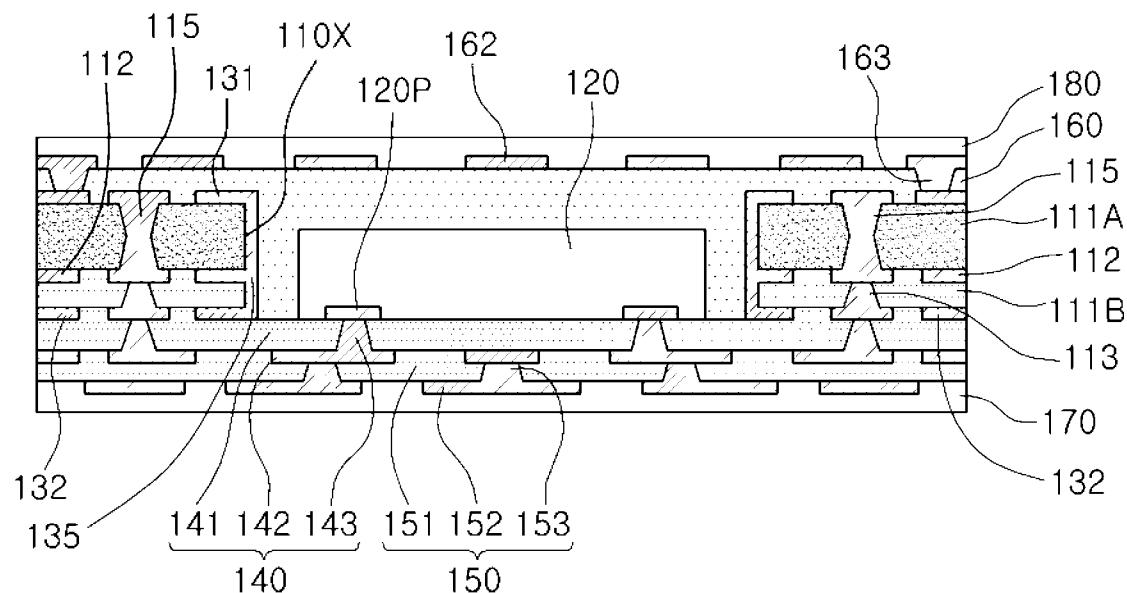

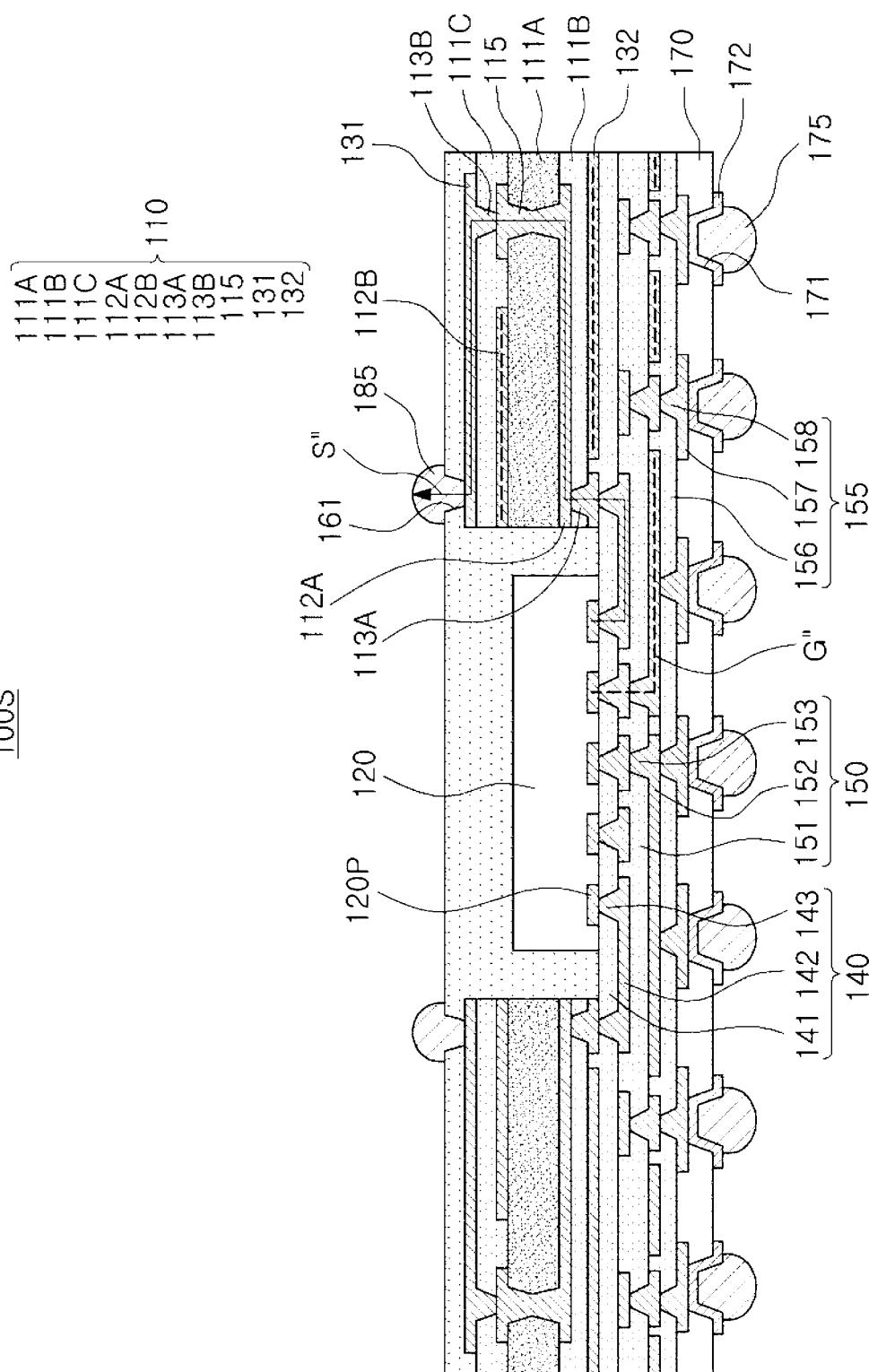

**【0097】** 圖 9 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0098】** 圖 10 是電子元件封裝沿圖 9 所示的線 III-III' 截取的示意性平面圖。

**【0099】** 參照圖 9 及圖 10，根據另一實例的電子元件封裝 100C

105-10-17

可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、用於囊封電子元件 120 的囊封劑 160、安置於囊封劑 160 上的外配線層 162、以及穿透過囊封劑 160 的外通孔 163。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0100】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 9 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0101】** 在下文中，將更詳細地闡述包含於根據另一實例的電子

105-10-17

元件封裝 100C 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0102】** 穿透過第一絕緣層 111A 的內部通孔 115 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修改。舉例而言，依安裝於電子元件封裝 100C 上的另一電子元件封裝的形式而定，內部通孔 115 可如圖 9 及圖 10 中所示在第一絕緣層 111A 的整個表面上方分散成彼此間隔開、或可在第一絕緣層 111A 的僅特定區中分散成間隔開。

**【0103】** 安置於囊封劑 160 上的外配線層 162 亦可充當重新分配圖案及/或焊墊圖案，且例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作外配線層 162 的材料。以上已闡述了詳細實例。外配線層 162 可依對應層的設計而定執行各種功能。舉例而言，外配線層 162 可充當接地 (GND) 圖案、功率 (PWR) 圖案、訊號 (S) 圖案等而作為重新分配圖案。此處，訊號 (S) 圖案可包括除接地 (GND) 圖案、功率 (PWR) 圖案等以外的各種訊號，例如資料訊號等。此外，外配線層 162 可充當通孔焊墊、外部連接端子焊墊等而作為焊墊圖案。由於外配線層 162 的圖案可在囊封劑 160 的整個表面上方分散成彼此間隔開且第二外部連接端子 185 亦可在以下將闡述的覆蓋層 180 的整個表面上方分散成彼此間隔開，因此可存在各種設計。外配線層 162 的厚度亦無特別限制，但可為例如約 10 微米至 50 微米左右。若需要，則可在外配線層 162 的被暴露出的部分

105-10-17

上進一步形成表面處理層。所述表面處理層可藉由例如電解鍍金、無電鍍金、有機可焊性保護劑、或無電鍍錫、無電鍍銀、無電鍍鎳/置換鍍金、直接浸金鍍覆、熱空氣焊料均塗等而形成。

**【0104】** 局部地穿透過囊封劑 160 的外通孔 163 可將形成於不同的層上的第三配線層 131 及外配線層 162 電性連接至彼此，藉此在電子元件封裝 100C 內形成電性路徑。例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等傳導性材料可用作外通孔 163 的材料。外通孔 163 可被完全填充以傳導性材料。作為另一選擇，傳導性材料可沿通孔的壁形成。此外，外通孔 163 可具有先前技術中習知的所有形狀，例如其中通孔的直徑朝下表面變得更小的錐形形狀、其中通孔的直徑朝下表面變得更大的倒錐形形狀、圓柱形形狀等。

**【0105】** 根據另一實例的電子元件封裝 100C 可更包括安置於囊封劑 160 之上的覆蓋層 180。使用覆蓋層 180 的目的可為保護囊封劑 160、外配線層 162 等不受外部的物理或化學損害等。覆蓋層 180 可具有第三開口部 181，第三開口部 181 暴露出安置於囊封劑 160 上的外配線層 162 的至少部分。儘管第三開口部 181 可暴露出外配線層 162 的上表面的部分，然而在某些情形中第三開口部 181 亦可暴露出外配線層 162 的側表面。覆蓋層 180 的材料並無特別限制。舉例而言，可使用阻焊劑作為覆蓋層 180 的材料。此外，可使用各種感光成像介電樹脂、味之素構成膜等作為覆蓋層 180 的材料。若需要，則覆蓋層 180 亦可由多個層形成。

105-10-17

**【0106】** 根據另一實例的電子元件封裝 100C 可更包括安置於覆蓋層 180 的第三開口部 181 中的第二外部連接端子 185。第二外部連接端子 185 可安置於第三開口部 181 中，且可連接至經由第三開口部 181 而暴露出的外配線層 162。亦即，第二外部連接端子 185 可如在電子元件封裝 100B 中般安置於囊封劑 160 的第二開口部 161 中，或可如在電子元件封裝 100C 中般安置於覆蓋層 180 的第三開口部 181 中。

**【0107】** 圖 11A 至圖 11M 是說明製造電子元件封裝 100C 的製程的實例的示意圖。

**【0108】** 在對製造電子元件封裝 100C 的製程的實例的說明中，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0109】** 參照圖 11A，可製備第一絕緣層 111A。參照圖 11B，可形成穿透過第一絕緣層 111A 的上表面及下表面的貫穿孔 111Y。參照圖 11C，可在第一絕緣層 111A 的上表面及下表面上分別形成第三配線層 131 及第一配線層 112。此外，可以導性材料填充貫穿孔 111Y，以形成內部通孔 115。參照圖 11D，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。參照圖 11E，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B 中形成通孔 113。參照圖 11F，可形成穿透過第一絕緣層 111A 及第二絕緣層 111B 的貫穿孔 110X。因此，可形成具有貫穿孔 110X 的框架 110。

105-10-17

【0110】 參照圖 11G，可將黏合膜 190 貼附至第二配線層 132。參照圖 11H，可在貫穿孔 110X 中安置電子元件 120。參照圖 11I，可使用囊封劑 160 對電子元件 120 進行囊封。參照圖 11J，可剝除黏合膜 190。參照圖 11K，可形成包括重新分配部絕緣層 141、重新分配部配線層 142、及重新分配部通孔 143 的重新分配部 140。接著，可形成包括重新分配部絕緣層 151、重新分配部配線層 152、及重新分配部通孔 153 的重新分配部 150。此外，可形成安置於囊封劑 160 上的外配線層 162 及穿透過囊封劑 160 的外通孔 163。亦可使用機械鑽孔及/或雷射鑽孔來形成用於形成外通孔 163 的通孔洞，或亦可藉由光刻方法來形成所述通孔洞。在其中使用機械鑽孔及/或雷射鑽孔形成通孔洞的情形中，可利用高錳酸鹽方法等對所述通孔洞執行除汙製程，以移除樹脂污垢。亦可使用乾膜圖案藉由電解鍍銅、無電鍍銅等來形成外配線層 162 及外通孔 163。更詳言之，可使用例如化學氣相沈積、物理氣相沈積、濺鍍、減性製程、加性製程、半加性製程、經修改半加性製程等方法來形成外配線層 162 及外通孔 163。參照圖 11L，可形成連接至重新分配部 140 及 150 的保護層 170 以及連接至囊封劑 160 的覆蓋層 180。亦可藉由對覆蓋層 180 的前驅物進行積層並接著硬化所述前驅物的方法、施加用於形成覆蓋層 180 的材料並接著硬化所述材料的方法等來形成覆蓋層 180。可使用例如以下方法等作為積層所述前驅物的方法：執行在高溫下對前驅物壓製預定時間的熱壓製製程、對所述前驅物進行減壓、並且接著將所述前驅物冷卻至室溫、

105-10-17

在冷壓製程中冷卻所述前驅物、並且接著分離作業工具。可使用例如利用刮板施加油墨的網版印刷方法、以霧形式施加油墨的噴霧印刷方法等作為施加所述材料的方法。所述硬化製程一其為後置製程一可為使材料乾燥以不被完全硬化從而使用光刻方法等的製程。參照圖 11M，可在覆蓋層 180 的外表面中形成第三開口部 181，從而暴露出外配線層 162 的至少部分，且可形成安置於第三開口部 181 中的第二外部連接端子 185。此外，可形成保護層 170 的第一開口部 171 及安置於第一開口部 171 中的第一外部連接端子 175。可使用機械鑽孔及/或雷射鑽孔來形成第三開口部 181。作為另一選擇，可藉由光刻方法來形成第三開口部 181。在其中使用機械鑽孔及/或雷射鑽孔形成第三開口部 181 的情形中，可利用高錳酸鹽方法等對第三開口部 181 執行除汙製程，以移除樹脂污垢。依第二外部連接端子 185 的結構或形式而定，可藉由在先前技術中眾所習知的方法來形成第二外部連接端子 185。可藉由回焊來固定第二外部連接端子 185，且第二外部連接端子 185 的部分可嵌置於覆蓋層 180 中以增強固定力，且第二外部連接端子 185 的其餘部分可暴露於外部，藉此可提高可靠性。在某些情形中，可僅形成安置於覆蓋層 180 的第三開口部 181 中的第二外部連接端子 185，且可在保護層 170 中僅形成第一開口部 171，並且若需要，則可藉由由購買電子元件封裝 100C 的客戶進行的單獨製程而形成安置於第一開口部 171 中的第一外部連接端子 175。

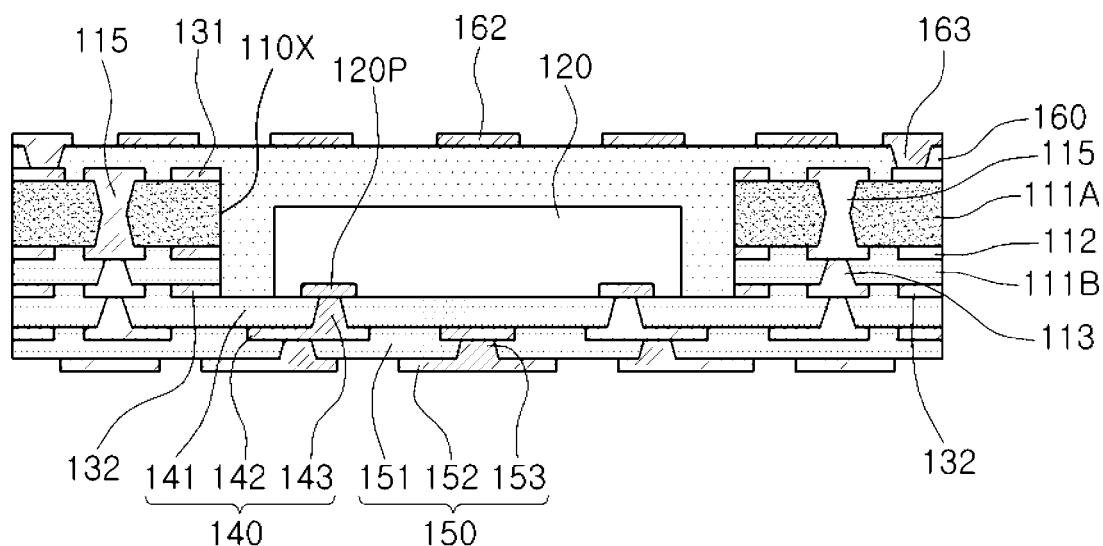

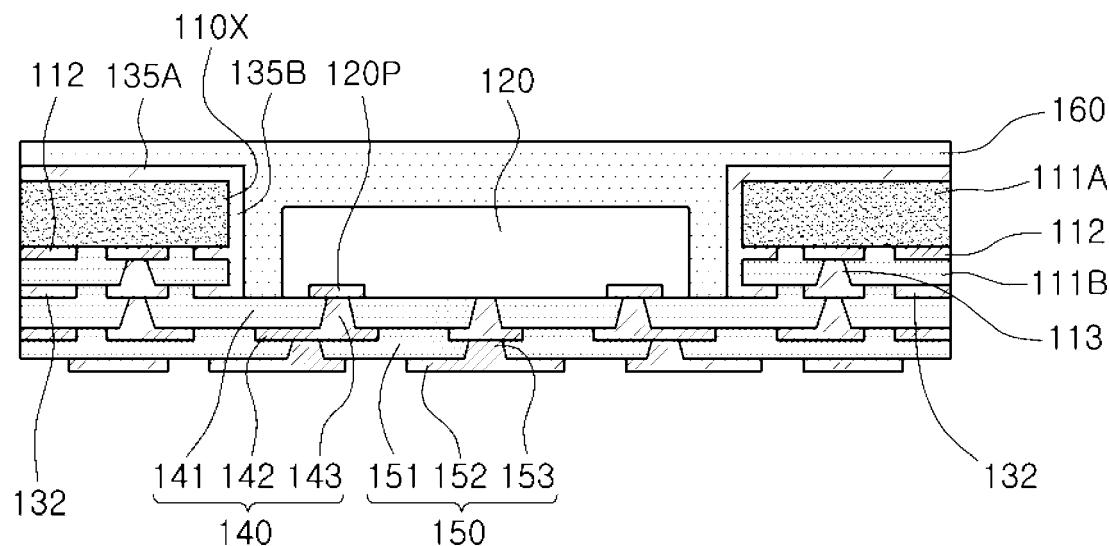

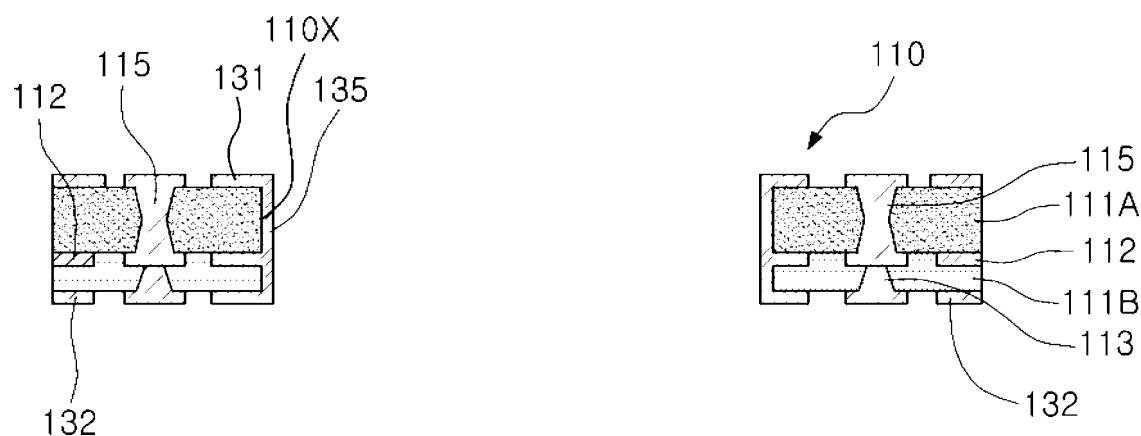

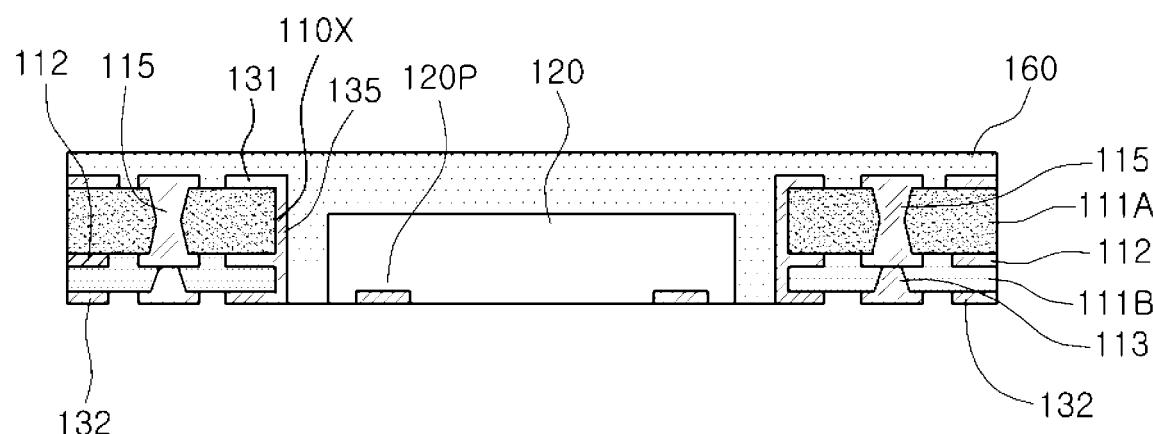

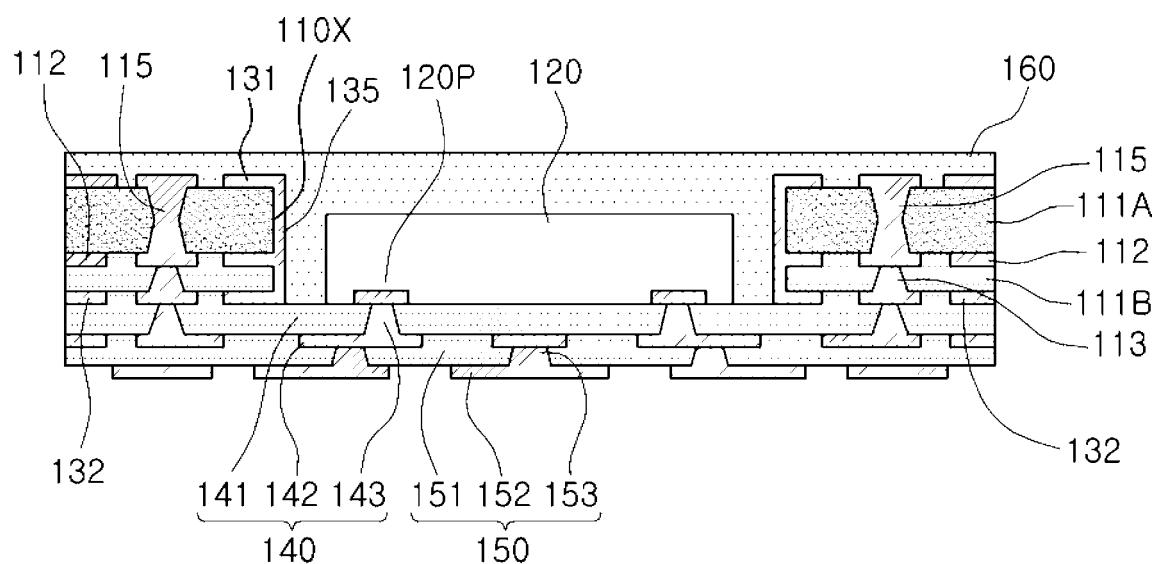

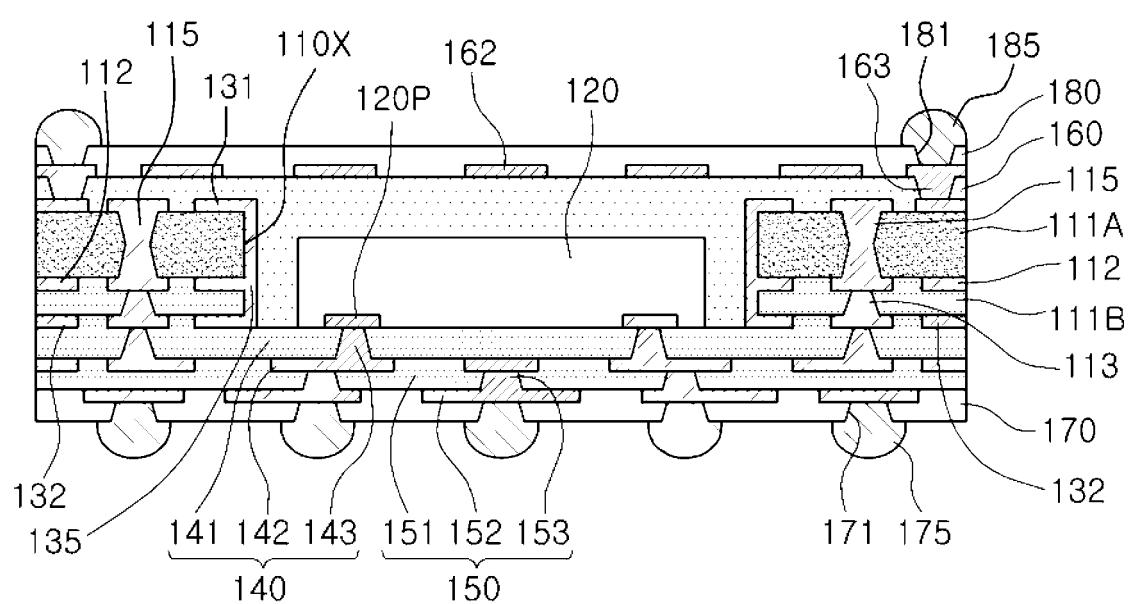

**【0111】** 圖 12 是示意性地說明電子元件封裝的另一實例的剖視

105-10-17

圖。

**【0112】** 圖 13 是電子元件封裝沿圖 12 所示的線 IV-IV' 截取的示意性平面圖。

**【0113】** 參照圖 12 及圖 13，根據另一實例的電子元件封裝 100D 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第一金屬層 135A、安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132、以及安置於貫穿孔 110X 的內表面上的第二金屬層 135B。

**【0114】** 貫穿孔 110X 可依序穿透過第一金屬層 135A、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 12 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第一金屬層 135A 的上表面下、或者位於與第一金屬層 135A 的上表

105-10-17

面相同的位階處或位於第一金屬層 135A 的上表面之上，只要第一金屬層 135A 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0115】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100D 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0116】** 使用安置於貫穿孔 110X 的內表面上的第二金屬層 135B 的目的可為改善熱輻射特性及/或阻擋電磁波。第二金屬層 135B 的材料並無特別限制，只要其為例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、或其合金等具有高熱傳導性的金屬即可。第一金屬層 135A 可連接至第二金屬層 135B。在此種情形中，自電子元件 120 發出的熱可經由第二金屬層 135B 而傳導至第一金屬層 135A，以藉此分散至電子元件封裝 100D 的上部部分。第二金屬層 135B 可連接至在第二配線層 132 中充當接地圖案的重新分配圖案。此外，第二金屬層 135B 亦可連接至在第一配線層 112 中充當接地 (GND) 圖案的重新分配圖案。自電子元件 120 發出的熱可經由第二金屬層 135B 而傳導至第一配線層 112 及第三配線層 132 中的接地 (GND) 圖案，以藉此分散至電子元件封裝 100D 的下部部分。所述接地 (GND) 圖案亦可用於阻擋電磁波。作為另一選擇，可藉由對流或輻射來分散熱。

**【0117】** 圖 14A 至圖 14L 是說明製造電子元件封裝 100D 的製程的實例的示意圖。

**【0118】** 在對製造電子元件封裝 100D 的製程的實例的說明中，將

105-10-17

不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0119】** 參照圖 14A，可製備第一絕緣層 111A。參照圖 14B，可在第一絕緣層 111A 的上表面及下表面上分別形成第一金屬層 135A 及第一配線層 112。參照圖 14C，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。參照圖 14D，可形成穿透過第一絕緣層 111A 及第二絕緣層 111B 的貫穿孔 110X。此外，可形成穿透過第二絕緣層 111B 的通孔洞 113Y。參照圖 14E，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B 中形成通孔 113。此外，可在貫穿孔 110X 的內表面上形成第二金屬層 135B。舉例而言，可使用乾膜圖案藉由電解鍍銅、無電鍍銅等來形成第二金屬層 135B。詳言之，可使用例如化學氣相沈積、物理氣相沈積、濺鍍、減性製程、加性製程、半加性製程、經修改半加性製程等方法來形成第二金屬層 135B，但並非僅限於此。如此一來，可形成具有貫穿孔 110X 的框架 110。

**【0120】** 與圖中所示者不同，可藉由封孔方法 (tenting method) 等而首先在第一絕緣層 111A 的僅下表面上形成第一配線層 112，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B，且可形成通孔洞 113Y 及貫穿孔 110X。接著，在藉由以傳導性材料填充通孔洞 113Y 而形成通孔 113 的同時可在貫穿孔 110X 的內壁上形成第二金屬層 135B。同時，可在第一絕緣層 111A 的上表面及第二絕緣層 111B 的下表面上分別形成第一金屬層 135A 及第二配線

層 132。

**【0121】** 參照圖 14F，可將黏合膜 190 貼附至第二配線層 132。參照圖 14G，可在貫穿孔 110X 中安置電子元件 120。參照圖 14H，可使用囊封劑 160 對電子元件 120 進行囊封。參照圖 14I，可剝除黏合膜 190。參照圖 14J，可形成包括重新分配部絕緣層 141、重新分配部配線層 142、及重新分配部通孔 143 的重新分配部 140。接著，可形成包括重新分配部絕緣層 151、重新分配部配線層 152、及重新分配部通孔 153 的重新分配部 150。參照圖 14K，可形成連接至重新分配部 140 及 150 的保護層 170。參照圖 14L，可在保護層 170 中形成第一開口部 171。接著，可形成安置於第一開口部 171 中的第一外部連接端子 175。在某些情形中，可僅形成第一開口部 171，且若需要，則可藉由購買電子元件封裝 100D 的客戶進行的單獨製程而形成第一外部連接端子 175。

**【0122】** 圖 15 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0123】** 圖 16 是電子元件封裝沿圖 15 所示的線 V-V' 截取的示意性平面圖。

**【0124】** 參照圖 15 及圖 16，根據另一實例的電子元件封裝 100E 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一

105-10-17

絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132、以及安置於貫穿孔 110X 的內表面上的金屬層 135。

**【0125】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 15 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0126】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100E 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0127】** 安置於貫穿孔 110X 的內表面上的金屬層 135 可連接至在第三配線層 131 中充當接地（GND）圖案的重新分配圖案。在此種情形中，自電子元件 120 發出的熱可經由金屬層 135 而傳導至

105-10-17

第三配線層 131 中的接地（GND）圖案，以藉此分散至電子元件封裝 100E 的上部部分。金屬層 135 可連接至在第二配線層 132 中充當接地（GND）圖案的重新分配圖案。金屬層 135 亦可連接至在第一配線層 112 中充當接地（GND）圖案的重新分配圖案。在此種情形中，自電子元件 120 發出的熱可經由金屬層 135 而傳導至第一配線層 112 及第三配線層 132 中的接地（GND）圖案，以藉此分散至電子元件封裝 100E 的下部部分。接地（GND）圖案亦可用於阻擋電磁波。作為另一選擇，可藉由對流或輻射來分散熱。

**【0128】** 圖 17A 至圖 17M 是說明製造電子元件封裝 100E 的製程的實例的示意圖。

**【0129】** 在對製造電子元件封裝 100E 的製程的實例的說明中，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0130】** 參照圖 17A，可製備第一絕緣層 111A。參照圖 17B，可形成穿透過第一絕緣層 111A 的上表面及下表面的貫穿孔 111Y。參照圖 17C，可在第一絕緣層 111A 的上表面及下表面上分別形成第三配線層 131 及第一配線層 112。此外，可以導性材料填充貫穿孔 111Y，以形成內部通孔 115。參照圖 17D，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。參照圖 17E，可形成穿透過第一絕緣層 111A 及第二絕緣層 111B 的貫穿孔 110X。此外，可形成穿透過第二絕緣層 111B 的通孔洞 113Y。參照圖 17F，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B

105-10-17

中形成通孔 113。此外，可在貫穿孔 110X 的內表面上形成金屬層 135。如此一來，可形成具有貫穿孔 110X 的框架 110。

**【0131】** 與圖中所示者不同，可藉由封孔方法等而首先在第一絕緣層 111A 的僅下表面上形成第一配線層 112，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B，且可形成通孔洞 113Y、貫穿孔 111Y 及貫穿孔 110X。接著，在藉由以傳導性材料填充通孔洞 113Y 及貫穿孔 111Y 而形成通孔 113 及內部通孔 115 的同時可在貫穿孔 110X 的內壁上形成金屬層 135。同時，可在第一絕緣層 111A 的上表面及第二絕緣層 111B 的下表面上分別形成第三配線層 131 及第二配線層 132。

**【0132】** 參照圖 17G，可將黏合膜 190 貼附至第二配線層 132。參照圖 17H，可在貫穿孔 110X 中安置電子元件 120。參照圖 17I，可使用囊封劑 160 對電子元件 120 進行囊封。參照圖 17J，可剝除黏合膜 190。參照圖 17K，可形成包括重新分配部絕緣層 141、重新分配部配線層 142、及重新分配部通孔 143 的重新分配部 140。接著，可形成包括重新分配部絕緣層 151、重新分配部配線層 152、及重新分配部通孔 153 的重新分配部 150。參照圖 17L，可形成連接至重新分配部 140 及 150 的保護層 170。參照圖 17M，可在保護層 170 中形成第一開口部 171，且可形成安置於第一開口部 171 中的第一外部連接端子 175。此外，可在囊封劑 160 的外表面中形成第二開口部 161，以便暴露出第三配線層 131 的至少部分，且可形成安置於第二開口部 161 中的第二外部連接端子 185。在某些情

形中，可僅形成安置於囊封劑 160 的第二開口部 161 中的第二外部連接端子 185，且可在保護層 170 中僅形成第一開口部 171，並且若需要，則可藉由由購買電子元件封裝 100E 的客戶進行的單獨製程而形成安置於第一開口部 171 中的第一外部連接端子 175。

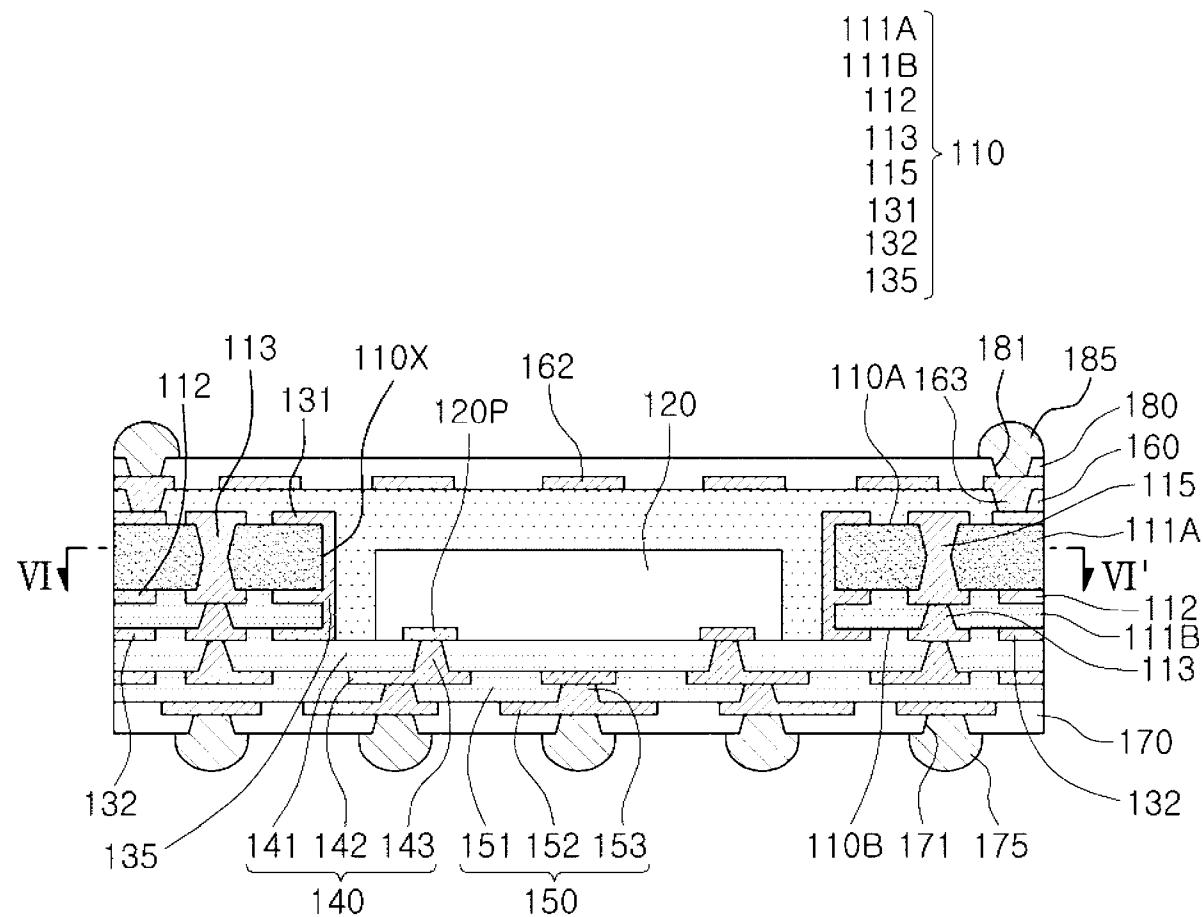

**【0133】** 圖 18 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0134】** 圖 19 是電子元件封裝沿圖 18 所示的線 VI-VI' 截取的示意性平面圖。

**【0135】** 參照圖 18 及圖 19，根據另一實例的電子元件封裝 100F 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、用於囊封電子元件 120 的囊封劑 160、安置於囊封劑 160 上的外配線層 162、及穿透過囊封劑 160 的外通孔 163。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132、及安置於貫穿孔 110X 的內表面上的金屬層 135。

**【0136】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件

105-10-17

120 的上表面與下表面之間的位階處。如圖 18 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0137】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100F 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0138】** 外配線層 162 的安置於囊封劑 160 上的一部分可為充當接地（GND）圖案的重新分配圖案。此處，金屬層 135 亦可經由在第三配線層 131 中充當接地（GND）圖案的重新分配圖案而連接至安置於囊封劑 160 上的外配線層 162。此處，安置於囊封劑 160 上的外配線層 162 可以板形式安置於由囊封劑 160 所囊封的電子元件 120 之上。在此種情形中，由於電子元件 120 的上部部分、下部部分、及側部部分的絕大部分被金屬覆蓋，因此熱輻射特性及電磁波阻擋效果可為優異的。作為另一選擇，可藉由對流或輻射來分散熱。

**【0139】** 圖 20A 至圖 20M 是說明製造電子元件封裝 100F 的製程的實例的示意圖。

105-10-17

**【0140】** 在對製造電子元件封裝 100F 的製程的實例的說明中，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0141】** 參照圖 20A，可製備第一絕緣層 111A。參照圖 20B，可形成穿透過第一絕緣層 111A 的上表面及下表面的貫穿孔 111Y。參照圖 20C，可在第一絕緣層 111A 的上表面及下表面上分別形成第三配線層 131 及第一配線層 112。此外，可以傳導性材料填充貫穿孔 111Y，以形成內部通孔 115。參照圖 20D，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B。參照圖 20E，可形成穿透過第一絕緣層 111A 及第二絕緣層 111B 的貫穿孔 110X。此外，可形成穿透過第二絕緣層 111B 的通孔洞 113Y。參照圖 20F，可在第二絕緣層 111B 之下形成第二配線層 132，且可在第二絕緣層 111B 中形成通孔 113。此外，可在貫穿孔 110X 的內表面上形成金屬層 135。如此一來，可形成具貫穿孔 110X 的框架 110。

**【0142】** 與圖中所示者不同，可藉由封孔方法等而首先在第一絕緣層 111A 的僅下表面上形成第一配線層 112，可在第一絕緣層 111A 的下表面上形成第二絕緣層 111B，且可形成通孔洞 113Y、貫穿孔 111Y、及貫穿孔 110X。接著，在藉由以傳導性材料填充通孔洞 113Y 及貫穿孔 111Y 而形成通孔 113 及內部通孔 115 的同時可在貫穿孔 110X 的內壁上形成金屬層 135。同時，可在第一絕緣層 111A 的上表面及第二絕緣層 111B 的下表面上分別形成第三配線層 131 及第二配線層 132。

105-10-17

**【0143】** 參照圖 20G，可將黏合膜 190 貼附至第二配線層 132。參照圖 20H，可在貫穿孔 110X 中安置電子元件 120。參照圖 20I，可使用囊封劑 160 對電子元件 120 進行囊封。參照圖 20J，可剝除黏合膜 190。參照圖 20K，可形成包括重新分配部絕緣層 141、重新分配部配線層 142、及重新分配部通孔 143 的重新分配部 140。接著，可形成包括重新分配部絕緣層 151、重新分配部配線層 152、及重新分配部通孔 153 的重新分配部 150。參照圖 20L，可形成連接至重新分配部 140 及 150 的保護層 170 以及連接至囊封劑 160 的覆蓋層 180。參照圖 20M，可在覆蓋層 180 的外表面中形成第三開口部 181，以便暴露出外配線層 162 的至少部分，且可形成安置於第三開口部 181 中的第二外部連接端子 185。此外，可形成保護層 170 的第一開口部 171 及安置於第一開口部 171 中的第一外部連接端子 175。在某些情形中，可僅形成安置於覆蓋層 180 的第三開口部 181 中的第二外部連接端子 185，且可在保護層 170 中僅形成第一開口部 171，並且若需要，則可藉由由購買電子元件封裝 100F 的客戶進行的單獨製程而形成安置於第一開口部 171 中的第一外部連接端子 175。

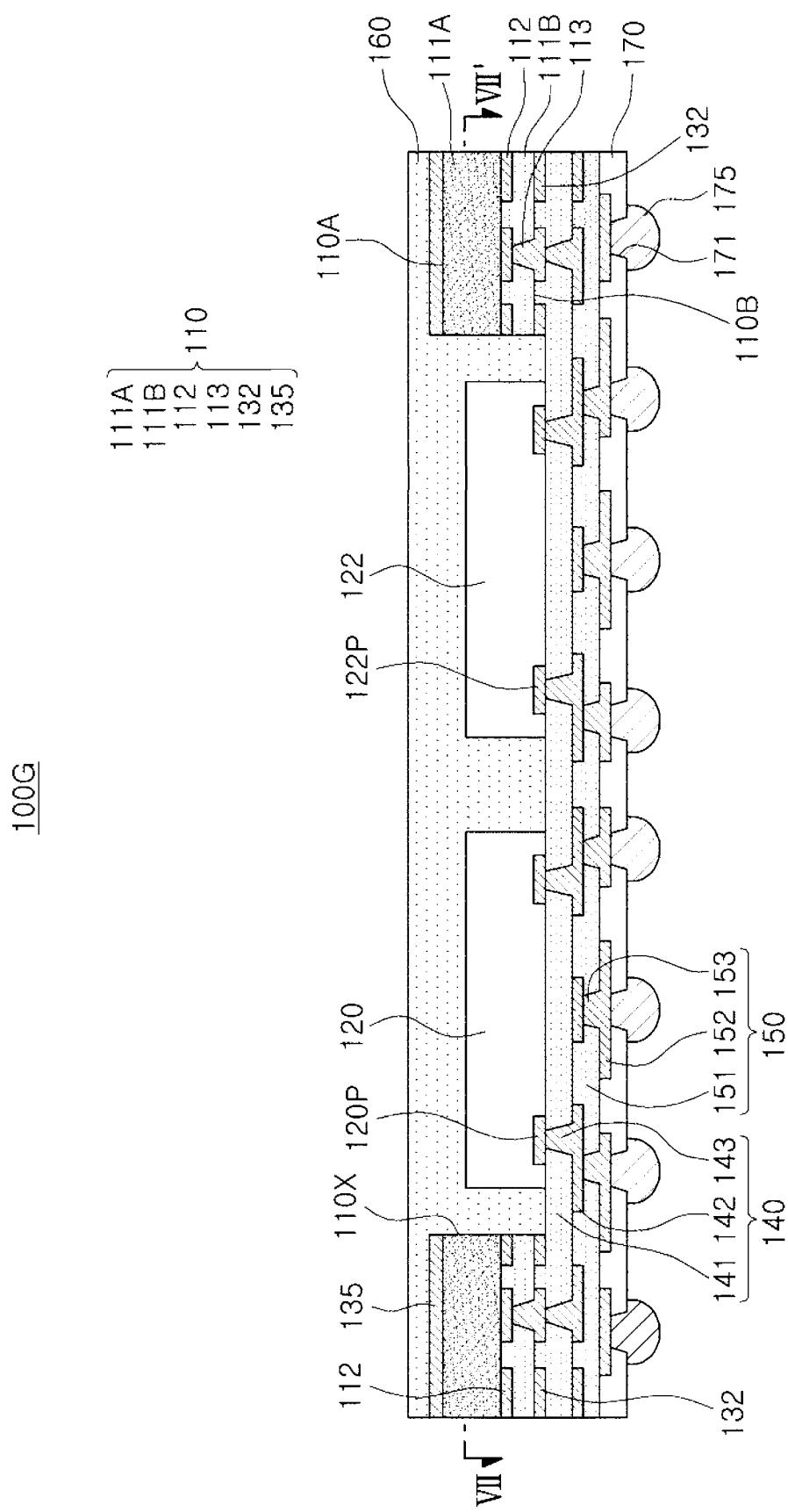

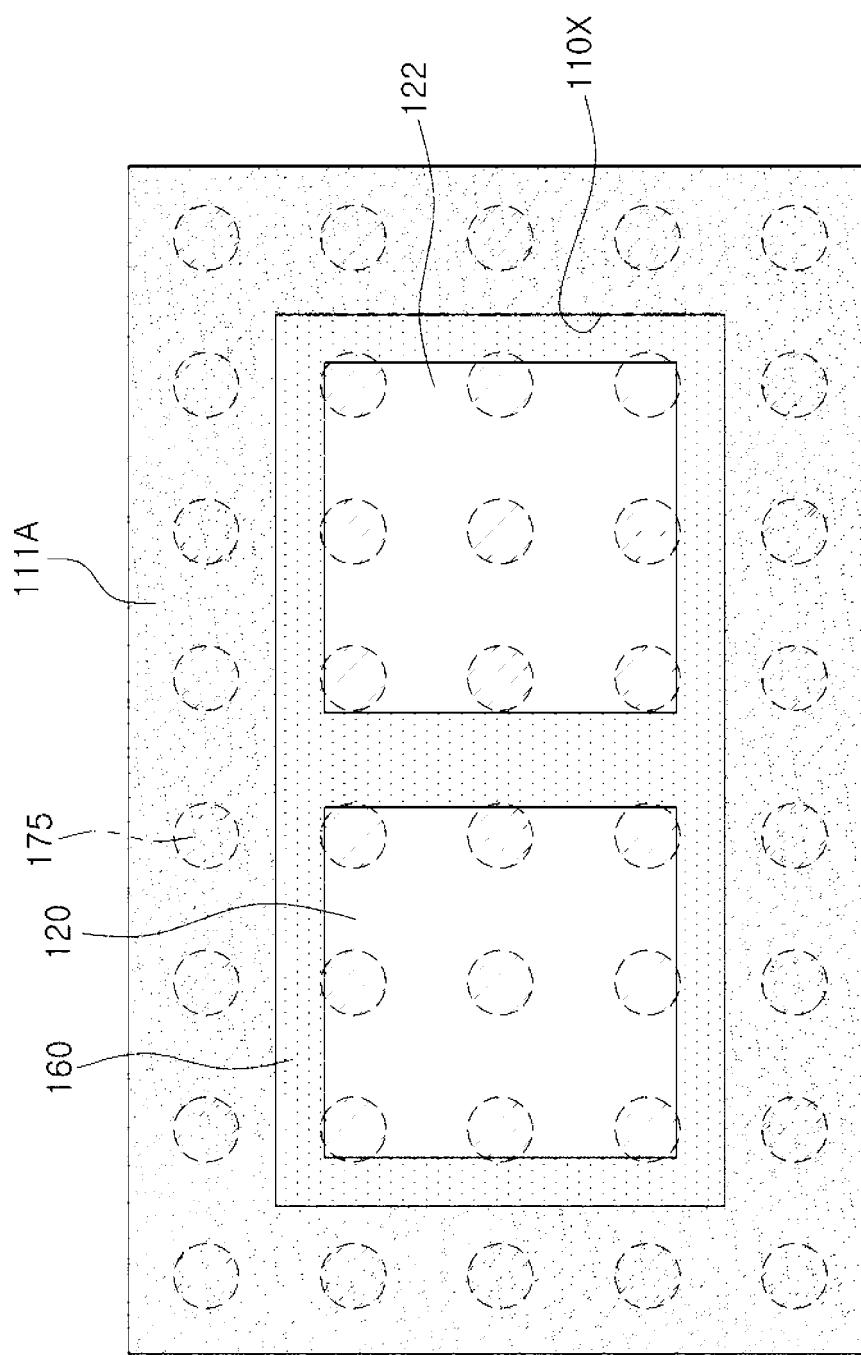

**【0144】** 圖 21 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0145】** 圖 22 是電子元件封裝沿圖 21 所示的線 VII-VII' 截取的示意性平面圖。

**【0146】** 參照圖 21 及圖 22，根據另一實例的電子元件封裝 100G

105-10-17

可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的多個電子元件 120 及 122、安置於框架 110 及所述多個電子元件 120 及 122 下的重新分配部 140 及 150、以及用於囊封所述多個電子元件 120 及 122 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、安置於第一絕緣層 111A 的上表面上的金屬層 135、安置於第二絕緣層 111B 的下表面上的第二配線層 132、及穿透過第二絕緣層 111B 的通孔 113。

**【0147】** 貫穿孔 110X 可依序穿透過金屬層 135、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 21 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於金屬層 135 的上表面下、或者位於與金屬層 135 的上表面相同的位階處或位於金屬層 135 的上表面之上，只要金屬層 135 以及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

105-10-17

**【0148】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100G 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0149】** 所述多個電子元件 120 及 122 可彼此相同或彼此不同。所述多個電子元件 120 及 122 可分別具有電性連接至框架 110、重新分配部 140 及 150 等的電極焊墊 120P 及 122P。電極焊墊 120P 及 122P 可分別藉由框架 110、重新分配部 140 及 150 等而重新分配。電子元件 120 及 122 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修改。舉例而言，如圖 21 及圖 22 中所示，電子元件 120 及 122 的數目可為兩個。然而，電子元件 120 及 122 的數目並非僅限於此，且可為二或更多個，例如為三個、四個等。若需要，則可在貫穿孔 110X 的內表面上進一步安置金屬層 135。

**【0150】** 由於除安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100G 的方法與製造電子元件封裝 100A 及 100D 的方法相同，因此將不再對其予以闡述。

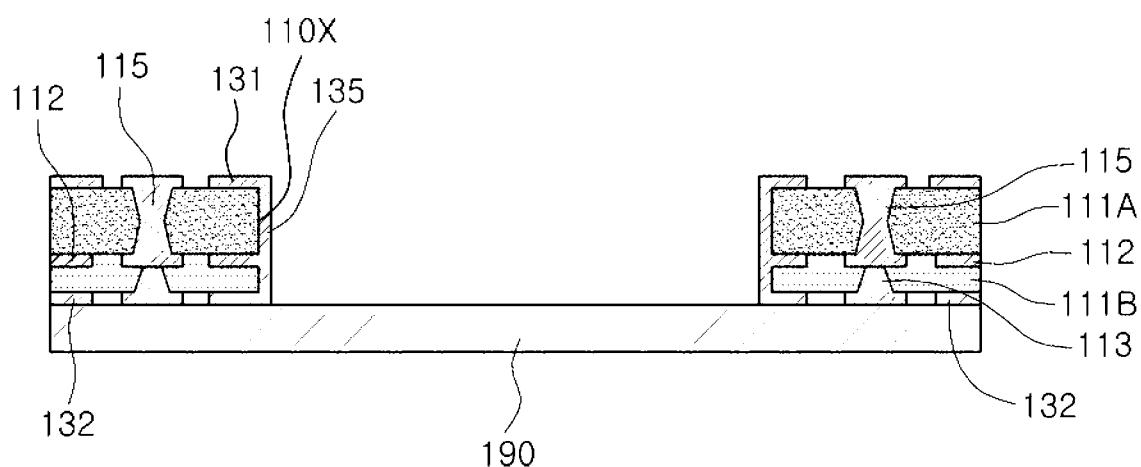

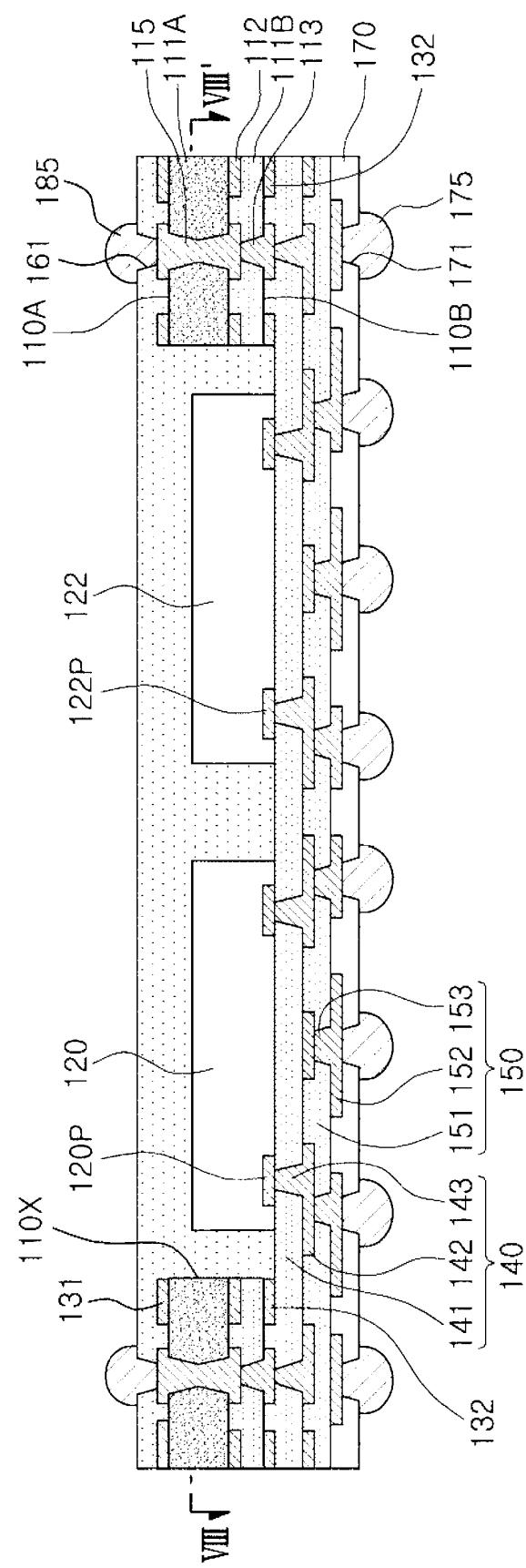

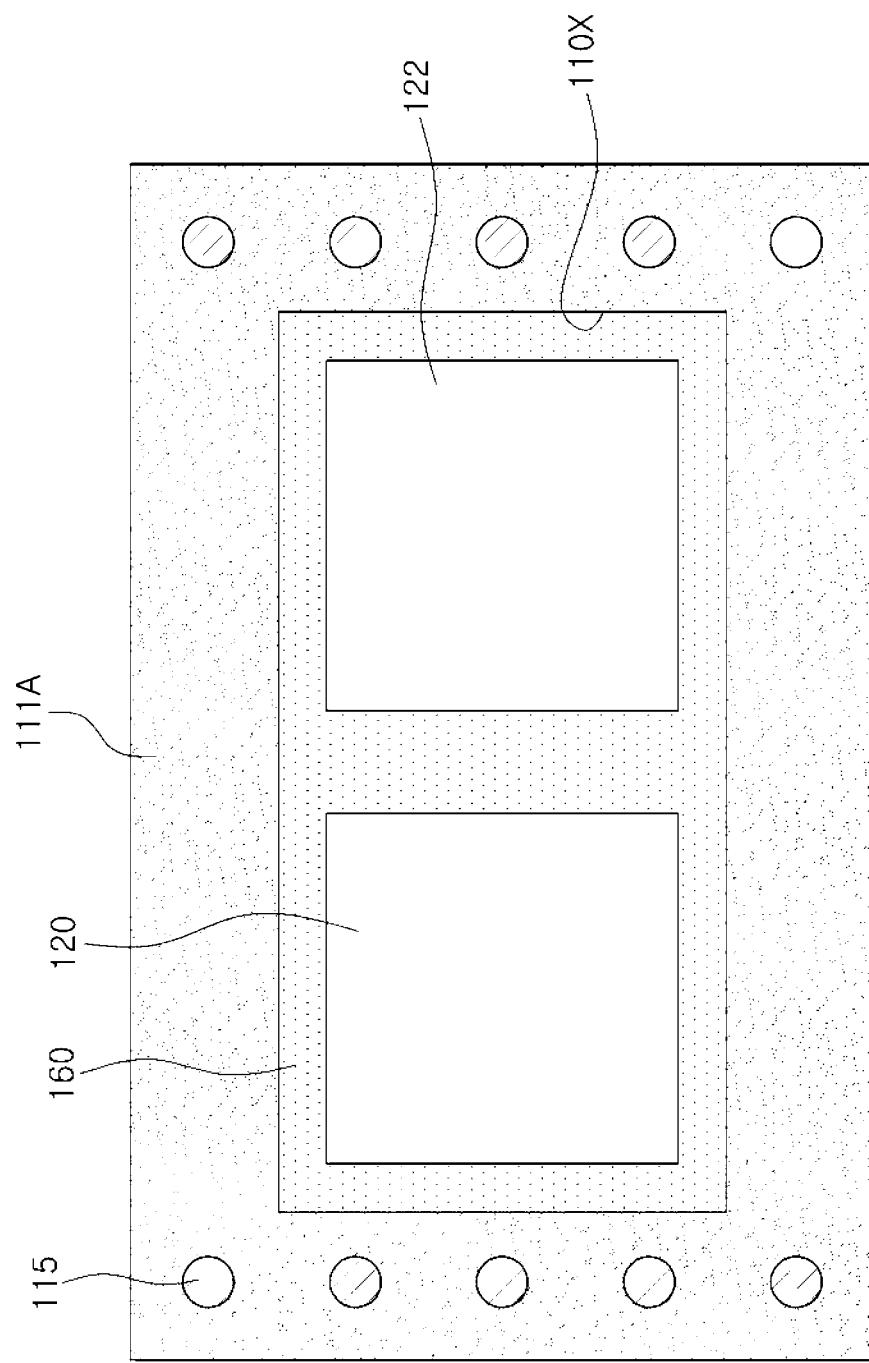

**【0151】** 圖 23 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0152】** 圖 24 是電子元件封裝沿圖 23 所示的線 VIII-VIII' 截取的示意性平面圖。

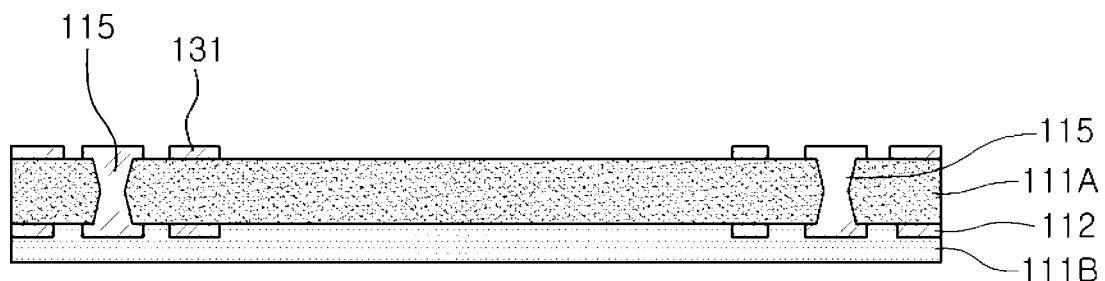

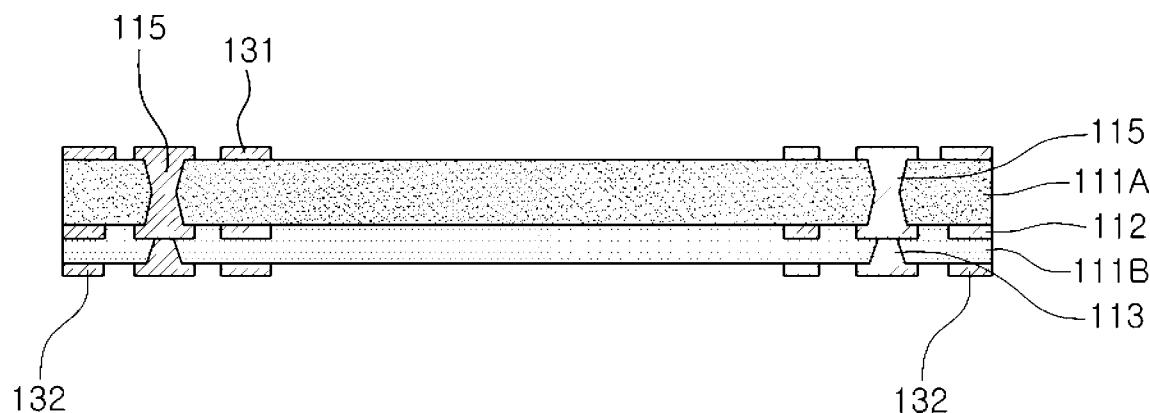

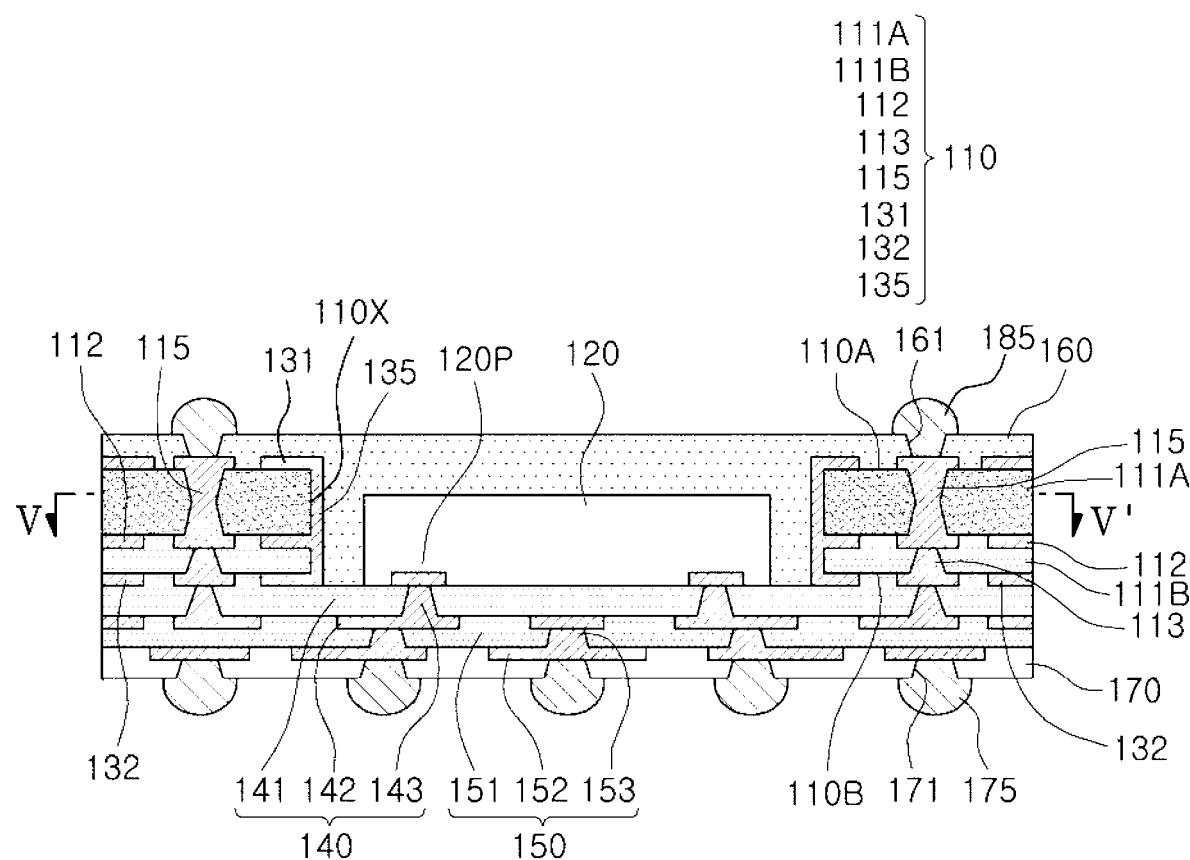

**【0153】** 參照圖 23 及圖 24，根據另一實例的電子元件封裝 100H 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔

105-10-17

110X 中的多個電子元件 120 及 122、安置於框架 110 以及所述多個電子元件 120 及 122 下的重新分配部 140 及 150、以及用於囊封所述多個電子元件 120 及 122 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0154】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 23 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

105-10-17

**【0155】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100H 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0156】** 另外，在其中安置有所述多個電子元件 120 及 122 的情形中，可應用分別安置於框架 110 的上表面 110A 及下表面 110B 上的第三配線層 131 及第二配線層 132，以及穿透過第一絕緣層 111A 的內部通孔 115。同樣地，囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分，且電子元件封裝 100H 可包括經由囊封劑 160 的外表面而暴露於外部的第二外部連接端子 185。若需要，則可在貫穿孔 110X 的內表面上進一步安置金屬層 135。

**【0157】** 由於除安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100H 的方法與製造電子元件封裝 100B 及 100E 的方法相同，因此將不再對其予以闡述。

**【0158】** 圖 25 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0159】** 圖 26 是電子元件封裝沿圖 25 所示的線 IX-IX' 截取的示意性平面圖。

**【0160】** 參照圖 25 及圖 26，根據另一實例的電子元件封裝 100I 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的多個電子元件 120 及 122、安置於框架 110 及所述多個電子元件 120 及 122 下的重新分配部 140 及 150、用於囊封所述多

105-10-17

個電子元件 120 及 122 的囊封劑 160、安置於囊封劑 160 上的外配線層 162、以及穿透過囊封劑 160 的外通孔 163。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0161】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 25 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 以及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

**【0162】** 在下文中，將更詳細地闡述包含於根據另一實例的電子

105-10-17

元件封裝 100I 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0163】** 另外，在其中安置有所述多個電子元件 120 及 122 的情形中，可應用安置於囊封劑 160 上的外配線層 162 及穿透過囊封劑 160 的外通孔 163。同樣地，電子元件封裝 100I 可更包括連接至囊封劑 160 的覆蓋層 180。覆蓋層 180 可具有第三開口部 181，第三開口部 181 暴露出安置於囊封劑 160 上的外配線層 162 的至少部分。此外，電子元件封裝 100I 可更包括經由覆蓋層 180 的上表面而暴露於外部的第二外部連接端子 185。若需要，則可在貫穿孔 110X 的內表面上進一步安置金屬層 135。

**【0164】** 由於除安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100I 的方法與製造電子元件封裝 100C 及 100F 的方法相同，因此將不再對其予以闡述。

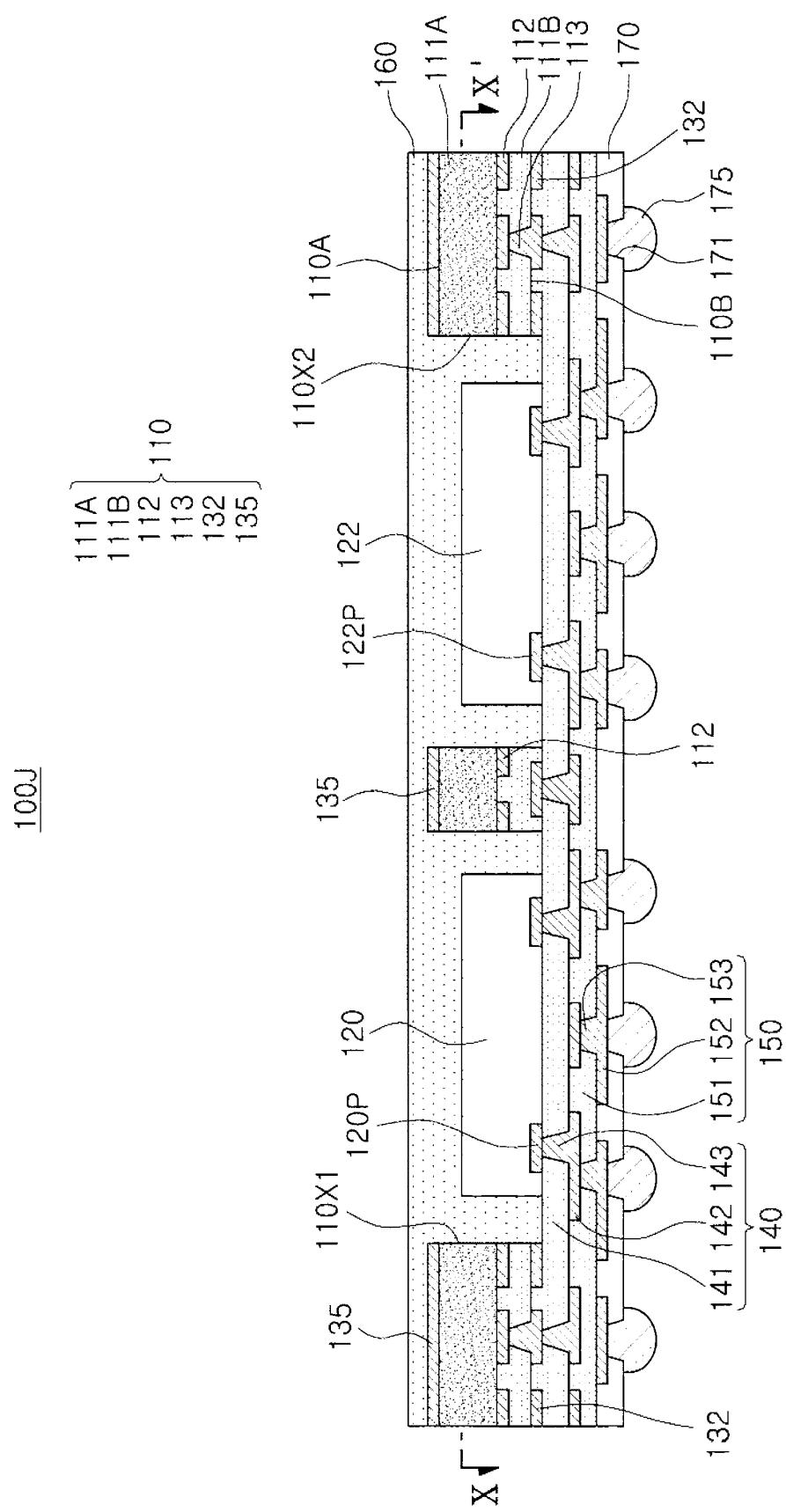

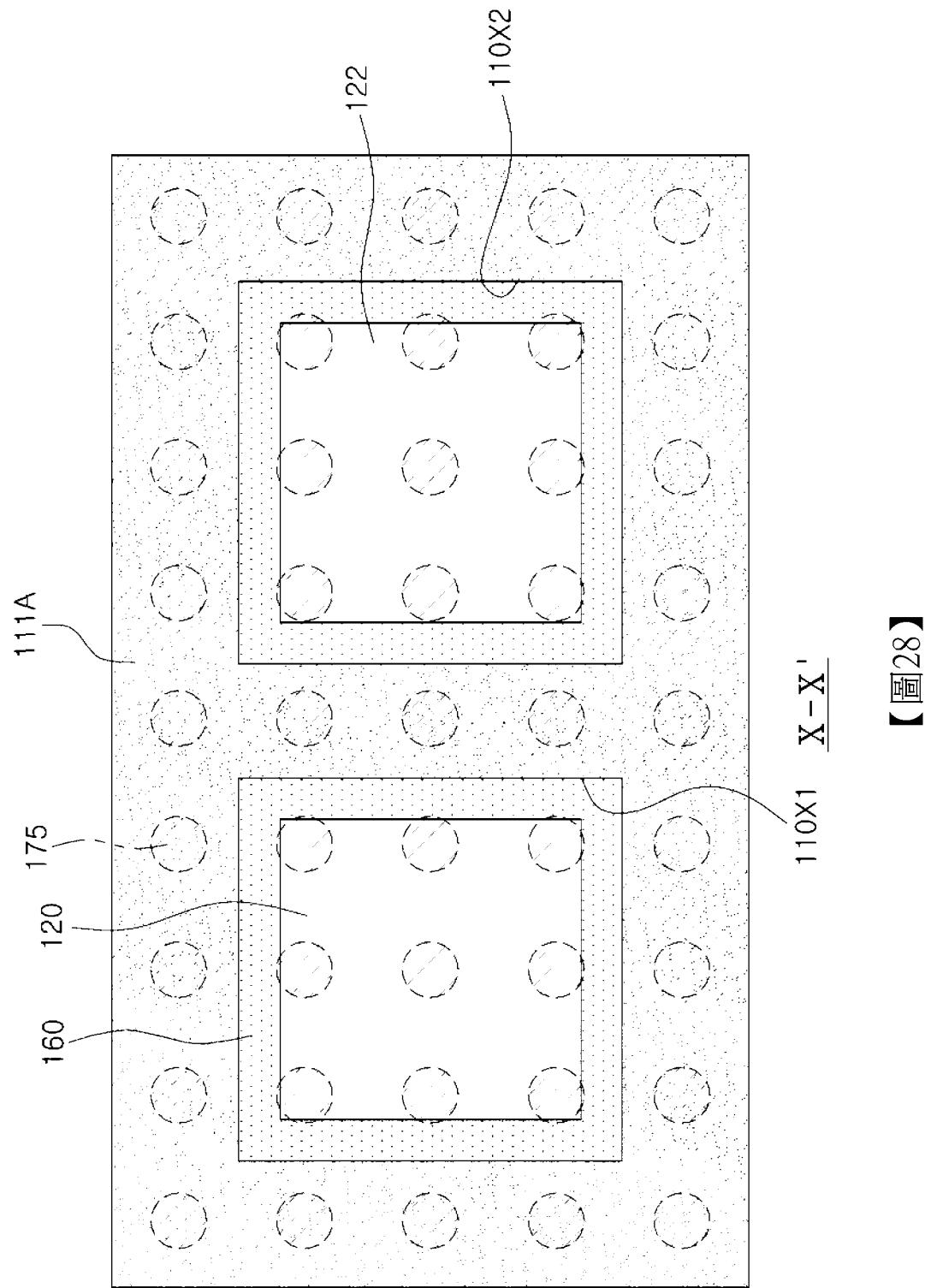

**【0165】** 圖 27 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0166】** 圖 28 是電子元件封裝沿圖 27 所示的線 X-X' 截取的示意性平面圖。

**【0167】** 參照圖 27 及圖 28，根據另一實例的電子元件封裝 100J 可包括具有多個貫穿孔 110X1 及 110X2 的框架 110；分別安置於框架 110 的所述多個貫穿孔 110X1 及 110X2 中的多個電子元件 120 及 122；安置於框架 110 及所述多個電子元件 120 及 122 下的重新分配部 140 及 150；以及用於囊封所述多個電子元件 120 及 122

105-10-17

的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、安置於第一絕緣層 111A 的上表面上的金屬層 135、安置於第二絕緣層 111B 的下表面上的第二配線層 132 及穿透過第二絕緣層 111B 的通孔 113。

**【0168】** 所述多個貫穿孔 110X1 及 110X2 中的每一者可依序穿透過金屬層 135、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 27 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於金屬層 135 的上表面下、或者位於與金屬層 135 的上表面相同的位階處或位於金屬層 135 的上表面之上，只要金屬層 135 以及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

**【0169】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100J 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

105-10-17

**【0170】**所述多個貫穿孔 110X1 及 110X2 的面積、形狀等可彼此形同或彼此不同，且分別安置於貫穿孔 110X1 及 110X2 中的電子元件 120 及 122 亦可彼此相同或彼此不同。貫穿孔 110X1 及 110X2 的數目、間距、配置形式等以及分別安置於貫穿孔 110X1 及 110X2 中的電子元件 120 及 122 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修改。舉例而言，如圖 27 及圖 28 中所示，貫穿孔 110X1 及 110X2 的數目可為兩個。然而，貫穿孔 110X1 及 110X2 的數目並非僅限於此，且可為二或多個，例如三個、四個等。此外，如圖 27 及圖 28 中所示，分別安置於貫穿孔 110X1 及 110X2 中的電子元件 120 及 122 的數目可為一個。然而，分別安置於貫穿孔 110X1 及 110X2 中的電子元件 120 及 122 的數目並非僅限於此，且可為一或多個，例如兩個、三個等。若需要，則可在所述多個貫穿孔 110X1 及 110X2 的內表面上進一步安置金屬層 135。

**【0171】**由於除形成所述多個貫穿孔 110X1 及 110X2 並在所述多個貫穿孔 110X1 及 110X2 中分別安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100J 的方法與製造電子元件封裝 100A 及 100D 的方法相同，因此將不再對其予以闡述。

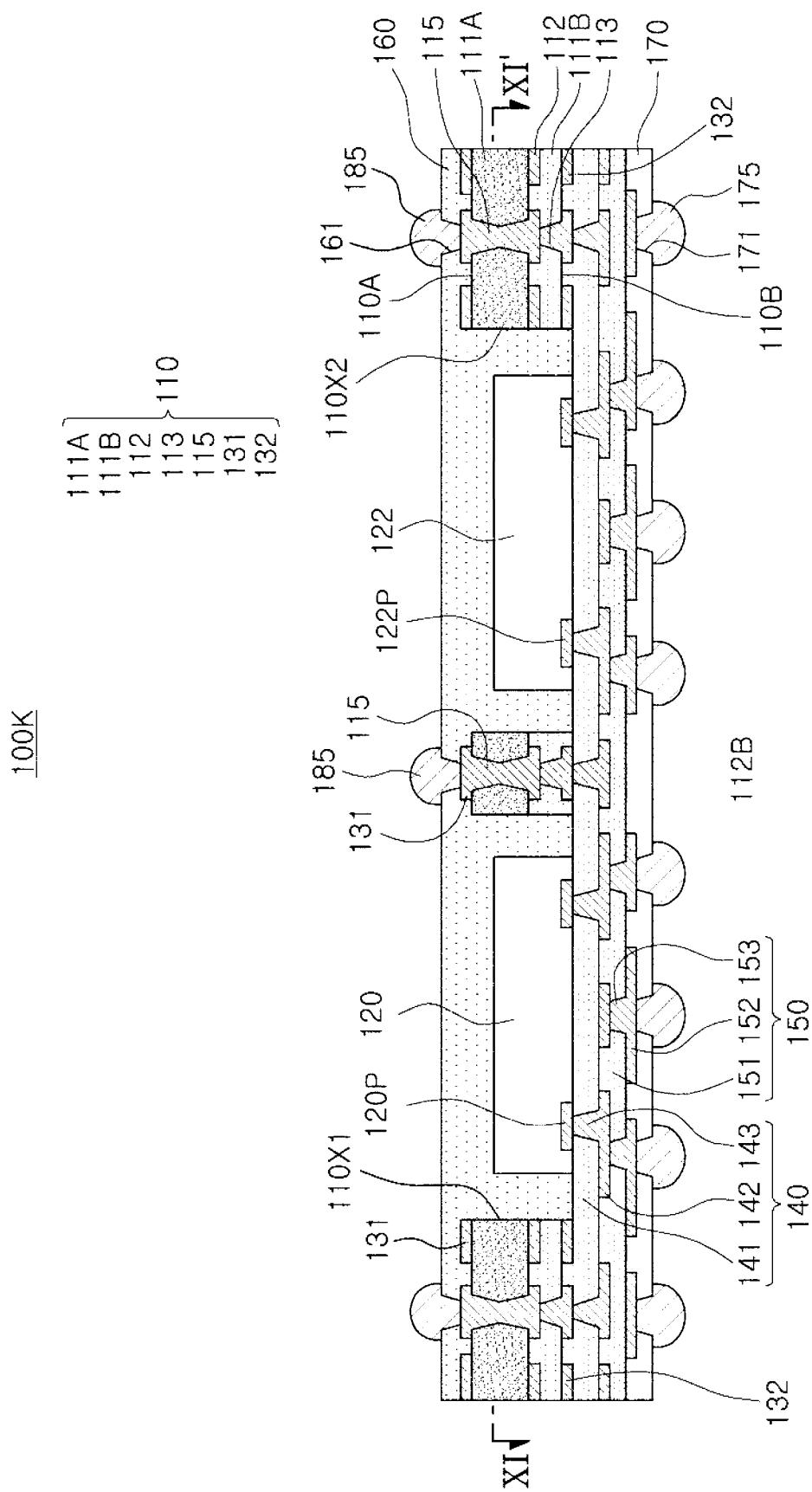

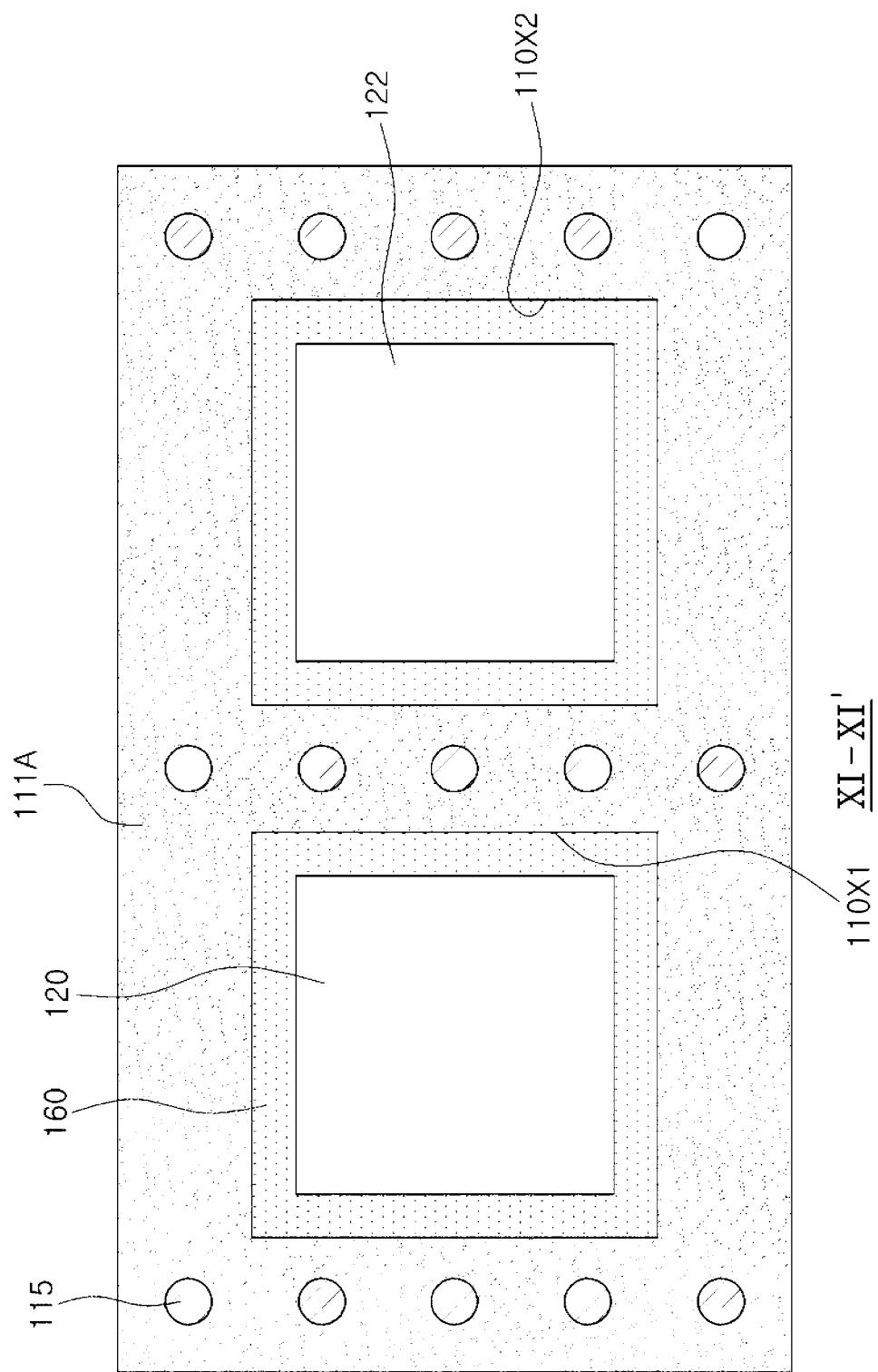

**【0172】**圖 29 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0173】**圖 30 是電子元件封裝沿圖 29 所示的線 XI-XI' 截取的示意性平面圖。

105-10-17

**【0174】** 參照圖 29 及圖 30，根據另一實例的電子元件封裝 100K 可包括具有多個貫穿孔 110X1 及 110X2 的框架 110、分別安置於框架 110 的所述多個貫穿孔 110X1 及 110X2 中的多個電子元件 120 及 122、安置於框架 110 及所述多個電子元件 120 及 122 下的重新分配部 140 及 150、以及用於囊封所述多個電子元件 120 及 122 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0175】** 所述多個貫穿孔 110X1 及 110X2 中的每一者可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 29 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表

105-10-17

面之上，只要第三配線層 131 以及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

**【0176】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100K 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0177】** 另外，在其中形成所述多個貫穿孔 110X1 及 110X2 並在所述多個貫穿孔 110X1 及 110X2 中分別安置電子元件 120 及 122 的情形中，可應用分別安置於框架 110 的上表面 110A 及下表面 110B 上的第三配線層 131 及第二配線層 132、以及穿透過第一絕緣層 111A 的內部通孔 115。第三配線層 131 及第二配線層 132 以及內部通孔 115 亦可形成於框架 110 的第一絕緣層 111A 的劃分所述多個貫穿孔 110X1 及 110X2 的中心部分中。同樣地，囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分，且電子元件封裝 100K 可包括經由囊封劑 160 的外表面而暴露於外部的第二外部連接端子 185。第二開口部 161 及第二外部連接端子 185 亦可形成於框架 110 的第一絕緣層 111A 的劃分所述多個貫穿孔 110X1 及 110X2 的中心部分中。若需要，則可在所述多個貫穿孔 110X1 及 110X1 的內表面上進一步安置金屬層 135。

**【0178】** 由於除形成所述多個貫穿孔 110X1 及 110X2 並在所述多

105-10-17

個貫穿孔 110X1 及 110X2 中分別安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100K 的方法與製造電子元件封裝 100B 及 100E 的方法相同，因此將不再對其予以闡述。

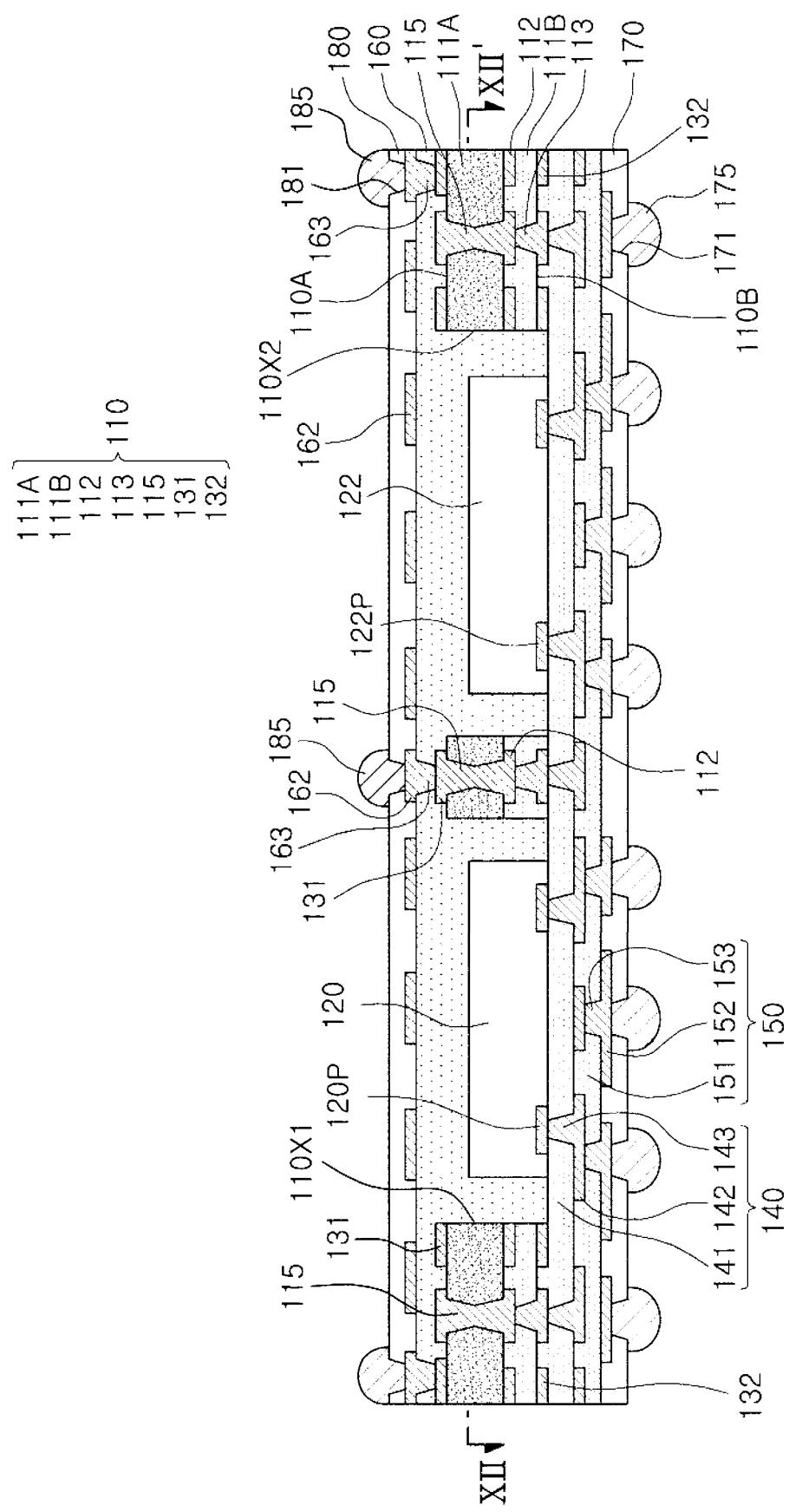

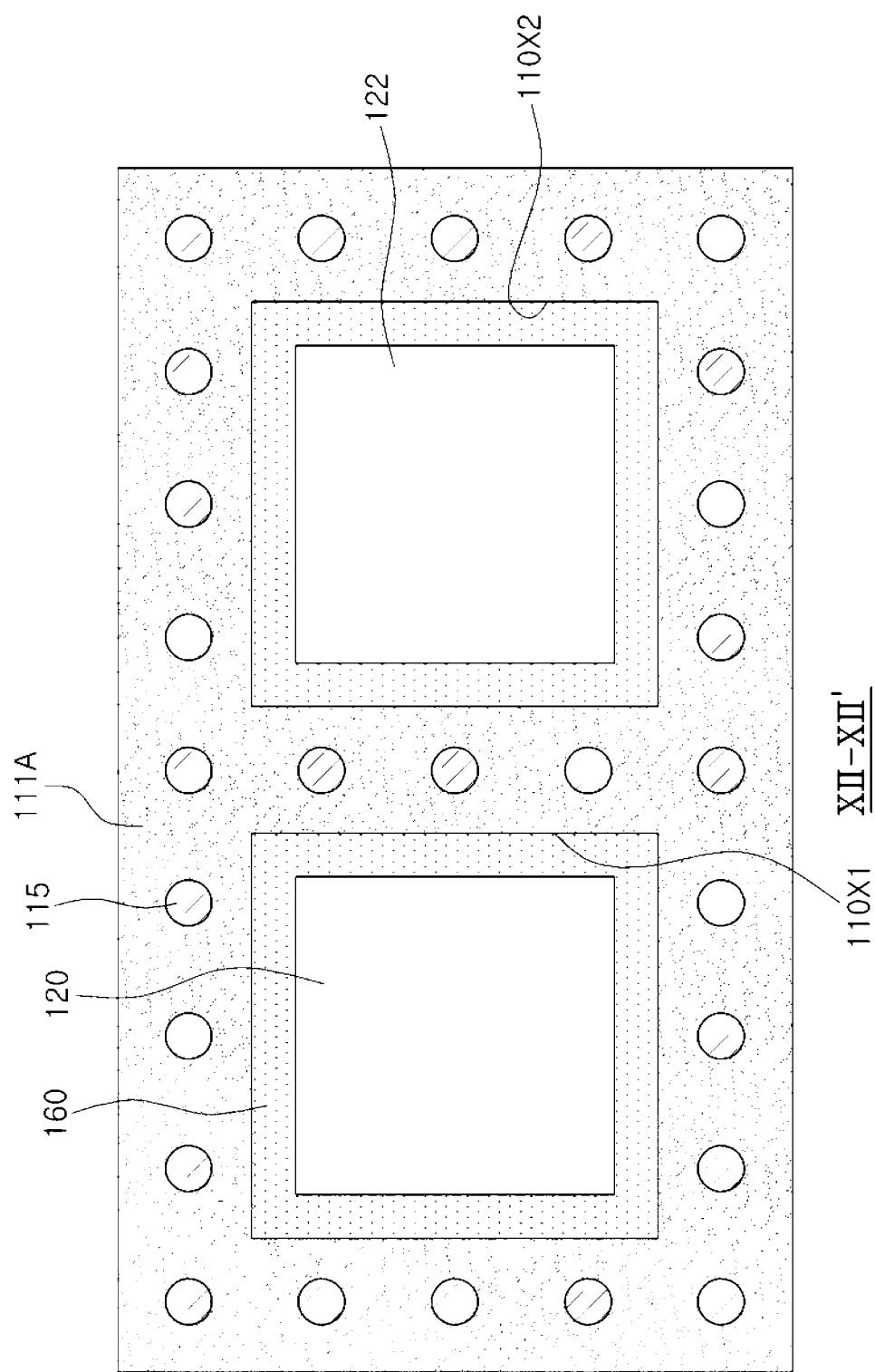

**【0179】** 圖 31 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0180】** 圖 32 是電子元件封裝沿圖 31 所示的線 XII-XII' 截取的示意性平面圖。

**【0181】** 參照圖 31 及圖 32，根據另一實例的電子元件封裝 100L 可包括具有多個貫穿孔 110X1 及 110X2 的框架 110、分別安置於框架 110 的所述多個貫穿孔 110X1 及 110X2 中的多個電子元件 120 及 122、安置於框架 110 及所述多個電子元件 120 及 122 下的重新分配部 140 及 150、用於囊封所述多個電子元件 120 及 122 的囊封劑 160、安置於囊封劑 160 上的外配線層 162、以及穿透過囊封劑 160 的外通孔 163。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0182】** 所述多個貫穿孔 110X1 及 110X2 中的每一者可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B

105-10-17

中的至少一者可位於所述多個電子元件 120 及 122 中的一者的上表面與下表面之間的位階處。如圖 31 中所示，所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 122 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 以及所述多個電子元件 120 及 122 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 122 的厚度不同時，所述多個電子元件 120 及 122 的上表面可位於不同的位階處。

**【0183】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100L 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0184】** 另外，在其中形成所述多個貫穿孔 110X1 及 110X2 並在所述多個貫穿孔 110X1 及 110X2 中分別安置所述多個電子元件 120 及 122 的情形中，可應用安置於囊封劑 160 上的外配線層 162 及穿透過囊封劑 160 的外通孔 163。外配線層 162 及外通孔 163 亦可形成於框架 110 的第一絕緣層 111A 的劃分所述多個貫穿孔 110X1 及 110X2 的中心部分中。同樣地，電子元件封裝 100L 可更包括連接至囊封劑 160 的覆蓋層 180。覆蓋層 180 可具有第三開口

105-10-17

部 181，第三開口部 181 暴露出安置於囊封劑 160 上的外配線層 162 的至少部分。此外，電子元件封裝 100L 可更包括經由覆蓋層 180 的上表面而暴露於外部的第二外部連接端子 185。第三開口部 181 及第二外部連接端子 185 亦可形成於框架 110 的第一絕緣層 111A 的劃分所述多個貫穿孔 110X1 及 110X2 的中心部分中。若需要，則可在所述多個貫穿孔 110X1 及 110X2 的內表面上進一步安置金屬層 135。

**【0185】** 由於除形成所述多個貫穿孔 110X1 及 110X2 並在所述多個貫穿孔 110X1 及 110X2 中分別安置所述多個電子元件 120 及 122 以外，根據另一實例的製造電子元件封裝 100L 的方法與製造電子元件封裝 100C 及 100F 的方法相同，因此將不再對其予以闡述。

**【0186】** 圖 33 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0187】** 圖 34 是電子元件封裝沿圖 33 所示的線 XIII-XIII' 截取的示意性平面圖。

**【0188】** 參照圖 33 及圖 34，根據另一實例的電子元件封裝 100M 可包括具有貫穿孔 110X 的框架 110、分別安置於框架 110 的貫穿孔 110X 中的多個電子元件 120 及 124、安置於框架 110 及所述多個電子元件 120 及 124 下的重新分配部 140 及 150、以及用於囊封所述多個電子元件 120 及 124 的囊封劑 160。所述多個電子元件 120 及 124 中的至少一者可為積體電路，且所述多個電子元件 120 及 124 中的其他電子元件可為被動元件。框架 110 可包括第一絕

105-10-17

緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0189】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於所述多個電子元件 120 及 124 中的一者的上表面與下表面之間的位階處。如圖 33 中所示，所述多個電子元件 120 及 124 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。所述多個電子元件 120 及 124 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 以及所述多個電子元件 120 及 124 皆被囊封劑 160 覆蓋即可。當所述多個電子元件 120 及 124 的厚度不同時，所述多個電子元件 120 及 124 的上表面可位於不同的位階處。

**【0190】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100M 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

105-10-17

**【0191】** 電子元件 120 指示其中將數百至數百萬個或更多個組件整合於一起的晶片，且可為例如：應用處理器晶片，例如中央處理器（例如，中央處理單元）、圖形處理器（例如，圖形處理單元）、數位訊號處理器、密碼學處理器、微處理器、微控制器等，但並非僅限於此。電子元件 124 可為例如電感器、電容器、電阻器等，但並非僅限於此。電子元件 120 可經由電極焊墊 120P 而電性連接至框架 110、重新分配部 140 及 150 等。電子元件 124 可經由例如外部電極等電極焊墊（圖中未示出）而電性連接至框架 110、重新分配部 140 及 150 等。

**【0192】** 電子元件 120 及 124 的數目、間距、配置形式等並無特別限制，且可由熟習此項技術者依設計特定細節充分地進行修改。舉例而言，電子元件 120 及 124 可安置於貫穿孔 110X 的中心附近及貫穿孔 110X 的內壁附近，但並非僅限於此。此外，電子元件 120 的數目可為一個且電子元件 124 的數目可為複數個。然而，電子元件 120 及 124 的數目並非僅限於此。舉例而言，電子元件 120 的數目可為複數個且電子元件 124 的數目可為一個，電子元件 120 及 124 二者的數目均可為一個，或者電子元件 120 及 124 二者的數目均可為複數個。若需要，則亦可應用金屬層 135、保護層 170、覆蓋層 180、第二開口部 161、第一開口部 171 及第三開口部 181、第一外部連接端子 175 及第二外部連接端子 185、外配線層 162、外通孔 163 等。

**【0193】** 由於除將電子元件 120 及 124 彼此安置於一起以外，根

105-10-17

據另一實例的製造電子元件封裝 100M 的方法與製造電子元件封裝 100A 至 100F 的方法相同，因此將不再對其予以闡述。

**【0194】** 圖 35 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0195】** 參照圖 35，根據另一實例的電子元件封裝 100N 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、以及穿透過第二絕緣層 111B 的通孔 113。第二絕緣層 111B 可安置於第一絕緣層 111A 之上。框架 110 可包括安置於第二絕緣層 111B 的上表面 110A 上的第三配線層 131、及安置於框架 110 的下表面 110B 上的第二配線層 132。

**【0196】** 貫穿孔 110X 可依序穿透過第三配線層 131、第二絕緣層 111B、第一配線層 112、第一絕緣層 111A 及第二配線層 132。第一配線層 112 及第一絕緣層 111A 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 35 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第

105-10-17

三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0197】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100N 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0198】** 除第二絕緣層 111B 安置於第一絕緣層 111A 之上以外，根據另一實例的電子元件封裝 100N 相似於上述電子元件封裝 100A 至 100M。舉例而言，若需要，則亦可應用金屬層 135、保護層 170、覆蓋層 180、第二開口部 161、第一開口部 171 及第三開口部 181、第一外部連接端子 175 及第二外部連接端子 185、外配線層 162、外通孔 163 等。

**【0199】** 由於除將第二絕緣層 111B 安置於第一絕緣層 111A 之上以外，根據另一實例的製造電子元件封裝 100N 的方法與製造電子元件封裝 100A 至 100F 的方法相同，因此將不再對其予以闡述。

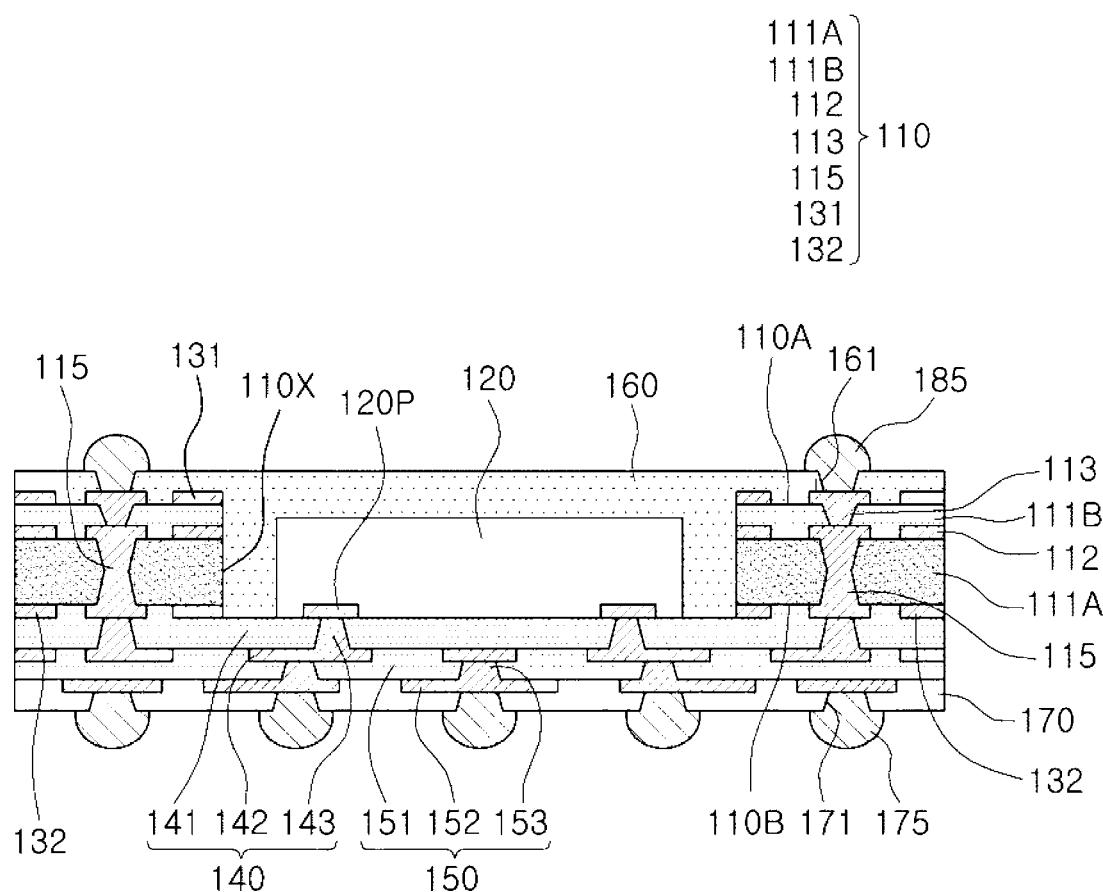

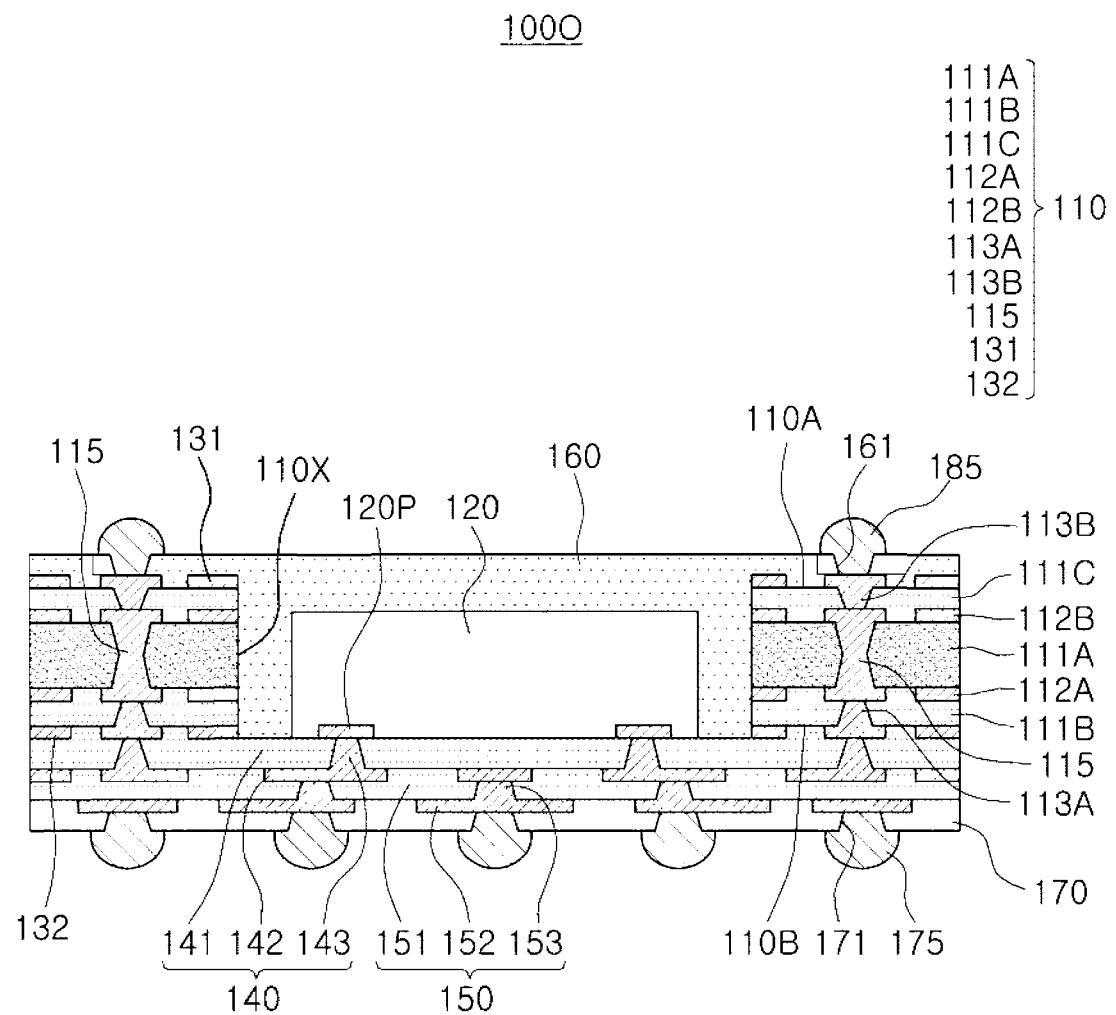

**【0200】** 圖 36 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0201】** 參照圖 36，根據另一實例的電子元件封裝 100O 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、第三絕緣層 111C、

105-10-17

分別安置於第一絕緣層 111A 與第二絕緣層 111B 之間及第一絕緣層 111A 與第三絕緣層 111C 之間的多個第一配線層 112A 及 112B、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的第一通孔 113A、以及穿透過第三絕緣層 111C 的第二通孔 113B。框架 110 可包括安置於第三絕緣層 111C 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0202】** 貫穿孔 110X 可依序穿透過第三配線層 131、第三絕緣層 111C、第一配線層 112B、第一絕緣層 111A、第一配線層 112A、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 36 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0203】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 1000 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0204】 第一絕緣層 111A、第二絕緣層 111B、及第三絕緣層 111C**

可以第二絕緣層 111B、第一絕緣層 111A 及第三絕緣層 111C 的順序自下向上堆疊於一起。第二絕緣層 111B 及第三絕緣層 111C 可由相同的材料形成，且可具有彼此對應的厚度。第二絕緣層 111B 及第三絕緣層 111C 具有彼此對應的厚度的含義為第二絕緣層 111B 的厚度與第三絕緣層 111C 的厚度實質上彼此相同。亦即，此是一包含其中在第二絕緣層 111B 與第三絕緣層 111C 之間存在就翹曲方面而言可忽略的厚度差的情形、以及其中第二絕緣層 111B 的厚度與第三絕緣層 111C 的厚度彼此完全相同的情形的概念。

**【0205】** 依對應層的設計而定，第一配線層 112A 及 112B 可執行各種功能。舉例而言，第一配線層 112A 及 112B 可充當接地(GND)圖案、功率(PWR)圖案、訊號(S)圖案等而作為重新分配圖案。此外，第一配線層 112A 及 112B 可充當通孔焊墊等而作為焊墊圖案。如上所述，由於第一配線層 112A 及 112B 可執行重新分配功能，因此第一配線層 112A 及 112B 可分擔重新分配部 140 及 150 的重新分配功能。若需要，則亦可應用金屬層 135、保護層 170、覆蓋層 180、第二開口部 161、第一開口部 171 及第三開口部 181、第一外部連接端子 175 及第二外部連接端子 185、外配線層 162、外通孔 163 等。

**【0206】** 由於除將第三絕緣層 111C 形成於第一絕緣層 111A 之上且將第一配線層 112B 等形成於第一絕緣層 111A 與第三絕緣層

105-10-17

111C 之間以外，根據另一實例的製造電子元件封裝 100O 的方法與製造電子元件封裝 100A 至 100F 的方法相同，因此將不再對其予以闡述。

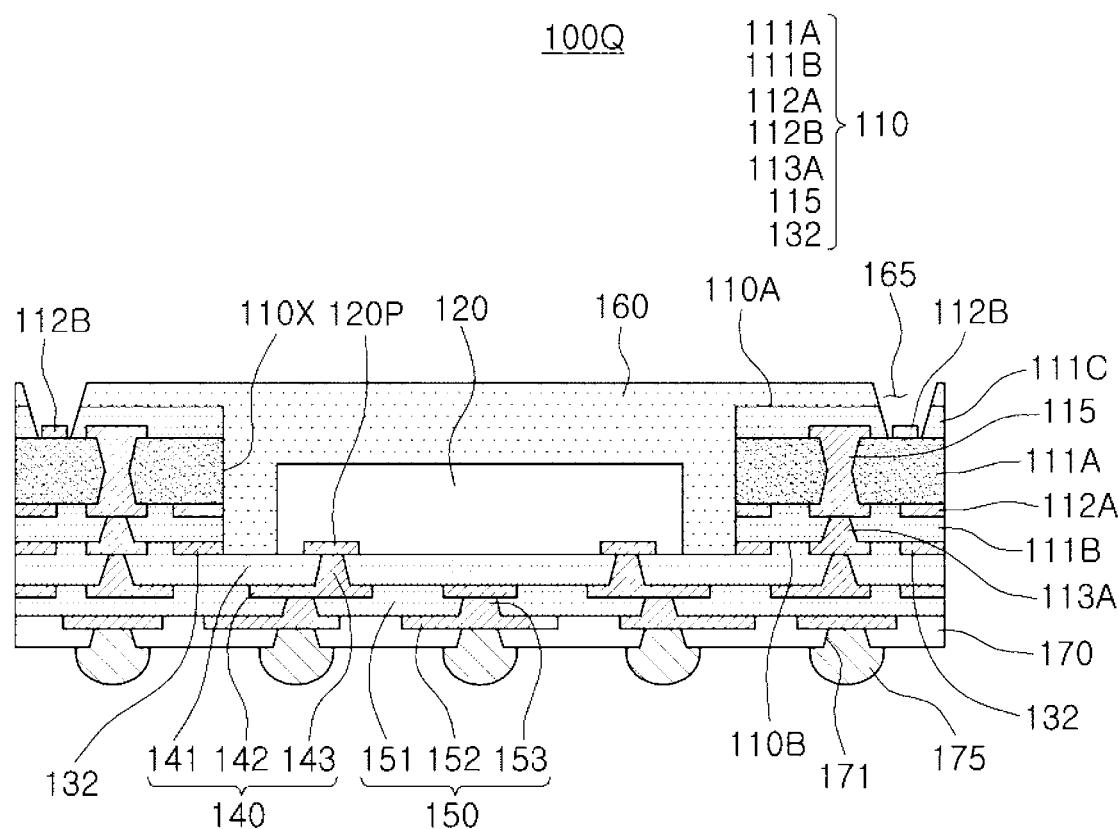

**【0207】** 圖 37 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0208】** 參照圖 37，根據另一實例的電子元件封裝 100P 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、多個第二絕緣層 111B1 及 111B2、分別安置於第一絕緣層 111A 與第二絕緣層 111B2 之間或所述多個第二絕緣層 111B1 及 111B2 之間的多個第一配線層 112A1 及 112A2、穿透過第一絕緣層 111A 的內部通孔 115、以及分別穿透過第二絕緣層 111B1 及 111B2 的多個通孔 113A1 及 113A2。框架 110 可包括安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B2 的下表面 110B 上的第二配線層 132。

**【0209】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112A1、第二絕緣層 111B1、第一配線層 112A2、第二絕緣層 111B2 及第二配線層 132。所述多個第一配線層 112A1 及 112A2 以及所述多個第二絕緣層 111B1 及 111B2 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 37 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於

框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0210】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100P 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0211】** 在其中第二絕緣層 111B1 及 111B2 的數目為複數個的情形中，亦可在所述多個第二絕緣層 111B1 及 111B2 之間安置第一配線層 112A2。如此一來，第一配線層可進一步代替重新分配部 140 及 150 的重新分配功能。第二絕緣層 111B1 及 111B2 的數目及第一配線層 112A1 及 112A2 的數目並無特別限制，且依設計特定細節而定可為複數個。若需要，則亦可應用金屬層 135、保護層 170、覆蓋層 180、第二開口部 161、第一開口部 171 及第三開口部 181、第一外部連接端子 175 及第二外部連接端子 185、外配線層 162、外通孔 163 等。

**【0212】** 由於除第二絕緣層 111B1 及 111B2 的數目為複數個以外，根據另一實例的製造電子元件封裝 100P 的方法與製造電子元件封裝 100A 至 100F 的方法相同，因此將不再對其予以闡述。

105-10-17

**【0213】** 圖 38 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0214】** 參照圖 38，根據另一實例的電子元件封裝 100Q 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、第三絕緣層 111C、分別安置於第一絕緣層 111A 與第二絕緣層 111B 之間及第一絕緣層 111A 與第三絕緣層 111C 之間的多個第一配線層 112A 及 112B、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的第一通孔 113A、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。此處，囊封劑 160 及第三絕緣層 111C 可具有第四開口部 165，且安置於第一絕緣層 111A 與第三絕緣層 111C 之間的第一配線層 112B 的部分可經由第四開口部 165 而暴露於外部。

**【0215】** 貫穿孔 110X 可依序穿透過第三絕緣層 111C、第一配線層 112B、第一絕緣層 111A、第一配線層 112A、第二絕緣層 111B、及第二配線層 132。所述多個第一配線層 112A 及 112B 以及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 38 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分

105-10-17

配部 140 及 150 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上，只要第三絕緣層 111C 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0216】** 在下文中，將更詳細地闡述包含於根據另一實例的電子元件封裝 100Q 中的相應元件，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0217】** 第一配線層 112B 可安置於第一絕緣層 111A 與第三絕緣層 111C 之間。舉例而言，第一配線層 112B 可安置於第一絕緣層 111A 的除經由第四開口部 165 而暴露於外部的某些圖案以外的上表面上，且可嵌置於第三絕緣層 111C 中。亦即，第一配線層 112B 可安置於框架 110 中。此處，第一配線層 112B 安置於框架 110 中的含義為第一配線層 112B 安置於框架 110 的上表面 110A 與下表面 110B 之間。依對應層的設計而定，第一配線層 112B 可執行各種功能。舉例而言，第一配線層 112B 可充當接地（GND）圖案、功率（PWR）圖案、訊號（S）圖案等而作為重新分配圖案。此處，訊號（S）圖案可包括除接地（GND）圖案、功率（PWR）圖案等以外的各種訊號，例如資料訊號等。此外，第一配線層 112B 可充當通孔焊墊、內部通孔焊墊等而作為焊墊圖案。如上所述，由於第一配線層 112B 可執行重新分配功能，因此第一配線層 112B 可分擔重新分配部 140 及 150 的重新分配功能。例如銅（Cu）、鋁（Al）、銀（Ag）、錫（Sn）、金（Au）、鎳（Ni）、鉛（Pb）、或其合金等傳導性材料可用作第一配線層 112B 的材料。第一配線層

105-10-17

112B 的厚度亦無特別限制，但可為例如約 10 微米至 50 微米左右。第一配線層 112B 的經由第四開口部 165 而暴露於外部的圖案可為用於連接至安置於電子元件封裝 100Q 上的另一電子元件、另一電子元件封裝等的配線結合焊墊。第二絕緣層 111B 與第三絕緣層 111C 可由相同的材料形成，且可具有彼此對應的厚度。第二絕緣層 111B 與第三絕緣層 111C 具有彼此對應的厚度的含義為第二絕緣層 111B 的厚度與第三絕緣層 111C 的厚度彼此相同。亦即，此是一包含其中在第二絕緣層 111B 與第三絕緣層 111C 之間存在就翹曲方面而言可忽略的厚度差的情形、以及其中第二絕緣層 111B 的厚度與第三絕緣層 111C 的厚度彼此完全相同的情形的概念。若需要，則亦可應用金屬層 135、保護層 170、第一開口部 171、第一外部連接端子 175 等。

**【0218】** 由於除將第三絕緣層 111C 形成於第一絕緣層 111A 之上並形成第四開口部 165 以外，根據另一實例的製造電子元件封裝 100Q 的方法與製造電子元件封裝 100B 及 100E 的方法相同，因此將不再對其予以闡述。

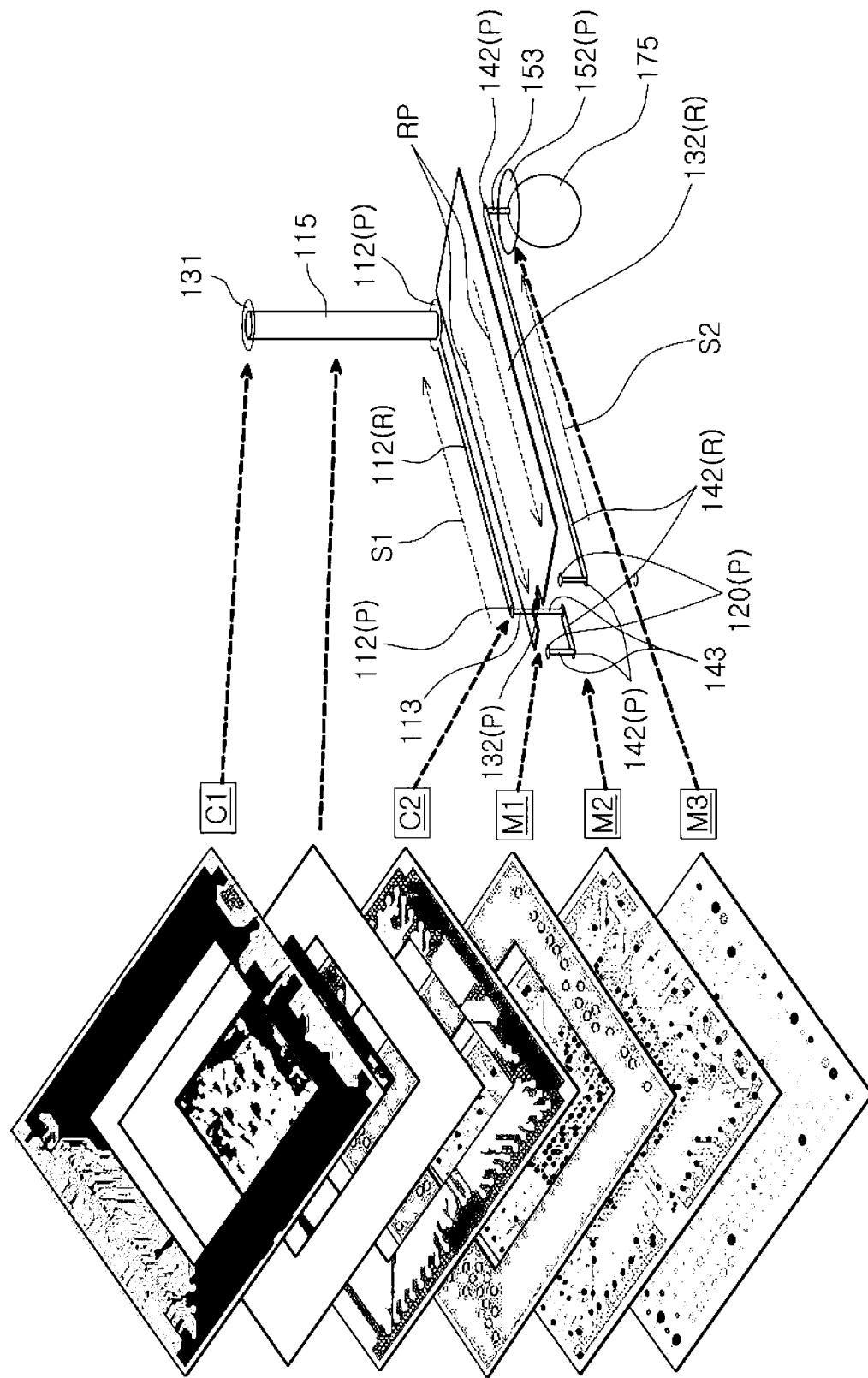

**【0219】** 圖 39 是示意性地說明電子元件封裝的信號傳遞的實例的圖。

**【0220】** 將闡述其中使用上述電子元件封裝 100B 作為電子元件封裝的情形，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0221】** 在實例中，第二配線層 132 (M1) 的絕大部分可由例如

105-10-17

接地平面等接地（GND）圖案形成。由於可在安置電子元件 120 之前形成的第二配線層 132（M1）的絕大部分是由接地（GND）圖案形成，因此配線層 142 及 152（M2 及 M3）的接地（GND）圖案可顯著地減少。因而，可使用僅兩個配線層 M2 及 M3 而充分地設計另一所需重新分配圖案 R 及/或焊墊圖案 P。如此一來，在安置電子元件 120 之後形成所述重新分配部的製程的數目可顯著地減少。此處，第二配線層的絕大部分是由接地（GND）圖案形成的含義為接地（GND）圖案的面積是所述第二配線層的平面面積的一半或更多。

**【0222】** 用於形成第二配線層 132（M1）的接地（GND）圖案可充當在第一配線層 112（C2）、配線層 142（M2）等中所設計的各種訊號（S）圖案等的返回路徑（RP）。由於第二配線層 132（M1）的接地（GND）圖案充分地充當在上述上層及下層上形成的各種訊號（S）圖案的返回路徑 RP，因此在電子元件封裝 100B 被電性連接於外部之後，電子元件封裝 100B 可平穩地運作。

**【0223】** 第二配線層 132（M1）與第一配線層 112（C2）之間的距離可小於第二配線層 132（M1）與配線層 142（M2）之間的距離。所述距離可根據橫截面的厚度方向來決定。如上所述，在其中第二配線層 132（M1）與第一配線層 112（C2）之間的距離小於第二配線層 132（M1）與配線層 142（M2）之間的距離的情形中，第二配線層 132（M1）的重新分配圖案 R 中的接地（GND）圖案可更有效地充當返回路徑 RP。

105-10-17

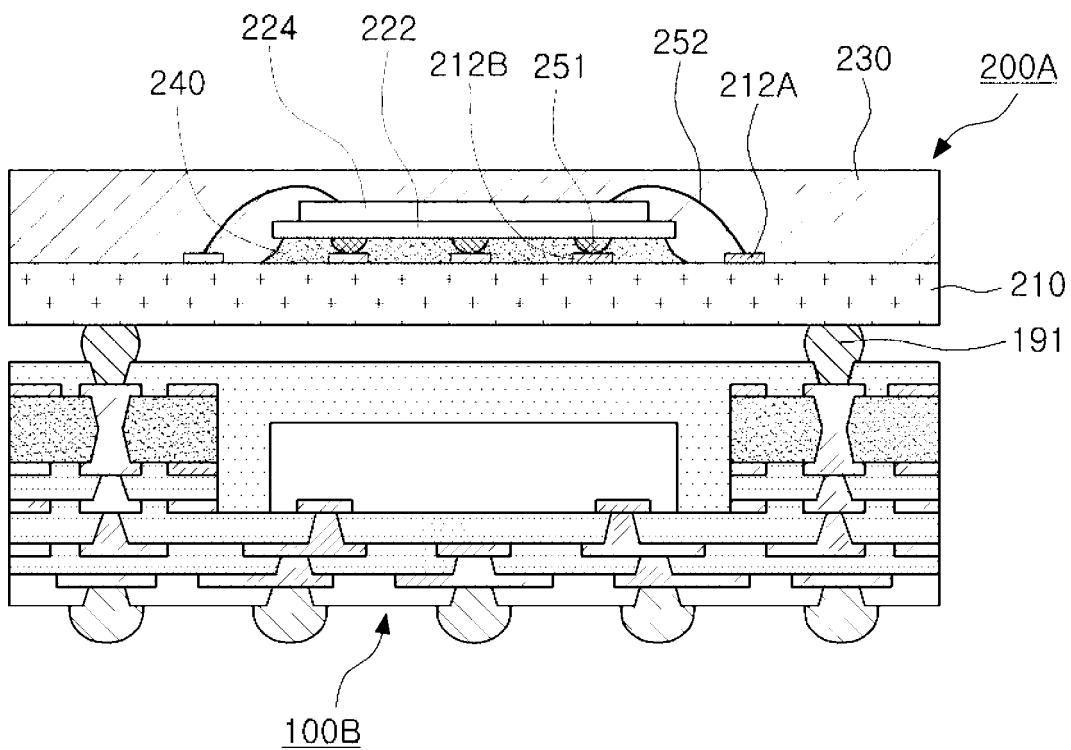

**【0224】** 圖 40 是示意性地說明電子元件封裝的另一實例的剖視圖。

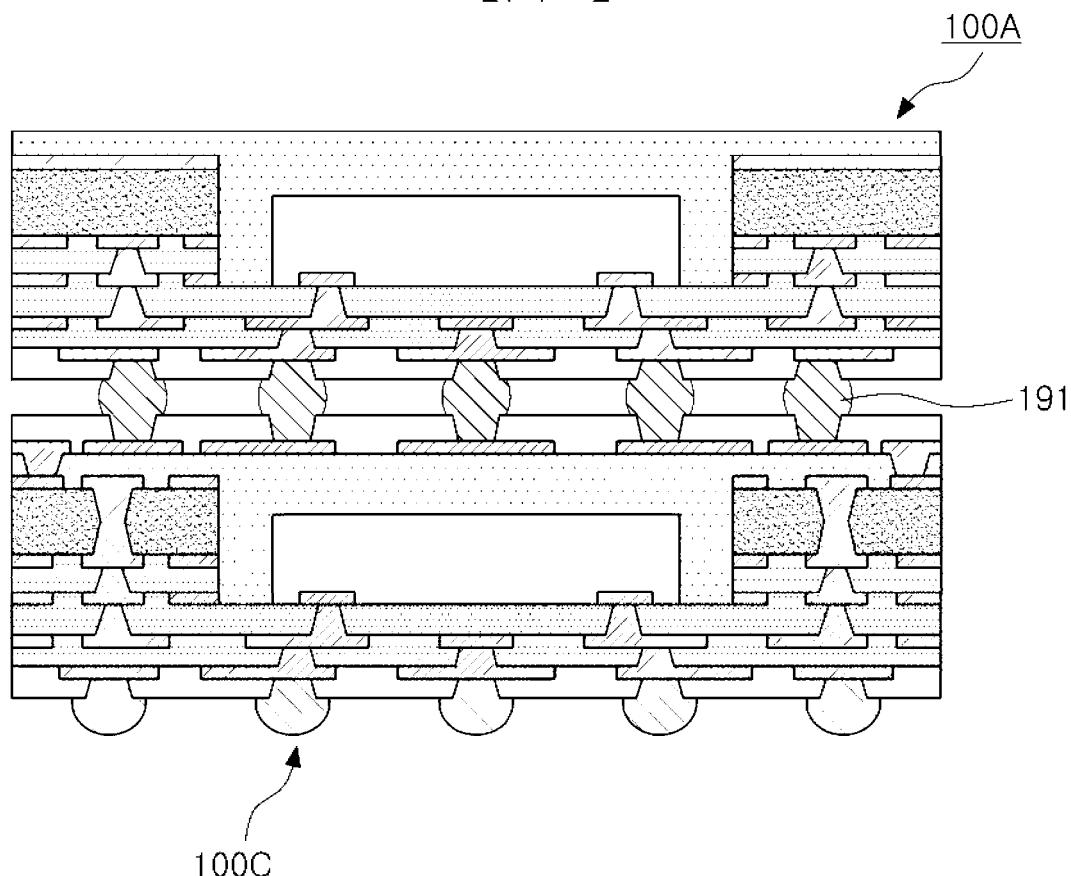

**【0225】** 參照圖 40，根據另一實例的電子元件封裝可具有其中堆疊有多個電子元件封裝的形式。根據上述各種實例的電子元件封裝 100A 至 100Q 可以各種形式應用於根據本實例的電子元件封裝。舉例而言，根據本實例的電子元件封裝可具有其中在上述電子元件封裝 100B 上安置有另一電子元件封裝 200A 的形式。

**【0226】** 如上所述，電子元件封裝 100B 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。由於相應元件相同於上述元件，因此將不再對其予以闡述。

**【0227】** 電子元件封裝 200A 可包括配線基板 210、以覆晶形式安裝於配線基板 210 上的第一電子元件 222、以及堆疊於第一電子元件 222 上的第二電子元件 224。此外，電子元件封裝 200A 可包括設置於第一電子元件 222 與配線基板 210 之間的間隙中的底部填充樹脂 240、以及用於囊封第一電子元件 222 及第二電子元件 224

等的囊封樹脂 230。

**【0228】** 第一電子元件 222 及第二電子元件 224 可為積體電路晶片，例如為揮發性記憶體（例如，動態隨機存取記憶體）、非揮發性記憶體（例如，唯讀記憶體）、快閃記憶體等記憶體晶片。第一電子元件 222 的平面形狀可較第二電子元件 224 的平面形狀大。

**【0229】** 結合焊墊 212A 及覆晶焊墊 212B 可安置於配線基板 210 的上表面上。配線基板 210 可包括多個絕緣層（圖中未示出）、通孔圖案（圖中未示出）、及形成於所述多個絕緣層上的配線圖案（圖中未示出）等。配線基板 210 的通孔圖案（圖中未示出）及配線圖案（圖中未示出）可電性連接至結合焊墊 212A、覆晶焊墊 212B 等。

**【0230】** 結合焊墊 212A 可經由結合配線 252 而電性連接至形成於第二電子元件 224 的表面上的電極焊墊（圖中未示出）。第一電子元件 222 的凸塊 251 可以覆晶形式結合至覆晶焊墊 212B。可使用以上所述的傳導性材料作為結合焊墊 212A 及覆晶焊墊 212B 的材料。可使用 Au、Ni/Au、Ni/Pb/Au 等對結合焊墊 212A 的及覆晶焊墊 212B 的表面執行金屬層處理。

**【0231】** 使用囊封樹脂 230 的目的為保護第一電子元件 222 及第二電子元件 224、可囊封第一電子元件 222 及第二電子元件 224。可使用例如環氧系絕緣樹脂等習知的絕緣材料作為囊封樹脂 230 的材料。

**【0232】** 使用底部填充樹脂 240 的目的可為提高第一電子元件

105-10-17

222 的凸塊 251 與覆晶焊墊 212B 之間的連接部分的連接強度。底部填充樹脂 240 可設置於配線基板 210 與第一電子元件 222 之間的間隙中。亦可使用例如環氧系絕緣樹脂等習知的絕緣材料作為底部填充樹脂 240 的材料。

**【0233】** 連接端子 191 可用於將電子元件封裝 200A 連接至電子元件封裝 100B。電子元件封裝 200A 及電子元件封裝 100B 可堆疊於一起並經由連接端子 191 而結合至彼此。連接端子 191 可為形成於電子元件封裝 100B 上的第二外部連接端子 185。作為另一選擇，連接端子 191 可為形成於電子元件封裝 200A 之下的外部連接端子（圖中未示出）。作為另一選擇，連接端子 191 可為藉由將形成於電子元件封裝 100B 上的第二外部連接端子 185 與形成於電子元件封裝 200A 之下的外部連接端子（圖中未示出）彼此整合於一起而形成的端子。例如銅（Cu）、鋁（Al）、銀（Ag）、錫（Sn）、金（Au）、鎳（Ni）、鉛（Pb）、焊料等傳導性材料可用作連接端子 191 的材料。連接端子 191 可為焊盤、球、引腳等。連接端子 191 可由多個層或單個層形成。在其中連接端子 191 由多個層形成的情形中，連接端子 191 可含有銅柱及焊料，且在其中連接端子 191 由單個層形成的情形中，連接端子 191 可含有錫銀焊料或銅。然而，此僅為實例，且連接端子 191 並非僅限於此。

**【0234】** 圖 41 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0235】** 參照圖 41，根據另一實例的電子元件封裝可具有其中上

105-10-17

述電子元件封裝 100A 堆疊於上述電子元件封裝 100C 上的形式。

**【0236】** 如上所述，電子元件封裝 100C 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、用於囊封電子元件 120 的囊封劑 160、安置於囊封劑 160 上的外配線層 162、以及穿透過囊封劑 160 的外通孔 163。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。由於相應元件相同於上述元件，因此將不再對其予以闡述。

**【0237】** 如上所述，電子元件封裝 100A 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140 及 150、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、安置於第一絕緣層 111A 的表面上的金屬層 135、安置於第二絕緣層 111B 的下表面上的第二配線層 132、以及穿透過第二絕緣層 111B 的通孔 113。由於相應元件相同於上述元件，因此將不再對其予以闡述。

**【0238】** 電子元件封裝 100C 與電子元件封裝 100A 可堆疊於一起

105-10-17

並經由連接端子 191 而結合至彼此。連接端子 191 可為形成於電子元件封裝 100C 上的第二外部連接端子 185。作為另一選擇，連接端子 191 可為形成於電子元件封裝 100A 之下的一第一外部連接端子 175。作為另一選擇，連接端子 191 可為藉由將形成於電子元件封裝 100C 上的第二外部連接端子 185 與形成於電子元件封裝 100A 之下的一第一外部連接端子 175 彼此整合於一起而形成的端子。例如銅 (Cu)、鋁 (Al)、銀 (Ag)、錫 (Sn)、金 (Au)、鎳 (Ni)、鉛 (Pb)、焊料等傳導性材料可用作連接端子 191 的材料。連接端子 191 可為焊盤、球、引腳等。連接端子 191 可由多個層或單個層形成。在其中連接端子 191 由多個層形成的情形中，連接端子 191 可含有銅柱及焊料，且在其中連接端子 191 由單個層形成的情形中，連接端子 191 可含有錫銀焊料或銅。然而，此僅為實例，且連接端子 191 並非僅限於此。

**【0239】** 圖 42 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0240】** 參照圖 42，根據另一實例的電子元件封裝 100R 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140、150 及 155、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔

105-10-17

113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、以及安置於第二絕緣層 111B 的下表面上的第二配線層 132。

**【0241】** 重新分配部 155 可包括重新分配部絕緣層 156、安置於重新分配部絕緣層 156 上的重新分配部配線層 157、以及穿透過重新分配部絕緣層 156 以藉此電性連接至重新分配部配線層 157 的重新分配部通孔 158。囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分。此外，暴露於外部的第二外部連接端子 185 可安置於囊封劑 160 的第二開口部 161 中。第二外部連接端子 185 可連接至經由第二開口部 161 而暴露出的第三配線層 131。具有第一開口部 171 的保護層 170 可安置於重新分配部 155 下、凸塊下金屬層 (under-bump metal layer) 172 可安置於第一開口部 171 中、且第一外部連接端子 175 可安置於凸塊下金屬層 172 上。

**【0242】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 42 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140、150 及 155 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上

105-10-17

表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0243】** 在下文中，將更詳細地闡述根據另一實例的電子元件封裝 100R 中的訊號移動路徑及依所述訊號移動路徑而定的接地的佈局，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0244】** 電子元件 120 可具有用於訊號的電極焊墊（電極焊墊 120P 中沿路徑 S' 的至少一者），所述用於訊號的電極焊墊（電極焊墊 120P 中沿路徑 S' 的至少一者）可經由重新分配部 140 的用於訊號的第一通孔（通孔 143 中沿路徑 S' 的至少一者）而電性連接至重新分配部 140 的配線層 142 的訊號圖案（配線層 142 中沿路徑 S' 的至少一個訊號圖案），重新分配部 140 的配線層 142 的訊號圖案（配線層 142 中沿路徑 S' 的至少一個訊號圖案）可經由重新分配部 140 的用於訊號的第二通孔（通孔 143 中沿路徑 S' 的至少另一者）而電性連接至框架 110 的第二配線層 132 的訊號圖案（第二配線層 132 中沿路徑 S' 的至少一個訊號圖案），框架 110 的第二配線層 132 的訊號圖案（第二配線層 132 中沿路徑 S' 的至少一個訊號圖案）可經由框架 110 的用於訊號的通孔（通孔 113 中沿路徑 S' 的至少一者）而電性連接至框架 110 的第一配線層 112 的訊號圖案（第一配線層 112 中沿路徑 S' 的至少一個訊號圖案），框架 110 的第一配線層 112 的訊號圖案（第一配線層 112 中沿路徑 S' 的至少一個訊號圖案）可經由框架 110 的用於訊號的內部通孔（內

105-10-17

部通孔 115 中沿路徑 S'的至少一者)而電性連接至框架 110 的第三配線層 131 的訊號圖案(第三配線層 131 中沿路徑 S'的至少一個訊號圖案),框架 110 的第三配線層 131 的訊號圖案(第三配線層 131 中沿路徑 S'的至少一個訊號圖案)可電性連接至安置於框架 110 之上的扇出區中的用於訊號的外部連接端子(外部連接端子 185 中沿路徑 S'的至少一者),且框架 110 的第二配線層 132 及第三配線層 131 可具有用於提供訊號的返回路徑的接地圖案(第三配線層 131 中沿路徑 G'的至少一個接地圖案及第二配線層 132 中沿路徑 G'的至少一個接地圖案)。

**【0245】**舉例而言，使用電子元件 120 的電極焊墊 120P 中的某些電極焊墊 120P 的目的可為用於訊號連接，且使用電極焊墊 120P 中的其他電極焊墊 120P 的目的可為用於接地連接。所述訊號中的某些訊號可自用於訊號連接的電極焊墊(電極焊墊 120P 中沿路徑 S'的至少一者)開始經由重新分配部的用於訊號的通孔(通孔 143 中沿路徑 S'的至少一者)而移動至重新分配部的配線層 142 的訊號圖案(配線層 142 中沿路徑 S'的至少一個訊號圖案)、經由重新分配部的用於訊號的通孔 143 而移動至框架 110 的第二配線層 132 的訊號圖案(第二配線層 132 中沿路徑 S'的至少一個訊號圖案)、經由框架 110 的用於訊號的通孔(通孔 113 中沿路徑 S'的至少一者)而移動至框架 110 的第一配線層 112 的訊號圖案(第一配線層 112 中沿路徑 S'的至少一個訊號圖案)、經由框架 110 的用於訊號的內部通孔(內部通孔 115 中沿路徑 S'的至少一者)而移動至

105-10-17

框架 110 的第三配線層 131 的訊號圖案（第三配線層 131 中沿路徑 S'的至少一個訊號圖案）、並接著經由用於訊號的第二外部連接端子（第二外部連接端子 185 中沿路徑 S'的至少一者）而移動至外部。

**【0246】** 為提供沿上述移動路徑的訊號的返回路徑，可在上述移動路徑之上或之下形成接地圖案。所述接地圖案可形成於框架 110 的第二配線層 132 及第三配線層 131 上以及重新分配部配線層 142 及 152 上。在其中框架 110 的第一配線層 112 的絕大部分上形成有訊號圖案的情形中，與第一配線層 112 的下部部分及/或上部部分對應的第二配線層 132 的及第三配線層 131 的絕大部分上可形成有接地圖案。此外，重新分配部配線層 142 的絕大部分上可形成有訊號圖案，且重新分配部配線層 152 的絕大部分上可形成有接地圖案。如上所述，框架 110 可用作訊號圖案、接地圖案等的重新分配區，且由於框架 110 可在安置電子元件 120 之前形成，因此可提高製程良率等。接地圖案可具有板形形狀等，但並非僅限於此。

**【0247】** 圖 43 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0248】** 參照圖 43，根據另一實例的電子元件封裝 100S 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140、150 及 155、以及用於囊封電子元件 120 的囊封劑 160。框架

105-10-17

110 可包括第一絕緣層 111A、第二絕緣層 111B、第三絕緣層 111C、分別安置於第一絕緣層 111A 與第二絕緣層 111B 之間及第一絕緣層 111A 與第三絕緣層 111C 之間的多個第一配線層 112A 及 112B、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的第一通孔 113A、以及穿透過第三絕緣層 111C 的第二通孔 113B。框架 110 可更包括安置於第三絕緣層 111C 的上表面 110A 上的第三配線層 131 及安置於第二絕緣層 111B 的下表面上的第二配線層 132。

**【0249】** 重新分配部 155 可包括重新分配部絕緣層 156、安置於重新分配部絕緣層 156 上的重新分配部配線層 157、及穿透過重新分配部絕緣層 156 以藉此電性連接至重新分配部配線層 157 的重新分配部通孔 158。囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分。此外，暴露於外部的第二外部連接端子 185 可安置於囊封劑 160 的第二開口部 161 中。第二外部連接端子 185 可連接至經由第二開口部 161 而暴露出的第三配線層 131。具有第一開口部 171 的保護層 170 可安置於重新分配部 155 下，凸塊下金屬層 172 可安置於第一開口部 171 中，且第一外部連接端子 175 可安置於凸塊下金屬層 172 上。

**【0250】** 貫穿孔 110X 可依序穿透過第三配線層 131、第三絕緣層 111C、第一配線層 112B、第一絕緣層 111A、第一配線層 112A、第二絕緣層 111B 及第二配線層 132。第一配線層 112 及第二絕緣

105-10-17

層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 43 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140、150 及 155 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0251】** 在下文中，將更詳細地闡述根據另一實例的電子元件封裝 100S 的訊號移動路徑及依所述訊號移動路徑而定的接地的佈局，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。

**【0252】** 電子元件 120 可具有用於訊號的電極焊墊（電極焊墊 120P 中沿路徑 S'' 的至少一者），所述用於訊號的電極焊墊（電極焊墊 120P 中沿路徑 S'' 的至少一者）可經由重新分配部 140 的用於訊號的第一通孔（通孔 143 中沿路徑 S'' 的至少一者）而電性連接至重新分配部 140 的配線層 142 的訊號圖案（配線層 142 中沿路徑 S'' 的至少一個訊號圖案），重新分配部 140 的配線層 142 的訊號圖案（配線層 142 中沿路徑 S'' 的至少一個訊號圖案）可經由重新分配部 140 的用於訊號的第二通孔（通孔 143 中沿路徑 S'' 的至少另一者）而電性連接至框架 110 的第二配線層 132 的訊號圖

105-10-17

案（第二配線層 132 中沿路徑 S'' 的至少一個訊號圖案），框架 110 的第二配線層 132 的訊號圖案（第二配線層 132 中沿路徑 S'' 的至少一個訊號圖案）可經由框架 110 的用於下級訊號的通孔（通孔 113A 中沿路徑 S'' 的至少一者）而電性連接至框架 110 的第一配線層 112A 的訊號圖案（第一配線層 112A 中沿路徑 S'' 的至少一個訊號圖案），框架 110 的第一配線層 112A 的訊號圖案（第一配線層 112A 中沿路徑 S'' 的至少一個訊號圖案）可經由框架 110 的用於訊號的內部通孔（內部通孔 115 中沿路徑 S'' 的至少一者）而電性連接至框架 110 的第一配線層 112B 的訊號圖案（第一配線層 112B 中沿路徑 S'' 的至少一個訊號圖案），框架 110 的第一配線層 112B 的訊號圖案（第一配線層 112B 中沿路徑 S'' 的至少一個訊號圖案）可經由框架 110 的用於上級訊號的通孔而電性連接至框架 110 的第三配線層 131 的訊號圖案（第三配線層 131 中沿路徑 S'' 的至少一個訊號圖案），框架 110 的第三配線層 131 的訊號圖案（第三配線層 131 中沿路徑 S'' 的至少一個訊號圖案）可電性連接至安置於框架 110 之上的扇出區中的用於訊號的外部連接端子（外部連接端子 185 中沿路徑 S'' 的至少一者），且框架 110 的第二配線層 132 及第一配線層 112B 可具有用於提供訊號的返回路徑的接地圖案（第二配線層 132 中沿路徑 G'' 的至少一個接地圖案及第一配線層 112B 中沿路徑 G'' 的至少一個接地圖案）。

**【0253】** 舉例而言，使用電子元件 120 的電極焊墊 120P 中的某些電極焊墊 120P 的目的可為用於訊號連接，且使用電極焊墊 120P

105-10-17

中的其他電極焊墊 120P 的目的可為用於接地連接。所述訊號中的某些訊號可自用於訊號連接的電極焊墊（電極焊墊 120P 中沿路徑 S''的至少一者）開始經由重新分配部的用於訊號的第一通孔（通孔 143 中沿路徑 S''的至少一者）而移動至重新分配部配線層 142 的訊號圖案（重新分配部配線層 142 中沿路徑 S''的至少一個訊號圖案）、經由重新分配部的用於訊號的第二通孔（通孔 143 中沿路徑 S''的至少一者）而移動至框架 110 的第二配線層 132 的訊號圖案（第二配線層 132 中沿路徑 S''的至少一個訊號圖案）、經由框架 110 的用於下級訊號的通孔（通孔 113A 中沿路徑 S''的至少一者）而移動至框架 110 的第一配線層 112A 的訊號圖案（第一配線層 112A 中沿路徑 S''的至少一個訊號圖案）、經由框架 110 的用於訊號的內部通孔（內部通孔 115 中沿路徑 S''的至少一者）而移動至框架 110 的第一配線層 112B 的訊號圖案（第一配線層 112B 中沿路徑 S''的至少一個訊號圖案）、經由框架 110 的用於上級訊號的通孔（通孔 113B 中沿路徑 S''的至少一者）而移動至框架 110 的第三配線層 131 的訊號圖案（第三配線層 131 中沿路徑 S''的至少一個訊號圖案）、並接著經由用於訊號的第二外部連接端子（第二外部連接端子 185 中沿路徑 S''的至少一者）而移動至外部。

**【0254】** 為提供沿上述移動路徑的訊號的返回路徑，可在上述移動路徑之上或之下形成接地圖案。所述接地圖案可形成於框架 110 的第二配線層 132 及第一配線層 112B 上以及重新分配部配線層 142 及 152 上。在其中框架 110 的第一配線層 112A 的絕大部分上

105-10-17

形成有訊號圖案的情形中，與第一配線層 112A 的下部部分及/或上部部分對應的第二配線層 132 的及第一配線層 112B 的絕大部分上可形成有接地圖案。此外，重新分配部配線層 142 的絕大部分上可形成有訊號圖案，且重新分配部配線層 152 的絕大部分上可形成有接地圖案。如上所述，框架 110 可用作訊號圖案、接地圖案等的重新分配區，且由於框架 110 可如上所述在安置電子元件 120 之前形成，因此可提高製程良率等。接地圖案可具有板形形狀等，但並非僅限於此。

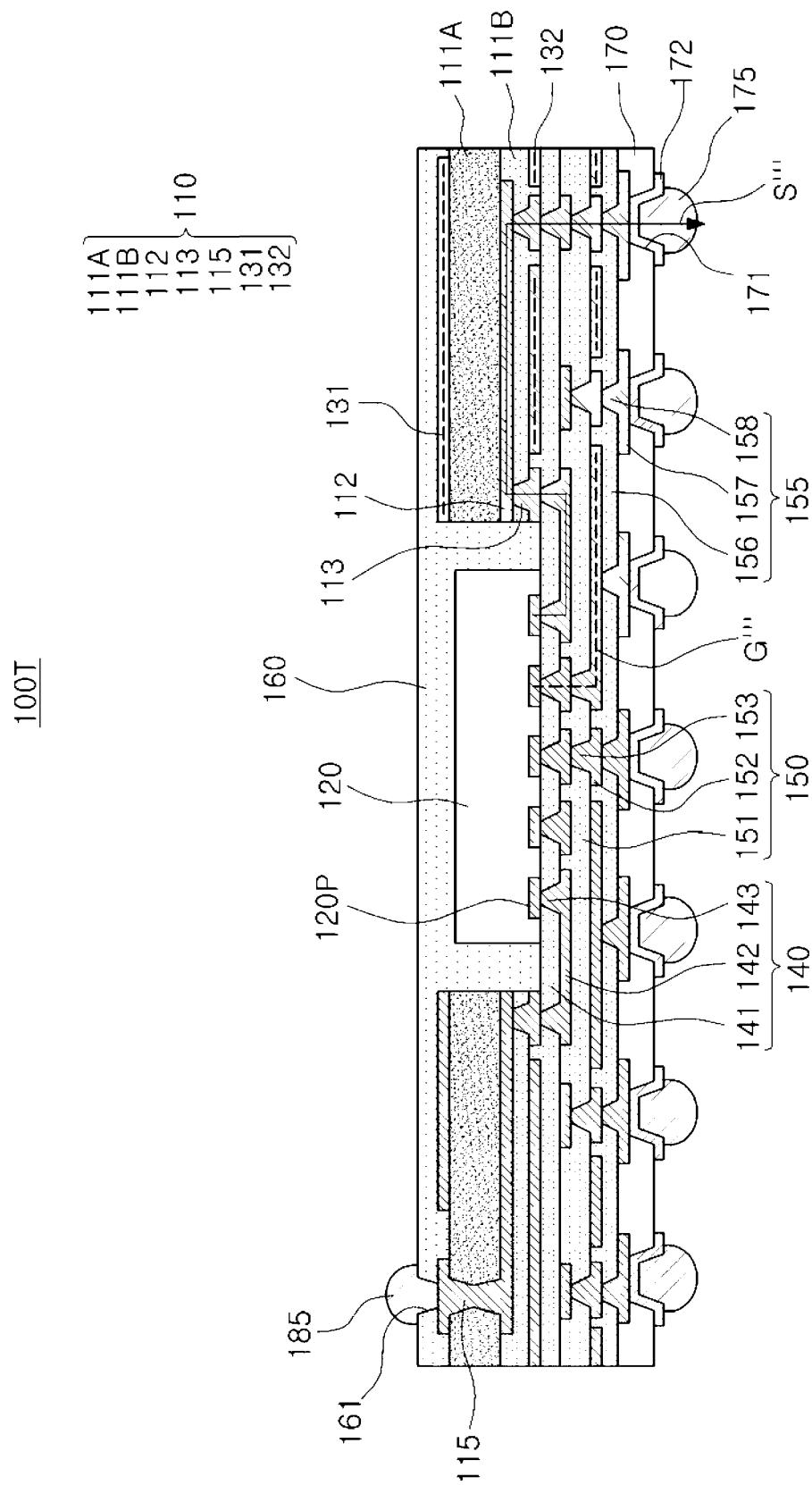

**【0255】** 圖 44 是示意性地說明電子元件封裝的另一實例的剖視圖。

**【0256】** 參照圖 44，根據另一實例的電子元件封裝 100T 可包括具有貫穿孔 110X 的框架 110、安置於框架 110 的貫穿孔 110X 中的電子元件 120、安置於框架 110 及電子元件 120 下的重新分配部 140、150 及 155、以及用於囊封電子元件 120 的囊封劑 160。框架 110 可包括第一絕緣層 111A、第二絕緣層 111B、安置於第一絕緣層 111A 與第二絕緣層 111B 之間的第一配線層 112、穿透過第一絕緣層 111A 的內部通孔 115、穿透過第二絕緣層 111B 的通孔 113、安置於第一絕緣層 111A 的上表面 110A 上的第三配線層 131、及安置於第二絕緣層 111B 的下表面 110B 上的第二配線層 132。

**【0257】** 重新分配部 155 可包括重新分配部絕緣層 156、安置於重新分配部絕緣層 156 上的重新分配部配線層 157、以及穿透過重新

105-10-17

分配部絕緣層 156 以藉此電性連接至重新分配部配線層 157 的重新分配部通孔 158。囊封劑 160 可具有第二開口部 161，第二開口部 161 暴露出安置於框架 110 的上表面 110A 上的第三配線層 131 的至少部分。此外，暴露於外部的第二外部連接端子 185 可安置於囊封劑 160 的第二開口部 161 中。第二外部連接端子 185 可連接至經由第二開口部 161 而暴露出的第三配線層 131。具有第一開口部 171 的保護層 170 可安置於重新分配部 155 下，凸塊下金屬層 172 可安置於第一開口部 171 中，且第一外部連接端子 175 可安置於凸塊下金屬層 172 上。

**【0258】** 貫穿孔 110X 可依序穿透過第三配線層 131、第一絕緣層 111A、第一配線層 112、第二絕緣層 111B、及第二配線層 132。第一配線層 112 及第二絕緣層 111B 中的至少一者可位於電子元件 120 的上表面與下表面之間的位階處。如圖 44 中所示，電子元件 120 的上表面相對於重新分配部 140 及 150 位於框架 110 的上表面 110A 下的位階處；然而，本發明並非僅限於此。電子元件 120 的上表面相對於重新分配部 140、150 及 155 可位於與框架 110 的上表面 110A 相同的位階處或位於框架 110 的上表面 110A 之上但位於第三配線層 131 的上表面下、或者位於與第三配線層 131 的上表面相同的位階處或位於第三配線層 131 的上表面之上，只要第三配線層 131 及電子元件 120 均被囊封劑 160 覆蓋即可。

**【0259】** 在下文中，將更詳細地闡述根據另一實例的電子元件封裝 100T 中的訊號移動路徑及依所述訊號移動路徑而定的接地的

105-10-17

佈局，將不再對與上述內容重複的內容予以闡述，且將主要闡述與上述內容不同的內容。