(12) 发明专利

(10) 授权公告号 CN 107690692 B

(45) 授权公告日 2022.01.25

(21) 申请号 201680032734.5

(74) 专利代理机构 北京律盟知识产权代理有限

(22) 申请日 2016.06.03

责任公司 11287

(65) 同一申请的已公布的文献号

代理人 沈锦华

申请公布号 CN 107690692 A

(51) Int.CI.

(43) 申请公布日 2018.02.13

H01L 21/02 (2006.01)

(30) 优先权数据

H01L 21/306 (2006.01)

14/735,359 2015.06.10 US

H01L 21/3105 (2006.01)

(85) PCT国际申请进入国家阶段日

H01L 21/311 (2006.01)

2017.12.05

H01L 21/762 (2006.01)

(86) PCT国际申请的申请数据

H01L 21/8234 (2006.01)

PCT/US2016/035785 2016.06.03

H01L 21/8238 (2006.01)

(87) PCT国际申请的公布数据

H01L 29/06 (2006.01)

W02016/200693 EN 2016.12.15

(56) 对比文件

US 2002168834 A1, 2002.11.14

(73) 专利权人 密克罗奇普技术公司

US 6391781 B1, 2002.05.21

地址 美国亚利桑那州

CN 103208453 A, 2013.07.17

(72) 发明人 贾斯丁·希罗奇·萨托

US 2001041420 A1, 2001.11.15

格雷戈里·艾伦·斯托姆

郭东明等.超大规模集成电路制造中硅片平坦化技术的未来发展.《机械工程学报》.2003, (第10期),

审查员 于鹏飞

权利要求书2页 说明书6页 附图18页

(54) 发明名称

除剩余氮化物层,使得所述剩余经氧化物填充沟槽界定突出于所述半导体衬底的经曝露上表面上方的沟槽隔离结构。

形成浅沟槽隔离(STI)结构的方法

(57) 摘要

1. 一种形成用于集成电路的沟槽隔离结构的方法,所述方法包括:

在半导体衬底上方形成氮化物层;

穿透所述氮化物层及所述半导体衬底的部分执行沟槽蚀刻工艺以形成沟槽;

沉积沟槽氧化物层于所述氮化物层的剩余部分上方且使其延伸到所述沟槽中以形成经填充沟槽;

沉积牺牲平坦化层于所述沟槽氧化物层上方,所述牺牲平坦化层对所述沟槽氧化物层具有蚀刻选择性;

执行多步骤蚀刻工艺,其包含:

平坦化蚀刻工艺,其移除所述牺牲平坦化层且减小所述沟槽氧化物层的上表面中的表面变化;及

移除所述氮化物层的所述剩余部分,使得所述经填充沟槽的剩余氧化物界定突出于所述半导体衬底的经曝露上表面上方的沟槽隔离结构;

其中所述多步骤蚀刻工艺包括:执行第一经调适蚀刻以敞开相对于所述沟槽氧化物层的所述牺牲平坦化层,然后执行对相对于所剩余的牺牲平坦化层的所述沟槽氧化物层具有选择性的第二蚀刻,然后执行相对于所述沟槽氧化物层和所述牺牲平坦化层的第三非选择性蚀刻。

2. 根据权利要求1所述的方法,其中:

所述沟槽蚀刻工艺形成多个沟槽;

使所述沟槽氧化物层沉积到所述多个沟槽中以形成多个经填充沟槽;

所述多步骤蚀刻工艺移除所述多个经填充沟槽外侧的所述沟槽氧化物层的剩余部分;

及

氮化物移除工艺移除所述氮化物层的所述剩余部分,使得所述多个经填充沟槽中的每一者的剩余氧化物界定突出于所述半导体衬底的经曝露上表面上方的沟槽隔离结构。

3. 根据权利要求2所述的方法,其中所述第二蚀刻在所述沟槽氧化物层的最高点与所述牺牲平坦化层大致齐平时停止,和/或,其中所述第三蚀刻在到达所述氮化物层之前停止。

4. 根据权利要求2所述的方法,其中执行所述多步骤蚀刻工艺直到将所述经氧化物填充沟槽的顶部表面向下蚀刻到邻近所述经氧化物填充沟槽的所述氮化物层的所述剩余部分的顶部表面下方的预定义距离为止。

5. 根据权利要求2所述的方法,其中执行所述多步骤蚀刻工艺直到将所述经氧化物填充沟槽的顶部表面向下蚀刻到邻近所述经氧化物填充沟槽的所述半导体衬底的顶部表面上方的预定义距离为止。

6. 根据权利要求1所述的方法,其中:

所述多步骤蚀刻工艺包括多步骤平坦化蚀刻工艺;且

通过所述多步骤平坦化蚀刻工艺执行所述移除所述氮化物层的所述剩余部分的步骤。

7. 根据权利要求6所述的方法,其中多步骤蚀刻工艺包括四步骤平坦化蚀刻工艺。

8. 根据权利要求6所述的方法,其中对氧化物具有选择性的所述第二蚀刻经执行直到将所述经氧化物填充沟槽的顶部表面向下蚀刻到邻近所述经氧化物填充沟槽的所述半导体衬底的顶部表面上方的预定义距离为止。

9. 根据权利要求1所述的方法,其中所述平坦化层包括有机硅酸盐。

10. 根据权利要求1所述的方法,其中所述平坦化层包括有机硅氧烷基聚合物。

11. 根据权利要求9所述的方法,其中所述有机硅酸盐包括有机硅氧烷基聚合物,所述有机硅氧烷基聚合物包括有机生色团。

12. 根据权利要求1所述的方法,其中将所述平坦化层旋涂于所述经沉积氧化物上方。

13. 根据权利要求1所述的方法,其中所述方法是在无需化学机械平坦化CMP工艺的情况下执行。

14. 根据权利要求1所述的方法,其中在半导体衬底上方形成所述氮化物层包括在所述半导体衬底上方形成薄垫氧化物且随后在所述薄垫氧化物上方形成所述氮化物层。

15. 一种半导体裸片,其根据在前述权利要求1-14中任一项界定的方法制造。

## 形成浅沟槽隔离 (STI) 结构的方法

### 技术领域

[0001] 本发明涉及半导体集成电路 (IC) 制造,且更特定来说,涉及形成例如用于互补金属氧化物半导体 (CMOS) 装置的浅沟槽隔离结构 (STI) 的方法。

### 背景技术

[0002] 浅沟槽隔离 (STI) 是防止邻近半导体装置组件之间的电流泄漏的集成电路特征。STI 结构常用于 CMOS 装置中,且通常在半导体装置制造过程初期、在形成晶体管之前形成。常规 STI 过程的关键步骤涉及在硅衬底中蚀刻沟槽的图案;沉积一或多种电介质材料(例如,二氧化硅)以填充所述沟槽;及使用化学机械平坦化 (CMP) 移除过量电介质。

[0003] 然而,常规 STI 形成中涉及的 CMP 处理可引起一或多个相关问题。举例来说,CMP 工艺可产生显著中心到边缘偏置,其可导致横跨晶片的足够变化以造成良率下降。作为另一实例,CMP 可造成场氧化物的局部非均匀性及凹陷。此外,CMP 工艺可将氧化物残余物留在最大作用区域上,其可造成导致良率损失的 SiN 残余物。最后,使用 CMP 的常规 STI 形成处理涉及相对大数目的步骤。

### 发明内容

[0004] 根据本发明的教示,可在不使用 CMP 及/或在与常规技术相比运用减小数目的步骤的情况下形成沟槽隔离结构,例如,浅沟槽隔离 (STI)。

[0005] 在一个实施例中,一种形成用于集成电路的沟槽隔离结构(例如,STI)的方法包含:在半导体衬底上方形成薄垫氧化物层,接着形成氮化物层;穿透所述氮化物层、所述垫氧化物及所述半导体衬底的部分执行沟槽蚀刻工艺以形成沟槽;沉积沟槽氧化物层于所述氮化物层的剩余部分上方且将其延伸到所述沟槽中以形成经填充沟槽;沉积牺牲平坦化层于所述经沉积氧化物上方,所述牺牲平坦化层对所述沟槽氧化物层具有蚀刻选择性;执行平坦化蚀刻工艺,其移除所述牺牲平坦化层且减小所述沟槽氧化物层的上表面中的表面变化;执行氧化物蚀刻工艺,其对所述沟槽氧化物层具有选择性以移除所述经填充沟槽外侧的所述沟槽氧化物层的剩余部分;及执行氮化物移除过程,其移除所述氮化物层的所述剩余部分,使得所述经填充沟槽的剩余氧化物界定突出于所述半导体衬底的经曝露上表面上方的沟槽隔离结构。当然,此技术可根据需要用来形成多个沟槽隔离结构。

[0006] 在另一实施例中,一种半导体裸片可包含:半导体衬底;及多个沟槽隔离结构(例如,STI),其通过一过程形成于所述半导体衬底中,所述过程包含:在所述半导体衬底上方形成薄垫氧化物层,接着形成氮化物层;穿透所述氮化物层、所述垫氧化物及所述半导体衬底的部分执行沟槽蚀刻工艺以形成多个沟槽;沉积沟槽氧化物层于所述氮化物层的剩余部分上方且使其延伸到所述沟槽中以形成多个经填充沟槽;沉积牺牲平坦化层于所述经沉积氧化物上方,所述牺牲平坦化层对所述沟槽氧化物层具有蚀刻选择性;执行平坦化蚀刻工艺,其移除所述牺牲平坦化层且减小所述沟槽氧化物层的上表面中的表面变化;执行氧化物蚀刻工艺,其对所述沟槽氧化物层具有选择性以移除所述经填充沟槽外侧的所述沟槽氧

化物层的剩余部分；及执行氮化物移除过程，其移除所述氮化物层的所述剩余部分，使得每一经填充沟槽的剩余氧化物界定突出于所述半导体衬底的经曝露表面上方的沟槽隔离结构。

[0007] 在其它实施例中，CMOS装置包括包含如上文所论述那样形成的多个沟槽隔离结构的半导体结构。

[0008] 在一些实施例中，所述牺牲平坦化层包括有机硅酸盐。在特定实施例中，所述牺牲平坦化层包括例如根据化学式 $R_xCH_3ySiO_z$ 的有机硅氧烷基聚合物，其中R是有机生色团。举例来说，在一些实施例中，所述牺牲平坦化层可包括由霍尼韦尔电子材料(Honeywell Electronic Materials) (地址为新泽西州07960莫里斯敦哥伦比亚路101(101Columbia Rd, Morristown, NJ 07960)) 供应的DUO<sup>TM</sup> 193或DUO<sup>TM</sup> 248抗反射涂层。

## 附图说明

[0009] 下文参考图式论述实例实施例，其中：

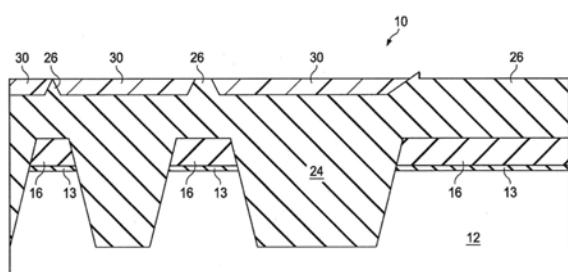

[0010] 图1A到1H说明根据本发明的实例实施例的实例半导体集成电路结构的横截面，其展示形成用于集成电路的沟槽隔离结构(例如，STI)的逐步过程；

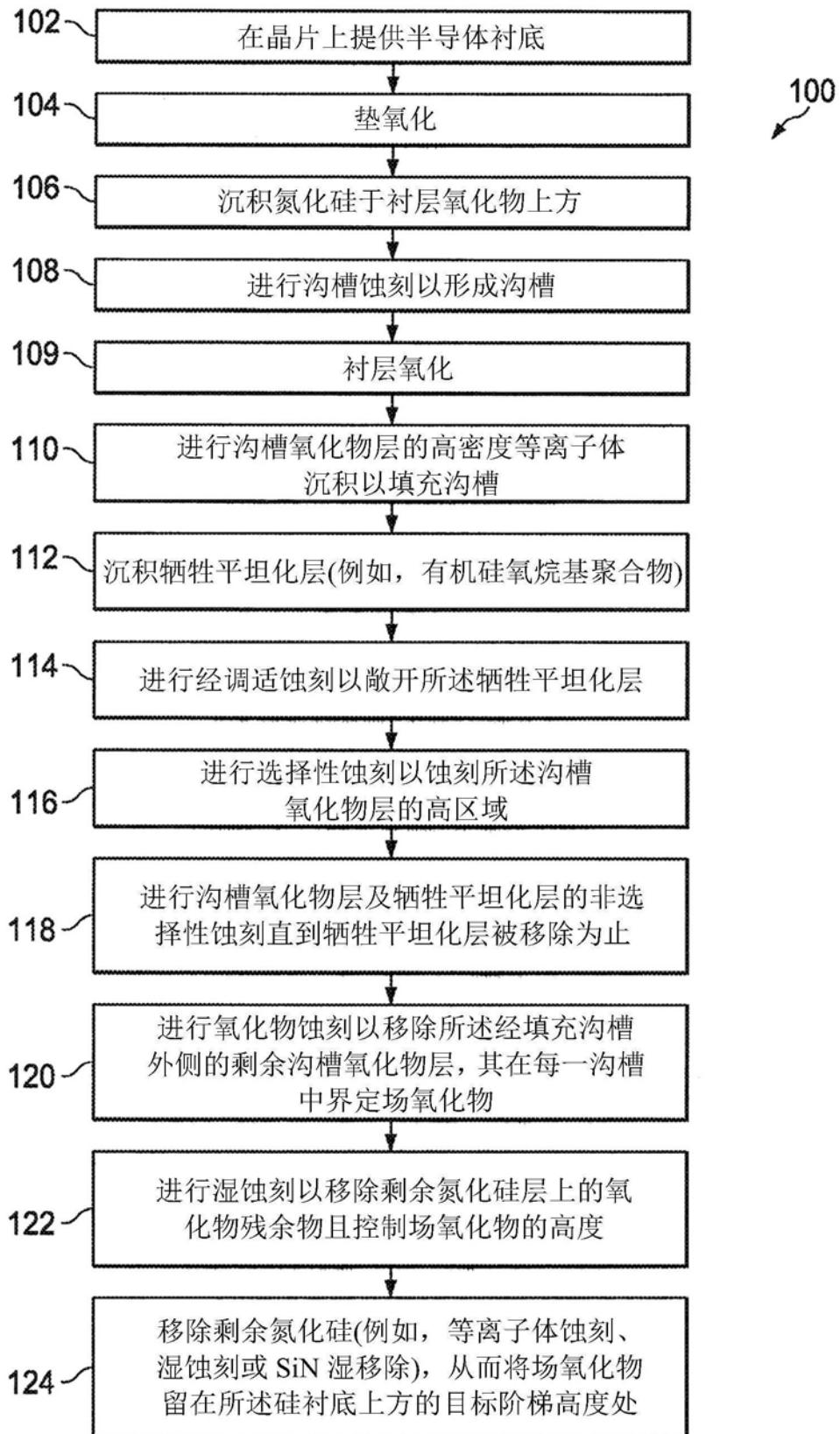

[0011] 图2是根据实例实施例的对应于图1A到1H中所说明的过程形成用于集成电路(例如，CMOS装置)的浅沟槽隔离的实例方法的流程图；

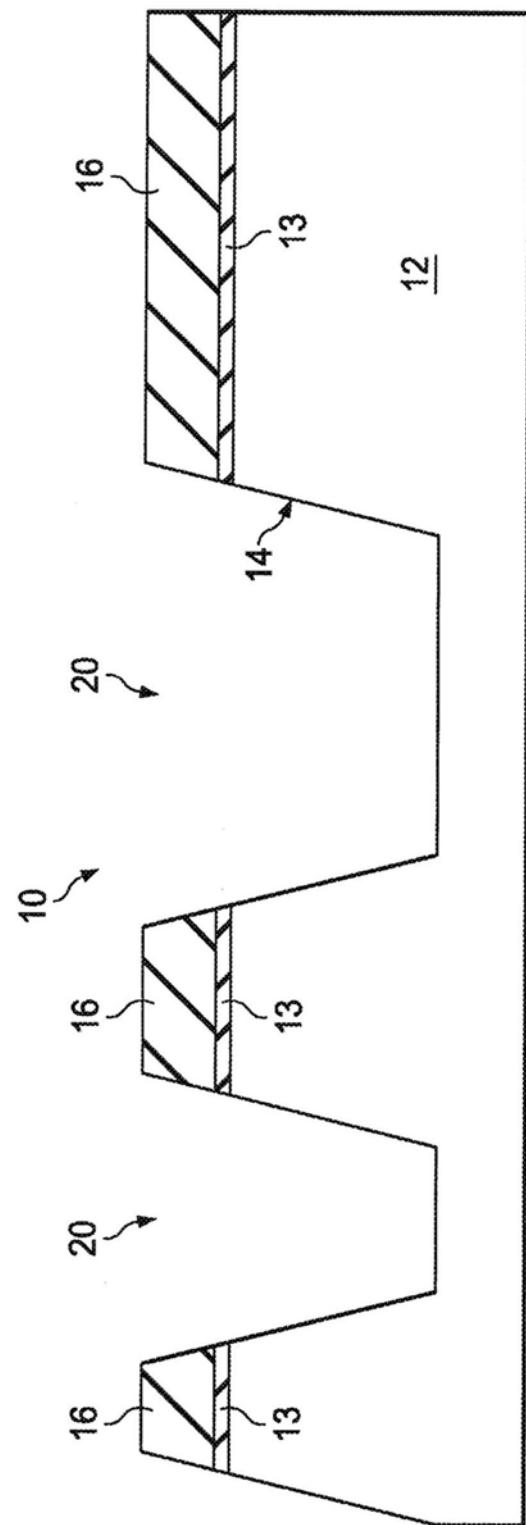

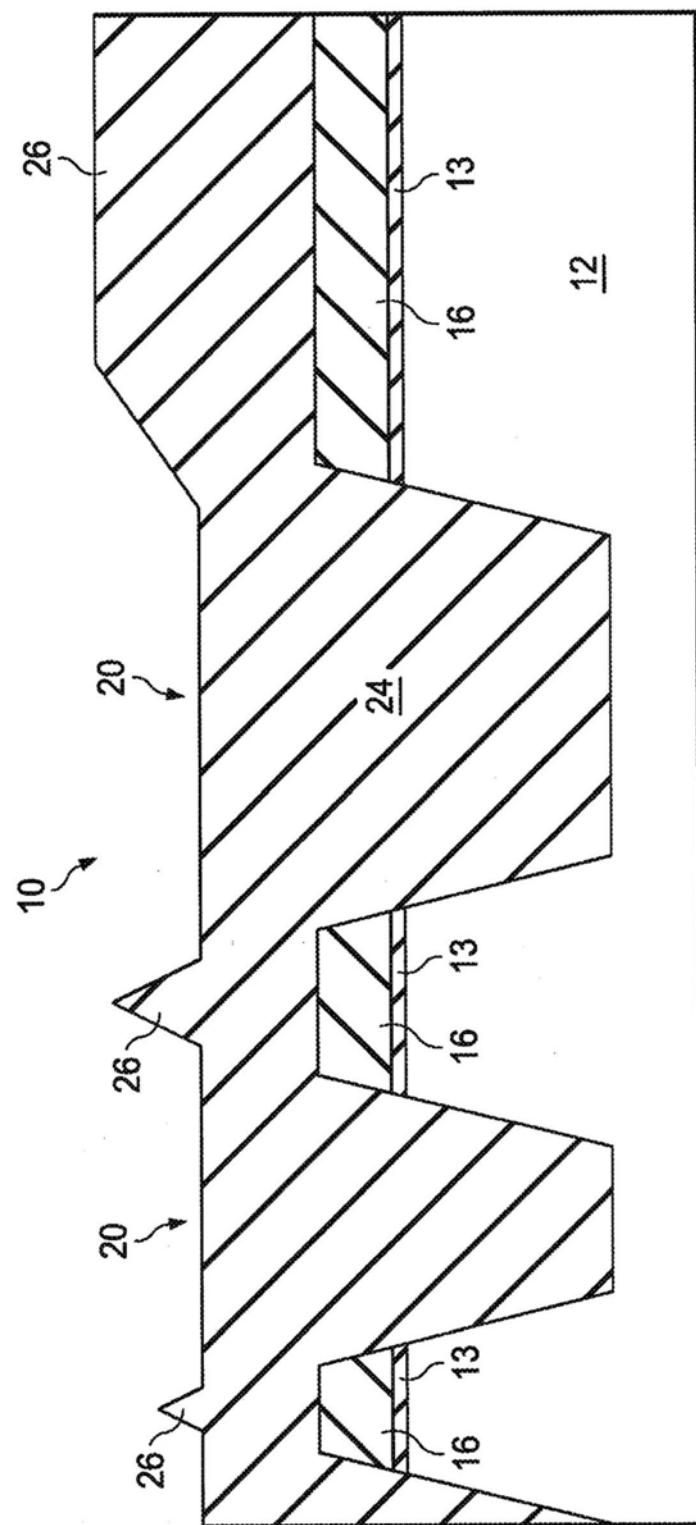

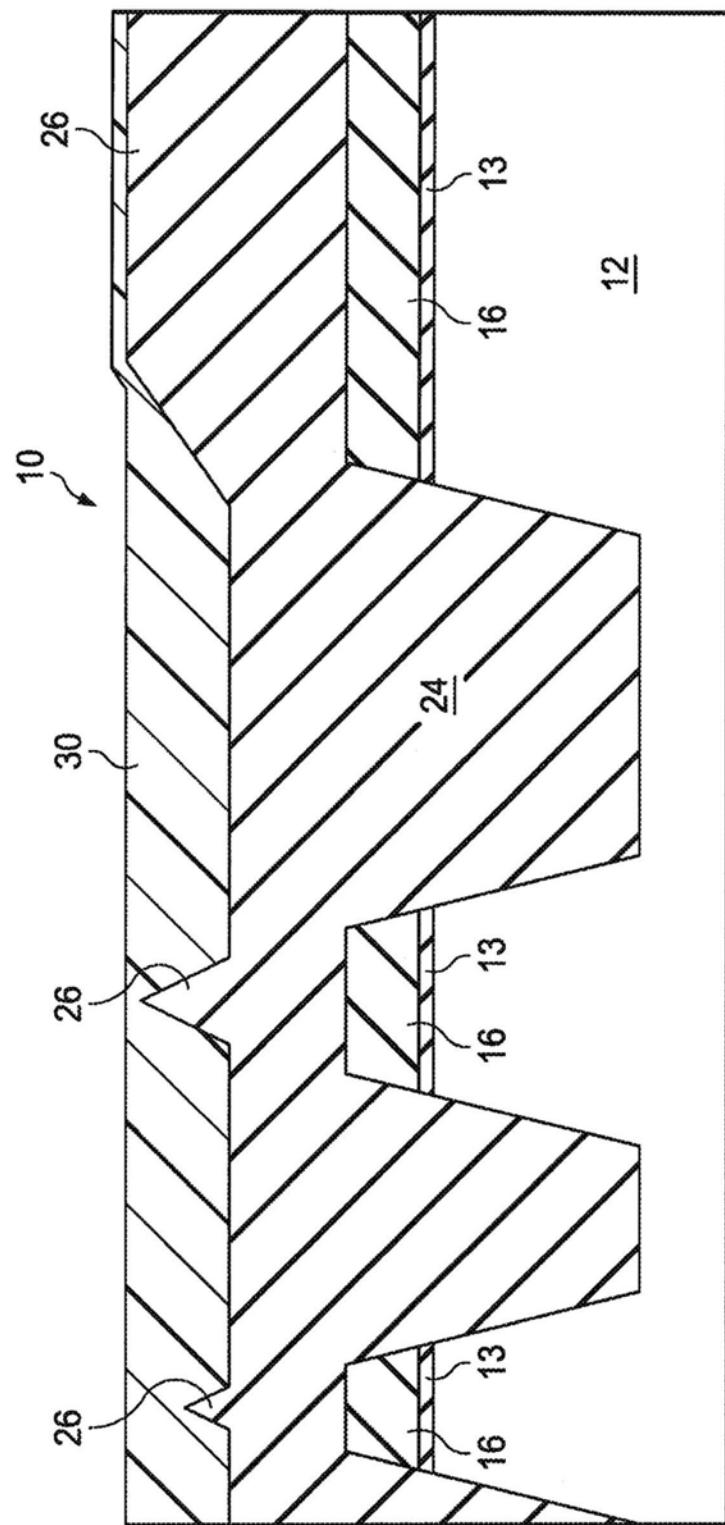

[0012] 图3A到3H说明根据本发明的实例实施例的另一实例半导体集成电路结构的横截面，其展示形成用于集成电路的沟槽隔离结构(例如，STI)的逐步过程；及

[0013] 图4是根据实例实施例的对应于图3A到3H中所说明的过程形成用于集成电路(例如，CMOS装置)的浅沟槽隔离的实例方法的流程图。

## 具体实施方式

[0014] 根据本发明的教示，可在不使用CMP及/或在与常规技术相比运用减小数目的步骤的情况下形成沟槽隔离结构，例如，浅沟槽隔离(STI)。此过程可减少或消除与CMP处理相关的一或多个问题，及/或可降低形成STI的成本及复杂度。

[0015] 现参考图式，示意地说明特定实例实施例的细节。图式中的相同元件将由相同数字表示，且类似元件将由具有不同小写字母后缀的相同数字表示。

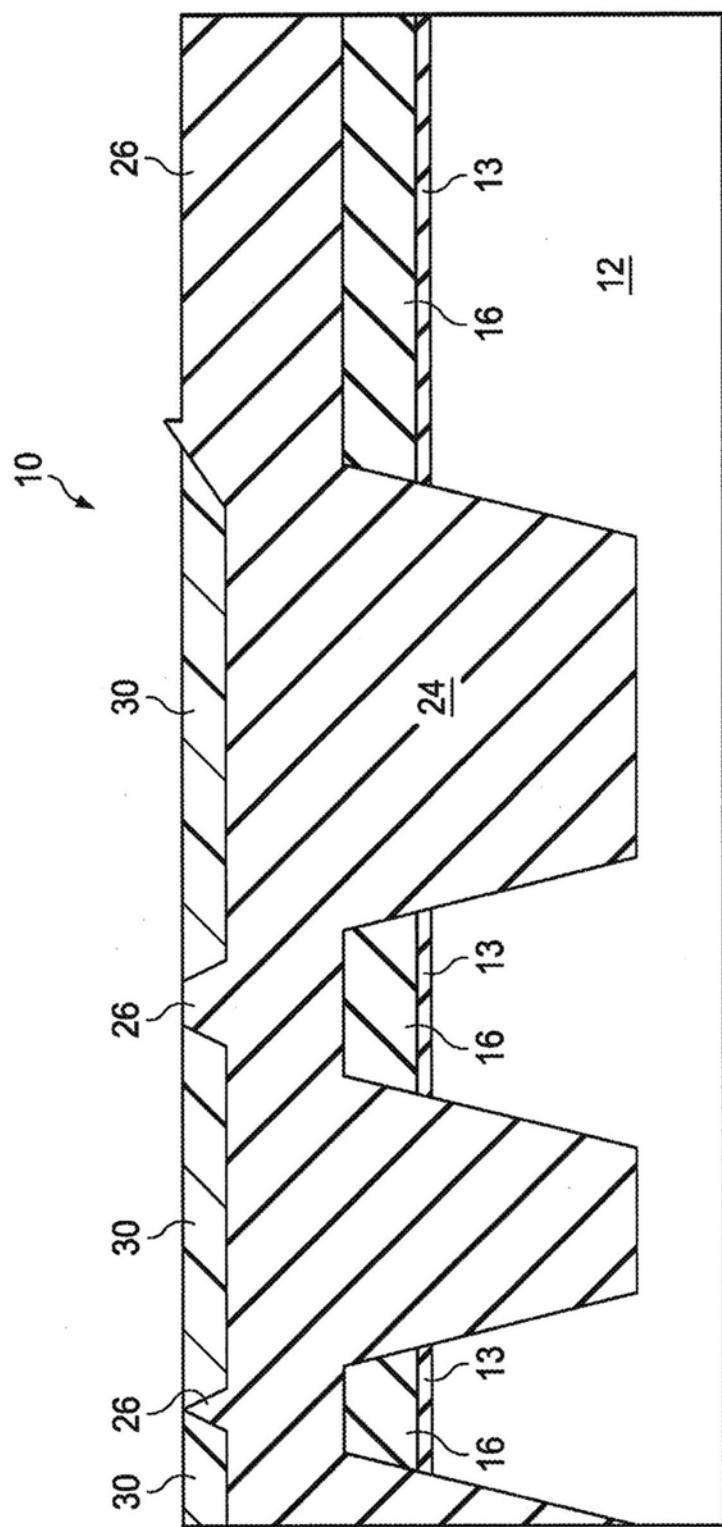

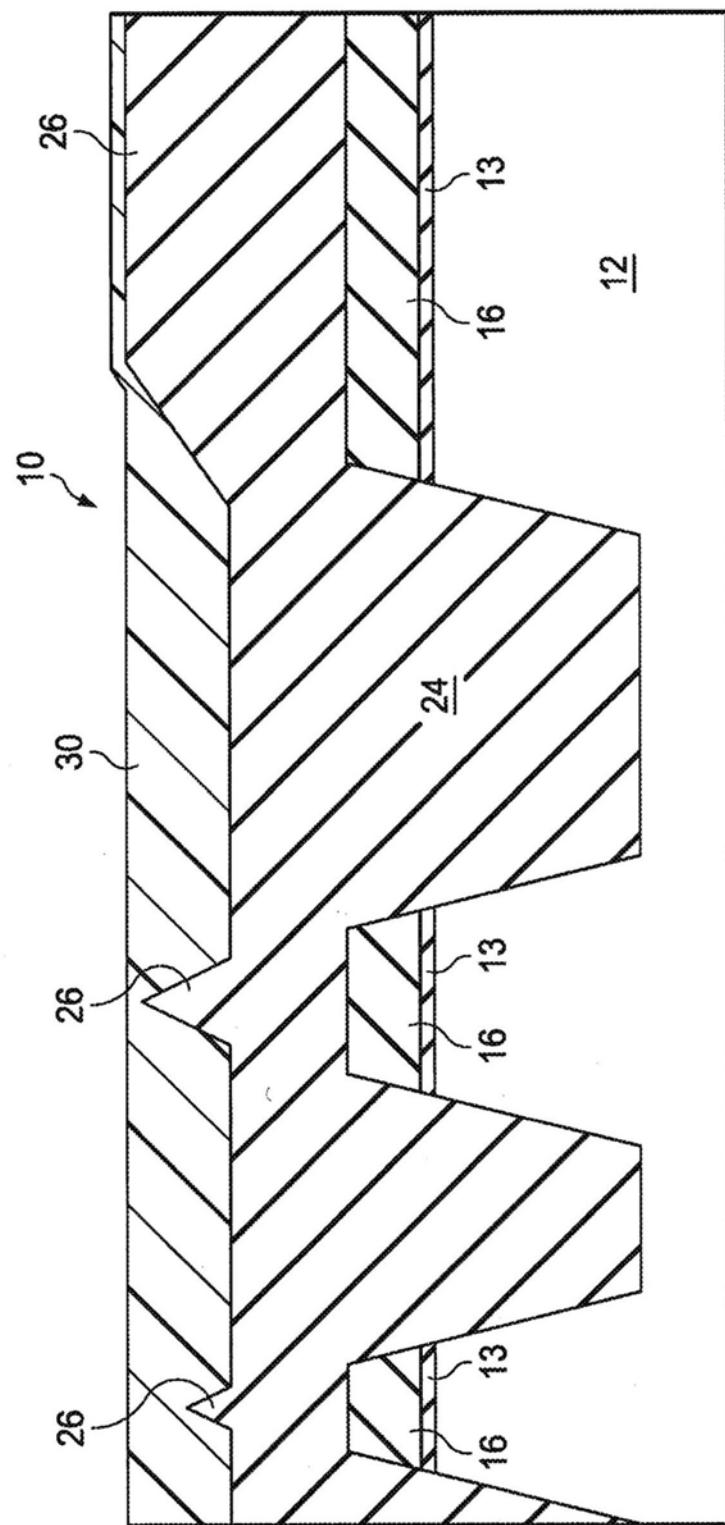

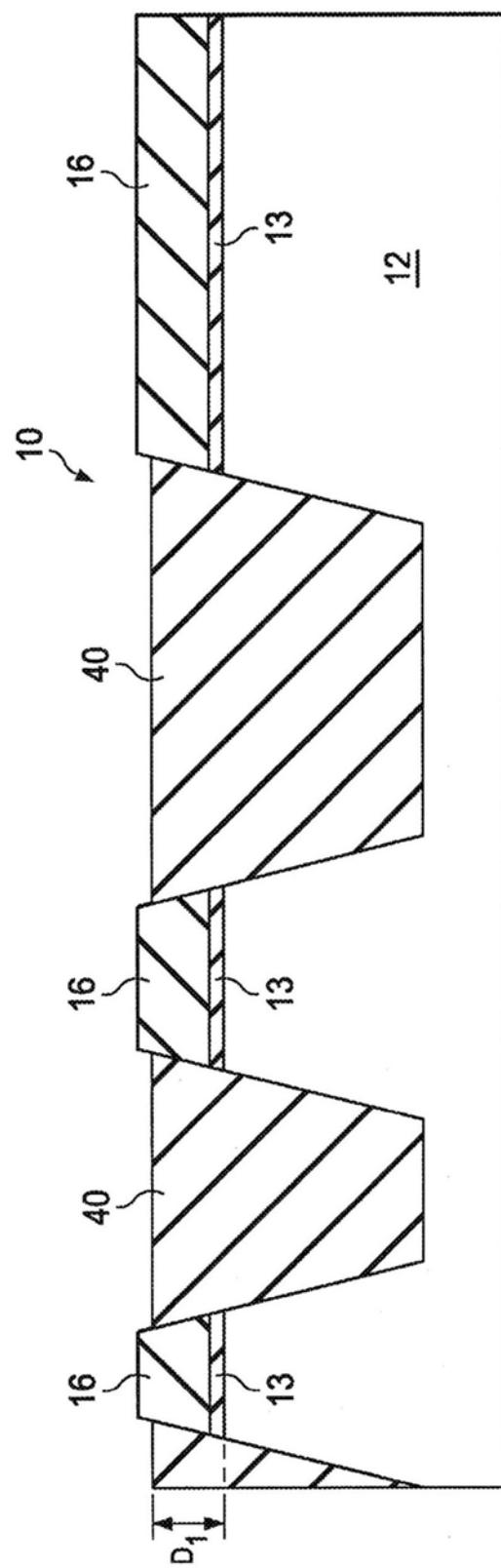

[0016] 图1A到1H说明根据实例实施例的形成用于集成电路(例如，CMOS装置)的沟槽隔离结构(例如，STI)的实例过程的步骤。

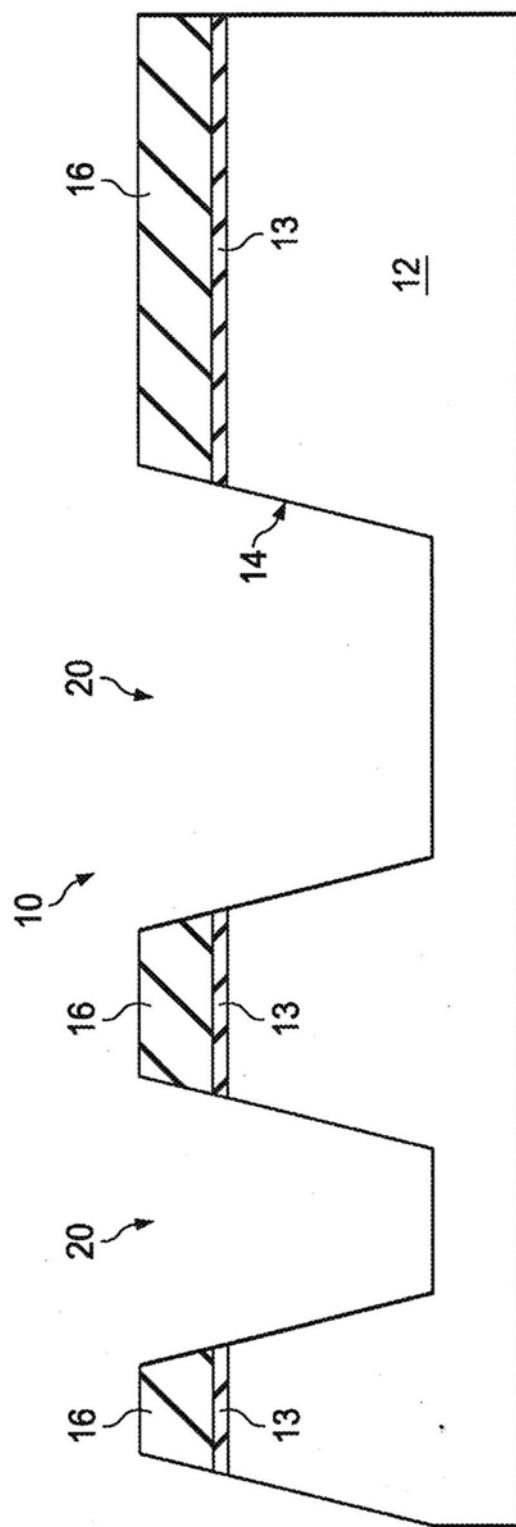

[0017] 如图1A中所展示，集成电路结构10包含形成于晶片表面上的半导体衬底12，例如，硅(Si)衬底。形成或沉积氧化物层13(例如，二氧化硅(SiO<sub>2</sub>)的薄垫氧化物层)于半导体衬底12上方以帮助对氮化物加应力/将其粘附到衬底。沉积氮化物层16(例如，氮化硅(SiN))于垫氧化物层13上方，且穿透氮化物层16、垫氧化物层13及半导体衬底12的部分执行沟槽蚀刻工艺(例如，STI蚀刻)以使用任何合适光刻技术形成一或多个沟槽20。氧化物层13可在氮化物层16之前形成或沉积以帮助对氮化物加应力/将其粘附到衬底，且可具有经沉积氮化物层16的厚度的约1/10的厚度。在蚀刻之后，衬层氧化可在半导体衬底12的经曝露表面上形成衬层氧化物层14。

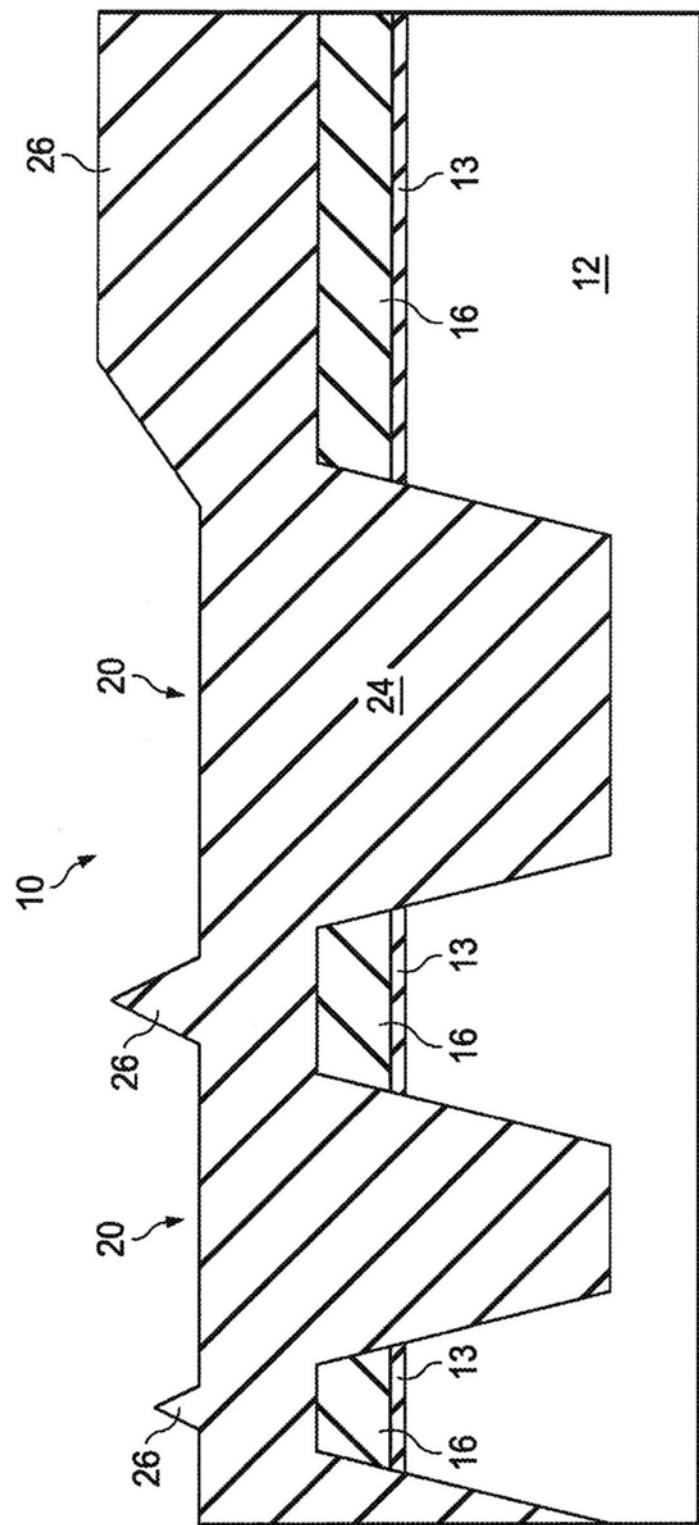

[0018] 如图1B中所展示，沉积沟槽氧化物层24(例如，二氧化硅(SiO<sub>2</sub>))于所述结构上方，

且所述沟槽氧化物层延伸到每一沟槽20中以形成经填充沟槽。在一些实施例中,通过高密度等离子体化学气相沉积(HDP CVD)沉积沟槽氧化物层24。如所展示,经沉积沟槽氧化物层24可例如归因于下伏结构的拓扑而具有非平坦拓扑。特定来说,沟槽氧化物层24的拓扑可界定数个向上突出或延伸特征或区域26。

[0019] 如图1C中所展示,沉积牺牲平坦化层30于沟槽氧化物层24上方。牺牲平坦化层30对沟槽氧化物层24具有蚀刻选择性。在一些实施例中,所述平坦化层包括有机硅酸盐。举例来说,平坦化层30可包括有机硅氧烷基聚合物,例如具有化学式 $R_xCH_3ySiO_z$ 的有机硅氧烷基聚合物,其中R是有机生色团。在实例实施例中,牺牲平坦化层30包括由霍尼韦尔电子材料(地址为新泽西州07960莫里斯敦哥伦比亚路101)供应的DUO<sup>TM</sup> 193或DUO<sup>TM</sup> 248抗反射涂层。可以任何合适方式沉积平坦化层30。在一些实施例中,将平坦化层30旋涂于沟槽氧化物层24上方,这提供部分平坦化效应。

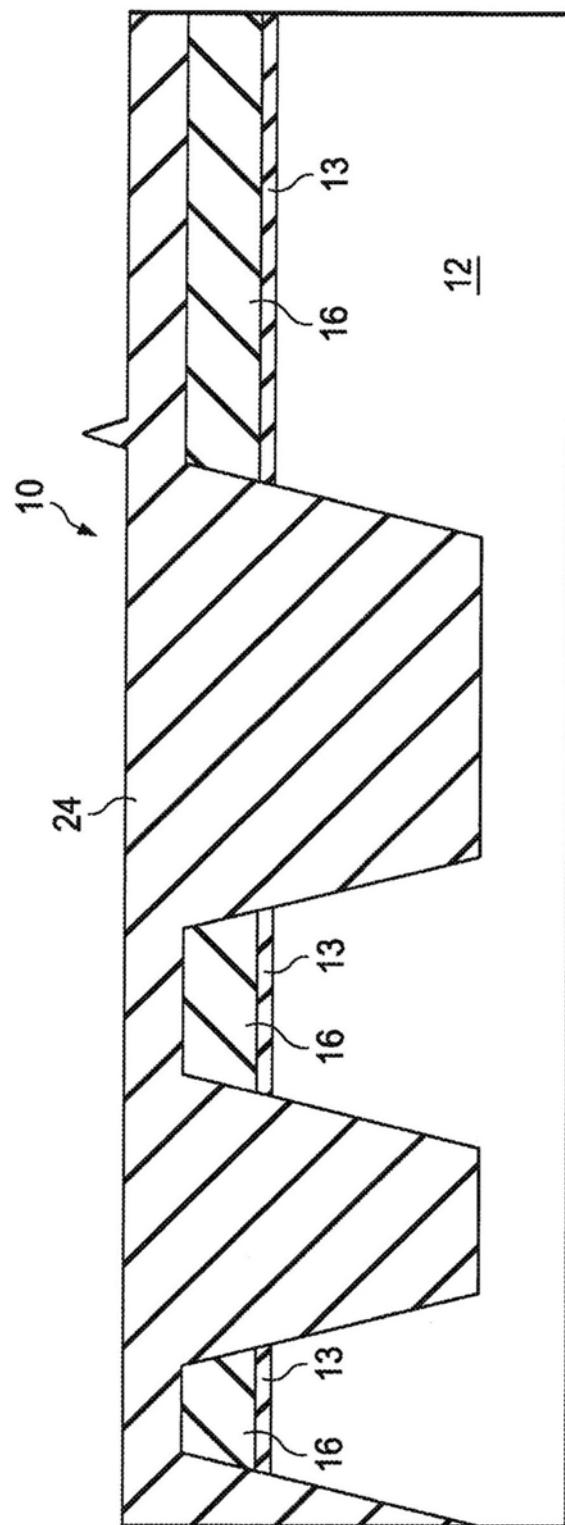

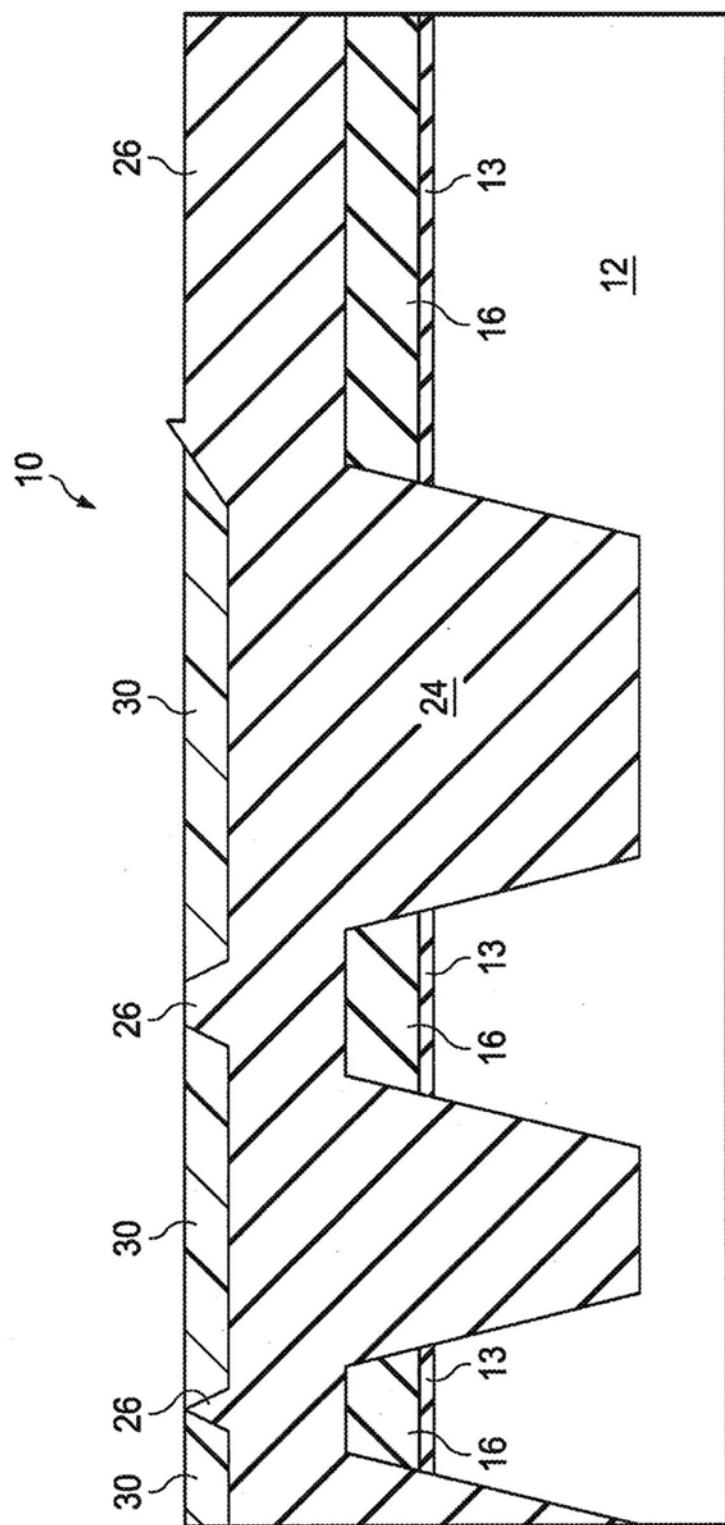

[0020] 接着执行平坦化蚀刻工艺以移除牺牲平坦化层30,且例如通过减少或消除向上突出或延伸特征或区域26而减小沟槽氧化物层24的上表面中的表面变化。所述平坦化蚀刻工艺可包含单蚀刻工艺或一系列不同蚀刻工艺。在下文所论述的实例中,图1D及1E中所展示的平坦化蚀刻工艺涉及三个不同蚀刻。

[0021] 参考图1D,在氧化物蚀刻器中蚀刻晶片,首先运用经调适蚀刻来敞开所述平坦化层且接着运用对沟槽氧化物层24具有选择性的短氧化物蚀刻。第二蚀刻将造成向上突出氧化物区域26被蚀刻,而氧化物层24的下部场区域受牺牲平坦化层30保护。在一个实施例中,第二蚀刻在最高点26与整体平坦化层30大致上齐平时停止。

[0022] 在本档案中,与第二物质/层相比更快地蚀穿第一物质/层的蚀刻工艺被称作对所述第一物质/层的“选择性”高于所述第二物质/层。

[0023] 参考图1E,接着执行对沟槽氧化物层24及牺牲平坦化层30不具选择性的第三蚀刻,以以类似速率移除沟槽氧化物层24及牺牲平坦化层30,直到平坦化层30被移除为止。此蚀刻可在到达氮化物层16之前停止,如图1E中所展示。

[0024] 如图1F中所展示,接着执行对沟槽氧化物层24具有高度选择性的氧化物蚀刻以移除经填充沟槽20外侧的沟槽氧化物层24的剩余部分,借此在每一沟槽20中界定场氧化物40。在一些实施例中,执行定义量的过度蚀刻,其可使场氧化物40沟槽化且清除剩余氮化物层16上的任何残余物。

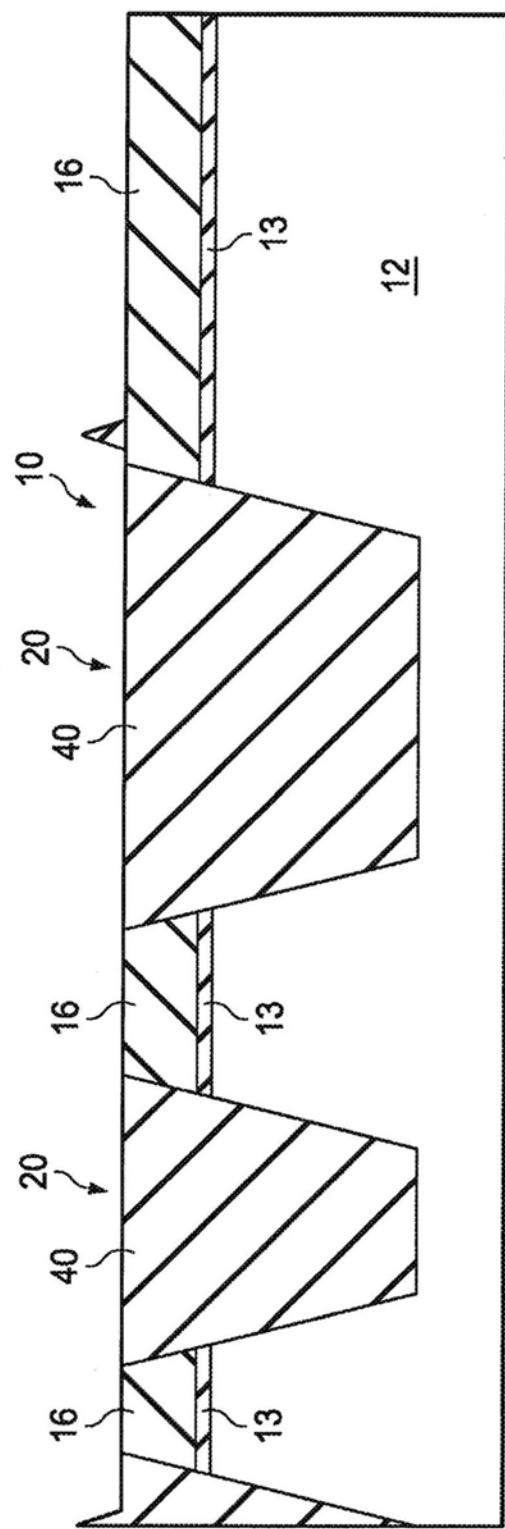

[0025] 如图1G中所展示,执行任选湿蚀刻以移除氮化物层16上的氧化物残余物及/或控制场氧化物40的高度。所述湿蚀刻可经设计以提供场氧化物40相对于衬底12顶部的定义高度(图1G中被指示为距离D<sub>1</sub>),所述高度可经选择以便基于与后续处理步骤相关联的高度减小的了解提供场氧化物40的最终高度(图1H中被指示为距离D<sub>2</sub>)。

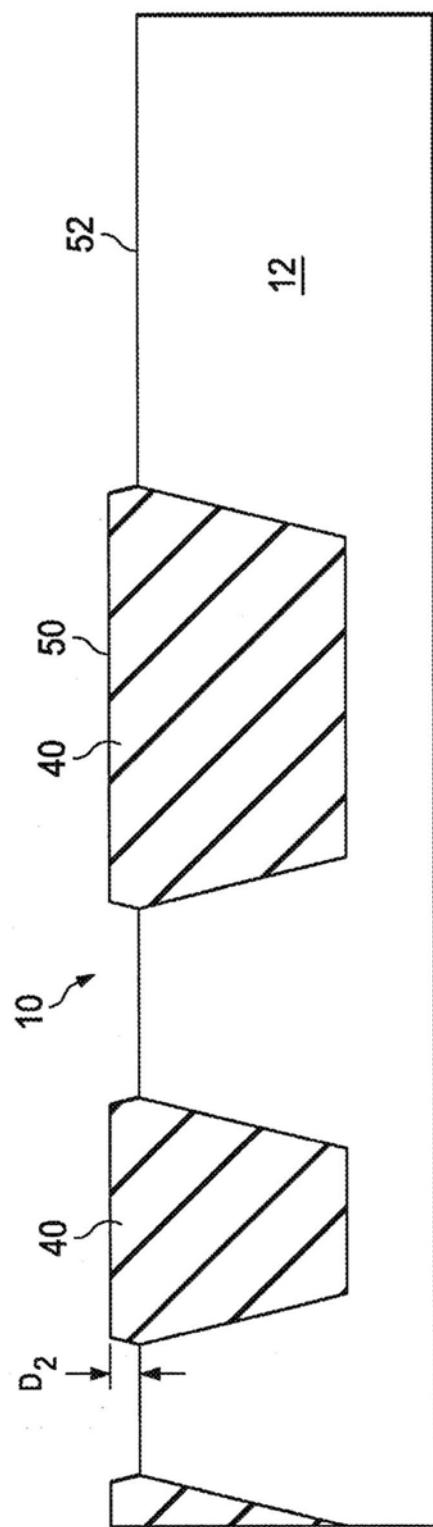

[0026] 如图1H中所展示,接着使用任何合适移除过程(例如,通过对氮化物层16的选择性高于场氧化物40及衬底12的材料的蚀刻)移除氮化物层16。如所展示,剩余场氧化物40(即,沟槽隔离结构)可突出于半导体衬底12的经曝露上表面上方达被指示为D<sub>2</sub>的目标阶梯高度(即,场氧化物40的顶部表面相对于衬底12的顶部表面52的高度)。在一些实施例中,可根据需要通过执行任何合适工艺(例如,等离子体蚀刻、湿蚀刻)或通过运行长湿移除工艺(例如,湿SiN移除)来移除氮化物层16的剩余部分而控制阶梯高度D<sub>2</sub>及/或场氧化物40的顶部形状。

[0027] 因此,在一些实施例中,可在不使用任何化学机械平坦化(CMP)工艺的情况下形成沟槽隔离结构40(例如,STI),其可提供如上文所论述的各种优点。如果跳过任选湿蚀刻,那么也可运用其余平坦化蚀刻就地执行氮化物移除步骤,借此进一步减少步骤的总数目。

[0028] 图2是根据对应于图1A到1H的实例实施例的形成用于集成电路(例如,CMOS装置)的浅沟槽隔离的实例方法100的流程图。在步骤102处,在晶片上形成硅衬底。在步骤104处,垫氧化过程形成垫氧化物于所述硅衬底的表面上方。在步骤106处,沉积氮化硅层于所述硅衬底上方。在步骤108处,执行沟槽蚀刻(例如,STI蚀刻)以形成多个沟槽。在步骤109处,衬层氧化过程在所述经形成沟槽中形成衬层氧化物。在步骤110处,通过高密度等离子体化学气相沉积(HDP CVD)沉积二氧化硅层(沟槽氧化物层)于所述晶片上方,其填充所述经蚀刻沟槽。所述经沉积二氧化硅层可例如归因于下伏结构的拓扑而具有非平坦拓扑。特定来说,所述二氧化硅层可界定数个向上突出或延伸特征或区域。

[0029] 在步骤112处,沉积有机硅氧烷基聚合物(例如,DUO<sup>TM</sup> 193或DUO<sup>TM</sup> 248)的牺牲平坦化层于所述二氧化硅层上方。在步骤114处,执行经调适蚀刻以敞开所述牺牲平坦化层,接着在步骤116处执行对所述二氧化硅层具有选择性的短氧化物蚀刻。步骤116处的蚀刻可至少部分蚀刻二氧化硅的向上突出区域,而二氧化硅的下部区域受所述牺牲平坦化层保护。在步骤118处,执行非选择性蚀刻以以类似速率蚀穿所述二氧化硅层及所述牺牲平坦化层,直到所述牺牲平坦化层被移除为止。此蚀刻可在到达下伏氮化硅层之前停止。

[0030] 在步骤120处,接着执行对二氧化硅具有高度选择性的氧化物蚀刻以移除经填充沟槽上方及外侧的二氧化硅层的部分,借此在每一沟槽中界定场氧化物。在一些实施例中,执行定义量的过度蚀刻,其可使场氧化物沟槽化且清除剩余氮化硅层上的任何残余物。在步骤122处,执行任选湿蚀刻以移除剩余氮化硅层上的氧化物残余物及/或控制场氧化物的高度。在步骤124处,使用任何合适移除工艺(例如,对氮化硅的选择性高于二氧化硅场氧化物及硅衬底的蚀刻)移除氮化硅层。剩余场氧化物(即,沟槽隔离结构)可突出于硅衬底的经曝露表面上方达目标阶梯高度,所述高度可根据需要使用任何合适精整过程控制或塑形。

[0031] 因此,以此方式,可在不使用任何化学机械平坦化(CMP)工艺的情况下形成浅沟槽隔离,其可提供如上文所论述的各种优点。

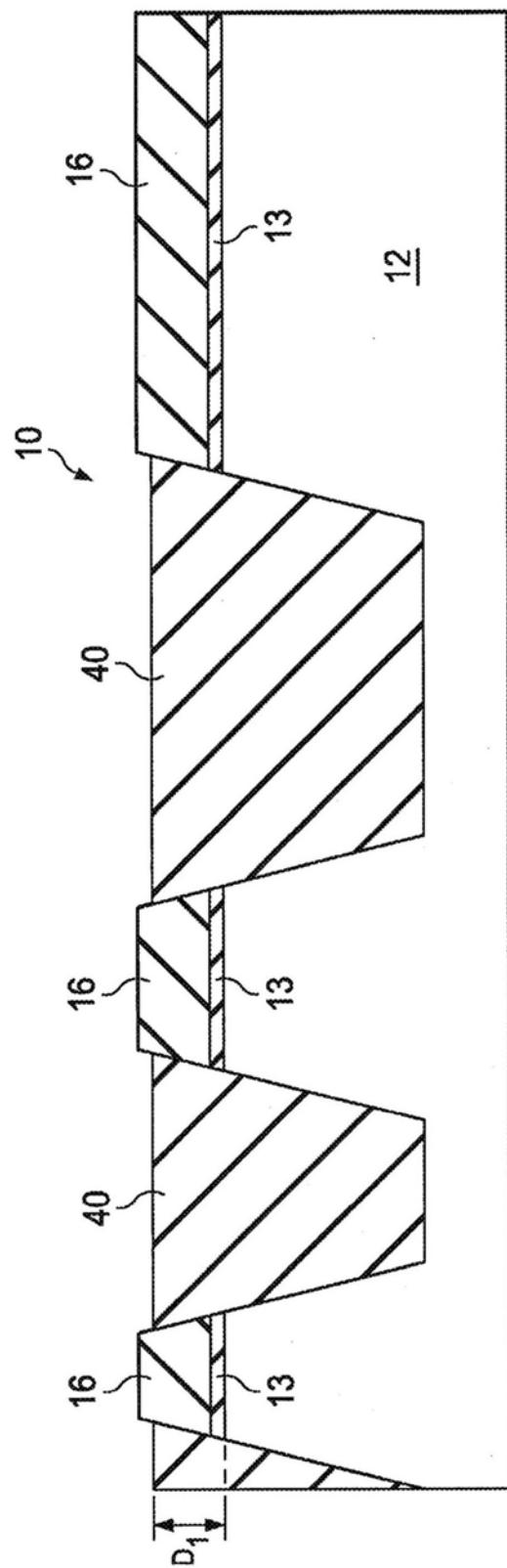

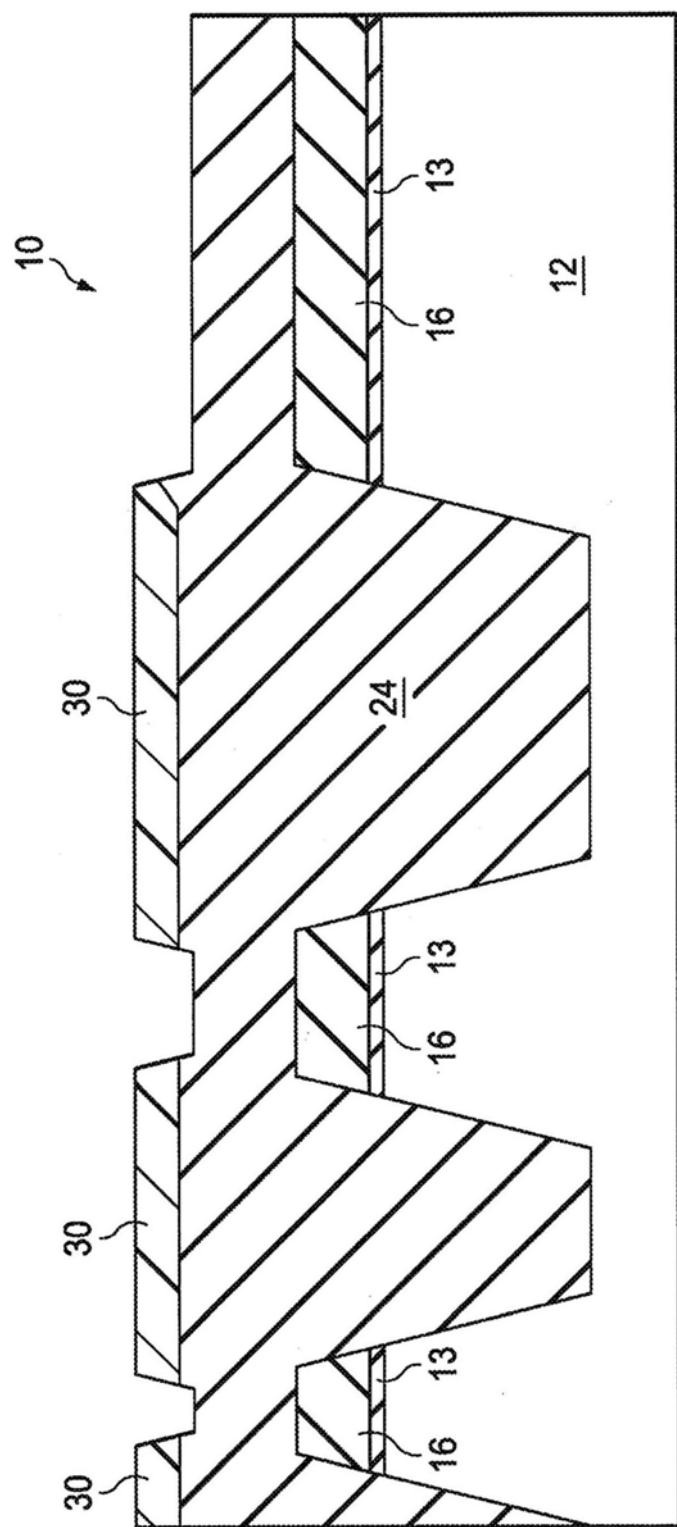

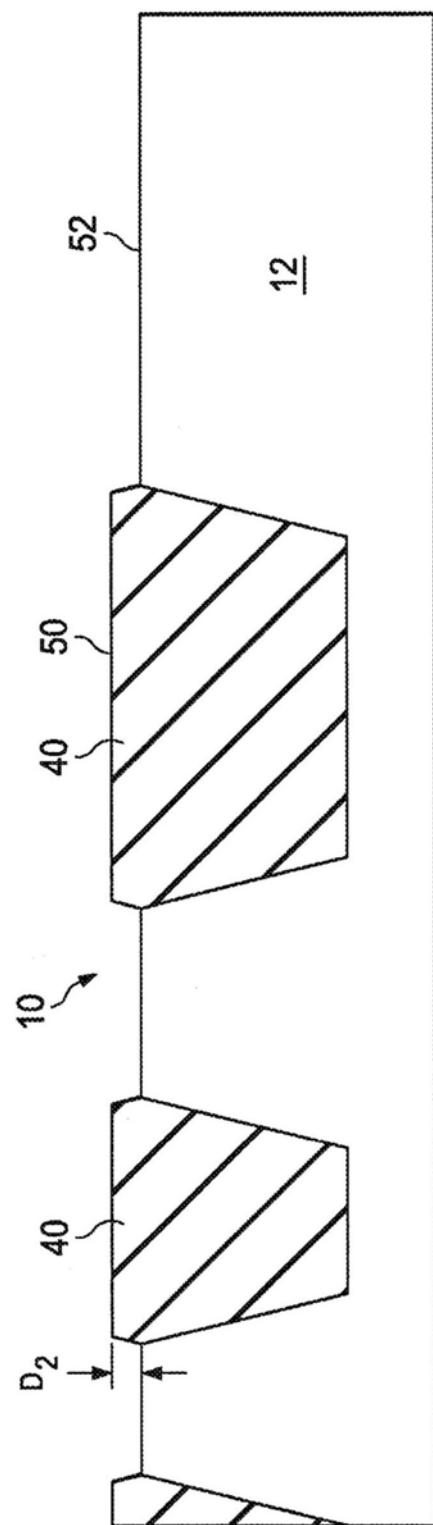

[0032] 图3A到3H说明用于形成用于集成电路(例如,CMOS装置)的沟槽隔离结构(例如,STI)的过程的另一实例实施例的步骤。

[0033] 所述过程的初始步骤可类似于上文所论述的实施例所述步骤。因此,对应于图3A到3C的步骤可类似于上文所论述的图1A到1C的所述步骤。

[0034] 如图3A中所展示,集成电路结构10包含形成于晶片表面上的半导体衬底12,例如,硅(Si)衬底。形成或沉积氧化物层13(例如,二氧化硅(SiO<sub>2</sub>)的薄垫氧化物层)于半导体衬底12上方以帮助对氮化物加应力/将其粘附到衬底。沉积氮化物层16(例如,氮化硅(SiN))于垫氧化物层13上方,且穿透氮化物层16、垫氧化物层13及半导体衬底12的部分执行沟槽蚀刻工艺(例如,STI蚀刻)以使用任何合适光刻技术形成一或多个沟槽20,例如,如上文参考图1A所论述。在蚀刻之后,衬层氧化可在半导体衬底12的经曝露表面上形成衬层氧化物层14。

[0035] 如图3B中所展示,沟槽氧化物层24(例如,二氧化硅(SiO<sub>2</sub>))沉积于所述结构上方,

且所述沟槽氧化物层延伸到每一沟槽20中以形成经填充沟槽。在一些实施例中,通过高密度等离子体化学气相沉积(HDP CVD)沉积沟槽氧化物层24。如所展示,经沉积沟槽氧化物层24可例如归因于下伏结构的拓扑而具有非平坦拓扑。特定来说,沟槽氧化物层24的拓扑可界定数个向上突出或延伸特征或区域26。

[0036] 如图3C中所展示,沉积牺牲平坦化层30于沟槽氧化物层24上方。牺牲平坦化层30对沟槽氧化物层24具有蚀刻选择性。在一些实施例中,所述平坦化层包括有机硅酸盐。举例来说,平坦化层30可包括有机硅氧烷基聚合物,例如具有化学式 $R_xCH_3ySiO_z$ 的有机硅氧烷基聚合物,其中R是有机生色团。在实例实施例中,牺牲平坦化层30可包括DUO<sup>TM</sup> 193或DUO<sup>TM</sup> 248抗反射涂层,例如,如上文参考图1A所论述。可以任何合适方式沉积平坦化层30。在一些实施例中,将平坦化层30旋涂于沟槽氧化物层24上方,这提供部分平坦化效应。

[0037] 接着执行一系列蚀刻以在沟槽20中形成沟槽隔离结构,如下文所论述,其在形成沟槽隔离结构的过程中,移除牺牲平坦化层30,且例如通过减少或消除向上突出或延伸特征或区域26而减小沟槽氧化物层24的上表面中的表面变化。

[0038] 参考图3D,执行大体上非选择性蚀刻(例如,在使用DUO<sup>TM</sup>涂层的实施例中其可称为DUO蚀刻),其以相同或大致上相同速率蚀刻沟槽氧化物层24及牺牲平坦化层30,例如,DUO<sup>TM</sup>涂层(及氮化物层16,如果相关)。此大体上非选择性蚀刻可将牺牲平坦化层30的部分留在所述结构的低洼区域中,例如,在沟槽20上方,如图3D中所展示。所述蚀刻可移除沟槽氧化物层24的向上突出氧化物区域26的部分,而氧化物层24的下部场区域受牺牲平坦化层30保护。在一个实施例中,第二蚀刻在最高点26与整体平坦化层30大致上齐平时停止。

[0039] 参考图3E,执行对沟槽氧化物层24的选择性高于牺牲平坦化层30及氮化物层16的氧化物蚀刻。如所展示,所述氧化物蚀刻可将牺牲平坦化层30留在沟槽区域上方,而将图3D中所展示的区域26(例如,在氮化物层16的区域上方)蚀刻到牺牲平坦化层30的区域下方的深度。

[0040] 参考图3F,接着执行第二非选择性或大体上非选择性清理蚀刻,其可平坦化剩余牺牲平坦化层30且剩余牺牲平坦化层30从所有区域(特定来说沟槽20(场氧化物)上方)移除。在一些实施例中,此蚀刻可在到达氮化物层16之前停止,如图3E中所展示。

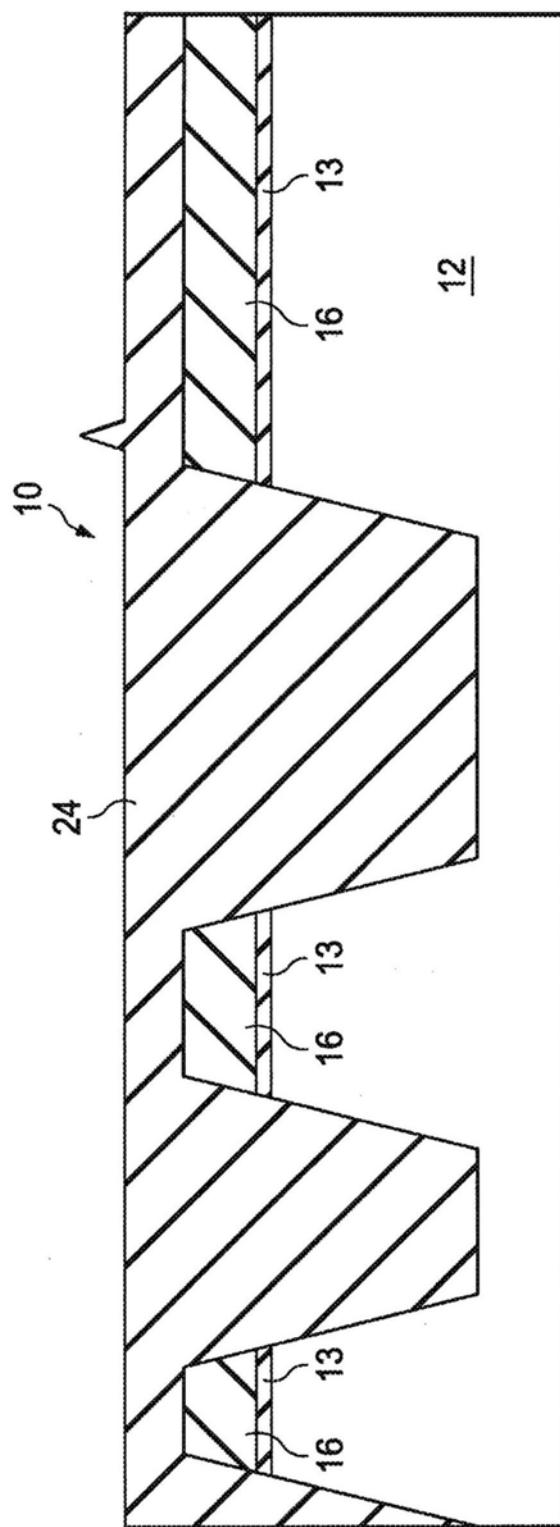

[0041] 如图3G中所展示,接着执行对沟槽氧化物层24的选择性高于牺牲平坦化层30及氮化物层16的氧化物蚀刻以移除经填充沟槽20外侧的沟槽氧化物层24的剩余部分,借此将场氧化物40界定于每一沟槽20中。在一些实施例中,执行定义量的过度蚀刻,其可使场氧化物40沟槽化,借此设置最终场氧化物高度且清除剩余氮化物层16上的任何残余物。

[0042] 如图3H中所展示,接着使用任何合适移除工艺(例如,通过对氮化物层16的选择性高于场氧化物40及衬底12的材料的蚀刻(例如,SiN蚀刻))移除氮化物层16。如所展示,剩余场氧化物40(即,沟槽隔离结构)可突出于半导体衬底12的经曝露上表面上方达被指示为D<sub>2</sub>的目标阶梯高度(即,场氧化物40的顶部表面相对于衬底12的顶部表面52的高度)。在一些实施例中,可根据需要通过执行任何合适工艺(例如,等离子体蚀刻、湿蚀刻)或通过运行长湿移除工艺(例如,湿SiN移除)来移除氮化物层16的剩余部分而控制阶梯高度D<sub>2</sub>及/或场氧化物40的顶部形状。

[0043] 因此,在一些实施例中,可在不使用任何化学机械平坦化(CMP)工艺的情况下形成沟槽隔离结构40(例如,STI),其可提供如上文所论述的各种优点。如果跳过任选湿蚀刻,那

么也可运用其余平坦化蚀刻就地执行氮化物移除步骤,借此进一步减少步骤的总数目。

[0044] 在其中图3G中所展示的氧化物蚀刻被跳过或包含于平坦化蚀刻工艺中的一些实施例中,可运用平坦化蚀刻工艺就地完成图3H中所展示的最终氮化物蚀刻。

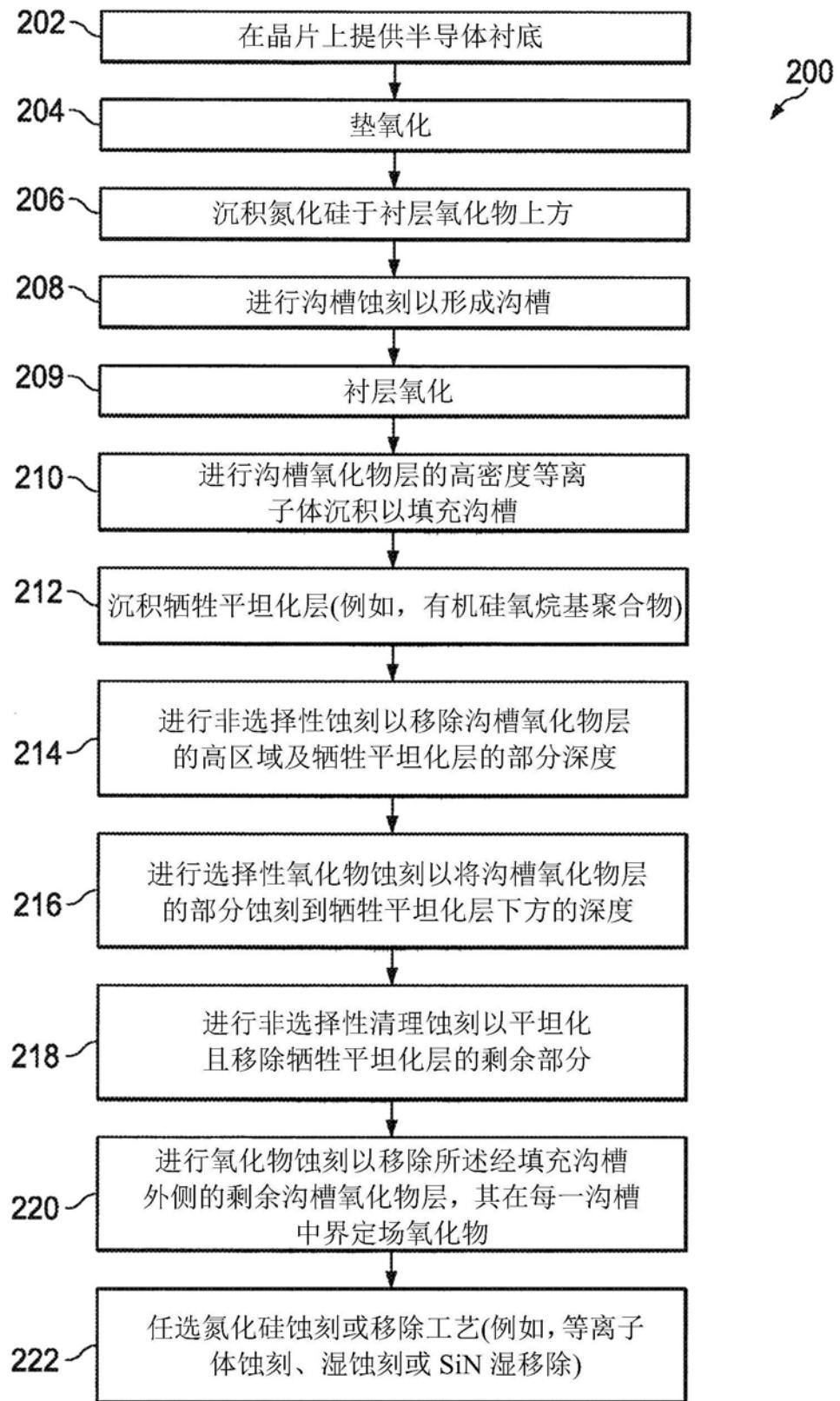

[0045] 图4是根据对应于图3A到3H的实例实施例的形成用于集成电路(例如,CMOS装置)的浅沟槽隔离的实例方法200的流程图。

[0046] 步骤202到210:在步骤202处,在晶片上形成硅衬底。在步骤204处,垫氧化过程在所述硅衬底的表面上方形成氧化垫。在步骤206处,沉积氮化硅层于所述硅衬底上方。在步骤208处,执行沟槽蚀刻(例如,STI蚀刻)以形成多个沟槽。在步骤209处,衬层氧化过程在所述经形成沟槽中形成衬层氧化物。在步骤210处,通过高密度等离子体化学气相沉积(HDP CVD)沉积二氧化硅层(沟槽氧化物层)于所述晶片上方,其填充所述经蚀刻沟槽。所述经沉积二氧化硅层可例如归因于下伏结构的拓扑而具有非平坦拓扑。特定来说,所述二氧化硅层可界定数个向上突出或延伸特征或区域。

[0047] 在步骤212处,沉积有机硅氧烷基聚合物(例如,DUO<sup>TM</sup> 193或DUO<sup>TM</sup> 248)的牺牲平坦化层于所述二氧化硅层上方。在步骤214处,执行非选择性蚀刻(例如,DUO蚀刻)以移除二氧化硅层的高或向上突出区域且以移除所述牺牲平坦化层的部分深度。步骤214处的蚀刻可至少部分蚀刻二氧化硅的向上突出区域,而二氧化硅的下部区域受所述牺牲平坦化层保护。在步骤216处,执行选择性氧化物蚀刻以将二氧化硅层的部分蚀刻到剩余牺牲平坦化层下方的深度。在步骤218处,执行非选择性“清理”蚀刻以平坦化所述结构且移除牺牲平坦化层的任何剩余部分,特定来说在沟槽(场氧化物)上方。此蚀刻可在到达下伏氮化硅层之前停止。

[0048] 在步骤220处,接着执行对二氧化硅具有高度选择性的氧化物蚀刻以移除经填充沟槽上方及外侧的二氧化硅层的部分,借此在每一沟槽中界定场氧化物。在一些实施例中,执行定义量的过度蚀刻,其可使场氧化物沟槽化且清除剩余氮化硅层上的任何残余物。在步骤222处,使用任何合适移除工艺(例如,对氮化硅的选择性高于二氧化硅场氧化物及硅衬底的SiN蚀刻)移除氮化硅层。剩余场氧化物(即,沟槽隔离结构)可突出于硅衬底的经曝露表面上方达目标阶梯高度,所述高度可根据需要使用任何合适精整过程控制或塑形。

[0049] 因此,以此方式,可在不使用任何化学机械平坦化(CMP)工艺的情况下形成浅沟槽隔离,其可提供如上文所论述的各种优点。

[0050] 尽管本发明中详细描述所揭示实施例,但应理解,可在不背离所述实施例的精神及范围的情况下对所述实施例作出各种改变、替代及更改。

图1A

图1B

图1C

图1D

图1E

图1F

图1G

图1H

图2

图3A

图3B

图3C

图3D

图3E

图3F

图3G

图3H

图4