(12)发明专利

(10)授权公告号 CN 105895646 B

(45)授权公告日 2019.03.12

(21)申请号 201610083928.X

(51)Int.CI.

(22)申请日 2016.02.05

H01L 27/146(2006.01)

(65)同一申请的已公布的文献号

申请公布号 CN 105895646 A

(56)对比文件

US 6091793 A, 2000.07.18,

(43)申请公布日 2016.08.24

WO 2008/096799 A1, 2008.08.14,

(30)优先权数据

JP 特开2011-61521 A, 2011.03.24,

JP2015-027924 2015.02.16 JP

审查员 马晓敏

(73)专利权人 佳能株式会社

地址 日本东京都大田区下丸子3丁目30-2

(72)发明人 小林昌弘 大贯裕介 小泉彻

(74)专利代理机构 北京怡丰知识产权代理有限公司 11293

代理人 迟军

权利要求书2页 说明书8页 附图14页

(54)发明名称

固态摄像设备

(57)摘要

本发明公开了一种固态摄像设备。所述固态摄像设备能够抑制在执行全局电子快门操作时可能会出现的图像质量的劣化。以靠近光电转换单元的方式来设置像素晶体管的栅极驱动线中的第一传输晶体管的栅极驱动线。

1. 一种具有图像传感区域的固态摄像设备，在所述图像传感区域中以矩阵形式排列多个像素，每个像素包括光电转换单元、用于传输所述光电转换单元中的电载流子的第一传输晶体管、用于累积从所述第一传输晶体管传输的电载流子的电载流子累积部、用于传输来自所述电载流子累积部的电载流子的第二传输晶体管、用于累积从所述第二传输晶体管传输的电载流子的浮置扩散部以及用于复位所述浮置扩散部的电势的复位晶体管，

所述固态摄像设备包括多个用于驱动多个像素晶体管的栅极的像素晶体管的栅极驱动线，每个所述像素晶体管包括所述第一传输晶体管、所述第二传输晶体管以及所述复位晶体管，所述栅极驱动线在一个布线层中在像素的行方向上延伸，

其中，在与所述像素的行对应设置的行(n-1)、行(n)和行(n+1)的驱动布线中，以靠近所述光电转换单元的方式来设置所述像素晶体管的栅极驱动线中的所述第一传输晶体管的栅极驱动线；

其中，以不相互靠近的方式来设置所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线。

2. 根据权利要求1所述的固态摄像设备，其中，所述固态摄像设备是正面照射的设备。

3. 根据权利要求1所述的固态摄像设备，其中，所述复位晶体管的栅极驱动线被设置在所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线之间。

4. 根据权利要求1所述的固态摄像设备，其中，行选择晶体管的栅极驱动线、电源线和接地线中的一个被设置在所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线之间。

5. 根据权利要求1所述的固态摄像设备，所述固态摄像设备还包括：

溢出晶体管，用于输出在所述光电转换单元中累积的电载流子，所述溢出晶体管被包括在所述像素晶体管中，

其中，所述溢出晶体管的栅极驱动线在与所述像素晶体管的栅极驱动线相同的布线层中在像素的行方向上延伸；以及

在与像素的行对应设置的行(n-1)、行(n)和行(n+1)的驱动布线中，以靠近所述光电转换单元的方式来设置所述溢出晶体管的栅极驱动线。

6. 根据权利要求5所述的固态摄像设备，其中，以不靠近的方式来设置所述第一传输晶体管的栅极驱动线和所述溢出晶体管的栅极驱动线。

7. 根据权利要求6所述的固态摄像设备，其中，所述复位晶体管的栅极驱动线被设置在所述第一传输晶体管的栅极驱动线和溢出晶体管的栅极驱动线之间。

8. 根据权利要求6所述的固态摄像设备，其中，行选择晶体管的栅极驱动线、电源线和接地线中的一个被设置在所述第一传输晶体管的栅极驱动线和所述溢出晶体管的栅极驱动线之间。

9. 根据权利要求5所述的固态摄像设备，其中，以不靠近的方式来设置所述溢出晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线。

10. 根据权利要求1所述的固态摄像设备，其中，所述像素晶体管的栅极驱动线被放置在所述电载流子累积部之上。

11. 一种具有图像传感区域的固态摄像设备，在所述图像传感区域中以矩阵形式排列多个像素，每个像素包括光电转换单元、用于传输所述光电转换单元中的电载流子的第一

传输晶体管、用于累积从所述第一传输晶体管传输的电载流子的电载流子累积部、用于传输来自所述电载流子累积部的电载流子的第二传输晶体管、用于累积从所述第二传输晶体管传输的电载流子的浮置扩散部以及用于复位所述浮置扩散部的电势的复位晶体管，

所述固态摄像设备包括多个像素晶体管的栅极驱动线，每个所述像素晶体管包括所述第一传输晶体管、所述第二传输晶体管以及复位晶体管，所述栅极驱动线在一个布线层中在像素的行方向上延伸，

其中，在与像素的行相对应地设置的行(n-1)、行(n)和行(n+1)的驱动布线中，所述第一传输晶体管的栅极驱动线和在所述第一传输晶体管的栅极驱动线的两侧设置的像素晶体管的栅极驱动线之间的布线距离的总和，大于除所述第一传输晶体管以外的像素晶体管的栅极驱动线和在所述除所述第一传输晶体管以外的像素晶体管的栅极驱动线的两侧设置的像素晶体管的栅极驱动线之间的布线距离的总和。

12. 根据权利要求11所述的固态摄像设备，其中，所述复位晶体管的栅极驱动线被设置在所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线之间。

13. 根据权利要求11所述的固态摄像设备，其中，行选择晶体管的栅极驱动线、电源线和接地线中的一个被设置在所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线之间。

14. 根据权利要求11所述的固态摄像设备，其中，所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线之间的布线距离是所述像素晶体管的栅极驱动线之间的布线距离中的最大布线距离。

15. 根据权利要求11所述的固态摄像设备，所述固态摄像设备还包括：

溢出晶体管，用于输出在所述光电转换单元中累积的电载流子，所述溢出晶体管被包括在所述像素晶体管中，

其中，所述溢出晶体管的栅极驱动线在与所述像素晶体管的栅极驱动线相同的布线层中在像素的行方向上延伸；以及

在与像素的行相对应地设置的行(n-1)、行(n)和行(n+1)的驱动布线中，所述第一传输晶体管的栅极驱动线和在所述第一传输晶体管的栅极驱动线的两侧设置的所述像素晶体管的栅极驱动线的布线距离的总和，大于所述溢出晶体管的栅极驱动线和在所述溢出晶体管的栅极驱动线的两侧设置的所述像素晶体管的栅极驱动线的布线距离的总和。

16. 根据权利要求15所述的固态摄像设备，其中，所述复位晶体管的栅极驱动线被设置在所述第一传输晶体管的栅极驱动线和所述溢出晶体管的栅极驱动线之间。

17. 根据权利要求15所述的固态摄像设备，其中，行选择晶体管的栅极驱动线、电源线和接地线中的一个被设置在所述第一传输晶体管的栅极驱动线和所述溢出晶体管的栅极驱动线之间。

18. 根据权利要求15所述的固态摄像设备，其中，所述第一传输晶体管的栅极驱动线和所述溢出晶体管的栅极驱动线之间的布线距离是所述像素晶体管的栅极驱动线之间的布线距离中的最大布线距离。

19. 根据权利要求11所述的固态摄像设备，其中，所述像素晶体管的栅极驱动线被放置在所述电载流子累积部之上。

## 固态摄像设备

### 技术领域

[0001] 本发明涉及固态摄像设备中的驱动线的配置。

### 背景技术

[0002] 近年来,诸如采用适用于低电力消耗和高速读出的CMOS图像传感器的数字摄像机和数字照相机等摄像设备已被普遍使用。提出了具有以行和列方向排列的多个像素的CMOS图像传感器,其中每个像素包含光电转换单元,所述CMOS图像传感器被配置为在所有的像素中同时电子控制曝光开始和曝光结束的全局电子快门(global electronic shutter)(国际公开号W011/043432)。

### 发明内容

[0003] 然而,本发明的发明人发现为了在应用全局电子快门时抑制图像质量劣化发生,必须考虑像素晶体管的驱动线的配置。本发明提供了一种能够在执行全局电子快门操作时抑制可能发生的图像质量劣化的固态摄像设备。

[0004] 根据本发明的一个方面,提供了一种具有图像传感区域的固态摄像设备,在所述图像传感区域中以矩阵形式排列多个像素,每个像素包括光电转换单元、用于传输所述光电转换单元中的电载流子的第一传输晶体管、用于累积从所述第一传输晶体管传输的电载流子的电载流子累积部、用于传输来自所述电载流子累积部的电载流子的第二传输晶体管、用于累积从所述第二传输晶体管传输的电载流子的浮置扩散部(下文中,称为FD)以及用于复位所述浮置扩散部的电势的复位晶体管,所述固态摄像设备包括多个用于驱动多个像素晶体管的栅极的像素晶体管的栅极驱动线,每个所述像素晶体管包括所述第一传输晶体管、所述第二传输晶体管以及所述复位晶体管,所述栅极驱动线在一个布线层中在像素的行方向上延伸。在此情况下,在与所述像素的行对应设置的行(n-1)、行(n)和行(n+1)的驱动布线中,以靠近所述光电转换单元的方式来设置所述像素晶体管的栅极驱动线中的所述第一传输晶体管的栅极驱动线,并且,以不相互靠近的方式来设置所述第一传输晶体管的栅极驱动线和所述第二传输晶体管的栅极驱动线。

[0005] 根据以下参照附图对示例性实施例的描述,本发明的其他特征将变得清楚。

### 附图说明

[0006] 图1是例示根据本发明的第一实施例的像素的平面图。

[0007] 图2是根据本发明的第一实施例的像素的横截面图。

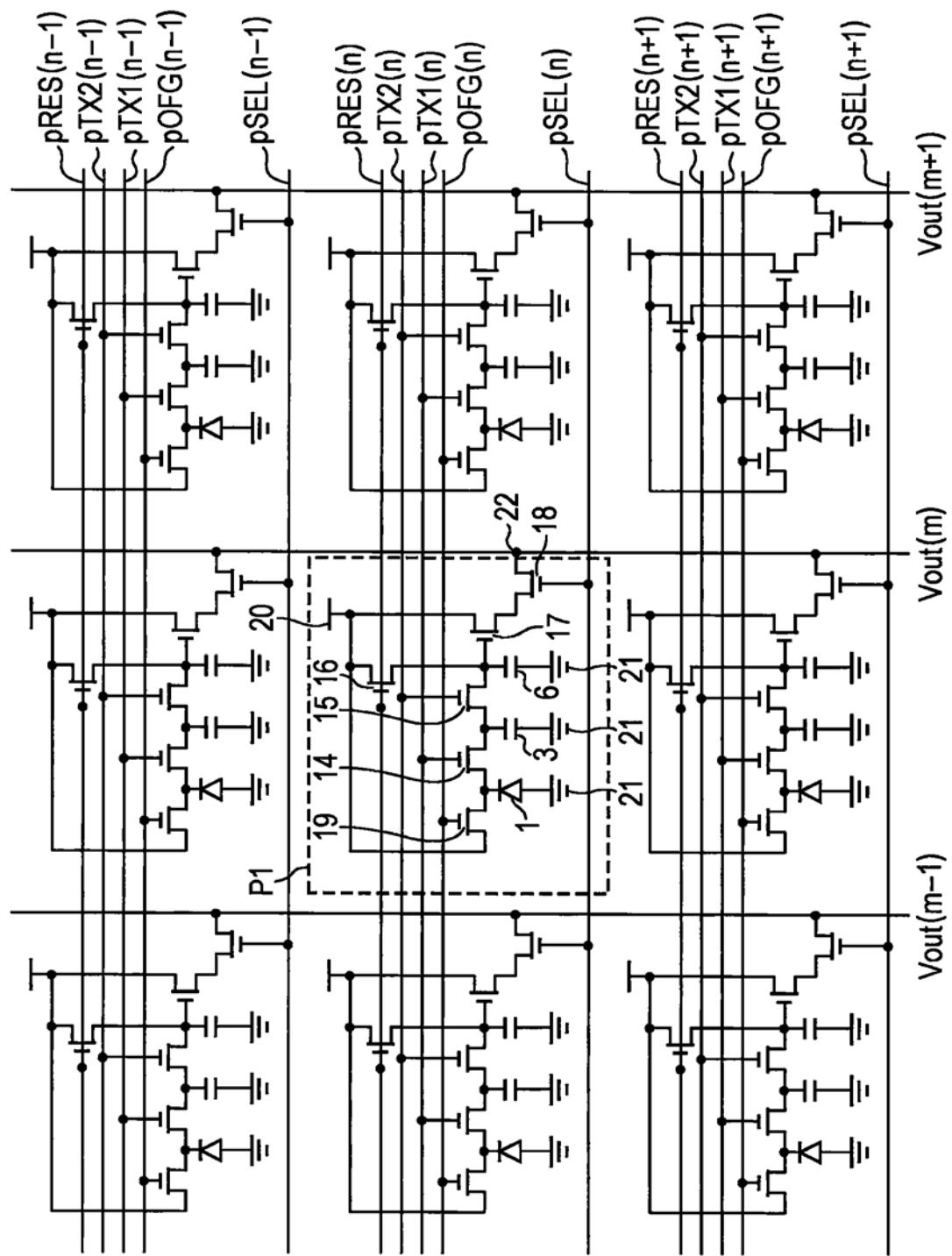

[0008] 图3是根据本发明的第一实施例的像素电路图。

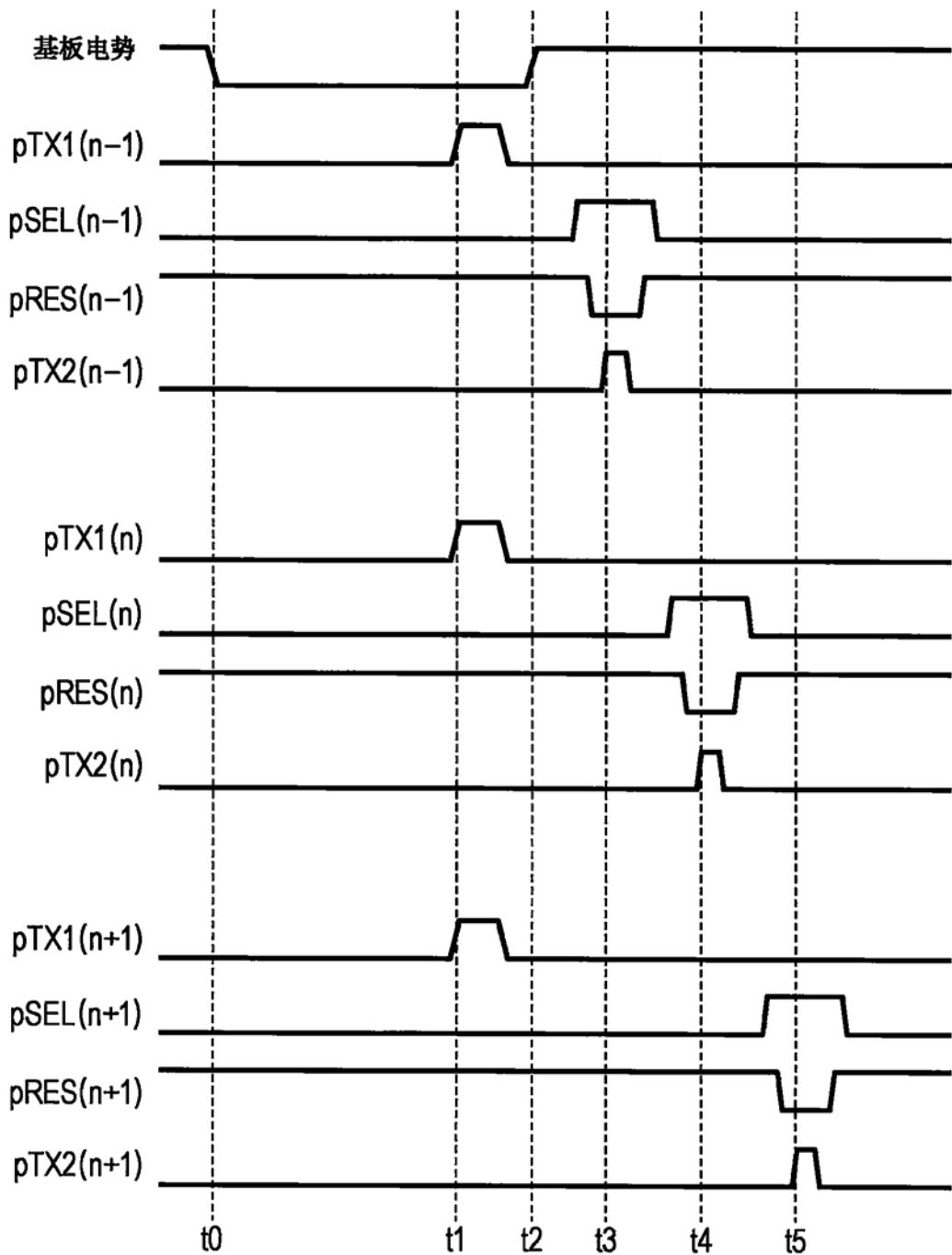

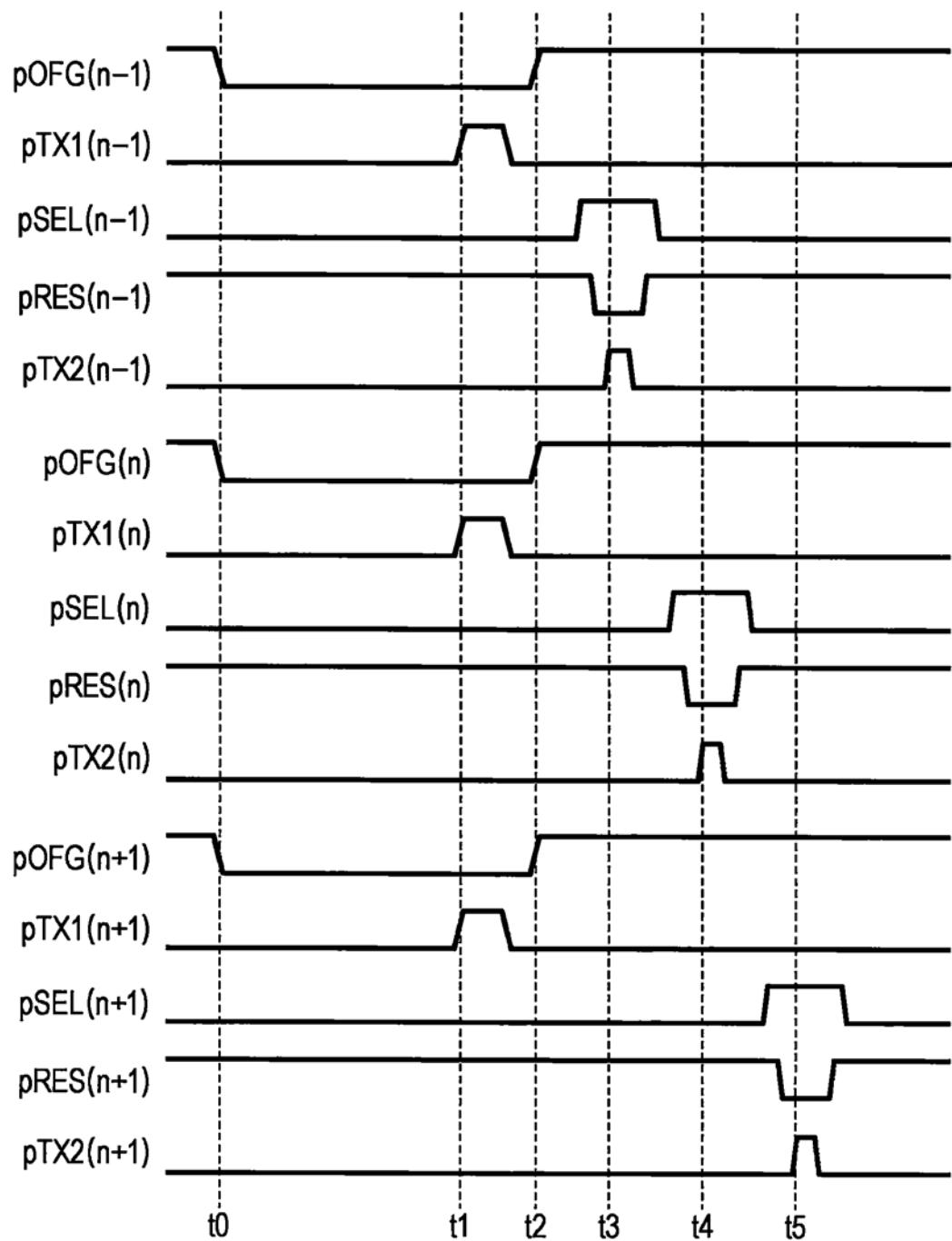

[0009] 图4是根据本发明的第一实施例的驱动时序图。

[0010] 图5是根据本发明的第二实施例的像素的平面图。

[0011] 图6是根据本发明的第二实施例和第三、第四实施例的横截面图。

[0012] 图7是根据本发明的第二、第三和第四实施例的像素电路图。

- [0013] 图8是根据本发明的第二、第三和第四实施例的驱动时序图。

- [0014] 图9是根据本发明的第三实施例的像素的平面图。

- [0015] 图10是根据本发明的第四实施例的像素平面图。

- [0016] 图11是关于根据本发明的第一实施例的驱动布线(driving wiring)的配置的示例的示意图。

- [0017] 图12是布线距离的解释图。

- [0018] 图13是关于根据本发明的第二实施例的驱动布线的配置的示例的示意图。

- [0019] 图14是关于根据本发明的第三实施例的驱动布线的配置的示例的示意图。

## 具体实施方式

### [0020] 第一实施例

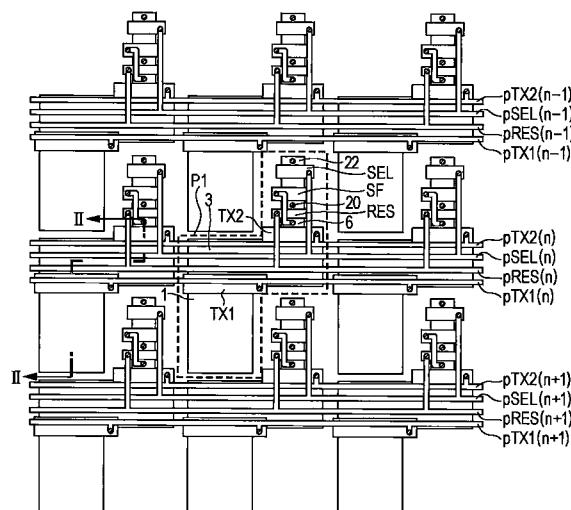

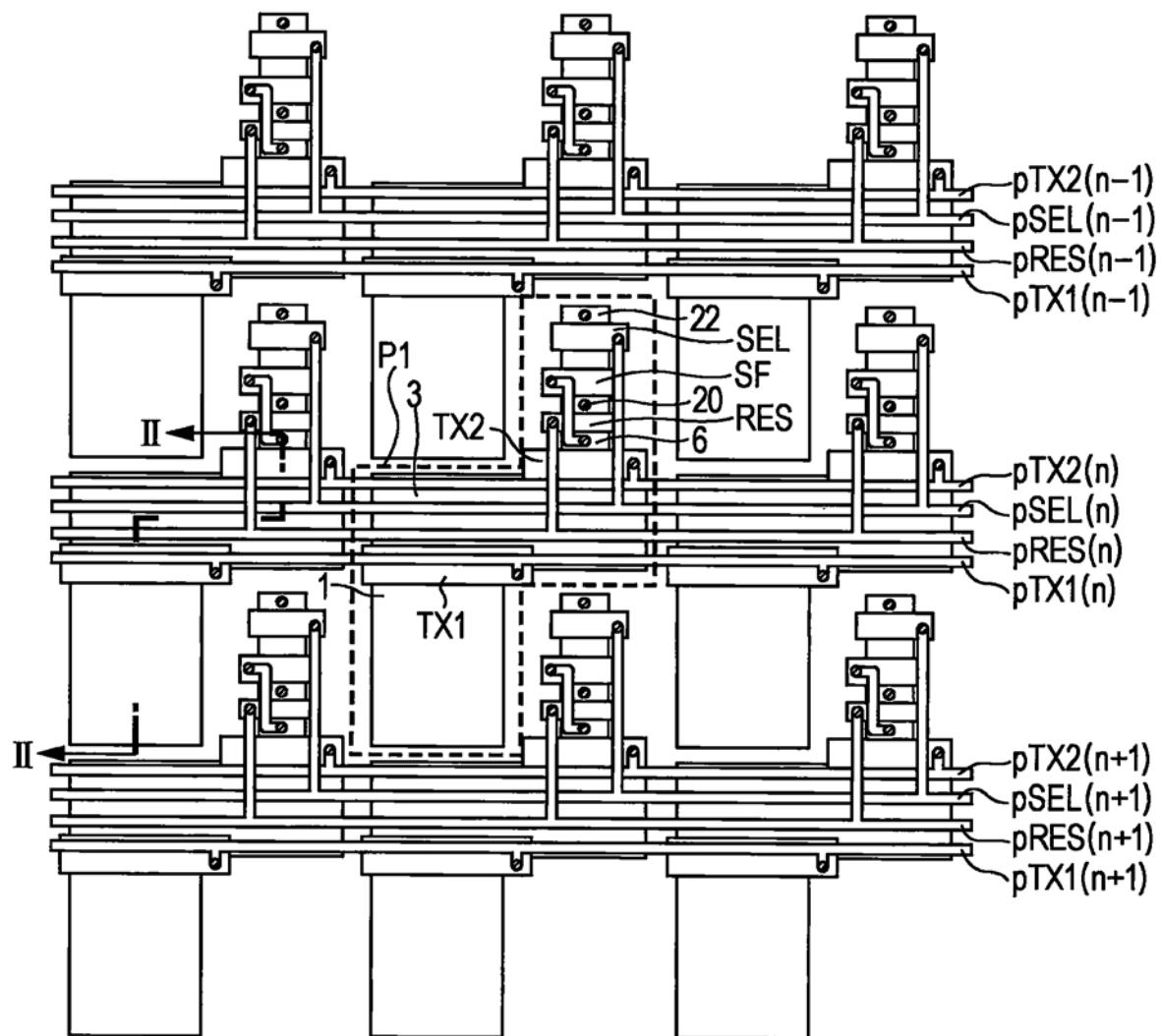

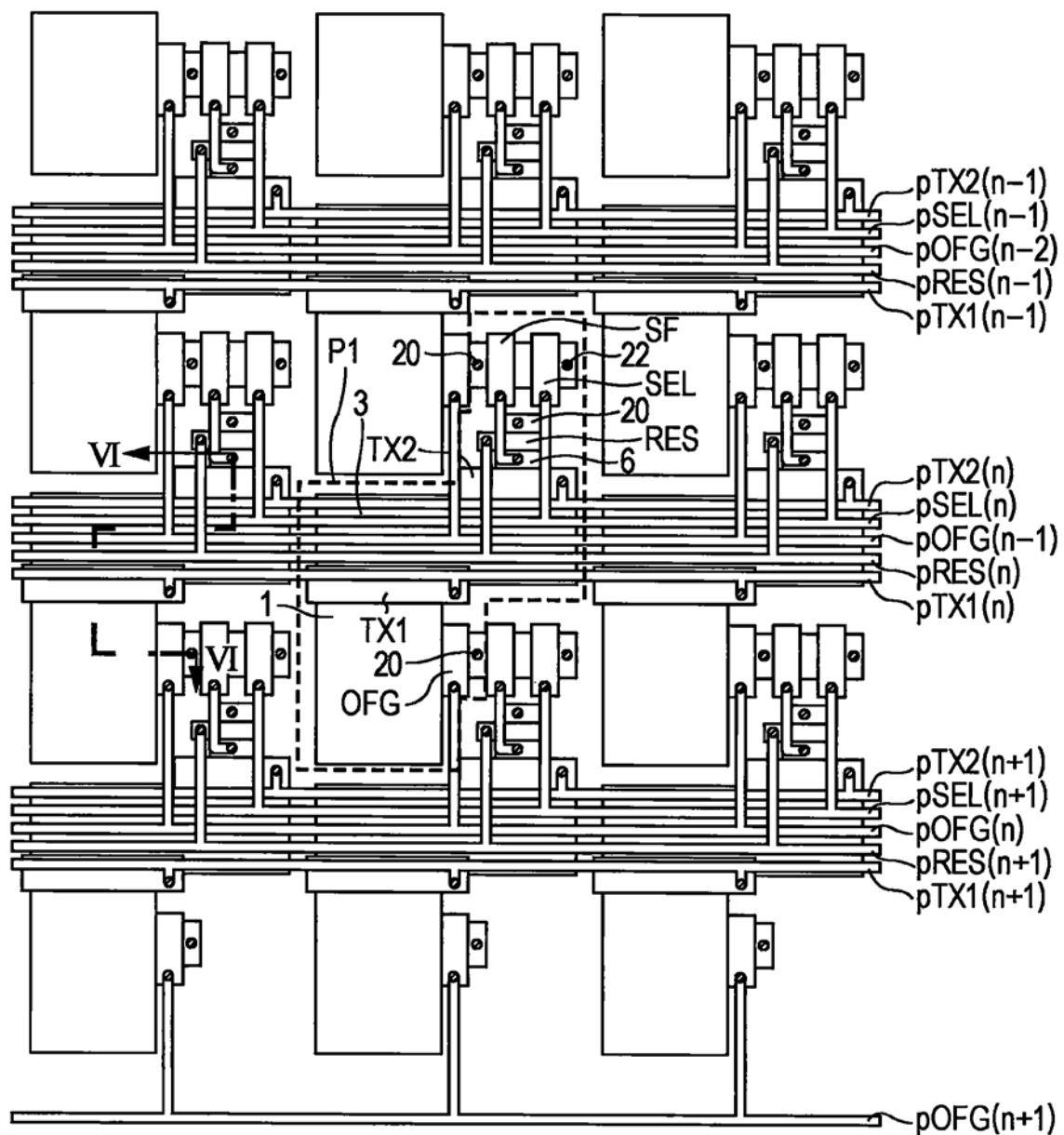

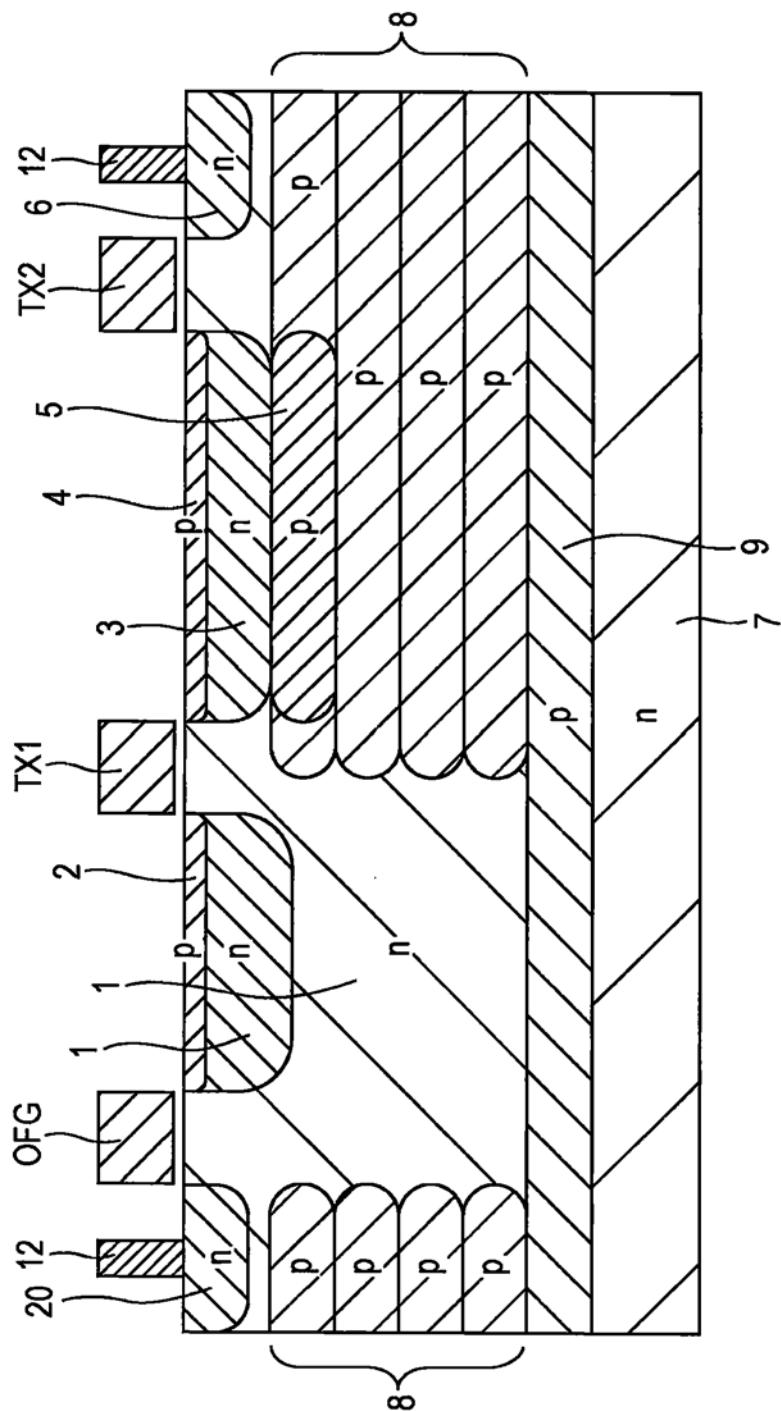

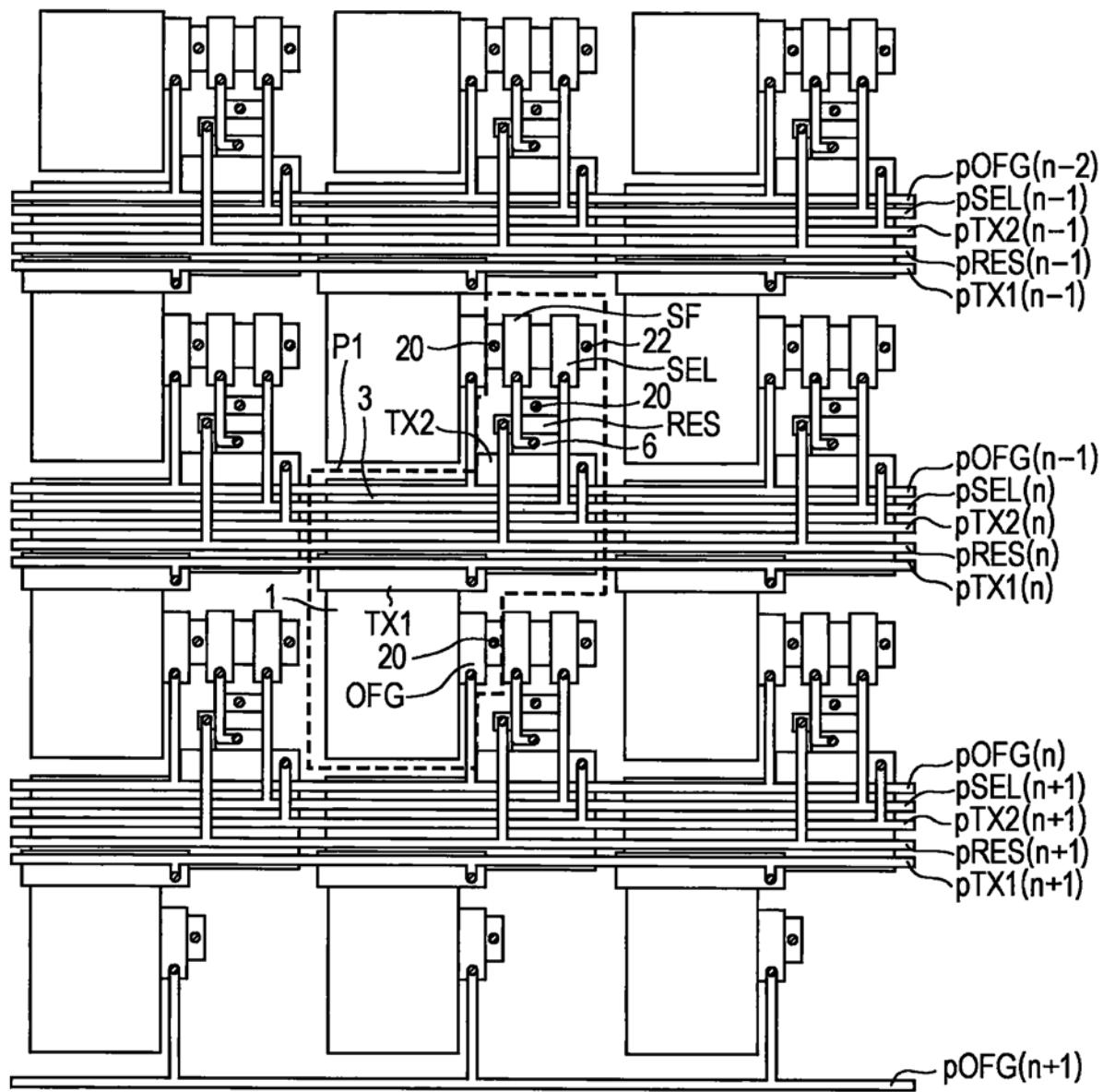

[0021] 将参照图1至图4以及图11来描述本发明的第一实施例。图1是以 $3 \times 3$ 矩阵形式设置的多个像素的平面图。图2是沿图1中的线II-II截取的一部分的像素横截面图。图3是例示与图1对应的三行和三列中的像素的等效电路图。图4是用于操作根据本实施例的固态摄像设备的驱动时序图。涉及相同部分的相同数字贯穿始终。尽管以下将描述将电子用作信号电载流子的结构，但是正空穴(Positive holes)也可以被用作信号电载流子。在正空穴被用作信号电载流子时，半导体区域的导电类型可能与在信号电载流子是电子的情况下相反。

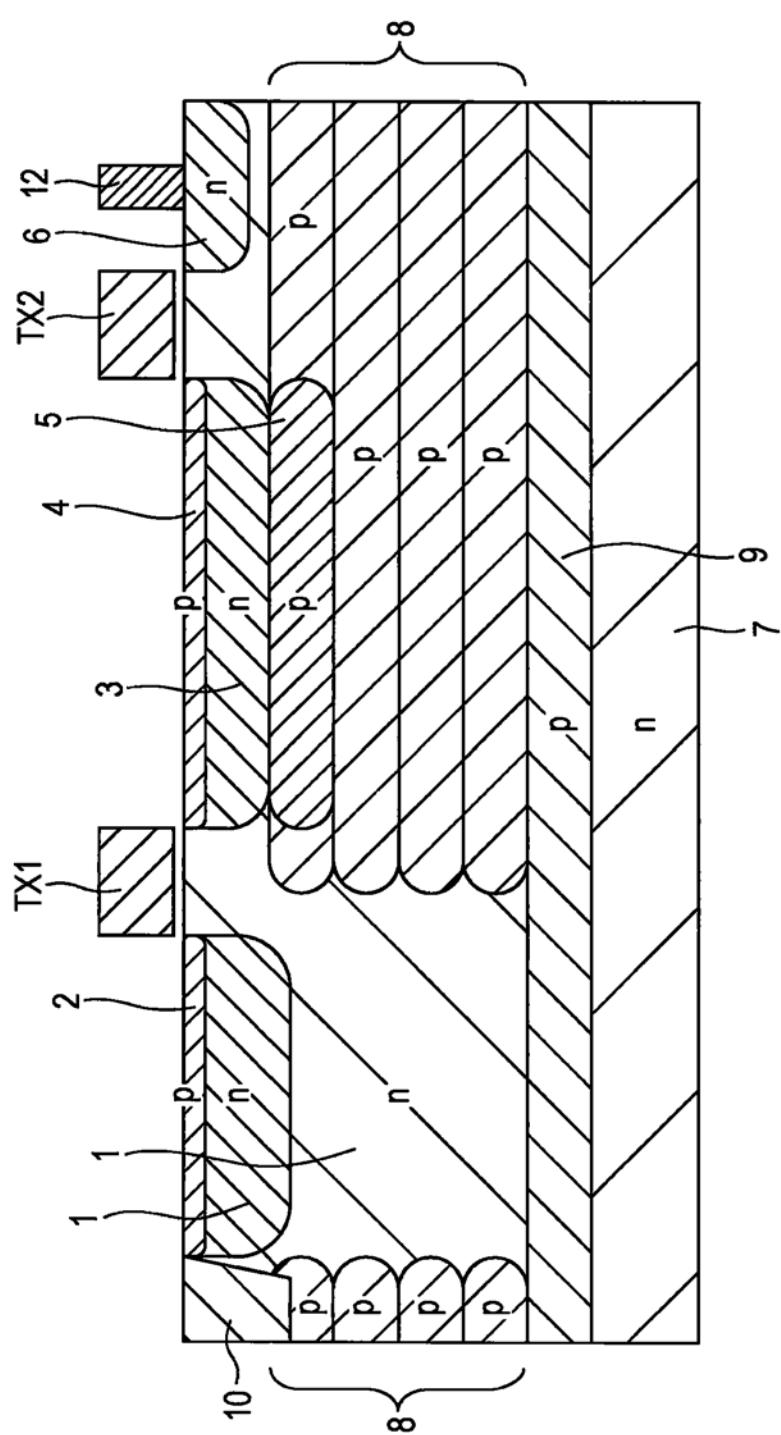

[0022] 参见图3，各像素P1包括用于传输光电转换单元1中的电载流子的第一传输晶体管14，以及用于累积从第一传输晶体管14传输的电载流子的电载流子累积部3。各像素P1还包括用于传输来自电载流子累积部3的电载流子的第二传输晶体管15。各像素P1还包括用于累积从第二传输晶体管15传输的电载流子的浮置扩散部6(下文称为“FD 6”)、用于复位FD 6的电势的复位晶体管16、源极跟随器晶体管17和行选择晶体管18。

[0023] 各像素P1通过像素输出单元22而与垂直输出线Vout相连。电源20和接地21也被设置在其中。根据本实施例，设置了被称为垂直溢漏(Vertical Overflow Drain)(下文中，VOFD)的结构，在该结构中，通过嵌入层9将电载流子从光电转换单元1输出到半导体衬底7。

[0024] 图2是沿图1中的线II-II截取的像素横截面图。p型嵌入层9和p型阱(well)8被设置在n型半导体衬底7上。表面保护层2被设置在具有n型和p型的光电转换单元1上，从而构成所谓的掩埋型光电二极管。p型表面保护层4被设置在n型电载流子累积部3上。

[0025] 耗尽抑制部5被设置在p型电载流子累积部3之下，耗尽抑制部5由比阱8更高浓度的半导体制成。

[0026] 向作为第一传输晶体管14的栅极的TX1供给用于接通第一传输晶体管14的脉冲，使光电转换单元1中的电载流子传输到电载流子累积部3。

[0027] 向作为第二传输晶体管15的栅极的TX2供给用于接通第二传输晶体管14的脉冲，使电载流子累积部3中累积的电载流子传输到FD 6。

[0028] 接下来，将参照图3和图4来描述将要由根据本实施例的固态摄像设备执行的操作。参见图4，处于低电平(在下文中，被称为L电平)的晶体管具有非导通状态，以及处于高电平(在下文中，被称为H电平)的晶体管具有导通状态。

[0029] 参见图3和图4，pTX1(n)表示第n行的第一传输晶体管14的栅极驱动线，pTX2(n)表

示第n行的第二传输晶体管15的栅极驱动线。pRES(n)表示第n行的复位晶体管16的栅极驱动线,pSEL(n)表示第n行的行选择晶体管18的栅极驱动线。在栅极驱动线名称之后的各括号中的数字表示像素的行号。

[0030] 在图4中的t0时刻,衬底电势的电平变为L电平,从而断开VOFD。因此,开始在光电转换单元1中累积经过了光电转换的电子。

[0031] 接下来,在t1时刻,第一传输晶体管14的栅极驱动线pTX1(n-1)、pTX1(n)以及pTX1(n+1)的电平变为H电平,从而接通第一传输晶体管14。因此,将电子传输到电载流子累积部3。在经过预定时间段之后,断开第一传输晶体管14,从而结束将电子传输到电载流子累积部3。

[0032] 由于在本实施例中配设了电载流子累积部3,因此所有像素中的光电转换单元1中的信号电载流子被同时传输到电载流子累积部3。这样能够实施将由全局电子快门执行的操作,即在所有像素中通过电子开关同时控制曝光开始和曝光结束。

[0033] 接下来,在t2时刻,衬底电势的电平变为H电平,从而在光电转换单元1和半导体衬底7之间发生穿通。因此,电载流子被输出到半导体衬底7。

[0034] 可以根据需要来设置从断开VOFD时的t0时刻到接通第一传输晶体管14时的t1时刻的时期,从而能够获得任意累积时间的图像。

[0035] 在t0时刻和t1时刻之间可以间歇性地使第一传输晶体管14多次接通。多次接通能够减少一次传输操作所处理的信号电载流子,并能够使传输操作变得容易。在多次接通的情况下,t1时刻是多次接通(ON)操作中的最后一次的时间。

[0036] 接下来,在t3、t4和t5时刻,第二传输晶体管15的栅极驱动线pTX2的电平以行顺次变为H电平,从而接通第二传输晶体管15。因此,信号电载流子从电载流子累积部3传输到FD6。

[0037] 针对CMOS图像传感器的传统方法是可适用于针对FD 6和后续级的信号传输方法。换句话说,信号经由源极跟随器晶体管17、行选择晶体管18和像素输出单元22而被输出到垂直信号线。噪音分量信号可以在接通第二传输晶体管15之前被输出到垂直信号线。尽管在图3中配设了行选择晶体管18,但是也可以采用没有行选择晶体管18的结构。

[0038] 这里,栅极驱动线由导体构成从而输送图4中例示的驱动脉冲,并在导体间形成寄生电容。导体的寄生电容和电阻会引起通过导体传输的驱动脉冲间的传播延迟。随着固态摄像设备中的像素数量的增加,图像传感区域的尺寸也增加。因此,图像传感区域可以有具有较小传播延迟的部分和具有较大传播延迟的其他部分。因而这样可能会造成在将要向图像传感区域内的像素中的晶体管的栅极输入驱动脉冲的操作定时方面的差异,这会造成在存储光电转换单元1中累积的图像信号的定时方面的差异。这样可能导致图像质量的劣化。

[0039] 在传统的行顺次快门(line-sequential shutter)取代全局电子快门的情况下,由于在画面内的累积定时方面存在相当大的差异,因此,在画面内的累积定时方面的差异可能不是图像质量中的严重的问题。然而,使用全局电子快门,由于可能不容易发生针对每行的累积定时的差异,因此,由于传播延迟所引起的累积定时的差异而导致的图像质量的劣化可能在图像传感区域内是严重的。随着累积时间的下降,累积定时的差异与累积时间之比会增大。因此,差异会变成更严重,这可能是防止累积时间下降的一个因素。

[0040] 如上所述,通过第一传输晶体管14来控制全局电子快门中的累积定时。因此,可能

会降低第一传输晶体管14的栅极驱动线pTX1的寄生电容以降低传播延迟,从而能够降低图像传感区域内的累积定时的差异。在多个像素晶体管的栅极驱动线被设置在一个布线层内且栅极驱动线紧密设置的情况下,上述寄生电容的影响可能会显著地出现。

[0041] pTX1的配置

[0042] 接下来,将参照图1来描述用于降低栅极驱动线pTX1的寄生电容的像素晶体管的驱动线的配置。

[0043] 图1例示了在光电转换单元1中的半导体区域、像素晶体管的栅极电极和用于将半导体区域和像素晶体管的栅极电极电连接的布线。在固态摄像设备中,除像素晶体管的驱动线以外,还根据需要将包括电源线、接地电源线和垂直输出线的线放置在包括多层的布线层中。图1例示了放置在一个布线层内的像素晶体管的驱动线。例如,在具有三层结构的布线层中,图1中例示的像素晶体管的驱动线被放置在第二布线层。

[0044] 参见图1,第一传输晶体管14、第二传输晶体管15和复位晶体管16的栅极驱动线被设置在电载流子累积部3上,从而在图像传感区域的行方向上延伸。这些栅极驱动线以周期的布局模式而设置。

[0045] 在栅极驱动线pTX1(n)附近仅设置复位晶体管16的栅极驱动线pRES(n),并远离第二传输晶体管15的栅极驱动线pTX2(n+1)地设置栅极驱动线pTX1(n)。在此配置中,相较于像素晶体管的栅极驱动线紧密地设置在pTX1(n)两侧的配置,pTX1(n)能够具有更低的寄生电容。

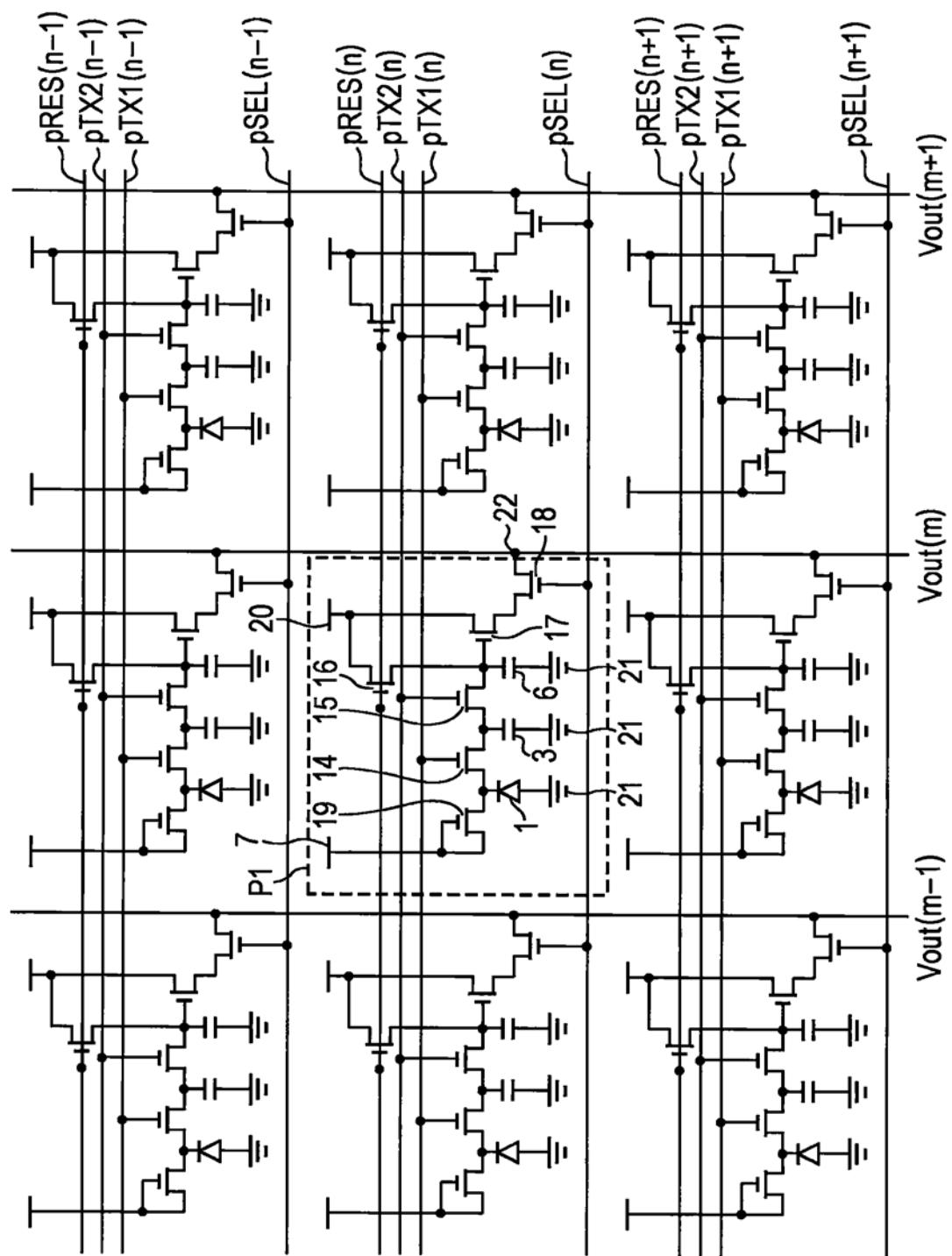

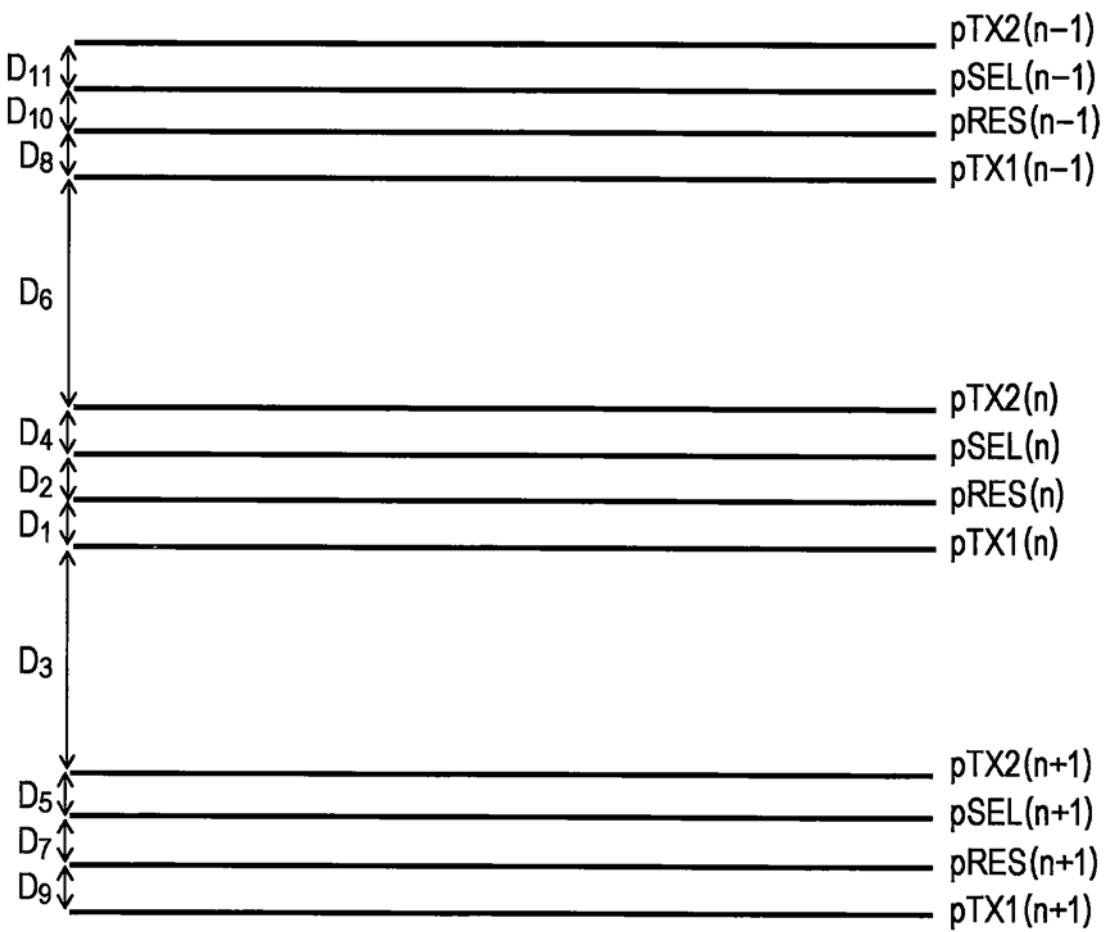

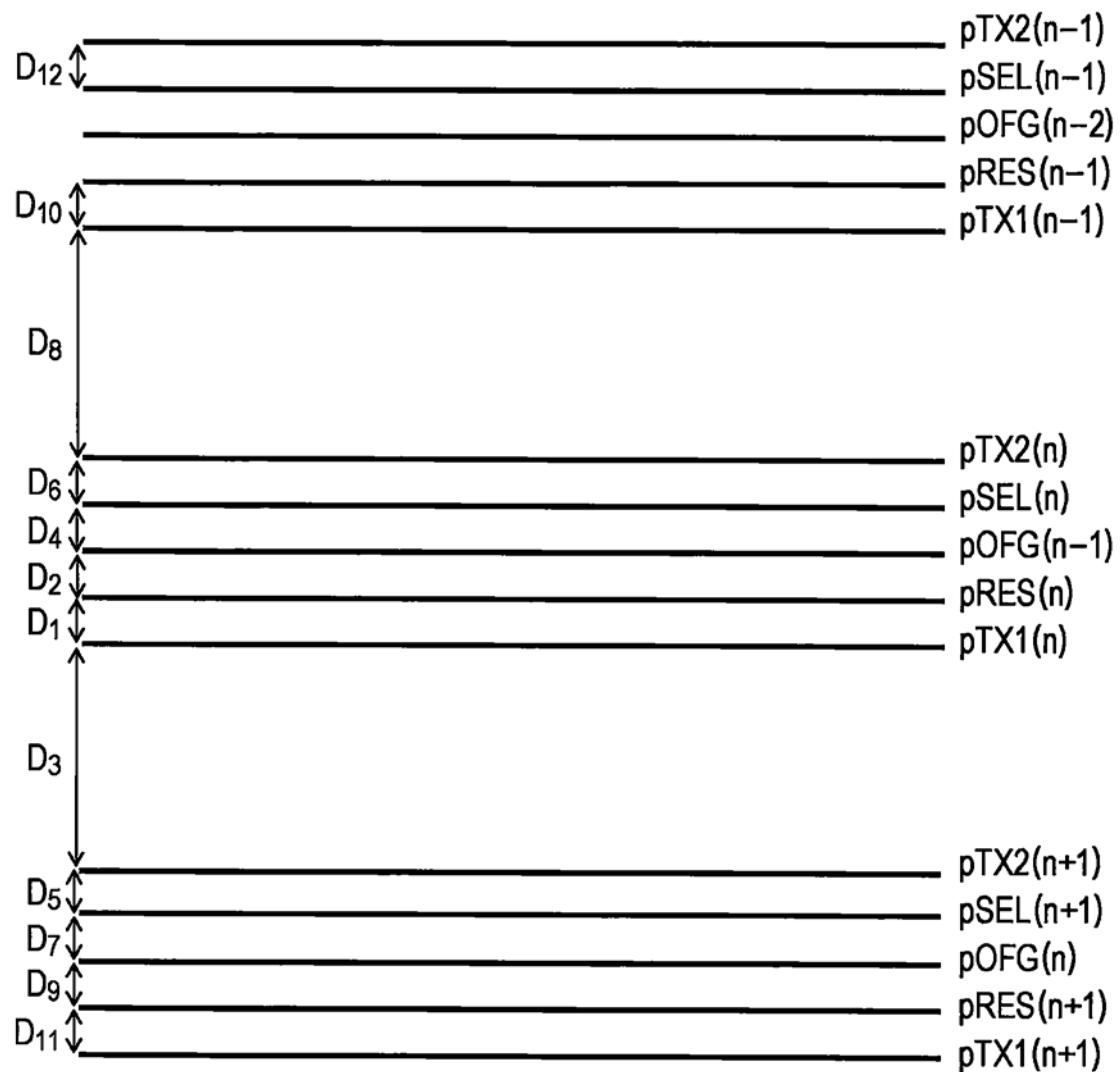

[0046] 图11示意性地例示了图1中所示的驱动布线的配置。Dx表示驱动线之间的距离。

[0047] 这里,假设在行(n-1)、行(n)和行(n+1)的驱动布线中,第一传输晶体管14的栅极驱动线和在第一传输晶体管14的栅极驱动线的两侧设置的像素晶体管的栅极驱动线之间的布线距离的总和等于DTX1<sub>Total</sub>。

[0048] 类似地,在除第一传输晶体管14以外的其他像素晶体管的栅极驱动线和在所述栅极驱动线的两侧设置的像素晶体管的栅极驱动线之间的布线距离的总和在针对第二传输晶体管15的情况下等于DTX2<sub>Total</sub>,针对复位晶体管16的情况下是DRES<sub>Total</sub>,以及针对行选择晶体管18的情况下是DSEL<sub>Total</sub>。

[0049] 在此情况下,DTX1<sub>Total</sub>是高于全部DTX2<sub>Total</sub>、DRES<sub>Total</sub>和DSEL<sub>Total</sub>的值。

[0050] 参见图11,假设行(n-1)、行(n)和行(n+1)的驱动线之间的间隔分别等于D<sub>1</sub>至D<sub>11</sub>。

[0051] 这里,在行(n-1)、行(n)以及行(n+1)的驱动布线中,DTX1<sub>Total</sub>等于D<sub>1</sub>+D<sub>3</sub>+D<sub>6</sub>+D<sub>8</sub>+D<sub>9</sub>。另一方面,DRES<sub>Total</sub>等于D<sub>1</sub>+D<sub>2</sub>+D<sub>7</sub>+D<sub>8</sub>+D<sub>9</sub>+D<sub>10</sub>。DSEL<sub>Total</sub>等于D<sub>2</sub>+D<sub>4</sub>+D<sub>5</sub>+D<sub>7</sub>+D<sub>10</sub>+D<sub>11</sub>。

[0052] 由于D<sub>3</sub>和D<sub>6</sub>是其他线之间的间隔的例如三倍或更多倍,因此,行(n-1)、行(n)和行(n+1)中的DTX1<sub>Total</sub>等于比DRES<sub>Total</sub>和DSEL<sub>Total</sub>更高的值。应当注意,如图12中所示,在此通过例如pTX1(n)的端部和pRES(n)的端部之间的距离来定义驱动线之间的布线距离。

[0053] 根据上述结构,能够减少在栅极驱动线pTX1中出现的寄生电容,因此,更小的传播延迟能够降低累积定时中的差异。

[0054] 上述的驱动线的配置不仅能够应用于正面照射(FSI, front side illumination),还能够应用于背面照射(BSI, back side illumination)。并且,针对背面照射,假定像素晶体管的驱动线与像素的行对应地放置。因此,可以在那样的情况下应用上述驱动线配置示例。

[0055] 图1例示了正面照射的像素的平面图。在正面照射中,通常各像素晶体管的驱动线被设置在没有光电转换单元1的区域中。例如,参见图1,各像素晶体管的栅极驱动线被放置在电载流子累积部3上。因此,考虑到驱动线的布局,为了降低第一传输晶体管14的栅极驱动线pTX1的寄生电容,以靠近光电转换单元1的方式设置像素晶体管的栅极驱动线中的栅极驱动线pTX1。因此,栅极驱动线pTX1被放置在驱动线区域的端部,并且栅极驱动线pTX1仅在驱动线区域的一侧具有导体。

[0056] pTX1和pTX2的配置

[0057] 根据本实施例,不以相互靠近的方式来设置栅极驱动线pTX1和栅极驱动线pTX2。表述“不以相互靠近的方式来设置”是指pTX2不放置在pTX1两侧的位置关系。可替代地,即使在pTX2被放置在pTX1的一侧的情况下,pTX1与pTX2之间的距离是pTX1与被放置在pTX1的另一侧的驱动线之间的距离的例如三倍或更多倍。

[0058] 以下将描述在以相互靠近的方式来放置栅极驱动线pTX1和栅极驱动线pTX2的情况下所涉及的问题。

[0059] 在栅极驱动线pTX1和栅极驱动线pTX2具有电容耦合时,栅极驱动线pTX2的电势可能在栅极驱动线pTX1的电平改变时有波动。例如,在图4中所例示的t1时刻,栅极驱动线pTX2的电平最初是L电平。然而,当栅极驱动线pTX1从L电平朝向H电平改变时,栅极驱动线pTX2的电势从L电平朝向H电平改变。这样使得从电载流子累积部3到FD 6的势垒降低了。因此,会降低电载流子累积部3中的饱和信号量。根据图像传感区域内寄生电容的变化的潜在波动的影响可能会引起图像传感区域内的电载流子累积部3中的饱和信号量的波动。在t0时刻至t1时刻之间间歇性地执行多次栅极驱动线pTX1的操作时,该现象会变得更明显。

[0060] 在某些情况下,在作为NMOS的第二传输晶体管15处于断开(OFF)状态期间,栅极驱动线pTX2可以被设置为负电势。因此,在沟道部中激励空穴,以便于即使在出现电子时电子和空穴之间的再复合能够抑制暗电流。这里,如果栅极驱动线pTX1和栅极驱动线pTX2具有电容耦合,则在栅极驱动线pTX1的电平从L电平变为H电平时,栅极驱动线pTX2的电势变得更高且会使空穴激励不足。因而可能使暗电流抑制变得不足。

[0061] 为了防止上述情况,根据本实施例,不以相互靠近的方式来设置栅极驱动线pTX1和栅极驱动线pTX2。具体地,参见图1和图11,在行(n-1)、行(n)和行(n+1)的驱动布线中,像素晶体管的栅极驱动线之间的布线距离中的最大布线距离可以是栅极驱动线pTX1和栅极驱动线pTX2之间的布线距离。

[0062] 如图4所理解的那样,在接通第一传输晶体管14时,复位晶体管16也处于接通状态。因此,即使复位晶体管16的电势具有从L电平到H电平的变化,这种变化也可能不容易产生影响。因而,能够以靠近栅极驱动线pTX1的方式来设置栅极驱动线pRES。

[0063] 可以以靠近栅极驱动线pTX1的方式来设置栅极驱动线pSEL而不是设置栅极驱动线pRES。这是因为,即使在接通第一传输晶体管14时行选择晶体管18处于断开状态时,如果恒流源处于断开状态则不存在信号电载流子的传输路径,且在图像传感区域内没有出现信号变化。

[0064] 可替代地,可以以靠近栅极驱动线pTX1的方式来设置电源线或接地线而不是设置栅极驱动线pRES,从而抑制电势波动。这是因为,该电源线和接地线不直接与信号电载流子的传输路径相关联且在图像传感区域内没有出现信号变化。

[0065] 根据本实施例,在每个像素中设置FD 6。然而,FD 6可以被多个像素共用。同样在此情况下,可以如上所述地设置第一传输晶体管14的栅极驱动线pTX1以获得相同的效果。多个像素共用FD 6可以减少驱动线的数量,从而可以将第一传输晶体管14的栅极驱动线pTX1设置为远离其他驱动线,因而能够降低寄生电容。

#### [0066] 第二实施例

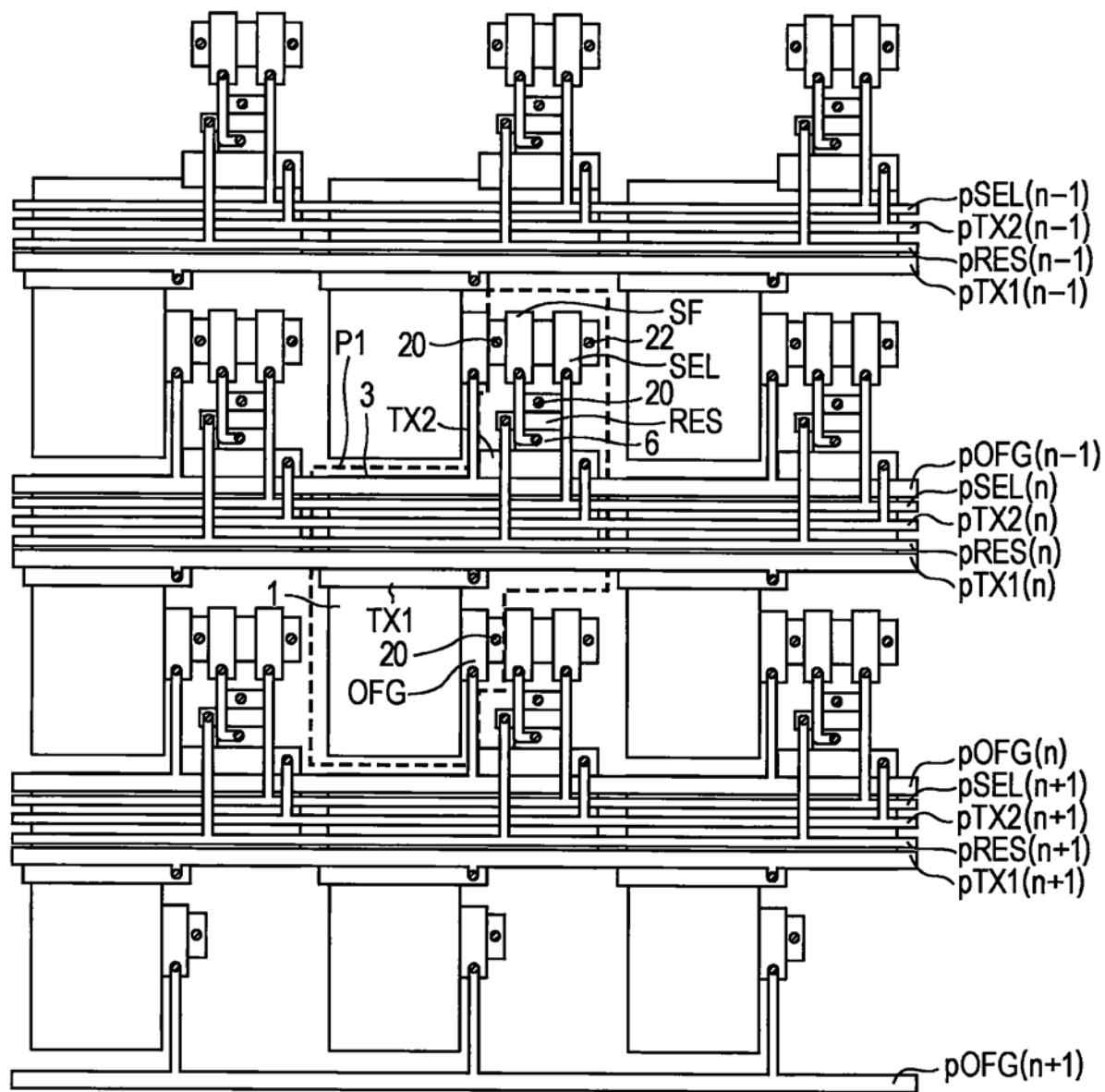

[0067] 将参照图5至图8以及图13来描述本发明的第二实施例。指代相同部分的相同数字贯穿第一和第二实施例,将省略对其的详述。图5是根据本实施例的固态摄像设备中的三行和三列像素的平面图。图6是沿图5中的线VI-VI截取的一部分的像素横截面图。图7是示与图5对应的三行和三列像素的等效电路图。图8是用于操作根据本实施例的固态摄像设备的驱动时序图。

[0068] 本实施例与第一实施例的不同之处在于:分离地设置了溢出晶体管(overflow transistor)而不采用VOFD结构。换句话说,如图6和图7所示,设置了溢出晶体管19。当接通溢出晶体管19的栅极OFG时,通过插头12将电载流子传输到电源20。

[0069] 图8示了时序图。在t0时刻,溢出晶体管19的栅极驱动线pOFG的电平变为L电平,从而断开溢出晶体管19。

[0070] 接着,在t1时刻,第一传输晶体管14的栅极驱动线pTX1的电平变为H电平,接通第一传输晶体管14。因此,电子被传输到电载流子累积部3。在经过预定时间段后,断开第一传输晶体管14,从而结束向电载流子累积部3传输电子。

[0071] 接着,在t2时刻,栅极驱动线pOFG的电平变为H电平,从而接通溢出晶体管19。因此,电载流子能够从光电转换单元1输出到作为溢漏的电源20。

[0072] 可以根据需要设置从栅极驱动线pOFG的电平变为L电平时的t0时刻到接通第一传输晶体管14的t1时刻的时间段,从而能够获得任意累积时间的图像。

[0073] 图13示意性地示出了图5中示例的驱动布线的布置。假设行(n-1)、行(n)和行(n+1)的驱动线之间的间隔分别等于D<sub>1</sub>至D<sub>12</sub>。应当注意,由于pOFG(n-2)是第(n-2)行的像素的驱动线,因此不考虑pOFG(n-2)和相邻驱动线之间的间隔。由于在pRES(n+2)和pSEL(n+2)之间设置了未示出的pOFG(n+1),因此也不考虑pOFG(n+1)。

[0074] 这里,在行(n-1)、行(n)和行(n+1)中,DTX1<sub>Total</sub>等于D<sub>1</sub>+D<sub>3</sub>+D<sub>8</sub>+D<sub>10</sub>+D<sub>11</sub>。另一方面,DRES<sub>Total</sub>等于D<sub>1</sub>+D<sub>2</sub>+D<sub>9</sub>+D<sub>10</sub>+D<sub>11</sub>。DSEL<sub>Total</sub>等于D<sub>4</sub>+D<sub>5</sub>+D<sub>6</sub>+D<sub>7</sub>+D<sub>12</sub>。DOFG<sub>Total</sub>等于D<sub>2</sub>+D<sub>4</sub>+D<sub>7</sub>+D<sub>9</sub>。

[0075] 由于D<sub>3</sub>和D<sub>8</sub>是其他线之间间隔的例如三倍或更多倍,因此,DTX1<sub>Total</sub>等于比行(n-1)、行(n)和行(n+1)中的DRES<sub>Total</sub>、DSEL<sub>Total</sub>和DOFG<sub>Total</sub>更高的值。根据该结构,能够减少在栅极驱动线pTX1中出现的寄生电容,因而更小的传播延迟能够减少累积定时中的差异。

[0076] 该布线布置能够表达为以不相互靠近的方式来设置pTX1和pTX2。此外,在行(n-1)、行(n)和行(n+1)中的pTX1和pTX2之间的距离能够表达为像素晶体管的栅极驱动线之间的布线距离中的最大布线距离。

#### [0077] pTX1和pOFG的配置

[0078] 在栅极驱动线pTX1和栅极驱动线pOFG具有电容耦合时可能会出现问题。换句话说,在栅极驱动线pTX1的电平从L电平变为H电平时的图8中的t1时刻,栅极驱动线pOFG的电平是L电平。然而,当栅极驱动线pTX1和栅极驱动线pOFG具有电容耦合时,在t1时刻,栅极驱动线pOFG的电势可能具有从L电平向H电平的改变。因此,降低了从光电转换单元1到作为溢

漏的电源20的势垒，电子从光电转换单元1传输到电源20，从而可能使光电转换单元1中的饱和信号量降低。这样可能会引起图像传感区域内的信号的变化。

[0079] 因此，如图5和图13所示，根据本实施例，在一个驱动布线区域中的栅极驱动线pTX1和栅极驱动线pOFG之间配设驱动线pRES，从而以相互靠近的方式来设置驱动线。

[0080] 本实施例采用溢出晶体管而第一实施例采用VOFD结构。为了提高对更长的波长侧的灵敏度而采用更深的光电转换单元1使得在VOFD结构的状态下输出电载流子变得困难。然而，同样在此情况下，可以采用溢出晶体管从而能够输出电载流子。在VOFD结构中，在光电转换单元1和半导体衬底7之间出现穿通。因此，可以要求由一定程度上低浓度半导体构成嵌入层9。另一方面，在采用溢出晶体管的状态下，可以由高浓度半导体构成嵌入层9。这样可以提高光电转换单元1的灵敏度并提高向电载流子累积部3传输的效率。

[0081] 另一方面，由于采用VOFD结构消除了溢出晶体管的栅极OFG和栅极驱动线pOFG的必要性，因此，空的区域可以分配给其他部件。例如，可以在保持光电转换单元1的相同尺寸的同时增大驱动线之间的间隔。因此，相较于第一实施例，能够进一步降低第一传输晶体管14的栅极驱动线pTX1的寄生电容。可以增加光电转换单元1的面积，从而能够提高光电转换单元1的饱和电荷量，以及能够提高其灵敏度。

### [0082] 第三实施例

[0083] 将参照图6、图7、图9和图14来描述本发明的第三实施例。指代相同部分的相同数字贯穿第一、第二和第三实施例，将省略对其的详述。

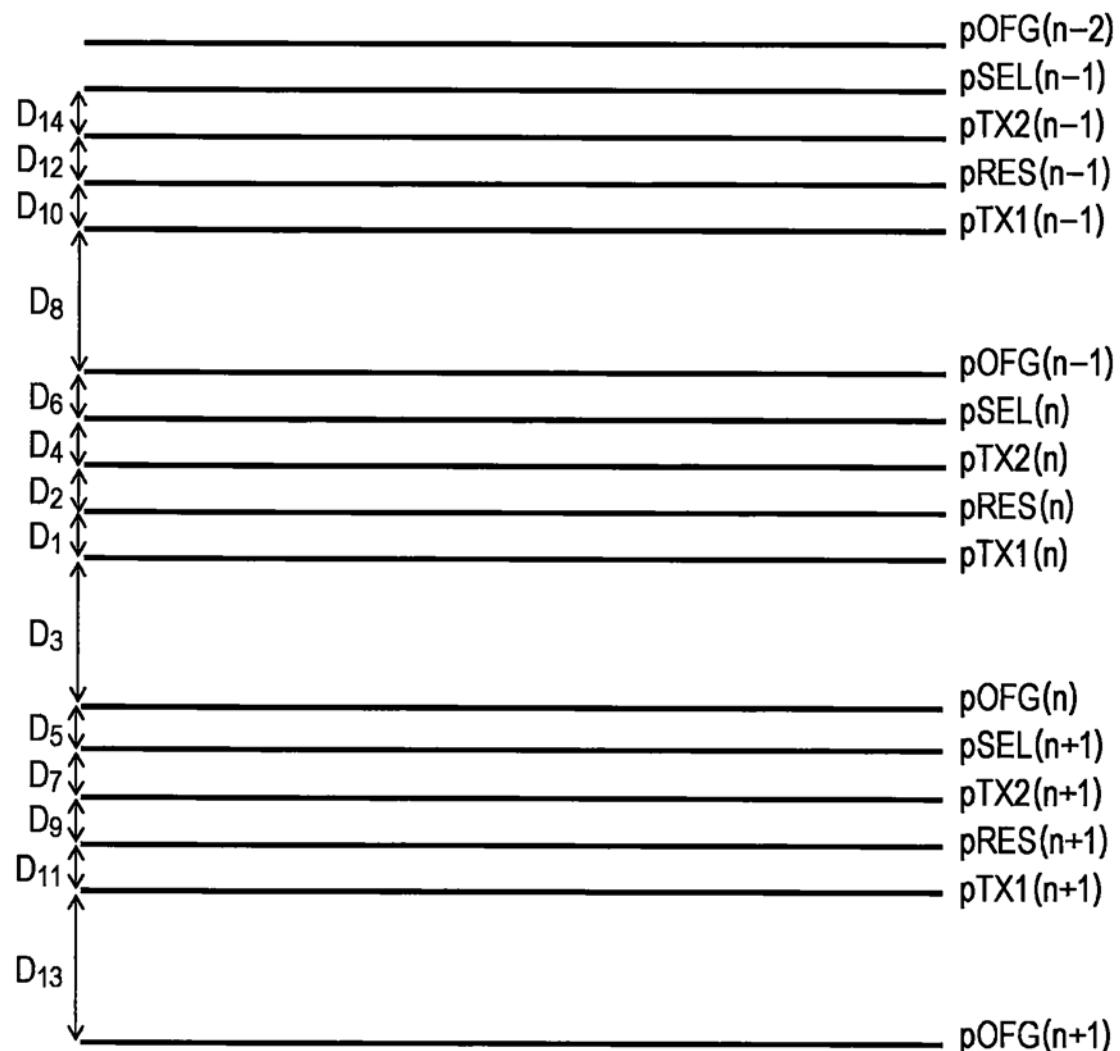

[0084] 图9是例示根据本实施例的固态摄像设备中三行和三列像素的平面图。第三实施例与第二实施例的不同之处在于栅极驱动线pOFG和栅极驱动线pTX2所设置的位置。

[0085] 参见图9，栅极驱动线pTX1和栅极驱动线pOFG之间的布线距离是像素晶体管的栅极驱动线之间的布线距离中的最大布线距离。该布置不仅能够降低栅极驱动线pTX1和其他栅极驱动线的寄生电容，还能够降低栅极驱动线pOFG和其他栅极驱动线的寄生电容。

[0086] 如上所述，还能够通过将驱动脉冲输入到溢出晶体管19的栅极OFG来控制使用全局电子快门的累积定时。因此，可以降低溢出晶体管19的栅极驱动线pOFG的寄生电容，并能够减少其中发生的传播延迟。因而可以降低累积定时中的差异。

[0087] 根据本实施例，以不靠近的方式来设置栅极驱动线pOFG和栅极驱动线pTX2。如果以靠近的方式来设置它们，可以降低电载流子累积部3中的饱和信号量，这可能会引起图像传感区域内的电载流子累积部3中饱和信号量的变化。

[0088] 在某些情况下，在作为NMOS的第二传输晶体管15的栅极驱动线pTX2处于断开状态期间，栅极驱动线pTX2可以被设置为负电势。因此，在沟道部中激励空穴，从而引起电子和空穴的再复合，这会抑制暗电流。这里，如果栅极驱动线pOFG和栅极驱动线pTX2具有电容耦合，则在栅极驱动线pOFG的电平从L电平变为H电平的时间点栅极驱动线pTX2的电势变得更高。因此，暗电流的抑制可能不足。

[0089] 因此，复位晶体管16的栅极驱动线pRES被设置在一个驱动布线区域中的栅极驱动线pOFG和栅极驱动线pTX2之间。可以设置行选择晶体管18的栅极驱动线pSEL、电源线、接地线等而不是栅极驱动线pRES。

[0090] 图14示意性地例示了图9中例示的驱动布线的布置。

[0091] 在此情况下，在行(n-1)、行(n)和行(n+1)的驱动布线中， $DTX1_{Total}$ 等于 $D_1+D_3+D_8+$

$D_{10}+D_{11}+D_{13}$ 。另一方面,  $DRES_{Total}$  等于  $D_1+D_2+D_9+D_{10}+D_{11}+D_{12}$ 。 $DSEL_{Total}$  等于  $D_4+D_5+D_6+D_7+D_{14}$ 。此外,  $DTX2_{Total}$  等于  $D_2+D_4+D_7+D_9+D_{12}+D_{14}$ 。

[0092] 由于  $D_3$ 、 $D_8$  和  $D_{13}$  是其他线之间间隔的例如三倍或更多倍, 因此,  $DTX1_{Total}$  是比行 (n-1)、行 (n) 和行 (n+1) 中的  $DRES_{Total}$ 、 $DSEL_{Total}$  和  $DTX2_{Total}$  更高的值。

[0093] 由于以上原因, 如图14中所示, 以不靠近的方式来设置 pTX1 和 pOFG, 以不靠近的方式来设置 pTX2 和 pOFG, 以及以不靠近的方式来设置 pTX1 和 pTX2。

[0094] 此外, 以靠近光电转换单元1的方式来设置 pOFG。

[0095] 另外, 如上所述, pTX1 和 pOFG 之间的布线距离是像素晶体管的栅极驱动线之间的布线距离中的最大布线距离。

[0096] 第四实施例

[0097] 将参照图6至图8以及图10来描述本发明的第四实施例。涉及相同部分的相同数字贯穿第一至第四实施例, 并将省略对其的详述。

[0098] 图10是例示根据本实施例的固态摄像设备中的三行和三列的像素的平面图。第四实施例与第二和第三实施例的不同在于: 栅极驱动线 pOFG 的线宽度和栅极驱动线 pTX1 的线宽度大于其他驱动线线宽度。还根据需要改变驱动线的位置。

[0099] 通过导体传输的各驱动脉冲的传播延迟可由寄生电容和导体的电阻的乘积来表达。因此, 可以降低电阻以获得与降低寄生电容相同的效果。换句话说, 可以增加栅极驱动线 pOFG 的线宽度和栅极驱动线 pTX1 的线宽度来减少传播延迟, 从而减少累积定时中的差异。

[0100] 根据本实施例所描述的, 增加了栅极驱动线 pOFG 和栅极驱动线 pTX1 两者的线宽度, 可以仅增加他们之一。可替代地, 可以进一步增加他们之一。

[0101] 上述利用具有增加的线宽度的驱动线的结构可以要求没有设置驱动线的布线开口区域的宽度降低或在保持布线开口区域的宽度的同时减少驱动线之间的间隔。对此, 通过检查降低寄生电容的效果以及降低电阻的效果, 可以选择具有更大效果的一个结构。

[0102] 虽然参照示例性实施例描述了本发明, 但是应当理解, 本发明并不限于所公开的示例性实施例。应当对下列权利要求的范围赋予最宽的解释, 以使其涵盖所有这些变型例以及等同的结构及功能。

图1

图2

图3

图4

图6

图7

图8

图9

图11

图12

图13

图14