(19) **日本国特許庁(JP)**

## (12) 特 許 公 報(B2)

(11)特許番号

特許第6393669号 (P6393669)

(45) 発行日 平成30年9月19日(2018.9.19)

(24) 登録日 平成30年8月31日 (2018.8.31)

(51) Int.Cl. F 1

**HO3M 1/60 (2006.01)** HO3M 1/60 **HO3M 1/36 (2006.01)** HO3M 1/36

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2015-183623 (P2015-183623)

(22) 出願日

平成27年9月17日 (2015. 9.17)

(65) 公開番号

特開2017-11667 (P2017-11667A)

(43) 公開日

平成29年1月12日 (2017.1.12)

審査請求日

平成27年9月17日 (2015.9.17)

(31) 優先権主張番号 10-2015-0088678

(32) 優先日 平成27年6月22日 (2015.6.22)

(33) 優先権主張国 韓国 (KR)

||(73)特許権者 515261756

エルセン ELSSEN

大韓民国 デジョン 34129, ユセオンーク, ガジェオンーロ, 218,

#11-203

#11-203, 218, Gajeong-ro, Yuseong-gu, Daejeon 34129, Repu

blic of Korea

(74)代理人 100130111

弁理士 新保 斉

(74)代理人 100174366

弁理士 相原 史郎

最終頁に続く

## (54) 【発明の名称】センサ装置及びセンシング方法

#### (57)【特許請求の範囲】

#### 【請求項1】

外部環境に応じて異なる電圧値を出力する測定電圧発生部(10)と、

入力された電圧値に比例する周期のパルスを発生させるパルス発生部(30)と、

前記パルス発生部(30)の出力を分周する分周部(40)と、

前記分周部40の出力パルスの長さをクロック単位で測定するカウンター部(50)と、を含み、

前記分周部(40)によって分周された後は、パルスの周期が所定倍に増加し、

前記分周部(40)の出力パルスから、パルス発生部(30)の出力のパルス幅以外のクロック遅延時間を含む遅延成分について、該遅延成分が所定倍された成分を除去する回路をさらに含むことを特徴とする、センサ装置。

【請求項2】

前記測定電圧発生部(10)の出力電圧値をサンプリングし、保持するS/H部(20)をさらに含むことを特徴とする、請求項1に記載のセンサ装置。

#### 【請求項3】

2個以上のS/H部(20)と、パルス発生部(30)と、分周部(40)と、カウンター部(50)と、を含み、

前記測定電圧発生部(10)は2個以上のS/H部(20)に連結され、それぞれのS/H部(20)の出力電圧は互いに異なるパルス発生部(30)、分周部(40)、カウンター部(50)に連結され、電圧測定の並列処理が可能であることを特徴とする、請求

20

項2に記載のセンサ装置。

## 【請求項4】

前記分周部(40)は、2<sup>n</sup>分周部(divider)であることを特徴とする、請求項1に記載のセンサ装置。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、センサ装置及びセンシング方法に関し、より詳細には、小型、高分解能のADCを含むセンサ装置及びセンシング方法に関する。

#### 【背景技術】

[0002]

様々な技術分野において様々なセンサ装置が使用されているが、センサ測定値をデジタル信号に変換するためには ADC (analog digital converter: A/Dコンバータ)が必要となる。

#### [0003]

従来のADC技術の一つであるパルス幅変換技術(パルス幅変換器を利用した方法)は、様々な利点があるが、チップに具現する際にパルス幅を大きくすることができず、分解能を高めることが困難である。すなわち、小型のチップに具現するためにはキャパシタの値が小さくなるが、パルス幅を大きくするために電流の充電される電流の大きさを過剰に小さくするとノイズに敏感になるため、電流の値を所定の値以下に小さくすることもできない。したがって、パルス幅を所定の値以上に増加させることができず、分解能も高めることが困難である。

#### 【先行技術文献】

## 【特許文献】

#### [0004]

【特許文献1】韓国公開特許公報2001 0101464号明細書

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

本発明は、上述の問題点を解決するために導き出されたものであり、本発明の目的は、 パルス幅変換技術を利用するADCを含むセンサ装置及びセンシング方法において、小型 の装置でも高い分解能を有するようにすることにある。

## 【課題を解決するための手段】

#### [0006]

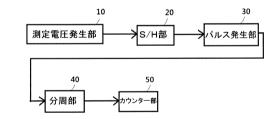

本発明のセンサ装置は、外部環境に応じて異なる電圧値を出力する測定電圧発生部 1 0 と、入力された電圧値に比例する周期のパルスを発生させるパルス発生部 3 0 と、前記パルス発生部 3 0 の出力を分周する分周部 4 0 と、前記分周部 4 0 の出力パルスの長さをクロック単位で測定するカウンター部 5 0 と、を含むことを特徴とする。

#### [0007]

前記センサ装置は、前記測定電圧発生部10の出力電圧値をサンプリングし、保持する 40 S / H 部20をさらに含むことを特徴とする。

## [ 0 0 0 8 ]

前記センサ装置は、2個以上のS/H部20と、パルス発生部30と、分周部40と、カウンター部50と、を含み、前記測定電圧発生部10は2個以上のS/H部20に連結され、それぞれのS/H部20の出力電圧は互いに異なるパルス発生部30、分周部40、カウンター部50に連結され、電圧測定の並列処理を可能にすることができる。

#### [0009]

前記パルス発生部 3 0 は、キャパシタと、電流源と、スイッチと、比較器と、を含むことができる。

## [0010]

50

10

20

前記センサ装置は、分周部40の出力パルスからパルス発生部30の出力のパルス幅以外の成分を除去する回路をさらに含むことができる。

#### [0011]

前記分周部40は、2<sup>n</sup>分周部(divider)であることができる。

#### [0012]

本発明のセンシング方法は、測定電圧発生部10と、パルス発生部30と、分周部40と、カウンター部50と、を含むセンサ装置を利用するセンシング方法であって、外部環境に応じて測定電圧発生部10が異なる電圧値を出力する第1段階と、パルス発生部30が、入力された電圧値に比例する周期のパルスを発生させる第3段階と、分周部40が、パルス発生部30の出力を分周する第4段階と、カウンター部50が、分周部40の出力パルスの長さをクロック単位で測定する第5段階と、を含むことを特徴とする。

[0013]

前記センシング方法は、第1段階と第3段階との間に、S/H部20が、測定電圧発生部10の出力電圧の特定の瞬間の電圧値を格納した後、出力する第2段階をさらに含むことができる。

[0014]

前記第4段階は、パルス発生部30の出力を2倍ずつ分周する過程をn回(nは、整数)繰り返すことを特徴とすることができる。

#### 【発明の効果】

[0015]

本発明によれば、パルス幅変換技術を利用するADCを含むセンサ装置は、小型の装置でありながらも高い分解能を有することにより、非常に小さい値の変化も測定することができる。

【図面の簡単な説明】

- [0016]

- 【図1】本発明に係るセンサ装置の概念図である。

- 【図2】S/H部の構成図である。

- 【図3】パルス発生部の実施例の構成図である。

- 【図4】分周部の実施例の構成図である。

- 【図5】図3と図4の回路における電圧グラフである。

- 【図6】図3と図4の変形実施例である。

- 【図7】図6の回路における電圧グラフである。

- 【図8】測定電圧発生部の出力電圧の例である。

- 【図9】並列高速変換回路の例である。

- 【発明を実施するための形態】

- [0017]

本発明は、様々な変更を加えることができ、様々な実施例を有することができるところ、特定の実施例を図面に例示し、詳細な説明に詳細に説明する。しかし、これは、本発明を特定の実施形態に対して限定するためではなく、本発明の思想及び技術範囲に含まれるすべての変換、均等物乃至代替物を含むものと理解すべきである。本発明を説明するにあたり、関連の公知技術に関する具体的な説明が本発明の要旨を不明にしうると判断した場合には、その詳細な説明を省略する。

[0018]

本出願で使用している用語は、単に特定の実施例を説明するために使用されたものであって、本発明を限定するためのものではない。単数の表現は、文脈上、明らかに異なっていない限り、複数の表現を含む。

[0019]

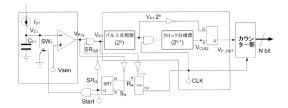

図1は本発明に係るセンサ装置の構成図である。

[0020]

本発明に係るセンサ装置は、測定電圧発生部10と、S/H部20と、パルス発生部3

20

10

30

40

10

20

30

40

50

0と、分周部40と、カウンター部50と、を含む。

#### [0021]

測定電圧発生部10は、外部環境に応じて異なる電圧値を出力する。

#### [0022]

S / H 部 2 0 は、測定電圧発生部の出力電圧値をサンプリングし、保持する役割をする

#### [0023]

パルス発生部30は、S/H部20の出力電圧値に比例する周期のパルスを発生させる

[0024]

分周部40は、パルス発生部30の出力を分周する役割をする。

[ 0 0 2 5 ]

カウンター部50は、分周部40の出力パルスの長さをクロック単位で測定する。

[0026]

この際、分周部40の分周比を増加させるほど分解能が向上する。

[0027]

測定電圧発生部 1 0 は、様々な形態に具現されることができる。従来のセンサにおいて多く用いられる方式は、外部環境(温度、湿度など)に応じて抵抗が変化する素子やキャパシタンスが変化する素子を利用するものである。抵抗が変化する素子に所定の電流を流すと、外部環境に応じて電圧が変化する。外部環境に応じてキャパシタンスが変化する素子に所定の電流を流すと、外部環境に応じて電圧の増加速度が変化する。外部環境に応じてキャパシタンスが変化する素子に所定の電圧を加えると、外部環境に応じて電流の量が変化し、抵抗を介してこの電流を流すと、抵抗にかかる電圧の大きさが変化する。

[0028]

外部環境に応じて出力電圧が変化するようにする技術は、従来、公知となっており、詳細な説明は省略する。

[0029]

外部環境に応じて出力電圧を変化するように、素子の出力は非常に弱いことが一般的であるため、増幅器を使用してもよい。増幅器は、設計上の必要に応じて様々な種類の増幅器(例えば、電圧 電圧増幅器、電流 電圧増幅器、電圧 電流増幅器など)から選択して使用することができる。当該増幅器は、外部環境による信号が小さいために使用するものであって、増幅器を使用しなくても相当大きい値を有する場合には増幅器を必要としない。

[0030]

また、測定電圧発生部10は、フィルター回路をさらに含んでもよく、外部環境による 信号にノイズがない場合にはフィルター回路を必要としない。

[0031]

従来のセンサにおいて測定電圧発生部10は、外部環境(温度、湿度など)に応じて抵抗が変化する素子やキャパシタンスが変化する素子を利用することが一般的であるが、そのような素子を利用することなく、外部環境の測定電圧値を発生させることもできる。例えば、心電図を測定する場合、心電図電圧が得られる点に電極さえ連結すれば測定電圧発生部10として動作することができる。このような場合、その信号が非常に小さいことがあるため、増幅器を含むことが好ましい。

[0032]

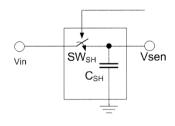

図2はS/H部の構成図である。

[0033]

S / H部 2 0 は、入力電圧をサンプリングし、保持するサンプルアンドホールド (Samp le & Hold) 回路である。

[0034]

S / H部 2 0 のスイッチ S W <sub>SH</sub>が閉じたときにはキャパシタンス C <sub>SH</sub>の電圧が入力電圧

10

20

30

40

50

Vinと一致するが、S/H部20のスイッチSW $_{SH}$ が開くと、キャパシタンスC $_{SH}$ の電圧は、スイッチSW $_{SH}$ が開く瞬間の値に保持される。

#### [0035]

このときの出力電圧は、周辺環境を測定した電圧値であるため、測定電圧(sensing voltage)という意味でその名称をVsenとすることができる。

#### [0036]

測定電圧発生部 1 0 の出力にはノイズがある可能性があるため、フィルター回路を設けることが好ましい。

#### [0037]

測定電圧発生部 1 0 と S / H 部 2 0 との間にノイズを除去するフィルター回路を設けて もよく、 S / H 部 2 0 とパルス発生部 3 0 との間にノイズを除去するフィルター回路を設 けてもよい。

#### [0038]

本発明のセンサ装置において、S/H部20の入力電圧が所定時間以上変化しない場合、S/H部20を除去してもよい。

#### [0039]

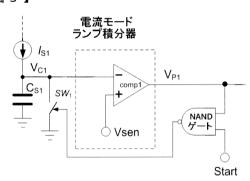

図3はパルス発生部の実施例の構成図である。

#### [0040]

#### [0041]

比較器 (comparator) comp1は、OPアンプに具現することができる。

#### [0042]

## [0043]

比較器 comp1 の出力と Start 信号が NAND が F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F の F F の F の F の F の F の F の F の F の F の F の F F の F の F の F の F の F の F の F の F の F の F

## [0044]

Start値がlow状態のときにはNANDゲートの出力値がhigh状態となりスイッチSW1が閉じるため、図3のパルス発生部は作動しない。

## [0045]

Start値がhigh状態に変化すると、NANDゲートの出力値がlow状態となりスイッチSW、が開く。

#### [0046]

スイッチ S  $W_1$ が開いている状態では、電流源 I  $_{S1}$ によりキャパシタ C  $_{S1}$ に蓄電される電荷量が増加し、キャパシタ C  $_{S1}$ に蓄電される電荷量が増加するにつれてキャパシタ C  $_{S1}$  の電圧 V  $_{C1}$  が増加する。

#### [0047]

$V_{C1}$ が増加して  $V_{S}$  e n より大きくなると、比較器 c o m p 1 の出力電圧  $V_{P1}$  は h i g h 状態から l o w 状態に反転する。

#### [0048]

$V_{P1}$ はhigh状態がlow状態になると、NANDゲート(NAND gate)の出力値がhigh状態となりスイッチSW $_1$ が閉じる。スイッチSW $_1$ が閉じると、キャパシタC $_{S1}$ の電圧 $V_{C1}$ はまた0となり、 $V_{P1}$ はlow状態からhigh状態に反転する。

#### [0049]

V<sub>P1</sub>はhigh状態になると、NANDゲート(NAND gate)の出力値が1o

w状態となりスイッチSW₁が開く。

## [0050]

すなわち、 $V_{P1}$ はlow状態とhigh状態を繰り返すことになるが、パルスの幅と周期はVsenの大きさに比例する。

## [0051]

図 3 におけるNANDゲートをANDゲート(AND gate)に変更し、ANDゲート出力値が high状態のときにスイッチSW $_1$ が開くように構成しても同様に動作する。

#### [0052]

NANDゲートの出力にはバッファーをさらに設けて、所定以上の遅延時間を有するようにすることが好ましい。

#### [0053]

図 3 では、比較器の + 入力に V s e n 値が入力されるが、比較器の - 入力に V s e n 値が入力されるように回路を変形してもよい。

#### [0054]

この際、V<sub>C1</sub>の値はランプ(ramp)状に増加するため、図3の回路(比較器を含む回路)は、電流モードランプ積分器(Current mode ramp integrator)と言える。

#### [0055]

$V_{P1}$ のパルス幅がVsenの大きさに比例するため、パルスの幅を測定すると、Vsenの大きさを知ることができる。

#### [0056]

万が一、パルスの幅がいくつのクロック周期と一致するかを判断する方法によりVsenの大きさを判断するとしたときに、Vsenの分解能を高めるためには、クロック周期に比べてパルスの幅が非常に大きいことが好ましい。

#### [0057]

しかし、クロック周期を減少させること、すなわちクロック周波数を増加させることに は限界がある。クロック周波数を過剰に高めると、電力消費が増加し、誤動作の恐れが増 加する問題点があるためである。

#### [0058]

また、 $V_{P1}$ のパルス幅を増加させるためには、キャパシタ $C_{S1}$ のキャパシタンスを増加させるか、電流源  $I_{S1}$ の電流値を減少させなければならないが、キャパシタンスを増加させるためにはキャパシタ $C_{S1}$ の大きさが増加して装置の小型化を図ることができず、電流源  $I_{S1}$ の電流値を減少させるとノイズに弱くなる問題がある。

## [0059]

このような問題を解決するために、本発明では、パルス発生部30の出力を分周部40に通過させてパルスの幅を増加させる。

## [0060]

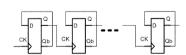

図4は分周部の実施例の構成図である。

#### [0061]

分周部40(divider)は、様々な方式で具現されることができ、図4の分周部では、 多数個のDフリップフロップが直列に連結されており、それぞれのDフリップフロップは 、出力Qbが入力Dに連結されており、入力CKの状態が2回変化する間に出力Qの状態 が1回変化する。

## [0062]

図4のDフリップフロップが直列にn個が連結されていると、入力の状態変化回数を2<sup>n</sup>倍だけ小さくなるように変更することから、2<sup>n</sup>分周部(divider)と称することができる。

## [0063]

本発明の分周部40(divider)は、入力の状態変化回数を所定の割合で減少させる回路であり、図4の形態以外にも設計上の必要に応じて様々な形態に変更されることができ

10

20

30

40

る。

#### [0064]

図4の分周部40は、2倍ずつ分周する回路を複数個直列に連結しているが、2倍ではなく整数倍(例えば、3倍や10倍など)に分周することも理論上可能である。しかし、2倍ずつ分周する場合、回路が単純で最も効率的であるため、図4のように2倍ずつ分周する回路を複数個直列に連結することが好ましい。

#### [0065]

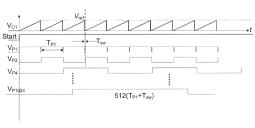

図5は図3と図4の回路における電圧グラフである。

#### [0066]

すなわち、図3の回路と図4の回路を連結したときに回路の様々な点の電圧値を比較したグラフである。

#### [0067]

$T_{P1}$ は、 $V_{P1}$ が h i g h 状態である間の時間であり、 $T_{SW}$ は、 $V_{P1}$ が l o w 状態である間の時間である。

#### [0068]

Start値がhigh状態に変化すると、 $V_{P1}$ は $T_{P1}$ のパルス幅と $T_{P1}$ + $T_{SW}$ の周期をもって規則的に変化する。

#### [0069]

$V_{P1}$ は $V_{ref}$ 値になるまで増加するが、図 3 において  $V_{ref}$ 値はV s e n 値と一致する。

#### [0070]

一般的に図 4 の D フリップフロップを通過する度にパルス幅と周期が 2 倍ずつ増加するため、  $V_{P1}$ が D フリップフロップを 1 個通過した後の値は、それぞれ、  $V_{P2}$ 、  $V_{P4}$ 、 ...、  $V_{P1024}$ のように称することができる。

#### [0071]

$V_{P1024}$ のパルス幅 5 1 2 (  $T_{P1}$  +  $T_{SW}$  ) は、パルス幅が広くて分解能が高く、 $V_{S}$  e n 値に比例して増加する値であるため、 $V_{P1024}$ のパルス幅がいくつのクロックに該当するかを判断すると、 $V_{S}$  e n 値が高い分解能に測定されることができる。

#### [0072]

カウンター部 5 0 は、分周部 4 0 の出力パルスの幅がいくつのクロックに該当するかを 判断する回路であり、様々な方法で具現されることができる。

#### [0073]

最も簡単な具現方法は、カウンティング回路(クロック入力が入力される度にNビットの出力値が1ずつ増加する回路)で分周部40の出力値をカウンティング回路のイネーブル入力として受け入れる方法である。このように回路を具現すると、分周部40の出力値がhigh状態のときにのみカウンティング回路が動作することから、分周部40の出力値のパルス幅がいくつのクロックに該当するかを測定することができる。このような方法を適用すると、測定しようとするパルスがhigh状態に変化するときにカウンティング回路の値を0に初期化する過程が必要である。

#### [0074]

カウンター部 5 0 の具体的な回路は、設計上の必要に応じて多様に変更されることがで 40 きる。

#### [0075]

また、図3と図4に図示された実施例は、不要な時間要素(スイッチング時間、クロック遅延時間)を計算し、分周部のパルス幅からその不要な時間要素を除去する形態に変更されて実施されることができる。

## [0076]

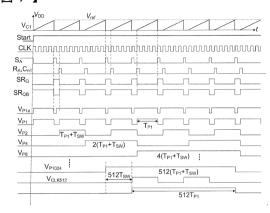

図6は図3と図4の変形実施例である。すなわち、図3の回路、図4の回路、カウンター部50が連結された回路を変形した例である。

#### [0077]

図7は図6の回路における電圧グラフである。

20

10

30

#### [0078]

図 6 の回路の利点は、出力電圧  $V_{P\#OUT}$ から  $T_{SW}$ が除去された 5 1 2  $T_{P1}$ のパルス幅を有することである。すなわち、最終パルス幅に含まれた不要な時間要素(スイッチング時間、クロック遅延時間)を除去する回路を挿入して、パルス発生部 3 0 で発生したパルスの幅を整数倍だけ正確に増幅して正確度を向上させることができる。

#### [0079]

したがって、図6の回路は、分周部40の出力パルスから「パルス発生部30の出力のパルス幅以外の成分」を除去する回路をさらに含むものと言える。この際、図6の回路のパルス発生部30は、S/H部20の出力電圧値に比例するパルス幅を有するパルスを周期的に発生させなければならない。

[0800]

カウンター部 5 0 でクロック単位で測定されたデジタル値は、メモリ素子(例えば、レジスター)に格納される。

[0081]

本発明のセンサ装置は、分解能を高める利点があるが、測定時間が増加する欠点がある。結果、時間の変化に伴う電圧の変化を正確に表現することができない欠点がある。

[0082]

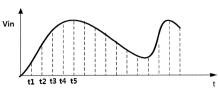

図8は測定電圧発生部の出力電圧の例である。

[0083]

測定電圧発生部 1 0 の出力電圧 V i n は時間の変化に伴い変化する。時間の変化に伴う電圧の変化を正確に測定するためには、短い時間の間隔で電圧を測定することが好ましいが、一つの時刻(例えば、t=t1)での電圧の測定が完了する前には、他の時刻(t=t2)での電圧の測定を開始できないという問題点がある。

[0084]

万が一、サンプリングした電圧値を並列に処理すると、このような問題点を解決することができる。

[0085]

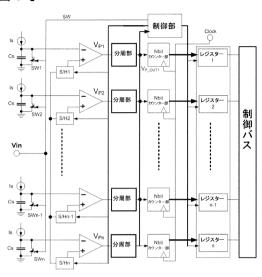

図9は並列高速変換回路の例である。

[0086]

図9の回路では、S/H部20、パルス発生部30、分周部40、カウンター部50が n個ずつ設けられていることから、1個ずつある場合よりn倍緻密な時間の間隔で電圧を 測定することができる。したがって、時間の変化に伴う電圧の変化を正確に表現すること ができる。

[0087]

換言すれば、本発明のセンサ装置では、2個以上のS/H部20と、パルス発生部30と、分周部40と、カウンター部50と、を含み、測定電圧発生部10は、2個以上のS/H部20に連結され、それぞれのS/H部20の出力電圧は、互いに異なるパルス発生部30、分周部40、カウンター部50に連結され、電圧測定の並列処理を可能にすることができる。

[0088]

本発明に係るセンシング方法は、測定電圧発生部 1 0 、 S / H 部 2 0 と、パルス発生部 3 0 と、分周部 4 0 と、カウンター部 5 0 と、を含むセンサ装置を利用するセンシング方法であって、以下の段階を含む。

[0089]

第1段階:外部環境に応じて測定電圧発生部10が異なる電圧値を出力する段階

[0090]

第2段階: S / H 部 2 0 が、測定電圧発生部 1 0 の出力電圧の特定の瞬間の電圧値を格納した後、出力する段階

[0091]

第3段階:パルス発生部30が、入力された電圧値に比例する周期のパルスを発生させ

10

20

30

40

#### る段階

#### [0092]

第4段階:分周部40が、パルス発生部30の出力を分周する段階

#### [0093]

第5段階:カウンター部50が、分周部40の出力パルスの長さをクロック単位で測定する段階

## [0094]

本発明のセンシング方法において、S/H部20の入力電圧が所定の時間以上の間に変化しない場合、第2段階を除去してもよい。

## [0095]

前記第5段階においてクロック単位で測定された値はデジタル値であって、メモリ素子 (例えば、レジスター)に格納されなければならないことから、本発明に係るセンシング方法は、以下の第6段階をさらに含んでもよい。

## [0096]

第6段階:レジスターがクロック単位で測定された値を格納する段階

## 【図1】

## 【図2】

## 【図3】

## 【図4】

## 【図5】

## 【図6】

# 【図8】

【図7】

【図9】

## フロントページの続き

(72)発明者 パク, ジ マン

大韓民国 デジョン 34021, ユセオンーク, ベウル 2-ロ, 3, #804-20

審査官 及川 尚人

(56)参考文献 特開平09-061487(JP,A) 特開昭59-128824(JP,A) 特開平10-188589(JP,A) 特開平07-177032(JP,A) 実開昭54-009651(JP,A) 特開2009-165064(JP,A) 特開2004-242283(JP,A) 特開平05-048461(JP,A) 特開平05-048461(JP,A) 特開2006-333203(JP,A)

(58)調査した分野(Int.CI., DB名) H03M 1/00-1/88