(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4756860号

(P4756860)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月10日(2011.6.10)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/76   | (2006.01) | HO1L 21/76 | M    |

| HO1L 21/331  | (2006.01) | HO1L 29/72 | P    |

| HO1L 29/732  | (2006.01) | HO1L 29/72 | Z    |

| HO1L 29/73   | (2006.01) | HO1L 21/76 | L    |

| HO1L 21/8228 | (2006.01) | HO1L 27/08 | 101C |

請求項の数 13 (全 45 頁) 最終頁に続く

(21) 出願番号 特願2004-529419 (P2004-529419)

(86) (22) 出願日 平成15年8月13日 (2003.8.13)

(65) 公表番号 特表2005-536060 (P2005-536060A)

(43) 公表日 平成17年11月24日 (2005.11.24)

(86) 國際出願番号 PCT/US2003/025516

(87) 國際公開番号 WO2004/017373

(87) 國際公開日 平成16年2月26日 (2004.2.26)

審査請求日 平成18年8月11日 (2006.8.11)

(31) 優先権主張番号 10/218,678

(32) 優先日 平成14年8月14日 (2002.8.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 505052191

アドバンスト・アナロジック・テクノロジーズ・インコーポレイテッド

ADVANCED ANALOGIC TECHNOLOGIES, INC.

アメリカ合衆国、95054 カリフォルニア州、サンタ・クララ、スコット・ブルバード、3230

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

最終頁に続く

(54) 【発明の名称】トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体構造であって、

半導体基板と、

前記基板の上に形成されるエピタキシャル層とを含み、前記エピタキシャル層は背景ドーピング濃度を有し、前記半導体構造はさらに、

第1および第2のトレンチを含み、前記第1および第2のトレンチは、前記第1のトレンチと前記第2のトレンチとの間にメサを規定するように前記エピタキシャル層の表面から下方に延在し、前記第1および第2のトレンチの各々の底部は前記エピタキシャル層に位置し、前記トレンチの各々は、実質的に誘電材料が充填されており、前記半導体構造はさらに、

前記第1のトレンチと前記第2のトレンチとの間の位置において、前記エピタキシャル層の前記表面から前記基板へと下方に延在するドーパントのウェルを含み、前記ウェルは、前記エピタキシャル層の前記背景ドーピング濃度とは異なるドーピング濃度を有し、前記ウェルは、前記エピタキシャル層の残りの部分と第1および第2の接合を形成し、前記第1の接合は、前記第1のトレンチの底部から前記基板に延在し、前記第2の接合は、前記第2のトレンチの底部から前記基板に延在し、

前記ウェルおよび前記第1および第2のトレンチは分離構造を構成し、前記分離構造は、前記分離構造の一方側の前記エピタキシャル層に形成された第1の素子と前記分離構造の他方側の前記エピタキシャル層に形成された第2の素子とを電気的に分離し、

10

20

前記分離構造による電気的分離は前記第1および第2のトレンチとP N接合とによってもたらされ、

前記基板および前記ウェルは第1の導電型の材料でドープされ、前記エピタキシャル層は、前記第1の導電型とは反対の第2の導電型の材料でドープされ、前記第1および第2の接合はP N接合である、半導体構造。

**【請求項2】**

前記ウェルが前記メサを占める、請求項1に記載の半導体構造。

**【請求項3】**

前記ウェルは前記第1の導電型の埋込層を含み、前記埋込層は、前記基板から上方に延在し、前記ウェルの残りの部分と融合する、請求項1に記載の半導体構造。

10

**【請求項4】**

前記埋込層は、前記第1および第2のトレンチの各々の前記底部のレベルよりも下の前記エピタキシャル層におけるレベルで前記ウェルの前記残りの部分と融合する、請求項3に記載の半導体構造。

**【請求項5】**

前記第1および第2のトレンチは、前記エピタキシャル層の厚さの10%～90%にまで延在する、請求項1に記載の半導体構造。

**【請求項6】**

前記第1および第2のトレンチは、前記エピタキシャル層の前記厚さの30%～70%にまで延在する、請求項5に記載の半導体構造。

20

**【請求項7】**

前記第1および第2のトレンチは、前記エピタキシャル層の前記厚さの半分まで延在する、請求項6に記載の半導体構造。

**【請求項8】**

前記誘電材料は酸化物を含む、請求項1に記載の半導体構造。

**【請求項9】**

前記誘電材料は窒化物を含む、請求項1に記載の半導体構造。

**【請求項10】**

前記第1および第2のトレンチは0.1μm～2μmの幅である、請求項1に記載の半導体構造。

30

**【請求項11】**

半導体構造を作製する方法であって、

第1の導電型の材料でドープされた半導体基板を設けるステップと、

前記基板の上に、前記第1の導電型とは反対の第2の導電型の材料でドープされ、かつ背景ドーピング濃度を有するエピタキシャル層を形成するステップと、

前記エピタキシャル層の表面から下方に延在するように第1および第2のトレンチを形成するステップとを備え、

前記第1および第2のトレンチは、前記第1および第2のトレンチの間にメサを規定するように、かつ前記第1および第2のトレンチの各々の底部が前記エピタキシャル層に位置するように形成され、さらに

40

前記第1および第2のトレンチに実質的に誘電材料を充填するステップと、

素子同士を互いに電気的に分離するウェルを形成するために、前記誘電材料を充填された前記第1および第2のトレンチ間ににおける前記メサに第1の導電型のドーパントを導入するステップとを備え、

前記ウェルは、前記エピタキシャル層の前記表面から前記基板へと下方に延在するように、かつ前記エピタキシャル層の前記背景ドーピング濃度とは異なるドーピング濃度を有するように、かつ前記エピタキシャル層の残りの部分と第1および第2の接合を形成するように形成され、

前記第1の接合は前記第1のトレンチの底部から前記基板に延在するように、前記第2の接合は前記第2のトレンチの底部から前記基板に延在するように形成され、

50

前記ウェルおよび前記第1および第2のトレンチは分離構造を構成し、前記分離構造は、前記分離構造の一方側の前記エピタキシャル層に形成された第1の素子と前記分離構造の他方側の前記エピタキシャル層に形成された第2の素子とを電気的に分離し、

前記分離構造による電気的分離は前記第1および第2のトレンチとP N接合とによってもたらされ、

前記第1および第2の接合はP N接合である、方法。

**【請求項12】**

前記エピタキシャル層において前記ドーパントを前記エピタキシャル層の前記表面から前記基板へと下方に拡散させるように前記基板を加熱するステップを含む、請求項11に記載の方法。

10

**【請求項13】**

前記基板から上方に延在するように埋込層を形成するステップをさらに備え、

前記ウェルは前記埋込層の上に形成され、さらに

前記基板を加熱して、前記埋込層を前記ウェルに達するまで上方に拡散させるステップを備えた、請求項11または12に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

発明の分野

この発明は、接合-分離型集積回路素子のための分離構造に関し、特に相補型アナログバイポーラ(CAB)トランジスタとこれを形成する方法とに関する。

20

**【背景技術】**

**【0002】**

発明の背景

集積回路の最小限のパターンサイズが小さくなると、集積回路(IIC)チップ上の素子の記録密度を高めることが必要になる。素子間の距離を同様に短くすることができなければ、より小さい素子の利点が大幅に損なわれる。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0003】**

30

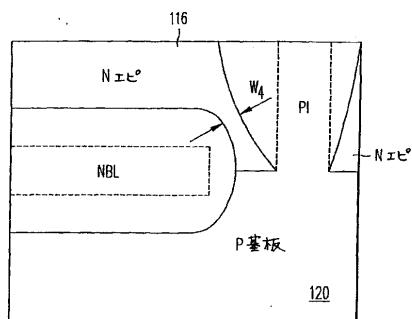

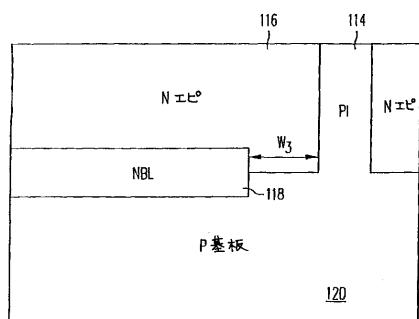

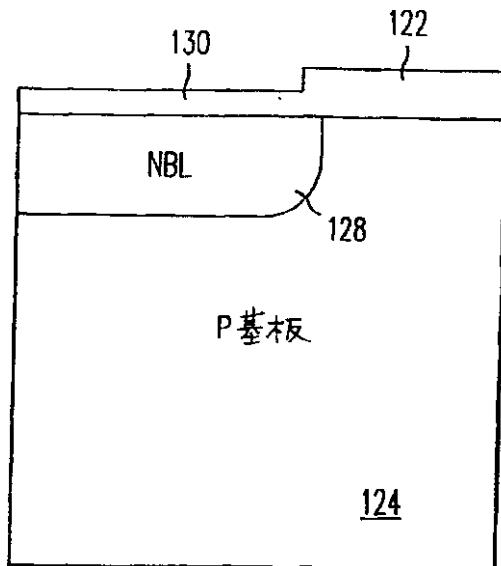

図1～図11は、先行技術のプロセスおよび構造、ならびにそれらのプロセスおよび構造に固有の問題のいくつかを示す。

**【0004】**

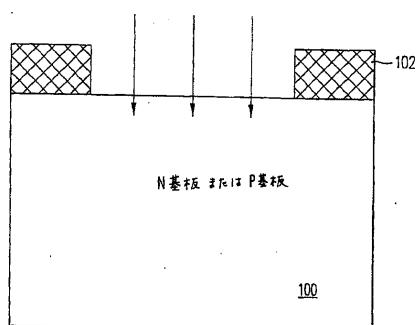

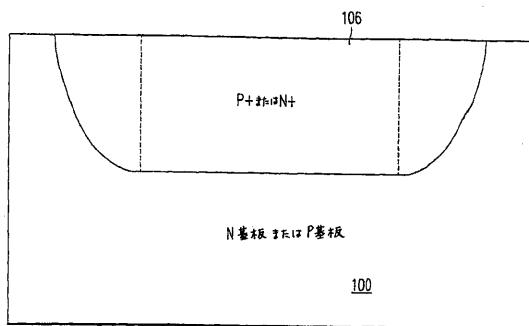

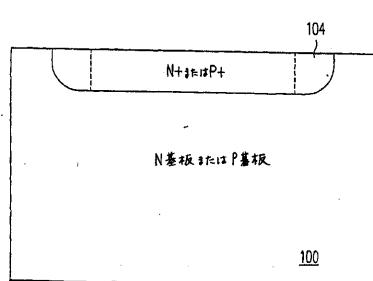

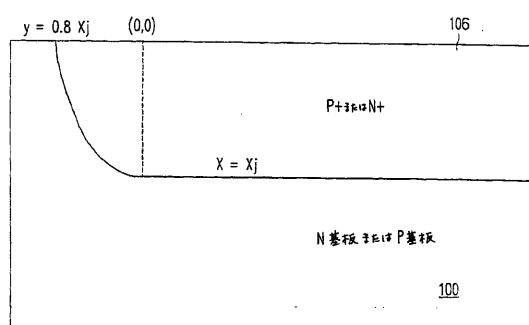

図1Aは半導体素子を作製する一般的な方法を示す。ドーパントは、酸化物、窒化物、フォトトレジストまたはそれらの何らかの組合せであり得るマスク層102に形成される開口部を通じてN基板またはP基板100に導入される。ドーパントはイオン注入または高温のプレデポジションによって導入され得る(すなわち、気体源または固体源からのドーピング源が半導体に導入されている浅い拡散)。次いで、図1Bに図示のとおり、浅い領域104を形成するよう加熱することによってドーパントが拡散され得るか、または図1Cに図示のとおり、はるかに深い領域106を形成するようより高温でまたはより長期間にわたってドーパントが拡散され得る。領域104は深さが0.5～2μmであってもよく、領域106は深さが2μm～10μmであってもよい。図1Dは領域106の左側を示し、熱拡散プロセス中の領域106の横方向の広がりを詳細に示す図である。示されるように、接合ドーパントは拡散中に横方向ならびに垂直方向に広がる。概して、マスク開口部のエッジにおけるポイント(0,0)からの横方向の広がりは、接合の垂直な深さ(x<sub>j</sub>)の約0.8倍に等しい。このドーパントの横方向の広がりにより、従来の熱拡散プロセスを用いて形成される水平方向の間隔と素子の記録密度とが制限される。

40

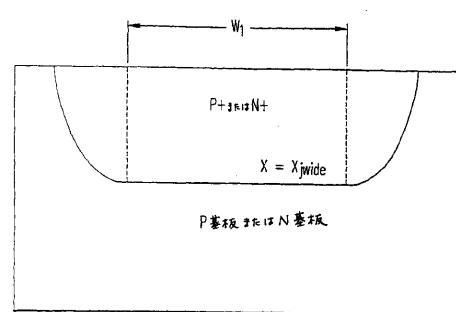

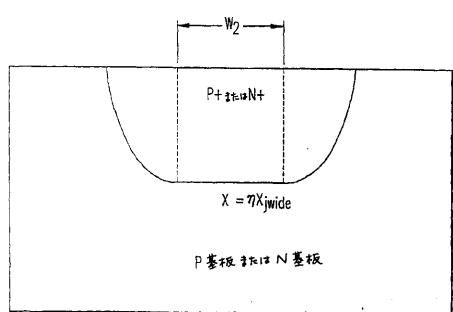

**【0005】**

図2Aおよび図2Bは、拡散プロセスにかかる別の問題、すなわち、接合の深さがマスク開口部の幅の関数であり得ることを示す。図2Aは、マスク開口部W<sub>1</sub>を介する注入

50

後に実行される拡散の結果を示し、図 2 B は、マスク開口部  $W_2$  を介する注入後に実行される拡散の結果を示すが、ここでは  $W_1 > W_2$  である。図 2 B における接合の最終的な深さは、1 未満である係数 だけ図 2 A における接合の深さよりも浅い。この現象が起こるのは、マスク開口部が比較的小さい場合のドーパントの横方向の広がりによって、マスク開口部が大きい場合よりも表面濃度と垂直方向へのドーピング濃度の勾配とが減じられるからである。こうして、マスク開口部が小さい場合にはドーパントがよりゆっくりと下方に拡散するが、この作用は「不十分な拡散 (starved diffusion)」と称される。したがって、マスク開口部は、たとえば厚い層に対する側壁分離領域を作るよう深い接合部を得るために比較的大きくなければならない。さらに、大きなマスク開口部が必要とされるために半導体素子の記録密度が制限される。

10

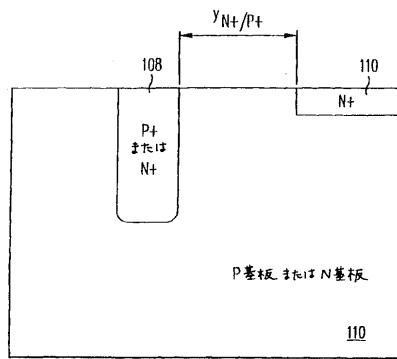

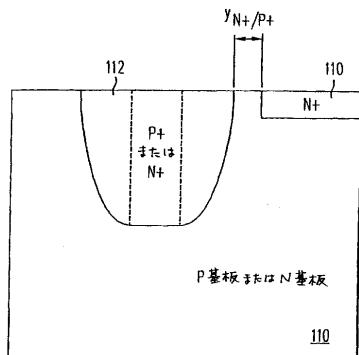

#### 【0006】

図 3 A および図 3 B はこれらの問題の影響のいくつかを例示する。理想的には、図 3 A に図示のとおり、浅い拡散領域 110 から距離  $Y_{N+/P+}$  だけ分離された深い拡散領域 108 が形成されることが望ましい。実際には、ドーパントが横方向に広がるために、図 3 A に示される形の深い拡散領域 108 は不可能である。代わりに、図 3 B に示されるはるかに幅の広い拡散領域 112 が結果としてもたらされるが、このはるかに幅の広い拡散領域 112 は、N+ 接合および P+ 接合の両方のマスク特徴間の間隔が同じであるにもかかわらず、拡散領域 110 からはるかに狭い距離  $Y_{N+/P+}$  だけ分離されている。

#### 【0007】

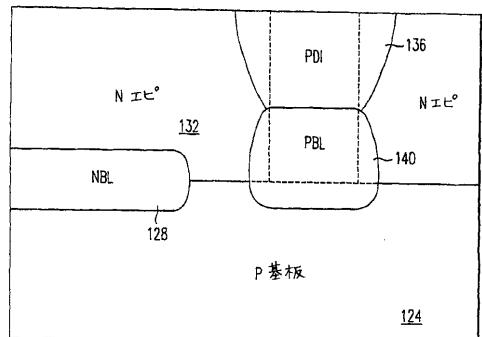

垂直な分離領域および埋込層を形成する際に類似の問題が生じる。図 4 A は、N エピ層 116 を通り P 基板 120 に延在する垂直な P 分離領域 114 を含む理想的な構造を示す。N 埋込層 (NBL) 118 は、N エピ層 116 と P 基板 120 との間の界面に形成される。P 分離領域 114 および N 埋込層 118 はともに、垂直なエッジを有し鋭く明確に規定された領域であり、距離  $W_3$  だけ分離されている。実際に従来の拡散プロセスで起こることが図 4 B に示される。N 埋込層 118 は N エピ層 116 の成長中および次の P 分離領域 114 のドライブイン中に水平に広がり、P 分離領域 114 が同様に横方向に広がって、N 埋込層 118 と P 分離領域 114 との間の分離を  $W_3$  よりもはるかに短い距離  $W_4$  に減らす。結果として、N 埋込層 118 と P 分離領域との間の破壊電圧が減じられることとなり、図 4 A に示される構造の破壊電圧を得るために N 埋込層 118 と P 分離領域 114 との間の分離を大きく広げなければならないだろう。

20

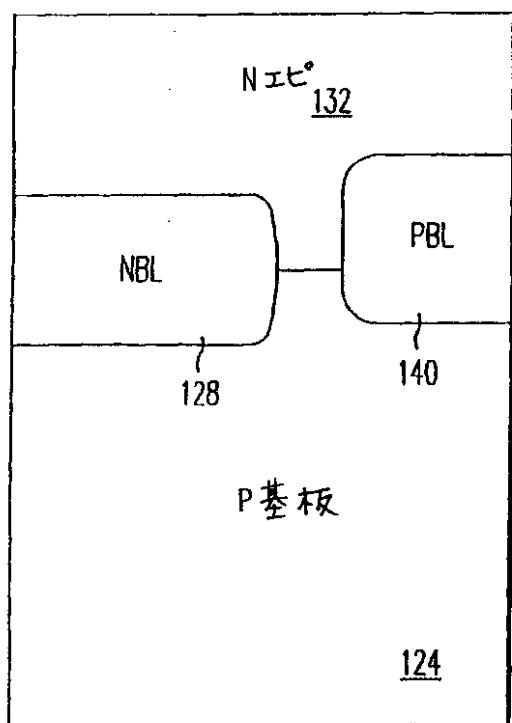

#### 【0008】

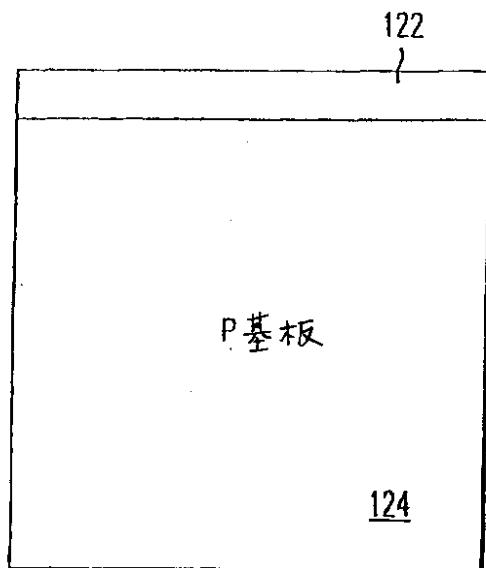

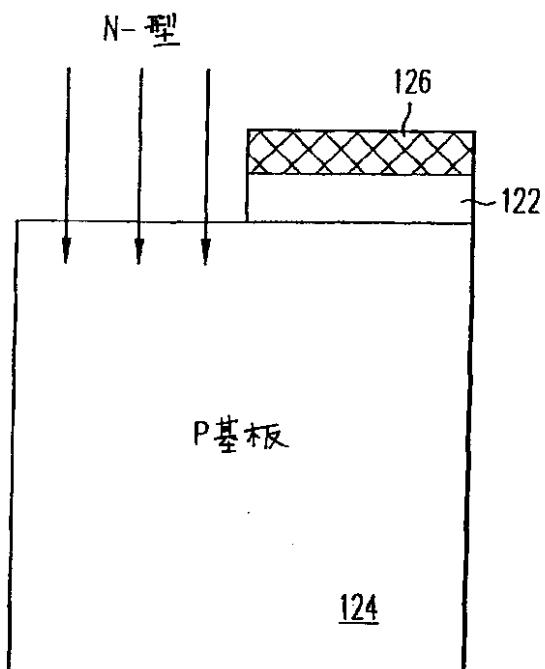

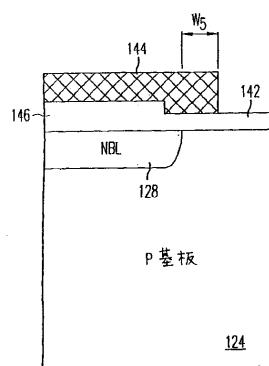

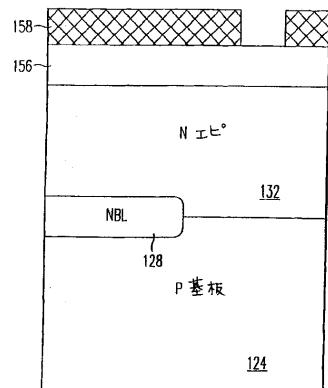

図 5 A ~ 図 5 F は従来のプロセスである接合 - 分離のステップ、すなわち上面から下方に延在する（「ダウンオンリー (down-only)」接合分離としても公知である）分離のステップを示す。図 5 A においては、厚い酸化層 122 (たとえば厚さ 1 ~ 5  $\mu\text{m}$ ) が P 基板 124 上に成長している。図 5 B においては、フォトレジスト層 126 が酸化層 122 の上に形成されており、酸化層 122 がフォトレジスト層 126 における開口部を通じてエッチングされている。薄い酸化層 130 が開口部に形成され、アンチモンまたはヒ素などの低速で拡散する N 型のドーパントが開口部を通じて注入されて、図 5 C に示される N 埋込層 128 を形成する。

30

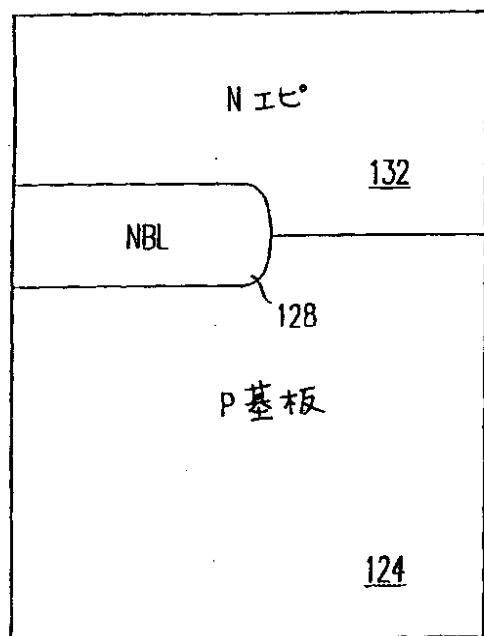

#### 【0009】

上に重なるエピタキシャル層のその後の成長に備えて、N 埋込層 128 におけるドーパントの表面濃度が減じられなければならない。これは、エピ層の成長中にエピタキシャルリニアクタへのドーパントの脱ガスを減ずるのに必要である。これを達成するために、N 埋込層 128 は、高温で長期間にわたって、たとえば 1100 ~ 1250 で 5 ~ 20 時間にわたってドライブされる。この熱処理の長さおよび温度が必要とされるのは、N 埋込層 128 を形成するのに用いられるドーパントが後の処理のために低速で拡散するので、これをエピタキシ前にシリコン表面から拡散させるのに必然的に高い温度と長い時間とを要するという事実による。

40

#### 【0010】

図 5 D は、P 基板 124 上の N エピ層 132 の成長後の構造を示す。示されるように、

50

N埋込層128はNエピ層132へと上方に拡散している。

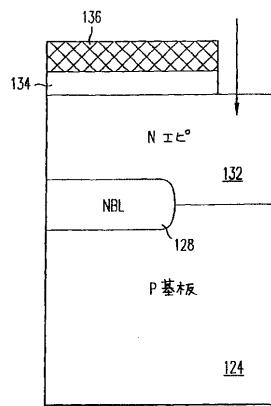

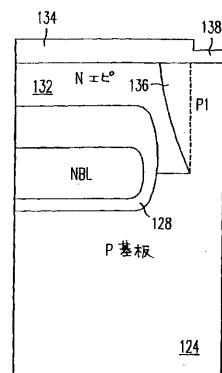

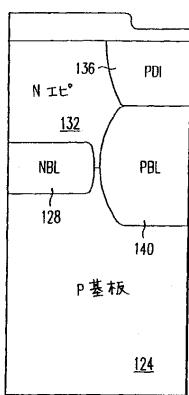

【0011】

図5Eに図示のとおり、酸化層134がNエピ層132の表面上に形成され、開口部が、フォトレジストマスク層136を用いて酸化層134にエッチングされる。ホウ素などのP型のドーパントが酸化層134における開口部を通じて注入されて、P分離領域136を形成する。次いで、構造全体が熱処理にさらされると、P分離領域136がNエピ層132を通じてP基板124へと下方に拡散させられ、同時に薄い酸化層138が形成される。N埋込層128は、この熱処理中に上方および横方向に拡散する。N埋込層128は、低速で拡散するドーパントで形成されているので、P分離領域136におけるホウ素よりも低速で拡散し、こうして、N埋込層128がP分離領域136から分離されたままとなる。それにもかかわらず、この分離を保証するために、Nエピ層132は、別の場合に所望されるよりも厚く作られなければならない。

【0012】

図6は、P分離領域136の真下にP埋込層140を形成することによってこの問題を緩和する方法を示す。P埋込層140は熱処理中に上方に拡散し、Nエピ層132の中間付近で下方に拡散するP分離領域136と接し、これにより、必要とされる熱処理量とN埋込層128の横方向の拡散とを減ずる。それにもかかわらず、このような横方向の拡散が起こり、これによってウェハの空間がさらに浪費される。

【0013】

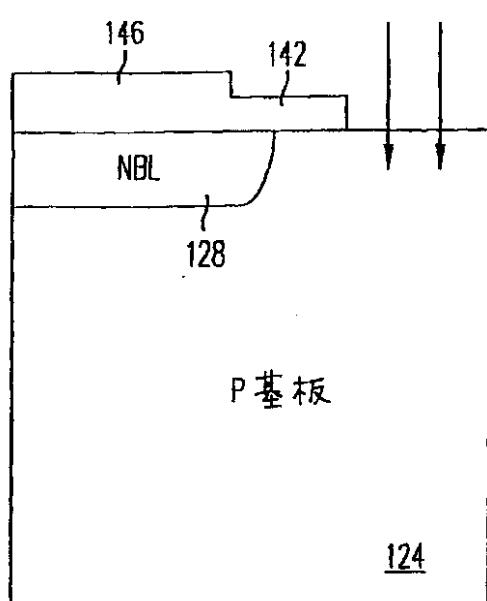

図7A～図7Fは図6の構造を形成するためのプロセスを示す。図7Aは、エピタキシャル層の成長前の表面のドーパント濃度を下げるようN埋込層128が注入および熱拡散された後の構造を示す。熱拡散プロセス中に厚い酸化層146が形成される。高濃度のヒ素を用いて埋込層を形成する場合には、NBLの上の酸化物は、より少量ドープされたP型の基板の上にわたって成長する部分よりもわずかに厚く成長し得る（「濃度の高い酸化」として知られる作用）。結果として、同じ酸化時間を有するにもかかわらず、酸化物146よりも厚さの薄い酸化層142を得ることができる。この現象はまた、アンチモンをドーパント種として用いると起こり得るが、この場合規模の縮小といった影響がある。フォトレジスト層144が酸化層142および146の上に堆積し、ホウ素イオンの注入のためにパターニングされてP埋込層140を形成する。フォトレジスト層144における開口部のエッジがN埋込層128のエッジから横方向に距離W<sub>5</sub>だけ間隔をあけて配置されることにより、N埋込層128およびP埋込層140が次の加熱処理中に融合しないことが確実にされる。

【0014】

図7Bに図示のとおり、酸化層142がフォトレジスト層144における開口部を通じてエッチングされ、ホウ素（または別のP型のドーパント）が開口部を通じて注入されてP埋込層140を形成する。その構造が再びアニールされてP埋込層140の表面濃度を下げる、図7Cに図示のとおり薄い酸化層148が形成される。

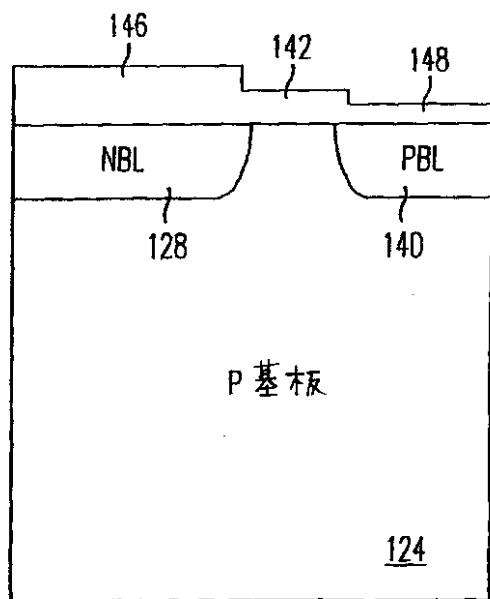

【0015】

次に、図7Dに図示のとおり、エピタキシャル堆積を用いてP基板124の上にNエピ層132を成長させる。通常、特にシリコンの堆積の場合には液相エピタキシよりも気相エピタキシャル（VPE）堆積が好ましい。しかしながら、VPEでは、典型的には1200を超える高温に基板を加熱する必要がある。Nエピ層132の成長中に、N埋込層128およびP埋込層140が垂直方向および横方向の両方向に広がって、これらの2つの埋込層間における分離を減らす。

【0016】

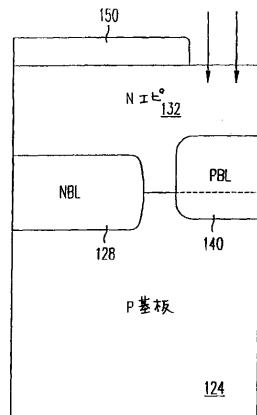

図7Eに図示のとおり、酸化層150がNエピ層132の表面上に形成される。酸化層150は一般的なフォトリソグラフィ技術を用いてパターニングされて開口部を形成し、この開口部を通じてホウ素が注入されてP分離領域136を形成する。図7Fに図示のとおり、次に当該構造を再度アニールすることにより、Nエピ層132内のどこかで融合するまでP埋込層140を上方に拡散させ、P分離領域136を下方に拡散させる。N埋込

10

20

30

40

50

層 1 2 8 および P 埋込層 1 4 0 は、それらの間の分離がかなり小さくなるまでこのアニール中に横方向に拡散する。図 7 A に示される分離  $W_5$  がないので、これらの 2 つの埋込層が実際に融合し、したがって、分離  $W_5$  は、要するに、最終的な構造において所要の破壊電圧を供給するために P 埋込層 1 4 0 が N 埋込層 1 2 8 から十分に間隔をあけられることを確実にするために受けなければならない「損失」である。

#### 【 0 0 1 7 】

明らかに分かるように、これは複雑で時間のかかるプロセスであり、特にウェハがより大きい場合にはウェハの反りを招き、歩留りを下げるおそれがある。分離拡散中の NBL の上方拡散によっても、Nエピ層 1 3 2 の「均一な」濃度部分が減じられて、上方拡散が起らなかった場合に必要とされるよりも厚いエピタキシャル層が必要となる。

10

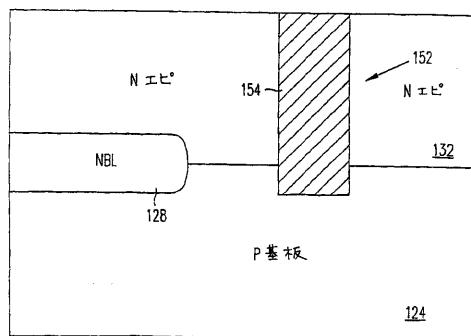

#### 【 0 0 1 8 】

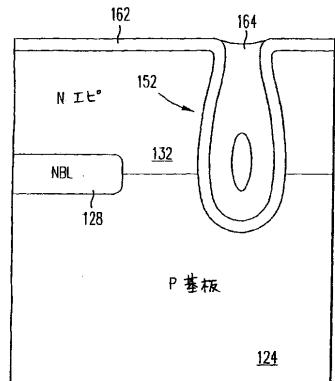

図 8 は、Nエピ層 1 3 2 の全体を貫通してトレンチ 1 5 2 をエッチングし、トレンチ 1 5 2 に誘導体 1 5 4 を充填することによってこの問題を回避する方法を示す。Nエピ層の厚さがたとえば 5  $\mu\text{m}$  ~ 20  $\mu\text{m}$  であり得るので、トレンチ 1 5 2 は Nエピ層 1 3 2 を通って全体に延在するよう非常に深くなければならないだろう。

#### 【 0 0 1 9 】

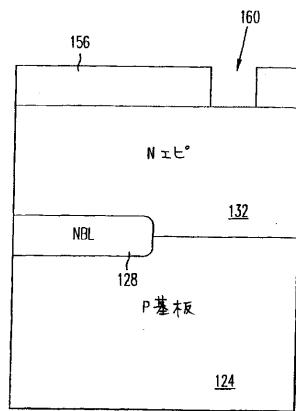

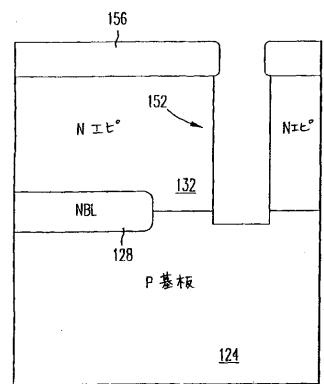

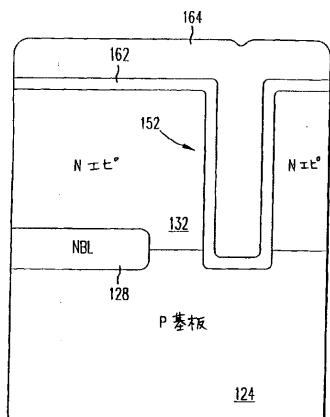

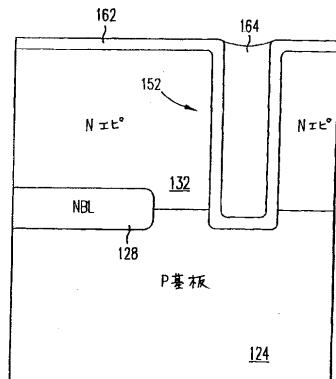

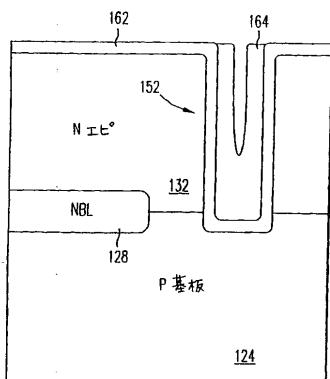

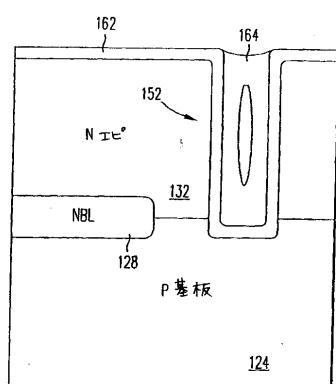

図 8 の構造を形成するためのプロセスが図 9 A ~ 図 9 F に示される。Nエピ層 1 3 2 が形成された後、図 9 A に図示のとおり、酸化物または他の硬質のマスク層 1 5 6 が Nエピ層 1 3 2 上に堆積し、フォトレジスト層 1 5 8 でパターニングされる。これにより、図 9 B に図示のとおり開口部 1 6 0 が層 1 5 6 に形成され、図 9 C に図示のとおりトレンチ 1 5 2 が Nエピ層 1 3 2 を通じてエッチングされる。これは典型的には反応性イオンエッチング (RIE) によってなされる。

20

#### 【 0 0 2 0 】

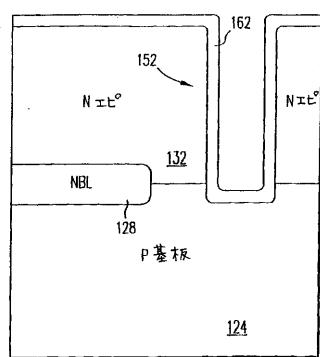

トレンチ 1 5 2 が形成された後、硬質のマスク層 1 5 6 が除去され、犠牲酸化層 (図示せず) がトレンチ 1 5 2 において成長して、RIE プロセスによってもたらされる結晶の損傷を修復する。犠牲酸化層が除去されると、図 9 D に図示のとおり、別の酸化層 1 6 2 がトレンチ 1 5 2 の壁と Nエピ層 1 3 2 の上面に成長する。トレンチ 1 5 2 は、図 9 E に図示のとおり、Nエピ層 1 3 2 の上面を部分的に覆う誘電材料 1 6 4 が充填され、誘電材料 1 6 4 は、図 9 F に図示のとおり、誘電材料 1 6 4 の上面が酸化層 1 6 2 の上面と同じ高さになるように平坦化される。

30

#### 【 0 0 2 1 】

トレンチ 1 5 2 がこのプロセス中に著しく広がったり拡散したりせず、エピタキシャル層への PN 接合を形成しないので、トレンチ 1 5 2 は、図 7 C に示される段階ではたとえば P 埋込層 1 4 0 よりも N 埋込層 1 2 8 の近くに位置し得る。それにもかかわらず、このプロセスはいくつかの問題およびリスクを有する。トレンチ 1 5 2 は、非常に深い可能性があるので充填するのが難しいかもしれない。図 10 A に図示のとおりトレンチが十分に充填されていない場合、図 10 A に示されるようにトレンチ自体に対してコンフォーマルに誘電材料 1 6 4 の上面から下方に延在する狭い空隙が残されるか、または、図 10 B に示されるように狭いボイドがトレンチに残される可能性がある。トレンチが狭い口を有する場合、図 10 C に図示のとおりボイドが底部分に残される可能性があるか、または、RIE が幅広の口を備えたトレンチをさほど異方的に形成していない場合、図 10 D に図示のとおり、誘電体 1 6 4 がエッチバック中にトレンチの内部から除去されてトレンチの底部にほんのわずかな部分しか残らない可能性がある。要するに、深いトレンチ分離および補充は大量生産するには依然として困難なプロセスである。

40

#### 【 0 0 2 2 】

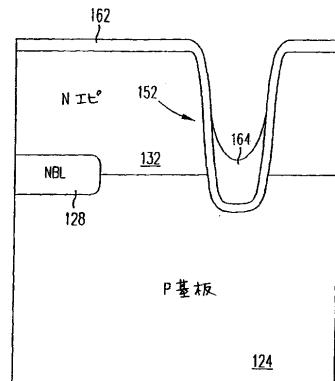

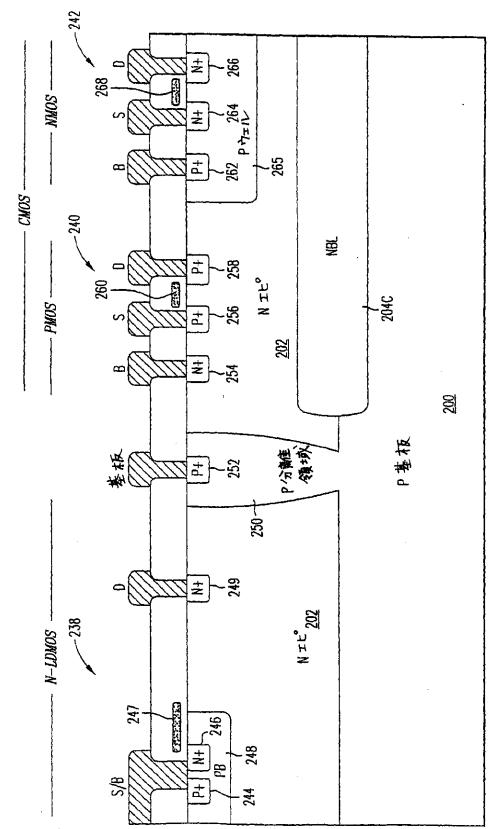

図 11 A ~ 図 11 E は、先行技術の拡散技術を用いて形成されるいくつかの半導体素子を示す。

#### 【 0 0 2 3 】

図 11 A は、P 基板 2 0 0 上に成長した Nエピ層 2 0 2 において形成される NPNトランジスタ 2 3 4 と PNPトランジスタ 2 3 6 とを示す。NPNトランジスタのエミッタは

50

N+領域208であり、ベースはP+領域（ベースコンタクトまたは外部ベース）210と専用のP-ベース領域（アクティブトランジスタまたは真性ベース領域）206とを含み、コレクタはN+領域212（コレクタコンタクト領域）と、Nエピ層202の一部分（コレクタ）と、N埋込層204A（いわゆるサブコレクタ領域）とを含む。N埋込層204はP基板200からトランジスタ234を分離し、コレクタの抵抗を下げる。

【0024】

PNPトランジスタ236においては、エミッタはP+領域226であり、ベースはN+外部ベースコンタクト領域224と専用の真性ベース領域222とを含み、コレクタはP+コレクタコンタクト領域228とP-ウェル220とP埋込層サブコレクタ218とを含む。PNPトランジスタ236はN埋込層204BによってP基板200から分離される。N埋込層（NBL）204BおよびP埋込層（PBL）218はNエピ層202とP基板200との界面で形成される。N埋込層204Bは、アンチモンまたはヒ素などの比較的低速で拡散するドーパントで形成され得、P埋込層218はホウ素などの急速に拡散するドーパントで形成され得る。結果として、P埋込層218がN埋込層204Bの上に延在し、場合によってはNBLの上と下の両方に延在し得る。

10

【0025】

PNPトランジスタ234は、Nエピ層202の表面からP基板200に延在するP分離領域214によってPNPトランジスタ236から分離される。P分離領域214はまた、P+コンタクト領域216を通じてP基板200の電位を設定する手段を提供し、しばしば、最も負であるオンチップの電位または接地でバイアスがかけられている。PNPトランジスタ236におけるNエピ層202の部分の電位は、N+コンタクト領域230を通じて設定され得るが、この場合、NBL204Bは、P基板200に等しいかまたはP基板200よりも正の電位で、かつPBL218に等しいかまたはPBL218よりも正の電位でバイアスがかけられなくてはならない。一般的な実施例は、しばしば、正の供給レール（たとえばVcc）でNBLにバイアスをかけるか、またはPBL218およびNBL204Bと同じ電位（0のバイアスがかけられた接合）に短絡させることを必要とする。

20

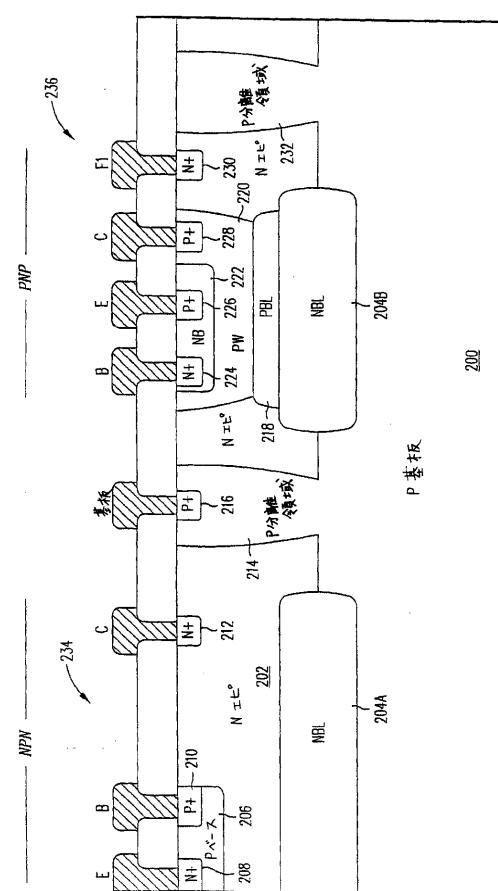

【0026】

図11Bは、（LDMOSFETとしても公知である）ラテラル二重拡散型NチャネルMOSFET238と、PMOSFET240およびNMOSFET242を含む分離されたCMOSの対とを示す。また、素子がNエピ層202に形成されている。NチャネルLDMOSFET238においては、ソースはN+領域246であり、ボディはP+コンタクト領域244および専用のP-ボディ拡散領域248（またはP-ウェル265）を含み、ドレインは、わずかにドープされたドレイン拡張部としての役割を果たすN+領域249とNエピ層202の一部分とである。P-ボディ（またはPウェル）248のチャネル部分はゲート247の下にあり、MOSFETのしきい値電圧を設定し、（P-ボディからN-エピ接合への空乏化の大部分を素子のエピタキシャルドレイン側に拡散することにより）ソースとドレインとの間のパンチスルーブレーキングを防ぐ。チャネル長がゲート領域の長さによって決定される従来のMOSFETとは異なり、この素子においては、表面に沿った、すなわち横方向のボディ248とソース246との接合深さの差によってLDMOSFETのチャネル長が設定される。自己整合的なタイプの素子においては、P-ボディ248は素子のゲート電極が形成された後に注入され、その後、接合が長期間にわたり高温で（たとえば1100度4時間）拡散されて、十分な接合深さとチャネル長とを達成する。ソースおよびボディ接合がともにゲートの後に形成されるので、素子は自己整合する。より低コストのタイプのLDMOSFETにおいては、（CMOSにおいて用いられる）P-ウェル拡散領域265が素子のボディとして用いられる。当該ウェルは、ゲートに先立って形成されるのでゲートと自己整合せず、マスクアライメントに依存してパンチスルーよびしきい値電圧を生成する。N+領域からチャネルを分離するNエピ層202の一部分は、それがP-ボディ領域248および分離拡散領域250の両方から十分に間隔を空けられているのであれば、素子の破壊電位を上昇させる。

30

40

50

## 【0027】

PMOSFET 240においては、ソースはP+領域256であり、ボディはN+コンタクト領域254とNエピ層202の一部分とを含み、ドレインはP+領域258である。Nエピ層202のチャネル部分はゲート260の下にある。NMOSFET 242においては、ソースはN+領域264であり、ボディはP+コンタクト領域262とPウェル265とを含み、ドレインはN+領域266である。Pウェル265のチャネル部分はゲート268の下にある。CMOSの対とわずかにドープされたドレインNMOSFET 238とはP分離領域250によって互いから分離される。P分離領域250とP+コンタクト領域252とを通じてP基板200への接触がもたらされる。NBL 204はP基板200からP-ウェル265を分離する。

10

## 【0028】

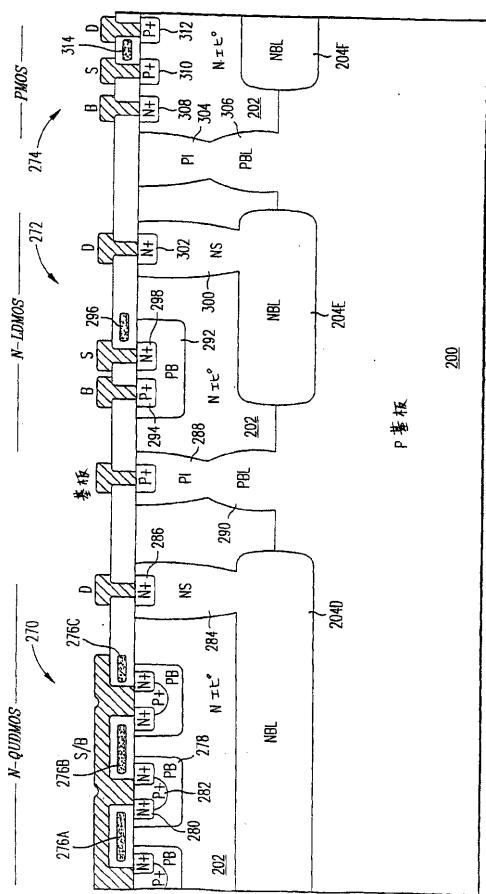

図11Cは、Nチャネルの準垂直なDMOSFET 270と、別の変形例であるNチャネルのラテラルDMOSFET 272と、完全に分離されたPMOSFET 274とを示す。準垂直なDMOSFET 270はゲート276A、276Bおよび276Cと接するセルのマトリクスとして構築される。DMOSFET 270の各セルは、ソースとして機能するN+領域280、ならびに、ともにボディとして機能するP+領域282およびPボディ278を含む。ソースおよびボディは一緒に短絡される。電流はソースからゲート276A、276B、276Cの下のチャネルを通り、Nエピ層202を通り、N埋込層204Dまで下がり、次にNシンカ284とN+領域286とを通って上り、ドレイン端子へと流れる（従って、学術用語である準垂直となる）。DMOSFET 270は、素子の抵抗を下げるN埋込層204DによってP基板200から分離される。

20

## 【0029】

NチャネルのラテラルDMOSFET 272は、ソースとして機能するN+領域298、ならびに、ともにボディとして機能するP+領域294およびP-ボディ292を含む。電流は、N+領域298から、ゲート296の下にあるチャネルを通り、N埋込層204Eまで下がり、Nエピ層202の表面に沿って進み、Nシンカ300とN+領域302とを通って上り、ドレイン端末に流れる。NチャネルLDMOSFET 272は、N埋込層204EによってP基板200から分離され、P分離領域288およびP埋込層290によってDMOSFET 270から分離される。

30

## 【0030】

分離されたPMOSFET 274は、ソースとして機能するP+領域310と、ドレインとして機能するP+領域312とを含む。ボディはNエピ層202の一部分であり、N+コンタクト領域308と接触する。電流は、P+領域310から、ゲート314の下にあるチャネルを通ってP+領域312に流れる。PMOSFET 274は、N埋込層204FによってP基板200から分離され、P分離領域304およびP埋込層306によってNMOSFET 272から分離される。

## 【0031】

図11Dは、NチャネルのラテラルDMOSFETの変形例308と、ラテラルNMOSFET 310と、垂直なPNPバイポーラトランジスタ312とを示す。NチャネルのLDMOSFET 308は、ゲート314がフィールド酸化層の上にわたって形成され、わずかにドープされたNMOSFET 308がN埋込層204GによってP基板200から分離されることを除いては、（類似の構成要素が同様に番号付けされている）図11Bに示されるNMOSFET 238に類似している。NチャネルのラテラルDMOSFET 310は、NMOSFET 310がN埋込層204を含まないことを除いては、図11Bに示されるNチャネルのLDMOSFET 242に類似している。

40

## 【0032】

垂直なPNPトランジスタ312においては、P+領域314がエミッタとしての役割を果たし、N-ベース316とN+領域318とNエピ層202の一部分とがベースとしての役割を果たし、P埋込層320とPシンカ322とがコレクタとしての役割を果たす。PNPトランジスタ312はN埋込層204HによってP基板200から分離される。

50

## 【0033】

NチャネルのラテラルDMOSFET308はP分離拡散領域324およびP埋込層326によってラテラルNMOSFET310から分離され、ラテラルNMOSFET310はPシンカ328およびP埋込層330によって垂直なPNPバイポーラトランジスタ312から分離される。

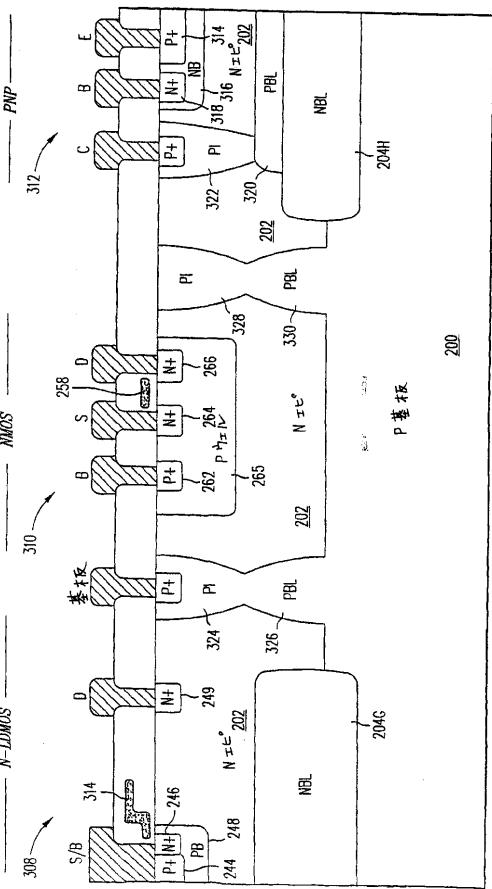

## 【0034】

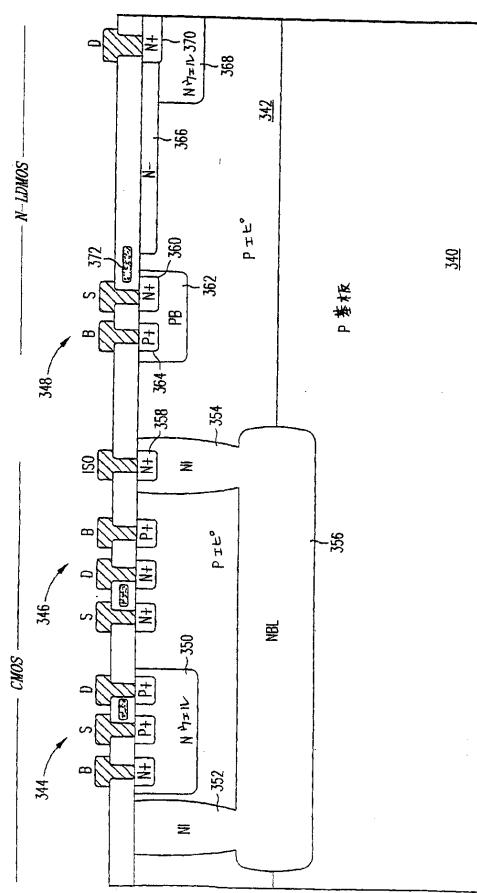

図11Eは、P基板340上に成長したPエピ層342に形成される素子を示す。CMOSの対はPMOSFET344およびNMOSFET346を含む。PMOSFET344およびNMOSFET346は、PMOSFET344がNウェル350に形成され、NMOSFET346がPエピ層342に形成される点を除いては、図11Bに示されるPMOSFET240およびNMOSFET242に類似している。PMOSFET344およびNMOSFET346は、N埋込層356ならびにN分離拡散領域(NI)352および354を含む分離構造によってP基板340から分離される。分離構造のバイアスはN+領域358を介して設定することができ、しばしば、CMOS素子に電力を供給する最も正の供給電圧でバイアスがかけられる。

## 【0035】

NチャネルのわずかにドープされたラテラルDMOSFET348はソースとしてN+領域360を含み、ボディとしてP+領域364とP-ボディ362とPエピ層342の一部分とを含み、ドレインとしてわずかにドープされたN-ドレイン領域366とNウェル368とN+領域370とを含む。チャネルが、ゲート372下のPウェル362およびPエピ層342に形成される。NMOSFET348はP基板340から分離されない。

## 【0036】

図11A～図11Eに示される素子の一般的な特徴は、それらの素子が概してエピ層を通じて接続するために長期にわたる熱拡散を必要とすることである。これらの接続は、分離領域を形成するか、または素子の一体型の構成要素として機能する埋込層に接続することを必要とする可能性がある。高い破壊電圧を供給するには、概して、より厚いエピ層とより長い熱処理とが必要である。熱処理はすべて、上方から注入される分離領域と下方から上方に拡散する埋込層との両方において横方向ならびに縦方向のドーパントの拡散をもたらす。この横方向のドーパントの拡散により、これらの先行技術のプロセスで達成可能な間隔と記録密度とが制限される。

## 【0037】

こうして、素子自体のパターンサイズが減じられると、これに応じてウェハの表面上に素子をより高密度に実装することを可能にするプロセスが必要とされる。

## 【課題を解決するための手段】

## 【0038】

## 発明の概要

この発明に従うと、熱拡散プロセス中のドーパントの横方向の拡散は、(拡散前に)拡散の一つの側またはいくつかの側にトレンチを形成し、トレンチに酸化物または他の誘電材料を充填することによって制限される。好ましくは、ドーパントの横方向の拡散は、ドーパントの2つまたはそれ以上の側上、特にプロセスにおいてより深く拡散した接合上にトレンチを形成することによっていくつかの方向に制限される。

## 【0039】

概して、拡散を制限するトレンチは、拡散領域のうち大部分が多量にドープされた表面部分がトレンチによって制限されるのに十分な深さを有し、当該トレンチの深さは好ましくは最終的な接合の深さの少なくとも15～20%である。場合によっては、トレンチは拡散全体を制限する。すなわちトレンチは最終的な接合深さよりも深い。トレンチは、たとえば0.5μm～5μmの範囲の深さであってもよいが、典型的にはトレンチの深さは1μm～3μmの範囲であるだろう。好ましい一実施例においては、トレンチは、拡散領域のうちより多量にドープされた部分を制限するのに十分に深く、容易に充填および平坦

化されるように十分に浅い。

【0040】

エピタキシャル層を含む実施例においては、トレンチはエピタキシャル層に延在するが、エピタキシャル層を通りその下にある基板にまでは延在しない。好ましい一実施例においては、素子は深い接合分離によって分離されており、この場合、分離する接合の実質的な部分は誘電体が充填されたトレンチによって制限されている。他の実施例においては、上方に拡散する埋込層は、トレンチによって制限されて下方に拡散する拡散領域を部分的に覆って分離構造を完成させる。

【0041】

このプロセスは、エピタキシャル層において比較的高電圧の素子を構築するのに特に有用である。たとえば確実な動作のために定格で20Vの動作電圧とされるバイポーラトランジスタ素子は典型的には60V～70Vの範囲の破壊電圧を必要とするだろう。これは、素子を基板または互いから電気的に分離するために、比較的厚いエピタキシャル層とエピタキシャル層を通って延在する深い拡散領域とを必要とする。この分離は逆バイアスがかかったPN接合によってもたらされる。従来の技術においては、これらの深い拡散領域は実質的な熱収支（温度と時間との積）を必要とし、これにより拡散領域が横方向に広げられ、素子の寸法が大きくなり、ウェハの所与の区域に配置することのできる素子の数が制限される。

【0042】

この発明の原理を用いると拡散領域の横方向の広がりが制限される。というのも、トレンチ内における誘電材料中のドーパントの拡散率が、典型的には、半導体基板またはエピタキシャル層におけるドーパントの拡散率よりも低いからである。さらに、トレンチの誘電体に拡散した後のドーパントは電気的に活性ではなく、隣接する接合または素子の接合破壊に悪影響または影響を及ぼさない。さらに、反対の導電性をもつドーパントがトレンチの下の領域において互いに接触したとしても、典型的には、この場所における拡散領域のドーピング濃度は、PN接合の破壊電圧が比較的高くなるように十分に低い。こうして、この発明を用いることにより記録密度をより高めることが可能となり、ウェハ上の利用可能な空間がはるかに効率的に用いられる。たとえば、素子は、数十ミクロンではなくわずかに1ミクロンしか間隔があけられないかもしれない。

【0043】

この発明の原理は、分離の目的で用いられる拡散領域または領域だけでなく、埋込層または基板への電気的接続をもたらすのに用いられる「シンカ」拡散領域にも適用される。このようなシンカ拡散領域は、拡散領域自体と同じ導電型または拡散領域自体とは反対の導電型の材料において形成され得る。分離しかもたらさない（製造するのが困難な）従来の深いトレンチ酸化分離とは異なり、トレンチにより制限された拡散は、製造し易いプロセスを用いてウェハの上面からシリコン内の接合深さまでの低抵抗の電気コンタクトを設けることができる。（というのも、困難なトレンチ充填および平坦化の工程を必要としないからである。）

この発明の別の局面に従うと、誘電体が充填されたトレンチがエピタキシャル層または基板の表面から埋もれた領域へと延在する。この埋もれた領域は、エピタキシャル層と比較的高いエネルギーで基板にドーパントを注入することによって形成される深い領域の基板との間の界面において形成される埋込層であってもよい。

【発明を実施するための最良の形態】

【0044】

発明の説明

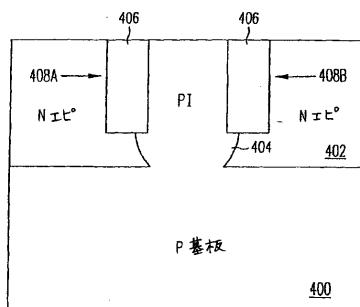

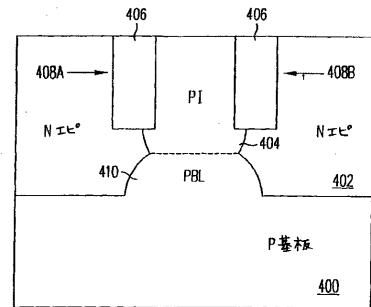

図12は、この発明の構造およびプロセスの基本的な例を示す。Nエピ層402はP基板400上に成長し、ホウ素などのP型のドーパントがNエピ層402の上面を通じて注入されてP分離領域404を形成する。トレンチ408Aおよび408BはP領域404の両側のNエピ層402に形成されている。トレンチ408Aおよび408Bは、酸化物、窒化物または異なる種類の誘電体でできた多重層であり得る誘電材料406が充填される

10

20

30

40

50

。

## 【0045】

熱処理中に、分離領域404におけるP型のドーパントが下方向に拡散すると、トレンチ408Aおよび408Bが横方向に広がるドーパントに対する障壁としての役割を果たす。ドーパントの拡散率は、概して、Nエピ層402におけるよりも誘電材料406における方が低い。これによりドーパントの横方向の拡散が制限される。さらに、トレンチ408Aと408Bとの間ににおいて結果として得られる高濃度のP型のドーパントは、ドーパント濃度の勾配を垂直方向に上げる傾向があり、これは、トレンチが存在しなかった場合よりも迅速にドーパントを下方向に拡散させる傾向がある。こうして、所与の拡散の深さを達成するのに熱処理はさほど必要とされない。

10

## 【0046】

分離拡散を実行するのに必要とされる時間を短縮することに加えて、当該方法は、不十分な拡散（所与の拡散時間にわたる予想されるよりも不所望に浅い接合につながる作用）の制限を被ることなくより狭い分離のパターンサイズを用いることを可能にする。後にトレンチにより制限された拡散を用いて不十分な拡散が始まる。というのも、より低い拡散速度により表面濃度が横方向に維持され、垂直な勾配がより高く維持されて、垂直な拡散がより急速に進むこととなる。当然、接合の底部がトレンチの底部に到達した後に速度が低下するが、いずれにしてもその時までに拡散速度は既に実質的に遅くなっている。

## 【0047】

上述のプロセスにおいては、ドーパントは、 $5 \text{ E } 12 \text{ cm}^{-2} \sim 5 \text{ E } 15 \text{ cm}^{-2}$ （しかし、より典型的には $2 \text{ E } 13 \text{ cm}^{-2} \sim 2 \text{ E } 14 \text{ cm}^{-2}$ ）の範囲であり得る注入ドーズ量を含むたとえば $140 \text{ keV}$ 未満の従来の低エネルギー注入を用いて表面付近に導入されるか、または（気体または固体のドーパント源が存在する場合に高温拡散からドープされた）プレデポジションによって形成される。拡散前の接合深さは一般に $0.5 \mu\text{m}$ 未満である。

20

## 【0048】

代替的には、注入は、いかなる高温拡散時間よりも前に、たとえばそのピーク濃度をシリコン内の $0.5 \sim 2.0 \mu\text{m}$ にして、より深く最初に形成され得る。より深い注入では、その目標とされた十分な深さに到達するのに拡散時間が短くて済むが、高エネルギー（すなわち100万ボルト）のイオン注入を用いる必要がある。注入エネルギーが $300 \text{ keV}$ から $3 \text{ MeV}$ までの範囲であり、高い製造スループットを達成するのに概して $1 \text{ MeV} \sim 2 \text{ MeV}$ の注入が好ましい。従って、他の区域からの注入を遮るのに必要なフォトレジストの厚さを典型的には $2 \sim 4 \mu\text{m}$ の厚さに増やさなければならない。

30

## 【0049】

分離拡散領域は通常、分離されているエピタキシャル層よりも深く、かつ、概してエピ層の厚さのバリエーションが不完全な分離につながらない（すなわち、イオン注入が基板を部分的に覆わない）ことを保証するエピ深さの120%以上の接合深さにまで実施される必要がある。 $4 \mu\text{m}$ の層については、 $4.8 \mu\text{m} \sim 5.2 \mu\text{m}$ の拡散深さが一般的である。このような拡散は、拡散炉に損傷を与えたリウェハに反りを生じさせたりせずに拡散速度を最高にするために、1050 ~ 1200、しかしそれより好ましくは1100 ~ 1150で実行され得る。

40

## 【0050】

図示される例においては、トレンチ深さは典型的にはエピの厚さの大体半分、たとえば $2 \mu\text{m}$ 、典型的には分離されている層の深さの30% ~ 70%にエッチングされ得るが、これはエピ層の10% ~ 90%であってもよい。トレンチが $5 \mu\text{m}$ よりも深いと充填および平坦化するのが徐々に難しくなる。

## 【0051】

トレンチ幅は $0.1 \mu\text{m} \sim 2 \mu\text{m}$ の範囲であってもよく、約 $0.5 \sim 1 \mu\text{m}$ のトレンチ寸法が好ましい。トレンチ間のメサは幅が $0.5 \mu\text{m} \sim 10 \mu\text{m}$ であってもよく、 $1.5 \sim 5 \mu\text{m}$ の幅が好ましい。トレンチは1つの側だけで、好ましくは2つの側で（縞または輪として）拡散領域を制限し得るが、ベイはまた、3つの側もしくは4つの側で拡散領域

50

を制限し得るかまたはすべての側で（同心状に）拡散領域を完全に囲み得る。

【0052】

代替的な発明においては、トレンチはまた、拡散後または一部の拡散後にエッチングおよび充填され得るが、その際に、当該プロセスはドーパントの横方向の拡散を制御する利点をいくらか失う。トレンチのエッチング前に拡散することにより、トレンチの位置は、領域404のより広範な横方向の拡散を交差するようより幅広に間隔があけられなければならない。このような方法は、狭いが深い接合を形成する利点をなくす。

【0053】

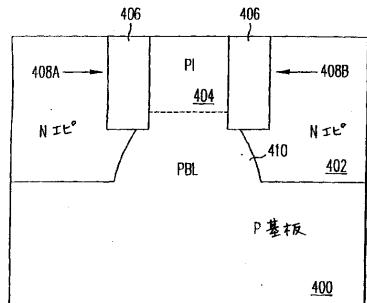

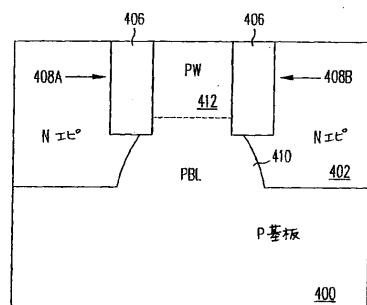

注入部分よりも下方に埋込層を形成する代替例がある。図13Aにおいては、たとえばP埋込層410はP分離領域404の下に形成されている。P型の分離柱については、P型の埋込層はホウ素（または注入されたアルミニウム）を含み得、エピタキシャル成長の前に $1E12\text{ cm}^{-2}$ ~ $4E14\text{ cm}^{-2}$ のドーズ量で、ただし好ましくは $2E13\text{ cm}^{-2}$ ~ $2E14\text{ cm}^{-2}$ のドーズ量で、さらに典型的には $120\text{ keV}$ 未満、たとえば $80\text{ keV}$ （ただし場合によっては $300\text{ keV}$ の高さ）のエネルギーで導入される。熱処理中に、P埋込層410は、トレンチ408Aおよび408Bの底部よりも下の（破線で示された）位置において下方に拡散するP分離領域404と融合するまで上方に拡散する。図13Bは、P分離領域404とP埋込層410との融合がトレンチ408Aと408Bとの間のメサにおいて起こる実施例を示す。図13Cは、P領域が、分離領域ではなく、Nエピ層402の表面とP基板400との間に接続を形成するのに用いられるPウェル412である実施例を示す。Pウェル412は、概して類似の分離拡散領域よりも低い濃度および低い注入ドーズ量を有し、しばしばウェル内部にNPNバイポーラトランジスタまたはPMOSなどの素子を組込むのに十分に低い表面濃度を有する。 $1E12\text{ cm}^{-2}$ ~ $5E13\text{ cm}^{-2}$ の注入ドーズ量が一般にウェル形成において用いられるが、分離注入のために報告されている注入エネルギーの可能な範囲は同じである。ウェルにおけるドーピング濃度が概して分離領域におけるドーピング濃度よりも低いので、ウェル拡散は、目標とされる深さに到達するのに $20\%$ ~ $60\%$ 長い拡散時間（または同等の温度・時間）を必要とするかもしれない。

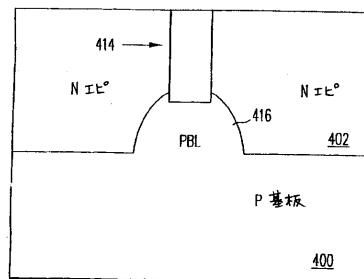

【0054】

図13Dは、単一のトレンチ414が用いられ、P埋込層416がトレンチ414と部分的に重なるまで上方に拡散される変形例を示す。この変形例が選択される場合、P埋込層416が実際にトレンチ414と部分的に重なるようにトレンチ414が十分に深くなりかつP埋込層416が十分に上方に拡散することを確実にするよう注意が払わなければならない。同様に、この変形例は単独では、トレンチにより制限された接合分離形態がもたらすようには基板とウェハの上側との間に電気接続をもたらさない。

【0055】

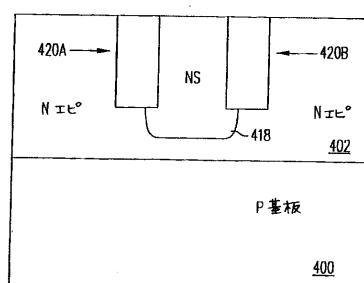

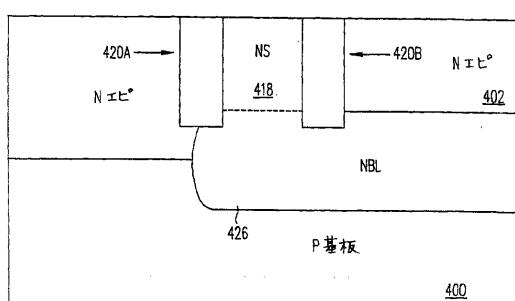

図14に図示のとおり、この発明の技術はまた、シンカ領域と同じ導電型のエピ層にシンカ領域を形成するのに用いることができる。Nシンカ418は、Nシンカ418の横方向の広がりを制限するトレンチ420Aと420Bとの間に下方向に注入および拡散されている。ドーパントはリンであってもよい。その注入特性および注入ドーズ量の範囲は、リンの注入がホウ素の注入と同じ深さに到達するのに $2.5$ ~ $3$ 倍のエネルギーを必要とする除いては、P型（ホウ素）の注入の特性およびドーズ量の範囲に類似している。拡散率もホウ素に類似しているが、特定の事例を計算するのに正確な条件が考慮されなければならない。リンの注入を用いてドーパントを浅い接合として導入する（が、接合の深さを決定しない）場合、 $60\text{ keV}$ ~ $120\text{ keV}$ の注入エネルギーが一般的であり、典型的な値は $90\text{ keV}$ である。

【0056】

完璧には、図14におけるNシンカ418の深さは、（図12のP分離拡散領域404の場合と同様に）P-N接合の深さではない。拡散されたN型の領域がN型のエピタキシャル層にP-N接合を形成しないので、「接合」は仮想の接合であり、濃度が異なる2つの接触するかまたは部分的に重なるN型の領域間における接合である。典型的には、 $10$

10

20

30

40

50

~15%の濃度の変化は仮想の接合と考えられてもよい。

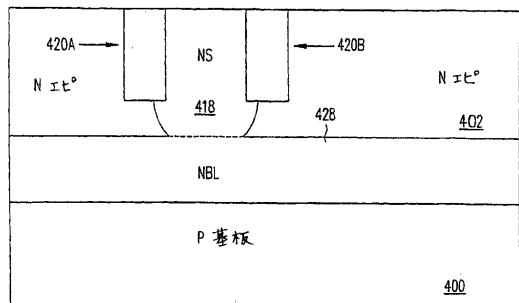

【0057】

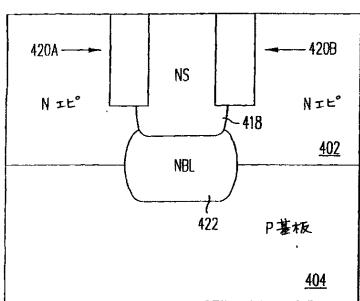

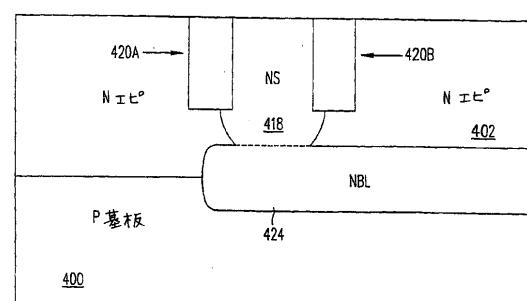

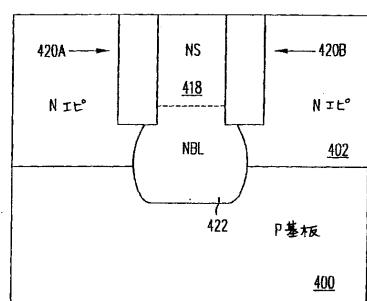

図15Aおよび図15Bは図13Aおよび図13Bにそれぞれ匹敵し、N埋込層422が上方に拡散し得、トレンチ420Aおよびトレンチ420B(図15A)の底部よりも下で、またはトレンチ420Aと420B(図15B)と間のメサにおいてNシンカ418と融合し得ることを示す。図15Cおよび図15Dは、N埋込層がNシンカの真下の区域に制限される必要はないが1つまたはいくつかの方向に横方向に延在し得ることを示す。図15CのN埋込層424は、トレンチ420Aおよび420Bの底部よりも下でNシンカ418と融合し、図15DのN埋込層426はトレンチ420Aと420Bとの間にあるメサにおいてNシンカ418と融合する。図15Eは、2つ(またはそれ以上)の方向に横方向に延在しNシンカ418と融合するN埋込層428を示す。N埋込層422、424、426および428bは、60keV~180keVで、1E12cm<sup>-2</sup>~5E15cm<sup>-2</sup>(但し典型的には5E14cm<sup>-2</sup>~3E15cm<sup>-2</sup>)のドーズ量で注入されるヒ素、アンチモンまたはリンであり得る。N埋込層は、エピタキシ中の脱ガスおよび横方向のオートドーピングを防ぐためにエピタキシャル成長前に拡散されなければならない。先行技術の埋込層の形成に特有の上述の先行技術の拡散サイクルは、エピタキシャル成長の準備をするのに適用可能でありかつ十分である。N埋込層424、426および428は、より一般的には、エピタキシャルの厚さ402の「平坦なゾーン」の上方拡散と損失とを防ぐためにヒ素またはアンチモンなどの低速で拡散するドーパントを含む。

【0058】

N埋込層422、424、426または428はまた、(たとえば5E15cm<sup>-2</sup>を超える)はるかに高いドーズ量で注入され得るが、エピタキシャル成長中に結晶欠陥および積層欠陥の形成を除去するために高温でアニールされなければならない。

【0059】

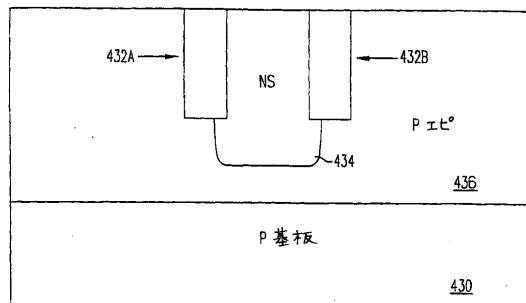

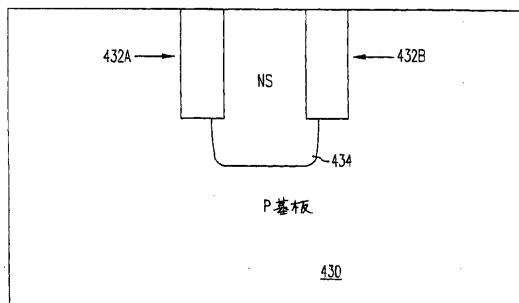

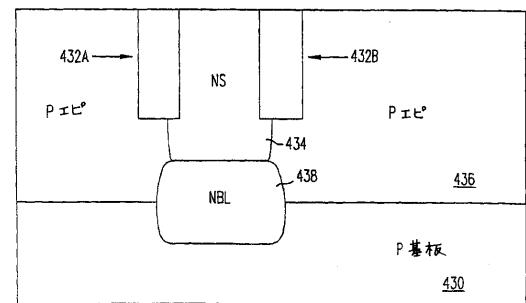

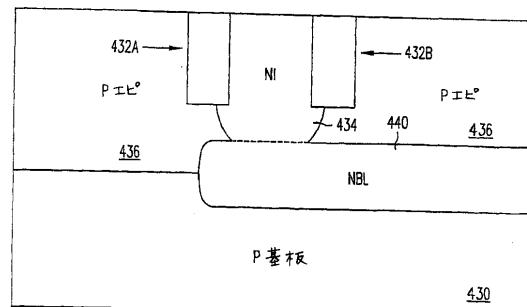

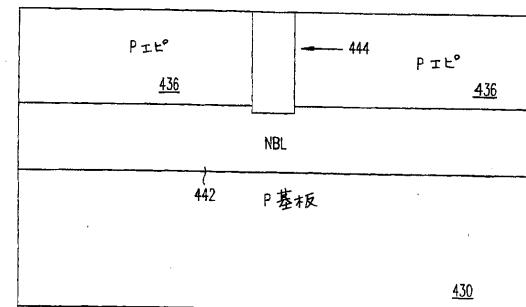

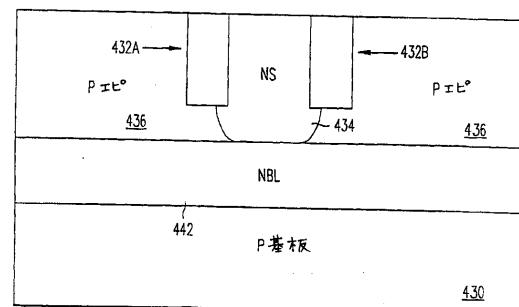

図16Aは、P基板430におけるトレンチ432Aと432Bとの間にNシンカ434を含む実施例を示す。その形成は、それがN型のエピタキシャル層ではなくP型の材料において形成される点を除いては、図14のNシンカ418に類似している。図16Bは、トレンチ432Aおよび432BならびにNシンカ434がP基板430ではなくPエピ層436に形成される点を除いては図16Aに類似している。図16Cは図16Bに類似しているが、P埋込層438と融合するNシンカ434を示し、当該P埋込層438は、P基板430とPエピ層436との間の界面において形成され、Nシンカ434と融合するよう上方に拡散している。図16Dは、横方向に一方向に延在するN埋込層440と融合し、トレンチ432Bの右側にPエピ層436の部分を囲む広角の分離構造を形成するNシンカ434を示す。図16Eは、図16Dに示されるのと類似の構造を示すが、N埋込層442は、Pエピ層436内にいくつかの分離されたポケットを作り出すために2(またはそれ以上の)次元に延在する。

【0060】

図17においては、Pエピ層436の分離されたポケットは、N埋込層442が誘電体が充填されたトレンチ444を部分的に覆うまでN埋込層を上方に拡散させることによって形成される。

【0061】

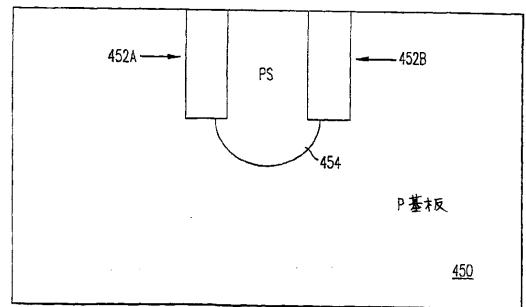

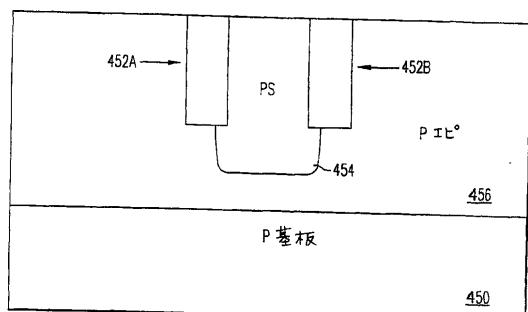

図18は、P基板450におけるトレンチ452Aと452Bとの間にPシンカ454を含む実施例を示す。この実施例は、PシンカがP型の材料またはエピに形成されているが、P型およびN型の領域がすべて交換される点を除いては、図14に示されるNエピ層におけるNシンカの構成に類似している。図19は、トレンチ452Aおよび452BならびにPシンカ454が、P基板450ではなくPエピ層456に形成される点を除いては、図18に類似している。

【0062】

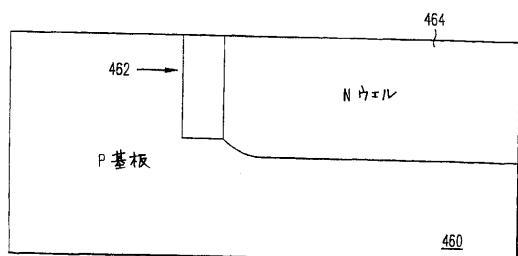

図20は、P基板460に形成される誘電体が充填された単一のトレンチ462とP基板460に拡散したNウェル464とを示し、当該トレンチ462は、Nウェル464が

10

20

30

40

50

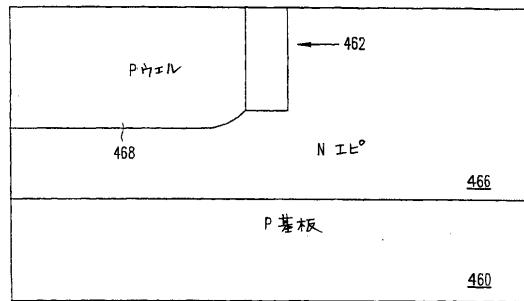

トレンチ462の左側に位置するP基板460の一部に拡散するのを防ぐ。図21は、P基板460の上に成長したNエピ層466に形成されたトレンチ462を示し、当該トレンチ462は、Pウェル468がトレンチ462の右側に位置するNエピ層466の一部に拡散するのを防ぐ。いずれの場合も、この構造は2つの利点を提供する。すなわち、この構造は、ドーピング濃度が高い場合に表面にPN接合が形成されるのを防ぎ、ウェルエッジにおける横方向の拡散を最小限にする。ウェルエッジにおいて拡散がいくらか向上し、接合深さが増大し得ることに留意されたい。

#### 【0063】

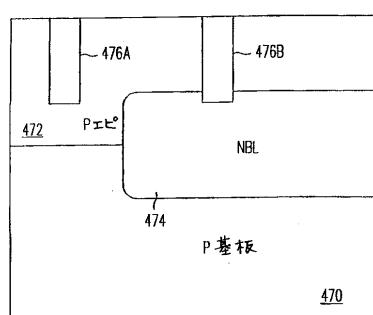

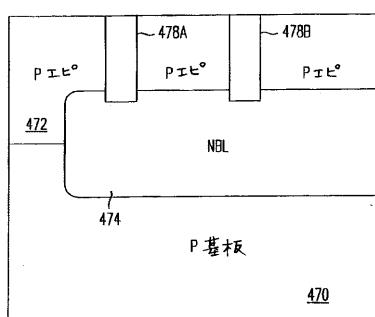

図22Aおよび図22Bは、Pエピ層472に形成されるトレンチがいかにN埋込層474とともに用いられてPエピ層472の分離されたポケットを形成し得るかを示す。図22Aにおいては、トレンチ476BだけがN埋込層474に延在し、トレンチ476Aは延在しない。図22Bにおいては、トレンチ478Aおよび478BがともにN埋込層474に延在する。いずれの場合も、同じトレンチを用いて、トレンチにより制限された拡散領域を分離、ウェルまたはシンカ領域として形成することができる。

#### 【0064】

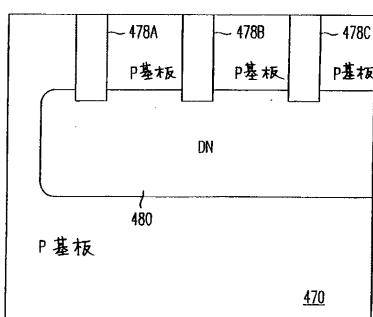

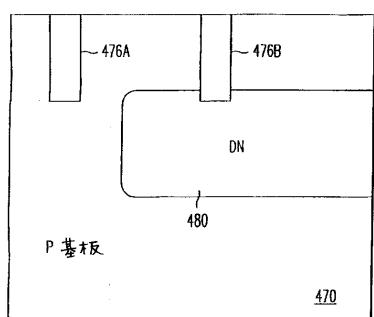

図23Aおよび図23Bは、ここではP基板470とPエピ層472との界面における拡散領域によって形成されるN埋込層ではなく、本願とともに共同出願され引用により全体がこの明細書中に援用される出願番号[代理人整理番号第AAT011 US]により詳細に記載されるように、N-ドーパントをP基板470に注入することによって深いN領域480が形成される点を除いては、図22Aおよび図22Bに類似している。図23Aにおいては、トレンチ476Bだけが深いN領域480に延在し、トレンチ476Aは延在しない。図23Bにおいては、トレンチ478A、478Bおよび478Cはすべて深いN領域480に延在する。当該トレンチはまた、トレンチにより制限された拡散領域をシンカ、分離またはウェルとして形成するのに用いられてもよい。

#### 【0065】

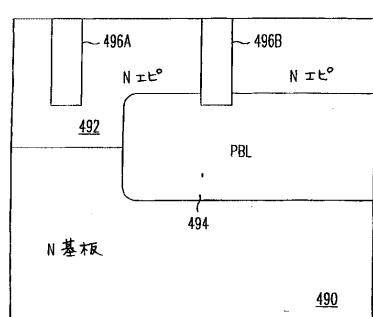

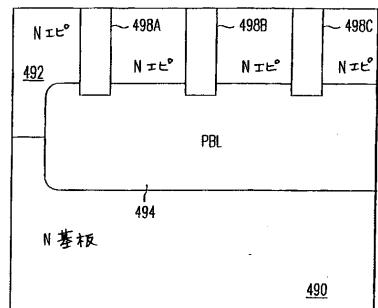

図24Aおよび図24Bは、Nエピ層492に形成されるトレンチがいかにP埋込層494とともに用いられてNエピ層492の分離されたポケットを形成し得るかを示す。図24Aにおいては、トレンチ496BだけがP埋込層494に延在し、トレンチ496Aは延在しない。図24Bにおいては、トレンチ498A、498Bおよび498CはすべてP埋込層494に延在する。当該トレンチはまた、トレンチにより制限された拡散領域をシンカ、分離またはウェルとして形成するのに用いられてもよい。

#### 【0066】

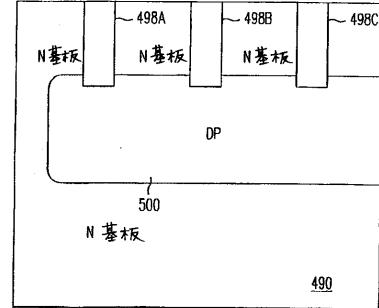

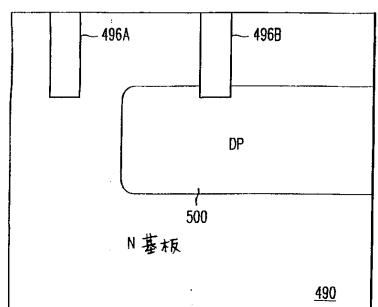

図25Aおよび図25Bは、ここでは、N基板490とNエピ層492との界面における拡散領域によって形成されるP埋込層ではなく、上述の出願番号[代理人整理番号第AAT011 US]に記載されるように、PドーパントをN基板490に注入することによって深いP領域500が形成される点を除いては、図24Aおよび図24Bに類似している。図25Aにおいては、トレンチ496Bだけが深いP領域500に延在し、トレンチ496Aは延在しない。図25Bにおいては、トレンチ498A、498Bおよび498Cはすべて深いP領域500に延在する。当該トレンチはまた、トレンチにより制限された拡散領域をシンカ、分離またはウェルとして形成するのに用いられてもよい。

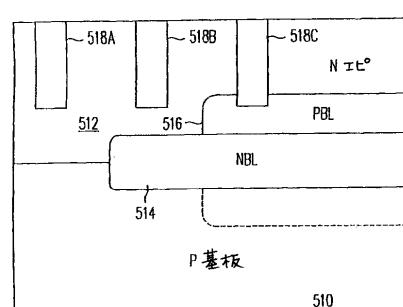

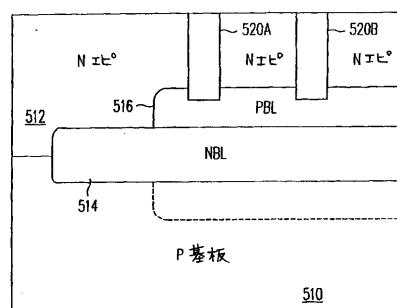

#### 【0067】

図26Aおよび図26Bは、P基板510とNエピ層512との間の界面において形成されるN埋込層514およびP埋込層516を含む構造を示す。P埋込層516はN埋込層514の上方のエッジを越えて上方向に拡散している。これにより、N埋込層514がP埋込層516を越えて横方向に延在する事実と組合わせると、N埋込層514の上方にありP基板510から分離されるP埋込層516の一部分が作り出される。当該トレンチはまた、トレンチにより制限された拡散領域をシンカ、分離またはウェルとして形成するのに用いられてもよい。

#### 【0068】

Nエピ層512は、Nエピ層512の表面から下方に延在する誘電体が充填されたトレ

10

20

30

40

50

ンチによって、分離されたポケットに分けられ得る。図26Aにおいては、誘電体が充填されたトレンチ518Cが、Nエピ層512を分離されたポケットに分ける。図26Bにおいては、誘電体が充填されたトレンチ520Aおよび520Bの各々が、Nエピ層512を分離されたポケットに分ける。通常、誘電体が充填されたトレンチはP埋込層516に延在するはずであるが、電流がP埋込層516全体にわたって横方向に流れることを可能にするために、当該トレンチはP埋込層516を通りN埋込層514に延在すべきではない。当該トレンチはまた、トレンチにより制限された拡散領域をシンカ、分離またはウェルとして形成するのに用いられてもよい。

## 【0069】

トレンチにより制限された拡散領域と（より一般的にはトレンチにより制限された接合として）、深いトレンチ酸化分離との違いをここで繰返すことが重要である。深いトレンチ分離（DTI）は、エピタキシャル層を完全に突抜けてその下にある基板に食い込むトレンチを用いる。したがって、DTIプロセスにおいては、トレンチが存在するいかなる断面においても、（ウェル、拡散された接合、さらには埋込層における）横方向の電流の流れが遮断される、すなわち、トレンチの存在によって遮られる。たとえば、2つの隣接するバイポーラ素子のコレクタのような関連のない素子を互いから完全に分離するのが望ましい場合、DTIタイプのトレンチの深さが有用となる。しかし、バイポーラの断面においては、ベースとコレクタとの間の横方向の電流の流れは深いトレンチによって遮断することができない、すなわち、DTIタイプのトレンチはバイポーラの「内部」では用いることができないが、バイポーラ間ににおいてのみ用いることができる。たとえば図26Bの構造を検討してみると、トレンチ520Aおよび520Bは、P埋込層516に延在しているが完全には突抜けていない。PBL層516が「遮断」されないので、電流が上記層において横方向に流れることが可能であり、これにより、能動素子が構築され得る以外の位置で上記層に接触するのが容易となる。さらに、エッジを含む素子の横方向の範囲のどこででもN埋込層514への電気接觸が可能であり、N埋込層514はなおも共通の電位にバイアスがかけられ、これにより、NBL514において（ウェハの表面に対して平行な）横方向の電流の流れが可能となる。DTIトレンチが用いられる場合、N埋込層は別個の島に切り分けられ、各々がそれ自体の電気接觸を必要とすることになるだろう。類似の議論が、図22BにおけるN埋込層479を部分的に覆うトレンチに適用される。

## 【0070】

図27A～図27Iは、誘電体が充填されたトレンチを形成するための可能なプロセスを示す。基板上に成長したエピ層において形成されるトレンチが示される。上述のように、エピ層および基板は、同じ電気導電型（NもしくはP）または異なる導電型であってもよい。さらに、図23Aおよび図23Bに示されるように、たとえばいくつかの実施例においては、トレンチはエピタキシャル層なしに基板に形成され得る。当該プロセスは、トレンチ深さのための基準が異なる可能性がある点を除いては、上述の条件で本質的に同じままであるだろう。

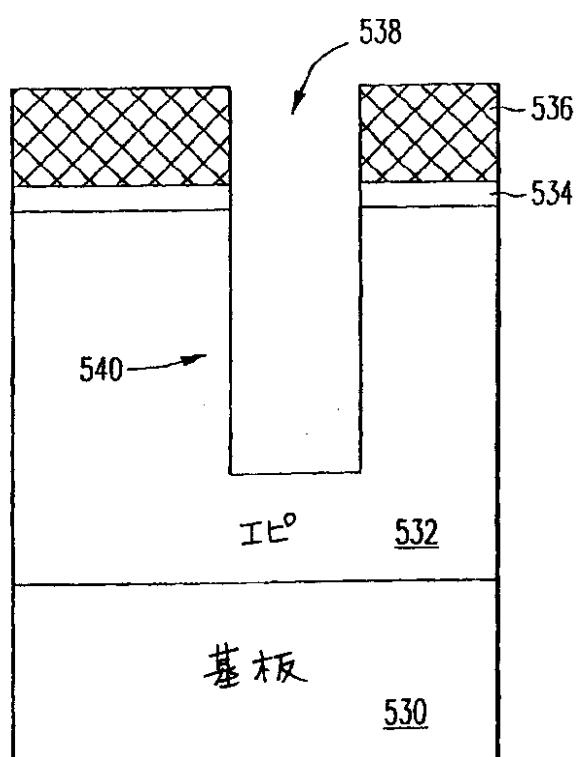

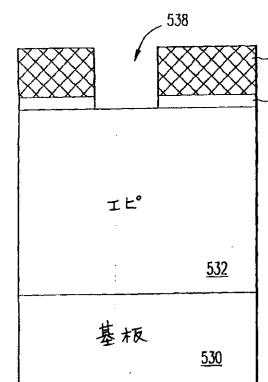

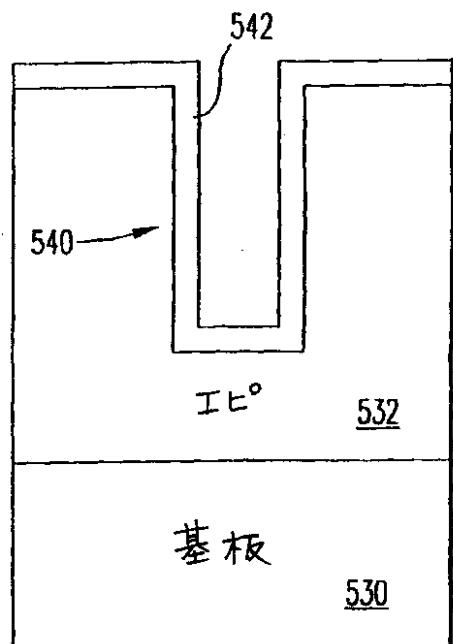

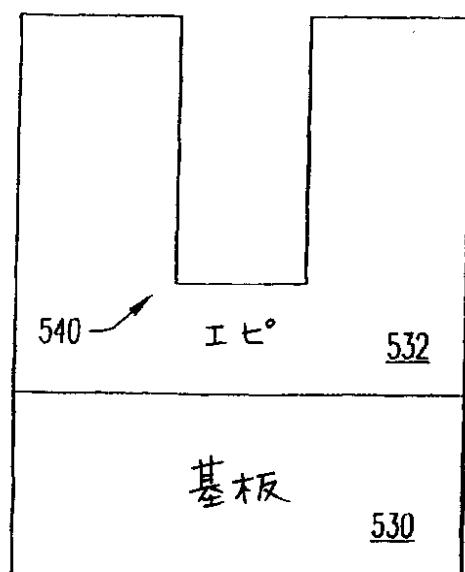

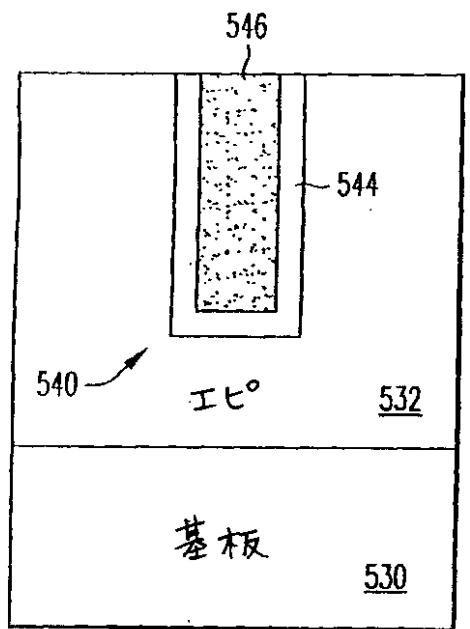

## 【0071】

図27Aに図示のとおり、酸化物または窒化物（またはそのサンドイッチ状のもの）などの材料の硬質のマスク層534がエピ層532の表面上に形成される。硬質のマスク層534はフォトレジスト層536でマスクされ、開口部358を形成するようエッチングされる。図27Bに図示のとおり、トレンチ540は、典型的には反応性イオンエッチング（RIE）を用いてエッチングされる。トレンチ-ゲート型MOSFETを作成するためのプロセスにおいてはフォトレジスト層536がしばしばRIE前に除去されるが、ここでは、RIE中に適所にフォトレジスト層536を残すことが望ましいかもしれない。というのも、トレンチは、トレンチゲート型垂直パワーMOSFETのために一般に用いられるトレンチよりも深い（たとえば2～4μm深い）可能性があるからである。代替的には、硬質のマスク層534の厚さは、シリコントレンチエッチングプロセスに耐えるよう厚くすることができる。

## 【0072】

10

20

30

40

50

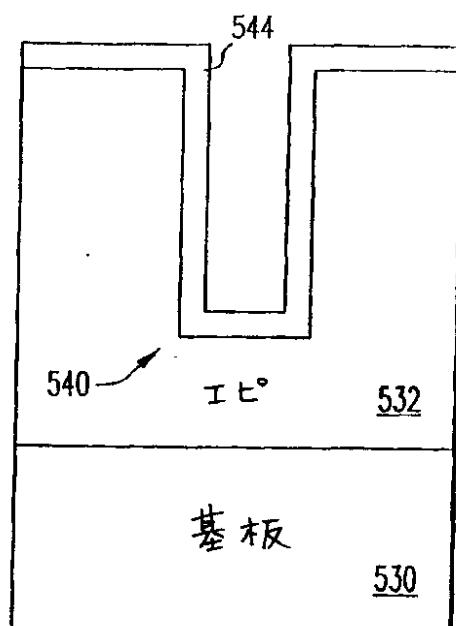

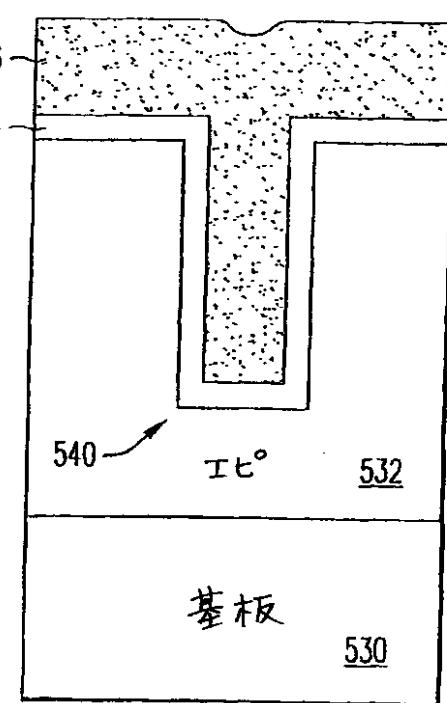

硬質のマスク層 534 およびフォトレジスト層 536 が除去され（またはマスクが選択的に除去され）、随意には、犠牲酸化層 542 が図 27C に図示のとおりトレンチ 540 の壁上に形成され、図 27D に図示のとおり除去される。これは、RIE プロセス中に通常発生する結晶損傷を修復するのに役に立つ。酸化ライナ 544 が図 27E に図示のとおりトレンチ 540 の壁上に成長し、TEOS 酸化物などの誘電体 546 が図 27F に図示のとおりトレンチ 540 においてエピ層 532 の表面上にわたって堆積する。酸化ライナ 544 は、ホウ素および／またはリンなどのドーパントに対してシールドの役割を果たすが、当該ドーパントが誘電体 546 に含まれることにより、誘電体 546 がより容易にトレンチ 540 に流入して充填され得る。このようなドーパントがエピ層 532 に入ることが可能である場合、素子の電気特性が変えられ得る。場合によっては、ドープされない酸化物をトレンチに最初に堆積させることにより、酸化ライナを省くことができるかもしれない。10

#### 【0073】

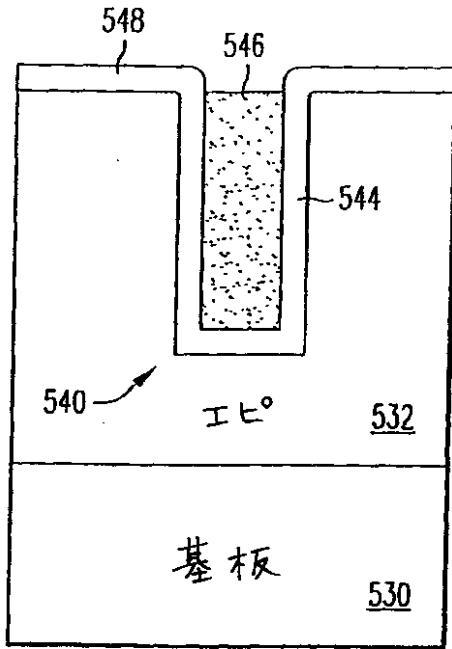

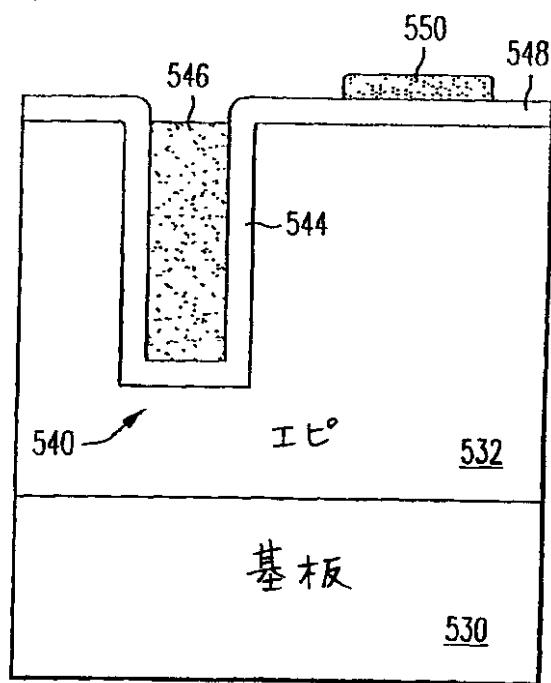

次に、当該構造の上面が化学機械研磨 (CMP) によって平坦化されて、図 27G に示されるセミフラットな表面が形成され得る。エピ層 532 の表面が再度酸化されて、図 27H に示される酸化層 548 が形成される。酸化プロセスは、エピ層 532 の一部を消費するが（既に酸化された）酸化物 546 を消費しないので、トレンチ 540 にわたって窪みが作り出される。代替的には、酸化ライナ 544 の一部分が平坦化プロセスの際にエピ層 532 の上面に残されてもよく、この場合、図 27H に示される再酸化ステップは不要になり得る。20

#### 【0074】

図 27F におけるガラス 546 のエッチバックを実行する代替例では、図 27G に示されるような平面な表面は作られないだろう。トレンチの上にわたっていくらか窪みが生じるのは、おそらく、堆積した酸化物がより速くエッティングをする傾向があるからである。次に、シリコン窒化物が堆積すると、CMP 方法を用いて平坦化されて、トレンチの上部が窒化物で覆われ得るかまたは封止され得る。

#### 【0075】

図 27I に図示のとおり、ポリシリコン層 550 が、レジスタまたはキャパシタを形成する際に用いるために酸化層 548 上に堆積されかつパターニングされ得る。キャパシタがポリシリコン層 550 とエピ層 532 との間に形成されるべき場合、酸化層 548 の厚さは限界であり、酸化層 548 を堆積させるのではなく加熱手段によって酸化層 548 を成長させることができないかもしれない。というのも、熱処理は概して、堆積プロセスよりも酸化層の厚さを大きく制御するからである。この要因は、ポリシリコン層 550 が、上に重なっている別のポリシリコン層とともにレジスタまたはキャパシタとして用いられるべき場合には重要ではない。30

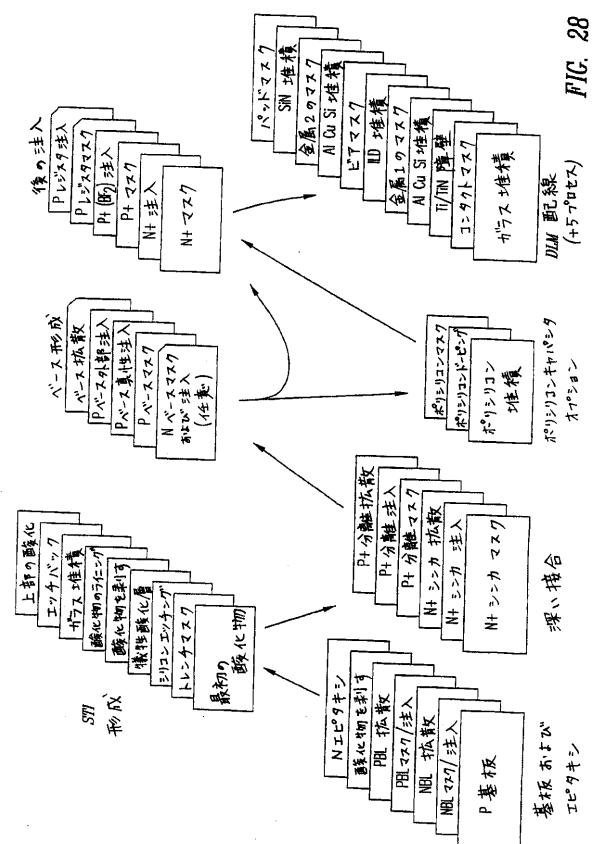

#### 【0076】

図 12～図 27 に記載されるプロセスステップは、バイポーラトランジスタ、MOSFET、ダイオードなどを含むがこれらに限定されない広範囲の半導体素子を作製するのに用いることのできるプロックを構築している。これらのプロセスステップは、トレンチにより制限された拡散および接合を用いて構造を集積化することを含む。図 28 および図 29 は、相補型アナログバイポーラトランジスタの構築（すなわち NPN および PNP の両方の集積化）におけるこの発明の使用を示すが、この特定の実施例の説明は、この発明がそのように限定されることを示していると解釈されるべきではない。「アナログ」という用語は、当該技術の目的が、供給電圧よりも低い持続電圧への  $V_{ce}$  スナップバックの問題を被ることなく高品質の電流源（高いアーリー電圧素子）と、たとえば 3V または 5 ボルトを超える高い破壊電圧とを作り出すことのできるバイポーラ素子を製造することであることを識別するためにだけ含まれている。当然、トレンチにより制限された拡散技術はアナログバイポーラの製造に限定されず、デジタル方式で最適化されたバイポーラのために用いることもできる。40

#### 【0077】

50

図28はプロセスの概要を示す。「カード」の各々はプロセスステップを表わす。概して、角が切り取られたカードはオプションのステップを示すが、ただし他のステップも特定の状況においては省かれててもよい。

#### 【0078】

プロセスは、一連の基板への注入および拡散、ならびに基板上でのエピタキシャル層の成長から始まる。中間の深さの部分的なトレンチ分離（PTI）領域の構築に関する次のステップが実行される。深い接合は、理想的にはトレンチにより制限された拡散領域から恩恵を受けるレイアウトを用いて注入および拡散され、バイポーラトランジスタのベース領域が形成される。随意には、ポリシリコンキャパシタが構築され得る。次いで、「後の（late）」注入では、トランジスタのエミッタ領域およびコレクタ領域が形成される。最後に、2層金属（DLM）配線構造がシリコンの上に構築されて、シリコンにおける領域への接続をもたらす。いわゆる「+5プロセス」は、5つのマスクを用いるDLM配線シーケンス全体を指し、1つのマスクはシリコンへのコンタクトの規定とエッチングとを行なうためのものであり、もう1つのマスクは金属1のためのものであり、第3のマスクは金属1と金属2との間における中間層の誘電体のビアエッチングのためのものであり、第4のマスクは金属2のためのものであり、最後のマスクはパッドを結合するためのパッシベーション層のエッチングを行なうためのものである。したがって、シリコン処理が完了すると、「+3プロセス」が単層の金属（SLM）を作製し、いわゆる「+5プロセス」により2層金属（DLM）がもたらされ、「+7プロセス」により3層の金属配線がもたらされる。これらの配線オプションはすべて、図示されるプロセスフローに対応し、トレンチにより制限された接合および拡散の使用に相互に対応している。

#### 【0079】

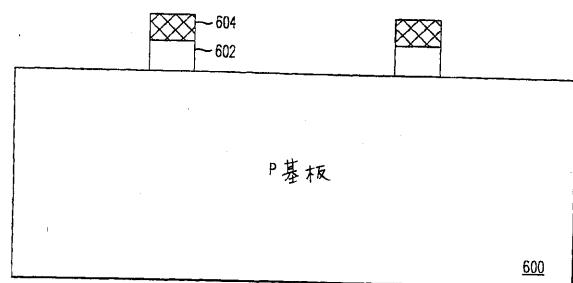

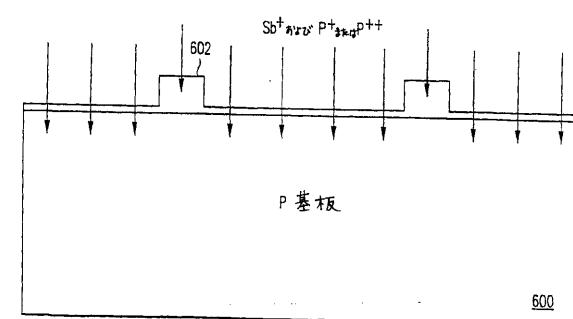

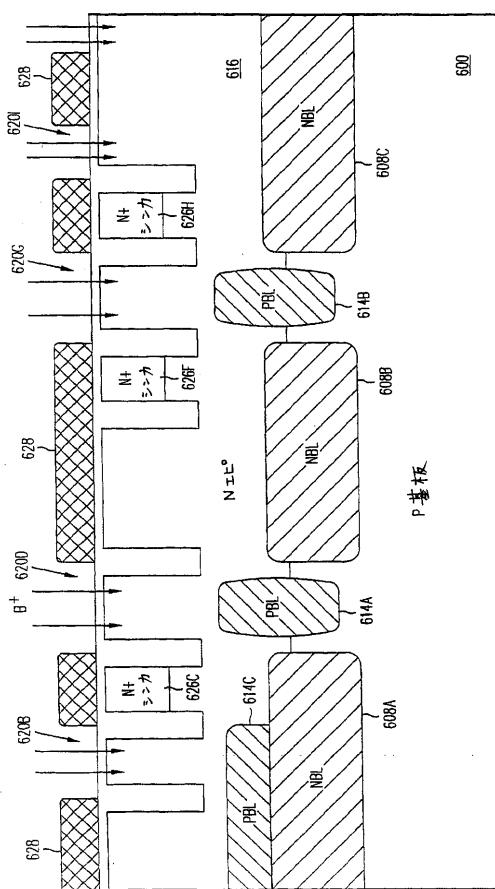

図29Aを参照すると、酸化層602およびフォトレジスト層604がP基板600上に連続して堆積し、フォトレジスト層604がパターニングされ、酸化層602がフォトレジスト層604における開口部を通じてエッチングされる。フォトレジスト層604が除去され、アンチモンおよび1回もしくは2回イオン化されたリン（またはこれらの両方の組合せ）が、図29Bに図示のとおり、酸化層602における開口部を通じて（上述の条件に匹敵する条件を用いて）注入される。

#### 【0080】

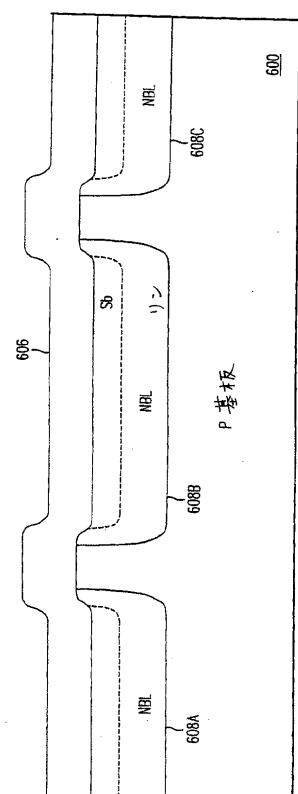

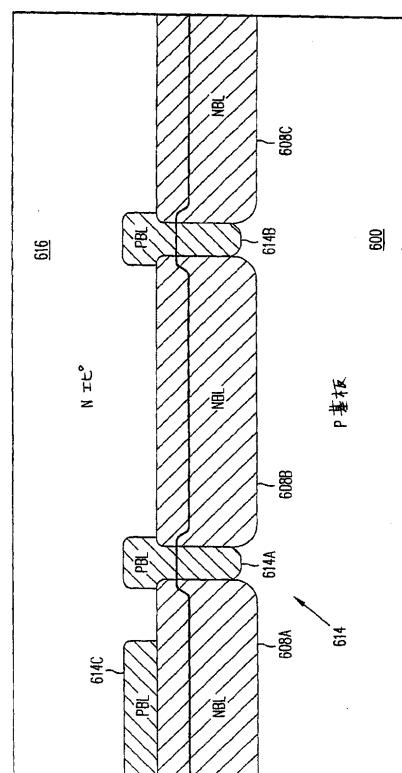

酸化層602が除去され、アンチモンおよびリンが長期間にわたってドライブインされる。これにより、新しい酸化層606がP基板600の表面上に形成され、部分608A、608Bおよび608Cに分割されるN埋込層608がP基板600の表面より下に形成される。部分608A、608Bおよび608Cは、酸化層602がフォトレジスト層604における開口部を通じてエッチングされた後に当該酸化層602が残る位置に分離される。

#### 【0081】

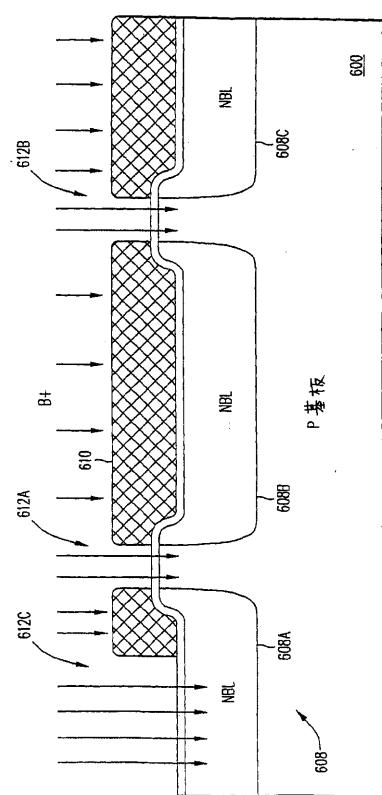

図29Dに図示のとおり、酸化層606が除去され、フォトレジスト層610が堆積し、パターニングされる。開口部612Aおよび612Bは、N埋込層608の部分608A、608Bおよび608Cを分離する空隙の上方にあるフォトレジスト層610において形成され、開口部612Cは、N埋込層608の部分608Aの上方にあるフォトレジスト層610において形成される。ホウ素が開口部612A、612Bおよび612Cを通じて注入されて、P基板600にP埋込層614の部分614Aおよび614Bが形成される（図29Eを参照）。リンを用いてN埋込層608を形成したので、ホウ素注入のドーズ量は、部分的に重なる領域においてホウ素が確実にリンのドーピングを圧倒するようかなり高く（たとえば、 $3 \times 10^{14} \sim 7 \times 10^{15} \text{ cm}^{-2}$ ）なければならない。アンチモンまたはヒ素などの低速で拡散するドーパントだけを用いてN埋込層608が形成される場合、ホウ素注入のドーズ量は、ことによると $8 \times 10^{13} \text{ cm}^{-2}$ ほどのドーズ量にまで減じられる可能性がある。開口部612Cを通るホウ素ドーパントは、N埋込層部分608Aにおけるリンおよびアンチモンを反対にドープせず、このため図29Eには示されない。

#### 【0082】

10

20

30

40

50

図29Eに図示のとおり、Nエピタキシャル(エピ)層616がP基板600の上に成長する。このプロセス中に、N埋込層608およびP埋込層614がNエピ層616へと上方に拡散する。この接合を形成するのに付加的な拡散は必要とされない。というのも、エピタキシャル堆積プロセス自体が高温で行なわれるからである。N埋込層608が急速に拡散するドーパントのリンを含んでいるので、N埋込層608におけるピークのドーパント濃度は、エピタキシャル成長前に実行される拡散におけるリンおよびアンチモン注入のドライブイン中に実質的に下方に移動する。したがって、Nエピ層616への上方拡散中に、ホウ素は概してリンよりも先に進み(ホウ素はより高い濃度およびより高い拡散率を有する)、P埋込層614は、N埋込層614のリンおよびアンチモンのドーパントよりも高くNエピ層616に到達する。逆に、図29Eに図示のとおり、P埋込層614は、P基板600におけるリン/アンチモン拡散領域の下には延在しない。これはP埋込層614の部分614Cの場合には重要である。というのも、P埋込層部分614CがN埋込層部分608Aの下に延在する場合、(N埋込層部分608Aによって囲まれるべき)ウェルの、その下にある基板への破壊電圧が減じられるからである(図29Mを参照)。

#### 【0083】

P埋込層618の部分614Aおよび614Bは、図29Eに図示のとおりN埋込層608の部分608A、608Bおよび608Cに接触し得るか、またはP埋込層618の部分614Aおよび614Bは、図29Fに図示のとおりN埋込層608の部分608A、608Bおよび608Cから分離され得る。P埋込層618の部分614Aおよび614Bと、N埋込層608の部分608A、608Bおよび608Cとの間の間隔、またはその間隔の不足は、フォトレジスト層610における開口部612Aおよび612Bの幅を変えることによって制御される(図29Dを参照)。この説明の残りの部分においては、開口部612Aおよび612Bの幅が図29Fに示される実施例をもたらすように設定されたと仮定されるだろう。

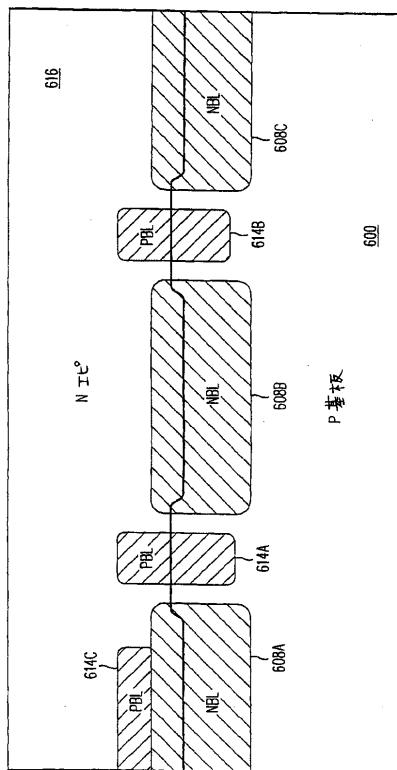

#### 【0084】

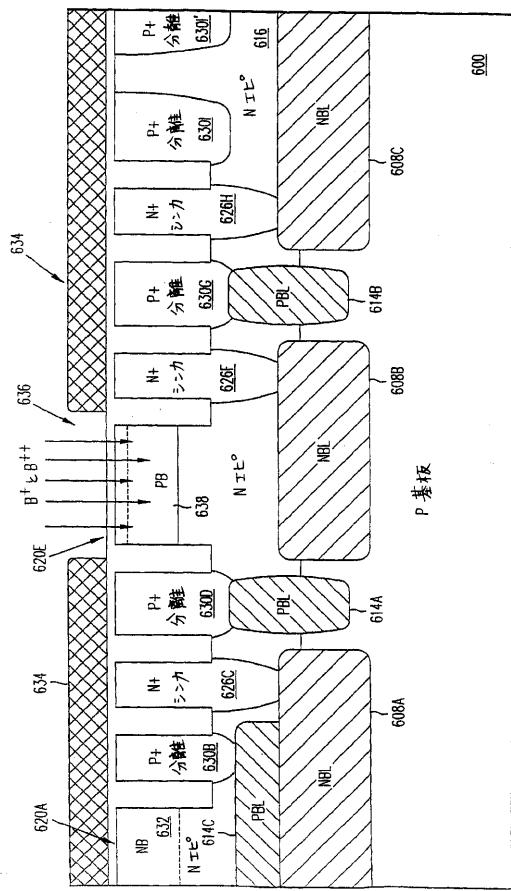

図29Gに図示のとおり、トレンチ618は、好ましくは図27A～図27Iに示されるプロセスを用いてNエピ層616に形成され、酸化層622が充填されている。トレンチ618はNエピ層616において介在するメサ620A～620Iを形成する。この実施例においては、トレンチ618は、P埋込層614の上方の境界ほど深くには延在しない。他の実施例においては、トレンチはP埋込層614に延在し得るが、P埋込層614全体またはNエピ層616全体を通ってP基板600までには延在しないはずである。トレンチ618の幅は好ましくは0.8～1.2μmの範囲であるが、ただし、より幅の狭いトレンチが用いられてもよい。

#### 【0085】

図29Gから明らかなように、トレンチ618のいくつかは、P埋込層614の部分614A、614Bおよび614Cの垂直なエッジに位置合わせされる。特に、トレンチ618Bは部分614Aのエッジに位置合わせされ、トレンチ618Cおよび618Dは部分614Bの両側のエッジに位置合わせされ、トレンチ618Fおよび618Gは、部分614Cの両側のエッジに位置合わせされる。結果として、メサ620Bは部分614Cの上方にあり、メサ620Dは部分614Aの上方にあり、メサ620Gは部分614Bの上方にある。これらのアライメントは、埋込層の注入中に成長した酸化層によってP基板600の上面に形成される窪みを用いてなされる。これらの窪みの「像」は、シリコンがいくらか透過的である場合に周波数の赤外線光を用いて、マスクアライナ装置によって薄いエピタキシャル層を通して見ることができる。「像」はエピタキシャル層の分散作用のためにいくらかぼやけているが、良好なマスクと埋込層とのアライメントを達成するのに十分に明瞭である。図29Cは、たとえば、エピ成長前のN埋込層608の形成中にP基板600に形成されたエッジを示す。これらのエッジは、Nエピ層616の成長中にシリコンによって覆われているが、依然として赤外線光によって基板とエピとの界面においてエピの底部のエッジに見ることができる。エピ層の表面上のパターンを埋込層に位置合わせするのに用いられる技術は当業者には周知であり、このため、ここではさらに詳細に

10

20

30

40

50

は説明されない。

【0086】

図29Gに示されるトレンチ618の深さは、エピ層616の深さのほぼ半分に示されているが、プロセス要件に従ってより浅く作られてより深く延在してもよい。最も重要なことは、トレンチ618はエピタキシャル層を完全には貫通しない、すなわち、トレンチはエピタキシャルの厚さほど深くなく、このため、深いトレンチ分離またはその同等物として考えられるべきではない。図29Gに図示のとおり、トレンチは、エッチングおよび充填される時点ではP埋込層614Cの上にほぼ部分的に重なる深さを有しているが、実際にはP埋込層614Cから間隔が空けられている。後に次の熱処理において、PBL614C層が上方拡散し、トレンチ618に部分的に重なり得るが、ただし、この結果はプロセスフローには求められていない。10

【0087】

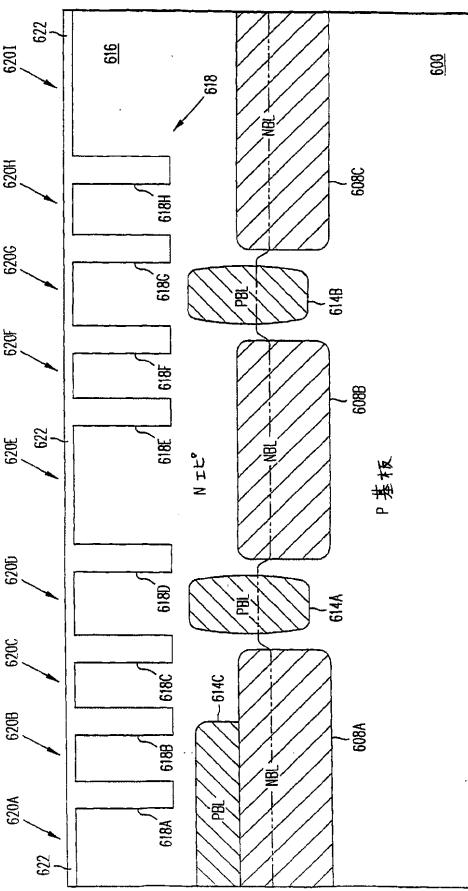

図29Hに図示のとおり、フォトレジスト層624が酸化層622の表面上に形成され、メサ620C、620Fおよび620Hの上にわたって開口部でパターニングされる。ヒ素およびリンがフォトレジスト層624における開口部を通じて注入されて、図29Iに図示のとおり、メサ620C、620Fおよび620HにN+シンカ626C、626Fおよび626Hがそれぞれ形成される。リンは急速に拡散し、ヒ素はより低速で拡散するので、これらの2つのドーパントを組合せることによりN+シンカ626C、626Fおよび626Hのドーパントプロファイルが同レベルにされる。ヒ素およびリンをともに含む混合注入は、拡散率が実質的に異なる2つのドーパントを含む。より急速に拡散するリンは、リンが次の熱処理中にシリコン内にあまり深く延在しないようにヒ素よりも少量（たとえば $2 \times 10^{-5} \text{ cm}^{-2}$ ではなく $7 \times 10^{-3} \text{ cm}^{-2}$ ）ドープされ得る。20

【0088】

次いで、フォトレジスト層624が剥がされ、N型のシンカ拡散物質が、1000～1200で、しかし好ましくは1100～1150で1～7時間にわたって高温の拡散プロセスを用いて部分的に拡散され得る。代替的には、当該拡散が全く省かれてもよいか、または注入およびアニールが（POCL<sub>3</sub>などの気体源を用いて）リンのプレデポジションと置換えられてもよい。プレデポジションは当該技術において公知であるので、この明細書中においてはこれ以上詳述されない。30

【0089】

次に、フォトレジスト層628が酸化層622の表面上に形成され、メサ620B、620D、620Gおよび620Iにわたって開口部でパターニングされる。ホウ素がフォトレジスト層628における開口部を通じて注入されて、メサ620B、620D、620Gおよび620IにおけるP+分離領域630B、630D、630Gおよび630I/630Iがそれぞれ形成される。フォトレジスト層628が除去される。30

【0090】

ここで構造がアニールされて、N+ドーパントおよびP+ドーパントをドライブインする（ここでは分離拡散と称される）。アニールの結果として、P+分離領域630BがP埋込層614Cと融合し、N+シンカ626CがN埋込層608Aと融合し、P+分離領域がN埋込層614Aと融合し、N+シンカ626FがN埋込層608Bと融合し、P+分離領域630GがP埋込層614Bと融合し、N+シンカ626HがN埋込層608Cと融合する。P+分離領域630Iおよび630Iは下方に拡散するが、他のいかなる領域とも融合しない。P+分離領域630DとP埋込層614Aとの組合せ、およびP+分離領域630GとP埋込層614Bとの組合せがP型のドーパントの柱を形成し、このP型のドーパントの柱は、P基板600に延在しつつNエピ層616に形成される素子を互いに分離するトレンチ618によって上部が横方向に制限されている。結果として得られる構造は、（PB領域638およびNB領域632がまだ形成されていない点を除いては）図29Jに示される。40

【0091】

このプロセスフローにおいては、ホウ素の分離、リンのシンカ、およびさまざまなドラ50

イブイン拡散の順序は、（全体的な熱収支、温度 - 時間のサイクルがこの時点まで固定されたままである限り）結果として得られる素子を実質的に変えることなく変更可能である。たとえば、ホウ素の分離は、注入後の部分的なドライブ拡散を用い得る（かまたは用い得ない）Nシンカ注入より前であってもよい。

#### 【0092】

別の代替例では、3 MeVまでの注入（しかし、好ましくは0.5 MeV ~ 2 MeVまでの異なるエネルギーのさまざまな注入）で高エネルギーイオン注入を用いて分離もしくはシンカまたはこれらの両方が注入されるが、これにより、注入後の（既に2.5 μmを超える）より深い接合は、その注入エネルギーが低く拡散が深いタイプよりも拡散時間が短く温度が低くなくてはならない。

10

#### 【0093】

図29Jには、N型の拡散領域（NシンカおよびN埋込層）がP型の拡散領域（P分離領域およびP埋込層）から間隔をあけて示される。（図29Eに示される実施例と同様に）N型の拡散領域およびP型の拡散領域とが接触する場合でも、ドーピング濃度が比較的低いトレンチ618の下でしかこの接触は起こり得ない。このようにして形成されるPN接合の破壊電圧は、特にトレンチがそこに存在しない場合に形成されるであろう表面接合に比べて比較的高くなるだろう。すなわち、NシンカおよびP分離領域は、これらの拡散領域のドーピング濃度が低い破壊電圧を生成するのに十分高い場合にNエピ層616の表面付近でトレンチ618によって分離される。NシンカとP分離領域（または対応するN埋込層とP埋込層）とが接触し得るNエピ層616の下方においては、これらの拡散領域のドーピング濃度は比較的低く（より傾斜がつけられるかまたは拡散され）、このため、形成され得るいかなるPN接合にもわたる破壊電圧が比較的高くなるだろう。

20

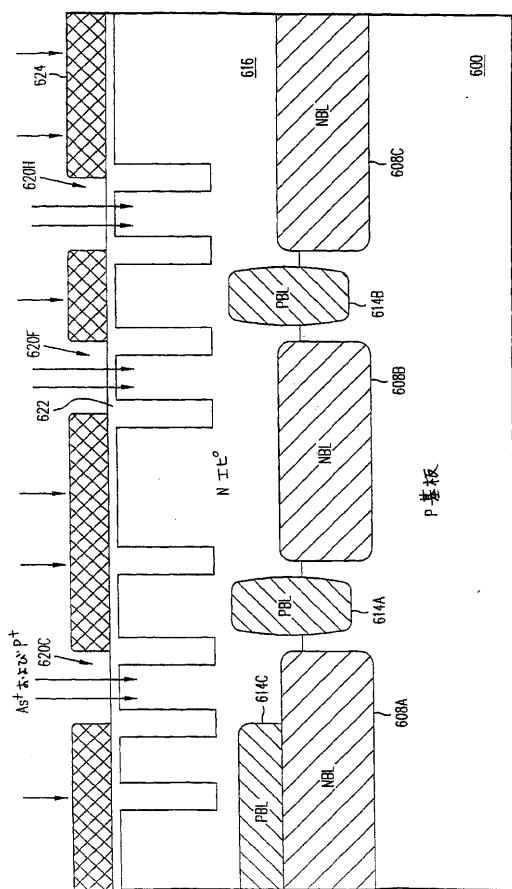

#### 【0094】

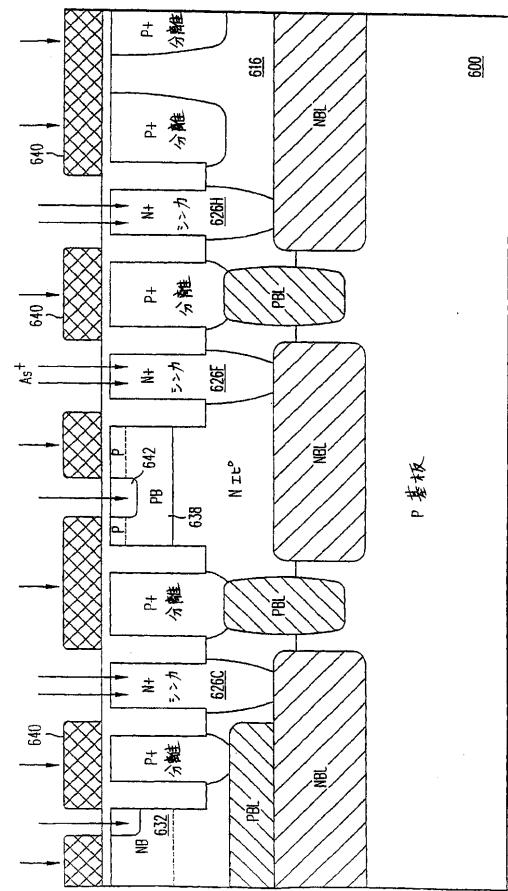

Nエピ層616の表面がマスクされ（図示せず）、リンなどのN型のドーパントがマスクにおける開口部を通じて注入されて、図29Jに示されるNベース領域632を形成する。リンの注入は60KeV ~ 2MeVほどの高さであり得る。より低い範囲の注入エネルギーは、典型的には、（0.5 μm ~ 2.5 μmの最終的な接合深さのために）プロセスの後の方でのドライブイン拡散かまたは（0.5 μm未満の接合深さのために）ポリシリコンエミッタの使用を必要とする。より高いエネルギー注入は拡散を殆どまたは全く必要としない。注入ドーズ量は3E13 cm⁻² ~ 2E14 cm⁻²の範囲である。フォトレジストマスクが剥がされ、フォトレジスト層634が堆積しつつパターニングされて開口部636を形成する。ホウ素（B⁺および/またはB⁺⁺）が開口部636を通じて注入されてメサ620EにPベース領域638を形成する。真性ベースと称されるホウ素のより深い注入は3E13 cm⁻² ~ 2E14 cm⁻²のドーズ量であり得、注入エネルギーは90KeV ~ 2MeVの範囲であり得る。より低い範囲の注入エネルギーは、典型的には、（0.5 μm ~ 2.5 μmの最終的な接合深さのために）プロセスの後の方でのドライブイン拡散かまたは（0.5 μm未満の接合深さのために）ポリシリコンエミッタの使用を必要とする。より高いエネルギー注入は拡散を殆どまたは全く必要としない。真性注入ドーズ量は3E13 cm⁻² ~ 2E14 cm⁻²の範囲である。

30

#### 【0095】

破線で示されるように、Pベース領域638は好ましくは2回の注入を重ね合わせることによって形成され、2回の注入とはすなわち、Nエピ層616の表面付近に低抵抗区域を作り出す低いエネルギー注入（外部ベース注入と称される）と、Nエピ層616により深く浸透するより高いエネルギー注入（上述の真性ベース注入）とである。外部ベース注入は、ドーズ量が5E14 cm⁻²を超える30 ~ 60KeVのエネルギーで実行される典型的にはB⁺またはBF₂⁺の種である。外部注入を用いることにより、かなりのベース拡散が実行される場合にその使用が制限されてしまう。これにより、浅い接合素子については性能が大きく向上する。

40

#### 【0096】

Nベース領域632またはPベース領域638が、より高い注入エネルギーを用いるので

50

はなく高温でかなりの拡散時間を用いて形成される場合には、高温の時間がシンカおよび分離拡散から除かれなければならない。

【0097】

2つのベース領域の注入後、フォトレジスト層634が除去され、フォトレジスト層640が堆積しつつパターニングされて、図29Kに図示のとおり一連の開口部が形成される。ヒ素がフォトレジスト層640における開口部を通じて注入されて、Nベース632ならびにNシンカ626C、626Fおよび626Hにコンタクト領域が形成され、Pベース領域638にNエミッタ領域642が形成される。Nエミッタ領域642は、ベースの電気的特性がNエミッタ領域642の下方におけるより少量ドープされた部分によって決定されて真性ベースを通じて垂直に伝わるように、(破線で示される)Pベース領域638の多量にドープされた表面領域の下方に延在する。N+注入は、 $2E15\text{ cm}^{-2} \sim 7E15\text{ cm}^{-2}$ のドーズ量では30KeV~50KeVのリンか、または好ましくは60KeV~120KeVのヒ素であり得る。

10

【0098】

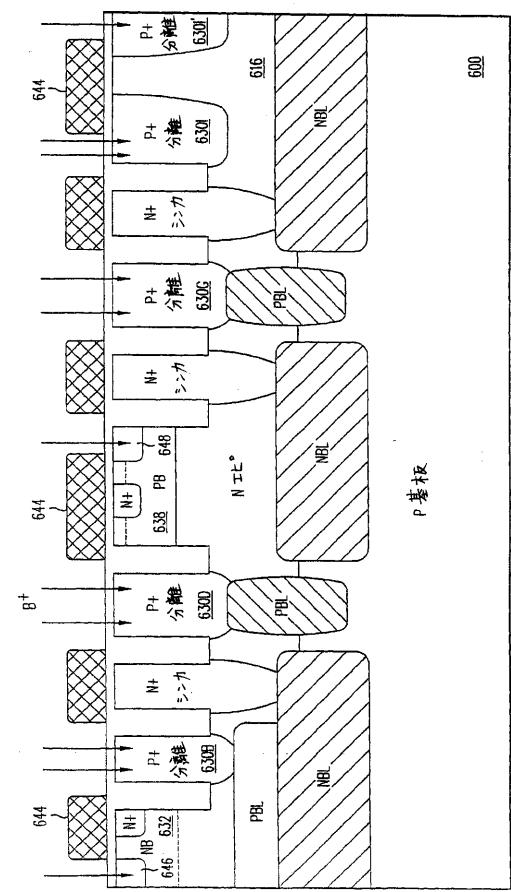

フォトレジスト層640が除去され、フォトレジスト層644が堆積しつつパターニングされて、図29Lに図示のとおり一連の開口部が形成される。ホウ素がフォトレジスト層644における開口部を通じて注入されて、P分離領域630B、630D、630G、630Iおよび630Lにコンタクト領域を形成し、Nベース領域632にPエミッタ領域646を形成し、Pベース領域638にコンタクト領域648を形成する。P+注入は、 $2E15\text{ cm}^{-2} \sim 7E15\text{ cm}^{-2}$ のドーズ量では30KeV~50KeVのホウ素か、または好ましくは60KeV~120KeVのBF<sub>2</sub><sup>+</sup>であり得る。次いでフォトレジスト層644が除去される。

20

【0099】

図29Mに図示のとおり、誘電体層650が酸化層622上に堆積する。誘電体層650がマスクされ、誘電体層650および酸化層622がマスクにおける開口部を通じてエッチングされて、Nエピ層616にさまざまな領域への開口部を形成する。TiまたはTiN障壁層651が開口部に堆積し、第1の金属層652が障壁層651にわたって堆積しつつパターニングされて金属コンタクトを形成する。第2の誘電体層654が誘電体層650上に堆積し、ビアマスクが、P分離領域630B、630Dおよび630Iに接触するよう位置決めされた開口部に適用される。ビアは、ビアマスクにおける開口部を通じて誘電体層654にエッチングされ、第2の金属層656がビアに堆積する。

30

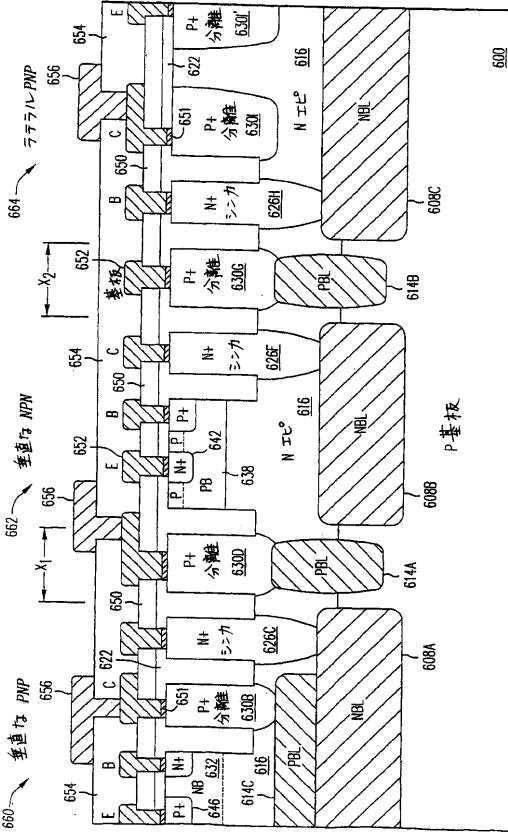

【0100】

このプロセスの終わりには、垂直なPNPトランジスタ660、垂直なNPNトランジスタ662およびラテラルPNPトランジスタ664がNエピ層616に形成されている。垂直なPNPトランジスタ660は以下の領域を含む：

エミッタ： P+領域646

ベース： Nベース領域632およびNエピ層616の一部分

コレクタ： P埋込層614CおよびP分離領域630B

垂直なPNPトランジスタ660は、N埋込層608AおよびNシンカ626Cを含む分離構造によってP基板600から分離される。

40

【0101】

垂直なNPNトランジスタ662は以下の領域を含む：

エミッタ： P+領域642

ベース： Pベース領域638

コレクタ： Nエピ層616の一部分、N埋込層608B、Nシンカ626F

ラテラルPNPトランジスタ664は以下の領域を含む：

エミッタ： P分離領域630I

ベース： Nエピ層616の一部分、N埋込層608C、Nシンカ626H

コレクタ： P分離領域630I

加えて、垂直なPNPトランジスタ660は、P分離領域630DおよびP埋込層61

50

4 A を含む垂直な柱によって垂直な N P N トランジスタ 6 6 2 から分離される。垂直な N P N トランジスタ 6 6 2 は、P 分離領域 6 3 0 G および P 埋込層 6 1 4 B を含む垂直な柱によってラテラル P N P トランジスタ 6 6 4 から分離される。

#### 【 0 1 0 2 】

先行技術のプロセスを用いると、トランジスタ 6 6 0 、 6 6 2 および 6 6 4 は、典型的には、熱処理中の横方向のドーパント拡散のために、互いから数十ミクロン間隔をあけて配置されなければならないだろう。対照的に、この発明の横方向に制限されたシンカおよび分離領域を用いると、図 2 9 M において  $X_1$  および  $X_2$  と示されるトランジスタ 6 6 0 と 6 6 2 と 6 6 4 との間の間隔は 3 ~ 4 ミクロンしか減じることができない。これにより、素子間の電気的分離の質を犠牲にすることなくウェハ上の素子の記録密度を大きく高めることが可能となる。

10

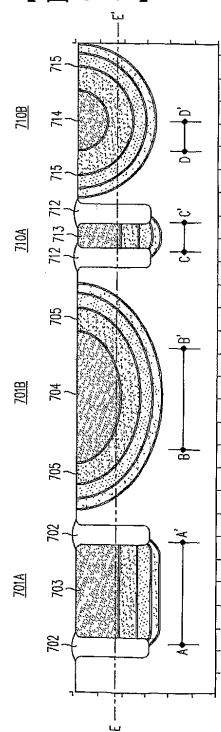

#### 【 0 1 0 3 】

図 3 0 は、特に小さなパターンサイズの深い拡散領域における横方向の間隔を減らすための、トレンチにより制限された拡散領域の利点を示す。この図は 4 つの拡散された領域を示し、各々は（すべて  $8 \text{ E } 1 3 \text{ cm}^{-2}$  のドーズ量で  $8 0 \text{ KeV}$  のエネルギーで）同じ浅いイオン注入から始まり、次に（ 1 1 0 0 で 4 時間の）同一の拡散が続く。縦および横の目盛り上のマークは  $0.5 \mu\text{m}$  刻みである。灰色の影は最終的なドーピング濃度の数桁の差を示している。

#### 【 0 1 0 4 】

トレンチにより制限された幅広の拡散領域 7 0 1 A においては、注入された領域はトレンチ 7 0 2 間の幅にわたり、結果として（線 A - A で示される） $2 \mu\text{m}$  の幅を有する拡散領域 7 0 3 をもたらす。最も多量にドープされた部分は、線 E - E で示されるように  $1 \mu\text{m}$  の深さにまで拡散する。この拡散はトレンチの下方に  $2 \mu\text{m}$  未満の深さに延在するが、多量にドープされた部分は E - E の線にまでしか延在しないことに留意されたい。

20

#### 【 0 1 0 5 】

拡散領域 7 0 1 B は、（線 B - B で示され、長さが線 A - A に等しい） $2 \mu\text{m}$  の幅を有する注入から構築される拡散領域 7 0 4 を含む幅広の制限されない拡散の一例である。高温のドライブインの後、領域 7 0 4 が拡散し、その多量にドープされた部分が線 E - E で識別される深さに達する  $1 \mu\text{m}$  の深さに到達し、横方向の拡散領域 7 0 5 が  $2 \mu\text{m}$  の幅の注入をはるかに超える拡散の幅に広がる。横方向の拡散領域 7 0 5 は典型的には接合深さの 8 5 % に等しい横方向の範囲を示す。注入を規定するのに用いられるマスクにおける開口部の幅は、拡散領域 7 0 4 の多量にドープされた部分の深さよりも広いので、従来の拡散領域 7 0 1 B は制限された拡散領域 7 0 1 A と本質的に同じ深さを有する。

30

#### 【 0 1 0 6 】

拡散領域 7 1 0 A はトレンチ 7 1 2 によって制限される狭い拡散の一例である。注入 7 1 3 は線 C - C の長さで示されるようにトレンチ間に延在し、幅が約  $0.5 \mu\text{m}$  である。拡散領域 7 1 0 A の幅が拡散の深さ未満であるにもかかわらず、接合 7 1 3 は広い拡散領域 7 0 1 A および 7 0 1 B に対し（少しも広くないにしても）明らかに等しい深さを有するので、不十分な拡散を示さない。その深さにもかかわらず、トレンチにより制限された拡散領域 7 1 3 はまた極めて狭い幅を有する。

40

#### 【 0 1 0 7 】

拡散領域 7 1 0 B は狭い制限されない拡散の一例であり、ここでは 2 次元の拡散の損失、いわゆる「不十分な拡散」が明らかになる。拡散された領域 7 1 4 が領域 7 1 5 に横方向に広がるだけでなく、拡散領域 7 1 4 の多量にドープされた部分は線 E - E を越えるほど深くに拡散すらしない。実際には、これは、拡散を 1 次元から 2 次元に変えてポイント源（point source）を作り出す大きな横方向の拡散の成分である。7 1 0 A と 7 1 0 B とを比較すると、トレンチにより制限された拡散領域はより深く、より多量にドープされ、はるかに狭くなるが、それらはすべて集積回路の構成要素を実現する際の所望の特徴である。

#### 【 図面の簡単な説明 】

50

## 【0108】

【図1A】半導体素子における拡散された領域を形成するための一般的なプロセスと、特に熱処理中に発生する横方向のドーパント拡散とを示す図である。

【図1B】半導体素子における拡散された領域を形成するための一般的なプロセスと、特に熱処理中に発生する横方向のドーパント拡散とを示す図である。

【図1C】半導体素子における拡散された領域を形成するための一般的なプロセスと、特に熱処理中に発生する横方向のドーパント拡散とを示す図である。

【図1D】半導体素子における拡散された領域を形成するための一般的なプロセスと、特に熱処理中に発生する横方向のドーパント拡散とを示す図である。

【図2A】拡散された区域の深さがドーパントを注入するマスク開口部の幅によっていかに異なるかを示す図である。

【図2B】拡散された区域の深さがドーパントを注入するマスク開口部の幅によっていかに異なるかを示す図である。

【図3A】図1A～図1Dおよび図2A～図2Bに示される問題の概要を示す図である。

【図3B】図1A～図1Dおよび図2A～図2Bに示される問題の概要を示す図である。

【図4A】熱処理中の埋込層と垂直な分離領域との間の分離を維持する際の問題を示す図である。

【図4B】熱処理中の埋込層と垂直な分離領域との間の分離を維持する際の問題を示す図である。

【図5A】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図5B】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図5C】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図5D】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図5E】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図5F】図4Bに示される構造を形成するためのプロセスのステップを示す図である。

【図6】熱収支と横方向のドーパント拡散の量とを減じる技術として分離領域の下方における上方拡散する埋込層の使用を示す図である。

【図7A】図6に示される構造を形成するプロセスのステップを示す図である。

【図7B】図6に示される構造を形成するプロセスのステップを示す図である。

【図7C】図6に示される構造を形成するプロセスのステップを示す図である。

【図7D】図6に示される構造を形成するプロセスのステップを示す図である。

【図7E】図6に示される構造を形成するプロセスのステップを示す図である。

【図7F】図6に示される構造を形成するプロセスのステップを示す図である。

【図8】誘電体が充填されたトレンチを含む分離構造を示す図である。

【図9A】図8に示される分離構造を作製するためのプロセスを示す図である。

【図9B】図8に示される分離構造を作製するためのプロセスを示す図である。

【図9C】図8に示される分離構造を作製するためのプロセスを示す図である。

【図9D】図8に示される分離構造を作製するためのプロセスを示す図である。

【図9E】図8に示される分離構造を作製するためのプロセスを示す図である。

【図9F】図8に示される分離構造を作製するためのプロセスを示す図である。

【図10A】図8に示される分離構造のトレンチを充填する際に発生し得る問題を示す図である。

【図10B】図8に示される分離構造のトレンチを充填する際に発生し得る問題を示す図である。

【図10C】図8に示される分離構造のトレンチを充填する際に発生し得る問題を示す図である。

【図10D】図8に示される分離構造のトレンチを充填する際に発生し得る問題を示す図である。

【図11A】先行技術の拡散技術を用いて形成される半導体素子を示す図である。

【図11B】先行技術の拡散技術を用いて形成される半導体素子を示す図である。

10

20

30

40

50

- 【図11C】先行技術の拡散技術を用いて形成される半導体素子を示す図である。

- 【図11D】先行技術の拡散技術を用いて形成される半導体素子を示す図である。

- 【図11E】先行技術の拡散技術を用いて形成される半導体素子を示す図である。

- 【図12】分離拡散領域とは反対の導電型のエピタキシャル層において形成されるトレンチにより制限された基本的な分離拡散領域を示す図である。

- 【図13A】図12に示されるトレンチにより制限された分離拡散領域の変形例を示す図である。

- 【図13B】図12に示されるトレンチにより制限された分離拡散領域の変形例を示す図である。

- 【図13C】図12に示されるトレンチにより制限された分離拡散領域の変形例を示す図である。

10

- 【図13D】図12に示されるトレンチにより制限された分離拡散領域の変形例を示す図である。

- 【図14】シンカ拡散領域と同じ導電型のエピタキシャル層に形成されるトレンチにより制限されたシンカ拡散領域を示す図である。

- 【図15A】図14に示されるトレンチにより制限されたシンカ拡散領域の変形例を示す図である。

- 【図15B】図14に示されるトレンチにより制限されたシンカ拡散領域の変形例を示す図である。

- 【図15C】図14に示されるトレンチにより制限されたシンカ拡散領域の変形例を示す図である。

20

- 【図15D】図14に示されるトレンチにより制限されたシンカ拡散領域の変形例を示す図である。

- 【図15E】図14に示されるトレンチにより制限されたシンカ拡散領域の変形例を示す図である。

- 【図16A】P型の基板におけるトレンチにより制限されたN型のシンカを示す図である。

- 【図16B】P型のエピタキシャル層におけるトレンチにより制限されたN型のシンカを示す図である。

- 【図16C】下にあるN埋込層と融合するトレンチにより制限されたN型のシンカを示す図である。

30

- 【図16D】広角の分離構造の一部として形成されるトレンチにより制限されたN型のシンカを示す図である。

- 【図16E】広角の分離構造の一部として形成されるトレンチにより制限されたN型のシンカを示す図である。

- 【図17】N埋込層に延在する誘電体が充填されたトレンチを含む分離構造を示す図である。

- 【図18】P型の基板に形成されるP型のトレンチにより制限されたシンカを示す図である。

- 【図19】P型のエピタキシャル層に形成されるP型のトレンチにより制限されたシンカを示す図である。

40

- 【図20】P基板に形成されるトレンチにより制限されたNウェルを示す図である。

- 【図21】Nエピタキシャル層に形成されるトレンチにより制限されたPウェルを示す図である。

- 【図22A】誘電体が充填されたトレンチを用いるPエピタキシャル層とN埋込層との分離されたポケットの形成を示す図である。

- 【図22B】誘電体が充填されたトレンチを用いるPエピタキシャル層とN埋込層との分離されたポケットの形成を示す図である。

- 【図23A】誘電体が充填されたトレンチを用いるP基板と注入された深いN領域との分離されたポケットの形成を示す図である。

50

【図23B】誘電体が充填されたトレンチを用いるP基板と注入された深いN領域との分離されたポケットの形成を示す図である。

【図24A】誘電体が充填されたトレンチを用いるNエピタキシャル層とP埋込層との分離されたポケットの形成を示す図である。

【図24B】誘電体が充填されたトレンチを用いるNエピタキシャル層とP埋込層との分離されたポケットの形成を示す図である。

【図25A】誘電体が充填されたトレンチを用いるN基板と注入された深いP領域との分離されたポケットの形成を示す図である。

【図25B】誘電体が充填されたトレンチを用いるN基板と注入された深いP領域との分離されたポケットの形成を示す図である。 10

【図26A】誘電体が充填されたトレンチを用いるNエピタキシャル層と、N埋込層によってP基板から分離されているP埋込層との分離されたポケットの形成を示す図である。

【図26B】誘電体が充填されたトレンチを用いるNエピタキシャル層と、N埋込層によってP基板から分離されているP埋込層との分離されたポケットの形成を示す図である。

【図27A】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27B】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27C】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27D】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27E】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27F】誘電体が充填されたトレンチを形成するプロセスを示す図である。 20

【図27G】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27H】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図27I】誘電体が充填されたトレンチを形成するプロセスを示す図である。

【図28】相補型アナログバイポーラトランジスタの構築のためのプロセスフローを示す図である。

【図29A】図28に概略が示されたプロセスのステップを示す図である。

【図29B】図28に概略が示されたプロセスのステップを示す図である。

【図29C】図28に概略が示されたプロセスのステップを示す図である。

【図29D】図28に概略が示されたプロセスのステップを示す図である。

【図29E】図28に概略が示されたプロセスのステップを示す図である。 30

【図29F】図28に概略が示されたプロセスのステップを示す図である。

【図29G】図28に概略が示されたプロセスのステップを示す図である。

【図29H】図28に概略が示されたプロセスのステップを示す図である。

【図29I】図28に概略が示されたプロセスのステップを示す図である。

【図29J】図28に概略が示されたプロセスのステップを示す図である。

【図29K】図28に概略が示されたプロセスのステップを示す図である。

【図29L】図28に概略が示されたプロセスのステップを示す図である。

【図29M】図28に概略が示されたプロセスのステップを示す図である。

【図30】狭いパターンサイズおよび広いパターンサイズの両方について、制限されない拡散領域とトレンチにより制限された拡散領域との比較を示す図である。 40

【図 1 A】

FIG. 1A

(Prior Art)

【図 1 C】

FIG. 1C

(Prior Art)

【図 1 B】

FIG. 1B

(Prior Art)

【図 1 D】

FIG. 1D

(Prior Art)

【図 2 A】

FIG. 2A

(Prior Art)

【図 3 A】

FIG. 3A

(Prior Art)

【図 2 B】

FIG. 2B

(Prior Art)

【図 3 B】

FIG. 3B

(Prior Art)

【図 4 B】

FIG. 4B

(Prior Art)

【図 4 A】

FIG. 4A

(Prior Art)

【図 5 A】

FIG. 5A

(Prior Art)

【図 5 B】

FIG. 5B

(Prior Art)

【図 5 C】

FIG. 5C

(Prior Art)

【図 5 D】

FIG. 5D

(Prior Art)

【図 5 E】

FIG. 5E

(Prior Art)

【図 5 F】

FIG. 5F

(Prior Art)

【図 6】

FIG. 6

(Prior Art)

【図 7 A】

FIG. 7A

(Prior Art)

【図 7 B】

FIG. 7B

(Prior Art)

【図 7 C】

FIG. 7C

(Prior Art)

【図 7 D】

【図 7 E】

FIG. 7E

(Prior Art)

FIG. 7D

(Prior Art)

【図 7 F】

FIG. 7F

(Prior Art)

【図 8】

FIG. 8

(Prior Art)

【図 9 A】

FIG. 9A

(Prior Art)

【図 9 B】

FIG. 9B

(Prior Art)

【図 9 C】

FIG. 9C

(Prior Art)

【図 9 D】

FIG. 9D

(Prior Art)

【図 9 E】

FIG. 9E

(Prior Art)

【図 9 F】

FIG. 9F

(Prior Art)

【図 10 A】

FIG. 10A

(Prior Art)

【図 10 B】

FIG. 10B

(Prior Art)

【図 10C】

FIG. 10C

(Prior Art)

【図 10D】

FIG. 10D

(Prior Art)

【図 11A】

FIG. 11A

(Prior Art)

【図 11B】

FIG. 11B

(Prior Art)

【図 1 1 C】

【図 1 1 D】

FIG. 11D

(Prior Art)

【図 1 1 E】

FIG. 11C

(Prior Art)

【図 1 2】

FIG. 12

【図 1 3 A】

FIG. 13A

【図 13B】

FIG. 13B

【図 13C】

FIG. 13C

【図 13D】

FIG. 13D

【図 14】

FIG. 14

【図 15A】

FIG. 15A

【図 15C】

FIG. 15C

【図 15B】

FIG. 15B

【図 15D】

FIG. 15D

【図 15 E】

FIG. 15E

【図 16 B】

FIG. 16B

【図 16 A】

FIG. 16A

【図 16 C】

FIG. 16C

【図 16 D】

FIG. 16D

【図 17】

FIG. 17

【図 16 E】

FIG. 16E

【図 18】

FIG. 18

【図 19】

FIG. 19

【図 20】

FIG. 20

【図 21】

FIG. 21

【図 22 A】

FIG. 22A

【図 22 B】

FIG. 22B

【図 23 B】

FIG. 23B

【図 23 A】

FIG. 23A

【図 24 A】

FIG. 24A

【図 24B】

FIG. 24B

【図 25B】

FIG. 25B

【図 25A】

FIG. 25A

【図 26A】

FIG. 26A

【図 26B】

FIG. 26B

【図 27B】

【図 27A】

FIG. 27A

FIG. 27B

【図 27C】

FIG. 27C

【図 27D】

FIG. 27D

【図 27E】

FIG. 27E

【図 27F】

FIG. 27F

【図27G】

FIG. 27G

### 【図27H】

FIG. 27H

### 【図27Ⅰ】

FIG. 271

【 図 28 】

【図 29A】

FIG. 29A

【図 29B】

FIG. 29B

【図 29C】

FIG. 29C

【図 29D】

FIG. 29D

【図 29E】

FIG. 29E

【図 29F】

FIG. 29F

【図 29G】

FIG. 29G

【図 29H】

FIG. 29H

【図 29I】

FIG. 29I

【図 29J】

FIG. 29J

【図 29K】

FIG. 29K

【図 29L】

FIG. 29L

【図 29M】

FIG. 29M

【図 30】

FIG. 30

## フロントページの続き

|                          |                   |

|--------------------------|-------------------|

| (51)Int.Cl.              | F I               |

| H 01 L 27/082 (2006.01)  | H 01 L 27/06 101U |

| H 01 L 27/06 (2006.01)   | H 01 L 27/06 321C |

| H 01 L 21/8248 (2006.01) | H 01 L 27/08 102E |

| H 01 L 21/8222 (2006.01) |                   |

| H 01 L 21/8249 (2006.01) |                   |

| H 01 L 21/8234 (2006.01) |                   |

| H 01 L 27/088 (2006.01)  |                   |

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100109162

弁理士 酒井 將行

(72)発明者 ウィリアムズ, リチャード・ケイ

アメリカ合衆国、95014 カリフォルニア州、キューパーティーノ、ノーウィッヂ・アベニュー

、10292

(72)発明者 コーネル,マイケル・イー

アメリカ合衆国、95008 カリフォルニア州、キャンベル、サマーフィールド・ドライブ、1

576

(72)発明者 チャン,ワイ・ティエン

中華人民共和国、香港、ファンリン・エヌ・ティ、リージェントウィル、ロック・5、フラット

・エフ、23/エフ

審査官 三浦 尊裕

(56)参考文献 特開2000-315742 (JP, A)

特開昭58-100441 (JP, A)

特開昭60-186035 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/331

H01L 21/8222

H01L 21/8228

H01L 21/8234

H01L 21/8248

H01L 21/8249

H01L 27/06

H01L 27/082

H01L 27/088

H01L 29/73

H01L 29/732