(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 603 02 821 T2 2006.08.10

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 349 171 B1

(21) Deutsches Aktenzeichen: 603 02 821.7

(96) Europäisches Aktenzeichen: 03 251 315.2

(96) Europäischer Anmeldetag: 05.03.2003

(97) Erstveröffentlichung durch das EPA: 01.10.2003

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 21.12.2005

(47) Veröffentlichungstag im Patentblatt: 10.08.2006

(51) Int Cl.<sup>8</sup>: **G11C 7/10 (2006.01)**

**G11C 19/00 (2006.01)**

(30) Unionspriorität:

**107939** 27.03.2002 US

(74) Vertreter:

**Schoppe, Zimmermann, Stöckeler & Zinkler, 82049

Pullach**

(73) Patentinhaber:

**Hewlett-Packard Development Co., L.P., Houston,

Tex., US**

(84) Benannte Vertragsstaaten:

**DE, GB**

(72) Erfinder:

**Perner, Frederick A., Palo Alto CA 94304, US**

(54) Bezeichnung: **Data-Austauschvorrichtung zwischen Abtastketten**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingeleitet, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf Vorrichtungen zur Daten-Speicherung und -Wiedergewinnung, z. B. auf eine Speichervorrichtung, die vom Resistiv-Kreuzpunktspeicher-Zellentyp (RXPtM-Zellentyp; RXPtM = resistive cross point memory) sein kann (wobei ein Beispiel davon ein magnetischer Direktzugriffspeicher (MRAM; MRAM = magnetic random access memory) ist), der mehrere serielle Daten- und Steuer-Wege aufweist. Die mehreren seriellen Datenwege können zusammengeführt sein und können Daten nach Bedarf durch die Eingangs-/Ausgangs-Schaltungen (I/O-Schaltungen) austauschen, die mit einem seriellen I/O-Tor verbunden sind. Eine Mehrzahl von Abtastwegregistern kann durch ein Array aus Statischer-Direktzugriffspeicher-Speicherzellen (SRAM-Speicherzellen) verbunden sein, um eine parallele Übertragung von Daten von Abtastwertregistern zu und von temporären Registern in dem SRAM-Speicherarray auszuführen, um einen Datenaustausch zwischen mehreren Abtastwegregistern zu bewirken.

**[0002]** Eine Abtastkette ist ein Satz aus Registern, die in Reihe mit einer Einrichtung geschaltet sind, um Daten zwischen den Registern in der Reihe zu verschieben, um Daten von dem einen Ende der Abtastkette zu dem anderen Ende zu übertragen, oder um die Funktion zum Steuern des Zustands der Register der Abtastkette auszuführen. Ein Beispiel der Verwendung einer Abtastkette ist das Verbinden der I/O-Anschlussflächen eines Chips, als eine Einrichtung zum seriellen Übertragen von Steuerdaten und Adressdaten, angelegt an den Eingang des Chips, zu den Speichersteuerblöcken oder Speicherarrayblöcken, und zum seriellen Übertragen von Ausgangsdaten von dem Speicherarray oder den Steuerblöcken zu den I/O-Anschlussflächen des Chips. Ein Beispiel einer seriellen Abtastkette, die üblicherweise in digitalen integrierten Schaltungen angetroffen wird, ist eine „Grenz-Abtast-Kette“, bei der der I/O für einen Chip oder Schaltungsblock mit einer Abtastkette verbunden ist, um die Option zu liefern, den I/O parallel zu extrahieren oder den I/O auf serielle Weise zu extrahieren, durch Verschieben des I/O zu einem einzelnen Ausgangstor durch die „Grenz-Abtast-Kette“.

**[0003]** Eine andere Form einer Grenz-Abtast-Kette verbindet die parallelen Steuer- und I/O-Funktionen eines Systemblocks mit einem kleinen Satz aus seriellen Datentoren. Abtastketten werden auch in digitalen Logiksystemen angetroffen, die alle Register des Systems miteinander als Teil eines Abtasttestsystems verbinden. Ein Beispiel eines Systems, das viele Steuer- und Daten-Abtastketten enthalten kann, ist ein MRAM-Speicher. Ein solcher MRAM-Speicher wäre eine komplette Vorrichtung, die Systemsteuerelemente, wobei mehrere Lokal-Daten-I/O-Abtastket-

ten Teil-Blöcke der MRAM-Speicherzellenarrays miteinander verbinden, und eine Abtastkette zum Verbinden der System-I/O-Tore umfasst.

**[0004]** Bekannte Lösungen für das Problem des Austauschens von Daten zwischen mehreren Abtastkettenregistern habe erforderlich gemacht, das kundenspezifisch entworfene Logikschaltungen die Funktion des Bewegens von Daten von einer Abtastkette zu einer anderen ausführen. Diese herkömmliche Lösung erfordert nachteilhafterweise, dass eine kundenspezifische Logikschaltung für jede Anwendung entworfen wird. Ferner kann für eine minimale Konfiguration zum Koppeln von zwei Abtastketten die herkömmliche Lösung eine vernünftige Lösung sein. Wenn jedoch mehr als zwei Abtastketten gekoppelt werden sollen, dann besteht ein Bedarf nach einer verstärkt temporären Speicherung als Teil der Abtastketten-Datenaustauschschaltungsanordnung. In diesem Kontext wird die herkömmliche Lösung zu komplex, um praktikabel zu sein.

**[0005]** Beispiele einer bekannten Technik, die für die vorliegende Erfindung relevant sein kann, sind ersichtlich in den U.S.-Patenten Nr.: 5,197,070 erteilt am 23. März 1993 an Hideshi Maeno, 5,636,228 erteilt am 3. Juni 1997 an Claude Moughanni, u. a.; 5,719,504 erteilt am 17. Februar 1998 an Shtaka Yamada; und insbesondere in dem U.S.-Patent Nr. 5,953,285, erteilt am 14. September 1999 an Jonathan E. Churchill u. a. Das Patent Nr. 5,197,070 (Maeno) verwendet angeblich einen Abtastweg mit mehreren Registern, um eine Testfunktion in einem Speicher zu beeinflussen. Das U.S.-Patent Nr. 5,636,228 (Moughanni) scheint ein tristatemäßig betreibbares Abtastregister zu beschreiben, um das Befreien der Abtastkette zu unterstützen, während die Datenausgabe aus einer Schaltung gesteuert wird. Das U.S.-Patent Nr. 5,719,504 (Yamada) beschreibt angeblich ein Register (Flip-Flop), das in einer kombinatorischen Logik angetroffen wird, das seriell mit einem Abtastregister verbunden sein kann zum Zweck des Speicherns des Zustands der Register und des Erlaubens, dass die Inhalte der Register in die und aus der Schaltung unter Verwendung einer Abtastkette verschoben werden. Das U.S.-Patent Nr. 5,953,285 (Churchill) beschreibt angeblich ein Steueregister als eine Schnittstelle zu einer Speicher- schaltung und zeichnet sich aus durch synchrone oder asynchrone Operationsmodi, bei denen das Register ein Abtastregister enthalten kann. Schließlich offenbart das U.S.-Patent Nr. 5,867,507 Speicherzellen, die unterschiedliche Abtastketten verbinden und beim Übertragen der Daten von einer Abtastkette zu einer anderen verwendet werden.

**[0006]** Ferner ist der magnetische Direktzugriffs- speicher („MRAM“) ein nichtflüchtiger Speicher, der für Langzeitdatenspeicherung in Betracht gezogen wird. Eine typische MRAM-Vorrichtung umfasst ein

Array aus Speicherzellen. Wortleitungen erstrecken sich entlang Zeilen der Speicherzellen, und Bitleitungen erstrecken sich entlang Spalten der Speicherzellen. Die Speicherzellen sind jeweils an einem Kreuzungspunkt einer Wortleitung und einer Bitleitung angeordnet, und jede Speicherzelle umfasst zwei Massen aus Magnetmaterial. Eine der Massen ist magnetisch fest und die andere ist magnetisch variabel. Eine Speicherzelle speichert ein Informationsbit als die Ausrichtung der relativen Magnetisierung des festen und variablen Materials. Anders ausgedrückt nimmt die Magnetisierung jeder Speicherzelle zu einer gegebenen Zeit eine von zwei stabilen Ausrichtungen ein. Diese zwei stabilen Ausrichtungen, die als eine „parallele“ und „antiparallele“ magnetische Ausrichtung bezeichnet werden, stellen Logikwerte z. B. von „0“ und „1“ dar. Der Widerstand einer Speicherzelle variiert abhängig davon, ob sie einen „0“- oder einen „1“-Wert speichert. Das heißt, der Widerstand einer Speicherzelle ist ein erster Wert „R“, wenn die Ausrichtung der Magnetisierung des festgelegten Magnetmaterials und des variablen Magnetmaterials parallel ist, und der Widerstand der Speicherzelle wird auf einer zweiten Wert  $R + DR$  erhöht, wenn die Ausrichtung der Magnetisierung antiparallel ist. Die Ausrichtung der relativen Magnetisierung einer ausgewählten Speicherzelle (und daher der Logikzustand der Speicherzelle) kann erfasst werden durch Erfassen des Widerstandswerts der ausgewählten Speicherzelle.

**[0007]** Somit, obwohl die vorliegende Erfindung nicht derart beschränkt ist, kann eine Implementierung dieser Erfindung einen MRAM-Speicher verwenden. Das heißt, ein Beispiel dieser Erfindung kann in einer MRAM-Speichervorrichtung implementiert sein, wobei die Speichervorrichtung Steuer- und Daten-Abtastketten aufweist, wie oben erwähnt wurde.

**[0008]** Die vorliegende Erfindung schafft eine verbesserte Datenaustausch-Vorrichtung und ein -Verfahren.

**[0009]** Gemäß einem Aspekt der vorliegenden Erfindung wird eine Vorrichtung geschaffen, die Daten zwischen Abtastketten austauscht, wie in Anspruch 1 spezifiziert wird.

**[0010]** Das bevorzugte Ausführungsbeispiel kann eine effektive und effiziente Lösung zum Koppeln mehrerer Abtastketten schaffen, mit der Möglichkeit zum Addieren verschiedener Beträge von zusätzlichem Speicher zum Austauschen von Daten zwischen den Abtastketten, durch Bereitstellen eines SRAM-Speicherarrays an dem Übergang der mehreren Abtastketten.

**[0011]** Gemäß einem Ausführungsbeispiel der vorliegenden Erfindung werden mehrere Abtastkettenre-

gister mit einem SRAM-Speicher kombiniert, um eine parallele Übertragung von Daten von Abtastwegregistern zu einer temporären Speicherung in dem SRAM-Speicher auszuführen, um zu einem anderen der mehreren Abtastkettenregister, bei einem Prozess zum Austauschen von Daten zwischen den mehreren Abtastkettenregistern.

**[0012]** Gemäß einer Implementierung der vorliegenden Erfindung weisen MRAM-Speicher-Teilarrays ein Zugriffszeitintervall auf, das ausreichend lang ist, dass relativ lange Datenabtastketten parallel während eines Speicher-Teilarray-Zugriffsintervalls geladen werden können. Durch paralleles Zugreifen auf eine große Anzahl von Teilarrays kann ein Datenübertragungsverhalten auf höherer Ebene bei einer solchen Speichervorrichtung erreicht werden.

**[0013]** Ferner offenbart die vorliegende Erfindung eine registerbasierte Schaltung zum Austauschen von Daten zwischen mehreren Abtastketten, wobei zumindest eine derselben eine Schnittstelle mit den I/O-Schaltungen zum Ausgeben von Daten bilden kann.

**[0014]** Die vorliegende Erfindung schafft ferner ein Verfahren zum Austauschen von Daten unter mehreren Abtastketten. Die Abtastketten können während des Datenaustauschs statisch sein, aber vorzugsweise sind sie während des Datenaustauschs dynamisch. Ausführungsbeispiele der vorliegenden Erfindung schaffen eine dynamische Operation der Abtastketten, sogar während Daten unter den mehreren Abtastketten ausgetauscht und gemeinschaftlich verwendet werden.

**[0015]** Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend ausschließlich beispielhaft Bezug nehmend auf die beiliegenden Zeichnungen beschrieben, in denen:

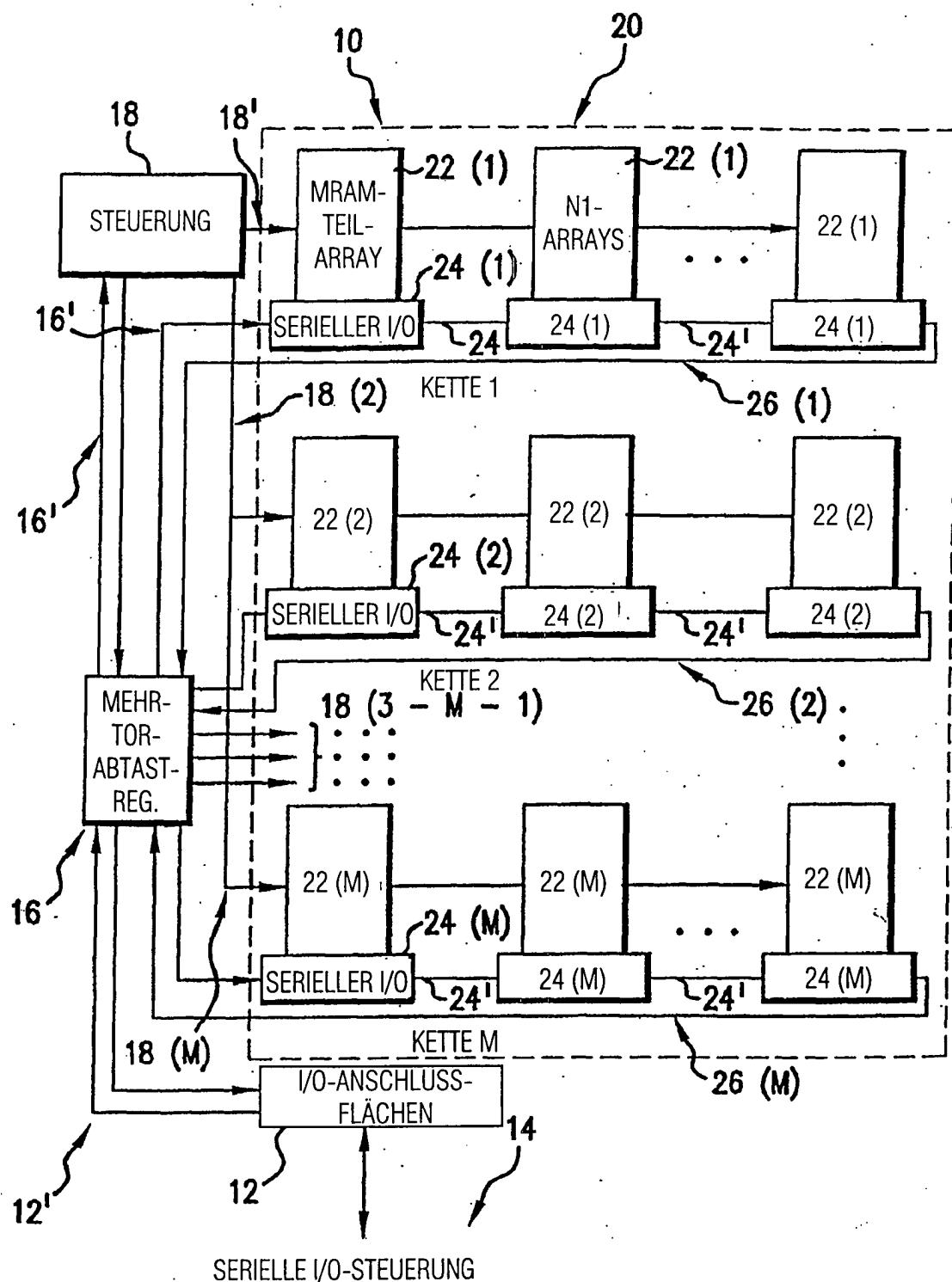

**[0016]** [Fig. 1](#) eine sehr verallgemeinerte, schematische Darstellung eines Ausführungsbeispiels der Speichervorrichtung ist;

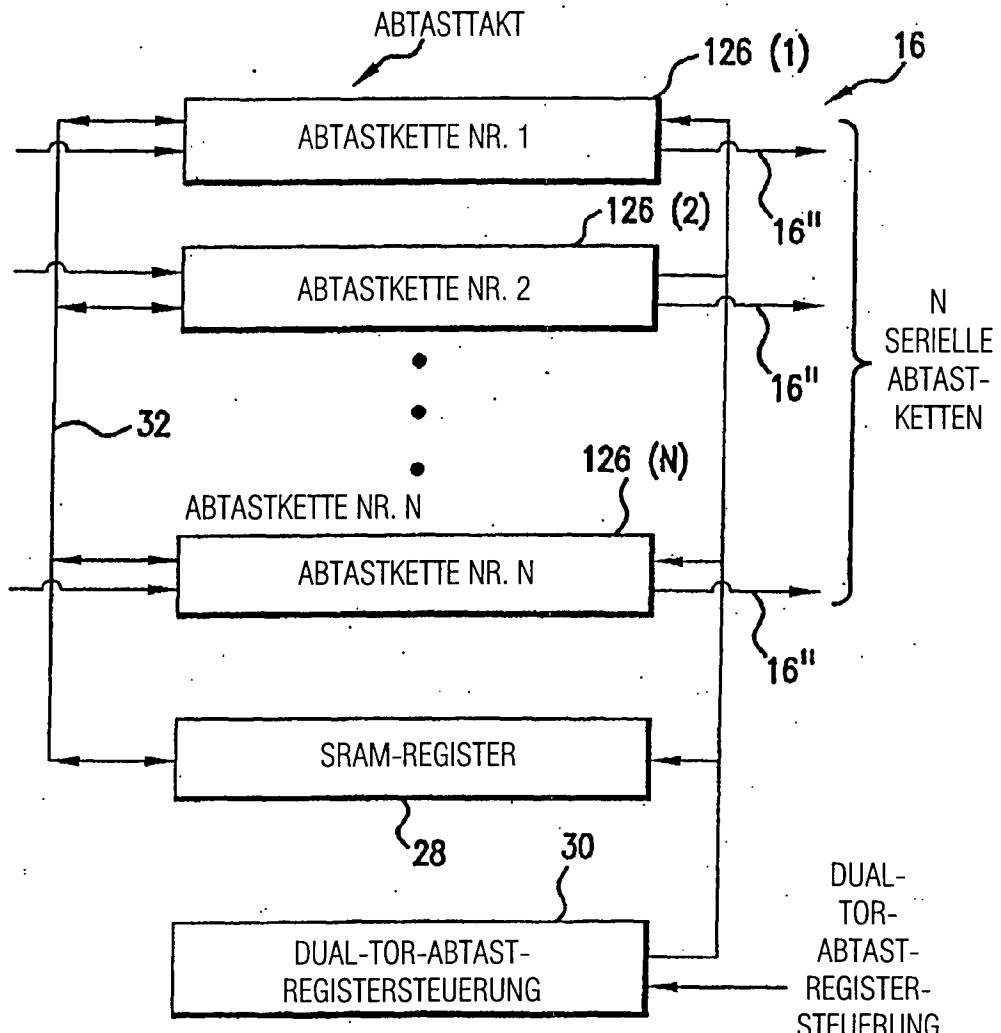

**[0017]** [Fig. 2](#) schematisch einen Abschnitt der Speichervorrichtung darstellt, die in [Fig. 1](#) gezeigt ist;

**[0018]** [Fig. 3](#) schematisch den Abschnitt der Speichervorrichtung darstellt, die in [Fig. 1](#) und [Fig. 2](#) gezeigt ist, und detaillierter präsentiert wird;

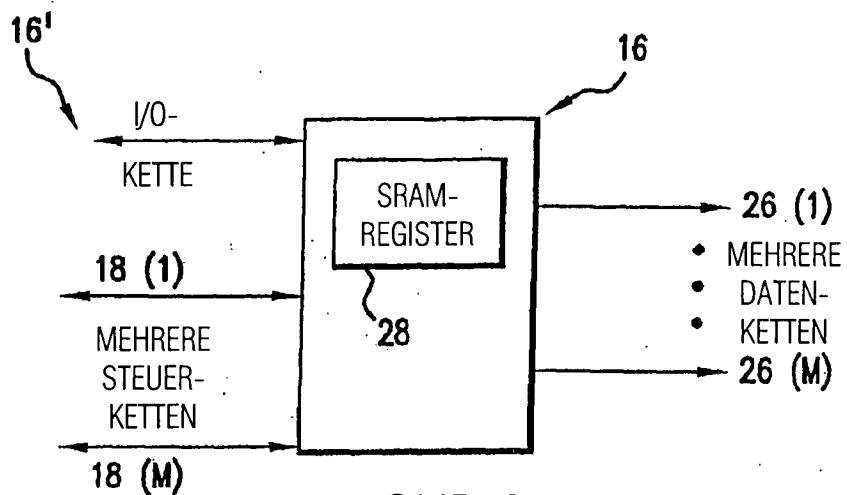

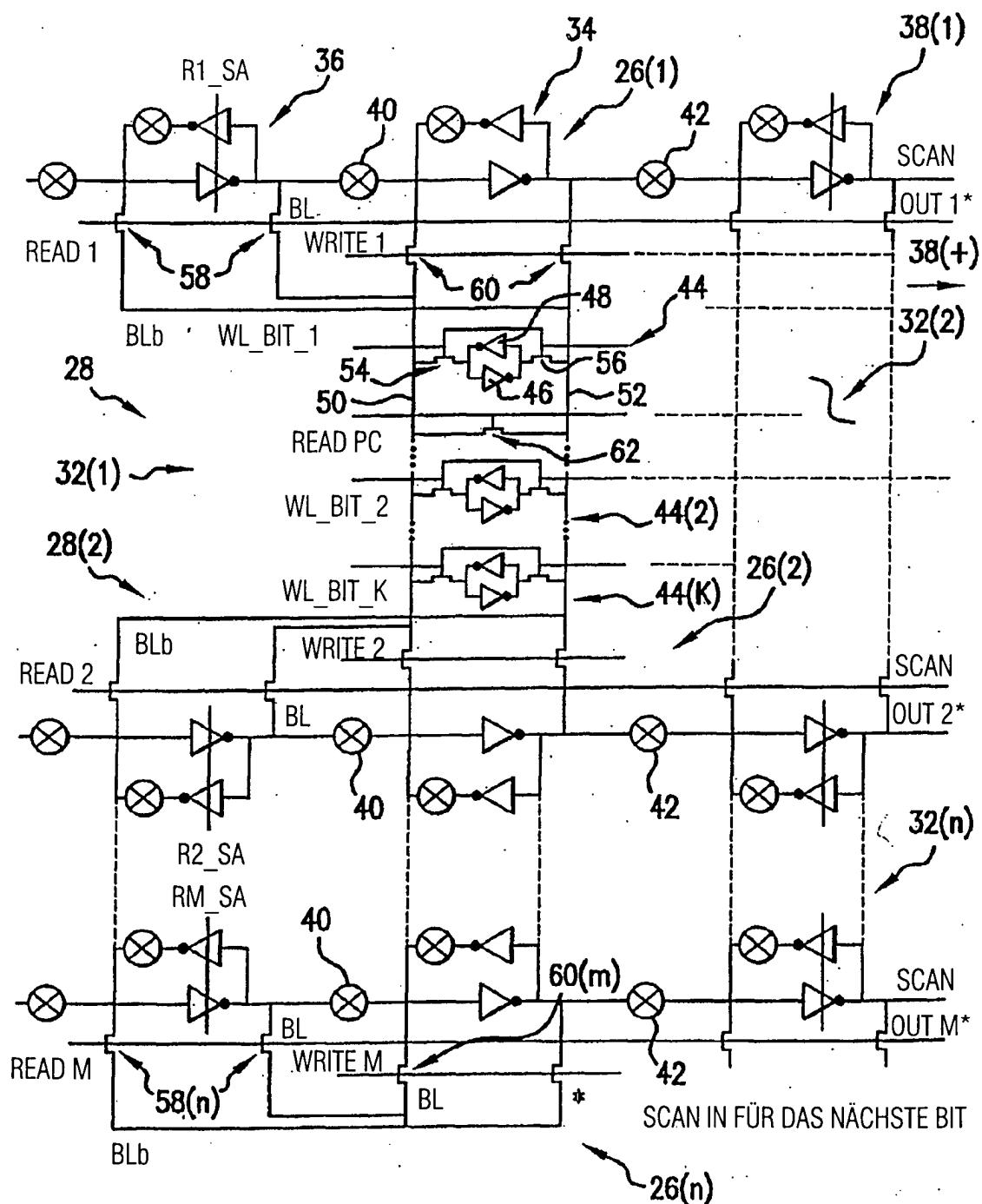

**[0019]** [Fig. 4](#) eine spezifizierte Darstellung der Vierichtungsarchitektur ist, die in [Fig. 3](#) gezeigt ist; und

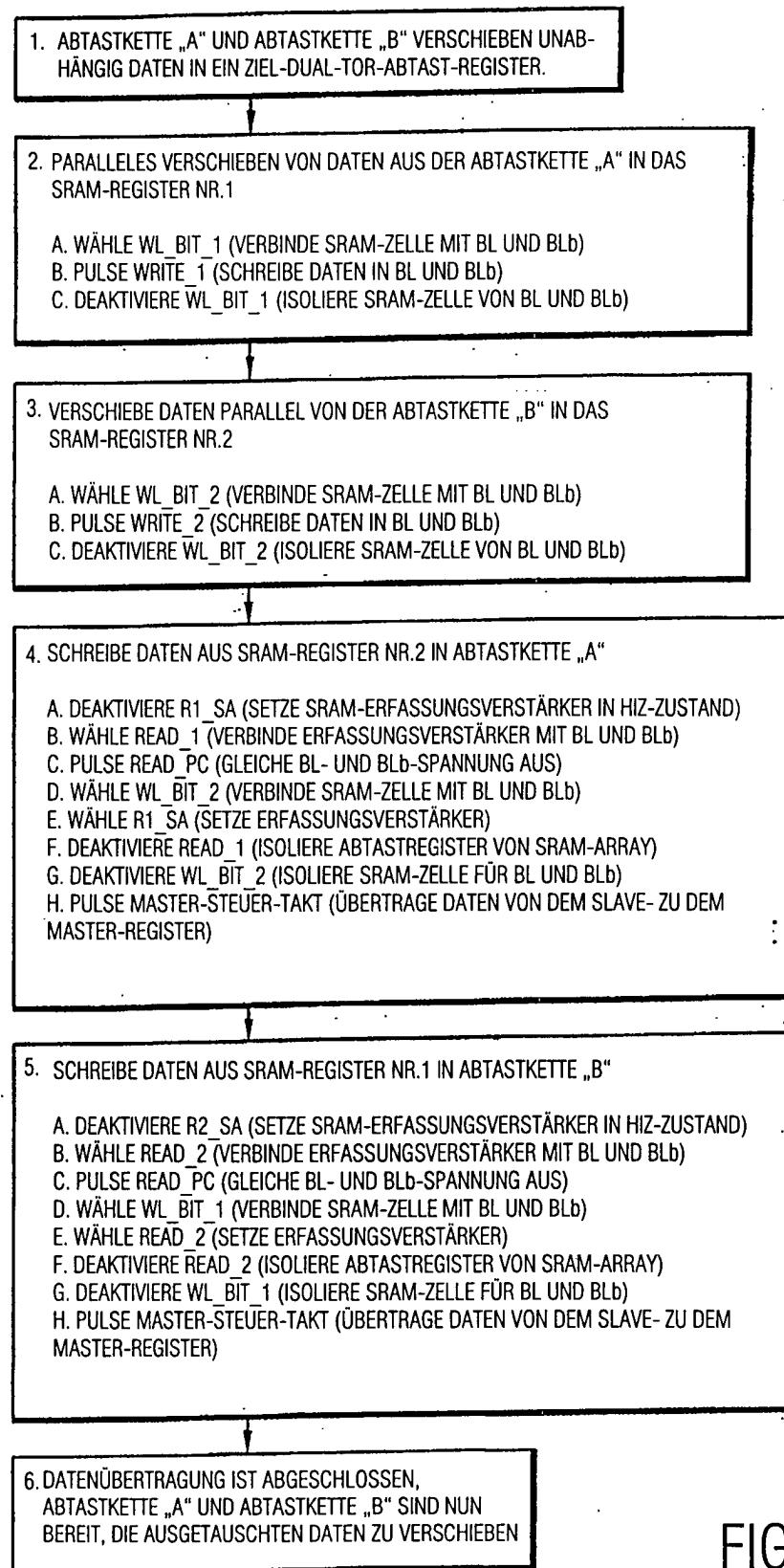

**[0020]** [Fig. 5](#) eine graphische Darstellung oder ein Prozessflussdiagramm ist, das Ereignisse und Aktionen bei einem Prozess zum Implementieren eines Datenaustauschs darstellt.

**[0021]** Die vorliegende Erfindung schafft ein Verfahren und eine Vorrichtung zum Austauschen von Daten zwischen mehreren Abtastketten. Ein Beispiel einer Implementierung dieser Erfindung ist eine SRAM-Speichervorrichtung, die die I/O-Datenwege aus einer Gruppe von MRAM-Speicherarrays, einen Satz aus SRAM-Registern und eine Eingabe-/Ausgabe-(I/O-)Steuerung umfasst. Andere Typen von Vorrichtungen und andere Typen von Speicher jedoch, abgesehen von einem SRAM, können gemäß der vorliegenden Erfindung implementiert werden.

**[0022]** Es ist wichtig, dass das System und das Verfahren ermöglichen, dass mehrere serielle Datenwege zusammengeführt werden und Daten nach Bedarf durch das Daten-Eingangs-/Ausgangs-I/O-Tor austauschen.

**[0023]** Unter Betrachtung von [Fig. 1](#) ist sehr allgemein eine MRAM-Speichervorrichtung **10** gezeigt. Diese Vorrichtung kann derart betrachtet werden, dass sie eine „Größe“ aufweist, die durch die zufälligen Zahlen  $N \times M$  angezeigt wird, wobei  $N$  und  $M$  jeweils die Anzahl von MRAM-Teilarrays in einer Zeile der Vorrichtung und die Anzahl von solchen Zeilen von MRAM-Teilarrays anzeigen, wie nachfolgend weiter erklärt wird. Das heißt, die Vorrichtung **10**, die in [Fig. 1](#) dargestellt ist, weist eine unbestimmte Größe auf, und Vorrichtungen verschiedener Größen können durch die Erfindung implementiert werden. Die Erfindung ist nicht auf die Implementierung von Speichervorrichtungen einer bestimmten Größe beschränkt. Weder ist die Erfindung auf die Implementierung einer Speichervorrichtung beschränkt. Diese bestimmte exemplarische MRAM-Vorrichtung **10** umfasst ein Array aus Kontaktanschlussflächen **12**, allgemein gezeigt als ein I/O-Tor, an dem serielle Daten- und Steuer-Informationen **14** (angezeigt durch den Pfeil und die Inschrift in [Fig. 1](#)) ausgetauscht werden.

**[0024]** Daten- und Steuer-Informationen, die über das I/O-Tor **12** ausgetauscht werden, werden über eine Verbindung **12'** zu und von einem Mehrtor-Abtastregister-Block (MPSR-Block; MPSR = multi-ported scan register) **16** geleitet, wobei die Steuerinformationen weiter über eine Verbindung **16'** zu und von einer Steuerung **18** geleitet werden. Die Steuerung **18** weist mehrere Verbindungen **18'** auf, wie nachfolgend weiter erklärt wird, wobei jede derselben auch ein eingeklammertes Suffix aufweist, das die jeweilige Zeilenverbindung in ein  $N \times M$ -Speicherarray angezeigt, wie nachfolgend weiter erklärt wird.

**[0025]** Der Mehrtor-Abtastregister-Block **16** und die Steuerung **18** steuern jeweils einen Fluss aus Daten- und Steuer-Informationen zu von einem  $N \times M$ -Array **20** aus MRAM-Speicher-Teilarrays, wobei jedes Teilarray durch das Bezugszeichen **20** angezeigt wird (d. h. mit einer eingeklammerten Suffix-Nummer 1 bis

M, die die Zeile des Speicher-Teilarrays anzeigt (z. B. **22(1)** bis **22(M)**). Die Verbindungen zwischen dem MPSR **16** und den Teilarrays **22** sind in [Fig. 1](#) durch die Bezugszeichen **16"** angezeigt. Beispielsweise und ohne Einschränkung kann jedes MRAM-Teilarray **22** eine Fähigkeit zum Erfassen von zwei Datenbytes mit einem Speicherzugriff aufweisen. Das heißt, während eines einzelnen Speicherzugriffsintervalls, kann jedes der  $N \times M$ -Teilarrays **22** zwei Datenbytes erfassen.

**[0026]** Bezug nehmend nun auf [Fig. 2](#) (die allgemein die Architektur eines Mehrtor-Abtastregisters (MPSR) **16** in Kombination mit [Fig. 1](#) darstellt), ist ersichtlich, dass Datenabtastketten, die serielle I/O-Teile **24** (am besten ersichtlich in [Fig. 1](#)) und Verbindungen **24'** aufweisen, verwendet werden können, um die zwei Datenbytes auf serielle Weise (über die verbundenen jeweiligen seriellen I/O-Teile **24** und Verbindungen **24'**) durch eine Anzahl der MRAM-Teilarrays **22** (d. h. durch „N“ Teilarrays einer Zeile) zu übermitteln, um eine Datenabtastkette **26** zu bilden. Die mehreren Abtastketten der „M“ Zeilen werden jeweils mit den Bezugszeichen **26(1)** bis **26(M)** angezeigt. Ferner kann die Anzahl „M“ der Abtastketten über den Mehrtor-Abtastkettenregister-Block (MPSR-Block) **16** verbunden sein, und die Zahl „M“ könnte (z. B.) 16 oder 32 sein, so dass die Datenabtastkette jeweils 32 oder 64 Datenbytes während eines einzelnen MRAM-Zugriffsintervalls übermitteln kann.

**[0027]** Ferner können mehrere Datenabtastketten **26** mit jedem MRAM-Teilarray vorliegen (obwohl nur eine repräsentative einzelne Abtastkette in [Fig. 1](#) gezeigt ist). In [Fig. 1](#) könnte die Zahl „N“ auch (z. B.) 16 oder 32 sein. Somit muss der Mehrtor-Abtastkettenregister-Block **16** Daten von „N“ Datenketten verwalten, und Ketten **18(1)** bis **18(M)** und die serielle I/O-Kette, die die Verbindung **16'** bewirkt (insbesondere im Hinblick auf [Fig. 2](#)) steuern. Es wird aus [Fig. 2](#) ersichtlich, dass das MPSR **16** eine speziell konfigurierte SRAM-Einrichtung **28** umfasst, die ferner nachfolgend beschrieben ist. Durch ihre spezielle Konfiguration schafft die SRAM-Einrichtung **28** das parallele Lesen von Daten aus ausgewählten Orten in einer Abtastkette und das Schreiben dieser Daten in einen unterschiedlichen ausgewählten Ort in der Abtastkette, wie nachfolgend weiter beschrieben wird.

**[0028]** Somit schafft das bevorzugte Ausführungsbeispiel ein Verfahren und eine Vorrichtung zum Lösen dieses Leit-Problems für Daten- und Steuer-Informationen und wird in dem Kontext einer MRAM-Speichervorrichtung präsentiert, obwohl wiederum darauf hingewiesen wird, dass die Erfindung nicht darauf eingeschränkt ist.

**[0029]** Somit, Bezug nehmend auf [Fig. 3](#), ist die Ar-

chitektur des Mehrtor-Abtastregisters (MPSR) **16** de-taillierter dargestellt, wobei ersichtlich ist, dass dieses MPSR **16** Abschnitte der seriellen Abtastketten **26** umfasst (wobei die Abschnitte in [Fig. 3](#) mit den Bezugzeichen **126** angezeigt sind, das auch ein eingeklammertes Suffix aufweist, das hinzugefügt ist, das jenen Suffixen aus [Fig. 1](#) und [Fig. 2](#) entspricht). Das MPSR **16** umfasst ferner die speziell konfigurerte SRAM-Einrichtung **28** und eine Dualtor-Abtastregister-Steuerung **30**. Eine parallele Verbindung **32** (eine von mehreren ist detailliert dargestellt – siehe die eingeklammerten Suffixe) schafft einen parallelen Datenaustausch zwischen ausgewählten Abtastketten (d. h. **26(1)** bis **26(M)**) und der SRAM-Einrichtung **28**, die auch als ein Register bezeichnet werden kann.

**[0030]** Bezug nehmend nur auf [Fig. 4](#) ist ersichtlich, dass drei exemplarische (d. h. aus der Mehrzahl von 1 bis M) Abtastketten **26** dargestellt sind, wie sie durch einen repräsentativen, dargestellten Teil des speziell konfigurierten SRAM-Registers **28** verbunden sind. Der dargestellte Teil jedes Abtastregisters in den Abtastketten **26(1)**, **26(2)** bis **26(N)** umfasst zwei Register, ein Master-Register **34** und ein Slave-Register **36**. Diese zwei Register **34** und **36** arbeiten zusammen, um Daten durch eine serielle Folge aus Abtastregisterabschnitten **38** zu bewegen (wobei der erste angezeigt ist und nachfolgende Registerabschnitte durch die rechtsgerichteten Pfeile in [Fig. 4](#) und das Bezugssymbol **38(+)** angezeigt sind). Diese Datenbewegung durch die Registerabschnitte wird bewirkt durch Pulsen von nichtüberlappenden entsprechenden Takten, angezeigt als Master-Takt **40** und Slave-Takt **42** (wobei Verbindungspunkte für diese Taktsignale angezeigt sind). Es wird in [Fig. 4](#) darauf hingewiesen, das zusätzliche entsprechende Paare solcher nichtüberlappende Taktverbindungen für die zusätzlichen Abtastketten durch die Zahl „N“ des Arrays angezeigt sind.

**[0031]** Jeder Abtastregisterabschnitt **34** ist einer Mehrzahl von SRAM-Speicherzellen **44** zugeordnet, wobei die Anzahl von Speicherzellen **44** in einem SRAM-Registerabschnitt von der Anzahl der Datenwörter abhängt, die zwischen den Abtastregisterabschnitten **34** bewegt werden sollen. Somit ist die Tiefe der Mehrzahl von Speicherzellen **44**, die in [Fig. 4](#) dargestellt sind, ausschließlich exemplarisch, und ist keine Einschränkung für die Erfindung. Dementsprechend werden diese mehreren Speicherzellen mit den Zeichen **44(1)** bis **44(k)** angezeigt, wobei „k“ in diesem Fall die Anzahl von Speicherzellen in dem SRAM-Register anzeigt, die jedem Abschnitt des Abtastkettenregisters **34** zugeordnet sind. Jede Speicherzelle **44** umfasst ein Paar von kreuzgekoppelten Invertern **46**, **48** (wobei nur eine der Zellen in [Fig. 4](#) derart bezeichnet wird, aufgrund von Raumbegrenzungen bei der Zeichnung von [Fig. 4](#)), die jeweils mit einem Paar von Bitleitungen **50**, **52** durch ein Paar

von Auswahl-Transistoren **54**, **56** verbunden sind (wiederum nur jeweils ein Paar aus einer großen Mehrzahl, die derart in [Fig. 4](#) bezeichnet sind, aufgrund von Raumeinschränkungen bei der Zeichnung von [Fig. 4](#)). Daten werden in eine ausgewählte SRAM-Speicherzelle aus einer ausgewählten Abtastkette geschrieben, die das Master-Register **34** sowie die Auswahl-Transistoren **54** und **56** und die Auswahl-Transistoren **60** enthält. Und Daten werden in ein ausgewähltes Abtastketten-Slave-Register **36** aus einer ausgewählten SRRM-Speicherzelle **44** durch Auswahl-Transistoren **54** und **56** und Auswahl-Transistoren **58** geschrieben. Das heißt, die Lesoperations-Transistoren mit den Gate-Steuerelementen gekennzeichnet als „read 1“, „read 2“ bis „read M“, angelegt an die Gates der Transistoren **58**, während die Inverter in dem Slave-Register auf einen Hochimpedanzzustand getaktet werden mit Signalen gekennzeichnet als **R1\_SA**, **R2\_SA** bis **RM\_SA**, leiten in [Fig. 4](#) Daten von einer ausgewählten SRAM-Speicherzelle **44** zu einem ausgewählten Abtastkette-Slave-Register **36**. Und die Schreibtransistoren **60** mit Gate-Steuerelementen gekennzeichnet als „write 1“, „write 2“ bis „write M“ in [Fig. 4](#), leiten Daten aus dem ausgewählten Abtastkette-Master-Register **34**, zu einer ausgewählten SRAM-Speicherzelle **44**.

**[0032]** Die Basis-SRAM-Speicherschaltung aus [Fig. 4](#) umfasst SRAM-Speicherzellen und Decodierer, wie gezeigt wird. Bei diesem Ausführungsbeispiel sind die Decodiererschaltungen konfiguriert, um ausgewählte SRAM-Speicherzellen mit ausgewählten Abtastketten zu verbinden. Daten werden aus einem Abschnitt der ausgewählten Abtastketten gelesen (d. h. den Master-Registern **34**) und in einen unterschiedlichen Abschnitt der ausgewählten Abtastketten geschrieben (d. h. in die Slave-Register **36**). Das Lesen von Daten aus einem SRAM verwendet ein getaktetes Slave-Register, um die Slave-Register-Inverter (d. h. Inverter werden nicht individuell in [Fig. 4](#) bezeichnet sondern sind als Teil des Slave-Abtast-Registers **36** gezeigt und sie sind getaktete Inverter mit den Steuersignalen **R1\_SA**, **R2\_SA** bis **RM\_SA**) in einen Hochimpedanzzustand zu schalten. Dann werden die SRAM-Bitleitungen **50** und **52** abgeglichen (d. h. durch temporäres Schalten des Transistors **62** in einen leitfähigen Zustand und dann zurück in einen nichtleitfähigen Zustand), um zu verhindern, dass die gespeicherte Ladung auf dem Slave-Register die Daten unterbricht, die in der SRAM-Speicherzelle **44** gespeichert sind, die gelesen wird, dann wird die Wortleitung auf der ausgewählten Zeile der SRAM-Zellen aktiviert (d. h. durch Einschalten der Transistoren **54** und **56**). Die SRAM-Daten werden somit auf die Bitleitungen platziert, die mit dem ausgewählten Slave-Register **36** durch Transistoren **58** verbunden sind. Dieses Datensignal an diesem Punkt kann nur eine geringe Differenzspannung sein, abhängig von den Werten der

Schaltungselemente. Der Takt auf den Slave-Registern schaltet jedoch dann die Slave-Register-Inverter ein (d. h. schaltet sie in einen Niedrigimpedanzzustand). Somit wird die Differenzspannung auf dem Slave-Register auf ein Voll-Logik-Wert-Signal verstärkt, wodurch die Leseoperation abgeschlossen wird.

**[0033]** Im Hinblick auf das oben Genannte wird darauf hingewiesen, dass ein Minimum von einer SRAM-Einheit erforderlich ist, um Daten zwischen zwei Abtastketten auszutauschen, wenn die Abtastketten statisch gehalten werden (d. h. dass kein Abtast-Verschieben während des Datenaustauschs erlaubt ist). Andererseits ermöglicht eine Schaltung mit einem Minimum von zwei SRAM-Speichereinheiten, dass Daten zwischen zwei Abtastketten ausgetauscht werden, obwohl eine der zwei Ketten Daten während der Datenaustauschoperation verschieben kann, die über diese zwei SRAM-Speichereinheiten bewirkt wird. Auf ähnliche Weise, wenn drei unabhängige Abtastkettenregister konfiguriert sind, um Daten zwischen denselben auszutauschen, dann kann ein Bedarf bestehen, neun (9) SRAM-Speichereinheiten zu liefern, die diese drei Abtastkettenregister verknüpfen. Dementsprechend ist in der Darstellung aus [Fig. 4](#) ersichtlich, dass in demselben Sinn, wie die Anzahl von Abtastketten **26** unbestimmt ist (und nach Wahl variabel ist), dann die Anzahl von SRAM-Speichereinheiten **44**, die diese Abtastketten **26** verknüpfen, unbestimmt und nach Wahl variabel ist. Die Anzahl von SRAM-Speichereinheiten **44**, die verwendet werden, hängt teilweise von dem Freiheitsgrad, der erreicht werden soll, und ermöglicht, dass die verbundenen Abtastketten Daten während einer gemeinschaftlichen Datenverwendung (d. h. Datenaustauschoperation) zwischen der Mehrzahl von Abtastketten **26** Länge der Datenworte überschreiten, die übertragen werden sollen, um zu ermöglichen, dass die SRAM-Zellen ein größeres Datenspeichervolumen schaffen. Die gespeicherten Daten in den SRAM-Zellen **44** sind eigentlich Daten, die dabei sind, gemeinschaftlich zwischen diesen Abtastketten **26** verwendet zu werden.

**[0034]** Somit könnte diese größere Speicherkapazität (d. h. wenn die Anzahl von SRAM-Zellen **44** die Länge der Datenworte überschreitet) verwendet werden, um mehrere Durchläufe einer Abtastkette zu ermöglichen (d. h. interner Speicher-I/O), um Daten aus mehreren Datenzugriffen in einen temporären SRAM-Speicher zu laden, zur Übertragung zu den Speicher-I/O-Toren (siehe I/O-Tor **24** aus [Fig. 1](#)), zu einer verschobenen Zeit, so dass eine Host-Vorrichtung dann bereit ist, die Daten von der Speichereinheit **10** zu empfangen. Eine alternative Verwendung einer solchen zusätzlichen Tiefe (d. h. eine größere Tiefe als die Länge der Datenworte) eines temporären Speichers in den SRAM-Zellen **44**, bewirkt in den SRAM-Einheiten, die die Abtastketten **26** verbinden,

könnte das Halten von vorgeladenen Daten sein, die häufig in die Speichereinheit **10** gelesen werden können (z. B. BIST-Daten). Die Anzahl von zusätzlichen SRAM-Speichereinheiten **44**, die zu den Abtastkettenregistern **26** hinzugefügt werden, ist nur durch das Verhalten der Speichereinheit **10** beschränkt, das erwünscht ist, und durch das Datenübertragungsverhalten der Abtastregister (d. h. in dem Fall dass ein MRAM-Speicher verwendet wird). Die maximale Anzahl von SRAM-Speichereinheiten **44** wird gegenwärtig auf ungefähr Eintausend (1.000) geschätzt, obwohl dies nicht als eine Einschränkung für die Erfindung betrachtet werden sollte, da das Verhalten der verschiedenen Typen von Speichervorrichtungen, einschließlich MRAM-Speicher, sich verbessert und erwartet wird, dass es sich in der Zukunft weiter verbessert.

**[0035]** Bezug nehmend auf [Fig. 5](#) zeigt dieses Flussdiagramm die Schritte des Austauschens eines Paares aus Datenbits zwischen zwei exemplarischen Abtastkettenregistern. Anstelle hier jeden Schritt und Teilschritt des Prozesses zu wiederholen, der in [Fig. 5](#) dargestellt ist, wird der Leser auf diese Figur verwiesen, und nur Höhepunkte werden direkt nachfolgend detaillierter erläutert.

**[0036]** Schritt eins (1) aus [Fig. 5](#) erklärt, dass die Abtastketten (hier identifiziert als Abtastkette A und als Abtastkette B) die Datenbits jeweils unabhängig verschieben, die ausgetauscht werden sollen, zu entsprechenden Toren (d. h. Schnittstellen des entsprechenden Abtastkettenregisters mit einer SRAM-Speichereinheit).

**[0037]** Bei Schritt zwei (2) aus [Fig. 5](#) verschiebt die Abtastkette „A“ die jeweiligen Daten parallel in eine ausgewählte Zeile einer Verbindungs-SRAM-Speichereinheit. Unter Betrachtung von Schritt (2) aus [Fig. 5](#) ist ersichtlich, dass diese Verschiebung der Daten parallel für jedes Bit die Verwendung von drei Teilschritten umfasst, die gekennzeichnet als (a), (b) und (c). Diese Teilschritte werden sowohl in Flussdiagramm-Kurzschrift als auch in abgekürzter normaler Sprache in [Fig. 5](#) angezeigt. Teilschritt (a) umfasst die Verbindung einer ausgewählten SRAM-Zelle mit einer Bitleitung (BL in [Fig. 4](#)) und einer Bitleitung b (BLb in [Fig. 4](#)). Der Teilschritt (b) ist das tatsächliche Schreiben des Datenbitwerts in diese Bitzeilen, und somit in das SRAM-Register. Teilschritt (c) deaktiviert die Bitleitungen BL und BLb (siehe wiederum Erklärung aus [Fig. 4](#)).

**[0038]** Auf ähnliche Weise verschiebt bei Schritt drei (3) aus [Fig. 5](#) die „B“-Abtastkette ihre entsprechenden Daten parallel in eine andere Zeile der Verbindungs-SRAM-Speichereinheit.

**[0039]** Folglich erklären Schritte vier (4) und fünf (5) aus [Fig. 5](#), dass die Verbindungs-SRAM-Speicher-

einheiten später die entsprechenden Datenbits in die Empfangs-Abtastkette schreiben (d. h. das Datenbit aus der Abtastkette „A“ wird in die Abtastkette „B“ geschrieben, und das Datenbit aus der Abtastkette „B“ wird in die Abtastkette „A“ geschrieben). Es wird darauf hingewiesen, dass bei dem abgekürzten Normalsprachentext aus [Fig. 5](#), Schritt 4, Teilschritt (a) der Ausdruck „HIZ“ „hohe Impedanz“ bedeutet (siehe die Erklärung oben wie Daten in ein Slave-Register 36 einer ausgewählten SRAM-Speicherzelle 44 durch Auswahl-Transistoren 54 und 56 und Auswahl-Transistoren 58 geschrieben werden, während die Inverter in dem Slave-Register in einen Hochimpedanzzustand getaktet werden, mit den Signalen R1\_SA, R2\_SA bis RM\_SA).

**[0040]** Durchschnittsfachleute auf dem zugehörigen Gebiet verstehen, dass abhängig von der Anzahl von Bits in einem digitalen Wort, das von einer Abtastkette zu einer anderen übertragen werden soll, die Anzahl von Verbindungs-SRAM-Speichereinheiten ebenfalls variiert. Zusätzlich dazu können zusätzliche SRAM-Speicherzellen vorgesehen sein, wie oben erklärt wird. Ferner, abhängig von der Tiefe der SRAM-Speichereinheiten in ihrer Verbindung zwischen den Abtastketten, können die Datenbits eine Anzahl von Male entlang der Verbindungs-SRAM-Speicherzellen verschoben werden, bevor sie die Schnittstelle mit der Empfangs-Abtastkette erreichen und dann in die Empfangs-Abtastkette geschrieben werden. Diese „Ausdehnbarkeit“ oder der Pluralismus von sowohl den Abtastketten 26 als auch den Verbindungs-SRAM-Speichereinheiten 44 wurde oben erklärt.

**[0041]** Dementsprechend werden Durchschnittsfachleute auf dem zugehörigen Gebiet verstehen, dass die Erfindung einer Modifikation und Änderung gemäß dem Schutzbereich der Beschreibung und der obigen Offenbarung unterliegt. Obwohl Bezug auf ein bestimmtes bevorzugtes Ausführungsbeispiel der Erfindung genommen wird, impliziert ein solcher Bezug keine Einschränkung der Erfindung und keine solche Einschränkung soll daraus abgeleitet werden. Ferner ist die Erfindung nicht auf die oben beschriebenen und dargestellten spezifischen Ausführungsbeispiele beschränkt. Stattdessen ist die Erfindung gemäß den nachfolgenden Ansprüchen erdacht.

### Patentansprüche

1. Eine Vorrichtung zum Austauschen von Daten zwischen Abtastketten, die folgende Merkmale aufweist:

eine Mehrzahl von Abtastketten (26), wobei jede der selben eine Mehrzahl von Registern umfasst, die in der Lage sind, Datenbits zu speichern, wobei die Mehrzahl von Registern Master-Register (34) und Slave-Register (36) umfasst; und ein Array aus mehreren Statischer-Direktzugriffsspei-

cher-Zellen (SRAM-Zellen) (44), die die Mehrzahl von Abtastketten (26) verbinden, wobei das Array aus mehreren SRAM-Speicherzellen (44) wirksam ist, um Datenbits von Ausgewählten aus den Master-Registern (34) zu empfangen und die Datenbits in Ausgewählte aus den Slave-Registern (36) zu schreiben.

2. Eine Vorrichtung gemäß Anspruch 1, die eine parallele Datenverbindung zwischen der Mehrzahl von Abtastketten (26) und dem Array aus SRAM-Speicherzellen (44) umfasst.

3. Eine Vorrichtung gemäß Anspruch 1 oder 2, bei der jede SRAM-Speicherzelle des Arrays aus SRAM-Speicherzellen (44) ein Paar aus Invertern (46, 48) umfasst, die miteinander kreuzgekoppelt sind.

4. Eine Vorrichtung gemäß Anspruch 3, bei der jede SRAM-Speicherzelle des Arrays aus SRAM-Speicherzellen (44) ein Paar aus Auswahl-Schaltern (54, 56) umfasst, wobei einer des Paars aus Schaltern (54, 56) mit einer Seite des Paars aus kreuzgekoppelten Invertern (46, 48) verbunden ist und der andere des Paars aus Schaltern (54, 56) mit der gegenüberliegenden Seite des Paars aus kreuzgekoppelten Invertern (46, 48) verbunden ist.

5. Eine Vorrichtung gemäß Anspruch 4, die einen Ausgleichsschalter (62) umfasst, der über das Paar aus kreuzgekoppelten Invertern (46, 48) und über das Paar aus Auswahl-Schaltern (54, 56) einer SRAM-Speicherzelle verbindet.

6. Eine Vorrichtung gemäß Anspruch 5, bei der der Ausgleichsschalter (62) einen Transistor umfasst.

7. Eine Vorrichtung gemäß einem der Ansprüche 3 bis 6, die ein Paar aus Schreibschaltern (60) umfasst, die eine gemeinsame Schalter-Verschluß-Steuerverbindung umfassen, und bei der jeder des Paars aus Schreibschaltern (60) eine entsprechende eine Seite des Paars aus kreuzgekoppelten Invertern (46, 48) mit einer entsprechenden Seite eines Registers von einer des Paars der Abtastketten (26) verbindet.

8. Eine Vorrichtung gemäß Anspruch 7, bei der das Paar aus Schreibschaltern (60) eine Verbindung mit einem Master-Register (34) der einen Abtastkette (26) herstellt.

9. Eine Vorrichtung gemäß einem der Ansprüche 3 bis 8, die ein Paar aus Leseschaltern (58) umfasst, die eine gemeinsame Schalter-Verschluß-Steuerverbindung aufweisen, und bei der jeder der Leseschalter (58) eine entsprechende eine Seite des Paars aus kreuzgekoppelten Invertern (46, 48) mit einer ent-

sprechenden Seite eines Registers von einer des Paars aus Abtastketten (**26**) verbindet.

10. Eine Vorrichtung gemäß Anspruch 9, bei der das Paar aus Leseschaltern (**58**) mit einem Slave-Register der einen Abtastkette (**26**) verbunden ist.

Es folgen 4 Blatt Zeichnungen

FIGUR 1

FIGUR 3

FIGUR 4

FIGUR 5