US008473822B2

# (12) United States Patent

Shen et al.

(10) Patent No.: US 8,4 (45) Date of Patent: \*J

US 8,473,822 B2

atent: \*Jun. 25, 2013

## (54) TRUE BIT LEVEL DECODING OF TTCM (TURBO TRELLIS CODED MODULATION) OF VARIABLE RATES AND SIGNAL CONSTELLATIONS

(75) Inventors: **Ba-Zhong Shen**, Irvine, CA (US); **Kelly Brian Cameron**, Irvine, CA (US); **Hau**

Thien Tran, Irvine, CA (US)

(73) Assignee: **Broadcom Corporation**, Irvine, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 877 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 12/627,438

(22) Filed: **Nov. 30, 2009**

(65) Prior Publication Data

US 2010/0077282 A1 Mar. 25, 2010

#### Related U.S. Application Data

- (63) Continuation of application No. 10/429,362, filed on May 1, 2003, now Pat. No. 7,657,822.

- (60) Provisional application No. 60/384,698, filed on May 31, 2002, provisional application No. 60/427,979, filed on Nov. 20, 2002, provisional application No. 60/459,132, filed on Mar. 31, 2003.

- (51) **Int. Cl. H03M 13/45** (2006.01)

#### (56) References Cited

### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

EP 0735696 A2 \* 10/1996 EP 0735696 A3 \* 1/1999 FR 9105278 A1 \* 10/1992

#### OTHER PUBLICATIONS

Pyndiah et al., "Performance of Block Turbo Coded 16-QAM and 64-QAM Modulations", IEEE GLOBECOM '95, Nov. 1995, pp. 1039-1043.\*

#### (Continued)

Primary Examiner — Stephen M Baker (74) Attorney, Agent, or Firm — Garlick & Markison; Shayne X. Short

#### (57) ABSTRACT

True bit level decoding of TTCM (Turbo Trellis Coded Modulation) of variable rates and signal constellations. A decoding approach is presented that allows for decoding on a bit level basis that allows for discrimination of the individual bits of a symbol. Whereas prior art approaches typically perform decoding on a symbol level basis, this decoding approach allows for an improved approach in which the hard decisions/best estimates may be made individually for each of the individual bits of an information symbol. In addition, the decoding approach allows for a reduction in the total number of calculations that need to be performed as well as the total number of values that need to be stored during the iterative decoding. The bit level decoding approach is also able to decode a signal whose code rate and/or signal constellation type (and mapping) may vary on a symbol by symbol basis.

## 20 Claims, 31 Drawing Sheets

TTCM (Turbo Trellis Coded Modulation) decoder system

### U.S. PATENT DOCUMENTS

| 5,446,747    | Α  | »įk  | 8/1995  | Berrou            | 714/788 |

|--------------|----|------|---------|-------------------|---------|

| 5,563,897    | Α  | ¥.   | 10/1996 | Pyndiah et al     | 714/755 |

| 5,577,068    | Α  | *    | 11/1996 | Bottomley et al   | 375/232 |

| 5,790,595    | Α  | ajk  | 8/1998  | Benthin et al     | 375/224 |

| 5,867,538    | Α  | *    | 2/1999  | Liu               | 375/341 |

| 6,065,147    | Α  | *    | 5/2000  | Pyndiah et al     | 714/755 |

| 6,119,264    | Α  | rķ.  | 9/2000  | Berrou et al      | 714/786 |

| 6,122,763    | Α  | *    | 9/2000  | Pyndiah et al     | 714/755 |

| 6,131,180    | Α  | *    | 10/2000 | Ramesh            | 714/790 |

| 6,138,260    | Α  | »įk  | 10/2000 | Ketseoglou        | 714/751 |

| 6,324,224    | В1 | *    | 11/2001 | Ikeda             | 375/341 |

| 6,381,727    | В1 | *    | 4/2002  | Ikeda             | 714/780 |

| 6,396,871    | В1 | nje  | 5/2002  | Gelblum et al     | 375/222 |

| 6,480,552    | В1 | *    | 11/2002 | Tonello           | 375/265 |

| 6,484,283    | B2 | ×.   | 11/2002 | Stephen et al     | 714/786 |

| 6,516,437    | В1 | alk: | 2/2003  | Van Stralen et al | 714/755 |

| 6,529,559    | B2 | *    | 3/2003  | Reshef            | 375/262 |

| 6,567,481    | В1 | ajk  | 5/2003  | Molnar            | 375/341 |

| 6,594,318    | В1 | sk.  | 7/2003  | Sindhushayana     | 375/262 |

| 6,625,236    | В1 | *    | 9/2003  | Dent et al        | 375/341 |

| 6,658,071    | В1 | ajk  | 12/2003 | Cheng             |         |

| 6,697,441    | В1 | sķ.  | 2/2004  | Bottomley et al   |         |

| 6,731,696    | В1 |      | 5/2004  | Gelblum et al     |         |

| 6,760,390    | В1 |      | 7/2004  | Desai et al       |         |

| 6,785,861    | B2 |      | 8/2004  | Scalise et al     | 714/786 |

| 6,798,852    | B2 | *    | 9/2004  | Khayrallah et al  | 375/341 |

| 6,807,238    | В1 |      | 10/2004 | Rhee et al        | 375/340 |

| 6,885,711    | B2 |      | 4/2005  | Shiu et al        |         |

| 6,903,665    | B2 |      | 6/2005  | Akhter et al      |         |

| 6,904,097    | B2 |      | 6/2005  | Agami et al       | 375/261 |

| 6,907,084    | B2 |      | 6/2005  | Jeong             |         |

| 6,922,438    | В1 |      | 7/2005  | Eidson            |         |

| 6,934,317    | В1 |      | 8/2005  | Dent              |         |

| 6,961,388    | B2 |      | 11/2005 | Ling et al        |         |

| 6,973,615    | В1 |      | 12/2005 | Arad et al        | 714/792 |

| 7,032,164    | B2 |      | 4/2006  | Cameron et al     | 714/792 |

| 7,657,822    | B2 |      | 2/2010  | Shen et al        |         |

| 2002/0131515 | A1 |      | 9/2002  | Rodriguez         |         |

| 2002/0136318 | Αl | ak.  | 9/2002  | Gorokhov et al    | 375/261 |

|              |    |      |         |                   |         |

## OTHER PUBLICATIONS

Fegervik et al., "Low=Complexity Bit by Bit Soft Output Demodu-

lator", Electronics Letters, May 23, 1996, pp. 985-987.\*

Lauer et al., "Turbo Coding for Discrete Multitone Transmission Systems", IEEE Globecom '98, Nov. 1998, pp. 3256-3260.\*

Li et al., "Trellis-Coded Modulation with Bit Interleaving and Iterative Decoding", IEEE Journal on Selected Areas in Communications, vol. 17, No. 4, Apr. 1999, pp. 715-724.\*

Le Goff et al., "Turbo-Codes and High Spectral Efficiency Modulation", IEEE SUPERCOMM/ICC '94, May 1994, pp. 645-649.\* Zhang et al., "Turbo Coding for Transmission over ADSL", WCC-ICCT 2000, Aug. 2000, pp. 124-131.\*

Ormeci et al., "Adaptive Bit-Interleaved Coded Modulation", IEEE Transactions on Communications, vol. 49, No. 9, Sep. 2001, pp. 1572-1581.\*

Onggosanusi et al., Turbo Trellis-Coded Modulation with Time-Varying Mixed Mapping, IEEE VTC 2001, Oct. 2001, pp. 2409-2413.\*

Olivieri et al., "Dynamic Bit-Interleaved Turbo-Coded Modulation for Unequal Error Protection", Globecom '01, Nov. 2001, pp. 3267-3271 \*

Li et al., "A New Turbo Coded QAM Scheme with Very Low Decoding Complexity for ADSL Systems", Globecom '01, Nov. 2001, pp. 349-353.\*

Ritcey et al., "Design, Analysis and Performance Evaluation for BICM-ID with Square QAM Constellations in Rayleigh Fading Channels", IEEE Journal on Selected Areas in Communications, vol. 19, No. 5, May 2001, pp. 944-957.\*

Ritcey et al., "Trellis-Coded Modulation with Bit Interleaving and Iterative Decoding", IEEE Journal on Selected Areas in Communications, vol. 17, No. 4, Apr. 1999, pp. 715-724.\*

Divsalar et al., "Turbo Codes: Performance Analysis, Design and Iterative Decoding" GLOBECOM '97, Nov. 1997, pp. 45-53.\*

Liu et al., "A Transformation for Computational Latency Reduction in Turbo-MAP Decoding", ISCAS '99, Jul. 1999, pp. 402-405.\* Hoeher et al., "A Comparison of Optimal and Sub-Optimal MAP Decoding Algorithms Operating in the Log Domain", ICC '95, Jun.

1995, pp. 1009-1013.\* Hu et al., "Near-Optimal Reduced-Complexity Decoding Algorithms for LDPC Codes", ISIT 2002, Jul. 2002, p. 455.\*

<sup>\*</sup> cited by examiner

uni-directional microwave communication system

bi-directional microwave communication system

Fig. 4B

uni-directional point-to-point radio communication system

正 の な る

bi-directional point-to-point radio communication system

TTCM (Turbo Trellis Coded Modulation) communication system

о О Ш

| Feedforward<br>Polynomial<br>(octal) | Feedback<br>Polynomial<br>(octal) | $\mathrm{d}_2$ | $N_2$       | Other weights with 2 bit input (#sequence) |

|--------------------------------------|-----------------------------------|----------------|-------------|--------------------------------------------|

| 5                                    | 16                                | 4              | 3           |                                            |

| 11                                   | 13                                | 7              | <del></del> |                                            |

| 17                                   | 15                                | 7              | yaa aa      |                                            |

| 2                                    | 15                                | 3              | 1           | 5(1)                                       |

| 2                                    | 13                                | 3              | <b></b>     | 5(1)                                       |

| 7                                    | 12                                | 3              | I           | 4(10),5(1)                                 |

| 13                                   | 16                                | 3              | homomed     | 4(2),5(1)                                  |

| 13                                   | 11                                | 3              | 2           | 4(2),5(5)                                  |

| 15                                   | 12                                | 3              | hammed      | 4(11)                                      |

| 15                                   | 17                                | 3              | 3           | 4(8),5(2)                                  |

| 2                                    | 11                                | 2              | processor(  | 3(4),4(5),5(3)                             |

list of possible encoders that satisfy Ungerboeck's rule and minimum distance  $d_2>=3$  **Fig. 11**

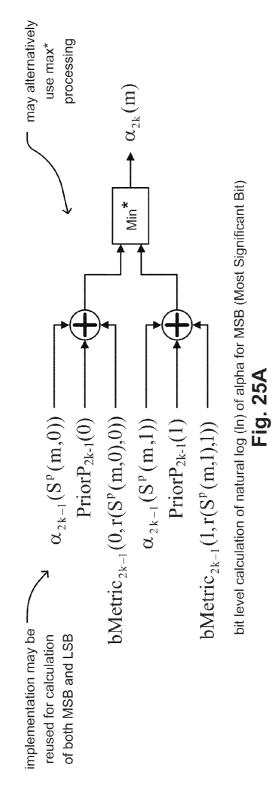

direct computation of bit metrics (no calculation of symbols metrics) **Fig. 18**

$$I/(2\sigma^{2})$$

$$I/($$

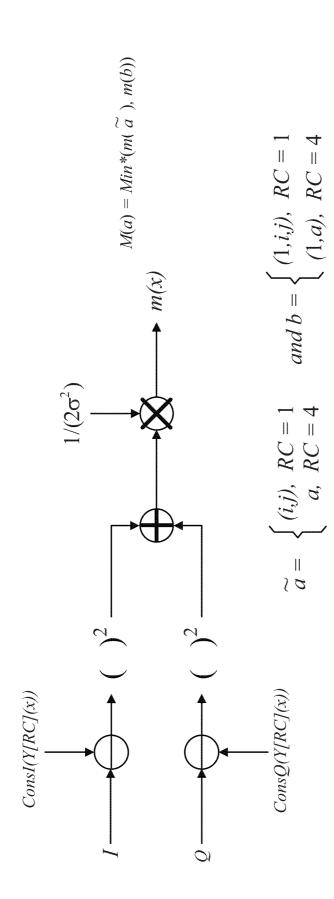

M(a) calculation for RCs: 0,2,6,8 and RCs: 5,7 **Fig. 20**

M(a) calculation for RCs: 1,4 using m(x) calculation **Fig. 22**

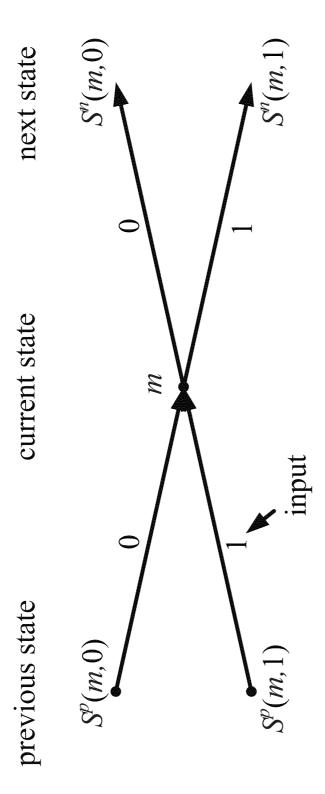

state transitions for rate 1/2 trellis encoder **Fig. 24**

bit level calculation of natural log (In) of alpha for LSB (Least Significant Bit)

Fig. 25B

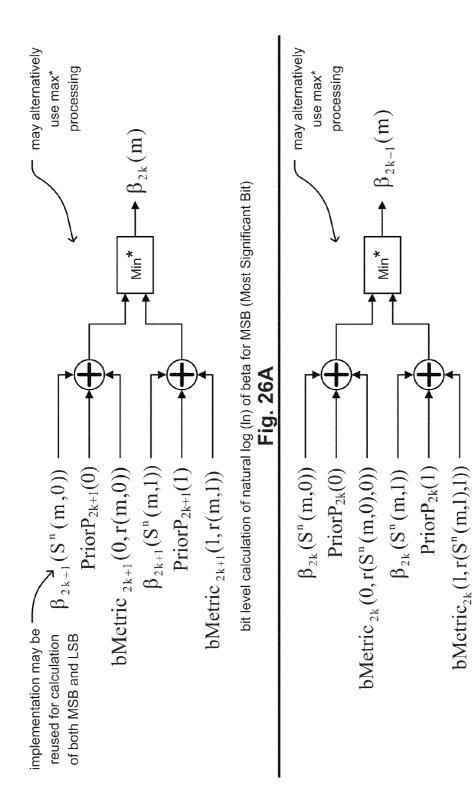

bit level calculation of natural log (In) of beta for LSB (Least Significant Bit)

Fig. 26B

1

## TRUE BIT LEVEL DECODING OF TTCM (TURBO TRELLIS CODED MODULATION) OF VARIABLE RATES AND SIGNAL CONSTELLATIONS

## CROSS REFERENCE TO RELATED PATENTS/PATENT APPLICATIONS

Continuation Priority Claim, 35 U.S.C. §120

The present U.S. Utility patent application claims priority pursuant to 35 U.S.C. §120, as a continuation, to the following U.S. Utility patent application which is hereby incorporated herein by reference in its entirety and made part of the present U.S. Utility patent application for all purposes:

- 1. U.S. Utility application Ser. No. 10/429,362, entitled "True bit level decoding of TTCM (Turbo Trellis Coded Modulation) of variable rates and signal constellations," now issued as U.S. Pat. No. 7,657,822 B2, issued on Feb. 2, 2010, 20 which claims priority pursuant to 35 U.S.C. §119(e) to the following U.S. Provisional Patent Applications which are hereby incorporated herein by reference in their entirety and made part of the present U.S. Utility patent application for all purposes:

- U.S. Provisional Application Ser. No. 60/384,698, entitled "Variable code rate and signal constellation turbo trellis coded modulation codec," May 31, 2002.

- b. U.S. Provisional Application Ser. No. 60/427,979, "Single stage implementation of min\*, max\*, min and/ or max to perform state metric calculation in SISO decoder," Nov. 20, 2002.

- c. U.S. Provisional Patent Application Ser. No. 60/459,132, entitled "True bit level decoding of TTCM (Turbo Trellis Coded Modulation) of variable rates and signal constellations," Mar. 31, 2003.

### Incorporation by Reference

The following U.S. Utility patent applications are hereby incorporated herein by reference in their entirety and made part of the present U.S. Utility patent application for all purposes:

- 1. U.S. Utility application Ser. No. 10/264,486, entitled 45 "Variable code rate and signal constellation turbo trellis coded modulation codec," filed Oct. 4, 2002, now U.S. Pat. No. 7,093,187 B2, issued on Aug. 15, 2006, which claims priority pursuant to 35 U.S.C. §119(e) to the following U.S. Provisional Patent Application which is hereby incorporated 50 herein by reference in its entirety and made part of the present U.S. Utility patent application for all purposes:

- a. U.S. Provisional Patent Application Ser. No. 60/384,698, entitled "Variable code rate and signal constellation turbo trellis coded modulation codec," filed May 31, 55 2002, now expired.

- 2. U.S. Utility application Ser. No. 10/335,702, "Single stage implementation of min\*, max\*, min and/or max to perform state metric calculation in SISO decoder," filed Jan. 2, 2003, now U.S. Pat. No. 7,137,059 B2, issued on Nov. 14, 60 2006, which claims priority pursuant to 35 U.S.C. §119(e) to the following U.S. Provisional Patent Application which is hereby incorporated herein by reference in its entirety and made part of the present U.S. Utility patent application for all purposes:

- a. U.S. Provisional Application Ser. No. 60/427,979, "Single stage implementation of min\*, max\*, min and/

2

or max to perform state metric calculation in SISO decoder," filed Nov. 20, 2002, now expired.

#### BACKGROUND OF THE INVENTION

#### 1. Technical Field of the Invention

The invention relates generally to communication systems; and, more particularly, it relates to decoding of signals 10 received within such communication systems.

### 2. Description of Related Art

Data communication systems have been under continual development for many years. One particular type of communication system has received particular attention is a communication system that operates using turbo code.

When performing decoding within such turbo code systems, it is necessary to perform updating of two real sequences during every iteration of the iterative decoding. These two sequences may be viewed as being be viewed as being forward metrics (alphas) and backward metrics (betas) within the context of TCM (Trellis Coded Modulation) decoding as well as TTCM (Turbo Trellis Coded Modulation) decoding. These alphas and betas may be represented as follows:  $(\alpha_0(m), \alpha_1(m), \ldots, \alpha_{n-1}(m))$  and  $(\beta_0(m), \beta(m), \ldots, \beta_n(m))$  $\beta_{n-1}(m)$ ). The updating performed within this iterative decoding is performed using the a posteriori probability and the branch metrics. When performing TTCM decoding, a symbol metric will typically involve more than one information bit (e.g., a plurality of information bits). Therefore, the calculation of the forward metric  $\alpha(m)$  and the backward metric  $\beta(m)$ involves more than one computing cycle to calculate all of the possible values of these various information bits of the symbol; this may be characterized as a symbol level decoding approach. However, using the prior art approaches of purely symbol level decoding, such decoding approaches are typically implemented in a manner that costs a lot of transistors (which may be viewed as occupying a great deal of real estate within an integrated circuit that performs the decoding). In addition, a relatively large amount of memory must also typically be dedicated to store all of the calculated values before making final best estimates of the information contained within a received signal. It is also noted that the prior art approaches to performing this purely symbol level decoding is typically performing using the same symbol metric in every iteration of the iterative decoding.

As such, given the relatively large amount of calculations required to perform the prior art symbol level decoding, as well as the relatively large amount of information that must be stored using such symbol level decoding, it would be advantageous to have a decoding approach that could provide for comparable (if not better) performance than symbol level decoding, while also allowing fewer computational steps and a lesser amount of information to be stored before making final best estimates of the information contained within a received signal.

## BRIEF SUMMARY OF THE INVENTION

The present invention is directed to apparatus and methods of operation that are further described in the following Brief Description of the Several Views of the Drawings, the Detailed Description of the Invention, and the claims. Other features and advantages of the present invention will become apparent from the following detailed description of the invention made with reference to the accompanying drawings.

3

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

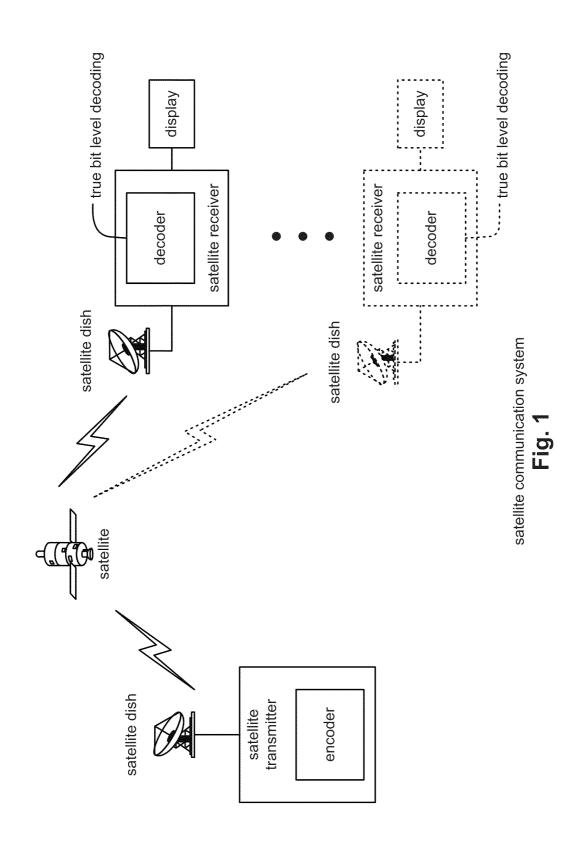

- FIG. 1 is a system diagram illustrating an embodiment of a satellite communication system that is built according to the invention

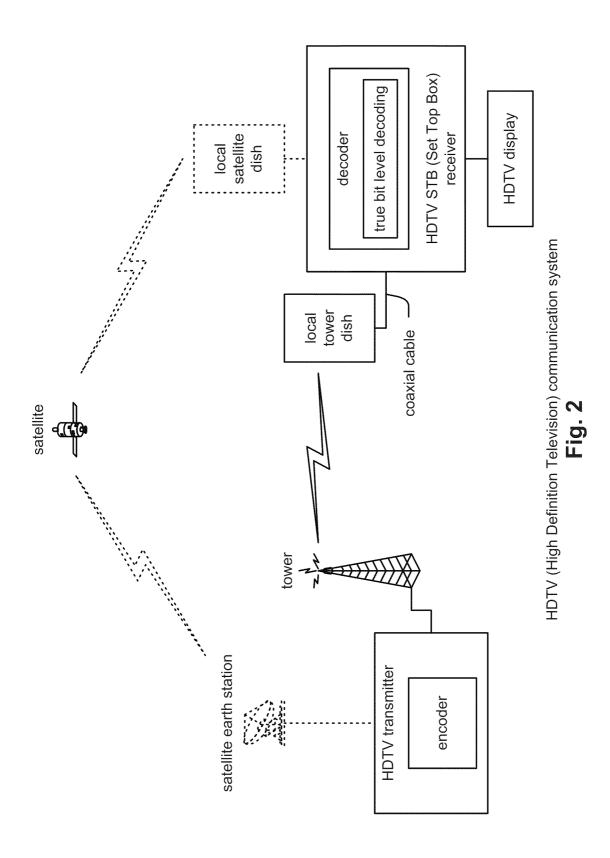

- FIG. 2 is a system diagram illustrating an embodiment of a HDTV (High Definition Television) communication system that is built according to the invention.

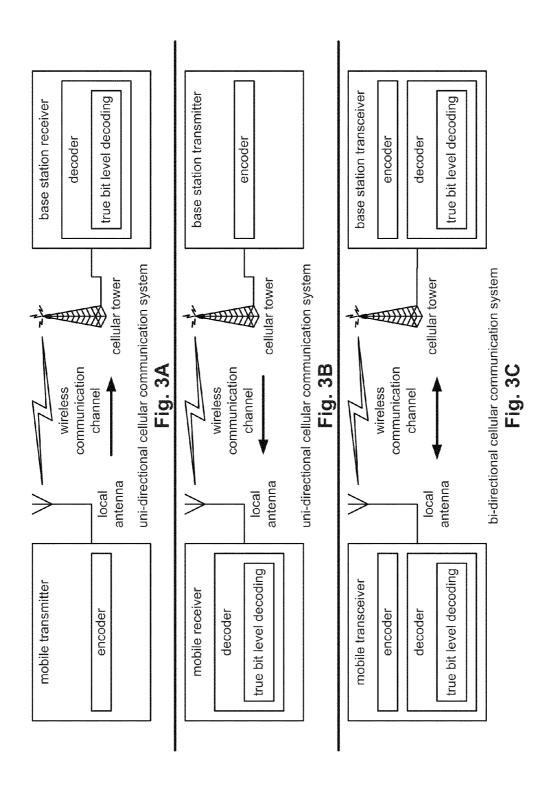

- FIG. **3**A and FIG. **3**B are system diagrams illustrating embodiments of uni-directional cellular communication systems that are built according to the invention.

- FIG. 3C is a system diagram illustrating an embodiment of a bi-directional cellular communication system that is built according to the invention.  $^{15}$

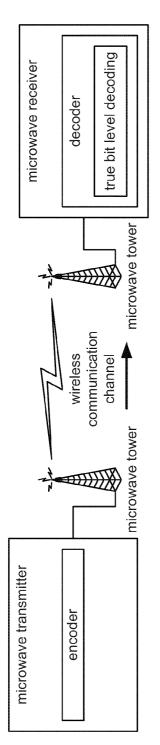

- FIG. 4A is a system diagram illustrating an embodiment of a uni-directional microwave communication system that is built according to the invention.

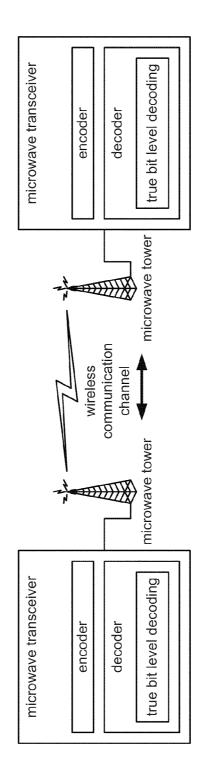

- FIG. 4B is a system diagram illustrating an embodiment of  $_{20}$  a bi-directional microwave communication system that is built according to the invention.

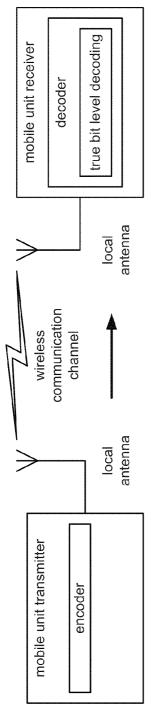

- FIG. 5A is a system diagram illustrating an embodiment of a uni-directional point-to-point radio communication system that is built according to the invention.

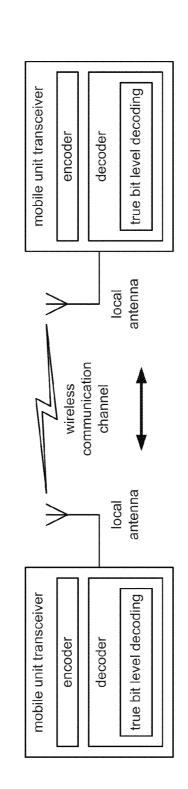

- FIG. 5B is a system diagram illustrating an embodiment of a bi-directional point-to-point radio communication system that is built according to the invention.

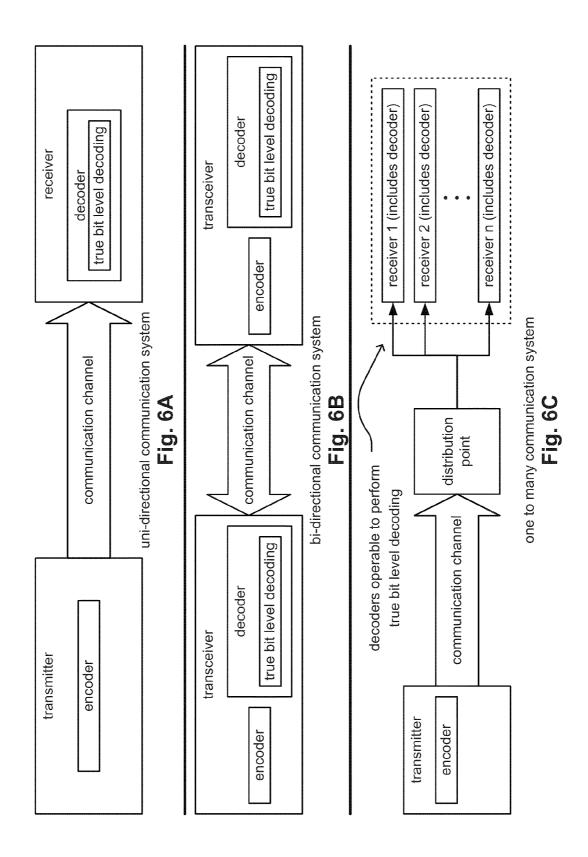

- FIG. **6A** is a system diagram illustrating an embodiment of a uni-directional communication system that is built according to the invention.

- FIG. 6B is a system diagram illustrating an embodiment of a bi-directional communication system that is built according to the invention.

- FIG. 6C is a system diagram illustrating an embodiment of 35 a one to many communication system that is built according to the invention.

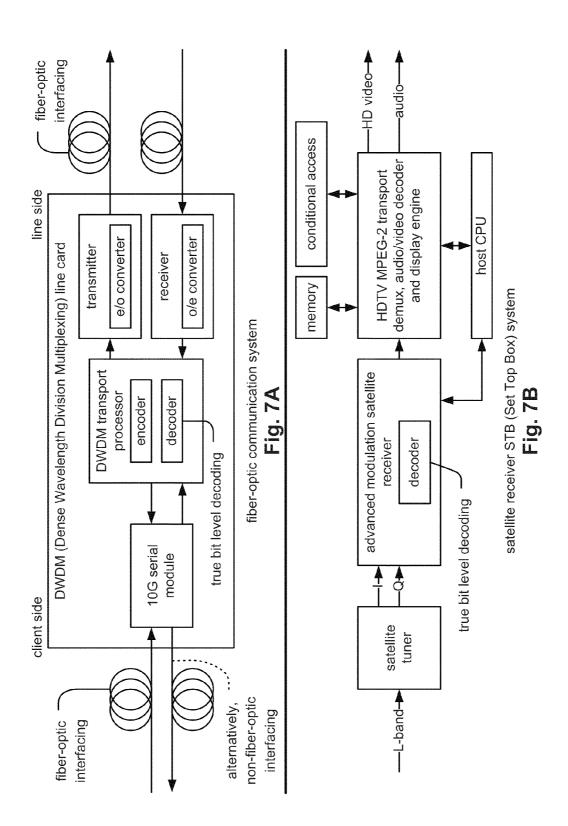

- FIG. 7A is a system diagram illustrating an embodiment of a fiber-optic communication system that is built according to the invention.

- FIG. 7B is a system diagram illustrating an embodiment of a satellite receiver STB (Set Top Box) system that is built according to the invention.

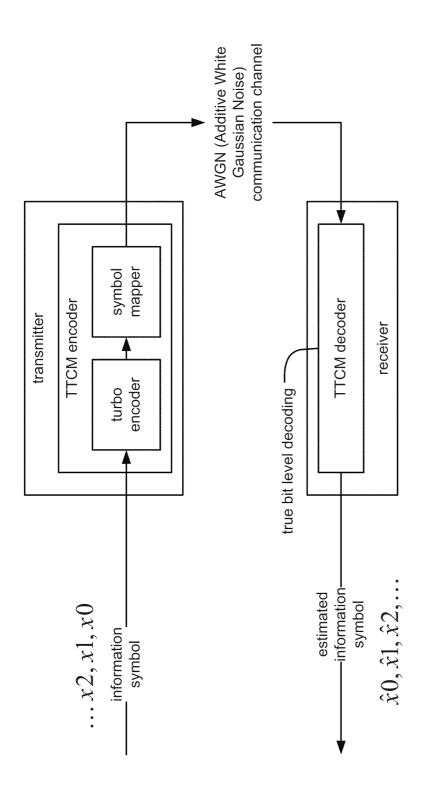

- FIG. 8 is a system diagram illustrating an embodiment of a TTCM (Turbo Trellis Coded Modulation) communication 45 system that is built according to the invention.

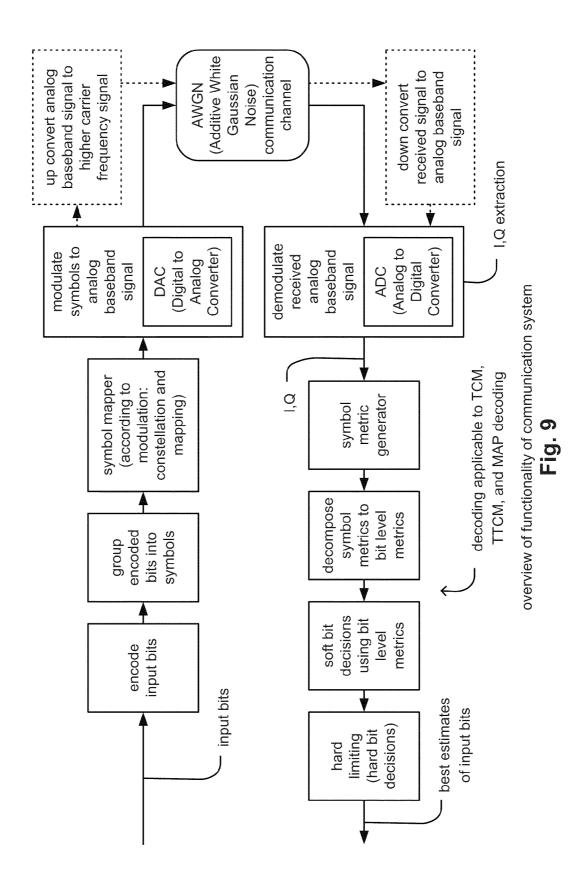

- FIG. 9 is a diagram illustrating an embodiment of an overview of functionality of a communication system that is built according to the invention.

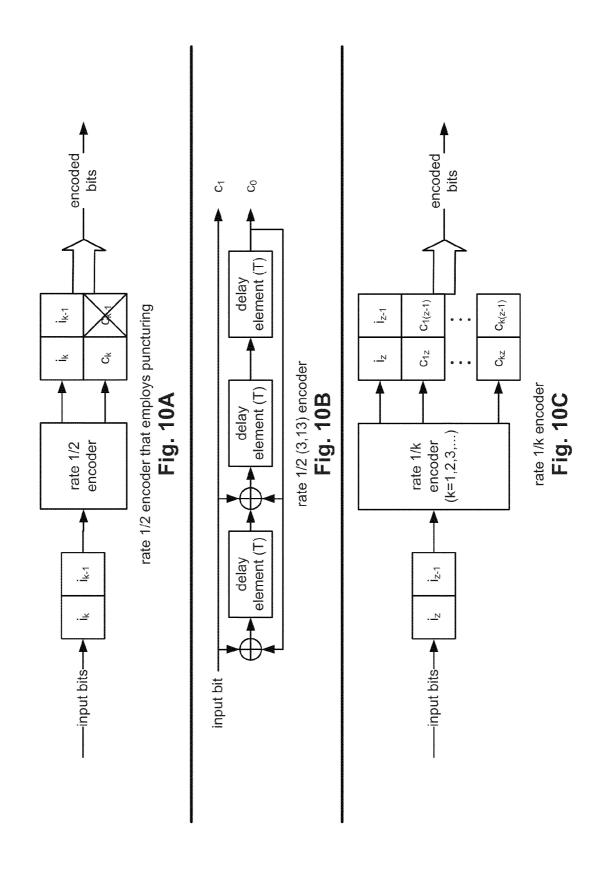

- FIG. 10A is a diagram illustrating an embodiment of a rate 50 1/2 encoder that employs puncturing according to the invention

- FIG. 10B is a diagram illustrating an embodiment of a rate 1/2 encoder (3,13) that is built according to the invention.

- FIG. **10**C is a diagram illustrating an embodiment of a rate 55 1/k encoder that is built according to the invention.

- FIG. 11 is a diagram illustrating a list of possible encoders that satisfy Ungerboeck's rule and a minimum distance of  $d_2 >= 3$  according to the invention.

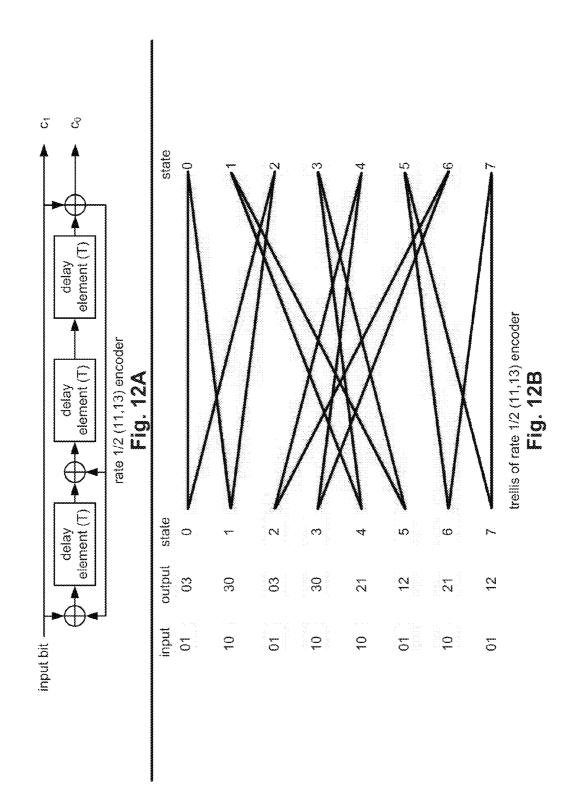

- FIG. 12A is a diagram illustrating an embodiment of a rate  $\,^{60}$   $\,^{1/2}$  encoder (11,13) that is built according to the invention.

- FIG. 12B is a diagram illustrating an embodiment of a trellis of the rate 1/2 encoder (11,13), shown in the FIG. 12A, according to the invention.

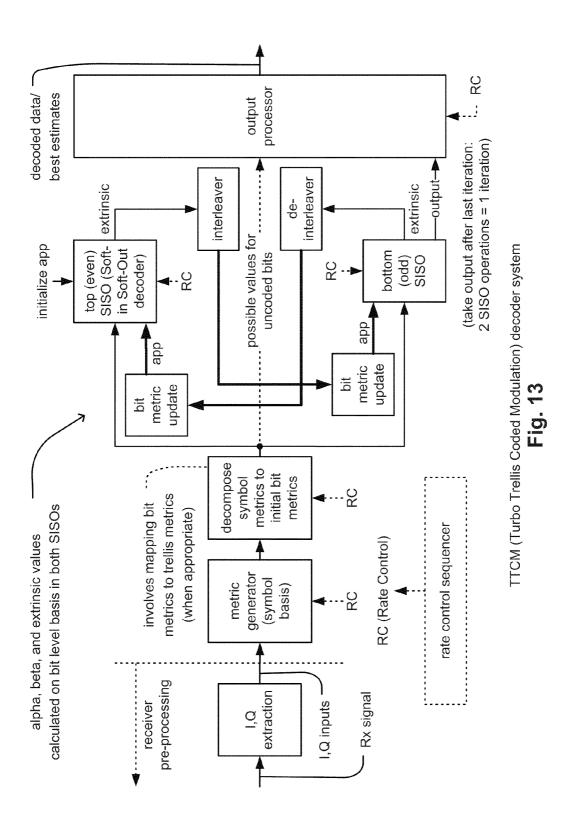

- FIG. 13 is a system diagram illustrating an embodiment of 65 a TTCM (Turbo Trellis Coded Modulation) decoder system that is built according to the invention.

4

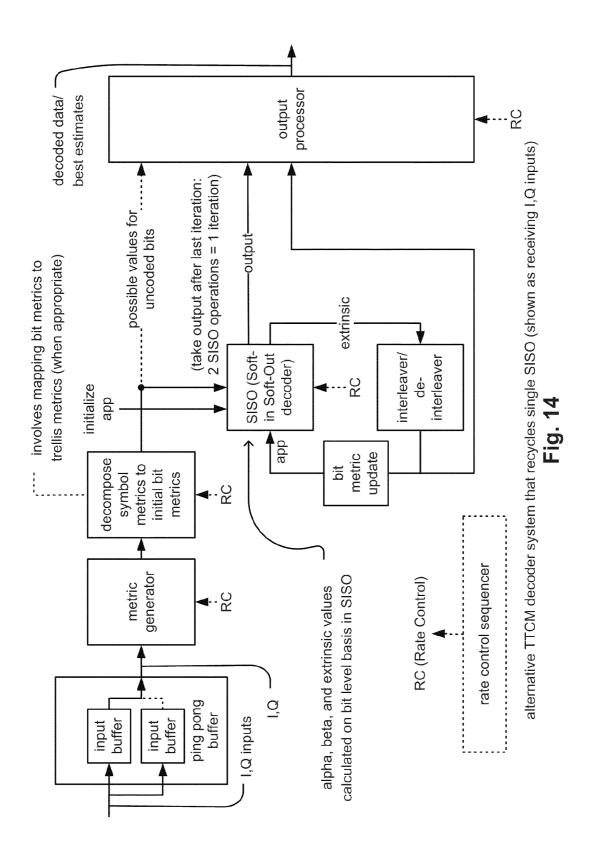

- FIG. 14 is a system diagram illustrating an embodiment of an alternative TTCM decoder system that recycles a single SISO according to the invention (shown as receiving I,Q inputs).

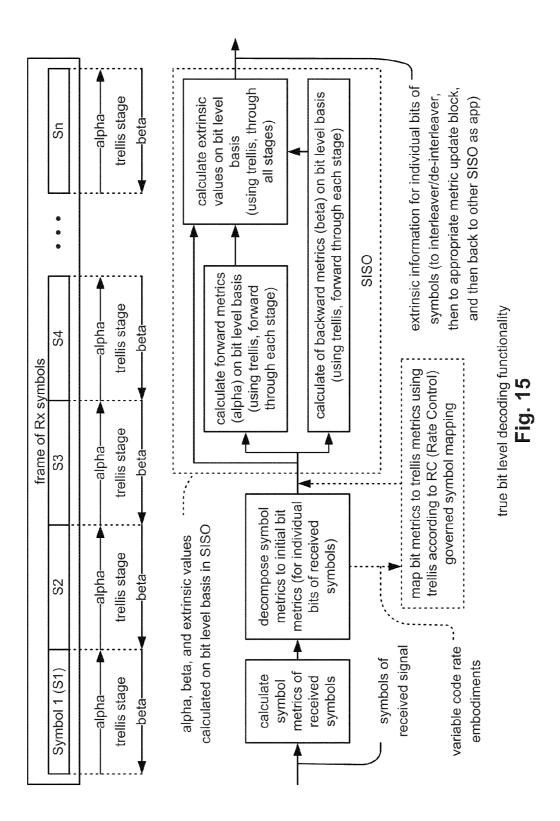

- FIG. 15 is a diagram illustrating an embodiment of true bit level decoding functionality according to the invention.

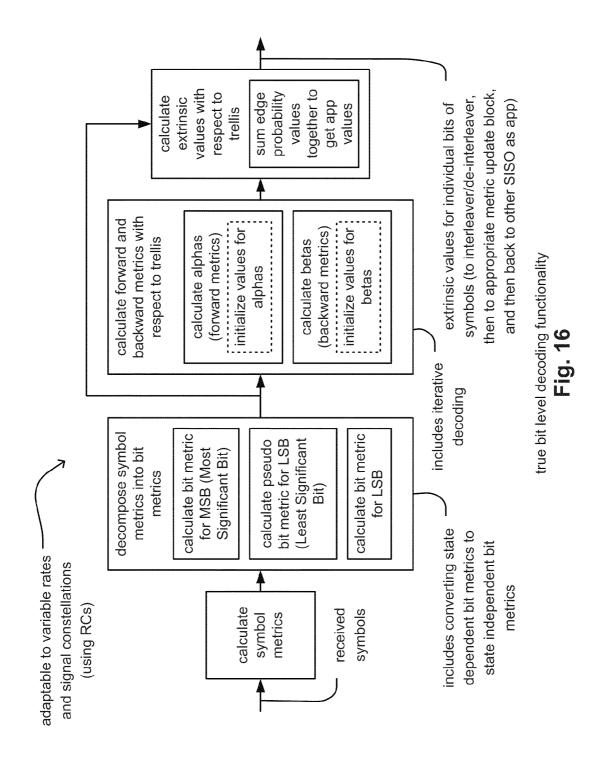

- FIG. 16 is a diagram illustrating another embodiment of true bit level decoding functionality according to the invention

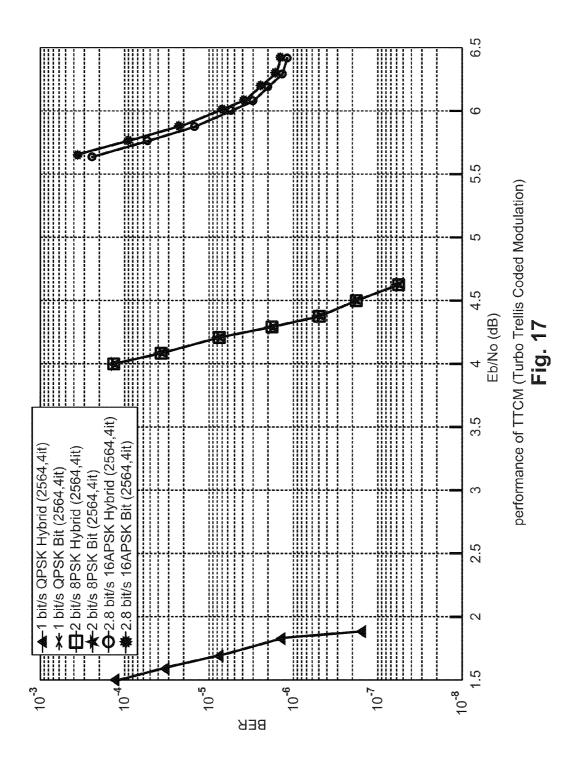

- FIG. 17 is a diagram illustrating an embodiment of performance of TTCM (Turbo Trellis Coded Modulation) according to the invention.

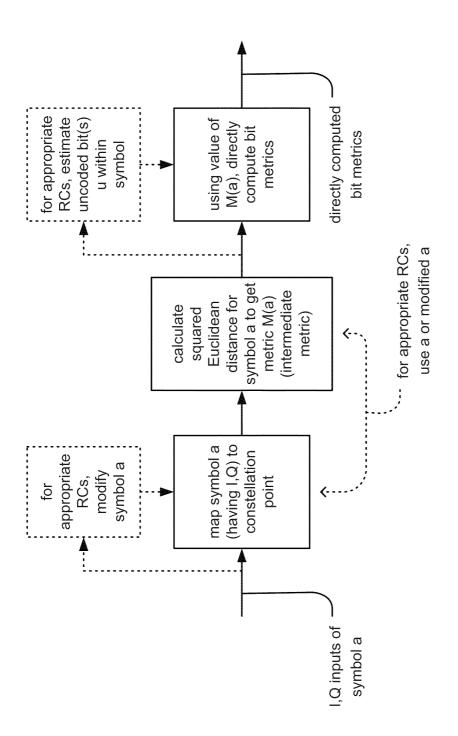

- FIG. 18 is a diagram illustrating an embodiment of direct computation of bit metrics (that involve no calculation of symbol metrics) according to the invention.

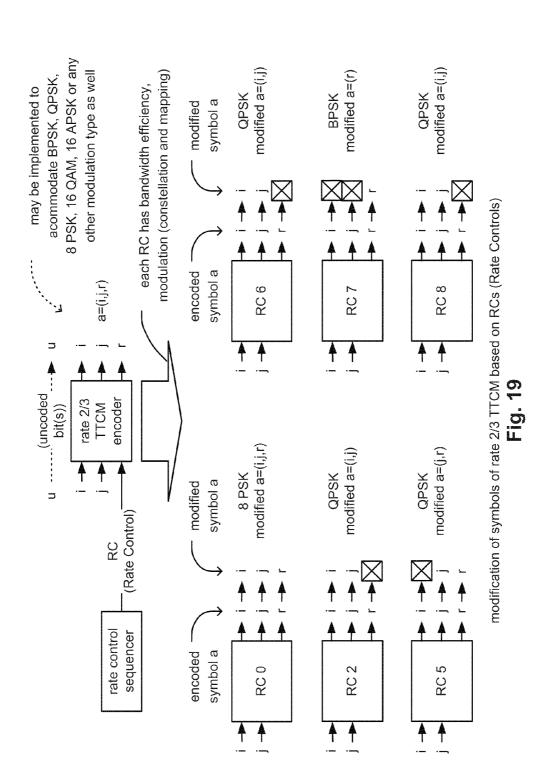

- FIG. 19 is a diagram illustrating an embodiment of modification of symbols of a rate 2/3 TTCM based on RCs (Rate Controls) according to the invention.

- FIG. **20** is a diagram illustrating an embodiment of intermediate metric M(a) calculation for RCs: 0, 2, 6, 8 and RCs: 5, 7 with a=ã according to the invention. This embodiment shows how the calculation of the

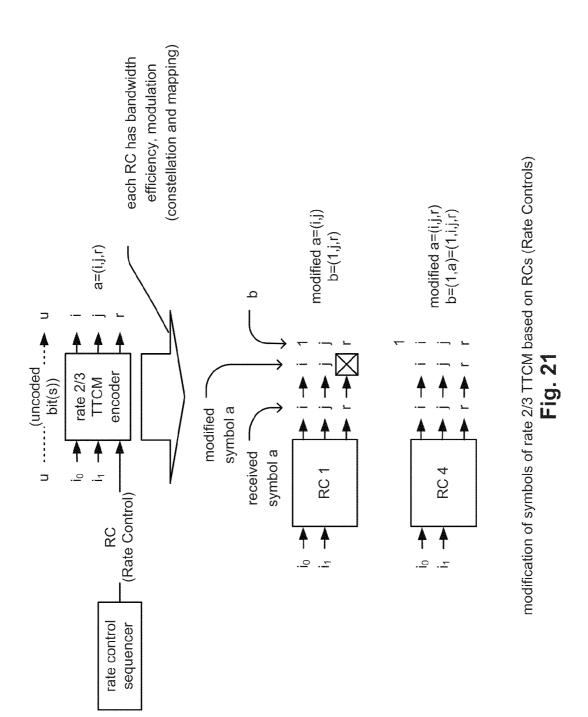

- FIG. 21 is a diagram illustrating another embodiment of modification of symbols of a rate 2/3 TTCM based on RCs (Rate Controls) according to the invention.

- FIG. 22 is a diagram illustrating an embodiment of intermediate metric M(a) calculation for RCs: 1, 4 using m(x) calculation according to the invention.

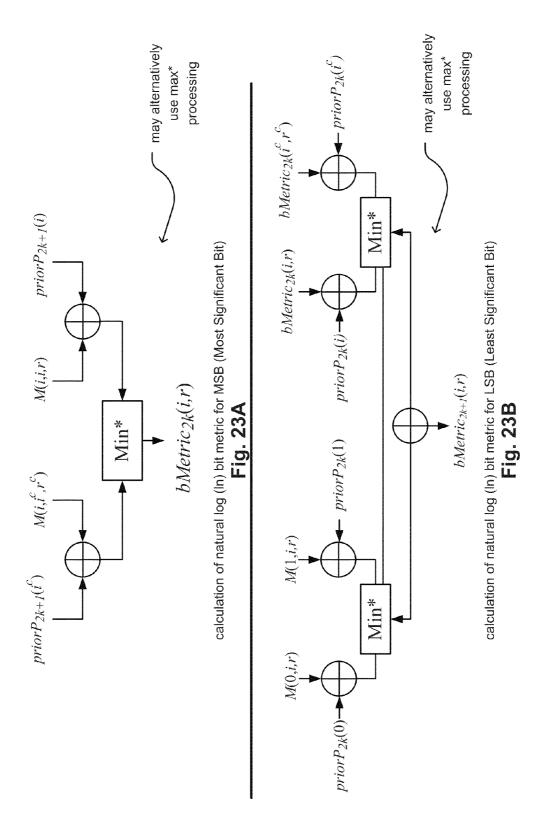

- FIG. **23**A is a diagram illustrating an embodiment of calculation of the natural log(ln) bit metric for an MSB (Most Significant Bit) according to the invention.

- FIG. 23B is a diagram illustrating an embodiment of calculation of the natural log(ln) bit metric for an LSB (Least Significant Bit) according to the invention.

- FIG. 24 is a diagram illustrating an embodiment of state transitions for a rate 1/2 trellis encoder according to the invention

- FIG. **25**A is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of forward metric (alpha) for an MSB (Most Significant Bit) according to the invention.

- FIG. **25**B is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of forward metric (alpha) for an LSB (Least Significant Bit) according to the invention.

- FIG. **26**A is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of backward metric (beta) for an MSB (Most Significant Bit) according to the invention.

- FIG. **26**B is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of backward metric (beta) for an LSB (Least Significant Bit) according to the invention.

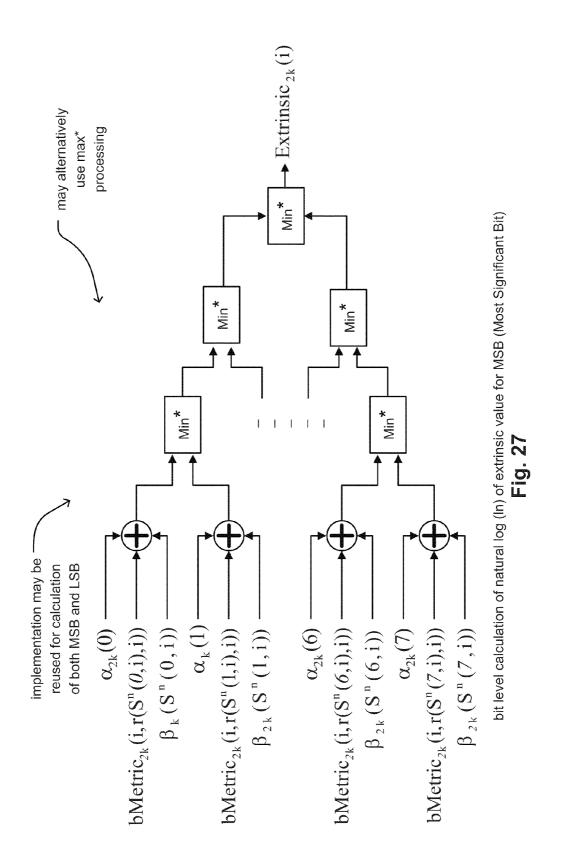

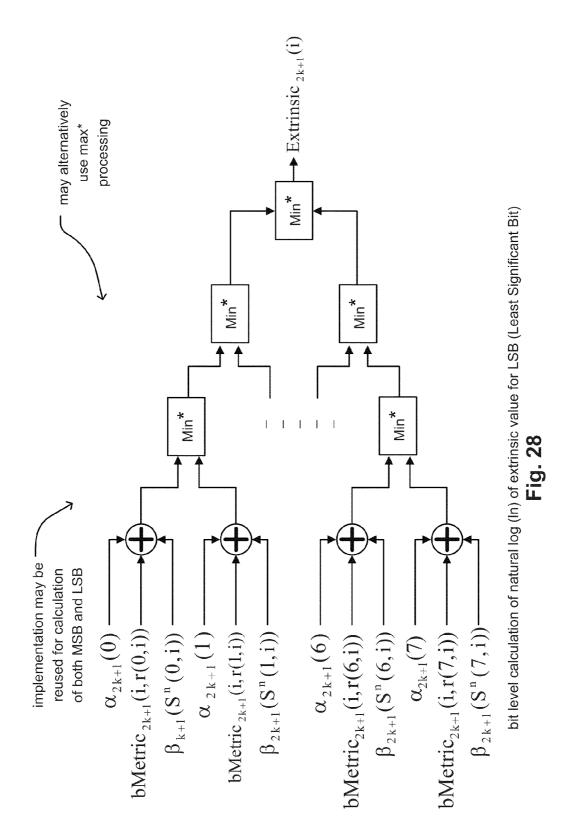

- FIG. 27 is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of extrinsic value for an MSB (Most Significant Bit) according to the invention.

- FIG. **28** is a diagram illustrating an embodiment of bit level calculation of the natural log(ln) of extrinsic value for an LSB (Least Significant Bit) according to the invention.

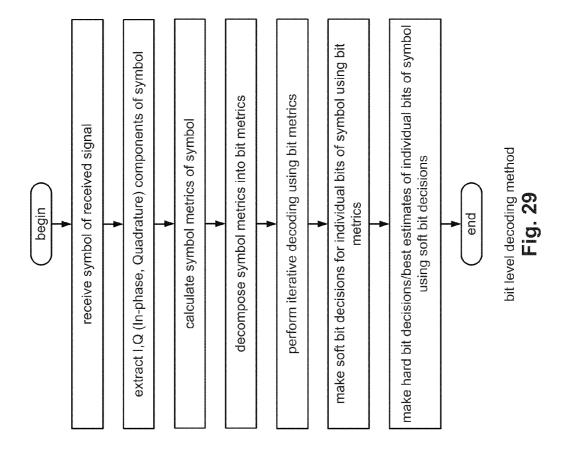

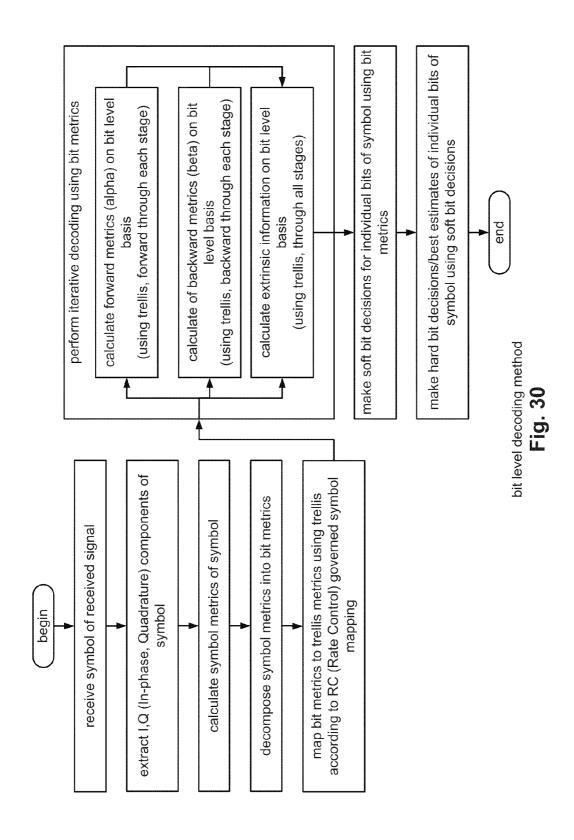

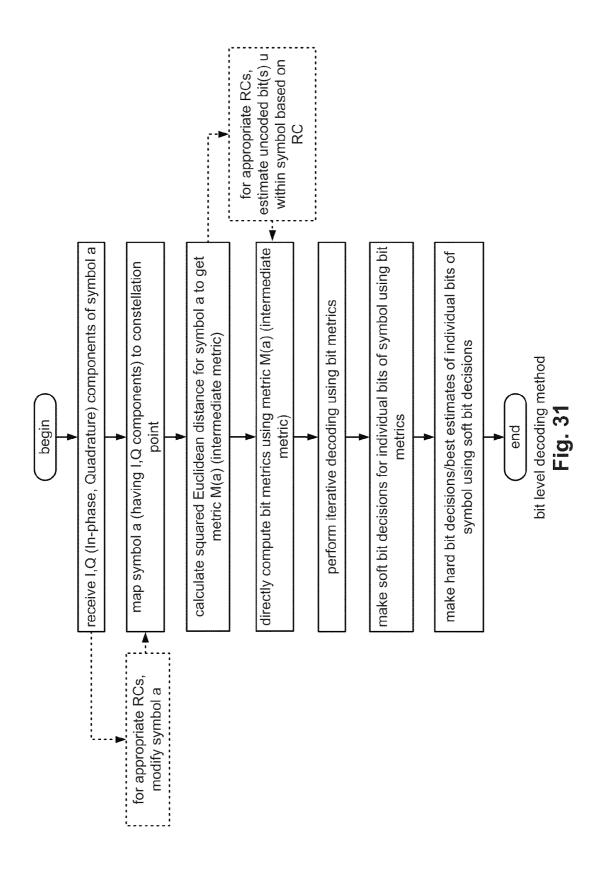

- FIG. 29, FIG. 30, and FIG. 31 are flowcharts illustrating embodiments of bit level decoding methods that are performed according to the invention.

## DETAILED DESCRIPTION OF THE INVENTION

The invention presents a solution that is able to decompose the various metrics employed within iterative decoding into 0.5 0, ..., 0.22 22

metrics that may be processed at the bit level. This is in contradistinction to the prior art approach to deal with these metrics on a symbol basis. The forward metrics (alphas), the backward metrics (betas), and the extrinsic values may all be processed on a bit level basis according to the invention. This can result in a great deal of memory when performing this decoding processing on a bit level basis. The various calculation when doing this decoding processing may be performed using min\* or max\* processing.

5

FIG. 1 is a system diagram illustrating an embodiment of a satellite communication system that is built according to the invention. A satellite transmitter is communicatively coupled to a satellite dish that is operable to communicate with a satellite. The satellite transmitter may also be communicatively coupled to a wired network. This wired network may include any number of networks including the Internet, proprietary networks, and/or other wired networks. The satellite transmitter employs the satellite dish to communicate to the satellite via a wireless communication channel. The satellite is able to communicate with one or more satellite receivers (each having a satellite dish). Each of the satellite receivers may also be communicatively coupled to a display.

Here, the communication to and from the satellite may cooperatively be viewed as being a wireless communication channel, or each of the communication to and from the satellite may be viewed as being two distinct wireless communication channels.

For example, the wireless communication "channel" may be viewed as not including multiple wireless hops in one embodiment. In other multi-hop embodiments, the satellite 30 receives a signal received from the satellite transmitter (via its satellite dish), amplifies it, and relays it to satellite receiver (via its satellite dish); the satellite receiver may also be implemented using terrestrial receivers such as satellite receivers, satellite based telephones, and/or satellite based Internet 35 receivers, among other receiver types. In the case where the satellite receives a signal received from the satellite transmitter (via its satellite dish), amplifies it, and relays it, the satellite may be viewed as being a "transponder;" this is a multi-hop embodiment. In addition, other satellites may exist that per- 40 form both receiver and transmitter operations in cooperation with the satellite. In this case, each leg of an up-down transmission via the wireless communication channel would be considered separately.

In whichever embodiment, the satellite communicates with 45 the satellite receiver. The satellite receiver may be viewed as being a mobile unit in certain embodiments (employing a local antenna); alternatively, the satellite receiver may be viewed as being a satellite earth station that may be communicatively coupled to a wired network in a similar manner in 50 which the satellite transmitter may also be communicatively coupled to a wired network.

The satellite transmitter is operable to encode information (using an encoder) that is to be transmitted to the satellite receiver; the satellite receiver is operable to decode the transmitted signal (using a decoder). The decoder is operable to perform decoding on a true bit level basis according to the invention. The FIG. 1 shows just one of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 2 is a system diagram illustrating an embodiment of a HDTV (High Definition Television) communication system that is built according to the invention. An HDTV transmitter is communicatively coupled to a tower. The HDTV transmitter, using its tower, transmits a signal to a local tower dish via 65 a wireless communication channel. The local tower dish may communicatively couple to an HDTV set top box receiver via

a coaxial cable. The HDTV set top box receiver includes the functionality to receive the wireless transmitted signal that has been received by the local tower dish; this may include any transformation and/or down-converting that may be needed to accommodate any up-converting that may have been performed before and during transmission of the signal from the HDTV transmitter and its tower.

6

The HDTV set top box receiver is also communicatively coupled to an HDTV display that is able to display the demodulated and decoded wireless transmitted signals received by the HDTV set top box receiver and its local tower dish. The HDTV transmitter (via its tower) transmits a signal directly to the local tower dish via the wireless communication channel in this embodiment. In alternative embodiments, the HDTV transmitter may first receive a signal from a satellite, using a satellite earth station that is communicatively coupled to the HDTV transmitter, and then transmit this received signal to the local tower dish via the wireless communication channel. In this situation, the HDTV transmitter operates as a relaying element to transfer a signal originally provided by the satellite that is destined for the HDTV set top box receiver. For example, another satellite earth station may first transmit a signal to the satellite from another location, and the satellite may relay this signal to the satellite earth station that is communicatively coupled to the HDTV transmitter. The HDTV transmitter performs receiver functionality and then transmits its received signal to the local tower dish.

In even other embodiments, the HDTV transmitter employs its satellite earth station to communicate to the satellite via a wireless communication channel. The satellite is able to communicate with a local satellite dish; the local satellite dish communicatively couples to the HDTV set top box receiver via a coaxial cable. This path of transmission shows yet another communication path where the HDTV set top box receiver may communicate with the HDTV transmitter.

In whichever embodiment and whichever signal path the HDTV transmitter employs to communicate with the HDTV set top box receiver, the HDTV set top box receiver is operable to receive communication transmissions from the HDTV transmitter.

The HDTV transmitter is operable to encode information (using an encoder) that is to be transmitted to the HDTV set top box receiver; the HDTV set top box receiver is operable to decode the transmitted signal (using a decoder). The decoder is operable to perform decoding on a true bit level basis according to the invention. The FIG. 2 shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 3A and FIG. 3B are system diagrams illustrating embodiments of uni-directional cellular communication systems that are built according to the invention.

Referring to the FIG. 3A, a mobile transmitter includes a local antenna communicatively coupled thereto. The mobile transmitter may be any number of types of transmitters including a one way cellular telephone, a wireless pager unit, a mobile computer having transmit functionality, or any other type of mobile transmitter. The mobile transmitter transmits a signal, using its local antenna, to a cellular tower via a wireless communication channel. The cellular tower is communicatively coupled to a base station receiver; the receiving tower is operable to receive data transmission from the local antenna of the mobile transmitter that has been communicated via the wireless communication channel. The cellular tower communicatively couples the received signal to the base station receiver.

The mobile transmitter is operable to encode information (using an encoder) that is to be transmitted to the base station receiver; the base station receiver is operable to decode the transmitted signal (using a decoder).

The decoder is operable to perform decoding on a true bit 5 level basis according to the invention. The FIG. 3A shows yet another of the many embodiments where true bit level decoding may be performed according to the invention. The FIG. 3A shows a uni-directional cellular communication system where the communication goes from the mobile transmitter to 10 the base station receiver via the wireless communication channel.

Referring to the FIG. 3B, a base station transmitter includes a cellular tower communicatively coupled thereto. The base station transmitter, using its cellular tower, transmits a signal to a mobile receiver via a communication channel. The mobile receiver may be any number of types of receivers including a one-way cellular telephone, a wireless pager unit, a mobile computer having receiver functionality, or any other type of mobile receiver. The mobile receiver is communicatively coupled to a local antenna; the local antenna is operable to receive data transmission from the cellular tower of the base station transmitter that has been communicated via the wireless communication channel. The local antenna communicatively couples the received signal to the mobile receiver.

The base station transmitter is operable to encode information (using an encoder) that is to be transmitted to the mobile receiver; the mobile receiver is operable to decode the transmitted signal (using a decoder).

The decoder is operable to perform decoding on a true bit 30 level basis according to the invention. The FIG. 3B shows yet another of the many embodiments where true bit level decoding may be performed according to the invention. The FIG. 3B shows a uni-directional cellular communication system where the communication goes from the base station transmitter to the mobile receiver via the wireless communication channel.

FIG. 3C is a system diagram illustrating an embodiment of a bi-directional cellular communication system that is built according to the invention. The communication within this 40 embodiment may go to and from the base station transceiver and to and from the mobile transceiver via the wireless communication channel.

Referring to the FIG. 3C, a base station transceiver includes a cellular tower communicatively coupled thereto. 45 The base station transceiver, using its cellular tower, transmits a signal to a mobile transceiver via a communication channel. The reverse communication operation may also be performed. The mobile transceiver is able to transmit a signal to the base station transceiver as well. The mobile transceiver 50 may be any number of types of transceiver including a cellular telephone, a wireless pager unit, a mobile computer having transceiver functionality, or any other type of mobile transceiver. The mobile transceiver is communicatively coupled to a local antenna; the local antenna is operable to receive data 55 transmission from the cellular tower of the base station transceiver that has been communicated via the wireless communication channel. The local antenna communicatively couples the received signal to the mobile transceiver.

The base station transceiver is operable to encode information (using its encoder) that is to be transmitted to the mobile transceiver; the mobile transceiver is operable to decode the transmitted signal (using its decoder).

In addition, the mobile transceiver is operable to encode information (using its encoder) that is to be transmitted to the 65 base station transceiver; the base station transceiver is operable to decode the transmitted signal (using its decoder).

8

The decoders within either of the mobile transceiver and the base station may be implemented to perform decoding on a true bit level basis according to the invention. The FIG. 3C shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 4A is a system diagram illustrating an embodiment of a uni-directional microwave communication system that is built according to the invention. A microwave transmitter is communicatively coupled to a microwave tower. The microwave transmitter, using its microwave tower, transmits a signal to a microwave tower via a wireless communication channel. A microwave receiver is communicatively coupled to the microwave tower. The microwave tower is able to receive transmissions from the microwave tower that have been communicated via the wireless communication channel.

The microwave transmitter is operable to encode information (using an encoder) that is to be transmitted to the microwave receiver; the microwave receiver is operable to decode the transmitted signal (using a decoder).

The decoder is operable to perform decoding on a true bit level basis according to the invention. The FIG. 4A shows yet another of the many embodiments where true bit level decoding may be performed according to the invention. The FIG. 4A shows a uni-directional microwave communication system where the communication goes from the microwave transmitter to the microwave receiver via the wireless communication channel.

FIG. 4B is a system diagram illustrating an embodiment of a bi-directional microwave communication system that is built according to the invention. Within the FIG. 4B, a first microwave transceiver is communicatively coupled to a first microwave tower. The first microwave transceiver, using the first microwave tower (the first microwave transceiver's microwave tower), transmits a signal to a second microwave tower of a second microwave transceiver via a wireless communication channel. The second microwave transceiver is communicatively coupled to the second microwave tower (the second microwave transceiver's microwave tower). The second microwave tower is able to receive transmissions from the first microwave tower that have been communicated via the wireless communication channel. The reverse communication operation may also be performed using the first and second microwave transceivers.

Each of the microwave transceivers is operable to encode information (using an encoder) that is to be transmitted to the other microwave transceiver; each microwave transceiver is operable to decode the transmitted signal (using a decoder) that it receives. Each of the microwave transceivers includes an encoder and a decoder.

The decoder of either of the microwave transceivers may be implemented to perform decoding on a true bit level basis according to the invention. The FIG. 4B shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 5A is a system diagram illustrating an embodiment of a uni-directional point-to-point radio communication system that is built according to the invention. A mobile unit transmitter includes a local antenna communicatively coupled thereto. The mobile unit transmitter, using its local antenna, transmits a signal to a local antenna of a mobile unit receiver via a wireless communication channel.

The mobile unit transmitter is operable to encode information (using an encoder) that is to be transmitted to the mobile unit receiver; the mobile unit receiver is operable to decode the transmitted signal (using a decoder).

The decoder is operable to perform decoding on a true bit level basis according to the invention. The FIG. 5A shows yet

another of the many embodiments where true bit level decoding may be performed according to the invention. The FIG. **5**A shows a uni-directional communication system where the communication goes from the mobile unit transmitter to the mobile unit receiver via the wireless communication channel.

FIG. 5B is a system diagram illustrating an embodiment of a bi-directional point-to-point radio communication system that is built according to the invention. Within the FIG. 5B, a first mobile unit transceiver is communicatively coupled to a first local antenna. The first mobile unit transceiver, using the 10 first local antenna (the first mobile unit transceiver's local antenna), transmits a signal to a second local antenna of a second mobile unit transceiver via a wireless communication channel. The second mobile unit transceiver is communicatively coupled to the second local antenna (the second mobile 15 unit transceiver's local antenna). The second local antenna is able to receive transmissions from the first local antenna that have been communicated via the communication channel. The reverse communication operation may also be performed using the first and second mobile unit transceivers.

Each mobile unit transceiver is operable to encode information (using an encoder) that is to be transmitted to the other mobile unit transceiver; each mobile unit transceiver is operable to decode the transmitted signal (using a decoder) that it receives.

The decoder of either of the mobile unit transceivers may be implemented to perform decoding on a true bit level basis according to the invention. The FIG. 5B shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 6A is a system diagram illustrating an embodiment of a uni-directional communication system that is built according to the invention. A transmitter communicates to a receiver via a uni-directional communication channel. The uni-directional communication channel may be a wireline (or wired) 35 communication channel or a wireless communication channel without departing from the scope and spirit of the invention. The wired media by which the uni-directional communication channel may be implemented are varied, including coaxial cable, fiber-optic cabling, and copper cabling, among 40 other types of "wiring." Similarly, the wireless manners in which the uni-directional communication channel may be implemented are varied, including satellite communication, cellular communication, microwave communication, and radio communication, among other types of wireless commu- 45 nication.

The transmitter is operable to encode information (using an encoder) that is to be transmitted to the receiver; the receiver is operable to decode the transmitted signal (using a decoder).

The decoder is operable to perform decoding on a true bit 50 level basis according to the invention. The FIG. **6**A shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 6B is a system diagram illustrating an embodiment of a bi-directional communication system that is built according 55 to the invention. Within the FIG. 6B, a first transceiver is communicatively coupled to a second transceiver via a bi-directional communication channel. The bi-directional communication channel may be a wireline (or wired) communication channel or a wireless communication channel without departing from the scope and spirit of the invention. The wired media by which the bi-directional communication channel may be implemented are varied, including coaxial cable, fiber-optic cabling, and copper cabling, among other types of "wiring." Similarly, the wireless manners in which 65 the bi-directional communication channel may be implemented are varied, including satellite communication, cellu-

10

lar communication, microwave communication, and radio communication, among other types of wireless communication

Each of the transceivers is operable to encode information (using an encoder) that is to be transmitted to the other transceiver; each transceiver is operable to decode the transmitted signal (using a decoder) that it receives.

The decoder of either of the transceivers may be implemented to perform decoding on a true bit level basis according to the invention. The FIG. 6B shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 6C is a system diagram illustrating an embodiment of a one to many communication system that is built according to the invention. A transmitter is able to communicate, via broadcast in certain embodiments, with a number of receivers, shown as receivers 1, 2, ..., n via a uni-directional communication channel. The uni-directional communication channel may be a wireline (or wired) communication channel 20 or a wireless communication channel without departing from the scope and spirit of the invention. The wired media by which the bi-directional communication channel may be implemented are varied, including coaxial cable, fiber-optic cabling, and copper cabling, among other types of "wiring." Similarly, the wireless manners in which the bi-directional communication channel may be implemented are varied, including satellite communication, cellular communication, microwave communication, and radio communication, among other types of wireless communication.

A distribution point is employed within the one to many communication system to provide the appropriate communication to the receivers 1, 2, ..., and n. In certain embodiments, the receivers 1, 2, ..., and n each receive the same communication and individually discern which portion of the total communication is intended for themselves.

The transmitter is operable to encode information (using an encoder) that is to be transmitted to the receivers  $1, 2, \ldots$ , and n; each of the receivers  $1, 2, \ldots$ , and n is operable to decode the transmitted signal (using a decoder).

The decoder of any of the receivers may be implemented to perform decoding on a true bit level basis according to the invention. The FIG. 6C shows yet another of the many embodiments where true bit level decoding may be performed according to the invention.

FIG. 7A is a system diagram illustrating an embodiment of a fiber-optic communication system that is built according to the invention. The fiber-optic communication system is operable to support true bit level decoding. The fiber-optic communication system includes a DWDM (Dense Wavelength Division Multiplexing (in the context of fiber optic communications) line card that is interposed between a line side and a client side.

DWDM is a technology that has gained increasing interest recently. From both technical and economic perspectives, the ability to provide potentially unlimited transmission capacity is the most obvious advantage of DWDM technology. The current investment already made within fiber-optic infrastructure can not only be preserved when using DWDM, but it may even be optimized by a factor of at least 32. As demands change, more capacity can be added, either by simple equipment upgrades or by increasing the number of wavelengths (lambdas) on the fiber-optic cabling itself, without expensive upgrades. Capacity can be obtained for the cost of the equipment, and existing fiber plant investment is retained. From the bandwidth perspective, some of the most compelling technical advantage of DWDM can be summarized as follows:

The transparency of DWDM: Because DWDM is a physical layer architecture (PHY), it can transparently support both Time Division Multiplexing (TDM) and data formats such as asynchronous transfer mode (ATM), Gigabit Ethernet, ESCON, and Fibre Channel with open interfaces over a common physical layer.

The scalability of DWDM: DWDM can leverage the abundance of dark fiber in many metropolitan area and enterprise networks to quickly meet demand for capacity on point-to-point links and on spans of existing SONET/SDH rings.

The dynamic provisioning capabilities of DWDM: the fast, simple, and dynamic provisioning of network connections give providers the ability to provide high-bandwidth services in days rather than months.

Fiber-optic interfacing is employed at each of the client and line sides of the DWDM line card. The DWDM line card includes a transport processor that includes functionality to support DWDM long haul transport, DWDM metro transport, next-generation SONET/SDH multiplexers, digital cross- 20 connects, and fiber-optic terminators and test equipment. On the line side, the DWDM line card includes a transmitter, that is operable to perform electrical to optical conversion for interfacing to an optical medium, and a receiver, that is operable to perform optical to electrical conversion for interfacing 25 from the optical medium. On the client side, the DWDM line card includes a 10 G serial module. That is operable to communicate with any other devices on the client side of the fiber-optic communication system using a fiber-optic interface. Alternatively, the interface may be implemented using non-fiber-optic media, including copper cabling and/or some other type of interface medium.

The DWDM transport processor of the DWDM line card includes a decoder that is used to decode received signals from either one or both of the line and client sides and an 35 encoder that is used to encode signals to be transmitted to either one or both of the line and client sides. The decoder is operable to perform decoding on a true bit level basis according to the invention. The FIG. 7A shows yet another of the many embodiments where true bit level decoding may be 40 performed according to the invention.

FIG. 7B is a system diagram illustrating an embodiment of a satellite receiver STB (Set Top Box) system that is built according to the invention. The satellite receiver STB system includes an advanced modulation satellite receiver that is 45 implemented in an all digital architecture. The satellite receiver STB system includes a satellite tuner that receives a signal via the L-band. The satellite tuner extracts I,Q (inphase and quadrature) components from a signal received from the L-band and provides them to the advanced modulation satellite receiver includes an embodiment of the decoder. The decoder is operable to perform decoding on a true bit level basis according to the invention.

The advanced modulation satellite receiver communicatively couples to an HDTV MPEG-2 (Motion Picture Experts Group 2 (Standard—Compressed Video at 4-9 Mbps)) transport de-mux, audio/video decoder and display engine. The advanced modulation satellite receiver and the HDTV MPEG-2 transport de-mux, audio/video decoder and display engine communicatively couple to a host CPU (Central Processing Unit). The HDTV MPEG-2 transport de-mux, audio/video decoder and display engine also communicatively couples to a memory module and a conditional access functional block. The HDTV MPEG-2 transport de-mux, audio/ video decoder and display engine provides HD video and audio output that may be provided to an HDTV display.

12

The advanced modulation satellite receiver is a single-chip digital satellite receiver supporting the decoder that is operable to support decoding on a true bit level basis according to the invention. The advanced modulation satellite receiver is operable to receive communication provided to it from a transmitter device that includes an encoder as well.

FIG. 8 is a system diagram illustrating an embodiment of a TTCM (Turbo Trellis Coded Modulation) communication system that is built according to the invention. The TTCM communication system includes a transmitter and a receiver that are communicatively coupled to one another via a communication channel that introduces AWGN (Additive White Gaussian Noise) to the signal. The communication channel may be wireline or wireless according to the invention. The AWGN communication channel may be viewed as being a relatively noisy communication channel in some embodiments.

The transmitter includes a TTCM encoder that encodes one or more information symbols and then modulates those encoded symbols. Those encoded symbol may also undergo modulation encoding to map those symbols to a constellation and an associating mapping. The transmitter then prepares this signal for transmission across the communication channel. At the other end of the communication channel, the receiver includes a TTCM decoder that receives and estimates the encoded symbols that have been transmitted across the communication channel. Further details of the operation of the various functional blocks contained within the TTCM encoder and the TTCM decoder are also described in more detail below.

Generally speaking, within the TTCM encoder, the turbo encoder performs symbol encoding and the symbol mapper maps those encoded symbols to an appropriate modulation (including a constellation and a corresponding mapping). Similarly, generally speaking within the TTCM decoder, the TTCM decoder performs calculations that are employed to perform decoding of the received symbols. The TTCM decoder is operable to perform decoding on a true bit level basis according to the invention.

It is also understood that a variety of means of modulation, transmission, receipt, and demodulation may be performed to generate the analog signals to be transmitted across the communication channel without departing from the scope and spirit thereof. Each and any such means may be practiced according to the invention while performing the TTCM encoding/decoding described herein.

FIG. 9 is a diagram illustrating an embodiment of an overview of functionality of a communication system that is built according to the invention. The functionality described within this embodiment may be viewed as being performed within a variety of the various communication system embodiments described within this specification.

Inputs bits are initially provided to a transmitter side of a communication channel. The input bits are initially encoded thereby generating encoded input bits. This encoding may be performed according to TTCM. These encoded bits are then grouped into symbols. These symbols, comprised of the encoded bits that are appropriately grouped, are provided to a symbol mapper that maps the symbols according to a modulation that includes a constellation and a corresponding mapping; this may be viewed as undergoing modulation encoding. At this point, the symbols may be viewed as being a digital baseband signal. These symbols are then modulated to generate an analog baseband signal whose frequency is that of baseband and whose magnitude and phase components vary at that baseband frequency. This may be performed using a DAC (Digital to Analog Converter). This analog baseband

signal may then be provided to a communication channel. The communication channel may be viewed as being an AWGN (Additive White Gaussian Noise) communication channel

In some embodiments, the analog baseband signal may undergo some up converting. For example, the analog baseband signal may be up converted to a higher carrier frequency for transmission on the communication channel. This up conversion may also involve transforming the analog baseband signal up to intermediate frequency before being transformed up to the higher carrier frequency at which the signal is transmitted across the communication channel.

The transmitted signal is then received at a receiver end of the communication channel. Initially, the received signal that has been transmitted may undergo some down converting to transform the received signal to an analog baseband signal. This may also include some transformation to an intermediate frequency before converting the signal down to an analog baseband signal. Alternatively, the conversion may be performed directly to the analog baseband signal.

The received analog baseband signal is then demodulated to generate a digital baseband signal. This may be performed using an ADC (Analog to Digital Converter). This may be viewed as performing the I,Q (In-phase, Quadrature) component extraction of the various symbols within the analog baseband signal. These I,Q components are then provided to a metric generator that calculated metrics for the symbols within the received digital baseband signal.

These symbol metrics are then decomposed to bit level 30 metrics. Theses bit level metrics may be viewed as those metrics that may be used to assist in any iterative decoding that is to be performed on a true bit level basis. Soft bit decisions are then made using these bit level metrics. Finally, hard limiting is performed on the soft bit decisions. This may 35 be viewed as making hard bit decisions using the soft bit decisions generated previously. These hard bit decisions may be viewed as being the best estimates of the input bits that had been provided at the transmitter side of the communication system.

Again, it is noted that this overview of the functionality of a communication system may be viewed as being supported within the context of many of the various embodiments described in this specification. The true bit level decoding may be supported in each of the various embodiments 45 described above. Below, several embodiments are described that show how this bit level decoding may be implemented.

As also indicated above, it is known that the iterative turbo decoding involves updating two real sequences during every iteration of the iterative decoding. These two sequences may 50 be viewed as being be viewed as being forward metrics (alphas) and backward metrics (betas) within the context of TCM (Trellis Coded Modulation) decoding as well as TTCM (Turbo Trellis Coded Modulation) decoding. These alphas and betas may be represented as follows:  $(\alpha_0(m), \alpha_1(m), \ldots, 55)$  $\alpha_{n-1}(m))$  and  $(\beta_0(m),\beta_1(m),\ldots,\,\beta_{n-1}(m)).$  The updating performed within this iterative decoding is performed using the a posteriori probability and the branch metrics. When performing TTCM decoding, a symbol metric will typically involve more than one information bit (e.g., a plurality of 60 information bits). Therefore, the calculation of the forward metric  $\alpha_1(m)$  and the backward metric  $\beta_1(m)$  involves more than one computing cycle to calculate all of the possible values of these various information bits of the symbol. This computing may be performed using various cycles of min\* or 65 max\* processing. However, using this approach is implemented in a manner that costs a lot of transistors (which may

14

be viewed as occupying a great deal of real estate within an integrated circuit that performs the decoding).

The invention presents a method to decompose these symbol metrics to bit metrics that are then used in the decoding processing. The number of transistors that would be required to perform decoding processing is greatly reduced by performing the decoding on a bit level. Using this bit level decoding, the metrics involving in performing the decoding processing, namely the forward metrics (alphas)  $\alpha_1(m)$  and the backward metrics (betas)  $\beta_1(m)$  are then represented as bit metrics.

FIG. **10**A is a diagram illustrating an embodiment of a rate 1/2 encoder that employs puncturing according to the invention. To support this decoding processing on a bit level basis, a trellis encoder is initially constructed using a rate 1/2 encoder. More specifically, a rate 2/3 trellis encoder can be constructed by puncturing a rate 1/2 encoder. Input bits  $i_k i_{k-1}$  are provided to the rate 1/2 encoder. When the first input bit,  $i_{k-1}$ , is provided to the rate 1/2 encoder, the encoded bits,  $i_{k-1}$  and  $c_{k-1}$ , are generated. The output bit  $c_k$  may be viewed as being a redundancy or coded bit. When the second input bit,  $i_k$ , is provided to the rate 1/2 encoder, the encoded bits,  $i_{k-1}$  and  $c_{k-1}$ , are generated. The output bit  $i_{k-1}$  may be viewed as being the input bit itself, and the output bit  $c_{k-1}$  may be viewed as being the input bit itself, and the output bit  $c_{k-1}$  may be viewed as being a redundancy or coded bit.

However, during this second coding iteration, the output bit  $c_{k-1}$  is punctured, or thrown away. These remaining bits,  $i_k$ ,  $c_k$ , and  $i_{k-1}$ , may be viewed as encoded bits. These remaining bits,  $i_k$ ,  $c_k$ , and  $i_{k-1}$ , may then be grouped to form a symbol. Overall, the operation of this rate 1/2 encoder that employs puncturing, when receiving the successive input bits  $i_k i_{k-1}$  and outputting the encoded bits  $i_k c_k i_{k-1}$  may be viewed as being a rate 2/3 encoder. The input bits  $i_k i_{k-1}$  may be viewed as being an input symbol and the encoded bits  $i_k c_k i_{k-1}$  may be viewed as being an output symbol.

In a coded modulation scheme, a signal value, such as I,Q (In-phase, Quadrature) component values of a signal received from a communication channel, may contain information corresponding to more than one information bit, one information bit, or no information bits. That is to say, the symbol may include information corresponding to more than one information bit. The invention presents a solution that allows a bit metric to be obtained from a signal value with more than one information bit according to bit level decoding thereby allowing the discrimination of the individual information bits within the symbol. In this specification, bit level decoding is presented that may be performed within a variety of embodiments including performing bit level MAP (maximum a posteriori probability) decoding where the maximum end result value is used to select the appropriate value.

Next, the selection of an appropriate code is selected that will support the bit level decoding according to the invention. An example code having a code rate of 1/2 and having 8 states is used to illustrate the functionality of the invention; however, the invention is also extendable to different code having other code rate as well as those employing trellises having different numbers of states.

In an illustrative example, a code having a code rate of 1/2 is initially sought. To find the rate 1/2 base code, some design criteria are required.

A first design criterion is to obey Ungerboeck's rule for TCM (Trellis Coded Modulation). This rule states, "All the transitions that diverge from a common state or reemerge into a same state must be assigned with signals from one subset at the first level of set partitioning."

A second design criterion is that the interleaving gain of the turbo code, which depends on the effective minimum distance d<sub>2</sub> (for convolutional code this is the weight of the output when two bits are input) of the final trellis, and the number of the nearest neighbor N<sub>2</sub> with respect to the effective minimum 5 distance d2. The criterion is that d2 should be as large as possible but N<sub>2</sub> should be as small as possible. The rate 2/3 code that is selected for a symbol decoder has a maximum d<sub>2</sub>=5 among all rate 2/3 and 8 state RSC (Reed-Solomon Code). In addition, this embodiment also includes a minimal  $N_2 = 1$ .

Such a rate 1/2 recursive encoder may be represented by two binary polynomials. One is feed forward polynomial, and one is feedback polynomial. For example, if the feed forward polynomial is f(D)=1+D and the feedback polynomial is b(D) $=1+D+D^3$ , then such a rate 1/2 encoder may be represented as shown within the FIG. 10B.

FIG. 10B is a diagram illustrating an embodiment of a rate 1/2 encoder (3,13) that is built according to the invention. 20 When an input bit is provided to the encoder, 2 bits are output. One of the output bits  $c_1$  is representative of exactly the input bit, and the other of the output bits  $c_0$  is a code bit (sometimes referred to as a parity bit or a redundancy bit). This represents in the design process of a code that supports bit level decod-

FIG. 10C is a diagram illustrating an embodiment of a rate 1/k encoder that is built according to the invention. In general, a rate 1/k encoder (a rate 1/k convolutional encoder, where 30  $k=1, 2, 3, \ldots$  and so on) may be employed when designing a code that supports bit level decoding. The code bits that are output from the encoder may be punctured, or selected to form encoded symbols according to the invention. It is noted that any number of encoders may be employed that operate by 35 receiving a single bit as input.

In this specification, octal numbers are used to present these polynomials (e.g., the feed forward polynomial and the feedback polynomial). In the embodiment of interest, f=3 and b=13. A search is then made for all possible encoders with a 40 degree of the feed forward polynomial and a degree of the feed back polynomial that is not greater than 3. Among all such encoders, there are 56 that have an effective minimum distance  $d_2 \ge 3$ . There are 2 such encoders with  $d_2 = 5$  and 17 such encoders with d<sub>2</sub>=4. However, most of these encoders do 45 not satisfy Ungerboeck's rule as stated above.

FIG. 11 is a diagram illustrating a list of possible encoders that satisfy Ungerboeck's rule and a minimum distance of  $d_2 \ge 3$  according to the invention. The order of the feed forward polynomial (in octal) and the order of the feedback 50 polynomial (in octal) are shown as a function of the effective minimum distance d<sub>2</sub> and the number of the nearest neighbor  $N_2$ . In addition, the other weights, when appropriate, with 2 bit input sequences and the number of the sequence are also

Based on the list shown within the FIG. 11 and the rule of minimum effective distance d<sub>2</sub>, the encoders (11,13) and encoder (17,15) should be the best. After performing a search among all possible signal constellations (for corresponding modulations) may then be performed. The encoder with the 60 best signal constellation that is found if the rate 1/2 (11,13) encoder.

Such a rate 1/2 recursive encoder may be represented by two binary polynomials. One is a feed forward polynomial  $f(D)=1+D^3$  and the other one is a feedback polynomial of 65  $b(D)=1+D+D^3$ . Such a rate 1/2 encoder (11,13) may be represented by the circuit shown within the FIG. 12A.

16

FIG. 12A is a diagram illustrating an embodiment of a rate 1/2 encoder (11,13) that is built according to the invention. When an input bit is provided to the encoder, 2 bits are output. One of the output bits  $c_1$  is representative of exactly the input bit, and the other of the output bits  $c_0$  is a code bit (again, sometimes referred to as a parity bit or a redundancy bit). This design represents the best rate 1/2 convolutional encoder that is selected in the design process of a code that supports bit level decoding.

In addition, from this encoder circuit, it can be concludes that, when the state is fixed, the redundancy bits are different for the two different input bits. This property is then used in the calculation of the bit metrics as is described in more detail below. The trellis of this encoder is shown below in the FIG.

FIG. 12B is a diagram illustrating an embodiment of a trellis of the rate 1/2 encoder (11,13), shown in the FIG. 12A, according to the invention. This trellis is an 8 state trellis.

The operation of this 8 state trellis, with the mapping shown, may then be described as follows. After looking at these examples, state transitions from the other states will also be understood.

When the encoder is in the state 0=000, and when a 0 bit one example of a convolutional encoder that may be selected 25 input is provided, then the state of the encoder will transition from the input state 0=000 to the output state 0=000. This may be viewed as the state of the encoder transitioning along the 1<sup>st</sup> possible branch of the trellis extending from the input state 0=000; this branch may be viewed as being indexed by the 0 bit input. That is to say: when starting from the input state 0=000, and when receiving as input the bit 0, the encoder will transition to output state 0=000, and a 2 bit, coded output symbol is generated by the encoder having a value of 0=00.

> Looking at another example: when the encoder is in the state 0=000, and when a 1 bit input is provided, then the state of the encoder will transition from the input state 0=000 to the output state 2=010. This may be viewed as the state of the encoder transitioning along the  $2^{nd}$  possible branch of the trellis extending from the input state 0=000; this branch may be viewed as being indexed by the 1 bit input. That is to say: when starting from the input state 0=000, and when receiving as input the bit 1, the encoder will transition to output state 2=010, and a 2 bit, coded output symbol is generated by the encoder having a value of 3=11.

Looking at another example: when the encoder is in the state 1=001, and when a 1 bit input is provided, then the state of the encoder will transition from the input state 1=001 to the output state 0=000. This may be viewed as the state of the encoder transitioning along the 1st possible branch of the trellis extending from the input state 1=001; this branch may be viewed as being indexed by the 1 bit input. That is to say: when starting from the input state 1=001, and when receiving as input the bit 1, the encoder will transition to output state 55 0=000, and a 2 bit, coded output symbol is generated by the encoder having a value of 3=11.

Looking at another example: when the encoder is in the state 1=001, and when a 0 bit input is provided, then the state of the encoder will transition from the input state 1=001 to the output state 2=010. This may be viewed as the state of the encoder transitioning along the  $2^{nd}$  possible branch of the trellis extending from the input state 1=001; this branch may be viewed as being indexed by the 0 bit input. That is to say: when starting from the input state 1=001, and when receiving as input the bit 0, the encoder will transition to output state 2=010, and a 2 bit, coded output symbol is generated by the encoder having a value of 0=00.

The state transitions of this trellis, along the other various branches of the trellis may be understood in reference to these example state transitions.

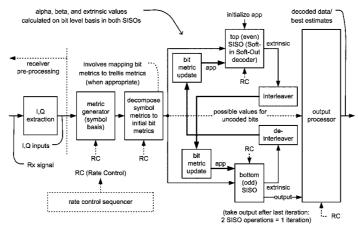

FIG. 13 is a system diagram illustrating an embodiment of a TTCM (Turbo Trellis Coded Modulation) decoder system 5 that is built according to the invention. A received signal (shown as Rx signal) is provided to an I,Q extraction functional block that extracts the I,Q (In-phase, Quadrature) components from the received signal that are mapped according to a RC (Rate Control) as determined by a rate control 10 sequencer. This may be viewed as being receiver pre-processing. The I,Q inputs are then mapped according to the modulation's appropriate constellation and mapping. Then, the mapped I,Q is passed to a metric generator that also receives the RC input from the rate control sequencer. The metric 15 generator generates the appropriate metrics that are measured from the received I,Q to the constellation points within the modulation's appropriate constellation and mapping; the metrics are indexed by the mapping of the constellation points within the modulation; these metrics may be viewed as being 20 the scaled Euclidian distances from the location of the actual received symbol to the expected constellation point locations within the modulation. The processing performed by the metric generator is performed on a symbol basis.

After the symbol metrics are calculated by the metric generator, these symbol metrics are output and provided to a decompose symbol metrics to bit metrics functional block that decomposes the symbol metrics into the initial bit metrics for each symbol of the signal. That is to say, the initial values of the metrics for each of the individual bits of the bits of the 30 received symbol are decomposed from the symbol metrics.

Continuing on with the decoding process and functionality, theses initial bit level metrics that are calculated by the decompose symbol metrics to bit metrics functional block are then provided to a top (even) SISO (Soft-In Soft-Out decoder) 35 and simultaneously to a bottom (odd) SISO. Each of these SISOs and calculates forward metrics (alphas) and backward metrics (betas), and extrinsic values according to the trellis employed (such as the trellis shown in the FIG. 12B). These alphas, betas, and extrinsics are then all calculated for each of 40 the individual bits of the symbols that are to be decoded. These calculations of alphas, betas, and extrinsics are all based on the trellis and according to the RC provided by the RC input from the rate control sequencer. Again, these alphas, betas, and extrinsics may all be calculated on a bit level basis. 45 These values may be calculated (directly and indirectly) using the bit metrics decomposed from the symbol metrics; these calculations may also be performed using min\* or max\* processing without departing from the scope and spirit of the invention.

Starting with the top SISO, after the extrinsic values have been calculated, they are passed to an interleaver. Afterwards these values are passed to a bit metric update functional block. It is noted here that the bit metrics are updated each iteration of the iterative decoding. In contradistinction, the prior art 55 approaches of performing iterative decoding typically use the same symbol metric during each of the iterations of the iterative decoding. After the bit metric values have been updated, then these values are passed to the bottom SISO as APP (a priori probability) information. Similarly, after extrinsic val- 60 ues have been calculated within the bottom SISO, they are passed to a de-interleaver whose output is then passed to another corresponding bit metric update functional block. The output from this bit metric update functional block is then passed back to the top SISO as APP information. It is noted 65 that a single decoding iteration, within the iterative decoding process of the TTCM decoder system consists of performing

18

two SISO operations; that is to say, the iterative decoding process must pass through both the top (even) SISO and through the bottom (odd) SISO.

After a significant level of confidence has been achieved and a solution is being converged upon, or after a predetermined number of decoding iterations have been performed, then the output from the bottom (odd) SISO may then be passed as output to an output processor. The final output from the bottom (odd) SISO may be viewed as being soft bit decisions. That is to say, the operation of the SISOs may generally be referred to as calculating soft bit decisions of the individual bits of the symbols contained within a signal received by the TTCM decoder system. The output processor uses these soft bit decisions to generate hard bit decisions for the input bits that have been encoded at an encoder end of a communication system.

Moreover, there may be situations where one or more uncoded bits u may have been used to generate the symbols that are provided to the TTCM decoder system. The TTCM decoder system is also operable to accommodate the decoding of those uncoded bits u, when appropriate.

FIG. 14 is a system diagram illustrating an embodiment of an alternative TTCM decoder system that recycles a single SISO according to the invention (shown as receiving I,Q inputs). This embodiment may be viewed as a variant of the TTCM decoder system described above that employs two separate SISOs (a top SISO and bottom SISO).

The alternative TTCM decoder system is shown as receiving as input the I,Q from a received signal. It is noted that receiver pre-processing may also be performed in this embodiment as with the other embodiment of a TTCM decoder system described above. For example, an I,Q extraction functional block may also be employed to extract these I,Q inputs within this embodiment. If desired in some embodiments, a ping pong buffer, employing two input buffers, may be employed for efficient buffering of the I,Q inputs. The I,Q inputs are then passed to the metric generator. The functionality of the metric generator may be viewed as being similar to that of the metric generator within the other embodiment of the TTCM decoder system described above.

Also similar to the embodiment described above, after the symbol metrics are calculated by the metric generator, these symbol metrics are output and provided to a decompose symbol metrics to initial bit metrics functional block that decomposes the symbol metrics into the initial values of the bit metrics for each symbol of the signal. That is to say, the initial values of the metrics for each of the individual bits of the bits of the received symbol are decomposed from the symbol metrics.

Continuing on with the decoding process and functionality, theses now bit level metrics that are calculated by the decompose symbol metrics to bit metrics functional block are then provided to a single SISO; the information necessary to perform decoding of any possible uncoded bits (when appropriate) is passed to the output processor. The SISO calculates forward metrics (alphas), backward metrics (betas), and extrinsic values according to the trellis employed and provides them to a functional block that is operable to perform both interleaving and de-interleaving (depending upon which SISO operation is being performed—either the first SISO operation of the single SISO or the second SISO operation of the single SISO). The output of the interleaver/de-interleaver functional block is passed first to an update bit metric functional block and then back to the SISO as APP. Again, it is noted that the values of alphas, betas, and extrinsic values are calculated on a bit level basis within the single SISO of this

embodiment. The bit metric values are updated during every iteration of the iterative decoding.

Similar to the embodiment of TTCM decoder system described above, it is again noted that a single decoding iteration, within the iterative decoding process of the alternative TTCM decoder system consists of performing two SISO operations; that is to say, the iterative decoding process must pass through both the SISO once (when the SISO performs the top SISO functionality when referenced to the TTCM decoder system described above) and through the SISO again 10 (when the SISO performs the bottom SISO functionality when referenced to the TTCM decoder system described above).

After a significant level of confidence for the soft bit decisions within the SISO have been achieved and a solution is 15 being converged upon, or after a predetermined number of decoding iterations have been performed, then the soft bit decisions are output from the SISO and passed as output to the output processor. The output processor uses these soft bit decisions to generate hard bit decisions and to provide 20 decoded output data. It is also noted that APP initialization may be performed within this embodiment as well as the other embodiment of TTCM decoder system described above.