(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6673077号

(P6673077)

(45) 発行日 令和2年3月25日(2020.3.25)

(24) 登録日 令和2年3月9日(2020.3.9)

(51) Int.CI.

G 0 1 R 15/20 (2006.01)

F 1

G 0 1 R 15/20

B

請求項の数 5 (全 15 頁)

(21) 出願番号 特願2016-146418 (P2016-146418)

(22) 出願日 平成28年7月26日 (2016.7.26)

(65) 公開番号 特開2018-17553 (P2018-17553A)

(43) 公開日 平成30年2月1日 (2018.2.1)

審査請求日 平成30年8月10日 (2018.8.10)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100106149

弁理士 矢作 和行

(74) 代理人 100121991

弁理士 野々部 泰平

(74) 代理人 100145595

弁理士 久保 貴則

(72) 発明者 江坂 卓馬

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72) 発明者 野村 江介

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

最終頁に続く

(54) 【発明の名称】電流センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

被検出電流が流れる電流経路(20)と、

前記電流経路に前記被検出電流が流れることによって生じる第1磁界と垂直方向に第2磁界を生成する磁界発生部(13)と、

前記第2磁界と、前記第1磁界と前記第2磁界とで構成される合成磁界との成す角度に応じた正弦値を含む信号及び余弦値を含む信号の少なくともいずれか一方を出力するセンサチップ(11)と、

前記センサチップから前記正弦値を含む信号及び余弦値を含む信号の少なくともいずれか一方が入力され、入力された前記信号を用いて前記成す角度における正接値を演算し、前記正接値に対応するセンサ信号を出力する信号処理部(12)と、

底部と環状の側壁とで収容空間(15e)が形成され、前記収容空間に前記センサチップと前記信号処理部を収容した状態で、前記底部が前記電流経路に実装されたセラミックパッケージ(15)と、を備えた電流センサであって、

前記電流経路は、前記被検出電流の流れ方向に沿って、第1スリット(21)と第2スリット(22)とが形成されており、

前記第1スリット及び前記第2スリットは、開口形状が矩形状であり、

前記センサチップは、前記電流経路における前記第1スリットと前記第2スリットとで挟まれた領域上であり、且つ前記被検出電流の流れ方向に沿う中心線上に配置されており、

10

20

前記セラミックパッケージは、前記センサ信号の出力先である絶縁性の樹脂基材に配線が形成された回路基板（200）に実装されるものであって、前記底部に対向し前記側壁で囲まれた開口端を有しており、前記開口端を囲む前記側壁の端部が、はんだを介して前記回路基板に実装されている電流センサ。

【請求項 2】

前記センサチップは、前記セラミックパッケージに収容され、前記電流経路との間に前記底部を介した状態で、前記領域上であり、且つ前記中心線上に配置されている請求項1に記載の電流センサ。

【請求項 3】

前記セラミックパッケージは、複数のセラミック板が積層されてなり、前記底部と前記側壁に、前記電流経路から発生する電界ノイズを遮蔽するシールド部（15g）が形成されている請求項2に記載の電流センサ。

【請求項 4】

前記シールド部は、前記セラミック板に形成された環状のシールド用パターン（15g2）と、前記セラミック板に形成されたシールド用ピア（15g3）と、前記セラミック板に形成されたグランドプレーン（15g1）とを含んでいる請求項3に記載の電流センサ。

【請求項 5】

前記セラミックパッケージは、幅が前記電流経路の幅よりも広い請求項1～4のいずれか1項に記載の電流センサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電流センサに関する。

【背景技術】

【0002】

従来、電流センサの一例として、特許文献1に開示された電流センサがある。この電流センサは、扁平形状の電流路と、電流路上に配設され電流路に被測定電流が流れたときに発生する磁界を検出する磁電変換素子と、を備えている。電流路には、被測定電流の流れる向きに沿って長い穴部が設けられており、この穴部によって2つに分流した第1分流路と第2分流路が形成されている。磁電変換素子は、磁気センサパッケージ内にパッケージングされ、第1分流路上に配設されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2014-55790号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記電流センサは、電流路の中心付近に穴部が形成されている。そして、電磁変換素子は、電流路における幅が狭い第1分流路上に配置されている。このため、電流センサは、第1分流路上における位置が幅方向にズレると、磁電変換素子で感じる磁場量が減少するため位置ロバスト性が悪いという問題がある。

【0005】

本開示は、上記問題点に鑑みなされたものであり、高周波特性を向上させつつ、位置ロバスト性を向上できる電流センサを提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するために本開示は、

10

20

30

40

50

被検出電流が流れる電流経路（20）と、

電流経路に被検出電流が流れることによって生じる第1磁界と垂直方向に第2磁界を生成する磁界発生部（13）と、

第2磁界と、第1磁界と第2磁界とで構成される合成磁界との成す角度に応じた正弦値を含む信号及び余弦値を含む信号の少なくともいずれか一方を出力するセンサチップ（11）と、

センサチップから正弦値を含む信号及び余弦値を含む信号の少なくともいずれか一方が入力され、入力された信号を用いて成す角度における正接値を演算し、正接値に対応するセンサ信号を出力する信号処理部（12）と、

底部と環状の側壁とで収容空間（15e）が形成され、収容空間にセンサチップと信号処理部を収容した状態で、底部が電流経路に実装されたセラミックパッケージ（15）と、を備えた電流センサであって、

電流経路は、被検出電流の流れ方向に沿って、第1スリット（21）と第2スリット（22）とが形成されており、

第1スリット及び第2スリットは、開口形状が矩形状であり、

センサチップは、電流経路における第1スリットと第2スリットとで挟まれた領域上であり、且つ被検出電流の流れ方向に沿う中心線上に配置されており、

セラミックパッケージは、センサ信号の出力先である絶縁性の樹脂基材に配線が形成された回路基板（200）に実装されるものであって、底部に対向し側壁で囲まれた開口端を有しており、開口端を囲む側壁の端部が、はんだを介して回路基板に実装されていることを特徴とする。

#### 【0007】

このように、本開示は、処理回路によって、第2磁界と合成磁界との成す角度における正接値を演算し、この正接値に対応するセンサ信号を出力する。このため、本開示は、センサ信号が被検出電流にリニアに対応する信号となり、検出精度を向上させることができる。

#### 【0008】

また、本開示は、電流経路に第1スリットと第2スリットとが形成されており、中心線上にセンサチップが配置されている。このため、本開示は、被検出電流の高周波側でも、センサチップで感じる磁場量の減少を抑制でき、高周波特性を向上できる。

#### 【0009】

また、本開示は、センサチップが電流経路の中心線に配置されているため、位置ロバスト性を向上できる。つまり、本開示は、センサチップが電流経路の中心線上に配置されているため、センサチップの位置が、中心線上から電流経路の幅方向にズレたとしても、センサチップで感じる磁場量の減少を抑えることができる。このように、本開示は、高周波特性を向上させつつ、位置ロバスト性を向上できる。

#### 【0010】

なお、特許請求の範囲、及びこの項に記載した括弧内の符号は、一つの態様として後述する実施形態に記載の具体的手段との対応関係を示すものであって、発明の技術的範囲を限定するものではない。

#### 【図面の簡単な説明】

#### 【0011】

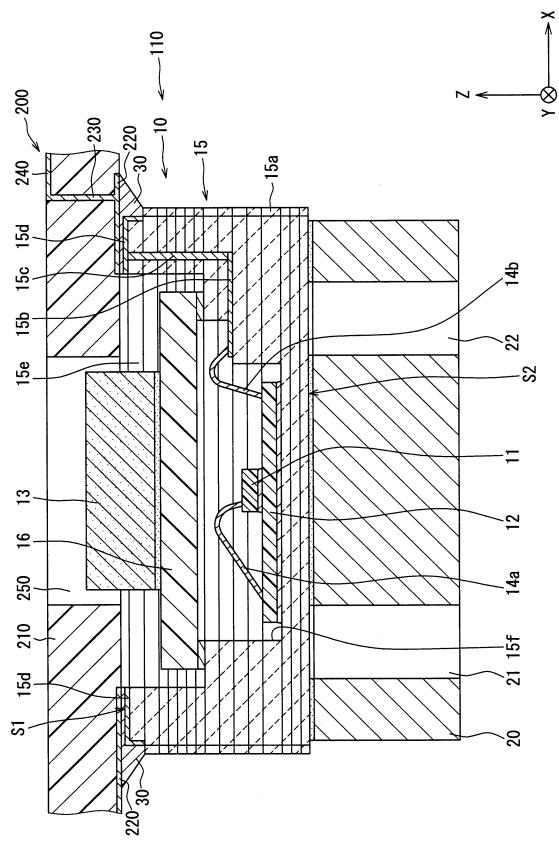

【図1】実施形態における電流センサの概略構成を示す断面図である。

【図2】図1におけるII-II線に沿う断面図である。

【図3】実施形態におけるセンサチップと処理回路の概略構成を示す回路図である。

【図4】実施形態における電流センサの概略構成を示す断面図である。

【図5】変形例1における電流センサの概略構成を示す断面図である。

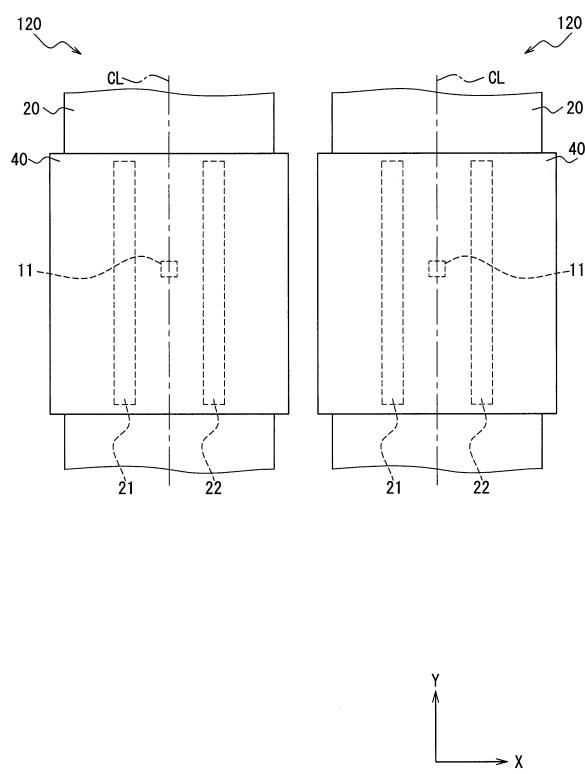

【図6】変形例2における電流センサの概略構成を示す平面図である。

#### 【発明を実施するための形態】

#### 【0012】

10

20

30

40

50

以下において、図面を参照しながら、発明を実施するための複数の形態を説明する。各形態において、先行する形態で説明した事項に対応する部分には同一の参照符号を付して重複する説明を省略する場合がある。各形態において、構成の一部のみを説明している場合は、構成の他の部分については先行して説明した他の形態を参照し適用することができる。

#### 【0013】

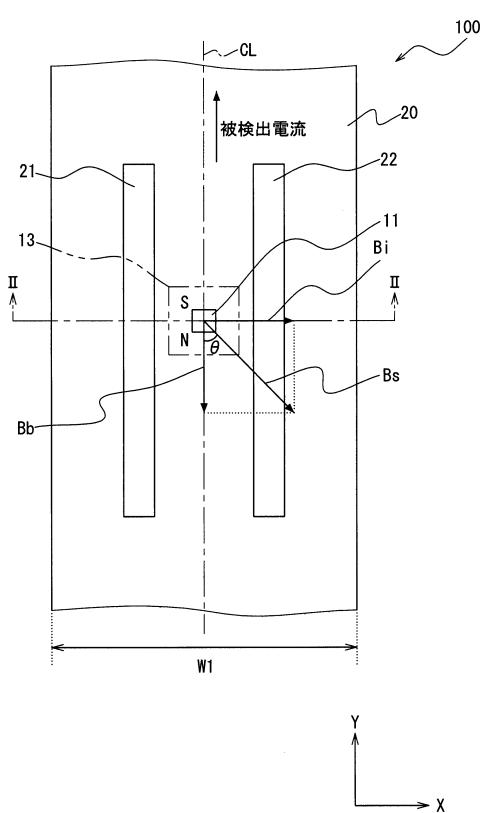

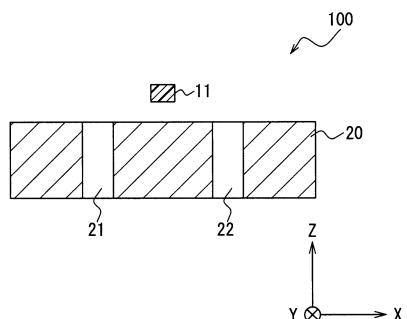

図1、図2、図3、図4を用いて、本実施形態の電流センサ100に関して説明する。なお、図1、図2では、センサチップ11とバスバ20との位置関係をわかりやすくするために、セラミックパッケージ15などの図示を省略している。

#### 【0014】

電流センサ100は、例えば、車載モータのインバータ制御に用いられる。電流センサ100は、インバータ制御のために、車載モータに電源を供給するバスバ20に流れる被検出電流を検出するものである。電流センサ100は、電流経路に相当するバスバ20に被検出電流が流れることで、バスバ20が発生させる検出磁界をセンサチップ11が電気信号に変換することで被検出電流を検出する。このように、本実施形態では、一例として、インバータ用の電流センサ100を採用する。しかしながら、本発明は、これに限定されず、車載バッテリの電流の検出にも適用できる。

#### 【0015】

なお、電流センサ100は、例えば電気自動車やハイブリッド車に搭載される。また、電流センサ100は、集磁コアを必要としないコアレス電流センサを採用している。バスバ20には、高電圧が印加されるため、高電圧部と称することもできる。

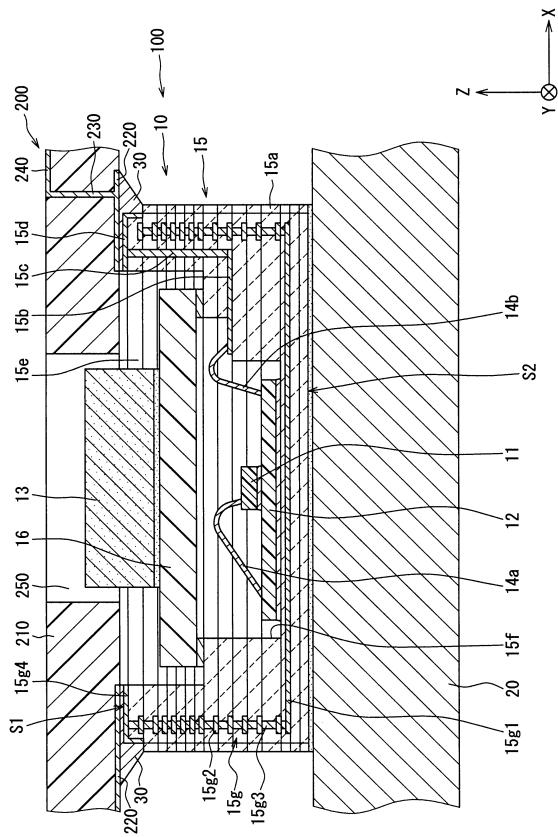

#### 【0016】

電流センサ100は、検出部10とバスバ20とを備えている。検出部10は、図4に示されるように、バスバ20に組みつけられている。具体的には、検出部10は、図1に示すように、バスバ20に流れる被検出電流の方向とバイアス磁界Bbとが平行となるように、バスバ20に組み付けられる。また、検出部10は、バスバ20に流れる被検出電流によって生成される電流磁界Biとバイアス磁界Bbとが垂直となるように、バスバ20に組み付けられる。

#### 【0017】

そして、検出部10(センサチップ11)には、バイアス磁界Bbと電流磁界Biとによって構成される合成磁界Bsが印加されるようになっている。なお、本実施形態では、電流磁界Biが第1磁界に相当し、バイアス磁界Bbが第2磁界に相当している。

#### 【0018】

検出部10は、図4に示すように、主に、センサチップ11と、処理回路12と、バイアス磁石13とを備えている。また、本実施形態では、この他に、セラミックパッケージ15と、第1ワイヤ14aと、第2ワイヤ14bと、スペーサ16とを備えた電流センサ100を採用している。センサチップ11、処理回路12、ワイヤ14a, 14b、及び後程説明する信号配線は、バスバ20よりも電圧が低いため、低電圧部とも称することができる。

#### 【0019】

センサチップ11は、バスバ20に流れる被検出電流が発生する磁束密度(検出磁界)を検知して磁電変換を行い電気信号に変換する。センサチップ11は、図4に示すように、接着材などを介して処理回路12に実装されており、第1ワイヤ14aを介して処理回路12と電気的に接続されている。センサチップ11で磁電変換された電気信号は、第1ワイヤ14aを介して処理回路12に出力される。なお、本実施形態では、一例として、バイアス磁界Bbと合成磁界Bsとのなす角度に応じた余弦値を含む信号を電気信号として出力するセンサチップ11を採用している。しかしながら、本発明は、バイアス磁界Bbと合成磁界Bsとのなす角度に応じた正弦値を含む信号を電気信号として出力するセンサチップ11でも採用できる。

#### 【0020】

10

20

30

40

50

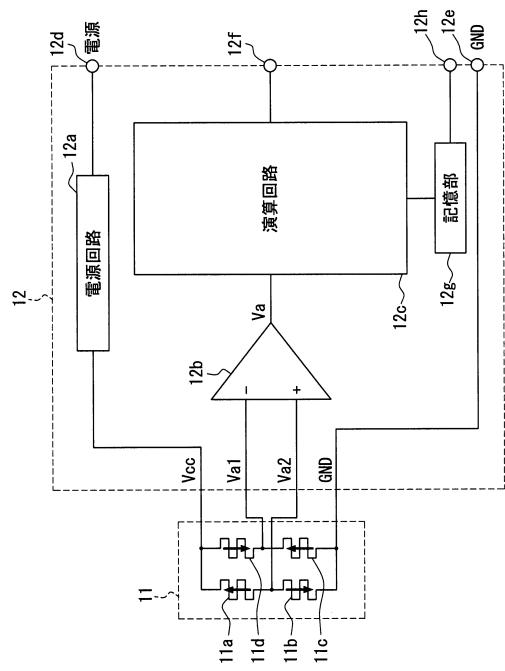

センサチップ 11 は、図 3 に示すように、ブリッジ回路を構成する第 1 磁気抵抗素子 11 a ~ 第 4 磁気抵抗素子 11 d を備えている。各磁気抵抗素子 11 a ~ 11 d としては、巨大磁気抵抗素子 (GMR)、異方性磁気抵抗素子 (AMR)、トンネル磁気抵抗素子 (TMR) などの、磁気ベクトルの向きによって電気信号が変化する素子を採用できる。このため、電流センサ 100 は、ベクトル検知式電流センサと言える。

#### 【0021】

なお、各磁気抵抗素子 11 a ~ 11 d は、特開 2013-64663 号公報に開示された磁気抵抗素子を採用できる。つまり、各磁気抵抗素子 11 a ~ 11 d は、磁化方向が所定方向に固定されたピン層、絶縁体で構成されるトンネル層、外部磁化に応じて磁化方向が変化するフリー層が順に積層され、下部電極及び上部電極を備えた一般的なものである。

10

#### 【0022】

処理回路 12 は、信号処理部に相当する。処理回路 12 は、図 4 に示すように、センサチップ 11 が実装された状態で、接着材などを介してセラミックパッケージ 15 に実装されている。処理回路 12 は、上記のように第 1 ワイヤ 14 a を介してセンサチップ 11 と電気的に接続されており、且つ、第 2 ワイヤ 14 b を介して信号配線に接続されている。信号配線は、セラミックパッケージ 15 に形成されたものであり、後程説明する。

#### 【0023】

処理回路 12 は、センサチップ 11 で変換された電気信号が第 1 ワイヤ 14 a を介して入力される。処理回路 12 は、入力された電気信号を用いて演算処理を行うことでセンサ信号を算出する。そして、処理回路 12 は、第 2 ワイヤ 14 b を介してセンサ信号を出力する。このセンサ信号は、例えば、信号用パッド 15 d、はんだ 30 を介して、後程説明する回路基板 200 の配線の一部であるランド 220 に伝達される。第 1 ワイヤ 14 a と第 2 ワイヤ 14 b のそれぞれは、出力経路と言える。

20

#### 【0024】

また、処理回路 12 は、図 3 に示すような回路構成を有している。処理回路 12 は、演算処理を行うことで、入力された電気信号を、後程説明する回路基板 200 に出力するためのセンサ信号に変換する。なお、処理回路 12 は、特開 2013-64663 号公報に開示された回路構成を採用できる。よって、処理回路 12 の詳細は、特開 2013-64663 号公報を参照できるため、ここでの説明を簡略化する。

30

#### 【0025】

処理回路 12 は、電源回路 12 a、差動增幅回路 12 b、演算回路 12 c、第 1 端子 12 d、第 2 端子 12 e、第 3 端子 12 f、記憶部 12 g、第 4 端子 12 h などを備えている。

#### 【0026】

電源回路 12 a は、定電圧回路等を備えて構成されており、第 1 磁気抵抗素子 11 a と第 4 磁気抵抗素子 11 d の中点に接続されている。そして、電源回路 12 a は、第 1 端子 12 d を介して電源から入力される電圧を定電圧  $V_{CC}$  に変換し、この定電圧  $V_{CC}$  を第 1 磁気抵抗素子 11 a と第 4 磁気抵抗素子 11 d の中点に印加する。なお、第 2 磁気抵抗素子 11 b と第 3 磁気抵抗素子 11 c の中点は、第 2 端子 12 e を介してグランドに接続されている。

40

#### 【0027】

差動增幅回路 12 b は、反転入力端子が第 3 磁気抵抗素子 11 c と第 4 磁気抵抗素子 11 d の中点に接続されて、この中点の電圧  $V_{a1}$  が入力される。また、差動增幅回路 12 b は、非反転入力端子が第 1 磁気抵抗素子 11 a と第 2 磁気抵抗素子 11 b の中点に接続されて、この中点の電圧  $V_{a2}$  が入力される。そして、差動增幅回路 12 b は、入力された電圧を差動增幅して、演算回路 12 c に対して信号  $V_a$  を出力する。

#### 【0028】

記憶部 12 g には、差動增幅回路 12 b の増幅率  $G$ 、センサチップ 11 に印加される電圧  $V_{CC}$ 、センサチップ 11 の温度特性  $K(t)$  が記憶されている。なお、これらは、第

50

4端子12hを介して記憶部12gに書き込まれる。

【0029】

演算回路12cは、差動増幅回路12bから入力された信号Vaと、記憶部12gに記憶されている増幅率G、電圧Vcc、温度特性K(t)を用いて演算処理を行うことでセンサ信号を算出する。つまり、演算回路12cは、 $Vc = G \cdot Vcc \cdot K(t) \cdot \cos$ を演算して、演算値Vcを算出する。そして、演算回路12cは、信号Vaを演算値Vcで除算して正接値を演算し、正接値に対応する信号をセンサ信号として出力する。なお、演算回路12cは、第3端子12fを介してセンサ信号を出力する。この第3端子12fは、第2ワイヤ14bに電気的に接続されている。

【0030】

バイアス磁石13は、磁界発生部に相当する。バイアス磁石13は、電気信号の基準となる磁気ベクトルであるバイアス磁界Bbを与えるために設けられている。つまり、バイアス磁石13は、バスバ20に被検出電流が流れることによって生じる電流磁界Biと垂直方向にバイアス磁界Bbを生成する。本実施形態では、図4に示すように、スペーサ16を介して、センサチップ11と対向配置されたバイアス磁石13を採用している。バイアス磁石13は、例えば接着材などを介して、スペーサ16に実装されている。なお、図1では、図面をわかりやすくするためにバイアス磁石13を二点鎖線で図示している。

【0031】

スペーサ16は、センサチップ11とバイアス磁石13との間隔を、所定距離に確保するための部材である。スペーサ16は、図4に示すように、接着剤などを介してセラミックパッケージ15に実装されている。

【0032】

なお、図4においては、第1ワイヤ14aと第2ワイヤ14bをそれぞれ一つずつ図示している。しかしながら、電流センサ100は、これに限定されず、複数の第1ワイヤ14aを備えていてもよいし、複数の第2ワイヤ14bを備えていてもよい。

【0033】

セラミックパッケージ15は、図4に示すように、センサチップ11などを収容するための収容空間15eが形成された容器である。セラミックパッケージ15は、環状の側壁と、環状の側壁の一端に形成された底とを有し、環状の側壁の他端が開口して、収容空間15eが形成された箱状の部材と言える。よって、セラミックパッケージ15は、一部が開口した有底の箱部材とも言える。また、セラミックパッケージ15は、一面S1と、一面S1の反対面であり、一面S1に平行に設けられた裏面S2とを有している。

【0034】

なお、セラミックパッケージ15は、収容空間15eに処理回路12、ワイヤ14a, 14b、スペーサ16も収容している。また、バイアス磁石13は、一部が収容空間15eに収納され、他部が収容空間15eから突出した状態で配置されている。

【0035】

セラミックパッケージ15は、底部における収容空間15e側にセンサチップ11や処理回路12が配置されており、底部における収容空間15eの反対側がバスバ20に固定されている。つまり、セラミックパッケージ15は、裏面S2がバスバ20に固定されている。よって、電流センサ100は、センサチップ11とバスバ20との間に、セラミックパッケージ15の一部であるセラミック板15aが配置されていると言える。なお、セラミックパッケージ15は、接着剤などを介して、バスバ20に固定されている。

【0036】

セラミックパッケージ15は、図4に示すように、複数のセラミック板15aが積層されて構成されている。本実施形態では、一例として、15層のセラミック板15aが積層されたセラミックパッケージ15を採用している。開口端側の最外層であるセラミック板15aの表面は、一面S1に相当する。反対側の最外層であるセラミック板15aの表面は、裏面S2に相当する。

【0037】

10

20

30

40

50

また、セラミックパッケージ 15 は、例えば  $\text{Al}_2\text{O}_3$  や  $\text{Si}_3\text{N}_4$  などの無機物を焼き固めた焼結体である。なお、本実施形態では、外形が略正方形のセラミック板 15 a を採用している。しかしながら、本発明はこれに限定されず、矩形状や円形であっても採用できる。

【0038】

セラミックパッケージ 15 は、収容空間 15 e を形成するために一部のセラミック板 15 a が環状に構成されており、底部を形成するために他のセラミック板 15 a が板状に構成されている。また、セラミックパッケージ 15 は、環状に構成されたセラミック板 15 a で側壁が形成されている。

【0039】

本実施形態では、積層方向の一方の端から順番に 12 層のセラミック板 15 a が環状に構成されており、残りの 3 層のセラミック板 15 a が板状に構成されている。セラミックパッケージ 15 は、積層された環状のセラミック板 15 a の開口壁面によって、内壁面 15 f が形成されている。

【0040】

なお、環状のセラミック板 15 a とは、厚み方向に貫通穴が形成されたものである。一方、板状のセラミック板 15 a とは、貫通穴が形成されていないものである。厚み方向は、Z 方向に相当する。

【0041】

また、本実施形態では、センサチップ 11 と回路基板 200 との電気的な経路である導電性の信号配線を含んだセラミックパッケージ 15 を採用している。セラミックパッケージ 15 は、例えば、信号配線を構成する信号用パターン 15 b、信号用ビア 15 c、及び信号用パッド 15 d を備えている。信号用パターン 15 b は、セラミック板 15 a 間に設けられて収容空間 15 e に露出しない部位と、第 2 ワイヤ 14 b が接続できるように収容空間 15 e に露出している部位とを含んでいる。

【0042】

信号用ビア 15 c は、セラミック板 15 a を貫通するように設けられており、異なる層の信号用パターン 15 b どうしや、信号用パターン 15 b と信号用パッド 15 d とを電気的に接続している。信号用パッド 15 d は、一面 S1 側に設けられており、回路基板 200 のランド 220 とはんだ 30 によって電気的及び機械的に接続される部位である。なお、信号用パッド 15 d は、一面 S1 の一部を成しているとも言える。

【0043】

また、本実施形態では、バスバ 20 から生じる電界ノイズを遮蔽するための構成要素であるシールド部 15 g が設けられたセラミックパッケージ 15 を採用している。本実施形態では、一例として、グランドプレーン 15 g 1、シールド用パターン 15 g 2、シールド用ビア 15 g 3、シールド用パッド 15 g 4 を含むシールド部 15 g を採用している。

【0044】

シールド用パターン 15 g 2 は、環状に設けられている。このため、シールド用パターン 15 g 2 は、ガードリングとも称することができる。シールド用パターン 15 g 2 は、センサチップ 11 や処理回路 12 を囲う位置に設けられている。また、シールド用パターン 15 g 2 は、信号配線の一部を囲う位置に設けられている。なお、シールド用パターン 15 g 2 は、収容空間 15 e を囲う位置に、環状に設けられていると言える。

【0045】

本実施形態では、一例として、連続して設けられた 12 層のセラミック板 15 a に、シールド用パターン 15 g 2 が設けられている例を採用している。また、シールド用パターン 15 g 2 は、グランドプレーン 15 g 1 とシールド用パッド 15 g 4 との間における各セラミック板 15 a に設けられている。

【0046】

シールド用ビア 15 g 3 は、シールド用パターン 15 g 2 どうし、シールド用パターン 15 g 2 とシールド用パッド 15 g 4、シールド用パターン 15 g 2 とグランドプレーン

10

20

30

40

50

15g1を電気的に接続している。つまり、シールド用ピア15g3は、各シールド用パターン15g2を介しつつ、グランドプレーン15g1からシールド用パッド15g4までを電気的に接続している。

【0047】

シールド用ピア15g3は、グランドプレーン15g1とシールド用パッド15g4との間における各セラミック板15aの少なくとも一箇所に設けられていればよい。よって、シールド用ピア15g3は、各セラミック板15aにおいて、二箇所以上に設けられてもよい。なお、本実施形態では、グランドプレーン15g1とシールド用パッド15g4との間における各セラミック板15aの二箇所にシールド用ピア15g3が設けられている例を採用している。

10

【0048】

シールド用パッド15g4は、一面S1側に設けられており、回路基板200のランド220とはんだ30によって電気的及び機械的に接続される部位である。なお、シールド用パッド15g4は、一面S1の一部を成しているとも言える。また、シールド用パッド15g4が接続されているランド220は、回路基板200のグランドである。

【0049】

グランドプレーン15g1は、シールド用パターン15g2とは異なり、べた状のパターンである。電流センサ100は、グランドプレーン15g1のZ方向における対向領域に低電圧部が含まれるように、グランドプレーン15g1が設けられている。また、グランドプレーン15g1は、低電圧部とバスバ20との間に設けられていると言える。

20

【0050】

このように、セラミックパッケージ15は、シールド用パターン15g2と、グランドプレーン15g1と、シールド用ピア15g3によって、立体構造のシールド部15gが形成されていると言える。また、シールド部15gは、シールド用パターン15g2と、グランドプレーン15g1と、シールド用ピア15g3とで低電圧部を囲うように構成されている。そして、シールド部15gは、シールド用パッド15g4を介して、回路基板200のグランドに接続されている。なお、シールド部15gは、処理回路12が接続されているセンサグランドとは別のボディグランドをとると好ましい。しかしながら、本発明はこれに限定されない。

【0051】

30

シールド部15gの構成は、これに限定されない。シールド部15gは、セラミックパッケージ15の収容空間15eに面する表面に形成されていてもよい。つまり、セラミックパッケージ15は、シールド部15gで内壁面15fが形成されていてもよい。

【0052】

バスバ20は、検出部10が実装可能に構成されており、センサチップ11に対向する部位を含んでいる。本実施形態では、図1に示すように、バスバ20のY方向に電流が流れる例を採用している。バスバ20は、電流が流れることで、図1に示すように電流磁界Biを発生させる。

【0053】

バスバ20は、図1、図2に示すように、第1スリット21と第2スリット22が形成されている。第1スリット21と第2スリット22は、バスバ20の厚み方向、すなわちZ方向に貫通した穴である。また、本実施形態では、一例として、開口形状が矩形状である第1スリット21と第2スリット22を採用している。

40

【0054】

第1スリット21と第2スリット22は、Y方向に沿って平行に設けられている。つまり、第1スリット21と第2スリット22は、長手側がY方向に沿って、短手側がX方向に沿って設けられている。言い換えると、第1スリット21と第2スリット22は、バイアス磁界Bbに沿って設けられている。

【0055】

また、第1スリット21と第2スリット22は、バスバ20の中心線CLを対称軸とし

50

て、線対称に設けられている。つまり、中心線 CL と第 1 スリット 21 との間隔は、中心線 CL と第 2 スリット 22 との間隔と同じである。しかしながら、第 1 スリット 21 と第 2 スリット 22 の位置は、これに限定されない。中心線 CL と第 1 スリット 21 との間隔は、中心線 CL と第 2 スリット 22 との間隔と異なっていてもよい。

#### 【0056】

なお、中心線 CL は、バスバ 20 の幅 W1 の中心を通り、Y 方向に延びる仮想直線である。バスバ 20 の幅 W1 は、バスバ 20 における X 方向の長さである。以下においては、各要素の X 方向の長さを単に幅とも称する。また、幅方向は、X 方向を示すものとする。

#### 【0057】

バスバ 20 は、第 1 スリット 21 と第 2 スリット 22 とで挟まれた部位に、センサチップ 11 に対向する部位を含んでいる。よって、センサチップ 11 は、バスバ 20 における第 1 スリット 21 と第 2 スリット 22 との間の領域に対向配置されている。さらに、センサチップ 11 は、バスバ 20 の中心線 CL 上に配置されている。

#### 【0058】

つまり、電流センサ 100 は、センサチップ 11 などがセラミックパッケージ 15 に収容された検出部 10 がバスバ 20 に実装された状態で、センサチップ 11 がバスバ 20 の中心線 CL 上に配置される。よって、電流センサ 100 は、図 1 に示すように、バスバ 20 上に検出部 10 が実装された状態で、中心線 CL を対称軸として線対称形状をなしているとも言える。

#### 【0059】

なお、本実施形態では、一例として、セラミックパッケージ 15 の一面 S1 側に、回路基板 200 が固定されている例を採用している。回路基板 200 は、電流センサ 100 におけるセンサ信号の出力先である。回路基板 200 は、絶縁基材 210、ランド 220、基板ビア 230、導体パターン 240、穴部 250 などを備えている。つまり、回路基板 200 は、絶縁性の樹脂基材である絶縁基材 210 に対して、ランド 220 と基板ビア 230 と導体パターン 240 を含む配線が形成され、且つ、絶縁基材 210 の厚み方向に貫通した穴部 250 が形成されている。

#### 【0060】

本実施形態では、例えばガラスエポキシ等の樹脂を絶縁基材 210 として採用している。また、本実施形態では、絶縁基材 210 を厚み方向に貫通した穴部 250 が形成された回路基板 200 を採用している。しかしながら、回路基板 200 は、絶縁基材 210 を貫通していない有底の穴部 250 であっても採用できる。

#### 【0061】

また、電流センサ 100 は、信号用パッド 15d が、はんだ 30 を介してランド 220 と電気的及び機械的に接続されて、回路基板 200 に実装されている。よって、電流センサ 100 は、はんだ 30 を介して、センサ信号を回路基板 200 に出力する。このため、はんだ 30 は、低電圧部の一部とみなすことができる。

#### 【0062】

なお、セラミックパッケージ 15 は、底部に対向し側壁で囲まれた開口端を有しており、開口端を囲む側壁の端部が回路基板 200 に実装されていると言える。また、電流センサ 100 は、回路基板 200 に実装された状態で、バイアス磁石 13 が穴部 250 に配置される。

#### 【0063】

このように、電流センサ 100 は、処理回路 12 によって、バイアス磁界 Bb と合成磁界 Bs との成す角度 における正接値を演算し、この正接値に対応する信号をセンサ信号として出力する。このため、電流センサ 100 は、センサ信号が被検出電流にリニアに対応する信号となり、検出精度を向上させることができる。また、電流センサ 100 は、X 方向と Y 方向の二方向の磁界を検出する。

#### 【0064】

また、電流センサ 100 は、バスバ 20 に第 1 スリット 21 と第 2 スリット 22 とが形

10

20

30

40

50

成されている。このため、電流センサ100は、高周波特性を向上できる。この点に関して、比較例の電流センサなどを用いて説明する。比較例の電流センサは、バスバが平板形状であり、スリットが形成されていないものとする。

#### 【0065】

一般的に、電流センサは、バスバに流れる被検出電流の大電流化に伴って、バスバの発熱が問題となる。バスバの発熱を抑えるためには、バスバの断面積を広くするか、バスバの幅を広くすることが考えられる。

#### 【0066】

しかしながら、比較例の電流センサは、バスバの断面積が広くなるにつれて、バスバにおける電流密度が減少する。このため、電流センサは、バスバが発生する磁界量も減少して、S/N比が悪化する。10

#### 【0067】

比較例の電流センサは、バスバの幅を広くすると、被検出電流の高周波側では、表皮効果により、幅方向の両端に被検出電流が流れることになる。このため、比較例の電流センサでは、バスバの中心線上にセンサチップが配置されていた場合、センサチップで感じる磁場量が減少する。また、比較例の電流センサでは、センサチップで感じる磁場量の減少を抑制するために、バスバの幅方向における一端上にセンサチップを配置した場合、位置口バスト性が低下する。

#### 【0068】

これに対して、電流センサ100は、バスバ20に第1スリット21と第2スリット22とが形成されている。このため、電流センサ100のバスバ20には、表皮効果によって、幅方向の両端、第1スリット21を介して対向している端部、及び、第2スリット22を介して対向している端部に被検出電流が流れることになる。20

#### 【0069】

よって、電流センサ100は、被検出電流の高周波側でも、センサチップ11で感じる磁場量の減少を抑制できる。したがって、電流センサ100は、高周波特性を向上できる。さらに、電流センサ100は、バスバ20の幅W1を広くしても、高周波特性を向上できるため、バスバ20の発熱を抑えることができる。

#### 【0070】

また、電流センサ100は、センサチップ11がバスバ20の中心線CL上に配置されている。このため、電流センサ100は、位置口バスト性を向上できる。つまり、電流センサ100は、センサチップ11がバスバ20の中心線CL上に配置されているため、センサチップ11の位置が、中心線CL上からバスバ20の幅W1方向にズレたとしても、センサチップ11で感じる磁場量の減少を抑えることができる。よって、電流センサ100は、センサチップ11が幅方向へ位置ズレしたとしても、センサチップ11で感じる磁場量を確保しやすく、S/N比を向上できる。このように、電流センサ100は、高周波特性を向上させつつ、位置口バスト性を向上できる。30

#### 【0071】

特に、電流センサ100は、上記のように、バスバ20の幅W1を広くしても高周波特性を向上できるため、比較的幅が広いバスバ20を採用できる。このため、電流センサ100は、バスバの幅が比較的狭い場合よりも、位置口バスト性を向上させやすい。40

#### 【0072】

また、上記のように、電流センサ100は、エポキシ系などのモールド樹脂よりも絶縁性に優れたセラミックパッケージ15にセンサチップ11が収納されている。このため、電流センサ100は、センサチップ11がモールド樹脂で封止されている場合よりも、センサチップ11とバスバ20との絶縁を確保しやすく、センサチップ11とバスバ20との距離を近づけることができる。

#### 【0073】

つまり、電流センサ100は、バスバ20に対してセンサチップ11を近づけても絶縁を確保できる。よって、電流センサ100は、センサチップ11がモールド樹脂で封止さ50

れている場合よりも、検出磁界を増加できる。これに伴って、電流センサ100は、検出精度を向上できる。

【0074】

なお、バスバ20は、電流が流れると、電界ノイズを発生させる。よって、セラミックパッケージ15は、バスバ20から生じる電界ノイズを遮蔽するための構成要素であるシールド部15gが設けられている。このシールド部15gは、例えば、低電圧部を囲うように、セラミックパッケージ15の底部と側壁に形成されている。

【0075】

また、電流センサ100は、このようにシールド部15gを有しているため、バスバ20が発する電界ノイズから低電圧部を保護できる。詳述すると、電流センサ100は、セラミックパッケージ15の底に対向する部位からの電界ノイズからだけでなく、セラミックパッケージ15の側壁に回り込む電界ノイズからも低電圧部を保護できる。10

【0076】

言い換えると、電流センサ100は、ワイヤ14a, 14bや信号配線と、バスバ20との静電カッピングを抑制できる。このため、電流センサ100は、センサチップ11で変換された電気信号や、処理回路12から出力されたセンサ信号の変動、すなわち出力変動を抑えることができる。

【0077】

特に、本実施形態の電流センサ100は、インバータ制御のために、車載モータに電源を供給するバスバ20に流れる被検出電流を検出する。この場合、バスバ20は、MOSFETやIGBT等の高速スイッチングによって過渡的な電界ノイズを発生しやすい。電流センサ100は、インピーダンスの高いワイヤ14a, 14bや信号配線に電界ノイズが静電カッピングした場合、誘導電流が流れて出力変動を引き起こす。しかしながら、電流センサ100は、上記のように静電カッピングを抑制できるため、インバータ用の電流センサに好適である。20

【0078】

ところで、電流センサ100は、セラミックパッケージ15の線膨張係数と、実装される回路基板200の絶縁基材210との線膨張係数が異なる。よって、セラミックパッケージ15と回路基板200とは、温度変化に伴う変形量が異なる。このため、はんだ30には、セラミックパッケージ15と回路基板200との変形量の差に起因する熱応力が印加される。30

【0079】

そこで、本実施形態では、セラミックパッケージ15の開口端側が回路基板200と対向した状態で、回路基板200に実装された電流センサ100を採用している。このため、電流センサ100は、底側が回路基板200と接続されている場合より、セラミックパッケージ15の側壁が変更しやすく、はんだ30に印加される熱応力を低減できる。

【0080】

なお、本実施形態では、センサチップ11や処理回路12がセラミックパッケージ15に収容された電流センサ100を採用した。しかしながら、本発明は、これに限定されず、特開2013-64663号公報と同様に、センサチップ11や処理回路12が樹脂部材で封止された構成などであっても採用できる。40

【0081】

以上、本発明の好ましい実施形態について説明した。しかしながら、本発明は、上記実施形態に何ら制限されることはなく、本発明の趣旨を逸脱しない範囲において、種々の変形が可能である。以下に、本発明のその他の形態として、変形例1～3に関して説明する。上記実施形態及び変形例1～3は、それぞれ単独で実施することも可能であるが、適宜組み合わせて実施することも可能である。本発明は、実施形態において示された組み合わせに限定されることなく、種々の組み合わせによって実施可能である。

【0082】

(変形例1)

図5を用いて、変形例1の電流センサ110について説明する。電流センサ110は、セラミックパッケージ15とバスバ20の幅が電流センサ100と異なる。なお、電流センサ110は、シールド部15gを備えたセラミックパッケージ15であってもよい。

【0083】

電流センサ110は、セラミックパッケージ15の幅が、バスバ20の幅W1よりも広くなるように構成されている。また、電流センサ110は、裏面S2の対向領域から幅方向にバスバ20がはみ出すことなく、バスバ20にセラミックパッケージ15が実装されている。

【0084】

電流センサ110は、電流センサ100と同様の効果を奏することができる。さらに、電流センサ110は、セラミックパッケージ15の幅がバスバ20の幅よりも広い。このため、電流センサ110は、電流センサ100よりも、高電圧部のバスバ20と、低電圧部のはんだ30と沿面距離を長くすることができる。したがって、電流センサ110は、電流センサ100よりも、はんだ30の絶縁耐性を向上できる。

【0085】

(変形例2)

図6を用いて、変形例2の電流センサ120について説明する。電流センサ120は、磁気シールド40を備えている点が電流センサ100と異なる。なお、電流センサ120は、検出部10として、センサチップ11と、処理回路12と、バイアス磁石13を備えている。

【0086】

磁気シールド40は、磁性材料によって構成されており、外部磁界がセンサチップ11を透過することを抑制するものである。電流センサ120は、例えば、一対の磁気シールド40で、センサチップ11と、処理回路12と、バイアス磁石13と、バスバ20が挟みこまれている。

【0087】

また、本変形例では、複数の電流センサ120が一体的に組み付けられて構成されている。具体的には、一例として、二つの電流センサ120が組み付けられている。このように、複数の電流センサ120が一体的に組み付けられ構造体は、電流センサ端子台とも称することができる。

【0088】

電流センサ120は、電流センサ100と同様の効果を奏することができる。また、電流センサ120は、磁気シールド40を備えているため、センサチップ11に外部磁界が印加されることを抑制でき、電流センサ100よりも検出精度を向上できる。

【0089】

さらに、電流センサ120は、バスバ20の中心線CL上にセンサチップ11が配置されているため、隣り合う電流センサ120からの磁気ノイズを受けにくい。つまり、電流センサ120は、バスバ20の中心線CL上よりも隣り合う電流センサ120側にズレた位置にセンサチップ11が配置されている場合より、隣り合う電流センサ120からの磁気ノイズを受けにくい。よって、電流センサ120は、電流センサ端子台としてのシールド性能確保も期待できる。

【0090】

(変形例3)

上記実施形態では、ブリッジ回路を構成する第1磁気抵抗素子11a～第4磁気抵抗素子11dを含む一つのセンサチップ11を備えた電流センサ100を採用した。しかしながら、本発明は、これに限定されない。変形例3の電流センサは、特開2013-64663号公報と同様に、二つのセンサチップを備えている。つまり、変形例3の電流センサは、センサチップ11に加えて、他の4つの磁気抵抗素子がブリッジ回路を形成するように形成された第2センサチップを備えている。この変形例3の電流センサは、上記実施形態の電流センサと同様の効果を奏することができる。

10

20

30

40

50

## 【符号の説明】

## 【0091】

100 ~ 120 ... 電流センサ、10 ... 検出部、11 ... センサチップ、11a ~ 11d ... 磁気抵抗素子、12 ... 処理回路、12a ... 電源回路、12b ... 差動增幅回路、12c ... 演算回路、12d ... 第1端子、12e ... 第2端子、12f ... 第3端子、12g ... 記憶部、12h ... 第4端子、13 ... バイアス磁石、14a ... 第1ワイヤ、14b ... 第2ワイヤ、15 ... セラミックパッケージ、15a ... セラミック板、15b ... 信号用パターン、15c ... 信号用ビア、15d ... 信号用パッド、15e ... 収容空間、15f ... 内壁面、16 ... スペーサ、20 ... パスバ、21 ... 第1スリット、22 ... 第2スリット、30 ... はんだ、40 ... 磁気シールド、S1 ... 一面、S2 ... 裏面、200 ... 回路基板、210 ... 絶縁基材、220 ... ランド、230 ... 基板ビア、240 ... 導体パターン、250 ... 穴部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 酒井 亮輔

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 杉戸 達明

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 繩山 浩二

(56)参考文献 特開2011-185772(JP, A)

特開2014-181981(JP, A)

特開平02-210887(JP, A)

特開2009-168790(JP, A)

特開2007-067778(JP, A)

特開2012-220469(JP, A)

特開2016-070904(JP, A)

特開2016-109663(JP, A)

欧州特許出願公開第00359886(EP, A1)

特開2015-135267(JP, A)

米国特許出願公開第2012/0112365(US, A1)

米国特許第05939772(US, A)

(58)調査した分野(Int.Cl., DB名)

G01R 15/00 - 15/26

G01R 33/06 - 33/09