(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5567489号

(P5567489)

(45) 発行日 平成26年8月6日(2014.8.6)

(24) 登録日 平成26年6月27日(2014.6.27)

(51) Int.Cl.

F 1

HO 1 L 23/12 (2006.01)

HO 1 L 21/3205 (2006.01)

HO 1 L 21/768 (2006.01)

HO 1 L 23/522 (2006.01)

HO 1 L 23/12 501 P

HO 1 L 21/88 T

請求項の数 15 (全 23 頁)

(21) 出願番号 特願2010-536543 (P2010-536543)

(86) (22) 出願日 平成20年12月4日 (2008.12.4)

(65) 公表番号 特表2011-505705 (P2011-505705A)

(43) 公表日 平成23年2月24日 (2011.2.24)

(86) 国際出願番号 PCT/IB2008/003343

(87) 国際公開番号 WO2009/071982

(87) 国際公開日 平成21年6月11日 (2009.6.11)

審査請求日 平成23年12月2日 (2011.12.2)

(31) 優先権主張番号 11/949,951

(32) 優先日 平成19年12月4日 (2007.12.4)

(33) 優先権主張国 米国(US)

(73) 特許権者 508301087

エーティーアイ・テクノロジーズ・ユーニューアルシー

ATI TECHNOLOGIES ULC

カナダ、オンタリオ エル3ティー 7

エックス6、マーカム、コマース バリー

ドライブ イースト 1

One Commerce Valley

Drive East, Markham, Ontario, L3T 7X6

Canada

(74) 代理人 100078916

弁理士 鈴木 由充

最終頁に続く

(54) 【発明の名称】アンダーバンプ配線層の方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の再配置層構造体を介して所定の回路構造体に電気的に接続される第1のサイトと、第1の再配置層構造体から所定距離を隔てて配置される第2の再配置層構造体を介して第1のサイトに接続されたのとは異なる回路構造体に電気的に接続される第2のサイトとが構造的に連ねられた構成のアンダーバンプメタライゼーション構造体を半導体チップ上に形成することと、

前記アンダーバンプメタライゼーション構造体に高分子層を装着することと、

前記アンダーバンプメタライゼーション構造体上における前記第1のサイトに、はんだ構造体を、当該はんだ構造体の一部が前記高分子層の上に位置づけられた状態にして形成する一方で、前記アンダーバンプメタライゼーション構造体上における前記第2のサイトには、はんだ構造体を形成しないようにすることと、

を含む、製造方法。

## 【請求項 2】

前記アンダーバンプメタライゼーション構造体を形成することは、前記第1の再配置層構造体に電気的に接続された前記第1のサイトと、前記第2の再配置層構造体に電気的に接続された第2のサイトとを有する導体グリッドを形成することを含む、請求項1に記載の製造方法。

## 【請求項 3】

前記アンダーバンプメタライゼーション構造体を形成することは、ハブおよび前記ハブ

に接続された少なくとも前記第1および第2のサイトを有するクラスターを形成することを含み、前記第1のサイトは前記第1の再配置層構造体に接続されると共に前記第2のサイトは前記第2の再配置層構造体に接続される、請求項1に記載の製造方法。

【請求項4】

前記半導体チップを基板に接続すると共に前記基板を演算装置に実装することを含む、請求項1に記載の製造方法。

【請求項5】

コンピュータ可読媒体に記憶された命令を実行することにより前記方法を実施する、請求項1に記載の製造方法。

【請求項6】

第1の再配置層構造体を介して所定の回路構造体に電気的に接続される第1のサイトと、第1の再配置層構造体から分離されている第2の再配置層構造体を介して第1のサイトに接続されたのとは異なる回路構造体に電気的に接続される第2のサイトとが構造的に連ねられた構成の第1の導体構造体を半導体チップ上に形成することと、

第3の再配置層構造体を介して所定の回路構造体に電気的に接続される第3のサイトと、第3の再配置層構造体から分離されている第4の再配置層構造体を介して第3のサイトに接続されたのとは異なる回路構造体に電気的に接続される第4のサイトとが構造的に連ねられた構成の第2の導体構造体を前記半導体チップ上に形成することと、

高分子層を、その一部分が前記第1の導体構造体上に位置づけられ、他の一部分が前記第2の導体構造体上に位置づけられるようにして、前記第1および第2の導体構造体に装着することと、

前記第1の導体構造体上における第1のサイトに、第1のはんだ構造体を、当該はんだ構造体の一部が第1の導体構造体に装着された前記高分子層の上に位置づけられた状態にして形成する一方で、前記第1の導体構造体上における第2のサイトには、はんだ構造体を形成しないようにすることと、

前記第2の導体構造体上に第2のはんだ構造体を形成することとを含む、製造方法。

【請求項7】

前記第1のはんだ構造体を前記半導体チップの接地経路に電気的に接続すると共に前記第2のはんだ構造体を前記半導体チップの電源経路に電気的に接続することを含む、請求項6に記載の方法。

【請求項8】

前記半導体チップを基板に接続すると共に前記基板を演算装置に実装することを含む、請求項6に記載の方法。

【請求項9】

それぞれ異なる回路構造体に電気的に接続され、かつ互いに所定距離を隔てて配置される少なくとも2つの再配置層構造体を有する半導体チップと、

前記半導体チップ上のアンダーバンプメタライゼーション構造体であって、前記少なくとも2つの再配置層構造体のうちの第1の再配置層構造体に電気的に接続される第1のサイトと、第1のサイトに構造的に連なると共に前記少なくとも2つの再配置層構造体のうちの第2の再配置層構造体に電気的に接続される第2のサイトを有するアンダーバンプメタライゼーション構造体と、

前記アンダーバンプメタライゼーション構造体上に配置される高分子層と、

前記アンダーバンプメタライゼーション構造体上における前記第1のサイトに、前記高分子層の上に一部分が位置づけられた状態で配置されるはんだ構造体とを備え、

前記アンダーバンプメタライゼーション構造体上における前記第2のサイトには、はんだ構造体は設けられていない、

ことを特徴とする装置。

【請求項10】

前記少なくとも2つの再配置層構造体は同タイプの電気経路の一部を含み、当該電気経路がグランド、電源、信号のうちの1つに対するものである、請求項9に記載の装置。

10

20

30

40

50

## 【請求項 1 1】

前記アンダーバンプメタライゼーション構造体は、前記少なくとも 2 つの再配置層構造体のうちの前記第 1 の再配置層構造体に電気的に接続される前記第 1 のサイトと、前記少なくとも 2 つの再配置層構造体のうちの前記第 2 の再配置層構造体に電気的に接続される前記第 2 のサイトとを有する導体グリッドを備える、請求項 9 に記載の装置。

## 【請求項 1 2】

前記アンダーバンプメタライゼーション構造体は、ハブと前記ハブに接続された前記第 1 および第 2 のサイトを有するクラスターとを備える、請求項 9 に記載の装置。

## 【請求項 1 3】

前記半導体チップに接続された基板を備える、請求項 9 に記載の装置。 10

## 【請求項 1 4】

前記基板に接続された演算装置を備える、請求項 1 3 に記載の装置。

## 【請求項 1 5】

第 1 の導体構造体を介して所定の回路構造体に電気的に接続される第 1 のサイトと、第 1 の導体構造体から所定距離を隔てて配置される第 2 の導体構造体を介して第 1 のサイトに接続されたのとは異なる回路構造体に電気的に接続される第 2 のサイトとが構造的に連ねられた構成のアンダーバンプメタライゼーション構造体を半導体チップ上に形成すること、

前記アンダーバンプメタライゼーション構造体に高分子層を装着すること、

前記アンダーバンプメタライゼーション構造体上における第 1 の サイト に、はんだ構造体を、当該はんだ構造体の一部が前記高分子層の上に位置づけられた状態にして形成する一方で、前記アンダーバンプメタライゼーション構造体上における第 2 の サイト には、はんだ構造体を形成しないようにすること、

を含む、製造方法。 20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、広義には半導体処理に関し、具体的には半導体ダイの導体構造体およびその製造方法に関する。

## 【背景技術】 30

## 【0002】

従来の集積回路は、2つの相対する主要面で構築された、一般的にはシリコンである半導体材料の長方形の小片から成る半導体基板またはダイ上に実装されることが多い。ダイの能動回路網は、2つの主要面の一方の付近に集中する。能動回路網を収容する面は、通常「能動回路網面」と呼ばれ、能動回路網面の反対側の面は、「バルクシリコン面」と呼ばれることが多い。ダイの熱出力に応じて、ヒートシンク等の伝熱装置をダイのバルクシリコン面上に実装することが望ましい場合がある。この実装はバルクシリコン面上に直接行ってもよいし、ダイの上に位置するリッド上に実装してもよい。

## 【0003】

従来のダイは、通常は、パッケージ基板またはプリント配線基板等のある種の基板上に実装される。ダイと、その下の基板またはボードとの間の電気伝導性は、様々な従来の機構によって確立される。いわゆるフリップチップ構造においては、ダイの能動回路網面は、複数の導体ボールまたはバンプを備え、この複数の導体ボールまたはバンプは、基板または回路基板上に位置する複数の対応する導体パッドとの金属結合を確立するように設計されている。ダイは、能動回路網面が下を向くようにひっくり返され、その下の基板上に載置される。後続の熱処理を行うことによって、バンプとパッドとの必須の金属結合が確立される。フリップチップ実装法の主な利点の1つは、集積回路と基板との電気経路が比較的短いことである。これらの比較的低いインダクタンス経路により、電子デバイスの高速性能が生み出される。 40

## 【0004】

はんだボールを半導体ダイのボンドパッドに電気的に接続する様式は、半導体ダイおよび半導体ダイが実装されるホスト電子デバイスの信頼性に多大な影響を与える。ある従来の技術においては、半導体ダイの能動回路網面上に誘電パッシベーション層を作製し、ボンドパッドの位置に対応する複数の開口と共に誘電パッシベーション層をリソグラフィによりパターニングする。次に、ポリイミド層をパッシベーション層上に作製し、パッシベーション層の開口に対して概ね同心状に位置する複数の開口を用いて、ポリイミド層をリソグラフィによりパターニングする。次に、金属がその下にあるボンドパッドへと下方に達し、ボンドパッドと接着するように、いわゆるアンダーバンプメタライゼーション層をポリイミド層上に堆積させる。従って、ポリイミド層は、アンダーバンプメタル層とパッシベーション層との間に位置する。この配置の重要性を、以下にさらに詳細に説明する。

10

。アンダーバンプメタライゼーション層を形成した後、ボンドパッドの概略位置上に位置する複数の開口を用いて膜またはステンシルをアンダーバンプメタル層上にパターニングし、めっきまたはステンシルペースト法を用いて、はんだ材料を堆積する。ステンシルを除去し、熱処理を行うことにより、はんだ構造体をリフローする。はんだ構造体は、ボール状構造体へと固化する。

#### 【0005】

鉛系はんだは、何十年もの間、半導体装置の製造に広く使用してきた。しかしながら最近になって、チップの製造業者らは、無鉛はんだに目を向け始めた。無鉛はんだ材料は、鉛系はんだと比べて比較的低い延性を有する傾向がある。剛性が増すことにより、特に動作温度が高い場合、または半導体ダイの熱膨張率と半導体ダイが上に実装される基板の熱膨張率とに大きな不一致がある場合に、はんだボールにかなりの応力がかかり得る。従来技術の問題は、ポリイミド層と、アンダーバンプメタライゼーション層と、はんだボールとの相対位置から生じる。ポリイミド層は、基本的に、アンダーバンプメタライゼーション層によってはんだボールから分離されるので、ポリイミド層の応力を低減させる能力を、はんだボールが利用することはできない。従って、はんだボール、特にアンダーバンプメタライゼーション層とのインターフェース付近のはんだボールの端部において、高い機械的応力がはんだボールに与えられ得る。この応力により、はんだボールにクラックが生じる可能性がある。応力が十分に強ければ、はんだボールの機械的故障が生じ、電気装置の故障を生じさせる可能性がある。

20

#### 【0006】

本発明は、1つ以上の上記欠点の影響を克服または低減させることに向けられる。

#### 【発明の概要】

#### 【0007】

本発明のある局面において、半導体ダイの導体パッド上に導体構造体を形成することを含む製造方法を提供する。導体層はある面を有する。導体層のこの面の上に高分子層を形成し、この面の一部が露出したままにする。この面の露出部分および高分子層の一部の上に、はんだ構造体を形成する。

#### 【0008】

本発明の別の局面において、半導体ダイの導体パッド上に導体構造体を形成することを含む製造方法を提供する。導体層はある面を有する。導体層のこの面の上に高分子層を形成し、この面の一部が露出したままにする。この面の露出部分および高分子層の一部の上に、はんだ構造体を形成する。半導体ダイを第1の基板に接続する。

40

#### 【0009】

本発明の別の局面において、ある面を持つ導体パッドを有する半導体ダイを含む装置を提供する。導体パッドには導体構造体が電気的に接続される。導体構造体の面上には高分子層が配置される。高分子層は、導体構造体のこの面の一部に開口部を有する。導体構造体のこの面のこの部分に、はんだ構造体が接続される。

#### 【0010】

本発明の別の局面において、第1の基板に接続される半導体ダイを含む装置を提供する。半導体ダイは、ある面を有する導体パッドを含む。導体パッドには導体構造体が電気的

50

に接続される。導体構造体のこの面上に高分子層が配置され、高分子層は導体構造体のこの面の一部に開口部を有する。導体構造体のこの面のこの部分に、はんだ構造体が接続される。

【0011】

本発明の別の局面において、半導体チップ上に導体構造体を形成することを含む製造方法を提供する。導体構造体は、第1の再配置層構造体に電気的に接続される第1のサイトおよび第2の再配置層構造体に電気的に接続される第2のサイトを有する。導体構造体上には、はんだ構造体を形成する。

【0012】

本発明の別の局面において、半導体チップ上に第1の導体構造体を形成することを含む製造方法を提供する。第1の導体構造体は、第1の再配置層構造体に電気的に接続される第1のサイトおよび第2の再配置層構造体に電気的に接続される第2のサイトを有する。半導体チップ上に第2の導体構造体を形成する。第2の導体構造体は、第3の再配置層構造体に電気的に接続される第3のサイトおよび第4の再配置層構造体に電気的に接続される第4のサイトを有する。第1の導体構造体上に第1のはんだ構造体を形成すると共に、第2の導体構造体上に第2のはんだ構造体を形成する。

【0013】

本発明の別の局面において、半導体チップ上に導体構造体を形成することを含む製造方法を提供する。導体構造体は、ある再配置層に電気的に接続される複数のサイトを有する。導体構造体上において複数のサイトのうちの1つのサイトの近傍に少なくとも1つのはんだ構造体を形成する。

【0014】

本発明の別の局面において、少なくとも2つの再配置層構造体を有する半導体チップを含む装置を提供する。半導体チップ上に導体構造体がある。導体構造体は、少なくとも2つの再配置層構造体のうちの第1の再配置層構造体に電気的に接続される第1のサイトおよび前記少なくとも2つの再配置層構造体のうちの第2の再配置層構造体に電気的に接続される第2のサイトを有する。導体構造体上にはんだ構造体がある。

【図面の簡単な説明】

【0015】

本発明の上記および他の利点は、以下の詳細な説明を読むことにより、および図面を参考することにより明らかとなるであろう。

【0016】

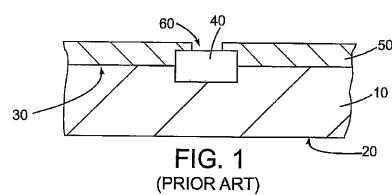

【図1】図1は、ボンドパッドおよびパッシベーション層を有する従来の半導体ダイの断面図である。

【0017】

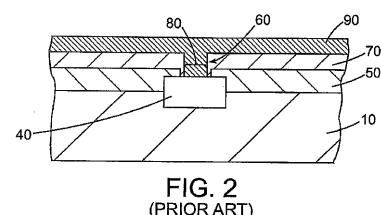

【図2】図2は、ポリイミドおよびメタル層の堆積後の従来の半導体ダイの断面図である。

【0018】

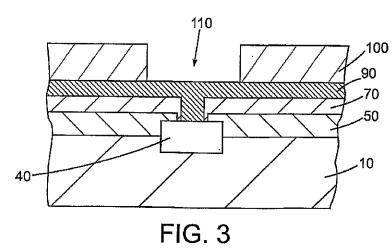

【図3】図3は、マスク形成後の従来の半導体ダイの断面図である。

【0019】

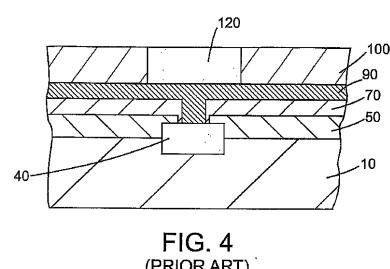

【図4】図4は、はんだ堆積後の従来の半導体ダイの断面図である。

【0020】

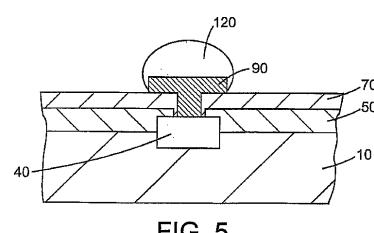

【図5】図5は、バンプを構築するためのはんだリフロー後の従来の半導体ダイの断面図である。

【0021】

【図6】図6は、フリップチップ実装後の従来の半導体ダイの断面図である。

【0022】

【図7】図7は、拡大して図示した図6の断面図の一部である。

【0023】

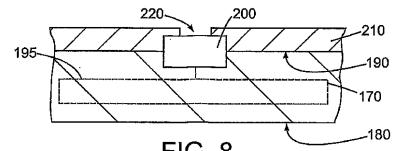

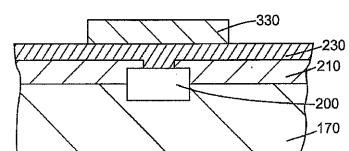

【図8】図8は、パッシベーション層の形成後の半導体ダイの例示的実施形態の断面図で

10

20

30

40

50

ある。

【0024】

【図9】図9は、メタル層および絶縁層の形成を図示する半導体ダイの例示的実施形態の断面図である。

【0025】

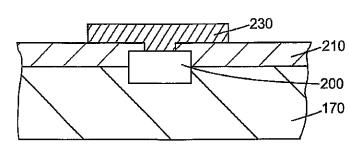

【図10】図10は、その上にマスクを形成したことを図示する半導体ダイの例示的実施形態の断面図である。

【0026】

【図11】図11は、その上に導体構造体を形成したことを図示する半導体ダイの例示的実施形態の断面図である。

10

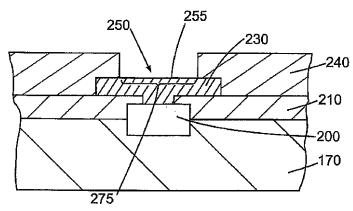

【0027】

【図12】図12は、導体構造体のリフローを図示する半導体ダイの例示的実施形態の断面図である。

【0028】

【図13】図13は、基板への実装例を図示する半導体ダイの例示的実施形態の断面図である。

【0029】

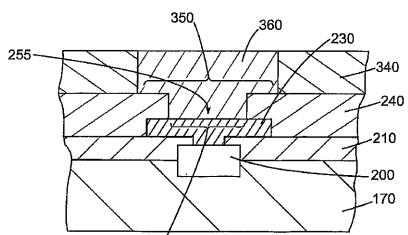

【図14】図14は、その上にパッシベーション、メタル層、およびマスクを形成したことを図示する半導体ダイの代替例示的実施形態の断面図である。

【0030】

20

【図15】図15は、マスクおよびメタル層の一部を除去することを図示する半導体ダイの代替例示的実施形態の断面図である。

【0031】

【図16】図16は、その上に絶縁層を形成したことを図示する半導体ダイの代替例示的実施形態の断面図である。

【0032】

【図17】図17は、その上に導体構造体を形成したことを図示する半導体ダイの代替例示的実施形態の断面図である。

【0033】

【図18】図18は、導体構造体のリフローを図示する半導体ダイの代替例示的実施形態の断面図である。

30

【0034】

【図19】図19は、複数のバンプ構造体および共通メタル層を備えた半導体ダイの別の代替例示的実施形態の絵図である。

【0035】

【図20】図20は、実装の構成例を図示した例示的半導体ダイの分解絵図である。

【0036】

【図21】図21は、複数の導体ボールが見えるように底面側を上にした例示的な従来の半導体チップの絵図である。

【0037】

40

【図22】図22は、図21に図示した従来の半導体チップのごく一部分を拡大した絵図である。

【0038】

【図23】図23は、複数のはんだ構造体が見えるように底面側を上にした半導体チップの例示的実施形態の絵図である。

【0039】

【図24】図24は、図23に図示した半導体チップの一部分の拡大絵図である。

【0040】

【図25】図25は、図23に図示した半導体チップの別の一部分の絵図である。

【0041】

50

【図26】図26は、図23に図示した半導体チップの別的一部分の平面図である。

【0042】

【図27】図27は、図23に図示した半導体チップの別的一部分の平面図である。

【0043】

【図28】図28は、半導体チップの代替例示的実施形態のごく一部分の平面図である。

【0044】

【図29】図29は、断面29-29における図28の断面図である。

【0045】

【図30】図30は、様々な特徴が見えるように基板から例示的半導体チップを剥がした場合の絵図である。

10

【発明を実施するための形態】

【0046】

以下に説明する図面において、2つ以上の図面で同一の構成要素が出てくる場合には、概ね同じ参照符号を使用する。本明細書中に開示する例示的実施形態を説明する前に、従来のはんだバンプメタライゼーション設計の構造および製造を簡単に見直すことが有益であろう。次に図面、特に図1～5を参照すると、半導体チップ10の下面に導電性はんだバンプを形成するための従来の製造工程例が示されている。図解を簡略化するために、図1～5では、半導体装置10の比較的小さな部分に注目している。初めに図1を参照すると、半導体装置10は、2つの相対する面20および30を有する。面20は、裏面と呼ばれることが多く、反対側の面30は、時に前面と呼ばれる。能動チップ回路網(図示せず。)は、一般的に、前面30の近傍の1つまたは複数の層に位置する。ボンドパッド40は、面30の近傍に設けられ、装置10の回路網から後に形成されるはんだバンプを通して電気経路を設けて、装置10の外部の回路網との電気伝導性を確立するように設計されている。装置10の複雑さに応じて、このようなボンドパッド40が多数存在し得る。窒化ケイ素のパッシベーション層50は、面30上に形成され、開口60がボンドパッド40にまで延びるようにパターニングされる。パッシベーション層50は、金属材料が半導体装置10の内部へと下に拡散することを防止するように設計されている。

20

【0047】

次に図2を参照すると、パッシベーション層50、ボンドパッド40および半導体装置10から成るスタック上にポリイミド層70が形成される。パッシベーション層50における開口60と同心状に位置する開口80を有するポリイミド層70が形成される。ポリイミドを選択する理由は、有利な構造上の柔軟性および電気絶縁性を共に提供するその能力にある。ポリイミド層70を塗布した後、ポリイミド層70の上と、その内部の開口80を通る下方へとメタライゼーション層90を形成し、それによってボンドパッド40とオーミックコンタクトをとる。メタライゼーション層90を、アンダーバンプメタライゼーション層またはUBM層と呼ぶ場合がある。UBM層90は、チタン、銅、およびニッケル等の異なる金属材料を連続させたスタックとして堆積されることもある。

30

【0048】

図3に示すように、メタライゼーション層90、ポリイミド層70、パッシベーション層50、ボンドパッド40および装置10から成るスタック上に絶縁膜100が形成される。メタライゼーション層90の一部分を露出する開口110を膜100でパターニングする。膜100は、最終的にはんだバンプへと形作られる導体材料が開口110に後で堆積されることが可能となるように、マスク、またはステンシルプロセスが用いられる場合にはステンシルとして機能するように設計されている。開口110は、一般的には、リソグラフィーパターニングプロセスによって形成される。

40

【0049】

次に図4を参照すると、膜100の開口110内およびメタライゼーション層90の露出部分上に導体材料120が堆積されるように、半導体装置10にめっき処理が施される。導体材料は、一般的に、メタライゼーション層90とオーミックコンタクトをとるはんだである。従来のはんだは、スズ-鉛混合物から成る。より最近の新しい方法によれば、

50

スズ-銅はんだ等の無鉛はんだが使用される。ポリイミド層70およびパッシベーション層は、導体120およびメタライゼーション層90から装置10内へと材料が拡散することを抑制する。ボンドパッド40は、めっきの影響を受けない。

#### 【0050】

図4に図示した膜100を除去し、図5に図示するように半導体装置10に対して熱リフロープロセスを行い、導体材料120を円形のバンプへとリフローする。はんだリフロープロセスに続いて、はんだバンプ120の横に位置するメタライゼーション層90の部分をウェットエッチングによってエッチング除去する。この時点で、はんだバンプ120と、メタライゼーション層90と、その下のボンドパッド40との間にオーミック経路が存在する。パッシベーション層50およびポリイミド層70は、所定の位置に残存する。

10

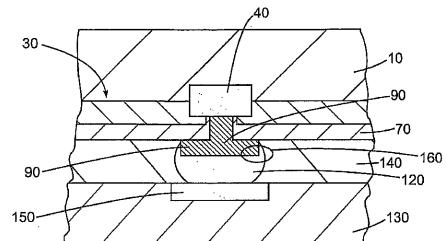

#### 【0051】

本明細書の背景の項に記載したように、メタライゼーション層90の下にポリイミド層70を配置することには、半導体装置10を別の装置にフリップチップ実装する際に明らかとなる重大な悪影響がある。この点について、図6は、他の基板130上に半導体装置10を面30が下を向くようにしてフリップチップ実装した場合の断面図を示す。アンダーフィル材料140をポリイミド層70と基板130との間に配置することにより、電気装置130と半導体装置10との熱膨張率の違いによる応力を低減する。半導体装置10のはんだバンプは、装置130の対応するボンドパッド150上に位置する。このように、メタライゼーション層90およびはんだバンプ120を介して、装置10のボンドパッド40と装置130のボンドパッド150との間に電気経路を確立する。はんだバンプ120、アンダーフィル層140およびメタライゼーション層90のごく一部分を、小橋円形160で囲んでいる。橋円形160で囲んだ部分を、図7に拡大して示す。

20

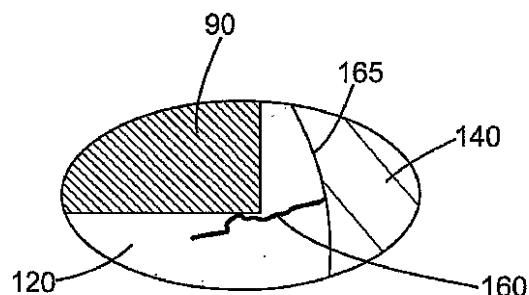

#### 【0052】

図7は、メタライゼーション層90とはんだバンプ120との間の図6に図示したポリイミド層70の配置の欠点を示している。アンダーフィル材料140との境界線165からははんだバンプ120の中心部分へと延びるクラック160が、はんだバンプ120中に図示されている。クラック160は、無鉛はんだバンプ120が比較的堅固であることや、そのクラック160が形成されている場所からのポリイミド層70の相対距離が原因となって、熱応力が十分に補償されなかつたために生じたものである。クラック160は、はんだバンプ120の幅全体にわたって進み、開回路を作り得る。

30

#### 【0053】

上記の従来のプロセスの落とし穴を克服する例示的な新規の製造プロセスは、はんだバンプの形成につながる様々な工程段階を経ている集積回路または半導体装置170の連続する断面図を示す図8～12を次に参照することにより理解され得る。図8～12は、装置170のごく一部分のみを図示していることを理解されたい。半導体装置170は、例えば、マイクロプロセッサ、グラフィックプロセッサ、特定用途向け集積回路、メモリ素子等の電子機器に用いられる無数の異なる種類の回路装置のいずれでもよく、シングルまたはマルチコアでもよい。

#### 【0054】

構造的に言えば、装置170は、相対する面180および190を有する。破線ボックス195で模式的に表した装置回路網は、面190近傍に配置されてもよい。回路網195を外部装置と電気的に接続するためには、半導体装置170は、面190近傍に位置する複数の導体またはボンドパッドを備えていてもよく、そのうちの1つが図示され、200の参照符号が付されている。半導体装置170の複雑さおよびサイズに応じて、多数のパッド200が存在し得る。ボンドパッド200は、アルミニウム、銅、銀、金、チタン、耐火金属、耐火金属化合物、これらの合金等の様々な導体材料から構成され得る。ボンドパッド200は、めっき、物理蒸着または他の材料堆積技術によって形成してもよい。

40

#### 【0055】

パッシベーション層210を、開口220と共に面190上に形成する。パッシベーション層210は、金属または他の材料が半導体装置170の内部へと下に拡散することを

50

阻止するように設計されている。層 210 は、例えば、窒化ケイ素、二酸化ケイ素、様々なケイ酸塩ガラス等の様々な絶縁材料から構成され得る。開口 220 は、周知のリソグラフィーパターニングおよびエッチング技術を用いて形成してもよい。

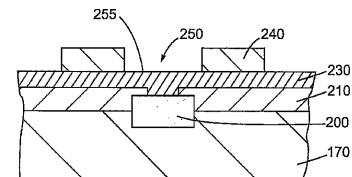

#### 【0056】

図解を簡略化するために、残りの図面は、回路網 195 を含んでいない。次に、図 9 に注目する。導体またはメタル層 230 を、パッシベーション層 210 の上、およびその開口 220 の内部に形成し、それによって、ボンドパッド 200 とのオーミックコンタクトをとる。メタライゼーション層 230 は、ボンドパッド 200 と、後に形成されるはんだ構造体（図示せず。）との導電性インターフェースを提供するように設計されている。メタライゼーション層 230 は、アルミニウム、銅、銀、金、チタン、耐火金属、耐火金属化合物、これらの合金等の様々な導体材料から構成され得る。単一構造の代わりに、層 230 は、チタン層、その次にニッケル-バナジウム層、その次に銅層といった複数のメタル層の積層で構成されていてもよい。別の実施形態では、チタン層は、銅層で覆われ、その次に、ニッケルでトップコーティングされていてもよい。しかしながら、当業者であれば、多種多様の導電性材料をメタライゼーション層 230 に使用し得ることを理解するであろう。物理蒸着、化学蒸着、またはめっき等の金属材料を用いるための様々な周知の技術を用いることができる。なお、追加の導体構造体が、メタル層 230 と導体パッド 200 との間に介在され得ることを理解されたい。

#### 【0057】

メタライゼーション層 230、パッシベーション層 210、パッド 200 および半導体装置 170 から成るスタックの上に絶縁膜 240 を堆積する。絶縁膜 240 は、メタル層 230 の表面 255 の上に位置する。層 240 は、パッシベーションを提供することと、半導体装置 170、メタライゼーション層 230 および後に形成されるはんだバンプ（図示せず。）の熱膨張の差異に対する緩衝を提供することとを目的としている。絶縁層 240 の材料例には、例えば、ポリイミドおよびベンゾシクロブテン等の高分子材料等、または窒化ケイ素等の他の絶縁材料が含まれる。スピンドルコーティング、化学蒸着、または他の堆積プロセスを用いてもよい。メタライゼーション層 230 の一部分を露出する開口 250 を有するように、絶縁層 240 をリソグラフィによりパターニングする。なお、図 1～5 に図示した従来技術の場合ではメタライゼーション層 90 の下に位置したこととは対照的に、絶縁層 240 は、メタライゼーション層 230 の上に位置する。この配置により、以下により詳細に説明するような構造的利点がもたらされる。

#### 【0058】

次に、図 10 に注目する。絶縁層 240、メタライゼーション層 230、パッシベーション層 210、パッド 200 および半導体装置 170 から成るスタックの上に、マスク膜 260 を堆積する。マスク膜 260 は、絶縁層 240 における開口 250 と同心の開口 270 と共にリソグラフィによりパターニングされる。開口 250 および 270 は共に、メタル層 230 の表面 255 の露出した部分 275 をそのままの状態にしておく。後続のプロセスにおいて、導体材料を一体化した開口 250 および 270 内に配置し、それによって、メタライゼーション層 230 と、その下の装置 170 のボンドパッド 200 とのオーミックコンタクトをとる。膜 260 は、例えば、フェノール樹脂、溶融シリカおよび合成ゴムを有するゴム変性エポキシ樹脂（a rubberized epoxy resin）から作られていてよい。任意に、金属塗布マスクに適した他の材料を使用してもよい。

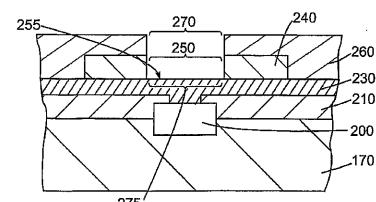

#### 【0059】

図 11 に図示するように、半導体装置 170 は、めっき処理を受け、それによって、開口 250 および 270 の中と、メタライゼーション層 230 の表面 255 の露出部分 275 の上とに、導体材料 280 を堆積する。膜 260 は、この堆積プロセスに対するマスクとして機能する。導体 280 は、要望に応じて、鉛系はんだ、または無鉛でもよい。材料例には、例えば、スズ-銅、スズ-銀、または他のはんだ材料が含まれる。導体材料 280 は、絶縁層 240 に接する。この時点では、ボンドパッド 200 と、メタライゼーション層 230 と、導体材料 280 との間に導電性経路が存在する。パッシベーション層 21

10

20

30

40

50

0は影響を受けない。もちろん、別の1つまたは複数の導体(不図示)が、導体280とボンドパッド200との間に位置し、所望のオーミック経路をさらに提供してもよい。

#### 【0060】

図12に示すように、図11に図示した膜260を除去し、リフロー・プロセスを行い、それによって、導体280をボールまたはバンプ状の構造体へとリフローする。ある例示的実施形態においては、半導体装置170を、約10～120秒間、約170～190にまで加熱してもよい。リフローの適切なパラメータは、導体材料280の組成によって決まる。メタライゼーション層230の不要部分は、化学エッチングプロセスによって除去する。従って、導体280の側方にあるパッシベーション層210の部分が露出する。導体280とバンプボンドパッド200との間に、メタライゼーション層230を介して導電性経路が存在する。なお、導体280は、絶縁層240の部分285上に位置する。部分285は、導体280の周辺隅部287に対して応力低減インターフェースを提供する。

#### 【0061】

絶縁層240の新しい配置の利点は、装置170を別の基板に実装した場合に明白となる。次に、別の電気装置290上に実装した半導体装置170を図示した図13に注目する。電気装置290は、プリント配線基板、または要望に応じて他の電気装置でもよい。図13は、装置170をひっくり返して電気装置290上に実装することにより、はんだ構造体280が電気装置290のボンドパッド300上に載置されるフリップチップ実装の構成を図示する。装置290は、このようなパッド300を多数含むことにより、装置170の対応するバンプ280を受け得ることを理解されたい。所望であれば、パッド300には、後続のリフロー中に1つまたは複数のはんだ構造体280と融合するように設計された小はんだバンプ(図示せず。)が設けられていてもよい。アンダーフィル材料310は、装置170と電気装置290との間に分散し、それによって、装置170および装置290の熱膨張率の差異の影響を低減する。アンダーフィル310は、例えば、シリカフィラーおよびフェノール樹脂を混合したエポキシ樹脂でもよい。絶縁層240は、メタライゼーション層230とはんだ構造体280との間に位置するので、図6および7に図示した従来の構造に関連して起こるような熱応力および割れに対して、さらなる柔軟な緩衝効果が、はんだバンプ280の隅部320にもたらされる。なお、隅部320は、はんだ構造体280の全周囲にわたって延びている。

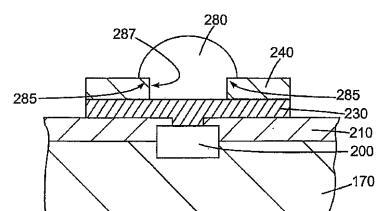

#### 【0062】

上記の例示的実施形態では、めっき処理を用いて、はんだ構造体280を形成してもよい。図14～18に図示する代替のプロセス例においては、ステンシルプロセスを用いて、はんだ構造体を構築してもよい。初めに図14を参照すると、本明細書の他の箇所に記載したように半導体装置170を処理することにより、ボンドパッド200、パッシベーション層210およびメタライゼーション層230を設け得る。この段階で、レジストまたは他のマスク材料によるエッチマスク330をメタライゼーション層230の上に形成し、メタライゼーション層230に対してエッチングを行い、それによって、図15に示すように、ボンドパッド200の側方にあるメタライゼーション層230の部分を削り、パッシベーション層210の一部を露出させる。エッチマスク330は、アッシングまたは溶媒剥離等によって除去してもよい。上から見ると、メタライゼーション層230は、円形または要望に応じた別の形状でもよい。ボンドパッド200は、エッチングまたはマスク剥離の影響を受けない。

#### 【0063】

図16に示すように、本明細書中の他の箇所に概して記載したように、メタライゼーション層230、パッシベーション層210、ボンドパッド200および半導体装置170から成るスタック上に絶縁層240を形成する。絶縁層240は、メタライゼーション層230に通じ、メタライゼーション層の表面255に露出部分275を残す前述の開口250を有する。

#### 【0064】

10

20

30

40

50

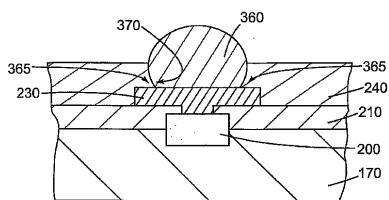

次に図17を参照すると、絶縁層240、メタライゼーション層230、パッシベーション層210、ボンドパッド200および半導体装置170から成るスタック上にステンシル340を形成する。ステンシル340は、メタライゼーション層230および絶縁層240の一部の上に開口350を有する。ステンシル340は、例えば、フェノール樹脂、溶融シリカおよび合成ゴムを有するゴム変性エポキシ樹脂(a rubberized epoxy resin)から作成してもよい。任意に、金属塗布ステンシルに適した他の材料を使用してもよい。導体ペースト360をステンシル340の開口350内に圧入する。導体ペースト360は、メタル層230の表面255の露出部分275および絶縁層240の部分365の上に位置する。ペースト360は、本明細書中の他の箇所に記載したはんだバンプ280に使用するのと同じ材料から構成されていてもよい。もちろん、別の1つまたは複数の導体(図示せず。)が、導体360とボンドパッド200との間に位置し、所望のオーミック経路をさらに提供していてもよい。

#### 【0065】

プロセスを完了するために、ステンシル340を除去し、熱リフロー・プロセスを行い、図18に示すように、パッド200と金属的に接着するバンプへと導体ペースト360を再形成する。ある例示的実施形態では、半導体装置170を、約10~120秒間、約170~190にまで加熱してもよい。リフローの適切なパラメータは、導体ペースト360の組成によって決まる。パッシベーション層210は影響を受けない。導体360は、絶縁層240の部分365の上に位置する。上記の実施形態と同様に、絶縁層240により、はんだバンプ360の周辺隅部370に対して、構造的保護が強化される。

#### 【0066】

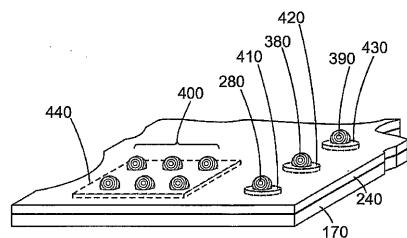

はんだバンプ280、360等に対する構造的保護が向上することに加え、本明細書に開示するような絶縁層240の配置により、アンダーバンプメタライゼーション層230を電気配線構造体として機能させることが可能となる。例示的実施形態は、次の図19を参照することにより理解され得る。この図19は、絶縁層240および上を向いた数個のバンプと共に配置された半導体装置170の一部の絵図である。図8~12と同様に、バンプの1つに参照符号280を付している。別の2つのバンプには、参照符号380および390をそれぞれ付している。6つのバンプから成る一群には、参照符号400を集合的に付している。バンプ280、380および390を形成し、本明細書に開示する技術を用いて構造的に分離させた別個のアンダーバンプ導体構造体またはメタル層410、420および430を設けてもよい。メタル層410、420および430は、絶縁層240で覆われるので、破線で示している。しかしながら、バンプの一群400は、本明細書に開示する技術を用いて形成され得るが、共通アンダーバンプ導体構造体またはメタル層440を有する。共通アンダーバンプ導体構造体またはメタル層440は、絶縁層240で覆われるので、同様に破線で示される。従って絶縁層240は、バンプ400の形成前にはメタル層440の複数の部分を露出させる複数の開口を有して形成される。この様に、メタル層440は、バンプの一群400に対する配線構造体として機能できる。このことは、数個のバンプが一時的または恒久的に電源または接地等の一種類の入出力専用である場合に有利になり得る。絶縁層240は、バンプの一群400とメタライゼーション層440との間に位置するため、リフロー中にははんだが側方に漏れだして望ましくない短絡をおこす危険性なしに、選択されたバンプをつなぐことができる。もちろん、バンプの数およびグループ分けや、1つまたは複数の共通アンダーバンプメタライゼーション層440の成形には、様々なバリエーションがある。

#### 【0067】

ウェーハ上に配置される複数のダイに対して、本明細書に開示するプロセス例を同時に用い得ることを当業者は理解するであろう。その後、シンギュレーションを行ってもよい。任意で、シンギュレーション後に個々のダイを処理してもよい。

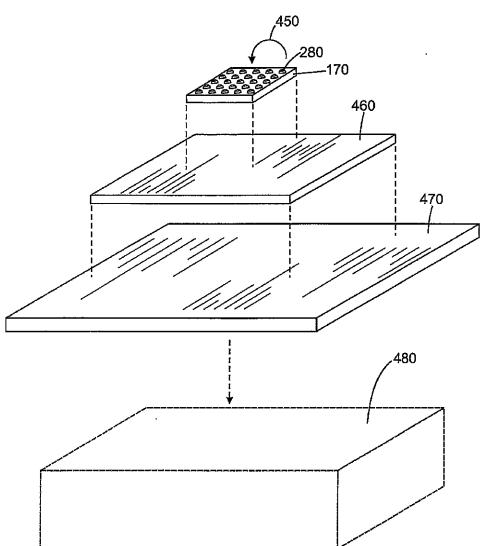

#### 【0068】

半導体装置170は、様々な方法で実装することができる。図20は、実装可能例を幾つか示した分解絵図である。半導体装置170は、上を向いたはんだバンプ280と共に

10

20

30

40

50

図示されている。装置 170 は、矢印 450 で示すようにひっくり返され、基板 460 の上にフリップチップ実装されてもよい。基板 460 は、パッケージ基板、プリント配線基板または他の種類の基板でもよい。パッケージ基板として構成される場合には、基板 460 は、ピングリッドアレイ、ボールグリッドアレイ、ランドグリッドアレイ、表面実装または他の種類の構成でもよい。基板 460 は、別の基板 470 に実装してもよい。基板 470 は、プリント配線基板または他の種類の基板でもよい。例えば、基板 470 は、コンピュータシステムのマザーボードでもよい。半導体装置 170 は、破線ボックス 480 で表される演算装置等のより大きなシステムに含まれ得る。演算装置 480 には、例えば、デジタルテレビ、ハンドヘルドモバイル機器、パーソナルコンピュータ、サーバー、メモリ素子、グラフィックスカード等の拡張ボード、または半導体を用いたその他の演算装置が含まれ得る。

#### 【0069】

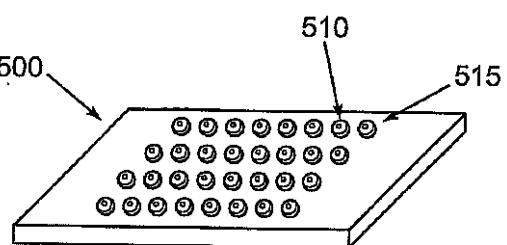

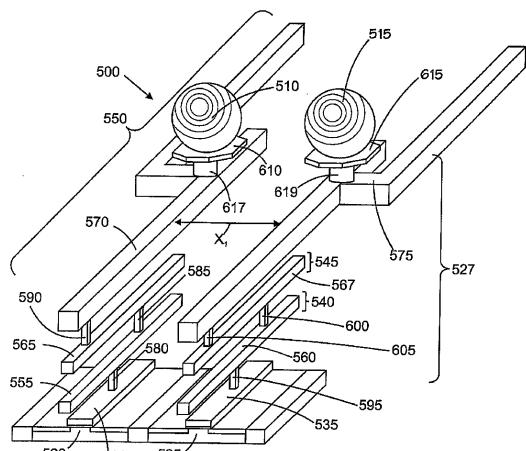

上に説明した図 19 では、電気配線に UBM 構造体を使用した例を示した。UBM 配置を用いた複雑な配線の数例を図 23 ~ 30 に図示する。これらの図面の説明を始める前に、入出力にはんだ構造体を利用する半導体チップの従来の電気配線設計の簡単な再確認が有益であろう。図 21 は、複数の導体ボールが見えるように底面側を上に配置させた従来の例示的な半導体チップ 500 の絵図である。ボールの 2 つに参照符号 510 および 515 を付している。プリント配線基板（図示せず。）へ実装する際に、チップ 500 をひっくり返すことにより、ボール 510、515 等が下を向き、プリント配線基板上の対応するはんだ構造体との金属接続が確立される。はんだボール 510、515 等は、図 21 には示されていないチップ 500 の本体における様々な回路構造体と相互接続される。しかしながら、はんだボール 510 および 515 とチップ 500 における回路構造体との相互接続構造体例の幾つかを、図 22において、はるかに大きく拡大して示す。

#### 【0070】

次に図 22 に注目する。図 22 は、図 21 に図示する 2 つのはんだボール 510 および 515、並びに、はんだボール 510 および 515 からチップ 500 における 2 つの例示的な従来の電子デバイス 520 および 525 へと下方につながる一般的な相互接続構造体を示した絵図である。はんだボール 510 および 515 と、電子デバイス 520 および 525 との間の領域 527 に存在する様々な絶縁層は、デバイス 520 および 525 と、ボール 510 および 515 との電気相互接続体の詳細が明瞭に目に見えるように図示されていないことを理解されたい。電子デバイス 520 および 525 は、それぞれのゲート 530 および 535 を有する電界効果トランジスタとして図示されている。2 つのメタライゼーション層 540 および 545 と、再配置層（RDL）550 とは、はんだボール 510 および 515 と、電子デバイス 520 および 525 との間に設けられる。メタライゼーション層 540 は、複数のメタル配線から成り、そのうちの 2 つを図示し、参照符号 555 および 560 を付している。メタライゼーション層 545 も同様に複数のメタル配線から成り、そのうちの 2 つを図示し、参照符号 565 および 567 を付してあり、RDL 550 は、複数のメタル配線から成り、そのうちの 2 つを図示し、参照符号 570 および 575 を付している。メタル構造体 555 は、コンタクト 580 を介して、デバイス 520 のゲート 530 と電気的に接続される。メタル構造体 555 および 565 は、ビア 585 によって電気的に接続され、RDL 構造体 570 は、ビア 590 を介して、メタル層構造体 565 と電気的に接続される。コンタクト 595 および 2 つのビア 600 および 605 を設けることにより、RDL 構造体 575 をデバイス 525 のゲート 535 に電気的に連結する。はんだボール 510 および 515 は、それぞれの UBM ボールまたはボンドパッド 610 および 615 と、導体エクステンション 617 および 619 とを介して、それぞれの RDL 構造体 570 および 575 と電気的に接続される。

#### 【0071】

RDL 550 は、はんだボール 510 および 515、並びに図 21に示す他のはんだボールの配線およびレイアウトにさらなる柔軟性を提供するように設計される。はんだボールは一般的に、初期のミスアライメントまたは熱リフロー中の流出および結果的に生じ

10

20

30

40

50

る短絡の多少の危険性を有して製造されるので、このような相互間の悪影響や短絡の可能性を減らすために、RDL550のRDL構造体570と575との間に、一定の最小ピッチX<sub>1</sub>が維持されなければならない。

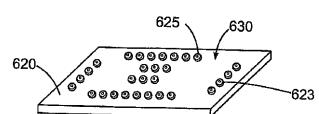

【0072】

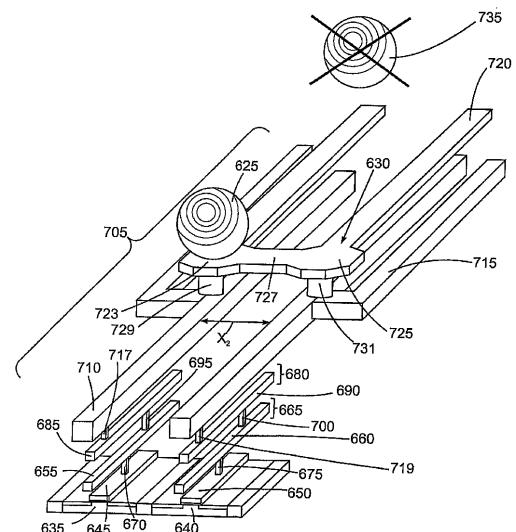

複雑な配線のためにUBM層を組み込んだ半導体チップまたは装置の例示的実施形態は、次に図23および24を参照することにより理解され得る。図23は、そのうちの2つに623および625の参照符号を付した複数のはんだ構造体が見えるように底面側を上に示した半導体チップまたは装置620の例示的実施形態の絵図である。チップ620は、数十、数百、または数千のはんだ構造体を有し得る。しかしながら、図解の簡略化のために、図23においては、このようなはんだ構造体をほんの少しだけ図示している。なお、630の参照符号が付された位置に、はんだ構造体は存在しない。この削除の重要性は、図24に関連して詳細に説明する。半導体装置620は、例えば、マイクロプロセッサ、グラフィックプロセッサ、特定用途向け集積回路、メモリ素子等の電子機器に用いられる無数の異なる種類の回路装置のいずれでもよく、シングルまたはマルチコアでもよい。

10

【0073】

次に図24に注目する。図24は、図23に図示したはんだ構造体625および半導体チップ620の位置630の両方を、チップ620から取り外した状態で、絵の形態で、より大きく拡大して図示する。半導体チップ620中のおそらく何百万という回路装置のうちの2つを図24に図示し、635および640の参照符号をそれぞれ付している。回路装置635および640は、電界効果トランジスタとして図示しているが、集積回路に用いられる無数の異なる種類の回路装置のいずれでもよい。トランジスタ635および640は、それぞれゲート645, 650を有し、これらのゲート645, 650は、コンタクト670および675を介して、メタライゼーション層665のそれぞれのメタル配線655および660に接続される。第2のメタライゼーション層680は、ビア695および700を介して、メタル層665に接続されるメタル配線685および690から成る。2つのメタライゼーション層665および680のみが図示されているが、半導体チップ620の複雑さ次第で、さらに多くのメタライゼーション層が存在し得る。

20

【0074】

複数のRDL構造体（そのうちの2つを図示し、710および715の参照符号を付している）で構成されるRDL705を設けることにより、はんだボール623（図23を参照）および625と、その下の回路装置との間に電気配線を確立する。RDL705は、比較的大きなサイズおよび/または選択的に低い抵抗損をもたらす他の特性を有するように有利に製造された多数の導体配線から有利に構成されている。RDL構造体710は、ビア717を介してメタル配線685に接続され、RDL構造体は、ビア719を介してメタル配線690に接続される。ここまででは、図24に図示した構造は、図22に図示した従来のはんだボールおよび電気配線の構造とほぼ同一である。しかしながら、この例示的実施形態においては、より広大なUBM層の一部であり得る導体またはUBM構造体720が、はんだボール625とRDL構造体710および715との間に介在し、それらと電気的に接続している。UBM構造体720は、横材727によってつながれたパッドまたはサイト723および725を含み、これらは、2つのエクステンション部材729および731によってそれぞれRDL構造体710および715に接続されている。この様に、通常であればパッドRDL構造体715に対する入出力を提供するためにパッド725の上の位置630に配置されるべきはんだボール735を削除することができる。はんだボール735を削除し得るので、図22に図示した従来の構造の最小ピッチX<sub>1</sub>より小さくなり得る最小ピッチX<sub>2</sub>をもって、RDL構造体710および715を互いにより近づけることができる。UBM構造体720のパッドサイト723および725は、トランジスタ635および640のゲート645および650に共通して電気的に接続される。従って、UBM構造体720は、例えば、場合によっては電源、接地、または信号といった同じ種類の電気信号専用のボール/バンプサイトを共通してつなげるために使用されるべきである。UBM構造体720は、単純な馬蹄形装置として図示されているが、U

30

40

50

B M構造体 720 は、多種多様の異なる形状を呈していてもよく、図23において半導体チップ620上に図示した様々な導体バンプを様々な方法でつなげるために使用される同様のU B M構造体を多数備えていてもよいことを理解されたい。U B M構造体720は、本明細書中の他の箇所に開示した技術および材料を用いて製造され得ることを理解されたい。

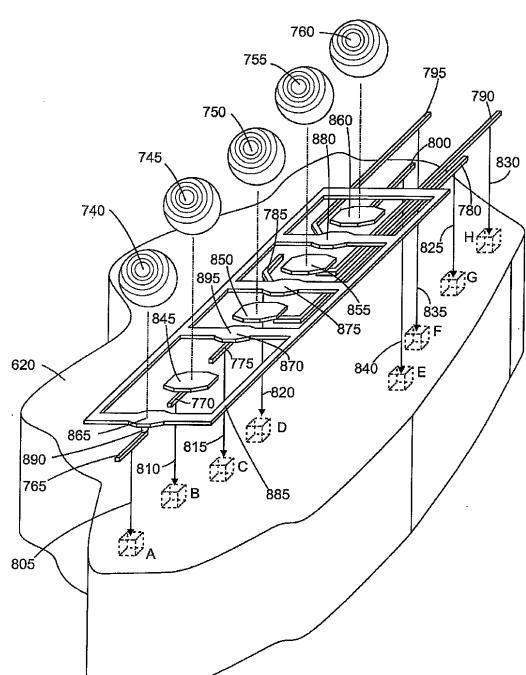

#### 【0075】

次に図25に注目する。図25は、図23に図示した半導体チップ620のごく一部を、チップ620から分解した状態の数個のはんだボール740、745、750、755および760と共に示した絵図である。半導体チップ620の無数の内部回路構造体の数個を、模式的に破線ボックスA、B、C、D、E、F、GおよびHで表している。回路構造体A、B、C、D、E、F、GおよびHは、例えば、電源レール、接地レール、コンデンサ、より大きな集積回路機能ブロック、メモリ素子、プロセッサコアまたは実質的に半導体チップに利用されるどのようなものでもよい。回路構造体A、B、C、D、E、F、GおよびHは、矢印線805、810、815、820、825、830、835および840によって模式的に表したそれぞれの相互接続体を介して、それぞれのRDL構造体765、770、775、780、785、790、795および800に電気的に接続されている。相互接続体805、810、815、820、825、830、835および840は、図24に図示した複数のメタライゼーション層665および680等の、1つまたは複数のメタライゼーションまたは他の導体材料の層から構成され得る。導体パッド845、850、855および860は、RDL構造体770、780、790および800にそれぞれ接続される。はんだボール745、750、755および760は、導体パッド845、850、855および860に実装される。

#### 【0076】

導体パッド865、870、875および880は、RDL構造体765、775、785および795にそれぞれ接続されている。導体パッド865、870、875および880は、電気的に共につながれ、格子状構造体として構築されるU B M構造体885の一部として製造される。U B M構造体885は、それぞれのエクステンション（そのうちの1つは、パッドサイト865近傍に見えており、参照符号890が付されている）によって、その下のRDL構造体765、775、785および795に接続され得る。実際には、パッド845、850、855および860は、図示されていない同様のエクステンションを使用し得る。はんだボール740は、パッド865においてU B M構造体885に接続されている。この様に、はんだボール740を介した電気入出力が、ボンドパッド865、870、875および880の全てと、結果的にその下の回路構造体A、C、DおよびFとに与えられる。U B M構造体885の格子状構造は、簡単にリソグラフィによりパターニングすることが可能で、かつ周知の技術を用いて形成することが可能な比較的単純なレイアウトであるという利点を持つ。さらに、このような構造により、比較的効率的に電流が運ばれ、その結果、抵抗損が比較的小さい。導体パッド865、870、875および880は全て、共通して接続され、U B M構造体885の一部であるので、これらのボンドパッドは、一般的には、接地、電源または信号等のある特定の種類の電気入出力専用となる。その他のパッド845、850、855および860は、場合によっては電源、接地、または信号のための入出力として接続され得る。もちろん、全てのパッド845、850、855、860、865、870、875および880は、製造を簡略化するために、同一平面上に作製してもよい。

#### 【0077】

U B M構造体885により、通常であればパッド870、875および880においてパッドに配置されるべきはんだボールを削除することが可能となる。従って、残りのはんだボール740、745、750、755および760の全体的な配置が、それに応じてコンパクトになり得る。

#### 【0078】

開示したU B M構造体と共に利用できる潜在的な配線に関して、かなりの柔軟性が想定

10

20

30

40

50

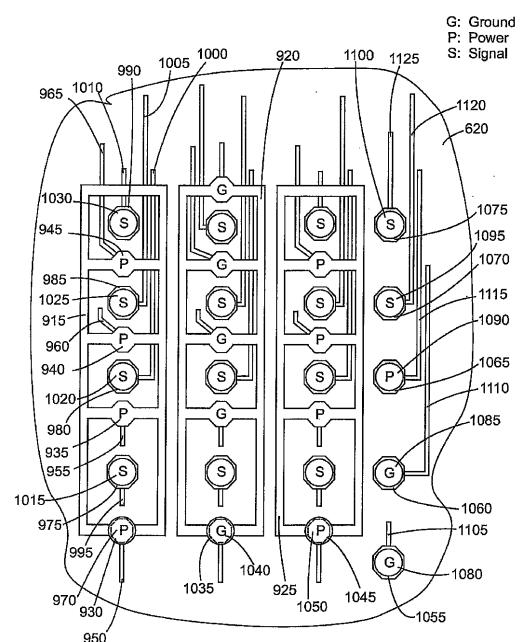

される。次に、チップ 620 のごく一部分の平面図である図 26 に注目する。ここでは、もう少し広大な UBM 層の一部であり得る 3 つの格子型 UBM 構造体 915、920 および 925 が、図示を簡単にするために、UBM 構造体の内部および周辺にある絶縁材料なしに図示されている。まず UBM 構造体 915 に関連する位置に目を向けると、導体パッド 930 (破線で示す)、935、940 および 945 は、それぞれの RDL 層構造体 950、955、960 および 965 に接続されて示されている。再配置層構造体 950、955、960 および 965 は、パッド 930、935、940 および 945 の下に位置し、半導体チップ 620 の内部の他の相互接続体または回路構造体と電気的に接続されている。導体パッド 930、935、940 および 945 は、チップ 620 の電源経路につながれ、その結果、記号「P」で示すように、電源の入出力用とされる。しかしながら、UBM 構造体 915 を含むことにより、パッド 930、935、940 および 945 の全てに対する電源の入出力が、導体パッド 930 の近傍に位置する単一のはんだボール 970 を通して配線されることが可能となる。幾つかの他の導体またはボンドパッド 975、980、985 および 990 は、UBM 構造体 915 の内部および周辺に重ねられていてもよく、チップ 620 の信号経路につながれていてもよく、例えば記号「S」で示すように、信号の入出力用となっていてもよい。この関連で、パッド 975、980、985 および 990 は、それぞれ RDL 構造体 995、1000、1005 および 1010 に電気的につながれていてもよく、はんだボール 1015、1020、1025 および 1030 がそれぞれ設けられていてもよい。

## 【0079】

同様に、UBM 構造体 920 は、記号「G」で示すように、接地経路の複数の位置を破線で示すボンドパッド 1035 および対応するはんだボール 1040 へと配線するように構成されていてもよい。また、UBM 構造体 925 は、電源入出力の複数のサイトを導体パッド 1045 (破線で示す) およびはんだバンプ 1050 へと配線するように構成されていてもよい。もちろん、UBM 構造体 915、920 および 925 は、複数の導体パッド 1055、1060、1065、1070 および 1075 と併せて用いられてもよい。これらの導体パッドには、はんだバンプ 1080、1085、1090、1095 および 1100 がそれぞれ対応して設けられ、その場合、導体パッド 1055、1060、1065、1070 および 1075 は、それぞれの RDL 構造体 1105、1110、1115、1120 および 1125 とオーム接続されている。この配置は、例えば、導体パッド 1055 および 1060 が接地の入出力用であり、導体パッド 1065 が電源の入出力用であり、そして導体パッド 1070 および 1075 が信号の入出力用である場合に適し得る。重要な点は、所望のレイアウトパターンを得るために、従来のはんだバンプ - RDL 相互接続体を UBM 配線構造体と共に使用し得る、ということである。

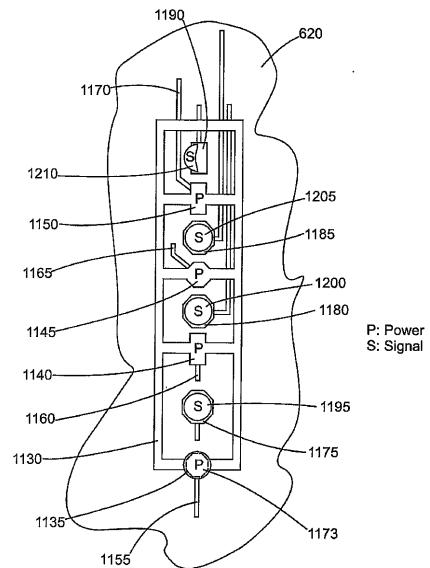

## 【0080】

次に、半導体チップ 620 の別の一部分の平面図である図 27 に注目する。この部分では、UBM 構造体 1130 は、UBM 構造体 1130 に電気的に接続され、UBM 構造体 1130 の一部を構成する 1 組の導体パッド 1135 (破線で示す)、1140、1145 および 1150 と共に表されている。UBM 構造体 1130 およびパッド 1135、1140、1145 および 1150 は、図解を簡略化するために、周囲を囲んで覆う絶縁材料なしで図示されている。導体パッド 1135、1140、1145 および 1150 は、それぞれの RDL 構造体 1155、1160、1165 および 1170 とつながれていてもよい。導体パッド 1135、1140、1145 および 1150 は、図のようにパッド 1135 近傍の UBM 1130 に接続された単一バンプ 1173 を介した電源の入出力用であってもよい。さらに、他のパッド 1175、1180、1185 および 1190 を設け、それらを信号の入出力用としてもよい。パッド 1175、1180、1185 および 1190 上には、それぞれはんだバンプ 1195、1200、1205 および 1210 を設けてもよい。なお、導体パッド 1190 のさらなる詳細を明らかにするために、バンプ 1210 の一部分を切り取って示されている。この例示的実施形態では、ボンドパッド 1190 は、本明細書の他の箇所に開示したような円形または八角形の構造体とは対照的に

10

20

30

40

50

、長方形の構造体として構成されていてもよい。長方形の構造体は、導体パッドおよびそれらに関連するRDL構造体をより密に詰めることができるという利点を有する。実際に、UBM構造体1130に電気的に接続される導体パッド1140および1150もまた、長方形の構造体として図示されている。

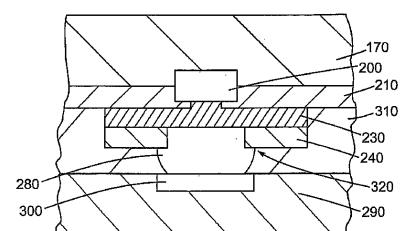

【0081】

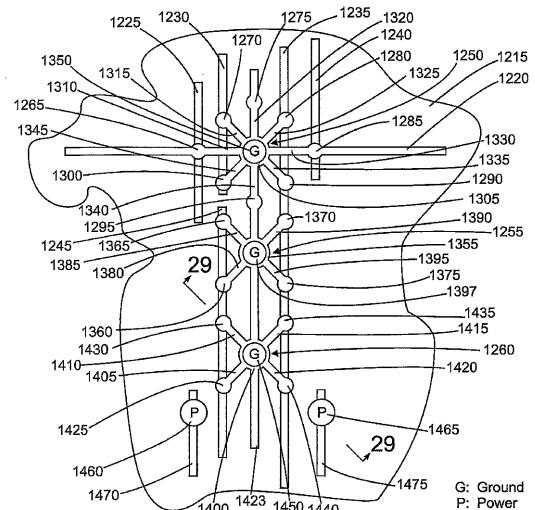

半導体チップ1215の別の例示的実施形態の平面図を図28に示す。半導体チップ1215のごく一部分のみを、図解を簡略化するために周囲を囲んで覆う絶縁材料を除いて図示している。例示的UBM構造体1220は、数個のRDL構造体1225、1230、1235、1240および1245の上に位置すると図示されている。UBM構造体1220は、リード線構造体の数個のクラスター1250、1255および1260を備えてもよい。クラスター1250は、各スパーク1310、1315、1320、1325、1330、1335および1340によって中央ハブ1305に接続された複数のリード線1265、1270、1275、1280、1285、1290、1295および1300で構成されていてもよい。スパークは、スパーク1310、1320、1330および1340の場合のように、それぞれのリード線で終端している必要はない。リード線1265は、その下のRDL構造体1225に電気的に接続され、リード線1270および1300は、その下のRDL構造体1230に接続され、リード線1280および1290は、その下のRDL構造体1235に接続され、リード線1285は、その下のRDL構造体1240に接続されている。ハブ1305には、接地の入出力用であり得るはんだバンプ1350が設けられていてもよい。

【0082】

クラスター1255は、ハブ1355と、ハブ1355から離れる方向に延びるが、それぞれのスパーク1380、1385、1390および1395によってハブ1355に接続される複数のリード線1360、1365、1370および1375とを備えていてもよい。リード線1360および1365は、その下のRDL構造体1245に接続され、リード線1370および1375は、その下のRDL構造体1235に接続されている。クラスター1255は、図のようにリード線1295において、あるいは要望に応じて他の場所で、クラスター1250とつながっていてもよい。はんだボール1397は、ハブ1355に接続されていてもよい。

【0083】

最後に、クラスター1260は、ハブ1400と、スパーク1405、1410、1415、1420および1423と、スパーク1405、1410、1415、1420にそれぞれ接続されたリード線1425、1430、1435および1440とで構成されていてもよい。リード線1425および1430は、その下のRDL構造体1245に接続されていてもよく、リード線1435および1440は、その下のRDL構造体1235に接続されていてもよい。クラスター1250および1255と同様に、クラスター1260には、接地の入出力用であるはんだバンプ1450が設けられていてもよい。電源バンプ1460および1465は、その下のRDL構造体1470および1475に接続されている。

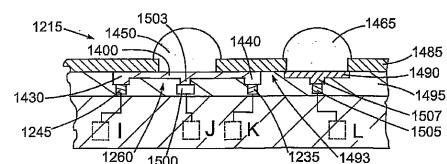

【0084】

次に、図28の断面29-29における断面図である図29に注目する。図29を詳細に観察する前に、(1)断面29-29が、リード線1430と、ハブ1400およびはんだボール1450の組み合わせと、リード線1440と、はんだボール1465とを通過することと、(2)図29は、様々な導体構造体およびUBM構造体の他の詳細を観察できるように、図28では図示されなかった半導体チップ1215の詳細を幾つか図示していることに注目されたい。したがって、例えば、2つのはんだバンプ1450および1465は、ポリイミドまたは他の高分子材料膜1485によって、横方向に分離され、且つ横方向に電気的に絶縁されている。膜1485は、それと共に描写される他の構造体を不明瞭にしないために、図28では図示されていないことを再度念頭に置くべきである。特に、はんだボール1465の下には、間隙1493によってUBMクラスター1260か

10

20

30

40

50

ら横方向に分離した UBM 構造体 1490 が存在する。間隙 1493 には、絶縁材料層 1495 の一部である絶縁材料が充填されている。絶縁材料層 1495 は、本明細書の他の箇所で説明した他の実施形態に関連して記載したパッシベーション層の様に構成されてもよい。本明細書中の他の箇所で述べたように、はんだボール 1450 と、その下の UBM 構造体、この場合はハブ 1400 との間でオーミックコンタクトがとられる。次に、リード線またはエクステンション 1503 を介して、ハブ 1400 と図 28 には示されていない下部の RDL 構造体 1500 との間でオーミックコンタクトがとられる。リード線 1430 および 1440 と、その下の RDL 構造体 1245 および 1235 との間でオーミックコンタクトがとられる。RDL 構造体 1245、1500 および 1235 は、半導体チップ 1215 のより深い位置の、破線ボックス I、J および K によって表される回路構造体と電気的に接続される。回路構造体 I、J および K は、概して、図 25 において回路構造体 A、B、C、D 等に関して上述された種類のものでもよい。はんだバンプ 1465 は、その下の UBM 構造体 1490 とオーミックコンタクトをとり、UBM 構造体 1490 は、次に、図 28 に示されていないエクステンションまたはリード線 1507 を介して RDL 構造体 1505 とのオーミックコンタクトをとる。RDL 構造体 1505 は、破線ボックス L によって表され、回路構造体 I、J および K に関して上記したように構成され得る下部の回路に接続される。10

#### 【0085】

クラスター構造を、電源、接地または信号に使用してもよい。電源、接地または信号の入出力への使用のいずれであろうとも、クラスター配置を用いる利点は、より密に詰めることができることと、レイアウトをより柔軟にできることにある。当業者であれば、あるクラスターに対してリード線およびスパークの数が変化し得ることを理解するであろう。さらに、クラスター配置を本明細書に開示した他の種類の UBM 構造体に用いてもよい。20

#### 【0086】

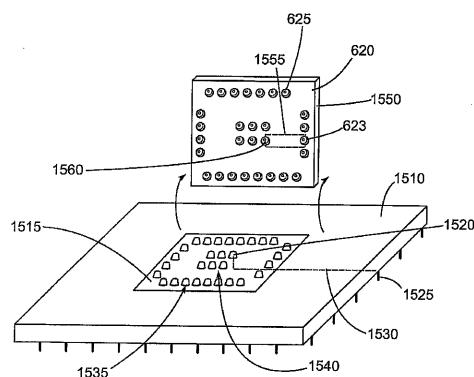

図 30 は、半導体チップパッケージ基板または他の種類のプリント配線基板でもよいプリント配線基板 1510 から上方へ剥がした状態の半導体チップ 620 の絵図である。組み立てる際には、半導体チップ 620 は、パッケージ基板 1510 のバンプアレイ 1515 の上にフリップチップ実装される。バンプアレイ 1515 は、半導体チップ 620 のはんだバンプ 623、625 等と係合するように設計された上方を向いた複数のはんだバンプを含み、それらのうちの 1 つに参照符号 1520 を付している。基板 1510 は、この基板 1510 が接続される別の電子デバイスとの入出力を行うためのある種の相互接続構造体を備える。この例示的実施形態においては、複数のピンから成るピングリッドアレイが基板 1510 から突出しており、それらのうちの 1 つに参照符号 1525 を付している。しかしながら、ボールグリッドアレイ、ランドグリッドアレイまたは他の種類の相互接続体を用いてもよい。破線 1530 で模式的に表した電気相互接続構造体によって、ピン 1525 等のあるピンと、基板 1510 上のバンプ位置 1520 等のあるバンプ位置との間に電気経路を確立する。相互接続構造体 1530 は、1 つまたは複数の導体線から構成されていてもよい。この導体線は、基板 1510 のうちの 1 つまたは複数の異なる高さの相互接続体の上にある場合もあれば、それらの上にない場合もある。30

#### 【0087】

様々な理由から、バンプアレイ 1515 の周囲 1535 の付近にあるバンプ位置は、信号の入出力専用である傾向があり、アレイ 1515 のコアパッド位置 1540 は、電源および接地の入出力専用である傾向がある。この従来の設計手法は、多くの設計状況において満足に機能する。しかしながら、いわゆるディープバンプ、すなわち、チップ 620 の縁 1550 に比較的近い場所にある、バンプ 623 等の半導体チップ 620 上のバンプが、電源または接地の入出力を必要とする特定の設計状況が存在する。アレイ 1515 の周囲バンプ位置 1535 は、信号の入出力専用である傾向があるので、あるピン 1525 からアレイ 1515 上の周囲に位置するパッドサイトへと電源または接地を配線するためには、基板 1510 において何らかの埋設相互接続構成を構築することが必要となり得る。この解決法には、費用上の不利益があり、おそらく、基板トレースの配線を大幅に変更し4050

なければならない場合に性能の問題が生じ得る。しかしながら、本明細書に開示したような UBM 配線の使用により、電源または接地の入出力をこのようなディープバンプ 623 へと配線し得る。この点に関して、UBM 配線構造体 1555 は、ディープバンプ 623 およびチップ 620 の中央に位置するバンプ 1560 の1つに電気的に接続される。バンプ 623 および 1560 とその下の UBM 構造体 1555 との間に配置される絶縁材料が存在するので、UBM 構造体 1555 を破線で示している。UBM 構造体 1555 は、本明細書に開示した実施形態のいずれかに記載したように構成され得る。

#### 【0088】

本明細書に開示した例示的実施形態はいずれも、例えば、半導体、磁気ディスク、光ディスクまたは他の記憶媒体等のコンピュータ可読媒体における命令により、またはコンピュータデータ信号として実施可能である。それらの命令またはソフトウェアは、本明細書に開示した回路構造体を合成および/またはシミュレートすることが可能であり得る。ある例示的実施形態では、Cadence の A P D 等の電子設計自動化プログラム等を用いて、開示された回路構造体を合成し得る。その結果得られたコードを用いて、開示された回路構造体を製造し得る。別の例示的実施形態では、高周波 S P I C E シミュレータ等のシミュレーションプログラムを用いて、開示された回路構造体の電気的挙動をシミュレートし得る。

#### 【0089】

本発明は、様々な改変および代替の形態が可能であるが、具体的な実施形態を例として図面に示し、かつ本明細書において詳細に説明した。しかしながら、本発明は、開示された特定の形態に限定されるものではないことに留意されたい。むしろ、本発明は、以下に添付する請求項によって画定されるような本発明の精神および範囲に含まれるあらゆる改変例、均等物および代替例を包含するものである。

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図6】

FIG. 6

(PRIOR ART)

【図7】

FIG. 7

(PRIOR ART)

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

【図 16】

FIG. 16

【図 17】

FIG. 17

【図 18】

FIG. 18

【図 20】

FIG. 20

【図 19】

FIG. 19

【図 21】

FIG. 21

(PRIOR ART)

## 【図22】

FIG. 22

(PRIOR ART)

【図2-3】

FIG. 23

【 図 2 4 】

FIG. 24

【図25】

FIG. 25

【 図 2 6 】

FIG. 26

【図27】

FIG. 27

【 図 2 8 】

FIG. 28

【 図 29 】

FIG. 29

【図30】

FIG. 30

---

フロントページの続き

(74)代理人 100142114

弁理士 小石川 由紀乃

(72)発明者 マクレラン,ニール

カナダ国 M 2 K 3 B 8 オンタリオ,トロント,リーン・ドライブ 2 2104

(72)発明者 イ,ユエ

カナダ国 L 3 P 7 K 5 オンタリオ,マークハム,グリーンウィッヂ・アベニュー 18

(72)発明者 トーパシオ,ローデン

カナダ国 L 3 R 4 S 8 オンタリオ,マークハム,カーマ・ロード 7

(72)発明者 チャン,テレンス

カナダ国 M 2 N 7 E 3 オンタリオ,トロント,ハリソン・ガーデン・ブルーバード 80,

エイピー・ティ 1826

審査官 宮本 靖史

(56)参考文献 特開2001-144212 (JP, A)

国際公開第03/012863 (WO, A1)

特開2000-031188 (JP, A)

特開2003-152081 (JP, A)

特開平01-209746 (JP, A)

特開2007-266588 (JP, A)

特開2006-339331 (JP, A)

国際公開第2005/062381 (WO, A2)

(58)調査した分野(Int.Cl., DB名)

|        |               |   |               |

|--------|---------------|---|---------------|

| H 01 L | 2 3 / 1 2     | - | 2 3 / 1 5     |

| H 01 L | 2 1 / 3 2 0 5 | - | 2 1 / 3 2 1 3 |

| H 01 L | 2 1 / 4 4 7   | - | 2 1 / 4 4 9   |

| H 01 L | 2 1 / 6 0     | - | 2 1 / 6 0 7   |

| H 01 L | 2 1 / 7 6 8   |   |               |

| H 01 L | 2 3 / 5 2 2   |   |               |

| H 01 L | 2 3 / 5 3 2   |   |               |

| H 01 L | 2 5 / 0 0     | - | 2 5 / 1 8     |