(19) **日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号

特許第3973251号 (P3973251)

(45) 発行日 平成19年9月12日(2007.9.12)

(24) 登録日 平成19年6月22日 (2007.6.22)

(51) Int.C1. F 1

G11C 16/06 (2006.01) G11C 17/00 632A HO3K 19/173 (2006.01) G11C 17/00 634Z HO3K 19/177 (2006.01) HO3K 19/173 101 HO3K 19/177

請求項の数 6 (全 21 頁)

(21) 出願番号 特願平8-255983

(22) 出願日 平成8年9月27日 (1996.9.27)

(65) 公開番号 特開平9-147579

(43) 公開日 平成9年6月6日 (1997.6.6) 審査請求日 平成15年9月26日 (2003.9.26)

(31) 優先権主張番号 08/536026

(32) 優先日 平成7年9月29日(1995.9.29)

(33) 優先権主張国 米国(US)

(73)特許権者 597154922

アルテラ コーポレイション

Altera Corporation アメリカ合衆国 95134 カリフォル ニア州 サン ホセ イノベーション ド

ライヴ 101

(74)代理人 100064746

弁理士 深見 久郎

(74)代理人 100085132

弁理士 森田 俊雄

(74)代理人 100091409

弁理士 伊藤 英彦

(74)代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】集積回路のためのメモリセル、メモリセルを有するプログラマブル論理装置、メモリセルを有するシステム、メモリセル、およびダイナミックメモリセル

# (57)【特許請求の範囲】

### 【請求項1】

集積回路のためのメモリセルであって、

チャージポンピングノードと、

充電装置とを備え、

## 前記充電装置は、

前記チャージポンピングノード<u>に電気的に結合された一端および</u>出力ノー<u>ドに</u>電気的に 結合された<u>他端を有する導電経路と、ゲートとを有する</u>充電トランジスタと、

前記充電トランジスタの前記ゲートと前記出力ノードとの間に結合された抵抗器と、

前記充電トランジスタの前記ゲートと前記チャージポンピングノードとの間に結合され た第1のキャパシ<u>タと</u>を含み、

プリチャージ電圧レベルのプリチャージ信号は前記チャージポンピングノードに電気的に結合されて、前記充電トランジスタを介して前記出力ノードを第 1 の電圧レベルに充電し、

# 前記メモリセルはさらに、

第2の電圧レベルの電圧源と前記出力ノードとの間に電気的に結合されたメモリ素子を<u>備え</u>、前記第2の電圧レベルは前記第1の電圧レベルより下であり、前記メモリ素子はデータを記憶し、電力が前記集積回路から取除かれるときに前記データを保持する、メモリセル。

【請求項2】

30

40

50

前記出力ノードは前記プリチャージ信号によって周期的にリフレッシュされる、請求項1に記載のメモリセル。

## 【請求項3】

前記プリチャージ信号のサイクルはほぼ前記第1の電圧レベルで第1の論理レベルを有し、前記第1の電圧レベルより上の第3の電圧レベルで第2の論理レベルを有する、請求項1に記載のメモリセル。

#### 【請求項4】

前記プリチャージ信号のサイクルはパルスを含み、前記パルスは前記第1の電圧レベルより上の第3の電圧レベルであり、前記パルスの持続時間は、前記プリチャージ信号がほぼ前記第1電圧レベルであるときの持続時間よりも実質的に短い、請求項1に記載のメモリセル。

### 【請求項5】

前記出力ノードは第1のメモリ記憶状態でほぼ前記第1の電圧レベルより上に動的に保たれ、第2のメモリ記憶状態でほぼ前記第2の電圧レベルに放電される、請求項1に記載のメモリセル。

#### 【請求項6】

前記出力ノードと接地との間に結合された第2のキャパシタをさらに<u>備える</u>、請求項1に記載のメモリセル。

### 【発明の詳細な説明】

## [0001]

【発明の背景】

この発明は集積回路メモリ技術の分野に関する。特に、この発明はデータを記憶するためのダイナミック不揮発性メモリセルを提供する。

### [0002]

メモリセルは多くの型の電子装置および集積回路を実現するのに用いられる。これらの装置は数ある中でマイクロプロセッサ、スタティックランダムアクセスメモリ(SRAM)、消去可能プログラマブルリードオンリメモリ(EPROM)、電気的消去可能プログラマブルリードオンリメモリ(EEPROM)、フラッシュEEPROMメモリ、プログラマブル論理装置(PLD)、フィールドプログラマブルゲートアレイ(FPGA)、および特定用途向け集積回路(ASIC)を含む。メモリセルはこれらおよび他の集積回路のためのデータおよび他の情報を記憶するために用いられる。

## [0003]

集積回路技術および半導体プロセスが進歩し続けるにつれて、主にメモリセルの大きさによってしばしば判断される、集積回路の密度および機能性が高まることが必要とされる。 さらに、メモリセルが、より少ない電力消費と、不揮発性と、より長い装置寿命と、向上 されたデータ保存と、より良い過渡性能と、優れた電圧および電流属性と、他の類似した 属性における改良点とのような動作性能を向上させていることが望ましい。

## [0004]

さらに、改良されたメモリセルがPLD集積回路のような特定的なアプリケーションに特に必要とされる。PLDは電子技術の当業者には周知である。このようなプログラマブル 論理装置は通常PAL(プログラマブルアレイ論理)、PLA(プログラマブル論理アレイ)、EPLA、PLD、EPLD(消去可能プログラマブル論理装置)、EEPLD(電気的消去可能プログラマブル論理装置)、LCA(論理セルアレイ)、FPGA(フィールドプログラマブルゲートアレイ)などと称される。このような装置は、標準的な既製の装置を特定的なアプリケーションにプログラムすることが望ましい場合にアプリケーションの広いアレイで用いられる。このような装置はたとえば、アルテラ・コーポレイション(Altera Corp.)によって製造されるEPLDの周知のClassic (商標)、MAX(登録商標)5000、およびFLEX(登録商標)8000を含む。

## [0005]

多くの論理アレイブロック (LAB)が 2 次元アレイで与えられる P LDが一般に既知で

ある。LABは、NAND、NOR、および排他的ORのような相対的に基本的な論理機能を与える、多数の個々のプログラマブル論理素子(LE)を含む。さらに、PLDは、プログラム可能に論理信号を選択し、かつそれをLABおよびLAEへ、LABおよびLEから、および、LABとLEとの間に導くための交差する信号導体のアレイを有する。LABとLEとこれらの論理素子間の相互接続との構成はメモリセルに記憶される。メモリセルは、論理アレイブロック(LAB)および論理素子(LE)の配置、構成、および配列と、これらの論理アレイブロックおよび論理素子の間の相互接続とをプログラム可能に制御するために用いられ得る。

## [0006]

(「チップ」としても知られる)集積回路を形成するために用いられる半導体装置ジオメトリの連続的なスケーリングおよび縮小から生じて、集積回路は漸進的により小さく、より高密度になってきた。プログラマブル論理では、より多くの数のプログラマブル論理装置を1つの集積回路へ入れることが可能になる。さらに、素子の数が増加するにつれ、素子を相互接続し、かつ信号を論理ブロック間に送るために用いられる技術およびアーキテクチャを改良することがますます重要になる。また、PLDの大きさおよび複雑さが増すにつれ、より多くのメモリセルが論理素子の構成情報を保持するために必要とされる。

### [0007]

このような装置はかなり成功したが、同時にある制限を受ける。それは特に、より複雑な論理モジュールと論理モジュール間の付加的または代替的な型の相互接続とを与えることが付加的な回路構成要素とプログラムの複雑さとを正当化するに足る利点を有する状況においてである。また、より大きな容量の論理装置が引続いて所望される。このために、より効率的に論理機能を実現する必要性と個々の論理モジュールを相互接続するための装置の部分をよりよく用いる必要性とが生じる。さらに、PLDの構成情報をより効率的かつ効果的に記憶することが必要である。PLDの構成情報を記憶するために用いられるメモリ技術は小型で、電力面で効率的で、再プログラム可能で、かつ不揮発性であるべきであり、あまり付加的なプログラム回路を上に必要としないべきであり、一般にPLD論理モジュールおよび相互接続の性能および特徴に改良を加えるべきである。

#### [00008]

理解されるように、改良されたメモリセルが必要であり、特に、プログラマブル論理装置の論理素子および相互接続に対する構成情報を記憶するための改良されたメモリセルが必要である。

# [0009]

#### 【発明の概要】

この発明は集積回路においてデータを記憶するための動的、不揮発性、かつ再プログラム可能なメモリセルを提供する。メモリセルは電圧源と出力ノードとの間に結合されたプログラマブルメモリ素子を含む。通常動作の間、電圧源はほぼVSSである。出力ノードはメモリセルの記憶された状態を出力する。充電トランジスタはチャージポンピングノードと出力ノードとの間に結合される。チャージポンピングノードは充電トランジスタを介して出力ノードをほぼVDDに動的に充電する。出力ノードの電荷は周期的にリフレッシュされる。

# [0010]

論理ハイを記憶するためには、プログラマブルメモリ素子がプログラムされ、これが電圧源から出力ノードを分離する。出力ノードはVDDのままである。論理ローを記憶するためには、プログラマブルメモリ素子が消去され、これが出力ノードを電圧源に結合する。出力ノードの動的電荷はプログラマブルメモリ素子を介して電圧源に放電される。出力ノードはVSSである。

## [0011]

プログラマブルメモリ素子はNMOSであってもよく、プログラム可能であり得る。ある 実施例では、フラッシュEEPROMトランジスタまたはEEPROMトランジスタがR AM型動作を達成するために用いられ得る。ROM型動作が所望されるならば、EPRO 10

20

30

40

30

40

50

M、ヒューズ、またはアンチヒューズ技術が用いられ得る。読出動作の間、プログラマブルメモリ素子の制御ゲートは固定した(切換わらない)電圧に保たれる。

# [0012]

ある実施例では、漏れ電流以外の静的電力を消費せずに、メモリセルはフルレールまたはほぼフルレールの電源電圧をその出力に届ける。この発明のメモリセルは動的(周期的なリフレッシュを必要とする)および不揮発性(電力が取除かれるならばそのメモリを保存する)の両方である。これが用いられ得るのは、1ビットかまたはビットのストリングが1度に読出され得る標準的なRAMセルとしてか、または、プログラマブル論理装置において用いられるときなどにマルチプレクサまたは他の回路構成要素をその出力が駆動する構成ビットとしてである。さらに、メモリセルはプログラマブル論理装置の構成情報を記憶するために用いられ得る。メモリセルはまた優れたデータ保存性能を与える。

#### [0013]

より具体的に、この発明のメモリセルは、チャージポンピングノードと、チャージポンピングノードおよび出力ノードの間に結合された充電装置とを含み、ここでプリチャージ信号がチャージポンピングノードに結合されて、充電装置を介して出力ノードを第1の電圧に充電する。さらに、メモリ装置は第2の電圧レベルの電圧源と出力ノードとの間に結合され、ここで第2の電圧レベルは第1の電圧レベルより下である。メモリはデータを記憶し、電力が集積回路から取除かれるときこのデータを保存する。

#### [0014]

この発明の他の目的、特徴、および利点は、同じ参照番号が図面を通して同じ特徴を表わす以下の詳細な説明および添付の図面を検討すると明らかになるであろう。

## [0015]

# 【好ましい実施例の詳細な説明】

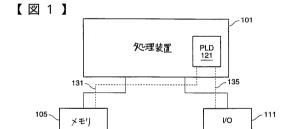

図1は、この発明がその中で実施され得るデジタルシステムのブロック図を示す。図1の特定的な実施例では、処理装置101がメモリ105およびI/O111に結合され、プログラマブル論理装置(PLD)121を組入れる。PLDは特に、接続131を介してメモリ105に、接続135を介してI/O111に結合され得る。このシステムは、プログラムされるデジタルコンピュータシステム、デジタル信号処理システム、特殊デジタルスイッチングネットワーク、または他の処理システムであってもよい。さらに、このシステムは、汎用コンピュータか、PLD121をプログラムするような特定用途向けの課題のために最適化された(電気通信機器のような)専用コンピュータか、または汎用コンピュータと補助専用ハードウェアとの組合せであってもよい。

#### [0016]

処理装置101は処理または記憶のために適切なシステム構成要素にデータを送り、メモリ105に記憶されるかまたはI/O111を用いて入力されたプログラムか、または他の同様の機能を実行できる。処理装置101は中央処理装置(CPU)、マイクロプロセッサ、浮動小数点コプロセッサ、グラフィックスコプロセッサ、ハードウェアコントローラ、マイクロコントローラ、コントローラとして用いるためにプログラムされたプログラマブル論理装置、または他の処理装置であってもよい。さらに、多くの実施例ではしばしばCPUの必要性がない。たとえば、CPUの代わりに、1つ以上のPLD121がシステムの論理演算を制御できる。

#### [0017]

いくつかの実施例では、処理装置101はコンピュータシステムでさえあってもよい。ある実施例では、ソースコードがメモリ105に記憶され、機械言語に変換され、処理装置101はCPUを含む必要はなく、ある実施例では命令が1つ以上のPLD121によって実行され得る。メモリ105にソースコードを記憶する代わりに、ソースコードを表わす機械言語だけがソースコードなしで、処理装置101によって実行するためにメモリ105に記憶されてもよい。メモリ105はランダムアクセスメモリ(RAM)、リードオンリメモリ(ROM)、固定またはフレキシブル媒体、PCカードフラッシュディスクメモリ、テープ、または何か他の記憶検索手段か、

またはこれらの記憶検索手段の組合せであってもよい。

## [0018]

処理装置101はI/O111を用いてユーザのインタラクションのための入出力経路を与える。たとえば、ユーザはプログラムされるべき論理機能をプログラマブル論理装置121に入力できる。I/O111はキーボード、マウス、トラックボール、タブレット装置、テキストまたはグラフィックディスプレイ、タッチスクリーン、ペンタブレット、プリンタ、または他の入出力手段、またはこれらの手段のいかなる組合せであってもよい。ある実施例では、I/O111はどのような処理装置101出力のハードコピーをも印刷するために用いられるプリンタを含む。特に、I/O111を用いて、処理装置101を用いて実行されるワードプロセシングプログラムを用いて準備された文書のコピーをユーザは印刷できる。他の場合では、ユーザはPLD121内に含まれた、ソースコードのコピーかまたは論理機能のリスティングをプリントアウトできる。

#### [0019]

PLD121は図1のシステム内で多くの異なった目的を果たし得る。PLD121は処理装置101の論理ビルディングブロックであって、その内部および外部の動作を指示してもよい。PLD121はシステム動作においてその特定の役割を実行するのに必要な論理機能を実現するようにプログラムされる。

## [0020]

PLD121に対する多数の用途のいくつかの例として、処理装置101は、メモリ105またはI/O111にアクセスするために接続131を介してメモリまたはポートアドレスを復号化するようにPLD121を用いることができる。PLD121はメモリまたは特殊メモリのようなデータを記憶するようにプログラムでき、これは処理装置101または(接続131を経て)メモリ105から届く。PLD121は固定またはフレキシブルディスクドライブのようなメモリ105装置のためのマイクロコントローラとして用いられ得る。PLD121はまた、接続135を介してデータを渡す、キーボードまたはスキャナのようなI/O111装置のためのマイクロコントローラに構成できる。

## [0021]

他の実施例では、PLD121は数学的計算またはグラフィック計算を行なうためのコプロセッサのようなコントローラまたは特殊処理装置として用いられてもよい。さらにほかの実施例では、PLD121は電気通信アプリケーションのために用いられ得る。たとえば、処理装置101がデータをPLD121に送り、PLD121がこのデータを処理し、次に、結果を処理装置101に戻す。さらに、処理装置101は、メモリ105に記憶されるかまたはI/O111を用いて入力されたプログラムを実行するためにPLD121に渡すかまたは送ることができる。これらはデジタルシステム内でのPLD121の多数の用途のうちのいくつかである。また、図1に示されるもののようなシステムが、異なったシステム機能を各々行なう複数個のPLD121を実現できる。

# [0022]

図1に示されるシステムは特定の論理パターンでPLD121をプログラムするためにも用いられ得る。機能をPLDへ設計するためのコンピュータプログラムがメモリ105に記憶され得、処理装置101を用いて実行され得る。次に、PLD121にプログラムされるべき設計特性がI/O111を経て入力され、処理装置101によって処理される。最後に、処理装置101は設計特性をPLD121に転送かつプログラムする。

## [0023]

図1では、処理装置101がPLD121を組入れて示される。しかしながら、他の実施例では、PLD121は処理装置101の外部にあってもよく、PLDインタフェースが処理装置101とPLD121との間に結合されてもよい。PLDインタフェースはPLD121を処理装置101にインタフェースするための適切なアダプタまたはソケットを設けるであろう。さらに、PLDインタフェースはPLD121を処理装置101に結合するための適切な電圧と電気特性とを与えるであろう。

## [0024]

40

20

30

40

50

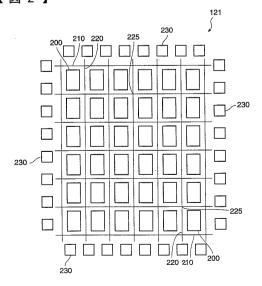

図2は図1のPLD121の全体の内部アーキテクチャおよび組織を示す簡略化されたブロック図である。PLDアーキテクチャ、組織、および回路設計の多くの詳細がこの発明を理解するために必要ではなく、このような詳細は図2に示されない。

#### [0025]

図2は36個の論理アレイブロック(LAB)200の6×6の2次元アレイを示す。LAB200は、論理機能を行なうように構成またはプログラムされた論理資源の物理的に分類された組である。LABの内部アーキテクチャは図3と関連して以下にさらに詳しく説明される。PLDは図2に示されるPLD121よりも多いか少ない、どのような任意の数のLABを含んでもよい。一般に、将来において、技術が進歩かつ向上するにつれ、さらに多数の論理アレイブロックを有するプログラマブル論理装置が疑いもなく作り出されるであろう。さらに、LAB200は正方行列で組織される必要はなく、たとえば、アレイはLABの5×7または20×70の行列で組織されてもよい。

#### [0026]

LAB200は、広域水平相互接続(GH)210および広域垂直相互接続(GV)220のアレイを含んだ広域相互接続構造にプログラム可能に接続されてもされなくてもよい入力および出力(図示せず)を有する。図2には単一のラインとして示されるが、GH210ラインおよびGV220ラインの各々が複数個の信号導体を表わす。LAB200の入力および出力は隣接したGH210と隣接したGV220とにプログラム可能に接続できる。GH210相互接続およびGV220相互接続を利用して、多数のLAB200が、単一のLAB200を用いて実現できるよりも大きく、複雑な論理機能を実現するように接続され、かつ組合され得る。

## [0027]

ある実施例では、GH210導体およびGV220導体がこれらの導体の交差225でプログラム可能に接続可能であってもなくてもよい。さらに、GH210導体およびGV220導体は他のGH210導体およびGV220導体と多数の接続を作り得る。さまざまなGH210導体およびGV220導体が、PLD121上の1つの位置のLAB200からPLD121上の別の位置の別のLAB200への信号経路を生じるためにプログラム可能に接続され得る。さらに、1つのLAB200からの出力信号が1つ以上のLAB200の入力へ送られ得る。また、広域相互接続を用いて、LAB200からの信号が同じLAB200へとフィードバックできる。他の実施例またはこの発明において、選択されたGH210導体だけがGB220導体の選択にプログラム可能に接続される。さらに、さらなる実施例では、GH210導体およびGV220導体が、入力または出力であるがその両方ではないような特定の方向に信号を渡すために特別に用いられ得る。

# [0028]

図2のPLDのアーキテクチャはチップの周辺で入出力ドライバ230をさらに示す。入出力ドライバ230はPLDを外部のオフチップ回路構成要素にインタフェースするためのものである。図2は32個の入出力ドライバ230を示すが、PLDは示される数よりも多いか少ないどのような数の入出力ドライバを含んでもよい。各入出力ドライバ230は入力ドライバ、出力ドライバ、または双方向ドライバとして用いるために構成される。入力ドライバはチップの外部から信号を受け、それをオンチップ回路構成要素にインタフェースする。出力ドライブは内部信号を受け、それを外界にインタフェースする。双方向ドライバは入力ドライバおよび出力ドライバの両方の機能を行なう。加えて、双方向ドライブはドライバに双方向バスとインタフェースさせる高インピーダンスモードを有する。この発明の他の実施例では、PLDは専用の入力ドライバ、専用の出力ドライバ、特別な「急速」入力ドライバなどを有する。

# [0029]

LAB200と同様に、入出力ドライバ230は隣接したGH210導体およびGV22 0導体にプログラム可能に接続可能である。GH210導体およびGV220導体を用いて、入出力ドライバ230はどのLAB200にもプログラム可能に接続可能である。入出力ドライバ230はLAB200と外部のオフチップ回路構成要素との間でのデータの

30

40

50

(7)

転送を容易にする。たとえば、他のチップからのオフチップ論理信号は1つ以上のLAB200を駆動するために入出力ドライバ230を介して結合できる。これらのオフチップ入力とLAB200にプログラムされた論理機能とに基づいて、LAB200は、オフチップ回路構成要素とインタフェースするために広域相互接続を介して入出力ドライバ230に結合される出力信号を発生する。

#### [0030]

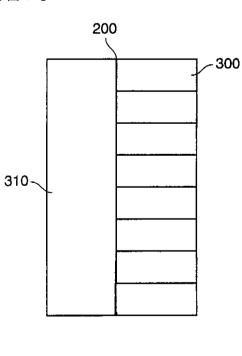

図3は図2のLAB200の簡略化されたブロック図を示す。LAB200は、時には「論理セル」と称される可変数個の論理素子(LE)300と局所(または内部)相互接続構造310とからなる。LAB200は8個のLE300を有するが、LAB200は8よりも大きいか小さいどのような数のLEを有してもよい。この発明のさらなる実施例では、LAB200は全体で16個のLEに対して8個のLEの2つの「バンク」を有し、ここで各バンクは別個の入力、出力、制御信号、およびキャリーチェーンを有する。

#### [0031]

この発明の基本的な理解を与えるのに十分な、LE300の一般的な概観がここに提示される。LE300はPLDの最小の論理ビルディングブロックである。LE300が図1・3に示されるものとは異なった多くのアーキテクチャで実現され得るが、GH210およびGV220からのような、LABの外部の信号は局所相互接続構造310によってLE300にプログラム可能に接続される。ある実施例では、この発明のLE300は、4変数ブール演算のような多くの変数の論理機能を与えるように構成可能な機能発生器を組入れる。組合せ機能と同様に、LE300はまた、たとえばDフリップフロップを用いて順次機能および登録された機能のための指示を与える。

#### [0032]

LE300は、GH210およびGV220に接続可能な組合せ出力および登録された出力をLAB200の外部に与える。さらに、LE300からの出力は局所相互接続構造310に内部的にフィードバックされ得、局所相互接続構造310によって、1つのLE300からの出力が、広域相互接続構造のGH210およびGV220を用いずに他のLE300からの出力が、広域相互接続構造のGH210およびGV220を用いずに他のLE300からの入力にプログラム可能に接続できる。局所相互接続構造310は、限られた広域資源、すなわちGH210およびGV220を利用せずにLEの短距離の相互接続をもたらす。局所相互接続構造310と局所フィードバックとによって、LE300は、単一のLE300を用いて実現できるよりも大きく、かつ複雑な論理機能にプログラム可能に接続可能である。さらに、その大きさが小さくなり、長さが短くなったために、局所相互接続構造310の寄生は広域相互接続構造に比較して減少している。したがって、局所相互接続構造310の寄生は広域相互接続構造に比較して減少している。したがって、局所相互接続構造310によるよりも早く信号を伝搬させる。

# [0033]

この発明のメモリセルはPLDのさまざまな位置で用いられ得る。たとえば、メモリセルはルックアップテーブルと、機能発生器と、プログラマブル相互接続と、PLDの他の構成要素との構成を実現かつ記憶するために用いられ得る。この発明のメモリセルを用いて、LE300で用いられるルックアップテーブルを実現するために用いられるRAMが構成できる。この発明のメモリセルはまた記憶ビットともなり得る。この記憶ビットは、たとえばLEが登録されたモードかまたは順次モードのいずれであるかを判断するために用いられ得る。記憶ビットはプログラマブルマルチプレクサの動作を構成するためにも用いられ得る。

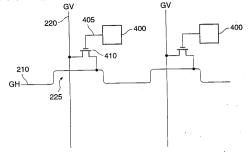

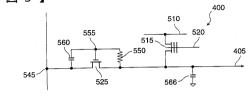

## [0034]

図4は、図2に示されるようなPLDのプログラマブル相互接続資源を実現するにあたってこの発明がいかに用いられるかの例を示す図である。メモリセル400はこの発明のプログラマブルメモリセルである。メモリセル400はハイまたはローの論理状態を記憶する。典型的に、論理ハイ状態は「1」またはVDDによって表わされ、論理ロー状態は「0」または接地によって表わされる。

#### [0035]

メモリセル400は再プログラム可能であり、これはセルが新しいデータで何回もプログ

20

30

40

50

ラムできることを意味する。さらに、この発明ではメモリセル400が不揮発性であり、これは電力が取除かれるときでも記憶された情報が保存されることを意味する。たとえば、メモリセル400は特定の論理状態でプログラムされた後、この情報をセルが再プログラムされるまで無限に記憶する。

## [0036]

メモリセル 4 0 0 はその記憶された状態を出力するための出力 ノード 4 0 5 を有する。出力 ノード 4 0 5 はメモリセル 4 0 0 に記憶された状態を表わす論理ロー出力または論理ハイ出力のいずれかを与える。出力 ノード 4 0 0 の出力電圧レベルは典型的にフルレール電圧であり、集積回路のほぼ V D D (時には V C C と称される)または V S S のいずれかと等しい。

## [0037]

メモリセル400は多くの型の論理素子および構成要素を実現するために用いられ得る。たとえば、メモリセル400はフリップフロップ、レジスタ、記憶ビット、アーキテクチャビット、ルックアップテーブル、プログラマブル相互接続アレイ、RAM、SRAM、ROM、EPROM、BEPROM、内容アドレス記憶装置(CAM)、PLD、EPGA、PCカードメモリカード、ならびに、他の同様のメモリ素子および装置を実現するために用いられ得る。図4に示されるように、メモリセル400はPLDのプログラマブル相互接続資源を実現するために用いられ得る。

#### [0038]

図4では、GH210導体およびGV220導体が交差225で交差する。交差225は時には交差点と称される。広域プログラマブル相互接続の場合では典型的であるように、GH210ラインおよびGV220ラインはプログラム可能に結合されなければ交差225で接続しない。パストランジスタ410およびプログラマブルメモリセル400は、GH210からGV220へ、およびGV220からGH210へのプログラム可能な結合を容易にする。特に、メモリセル400に記憶されるデータに依存して、GH210導体およびGV220導体が交差225でプログラム可能に接続されるか、またはプログラム可能に分離される。

#### [0039]

交差 2 2 5 で、パストランジスタ 4 1 0 は G H 2 1 0 と G V 2 2 0 との間に結合される。パストランジスタ 4 1 0 のゲートはメモリセル 4 0 0 の出力ノード 4 0 5 に結合される。メモリセル 4 0 0 によって制御され、パストランジスタ 4 1 0 は G H 2 1 0 を G V 2 2 0 にプログラム可能に結合する。たとえば、 G V 2 2 0 および G H 2 1 0 はメモリセル 4 0 0 に論理ハイを記憶することによって接続できる。メモリセル 4 0 0 はおそらく出力ノード 4 0 5 でハイレベルを出力し、これはパストランジスタ 4 1 0 のゲートに渡される。パストランジスタ 4 1 0 をターンオンし、したがって G V 2 2 0 が G H 2 1 0 に電気的に結合される。代替的に、 G V 2 2 0 および G H 2 1 0 がメモリセル 4 0 0 に 0 をプログラムすることによって互いから分離されてもよい。このように、この発明のメモリセル 4 0 0 は P L D のための広域プログラマブル相互接続構造を実現するために用いられ得る。

### [0040]

さらに、上述のようにこの発明はパストランジスタ410のゲートにフルレール電圧を与える。この場合、パストランジスタ410は実質的にオンであるか実質的にオフであるかのいずれかである。このために、GH210およびGV220が一般に良好な実行特性で集積回路中に信号を導く。たとえば、パストランジスタ410が十分にオンである(たとえば、ゲートがVDDである)とき、パストランジスタ410の抵抗の量が最小に維持され、こうして過渡性能を向上させる。また、パストランジスタ410のゲートのVDDは、ほぼVDD・VTの電圧(基板効果を含む、パストランジスタ410のしきい値電圧)を1つのGH210導体またはGV220導体から別のものへともたらす。また、パストランジスタ410が十分にオフである(たとえば、ゲートがVSSである)とき、GH210導体またはGV220導体から別のものへと信号が渡らない(または「漏れ」ない)

20

30

40

50

。さらに、パストランジスタ410が十分にオフであるとき、特定のGH210導体と交差するGV220導体はその特定のGH210導体を容量的にロードしない。これらの特徴によってプログラマブル論理装置集積回路の性能が向上する。

## [0041]

パストランジスタ4 1 0 は C M O S 、 N M O S 、 P M O S 、およびバイポーラを含む多くの異なったプロセス技術を用いて作成できる。好ましい実施例では、パストランジスタ 4 1 0 は N M O S トランジスタである。

## [0042]

図5はこの発明のメモリセル400のより詳細なブロック図を示す。メモリセル400は論理状態を記憶する。メモリセルはこの記憶された論理状態、すなわち論理ハイまたは論理ローを出力ノード405に出力する。集積回路では、論理ハイは第1の電圧レベルによって表わされ得、論理ローは第2の電圧レベルによって表わされ得る。第1の電圧レベルは一般に集積回路のための電源電圧、すなわちVDD(またはVCC)である。第2の電圧レベルはほぼVSSである。VDDは典型的に5ボルトであり、VSSは接地である。さらに、高度に集積された半導体回路を容易にするために、5ボルトの典型的な電圧源が5ボルト未満、通例約3.3ボルトから約3.6ボルトの電圧レベルに減少されている。将来において、電源電圧はさらに、たとえば2.5ボルトに減少されさえするかもしれない。

#### [0043]

さらに実施例において、メモリセル400に対する電源電圧は集積回路に対する電源電圧と同じでないかもしれない。この場合、第1の電圧レベルがほぼVDDではないかもしれない。第2の電圧レベルがほぼVSSではないかもしれない。たとえば、VDDが約5ボルトであり得るが、この電圧は内部回路と結合するために約3.3ボルトに減少され得る。この場合、第1の電圧レベルは「局所」VDD、すなわち、メモリセル400とおそらくは他の内部回路構成要素とに結合されたVDDであり得る。別の例では、集積回路の電源電圧がVDDであり得るが、メモリセル400に対する第1の電圧レベルがほぼVDD・VTであり得る。さらに別の例では、VDDが約3.3ボルトであり得、メモリセル500に対する第1の電圧レベルがより高い電圧、すなわち約5ボルトであり得る。

## [0044]

メモリセル400は、電圧源510と出力ノード405との間に結合されたプログラマブルメモリ素子515を含む。プログラムメモリ素子515は、多くの異なったメモリ技術から作成できる不揮発性メモリ素子であってもよい。不揮発性メモリセルは電力が除かれるときでさえその記憶された情報を保存する。たとえば、プログラマブルメモリ素子515はヒューズまたはアンチヒューズのような1回だけプログラム可能な装置を用いて作成できる。さらに、プログラマブルメモリ素子515はEPROM、EEPROM、フラッシュEEPROMなどのような不揮発性の再プログラム可能なメモリ装置を用いて作成できる。好ましい実施例では、プログラマブルメモリ素子515はEEPROMセルである。この実施例では、プログラマブルメモリ素子515は目EPROMセルである。この実施例では、プログラマブルメモリ素子515は制御ゲート520を有する。電圧源510は一般に集積回路の第2の電圧レベル、またはVSSに結合される。

### [0045]

さらに、メモリセル 4 0 0 では、充電トランジスタ 5 2 5 がチャージポンピングノード 5 4 5 と出力ノード 4 0 5 との間に結合される。充電トランジスタ 5 2 5 はバイポーラ装置および M O S 装置を含む多くの異なった型のトランジスタを用いて形成できる。好ましい実施例では、選択トランジスタは N M O S トランジスタである。

#### [0046]

抵抗器 5 5 0 は充電トランジスタ 5 2 5 のゲート 5 5 5 と出力ノード 4 0 5 との間に結合される。集積回路上で、抵抗器は多くの異なった技術を用いて、かつ異なった装置から作成できる。たとえば、抵抗器 5 5 0 は数ある中でポリシリコン、ドープされないポリシリコン、n型拡散、p型拡散、nウェル拡散、トランジスタチャネルを用いて形成され得る。抵抗器 5 5 0 はまた充電トランジスタ 5 2 5 と統合され得るか、または相互接続のレイ

20

30

40

50

アウトから形成され得る。たとえば、レイアウトでは、抵抗器 5 5 0 は充電トランジスタのゲート 5 5 5 と出力ノード 4 0 5 との間の曲がりくねったポリシリコン相互接続であり得る。ある実施例では、抵抗器 5 5 0 はほぼ 1 0 0 キロオームである。しかしながら、ある制約(以下に説明される)が満たされるならば、抵抗器 5 5 0 はたとえばわずか 1 0 オームであり得る。

#### [0047]

キャパシタ 5 6 0 は充電トランジスタ 5 2 5 のゲート 5 5 5 とチャージポンピングノード 5 4 5 との間に結合される。集積回路上で、キャパシタは多くの異なった技術を用いて、かつ異なった装置から形成できる。たとえば、プロセス技術に依存して、数ある中で、トランジスタのゲートキャパシタンスと、ポリシリコンから金属導体へのキャパシタンスと、ポリシリコンから金属導体へのキャパシタンスと、ま板への n ウェル拡散とを用いてキャパシタンスが形成され得る。好ましい実施例では、キャパシタ 5 6 0 は出力ノード 4 0 5 と接地との間に結合される。キャパシタ 5 6 6 は出力ノード 4 0 5 と接地との間に結合される。キャパシタ 5 6 6 は3 分の異なった技術を用いて、かつ異なった技のの場合と同様に、キャパシタ 5 6 6 は出力ノード 4 0 5 に結合された寄生キャパシタンスであり、これはゲートと接合と出力ノード 4 0 5 に結合された寄生キャパシタンスであり、これはゲートと接合と出力ノード 4 0 5 に結合された寄生キャパシタンスを含む。例から、図 4 に示される実施例では、キャパシタ 5 6 6 はパストランジスタ 4 1 0 のゲートのキャパシタンスを含む。

動作において、メモリセル400は論理ローまたは論理ハイを記憶および出力する。データはプログラマブルメモリ素子515をプログラムすることによってメモリセル400に記憶される。プログラマブルメモリ素子515はプログラムされるかまたは消去される(プログラムされない)かの2つの状態を有する。用いられるメモリ技術に依存して、用語「プログラムされる」および「消去される」は異なった意味を有し得る。この明細書では、これらの用語に対するIEEEの慣例が用いられる。具体的に、「プログラムされる」はメモリ素子を「オフ」または不導通状態におくことを指し、「消去される」はメモリ素子を「オン」または導通状態におくことを指す。プログラムされる状態では、プログラマブルメモリ素子515は電圧源510を分離する。消去される状態では、プログラマブルメモリ素子515は電圧源510を出力ノード405に結合する。

## [0048]

メモリセル400はプログラマブルメモリ素子515に記憶されたデータを表わす出力を出力ノード405で生成する。以下にさらに詳しく説明されるプリチャージ信号がチャージポンピングノード545で入力される。このプリチャージ信号はリフレッシュ信号とかがメーード545から充電トランジスタ525を介して出力ノード405に渡される。これは出力ノード405を第1の電圧レベル、またはほぼVDDに動的に充電する(またはプリチャージする)。プログラマブルメモリ素子515がプログラムされるとき、出力ノード405は電圧源510から分離される。第1の電圧レベルに動的に保たれる出力ノード405は流ブード405は論理ハイである。キャパシタ566は出力ノード405の電荷を記憶する。マブルメモリ素子515が消去されるとき、出力ノード405はプログラマブルメモリ素子515が消去されるとき、出力ノード405でのプリチャージ電流は電圧源510またはVSSに放電される。出力ノード405でのプリティージ電流は電圧源510またはVSSに放電される。の実施例では、この発明のメモリセル400は出力ノード405にフルレール電圧出力を与え得る。

# [0049]

この発明のメモリセル400はまた、プログラマブルメモリ素子515のプログラムおよび消去をもたらす特徴を含み得る。より具体的に、EPROMセル、EEPROMセル、フラッシュEEPROMセルは不揮発性および再プログラム可能性を与えるためのフローティングゲートを有する。これらのセルをプログラムしかつ消去するために、高電圧が用いられることができ、なだれ注入、チャネル注入、量子機械的トンネリング、ホットエレクトロン、および他の現象などのようなさまざまな物理機構によって、二酸化シリコンを

介してフローティングゲートに電荷を転送し、かつそこから電荷を取除く。

## [0050]

メモリセルをプログラムするために用いられる高電圧(VPP)は、メモリセルを消去するために用いられる高電圧(VEE)とはやや異なり得る。VPPおよびVEEの大きさは、基板とフローティングゲートとの間の誘電体の厚さおよび組成のような事柄を含む、メモリセルの物理特性に依存する。典型的に、VPP電圧およびVEE電圧はほぼ12ボルトからほぼ14ボルトの範囲である。しかしながら、プロセス技術が向上し続けるにつれて、より薄く、よりよい誘電体を作成することが可能になる。したがって、メモリセルをプログラムかつ消去するために必要とされる高電圧の大きさが低下し得る。

#### [0051]

## [0052]

EPROMメモリセル、EEPROMメモリセル、およびフラッシュEEPROMメモリセルがプログラムされるとき、フローティングゲートおよびメモリセルにかけられる電荷は高電圧しきい値(VT)状態(VTP)に置かれる。プログラムされるかまたはハイVT状態では、メモリセルのゲートでの適度な電圧がメモリセルをターンオンしない。この場合、適度な電圧は集積回路の電源間の電圧、すなわちVDDおよびVSSである。さらに、電圧源510より上の電圧がゲートに与えられる場合、メモリセルはターンオンし得る。たとえば、EPROMメモリセル、EEPROMメモリセル、およびフラッシュEEPROMメモリセルでは、ハイVT状態のメモリセルに対する典型的なしきい値電圧はほぼ4ボルトである。しかしながら、ハイVT状態は4ボルトより上でもあり得る。たとえば、EPROMセルでは、ハイVT状態は約7ボルトであり得る。「支援」技術(以下説明される)を用いてプログラムされるとき、EEPROMメモリセルに対するハイVT状態は4ボルトよりもわずかに高いかもしれない。

## [0053]

対照的に、消去されるとき、電荷はフローティングゲートから取除かれ、メモリセルがローVT状態(VTE)に置かれる。消去されるかまたはローVT状態では、メモリセルのゲートでの適度な電圧がメモリセルをターンオンする。EEPROMメモリセルおよびフラッシュEEPROMメモリセルでは、ローVT状態のメモリセルに対する典型的なしきい値電圧はほぼ・2ボルトからほぼ・3ボルトに及ぶ。EPROMメモリセルでは、ローVT状態の典型的なしきい値電圧は0ボルトであるか、または0ボルトよりもわずかに上である。

# [0054]

EEPROMセルまたはフラッシュEEPROMセルが「スマート」アルゴリズムを用いて消去されるとき、具体的なローVT電圧レベル状態が達成できる。たとえば、VTEは約・1 ボルトであり得る。別の例では、VTEは0 ボルトであるか、または0 ボルトよりもわずかに上であり得る。スマートアルゴリズムは反復技術を用いてフローティングゲートから電荷を取除き、所望のVTEが達成されるまで少量の電荷を取除く。スマートアルゴリズムは負のVTEを防ぐために用いられることができ、高密度、高容量のフラッシュ

10

20

30

30

40

50

EEPROMメモリなどに対して負のVTEが不所望であるいくらかのアプリケーションにおいて特に重要であり得る。プログラマブル論理装置のような他のアプリケーションでは、特にメモリセルがメモリセルと直列に読出トランジスタを用いてアクセスできるために、負のローVT状態が容認可能であり得る。この発明はスマートアルゴリズムを用いることを必要とはしない。なぜなら、プログラマブルメモリ素子515が負のVTEを有するときにメモリセル400が適切に動作かつ機能するからである。

[0055]

また、EPROMメモリセルまたはフラッシュEEPROMのアレイが初期設定されるとき、セルはローVT状態に消去される。たとえば、EEPROMアレイは紫外光を受けるときに初期化される。フラッシュEEPROMメモリセルはバルク消去されるときに初期設定される。しかしながら、EEPROMメモリセルのアレイが初期化されるとき、セルは典型的にハイVT状態にプログラムされ得る。メモリアレイの開始状態は、メモリセル装置自体の製作とメモリセルのための意図される用途とを含んだ多くの事柄に基づいて選択される。

[0056]

制御ゲート520はプログラマブルメモリ素子515を活性化する。通常動作の間、制御 ゲート520は、プログラマブルメモリ素子515の動作を活性化かつ能動化する電圧レ ベルに結合される。活性化されるまで、プログラマブルメモリ素子515は出力ノード4 05から電圧源510を分離する。プログラマブルメモリ素子515を活性化するために 、VTEよりも大きく、VTPよりも小さい第3の電圧レベルに制御ゲート520が結合 される。たとえば、典型的なEEPROMセルでは、制御ゲート520は約-1.5ボル ト(VTE)よりも上であり、かつ約4ボルト(VTP)よりも下であるべきである。こ の発明の好ましい実施例では、最大量のプログラムおよび消去のマージンを与えるために 第3の電圧レベルがVTEとVTPとのほぼ中心の電圧に選択される。たとえば、典型 的なEEPROMメモリセルでは、制御ゲート520は約1.7ボルトから約2ボルトの 範囲に設定される。さらなる例として、EPROMでは、VTEが約0ボルトに等しく、 VTPが約7ボルトに等しい場合、制御ゲート520は第1の電圧レベル、またはVDD 、またはより高い電圧レベルに結びつけられ得る。VDDより上の活性化電圧が用いられ 得るのは、たとえば、これがメモリ素子によって必要とされ得るか、またはより高い電圧 レベルが容易に利用可能であるためである。制御ゲート520はまたプログラマブルメモ リセル 5 1 5 をプログラムする間に用いられる。プログラマブルメモリセル 5 1 5 のプロ グラムのさらなる検討は以下に与えられる。

[0057]

図 6 は、チャージポンピングノード 5 4 5 に結合されるプリチャージ信号 6 2 0 のタイミング図を示す。プリチャージ信号 6 2 0 は、メモリセル 4 0 0 の通常動作の間チャージポンピングノード 5 4 5 に与えられる周期的な信号である。プリチャージ信号 6 2 0 は出力ノード 4 0 5 をほぼ第 1 の電圧レベルに動的に充電する。

[0058]

プリチャージ信号 6 2 0 は T o f f 6 3 0 の期間の間ほぼ第 1 の電圧レベルである。 T o n 6 4 0 の期間では、プリチャージ信号 6 2 0 は第 1 の電圧レベル 6 4 8 より上の第 4 の電圧レベル 6 4 5 にパルス 6 4 2 を有する。プリチャージ信号 6 2 0 の周期は T o n + T o f f である。 V 6 5 0 は第 1 の電圧レベル 6 4 8 と第 4 の電圧レベル 6 4 5 との間の差である。 V 6 5 0 は約 3 . 5 ボルトであり得る。以下の検討では、図 5 も参照されたい。 T o n 6 4 0 の期間の間、充電トランジスタ 5 2 5 のゲート 5 5 5 は第 4 の電圧レベルに結合される。 充電トランジスタ 5 2 5 はわずかにターンオンし、チャージポンピングノード 5 4 5 から出力ノード 4 0 5 にプリチャージ電流  $I_{T1}$ をわたす。 このプリチャージ電流はマイクロアンペアのオーダであり得る。ある実施例では、プリチャージ電流は約 2 マイクロアンペアである。

[0059]

パルス 6 4 2 は以下の制約に適うように選択される。 V<sub>T1</sub>は充電トランジスタ 5 2 5 に対

するしきい値電圧である。より具体的に、 $V_{\tau 1}$ は充電トランジスタ525をわずかにターンオンするための、ゲート555の電圧である。メモリセル400のキャパシタンスは以下のように $V_{\tau 1}$ に関連している。

[0060]

【数1】

$\Delta Vg = (C1/(C1+Cg))*\Delta V \ge V_{T1}$

[0061]

Vgはパルス642の結果としてゲート555に結合する電圧である。 Vgはゲート555でのキャパシタンスのキャパシタンス分割器によって V650に関連づけられる。C1はキャパシタ560のキャパシタンスを表わす。Cgは充電トランジスタ525のゲートキャパシタンスを表わす。

[0062]

Ton640の間、充電トランジスタ525をターンオフするために充電トランジスタ525のゲート電圧が出力ノード405の電圧と釣り合わないように、抵抗器550は出力ノード405からの十分な孤立を与える。より具体的に、ゲート555の電圧はキャパシタ560を介してその初期電圧より上の電圧 Vgに結合される。したがって、 Vg電圧の変化およびパルス642が出力ノード405にもれないように、抵抗器550はRC遅延を与える。したがって、Ton640の間、ゲート555と出力ノード405との間に電圧差があり得る。このために充電トランジスタ525がオン状態に維持される。充電トランジスタ525がオンである間、プリチャージ電流  $I_{T1}$  は量 Vpだけ出力ノード405を充電する。上の関係は以下によって表わされる。

[0063]

【数2】

$(R1*Ct)>(Ct*(\Delta Vb/I_{TI}))$  および

Ton =  $Ct * \Delta Vb / I_{T1}$

[0064]

C t はキャパシタ 5 6 6 のキャパシタンスを表わす。 R 1 は抵抗器 5 5 0 の抵抗を表わす。必要な R C 遅延が得られる限り R 1 がどのような値であってもよい。たとえば、ある実施例では R 1 は 1 0 オームである。

[0065]

Toff630の間、抵抗器550を通る電流の流れは充電トランジスタ525のゲート電圧を出力ノード405の電圧と釣り合わさせるはずである。特に、(定常状態での)通常動作の間、出力ノード405はほぼ(チャージポンピングノード545での)第1の電圧レベル648にVTを加えたものである。充電トランジスタ525のゲート555への、抵抗器550のフィードバック接続を介して、この発明のメモリセルはこの特定の電圧を維持するために自己調整する。たとえば、電圧がこの値より上に上がれば、525を通るプリチャージ電流は出力ノード405で一定の電圧レベルを維持するためにわずかに下げられる。実際、出力ノード405の電圧が極めて高くなれば、電流が出力ノード405から充電トランジスタ525を介してチャージポンピングノード545に流れ得る。出力ノード405の電圧が特定の値よりも下に下がれば、525を通るプリチャージ電流は出力ノード405で一定の電圧レベルを維持するためにわずかに上げられる。この関係は以下によって与えられる。

[0066]

【数3】

10

20

30

40

# (R1\*(C1+Cg)) < Toff

## [0067]

集積回路のための電力消費を最小にするために、充電電流  $I_{T1}$  と充電トランジスタ525を通る漏れ電流( $I_{J}$  leak )とがチップのための相対的に小さい電力消費源にとどまるべきである。プログラマブル素子515が消去されるとき、 $I_{T1}$  は充電トランジスタ525およびプログラマブル素子515を通る電流を表わす。プログラマブル素子515がプログラムされるとき、 $I_{J}$  leak は出力 J ード405をVDD+VTに維持するために必要な電流を表わす。集積回路は多数の、すなわちN個のメモリセルを含んでもよく、Nは100万個以上ものメモリセル400であってもよい。この場合、全体の時間平均電流は1ミリアンペア未満であるべきである。メモリセルの部分N1がプログラムされ、部分N2が消去される。N1およびN2の和がNと等しい。したがって、以下のとおりである。

[0068]

## 【数4】

$$(N1 * I_{T1} * (Ton / (Ton + Toff))) +$$

$(N2 * Ijleak * Toff / (Ton + Toff)) < 1 mA$

20

30

## [0069]

上の式を解くことによって、メモリセルパラメータの設計に対する多くの起こり得る解が 求められ得る。たとえば、パラメータの次の組が上の制約を満たす。

[0070]

## 【表1】

| Ct = 20fF         | C1 = 0.5 fF     | Cg = 1.5fF         |

|-------------------|-----------------|--------------------|

| $V_{T1} = 1V$     | $\Delta V = 4V$ | $\Delta Vb = 0.1V$ |

| $I_{T1} = 1\mu A$ | Ton = 50ns      | Toff = 1ms         |

| R1 = 1メカ・オーム      | N=100万          |                    |

### [0071]

これらのパラメータによって示されるように、パルス持続時間TonはToffの持続時間よりも実質的に短いかもしれない。

## [0072]

始めに出力ノード405を充電するとき、このノードの電圧は出力ノード405がほぼ第1の電圧レベル648にVTを加えたものになるまでゆっくりと上昇する。ある実施例では、出力ノード405はプリチャージ信号620の約20個のパルス648でほぼこのレベルまで充電され得る。出力ノード405を初期設定するための充電時間は約1ミリ秒であり得る。プリチャージ信号620の周波数と設計の具体的なパラメータとに依存して、この時間は1ミリ秒よりも多いかまたは少なくてもよい。メモリセル400のアレイは共通のプリチャージ信号620を用いて充電され得る。これは、この発明のメモリセル400を用いて設計の実現を簡単にする。

## [0073]

さらに、プリチャージ信号 6 2 0 のパルス 6 4 2 はメモリセル 4 0 0 の異なった行および列に対してずらされ得る。プリチャージ信号 6 2 0 のパルス 6 4 2 をずらすことによって

50

30

40

50

、より少ない電流がどんな瞬間においてもアレイをプリチャージするために必要とされる。たとえば、メモリセル400のある行が第1のプリチャージ信号620でプリチャージ信号620でプリチャージ信号620に対してずらされている第2のプリチャージ信号620でプリチャージ信号620のパルス642が第1のプリチャージ信号620のパルス642と同時に起こらないことを示す。より具体的に、第2のプリチャージ信号620のパルス642は第1のプリチャージ信号620のパルス642は第1のプリチャージ信号620のパルス642の少し後に起こり得る。さらなる例として、300列のメモリセル400のアレイでは、プリチャージ信号620は瞬間電流流出を最小にするために異なった列に対してずらされる。メモリセル400の1列当りの電流流出は1ミリアンペアであり得、これは全体のチップに対する瞬間的なプリチャージ電流流出である。したがって、プリチャージ信号620をずらすことによって、メモリセル400のより大きなアレイが作られ得る。

[0074]

出力ノード405が充電された後、プログラマブルメモリ素子515がオフ状態にあるときに電圧源510が出力ノード405から分離される。プリチャージ信号620は出力ノード405に電圧ブースト(パルス642)を与えて、この電圧レベルをほぼVDD+VTに維持する。この電圧ブーストはまた、出力ノード405でVDD+VTを維持するのに足る、出力ノード405でのいかなる漏れ電流をも補う。さらに、図4に示される構成では、VDD+VTがパストランジスタ410のゲートに与えられるので、これがGH210とGV200との間にフルレール信号をわたし、これもまた過渡性能を向上させる。

[0075]

プログラマブルメモリ素子515がオフ状態にあるとき、プログラマブルメモリ素子515のフローティングゲートとチャネルとの間の電界が減少される。具体的に、(EEPROMまたはフラッシュEEPROMのような)フローティングゲートメモリセルが用いられるとき、フローティングゲートは(フローティングゲート妨害現象と称される)チャネル・基板バイアスを受けない。この発明において、プログラマブルメモリ素子515のチャネルは0ボルトまたはカットオフである。チャネル・基板バイアスはエレクトロン・ホールの対を発生する。このエレクトロンはフローティングゲートに引きつけられ、これがメモリセルを妨害し、装置の寿命を低下させる。したがって、VDDが5ボルトであるときでも、この発明のメモリセル400は優れたデータ保存および信頼性の特性を有する。

[0076]

プログラマブルメモリ素子 5 1 5 がオフ状態にあるとき、電圧源 5 1 0 は出力ノード 4 0 5 から分離される。したがって、出力ノード 4 0 5 の電圧は V S S である。結果として、充電トランジスタ 5 2 5 はオフである。チャージポンピングノード 5 4 5 から充電トランジスタ 5 2 5 およびプログラマブルメモリ素子 5 1 5 を介して V S S への D C 経路がない。パルス 6 4 2 の間、充電トランジスタ 5 2 5 を通るプリチャージ電流  $I_{T1}$  はプログラマブルメモリ素子 5 1 5 を介して電圧源 5 1 0 に放電され得る。出力ノード 4 0 5 はほぼ電圧源 5 1 0 のレベル、典型的に V S S にとどまる。プログラマブルメモリ素子 5 1 5 を介して放電される電流の量を現象させ、集積回路の電力消費をも減少させるために、 $I_{T1}$  および T o D n 6 4 0 が最小にされるべきである。

[0077]

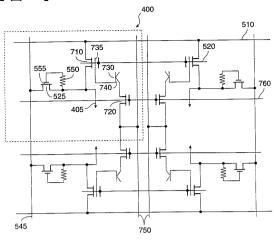

図 7 はメモリセル 4 0 0 のアレイのレイアウトを示す。この実施例では、メモリセル 4 0 0 は E E P R O M メモリセルを用いて実現される。図 7 は 4 つのメモリセル 4 0 0 を示す。メモリセル 4 0 0 のより大きなアレイは同様のレイアウト方法論を用いて構成できる。

[0078]

図 7 のメモリセル 4 0 0 は図 5 のメモリセル 4 0 0 の実施例である。図 7 では、プログラマブルメモリ素子 5 1 5 は単一または二重のポリシリコン E E P R O M セル 7 1 0 を用いて実現される。さらに、図 7 のメモリセル 4 0 0 は付加的なトランジスタおよび信号ラインを含んで E E P R O M セル 7 1 0 のプログラムに備える。図を簡略化するために、キャパシタ 5 6 0 および 5 6 6 が示されない。しかしながら、これらのキャパシタンスは図 5

20

30

40

50

に示されるような位置で図 7 のメモリセル 4 0 0 に存在する。これらのキャパシタンスも上述されたものと同じ目的を担う。

## [0079]

## [0800]

図 5 のメモリセル 4 0 0 は図 7 のメモリセル 4 0 0 と実質的に同様に動作する。 E E P R O M セル 7 1 0 はメモリセル 4 0 0 のデータを記憶するように構成される。メモリセル 4 0 0 に記憶されたデータは出力ノード 4 0 5 で出力される。初期設定されるとき、 E E P R O M セルのアレイはハイ V T 状態にバルクプログラムされる。 E E P R O M セルに対する典型的な V T P は約 4 ボルトから約 5 ボルトである。 ハイ V T 状態では、 E E P R O M セルはそのソース端子からそのドレイン端子を分離する。 ロー V T 状態に消去されるとき、 E E P R O M セルはそのドレイン端子をそのソース端子に結合する。 E E P R O M セルに対する典型的な V T E は約 - 1 . 5 ボルトである。上述のスマートアルゴリズムはまた、 約 0 ボルトの V T E を得るために E E P R O M を消去するのに用いられ得る。

## [0081]

EEPROMセル710を適切に構成することによって、メモリセル400は論理ハイまたは論理ローを記憶する。この発明では上述のように、出力ノード405が、チャージポンピングノード545から充電トランジスタ525を通るプリチャージ電流によって第1の電圧レベルまたはVDDに動的に充電される。論理ハイを記憶するためには、EEPROMセル710がプログラムされたままにとどまる。次に、出力ノード405が動的に充電され、キャパシタ566によってほぼ第1の電圧レベルに保たれる。出力ノード405の電圧はプリチャージ信号620によって周期的にリフレッシュされる。論理ローを記憶するためには、EEPROM710が消去される。出力ノード405の電荷はEEPROMセル710を介して電圧源510に放電される。出力ノード405は、第2の電圧レベルまたはVSSである電圧源510にほぼ等しい。したがって、メモリセル400は出力ローを出力する。

## [0082]

制御ゲート520はEEPROMセル710を活性化する。上述のように、通常動作の間、制御ゲート520はEEPROMセル710のVTEとVTPとの間の電圧に設定されて、プログラムおよび消去のマージンの量を最大にする。ある実施例では、この電圧はほぼ1.7ボルトから2ボルトの範囲である。

### [0083]

制御ゲート 5 2 0 はまた、EEPROMセル 7 1 0 のプログラムの間に用いられる。EEPROMセル 7 1 0 を初期設定する(プログラムする)ために、制御ゲート 5 2 0 はVPPに設定される。消去 ノード 7 5 0 は接地される。選択ゲート 7 6 0 は選択トランジスタ 7 2 0 をターンオンするための電圧に設定される。選択ゲート 7 2 0 は典型的には約 2 ボルトの電圧に設定されるが、2 ボルトから V D D の範囲のどんな電圧も選択トランジスタ 7 2 0 をターンオンする。電圧源 5 1 0 およびチャージポンピングノード 5 4 5 は接地される。これらの状況下で、エレクトロンはEEPROMセル 7 1 0 のトンネルダイオード 7 4 0 からトンネル誘電体 7 3 0 を介してフローティングゲート 7 3 5 に通り抜ける。フローティングゲート 7 3 5 は、EEPROMセル 7 1 0 がハイ V T 状態にプログラムされるように負に充電される。これはEEPROMセル 7 1 0 のアレイにおいてすべてのビッ

30

40

50

トをプログラムするために広域的に行なわれる。

## [0084]

支援プログラム技術を用いることによって、VTPがより高い値にブーストされ得る。支援プログラムでは、電圧源510はほぼVDDの支援電圧に設定される。チャージポンピングノード545は浮動させられる。制御ゲート520がVPPであるので、出力ノード405もVDDである。チャージポンピングノードは充電トランジスタ525(オンである)を介してVDD・VDに浮動する。これらの状況下で、フローティングゲートの初期電圧をブーストする、EEPROMセル710のチャネルを介してフローティングゲート735に結合する付加的な電圧がある。フローティングゲートの初期電圧がより高いとして生じるVTP電圧は高くなる。したがって、支援なしのプログラム状況下よりも、より多くのエレクトロンがフローティングゲート735にとらわれる。さらに、支援電圧がフローティングゲート735に結合する電圧を高めるためにVDDよりも上であり得る。たとえば、支援電圧はほぼVPPであってもよい。

## [0085]

EEPROMセルは量子機械的トンネリングを用いてプログラムされる。量子機械的トンネリングを用いることによって、たとえば、典型的にホットエレクトロンを用いてプログラムされるフラッシュEEPROMセルよりも実質的に少ない電流がEEPROMセルをプログラムするために必要とされる。EEPROMセルがプログラムされるのは、主に、非常に薄い(典型的に酸化膜の70 から80 )誘電体にかかる高電圧の大きさによる。したがって、高い電流が必要ではないので、EEPROMセルを用いると一般に、多くの電流がしばしば利用不可能である、ときにはイン・システムプログラム(ISP)と称される、システム基板上に存在して構成できる集積回路がもたらされる。

### [0086]

量子機械的トンネリングはまたEEPROMセル710を消去するために用いられる。EEPROMセルは選択的に消去される。たとえば、EEPROMセル710を消去するために、選択ゲート760がVEE+VT(選択トランジスタ720のしきい値電圧)に設定される。消去ノード750はVEEに結合される。制御ゲート520および電圧源510は接地される。VEEは選択トランジスタ720を通ってトンネルダイオード740にわたされる。EEPROMセル710のフローティングゲート735からのエレクトロンはトンネル誘電体730を通ってトンネルダイオード740に引きつけられる。これがEEPROMセル710のフローティングゲート735からエレクトロンを取り除く。このように、EEPROM710がローVT状態に消去される。EEPROMセル710のアレイでは、所望のパターンがアレイに与えられるまでこの動作が行ごとまたは列ごとに繰返される。

# [0087]

EEPROMセル710を消去するとき、負の支援プログラム技術が負の支援電圧を制御ゲート520に与えることによって用いられ得る。たとえば、 - 3 ボルトの電圧が制御ゲート520に与えられ得る。このためにVTEが低下され、EEPROMセル710の消去のマージンを高める。

# [ 0 0 8 8 ]

EEPROMセルのアレイは、プログラムを確かめ、ビットの状態を消去するためにモニタされ得る。プログラムのマージンを確かめるために、消去ノード750が接地される。電圧源510は一度に1つ2ボルトに設定される。EEPROMセル710が導通し始め、かつチャージポンピングノード545が導通し始めるまで、確かめられるセルの行に対応する制御ゲート520の電圧ははき出される。この手順のために、EEPROMセル710の1つの行が一度に確かめられる。その行のビットのすべてがチャージポンピングノード545を介して確かめられる。

## [0089]

図7はまた、集積回路区域を節約するようにメモリセル400のアレイのレイアウトがい

30

40

50

かに組織かつ小型化できるかを示す。複数個の信号が第1の方向にあり、複数個の信号が第2の方向にある。第1の方向の信号は第2の方向の信号を実質的に横断する。第1の方向において、信号は電圧源510、制御ゲート520、および選択ゲート760を含む。第2の方向において、信号はチャージポンピングノード545、出力ノード405、および消去ノード750を含む。

## [0090]

この構成はメモリセル400の信号ラインの効率的なレイアウトおよび配線を与える。さらに、信号の配置は集積回路において信号の効率的な配線を容易にする。たとえば、制御ゲート520の信号ラインがEEPROMセルの行によって共有されていることに注目されたい。また、消去ノード750がEEPROMセルの列によって共有される。これらの特徴がより小型のレイアウトをもたらす。さらに、EEPROMセルが単一の動作で容易にハイVT状態に初期設定できるように信号ラインが配列される。

#### [0091]

この発明の制御ラインは格子システムを用いて組織される。これがメモリセル400のより簡単なプログラム、消去、および読出をもたらす。たとえば、メモリセル400のアレイが構成されるまでメモリセル400は一度に多くのビットを構成できる。具体的に、選択ゲート760にVEE+VTを与え、制御ゲート520を接地した後で、メモリ400は適切な消去ノード750にVEEおよび接地を与えることによって選択的に構成できる。この技術を用いて、複数個のメモリセル400が同時に構成される。

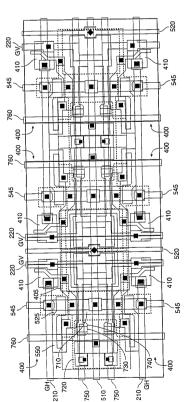

## [0092]

図8は図4のプログラマブル相互接続回路を実現するレイアウトを示す。図8において、メモリセル400は図7に示されるようなEEPROMメモリセルを用いて実現される。6つのEEPROMメモリセル400と6つのパストランジスタ410がある。より大きなアレイが、水平方向および垂直方向に構造およびジオメトリを繰返し、かつ映すことによって構成できる。

## [0093]

メモリセル 4 0 0 では、パストランジスタ 4 1 0 が G H 2 1 0 と G V 2 2 0 との間に結合される。パストランジスタ 4 1 0 のポリシリコンゲートはメモリセル 4 0 0 の出力ノード 4 0 5 に結合される。G H 2 1 0 はレイアウトの第 1 の方向に延び、G V 2 2 0 はレイアウトの第 2 の方向で、第 1 の方向に横断して延びる。メモリセル 4 0 0 は E E P R O M セル 7 1 0、抵抗器 5 5 0、充電トランジスタ 5 2 5、および選択トランジスタ 7 2 0 からなる。この実施例では、抵抗器 5 5 0 がポリシリコンを用いて形成される。レイアウトの第 1 の方向では、このメモリセルに対する信号が電圧源 5 1 0、消去ノード 7 5 0、および G H 2 1 0 にある。レイアウトの第 2 の方向では、制御信号が選択ゲート 7 6 0、チャージポンピングノード 5 4 5、制御ゲート 5 2 0、および G V 2 2 0 にある。選択トランジスタ 7 2 0 はトンネルウィンドウ 7 3 0 およびトンネルダイオード 7 4 0 を経てそのそれぞれの E E P R O M セル 7 1 0 のフローティングゲート 7 3 5 に結合される。

## [0094]

この発明の好ましい実施例の上述の説明は例示および説明の目的のために提示された。これはこの発明を網羅するものでも上述のその形に限定するものでもないことが意図され、多くの変更および変化が上の教示を考慮して可能である。実施例は、この発明の原則とその実用的なアプリケーションとを最良に説明し、これによって、予期される特定の用途に適したさまざまな実施例およびさまざまな変更でもって、当業者がこの発明を最良に利用することを可能にするよう選択かつ説明された。この発明の範疇は前掲の特許請求の範囲によって規定されることが意図される。

## 【図面の簡単な説明】

【図1】プログラマブル論理装置集積回路を組入れたデジタルシステムのブロック図である。

- 【図2】プログラマブル論理装置の全体のアーキテクチャを示すブロック図である。

- 【図3】プログラマブル論理装置の論理アレイブロック(LAB)の簡略化されたブロッ

ク図である。

- 【図4】プログラマブル論理装置のプログラマブル相互接続において用いられる、この発明のメモリセルの図である。

- 【図5】この発明のメモリセルのブロック図である。

- 【図6】この発明のメモリセルに対するプリチャージ信号波形のタイミング図である。

- 【図7】 E E P R O M セルを用いて実現された、この発明のメモリセルの小さいアレイを示す図である。

- 【図8】プログラマブル相互接続を実現するために用いられた、この発明のメモリセルのアレイのレイアウト図である。

## 【符号の説明】

400 メモリセル

405 出力ノード

5 1 0 電圧源

5 1 5 プログラマブルメモリ素子

525 充電トランジスタ

5 4 5 チャージポンピングノード

# 【図2】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# フロントページの続き

(72)発明者 ラミンダ・ユー・マドゥラウェ アメリカ合衆国、94087 カリフォルニア州、サニーベイル、ルイーズ・ドライブ、882

審査官 滝谷 亮一

(56)参考文献 特開平07-183385(JP,A)

特開平03-154516(JP,A)

特開平03-125398(JP,A)

特開平02-130798(JP,A)

伊藤清男,超LSIメモリ,日本,培風館,1994年11月 5日,初版,P.151-15 5

(58)調査した分野(Int.CI., DB名)

G11C16/02-16/06

H03K 19/173

H03K 19/177