(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5098619号

(P5098619)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年10月5日(2012.10.5)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G09G 3/20 (2006.01)**

**G02F 1/133 (2006.01)**

G09G 3/36

G09G 3/20 621 F

G09G 3/20 612 U

G09G 3/20 623 C

G09G 3/20 621 B

請求項の数 13 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2007-321098 (P2007-321098)

(22) 出願日

平成19年12月12日(2007.12.12)

(65) 公開番号

特開2009-145492 (P2009-145492A)

(43) 公開日

平成21年7月2日(2009.7.2)

審査請求日

平成22年9月8日(2010.9.8)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100095441

弁理士 白根 俊郎

(74) 代理人 100084618

弁理士 村松 貞男

最終頁に続く

(54) 【発明の名称】表示駆動装置及びそれを備えた表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画素電極と、該画素電極に対向する対向電極と、前記画素電極と前記対向電極との間に充填された液晶と、を有してなる表示画素を、表示データに基づいて所定の選択期間毎に表示駆動する表示駆動装置において、

前記表示データの階調数に応じた複数の階調電圧を発生する階調電圧発生回路と、

前記選択期間内に、前記表示データの階調値に応じて前記階調電圧発生回路で発生された前記複数の階調電圧の何れかを選択して出力し、前記画素電極に印加して、前記表示画素に前記画素電極と前記対向電極との間の電位差による表示信号電圧を書き込む書き込み回路と、

を具備し、

前記選択期間のうちの初期の期間からなる補正期間において、前記書き込み回路から出力される前記階調電圧を、前記表示信号電圧の絶対値が大きくなる方向に、前記表示データの階調値に応じたシフト量だけシフトした補正階調電圧とする補正手段を有し、

前記階調電圧発生回路は、上限電圧と下限電圧との間に直列接続された複数の分圧抵抗によって、前記上限電圧と前記下限電圧との間の電位差を分圧して前記複数の階調電圧を発生する分圧回路と、前記補正期間において、前記上限電圧又は前記下限電圧の何れか一方の電圧を、前記表示信号電圧の絶対値が大きくなる方向にシフトした電圧値を有するシフト電圧に切り替える手段と、を有する、

ことを特徴とする表示駆動装置。

10

20

**【請求項 2】**

前記表示信号電圧は前記選択期間毎に極性が反転されるように制御され、

前記階調電圧発生回路は、前記選択期間のうちの前記補正期間中であるか否かを示す補正制御信号及び前記表示信号電圧の極性を示す極性制御信号が供給され、前記補正制御信号及び前記極性制御信号に応じて、前記上限電圧又は前記下限電圧の何れか一方を前記シフト電圧にするか否かを切り替える切替回路を備えることを特徴とする請求項 1 に記載の表示駆動装置。

**【請求項 3】**

前記階調電圧発生回路は、更に、前記分圧回路における前記複数の分圧抵抗に並列に設けられる、前記複数の分圧抵抗の抵抗値より小さい抵抗値を有する、直列接続された複数の補助抵抗と、遅延制御信号が供給され、該遅延制御信号に応じて、前記補正期間及び該補正期間終了直後の期間において、前記複数の補助抵抗を前記複数の分圧抵抗に並列に接続する手段と、を有することを特徴とする請求項 2 に記載の表示駆動装置。

10

**【請求項 4】**

前記補正階調電圧は階調毎に異なる値を有し、

前記シフト量は、前記表示データの階調値が前記表示信号電圧の絶対値が最も大きくなる値であるときに最も大きい値に設定されることを特徴とする請求項 1 に記載の表示駆動装置。

**【請求項 5】**

前記階調電圧発生回路は、前記表示データの階調に対応した階調電圧に加えて、前記階調電圧の最大の電圧よりも高い電圧及び前記階調電圧の最小の電圧より低い電圧を有するシフト階調電圧を発生する手段を有し、

20

前記書き込み回路は、前記補正期間においては、前記複数の階調電圧から前記表示データの階調値より前記表示信号電圧の絶対値が大きくなる側の階調に対応した前記階調電圧又は前記表示信号電圧の絶対値が大きくなる側の前記シフト階調電圧を選択して、前記補正階調電圧として出力する手段を有することを特徴とする請求項 1 又は 4 に記載の表示駆動装置。

**【請求項 6】**

前記表示信号電圧は前記選択期間毎に極性が反転されるように制御され、

前記書き込み回路は、前記選択期間のうちの前記補正期間中であるか否かを示す補正制御信号及び前記表示信号電圧の極性を示す極性制御信号が供給され、該補正制御信号及び前記極性制御信号に応じて、出力する電圧を、前記補正階調電圧とするか否かを切り替える選択回路を備えることを特徴とする請求項 5 に記載の表示駆動装置。

30

**【請求項 7】**

前記選択回路は、前記表示データの階調値が少なくとも中間調より前記表示信号電圧の絶対値が大きくなる側の階調であるときに、前記補正期間において、前記補正階調電圧を選択して出力することを特徴とする請求項 6 に記載の表示駆動装置。

**【請求項 8】**

複数の走査ライン及び複数の信号ラインの各交点に対応してマトリクス状に配列され前記走査ライン及び前記信号ラインに電気的に接続された画素電極と、該画素電極に対向する対向電極と、前記画素電極と対向電極との間に充填された液晶と、を有してなる複数の表示画素を有する表示パネルと、

40

前記複数の走査ラインを所定の選択期間毎に順次選択する走査線駆動回路と、

表示データの階調数に応じた複数の階調電圧を発生する階調電圧発生回路と、前記走査線駆動回路による前記各走査ラインの前記選択期間内に、前記表示データの階調値に応じて前記階調電圧発生回路で発生された前記複数の階調電圧の何れかを選択して前記複数の信号ラインに出力して、当該選択された走査ラインの前記各表示画素に前記画素電極と前記対向電極との間の電位差による表示信号電圧を書き込む書き込み回路と、を有する信号線駆動回路と、

を備え、

50

前記信号線駆動回路は、前記選択期間のうちの初期の期間からなる補正期間において、前記書き込み回路から出力される前記階調電圧を、前記表示信号電圧の絶対値が大きくなる方向に、前記表示データの階調値に応じたシフト量だけシフトした補正階調電圧とする補正手段を有し、

前記階調電圧発生回路は、上限電圧と下限電圧との間に直列接続された複数の分圧抵抗によって、上記上限電圧と下限電圧との間の電位差を分圧して前記複数の階調電圧を発生する分圧回路と、前記補正期間において、前記上限電圧又は前記下限電圧の何れか一方の電圧を、前記表示信号電圧の絶対値が大きくなる方向にシフトした電圧値を有するシフト電圧に切り替える手段と、を有する、

ことを特徴とする表示装置。

10

#### 【請求項 9】

前記表示装置は、更に、前記選択期間のうちの前記補正期間中であるか否かを示す補正制御信号及び前記表示信号電圧の極性を示す極性制御信号を出力する制御回路を備え、

前記表示信号電圧は前記選択期間毎に極性が反転されるように制御され、

前記階調電圧発生回路は、前記制御回路から前記補正制御信号及び前記極性制御信号が供給され、前記補正制御信号及び前記極性制御信号に応じて、前記上限電圧又は前記下限電圧の何れか一方を前記シフト電圧にするか否かを切り替える切替回路を備えることを特徴とする請求項 8 に記載の表示装置。

#### 【請求項 10】

前記階調電圧発生回路は、更に、前記分圧回路における前記複数の分圧抵抗に並列に設けられる、前記複数の分圧抵抗の抵抗値より小さい抵抗値を有する、直列接続された複数の補助抵抗と、遅延制御信号が供給され、該遅延制御信号に応じて、前記補正期間及び該補正期間終了直後の期間において、前記複数の補助抵抗を前記複数の分圧抵抗に並列に接続する手段と、を有することを特徴とする請求項 9 に記載の表示装置。

20

#### 【請求項 11】

前記補正階調電圧は階調毎に異なる値を有し、

前記シフト量は、前記表示データの階調値が前記表示信号電圧の絶対値が最も大きくなる値であるときに最も大きい値に設定されることを特徴とする請求項 8 に記載の表示装置。

#### 【請求項 12】

30

前記階調電圧発生回路は、前記表示データの階調に対応した階調電圧に加えて、前記階調電圧の最大の電圧よりも高い電圧及び前記階調電圧の最小の電圧よりも低い電圧を有するシフト階調電圧を発生する手段を有し、

前記書き込み回路は、前記補正期間においては、前記複数の階調電圧から前記表示データの階調値より前記表示信号電圧の絶対値が大きくなる側の階調に対応した前記階調電圧又は前記表示信号電圧の絶対値が大きくなる側の前記シフト階調電圧を選択して、前記補正階調電圧として出力する手段を有することを特徴とする請求項 8 又は 11 に記載の表示装置。

#### 【請求項 13】

40

前記表示装置は、更に、前記選択期間のうちの前記補正期間中であるか否かを示す補正制御信号及び前記表示信号電圧の極性を示す極性制御信号を出力する制御回路を備え、

前記表示信号電圧は前記選択期間毎に極性が反転されるように制御され、

前記書き込み回路は、前記制御回路から前記補正制御信号及び前記極性制御信号が供給され、前記補正制御信号及び前記極性制御信号に応じて、出力する電圧を、前記補正階調電圧とするか否かを切り替える選択回路を備えることを特徴とする請求項 12 に記載の表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、例えばアクティブマトリクス型の駆動方式に対応した表示パネルを駆動する

50

表示駆動装置、及び、そのような表示駆動装置を備えた表示装置に関する。

【背景技術】

【0002】

近年、コンピュータや携帯電話、携帯情報端末等の情報機器や、デジタルビデオカメラやデジタルスチルカメラ、スキャナ等の画像処理関連機器の普及が著しい。このような機器においては、表示手段として液晶表示装置（Liquid Crystal Display；LCD）が多用されるようになっている。

【0003】

例えば、アクティブマトリクス液晶表示装置においては、薄膜トランジスタ等の画素トランジスタを備えた表示画素（液晶画素）がマトリクス状に配列され、各表示画素を行方向に接続する走査ラインと列方向に接続する信号ラインとを備えた液晶表示パネルに対して、ゲートドライバにより各走査ラインを順次選択状態とし、ソースドライバにより各信号ラインに所定の信号電圧を印加して、選択状態にある表示画素に対して画像情報に応じた信号電圧を書き込むことにより、各表示画素における液晶の配向状態を制御して所望の画像情報を所定のコントラストで表示するように構成されている。

10

【0004】

このようなアクティブマトリクス液晶表示装置の液晶駆動方法としては、例えば特許文献1に開示されているように、1水平期間のある時間だけ信号ラインを表示画素に書き込む一番高い電圧にプリチャージし、残りの時間で目的の電圧に書き込むようにする駆動方法がある。

20

【特許文献1】特開平7-121139号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年、液晶表示装置の高精細化が進んでおり、それについて1水平期間の時間が短くなっている。

【0006】

前記特許文献1に開示されているような駆動方法では、常に最大電圧にプリチャージしているため、目的の電圧が高ければ良いが、低い場合には、そのプリチャージされた最大電圧から目的の電圧に書き込むための書き込み時間が足りなくなるおそれがある。

30

【0007】

本発明は、前記の点に鑑みてなされたもので、表示データの各階調において、書き込み時間を短縮して、高精細化を可能とする表示駆動装置及びそれを備えた表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上述した目的を達成するため、この発明の表示駆動装置の一様態は、画素電極と、該画素電極に対向する対向電極と、前記画素電極と前記対向電極との間に充填された液晶と、を有してなる表示画素を、表示データに基づいて所定の選択期間毎に表示駆動する表示駆動装置において、前記表示データの階調数に応じた複数の階調電圧を発生する階調電圧発生回路と、前記選択期間内に、前記表示データの階調値に応じて前記階調電圧発生回路で発生された前記複数の階調電圧の何れかを選択して出力し、前記画素電極に印加して、前記表示画素に前記画素電極と前記対向電極との間の電位差による表示信号電圧を書き込む書き込み回路と、を具備し、前記選択期間のうちの初期の期間からなる補正期間において、前記書き込み回路から出力される前記階調電圧を、前記表示信号電圧の絶対値が大きくなる方向に、前記表示データの階調値に応じたシフト量だけシフトした補正階調電圧とする補正手段を有し、前記階調電圧発生回路は、上限電圧と下限電圧との間に直列接続された複数の分圧抵抗によって、前記上限電圧と前記下限電圧との間の電位差を分圧して前記複数の階調電圧を発生する分圧回路と、前記補正期間において、前記上限電圧又は前記下限電圧の何れか一方の電圧を、前記表示信号電圧の絶対値が大きくなる方向にシフトした

40

50

電圧値を有するシフト電圧に切り替える手段と、を有する、ことを特徴とする。

【0009】

また、上述した目的を達成するため、この発明の表示装置の一様態は、複数の走査ライン及び複数の信号ラインの各交点に対応してマトリクス状に配列され前記走査ライン及び前記信号ラインに電気的に接続された画素電極と、該画素電極に対向する対向電極と、前記画素電極と対向電極との間に充填された液晶と、を有してなる複数の表示画素を有する表示パネルと、前記複数の走査ラインを所定の選択期間毎に順次選択する走査線駆動回路と、表示データの階調数に応じた複数の階調電圧を発生する階調電圧発生回路と、前記走査線駆動回路による前記各走査ラインの前記選択期間内に、前記表示データの階調値に応じて前記階調電圧発生回路で発生された前記複数の階調電圧の何れかを選択して前記複数の信号ラインに出力して、当該選択された走査ラインの前記各表示画素に前記画素電極と前記対向電極との間の電位差による表示信号電圧を書き込む書き込み回路と、を有する信号線駆動回路と、を備え、前記信号線駆動回路は、前記選択期間のうちの初期の期間からなる補正期間において、前記書き込み回路から出力される前記階調電圧を、前記表示信号電圧の絶対値が大きくなる方向に、前記表示データの階調値に応じたシフト量だけシフトした補正階調電圧とする補正手段を有し、前記階調電圧発生回路は、上限電圧と下限電圧との間に直列接続された複数の分圧抵抗によって、上記上限電圧と下限電圧との間の電位差を分圧して前記複数の階調電圧を発生する分圧回路と、前記補正期間において、前記上限電圧又は前記下限電圧の何れか一方の電圧を、前記表示信号電圧の絶対値が大きくなる方向にシフトした電圧値を有するシフト電圧に切り替える手段と、を有する、ことを特徴とする。10

【発明の効果】

【0023】

本発明によれば、選択期間のうちの初期の補正期間中には、表示データの階調値に応じた正規の階調電圧より液晶印加電圧の絶対値が大きくなる側に、表示データの階調値に応じたシフト量だけシフトした補正階調電圧を表示画素に印加し、選択期間の残りの期間で表示データの階調値に応じた正規の階調電圧を表示画素に印加するようにしているので、表示画素への書き込みを表示データの各階調において良好に行うことができる。従って、書き込み時間を短縮して、高精細化を可能とする表示駆動装置及びそれを備えた表示装置を提供することができる。20

【発明を実施するための最良の形態】

【0024】

以下、本発明を実施するための最良の形態を、図面を参照して説明する。

【0025】

[第1実施形態]

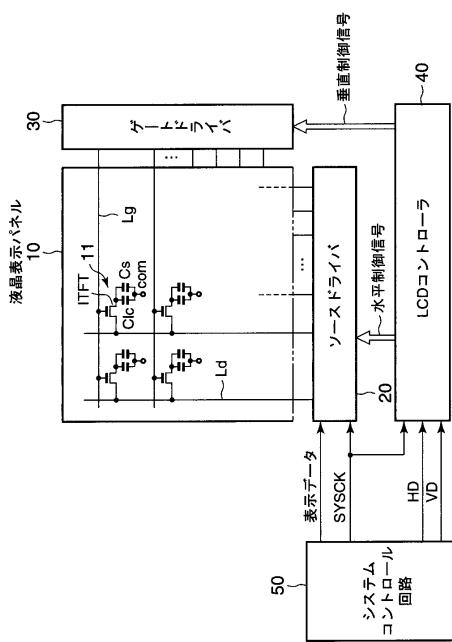

図1は、本発明の第1実施形態に係る液晶表示装置の全体構成を示す概略構成図である。なお、ここでは、液晶表示装置として、アクティブマトリックス型の液晶表示パネルを用いた液晶表示装置について説明する。

【0026】

本実施形態に係る液晶表示装置は、大別して、液晶表示パネル10と、ソースドライバ(表示駆動装置：信号線駆動回路)20と、ゲートドライバ(走査線駆動回路)30と、LCDコントローラ(コントロール回路)40と、システムコントロール回路(制御回路)50と、を有して構成されている。40

【0027】

以下、各構成について説明する。液晶表示パネル10は、マトリクス状に配置された画素電極、及び、画素電極に対向して配置された共通電極(コモン電極；コモン電圧 $V_{com}$ )、画素電極と共通電極の間に充填された液晶からなる液晶容量 $C_{LC}$ と、画素電極にソースが接続されたTFT(以下、「画素トランジスタTFT」と記す)と、マトリクスの行方向に延伸し、複数の画素トランジスタTFTのゲートに接続された複数の走査ライン $L_g$ と、マトリクスの列方向に延伸し、複数の画素トランジスタTFTのドレイ

ンに接続された複数（n本）の信号ラインLdと、を有して構成され、後述するソースドライバ20及びゲートドライバ30により選択される画素電極に表示信号電圧を印加することにより、画素電極と共に電極間の電界（液晶印加電圧VLCD）によって液晶の配列を制御して所定の画像情報を表示出力する。ここで、Csは、蓄積容量であり、前記液晶容量C1c、蓄積容量Cs及び画素トランジスタ TFTは、表示画素（液晶画素）11を構成する。

#### 【0028】

ソースドライバ20は、後述するLCDコントローラ40から供給される水平制御信号に基づいて、システムコントロール回路50から与えられる表示データ（画像信号R、G、B）に対応する表示信号電圧を、信号ラインLdを介して各画素電極に供給する。

10

#### 【0029】

一方、ゲートドライバ30は、LCDコントローラ40から供給される垂直制御信号に基づいて、水平走査期間（1H）毎に各走査ラインLgに走査信号を順次印加して選択状態とし、前記信号ラインLdと交差する位置に配置された画素電極（表示画素）に対して、前記ソースドライバ20により信号ラインLdに供給された表示信号電圧を印加する（書き込む）線順次駆動が行われる。即ち、走査信号を液晶表示パネル10の1走査ラインLgに印加することにより、当該走査ラインLgの各画素トランジスタ TFTが駆動制御され、前記ソースドライバ20により各信号ラインLdに印加された表示信号電圧が、画素トランジスタ TFTを介して、各画素電極に印加される。

#### 【0030】

LCDコントローラ40は、システムコントロール回路50から供給される水平同期信号HD、垂直同期信号VD及びシステムクロックSYCKに基づいて水平制御信号や垂直制御信号を生成し、ソースドライバ20及びゲートドライバ30に各自供給することにより、所定のタイミングで画素電極に表示信号電圧を印加して、液晶表示パネル10に所望の画像情報を表示させる制御を行う。

20

#### 【0031】

システムコントロール回路50は、システムクロックSYCKをソースドライバ20、LCDコントローラ40等に供給するとともに、このシステムクロックSYCKに同期した水平同期信号HD、垂直同期信号VDをLCDコントローラ40に供給する。また、デジタルRGB信号からなる表示データをソースドライバ20に出力する。

30

#### 【0032】

即ち、LCDコントローラ40とシステムコントロール回路50とは、図示を省略したインターフェースを介して、外部から供給される映像信号に基づいて、液晶表示パネル10に所望の画像情報を表示させるための種々の制御信号を生成して、ソースドライバ20及びゲートドライバ30に出力する。

#### 【0033】

一般的に、液晶表示装置では、液晶が充填される画素電極 - 共通電極間の電界（液晶印加電圧VLCD）の極性を所定周期で反転させる反転駆動が行われている。液晶表示パネル10では、上述のように、画素電極 - 共通電極間の電界に応じて液晶の配列が決定されるが、かかる画素電極 - 共通電極間に直流を印加すると、焼き付きが発生したり、液晶の劣化や破壊を引き起こしたりする原因となる。このため、画素電極 - 共通電極間の電界の極性を周期的に反転させることで、これを防止している。

40

#### 【0034】

反転駆動方法としてはライン反転駆動やフレーム反転駆動が一般的である。ライン反転駆動とは、液晶印加電圧VLCDの極性を走査ライン毎に反転させるとともに、フレーム期間毎にも反転させる方法である。また、フレーム反転駆動とは、各表示画素の極性をフレーム期間毎に反転させる方法である。ここで、「フレーム」とは、各液晶表示パネルの全表示画素11に表示信号電圧を供給して、1つの画像を表示させる期間の単位のことと言う。

#### 【0035】

50

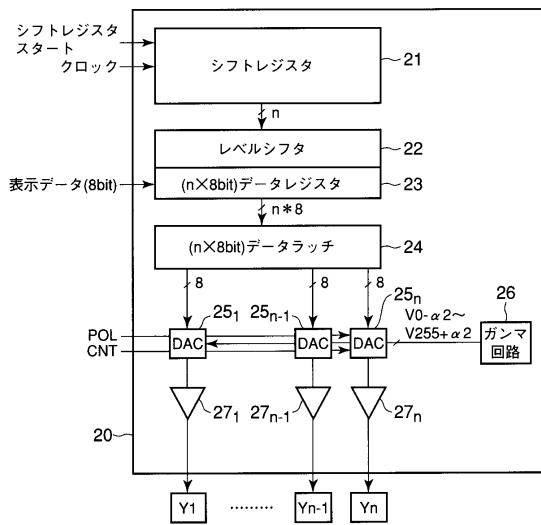

図2は、前記ソースドライバ20の構成を示すブロック構成図である。ここで、本実施形態における表示データは8bitのデジタルRGB信号からなるものとする。このソースドライバ20は、同図に示すように、n段のシフトレジスタ21、レベルシフタ22、 $n \times 8$ bitのデータレジスタ23、 $n \times 8$ bitのデータラッチ24、n個のDAC25( $25_1 \sim 25_n$ )、ガンマ回路(階調電圧発生回路)26、及びn個の出力AMP27( $27_1 \sim 27_n$ )によって構成されている。ここで、DAC25と出力AMP27によって書き込み回路が構成される。

#### 【0036】

シフトレジスタ21はn個の出力端子を有し、前記LCDコントローラ40から水平制御信号として供給されるシフトレジスタスタート信号によりスタートし、同じく水平制御信号として供給されるクロックで順次シフト動作を行って、各出力端子から出力信号を順次出力する。

#### 【0037】

レベルシフタ22は、シフトレジスタ21からの出力信号の信号レベルを、ロジック電圧レベルからソースドライバの電源電圧レベルにレベルシフトするものである。データレジスタ23は、前記システムコントロール回路50から供給される表示データを、前記シフトレジスタ21から出力される各出力信号のタイミングで取り込むものである。データラッチ24は、該データレジスタ23に取り込まれた表示データを一斉に取り込み、保持する。

#### 【0038】

DAC25( $25_1 \sim 25_n$ )は、前記LCDコントローラ40から水平制御信号として供給される後述する極性制御信号POLと補正制御信号CNTとに基づいて、データラッチ24に保持されたデジタルRGB信号からなる表示データをアナログRGB信号(画像信号R、G、B)に変換して出力するためのデジタル/アナログ(D/A)コンバータである。詳細は後述する。

#### 【0039】

ガンマ回路26は、DAC25に供給する複数の階調電圧を生成してDAC25に供給するものであり、従来は、表示データが8bitである場合、8ビットデータ( $0 \sim 255$ )に対応する階調電圧V0～V255(V255はV0に対して高電位)を生成するものであるが、本実施形態におけるガンマ回路26は、階調電圧V0～V255に加えて、更に、最小階調電圧V0を、より低い電位にシフトした、複数段階(本実施形態においては、2段階)のシフト階調電圧V0-2, V0-1、及び最高階調電圧V255を、より高い電位にシフトした、複数段階(本実施形態においては、2段階)のシフト階調電圧V255+1, V255+2も生成するものである。DAC25は、データラッチ24に保持された表示データに応じて、このようなガンマ回路26で生成されたV0-2～V255+2のシフト階調電圧及び階調電圧を選択することで、D/A変換を行う。このように、本実施形態では、ガンマ回路26が生成する電圧を、表示データが8bitである場合に本来ならV0～V255の256段階としたことにより、DAC25の出力電圧範囲を従来の構成の場合より広くすることができる。出力AMP27( $27_1 \sim 27_n$ )は、対応するDAC25( $25_1 \sim 25_n$ )の出力を増幅して、n本の信号ラインLdに表示信号電圧Y1～Ynとして出力する。

#### 【0040】

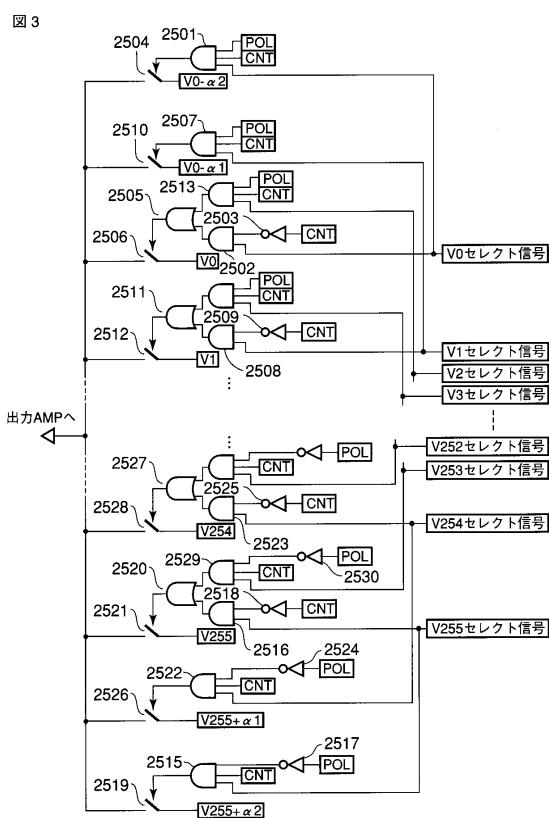

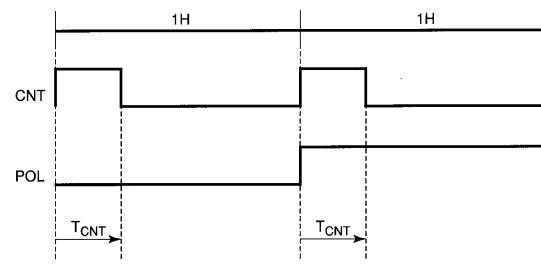

図3は、前記DAC25( $25_1 \sim 25_n$ )の構成を示す図であり、図4は、前記極性制御信号POLと前記補正制御信号CNTのタイミングチャートである。

#### 【0041】

各DAC25は、ガンマ回路26で生成された階調電圧V0-2～V255+2が供給されるとともに、データラッチ24に保持された表示データのうちの対応する8ビットデータをデコードして、表示データの階調値0～255に応じたV0セレクト信号～V255セレクト信号を出力するデコーダ(図示略)と、このデコーダからのV0セレクト

10

20

30

40

50

信号～V255セレクト信号と前記極性制御信号POL及び前記補正制御信号CNTが供給され、これらの信号の状態によって、シフト階調電圧及び階調電圧V0-2～V255+2の何れかを選択する選択回路と、を備えて、選択回路によって選択された階調電圧を対応する出力AMP27に出力するように構成されている。

#### 【0042】

即ち、図3に示すように、デコーダからのV0セレクト信号は、ANDゲート2501とANDゲート2502に入力される。前記ANDゲート2501には、更に、前記極性制御信号POLと前記補正制御信号CNTが入力される。また、前記ANDゲート2502には、インバータ2503を介して、前記補正制御信号CNTが入力される。前記ANDゲート2501の出力は、前記ガンマ回路26で発生されたシフト階調電圧V0-2を前記出力AMP27へ切り替え供給するためのスイッチ2504へ切替制御信号として与えられる。また、前記ANDゲート2502の出力は、ORゲート2505を介して、前記ガンマ回路26で発生された階調電圧V0を前記出力AMP27へ切り替え供給するためのスイッチ2506へ切替制御信号として与えられるように構成されている。10

#### 【0043】

ここで、本液晶表示装置においては、表示信号電圧Y1～Yn及びコモン電圧VCOMの極性が、1走査ライン毎に反転されるライン反転駆動を行うものである。本実施形態における反転駆動においては、反転する毎に表示データが反転され、液晶印加電圧VLCDの絶対値が大きくなる側の電圧がV0側であるフレームと、V255側であるフレームが交互に設けられる。前記極性制御信号POLは、液晶印加電圧VLCDの絶対値が大きくなる電圧が、V0側か、V255側かを示すものであり、図4に示すように、1水平走査期間(1H)毎にハイレベル/ローレベルが反転される。また、前記補正制御信号CNTは、1H期間の初期の期間に設定される補正期間( $T_{CNT}$ )ハイレベルとなる信号である。本実施形態においては、極性制御信号POLがハイレベルのときに液晶印加電圧VLCDの絶対値が大きくなる電圧がV0側であり、極性制御信号POLがローレベルのときに液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側であるとする。20

#### 【0044】

本実施形態における動作は、前記極性制御信号POLがハイレベルの場合、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV0側である場合に、表示データの階調値が最高階調255で、V0セレクト信号がDAC25に供給されるとき、前記補正制御信号CNTがハイレベルの期間中は、前記V0セレクト信号は、ANDゲート2501側からのみ出力されて、前記スイッチ2504はオン、前記スイッチ2506はオフとなり、結果として、前記出力AMP27へは、表示データの階調値に応じた正規の階調電圧であるV0よりも低い(液晶印加電圧VLCDの絶対値がV0のときよりも2だけ大きい)V0-2のシフト階調電圧が選択されて、補正階調電圧として出力AMP27に出力される。そして、前記補正制御信号CNTがローレベルとなると、前記V0セレクト信号は、ANDゲート2502側からのみ出力されて、前記スイッチ2504はオフ、前記スイッチ2506はオンとなり、結果として、前記出力AMP27へは、正規の階調電圧であるV0が選択されて出力される。30

#### 【0045】

このように、ANDゲート2501, 2502及びスイッチ2504, 2506でなる選択回路により、前記補正制御信号CNTがハイレベル期間つまり表示画素の液晶への書き込みの初期の補正期間に正規の階調電圧V0よりも液晶印加電圧VLCDの絶対値が2だけ大きいシフト階調電圧V0-2を出力し、その後の書き込み期間で補正制御信号CNTをローレベルとして正規の階調電圧V0を出力することができる。40

#### 【0046】

なお、表示データの階調値に応じてV0セレクト信号がDAC25に供給されるときに、前記極性制御信号POLがローレベルに反転したとき、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側である場合には、前記補正制御信号CNTの状態にかかわらずANDゲート2501からは前記V0セレクト信号は出力されず、前記補正制御信号CNTがハイレベルとなると、前記V0セレクト信号は出力される。50

御信号 CNT がローレベルの期間に前記 V0 セレクト信号が AND ゲート 2502 側から出力されて、前記スイッチ 2506 がオンして、正規の階調電圧である V0 が選択されて、前記出力 AMP 27 へ出力される。このとき、正規の階調電圧である V0 は低い電圧であるので、プリチャージを行う必要がなく、また、出力 AMP 27 から出力する期間が 1H よりも短い前記補正制御信号 CNT がローレベルの期間しかなくても表示データの階調値に応じた正規の表示信号電圧を書き込むことが可能である。

#### 【0047】

次に、表示データの階調値が最高階調より 1 階調低い 254 で、V1 セレクト信号が DAC 25 に供給されるとき、V1 セレクト信号は AND ゲート 2507 と AND ゲート 2508 に入力される。前記 AND ゲート 2507 には、更に、前記極性制御信号 POL と前記補正制御信号 CNT が入力され、また、前記 AND ゲート 2508 には、インバータ 2509 を介して、前記補正制御信号 CNT が入力される。前記 AND ゲート 2507 の出力は、前記ガンマ回路 26 で発生されたシフト階調電圧 V0 - 1 を前記出力 AMP 27 へ切り替え供給するためのスイッチ 2510 へ切替制御信号として与えられ、また、前記 AND ゲート 2508 の出力は、OR ゲート 2511 を介して、前記ガンマ回路 26 で発生された階調電圧 V1 を前記出力 AMP 27 へ切り替え供給するためのスイッチ 2512 へ切替制御信号として与えられるように構成されている。

#### 【0048】

従って、前記極性制御信号 POL がハイレベルの場合、つまり液晶印加電圧 VLCD の絶対値が大きくなる電圧が V0 側である場合には、前記補正制御信号 CNT がハイレベルの期間中は、前記 V1 セレクト信号は、AND ゲート 2507 側からのみ出力されて、前記スイッチ 2510 はオン、前記スイッチ 2512 はオフとなり、結果として、前記出力 AMP 27 へは、表示データの階調値に応じた正規の階調電圧である V1 よりも低い（液晶印加電圧 VLCD の絶対値が V1 のときより  $\frac{1}{2} + \frac{1}{2}$  階調差（255 階調と 254 階調の差）分だけ大きい） V0 - 1 のシフト階調電圧が選択されて、補正階調電圧として前記出力 AMP 27 に出力される。そして、前記補正制御信号 CNT がローレベルとなると、前記 V1 セレクト信号は、AND ゲート 2508 側からのみ出力されて、前記スイッチ 2510 はオフ、前記スイッチ 2512 はオンとなり、結果として、前記出力 AMP 27 へは、正規の階調電圧である V1 が選択されて出力される。

#### 【0049】

このように、AND ゲート 2507, 2508 及びスイッチ 2510, 2512 でなる選択回路により、前記補正制御信号 CNT がハイレベルの補正期間に正規の階調電圧 V1 よりも液晶印加電圧 VLCD の絶対値が  $\frac{1}{2} + \frac{1}{2}$  階調分だけ大きいシフト階調電圧 V0 - 1 を出力し、その後の書き込み期間で補正制御信号 CNT をローレベルとして正規の階調電圧 V1 を出力することができる。

#### 【0050】

なお、表示データの階調値に応じて V1 セレクト信号が DAC 25 に供給されるときに、前記極性制御信号 POL がローレベルに反転したとき、つまり液晶印加電圧 VLCD の絶対値が大きくなる電圧が V255 側である場合には、前記補正制御信号 CNT の状態にかかわらず AND ゲート 2507 からは前記 V1 セレクト信号は出力されず、前記補正制御信号 CNT がローレベルの期間に、前記 V1 セレクト信号が AND ゲート 2508 側から出力されて、前記スイッチ 2512 がオンして、正規の階調電圧である V1 が選択されて、前記出力 AMP 27 へ出力される。このとき、正規の階調電圧である V1 は低い電圧であるので、プリチャージを行う必要がなく、また、出力 AMP 27 から出力する期間が 1H よりも短い前記補正制御信号 CNT がローレベルの期間しかなくても表示データの階調値に応じた正規の表示信号電圧を書き込むことが可能である。

#### 【0051】

また、表示データの階調値が最高階調より 2 階調低い 253 で、V2 セレクト信号が DAC 25 に供給されるとき、V2 セレクト信号は AND ゲート 2513 と、出力が、OR ゲートを介して、階調電圧 V2 を前記出力 AMP 27 へ切り替え供給するためのスイッチ

10

20

30

40

50

(V2スイッチとする：図示略)へ切替制御信号として与えられるANDゲート(V2ANDゲートとする：図示略)に入力される。前記ANDゲート2513には、更に、前記極性制御信号POLと前記補正制御信号CNTが入力され、また、前記V2ANDゲートには、図示しないインバータを介して、前記補正制御信号CNTが入力される。前記ANDゲート2513の出力は、前記ORゲート2505を介して、前記ガンマ回路26で発生された階調電圧V0を前記出力AMP27へ切り替え供給するための前記スイッチ2506へ切替制御信号として与えられる。

#### 【0052】

従って、前記極性制御信号POLがハイレベルの場合、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV0側である場合には、前記補正制御信号CNTがハイレベルの期間中は、前記V2セレクト信号は、ANDゲート2513側からのみ出力されて、前記スイッチ2506はオン、前記V2スイッチはオフとなり、結果として、前記出力AMP27へは、表示データの階調値に応じた正規の階調電圧であるV2よりも低い(液晶印加電圧VLCDの絶対値がV2のときより2階調差(255階調と253階調の差)分だけ大きい)V0の階調電圧が選択されて、補正階調電圧として前記出力AMP27に出力される。そして、前記補正制御信号CNTがローレベルとなると、前記V2セレクト信号は、前記V2ANDゲート側からのみ出力されて、前記スイッチ2506はオフ、前記V2スイッチはオンとなり、結果として、前記出力AMP27へは、正規の表示信号電圧であるV2が選択されて出力される。

#### 【0053】

このように、ANDゲート2513と図示しないANDゲート及びスイッチ2506とV2スイッチでなる選択回路により、前記補正制御信号CNTがハイレベルの補正期間に正規の階調電圧V2よりも液晶印加電圧VLCDの絶対値が2階調分大きいシフト階調電圧V0を出力し、その後の書き込み期間で補正制御信号CNTをローレベルとして正規の階調電圧V2を出力することができる。

#### 【0054】

なお、表示データの階調値に応じてV2セレクト信号がDAC25に供給されるときに、前記極性制御信号POLがローレベルに反転したとき、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側である場合には、前記補正制御信号CNTの状態にかかわらずANDゲート2513からは前記V2セレクト信号は出力されず、前記補正制御信号CNTがローレベルの期間に、前記V2セレクト信号が前記図示しないANDゲート側から出力されて、前記図示しないスイッチがオンして、正規の表示信号電圧であるV2が選択されて、前記出力AMP27へ出力される。このとき、正規の階調電圧であるV2は比較的低い電圧であるので、プリチャージを行う必要がなく、また、出力AMP27から出力する期間が1Hよりも短い前記補正制御信号CNTがローレベルの期間しかなくても表示データの階調値に応じた正規の表示信号電圧を書き込むことが可能である。

#### 【0055】

以下、V3から中間のV127セレクト信号についても上記と同様に構成され、前記補正制御信号CNTがハイレベル期間において、デコーダからの各セレクト信号と極性制御信号POL及び補正制御信号CNTに応じて、書き込みの初期の補正期間にのみ、表示データの階調値に応じた正規の階調電圧よりも液晶印加電圧VLCDの絶対値が2階調差(自身の階調より2階調高い階調と自身の階調との差)分だけ大きくなる階調電圧が補正階調電圧として出力AMP27へ出力される。

#### 【0056】

一方、V255から中間のV128セレクト信号側に関しては、前述したV0～V127セレクト信号側における構成を、前記V127セレクト信号に関して対称にし、前記極性制御信号POLをインバータで反転させてANDゲートに入力するようにした構成を備えている。

#### 【0057】

即ち、デコーダからのV255セレクト信号は、ANDゲート2515とANDゲート

10

20

30

40

50

2516に入力される。前記ANDゲート2515には、更に、前記補正制御信号CNTと、インバータ2517を介して前記極性制御信号POLとが入力される。また、前記ANDゲート2516には、インバータ2518を介して前記補正制御信号CNTが入力される。前記ANDゲート2515の出力は、前記ガンマ回路26で発生されたシフト階調電圧V255+2を前記出力AMP27へ切り替え供給するためのスイッチ2519へ切替補正制御信号として与えられる。また、前記ANDゲート2516の出力は、ORゲート2520を介して、前記ガンマ回路26で発生された階調電圧V255を前記出力AMP27へ切り替え供給するためのスイッチ2521へ切替制御信号として与えられるよう構成されている。

## 【0058】

10

従って、前記極性制御信号POLがローレベルの場合、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側である場合に、表示データの階調値が最高階調255で、V255セレクト信号がDAC25に供給されるとき、前記補正制御信号CNTがハイレベルの期間中は、前記V255セレクト信号は、ANDゲート2515側からのみ出力されて、前記スイッチ2519はオン、前記スイッチ2521はオフとなり、結果として、前記出力AMP27へは、表示データの階調値に応じた正規の階調電圧であるV255よりも高い（液晶印加電圧VLCDの絶対値がV255のときより2だけ大きい）V255+2のシフト階調電圧が選択されて、補正階調電圧として前記出力AMP27へ出力される。そして、前記補正制御信号CNTがローレベルとなると、前記2550セレクト信号は、ANDゲート2516側からのみ出力されて、前記スイッチ2519はオフ、前記スイッチ2521はオンとなり、結果として、前記出力AMP27へは、正規の階調電圧であるV255が選択されて出力される。

20

## 【0059】

このように、ANDゲート2515, 2516及びスイッチ2519, 2521でなる選択回路により、前記補正制御信号CNTがハイレベルの補正期間に正規の階調電圧V255よりも液晶印加電圧VLCDの絶対値が2だけ大きいシフト階調電圧V255+2を出力し、その後の書き込み期間で補正制御信号CNTをローレベルとして正規の階調電圧V255を出力することができる。

## 【0060】

30

なお、表示データの階調値に応じてV255セレクト信号がDAC25に供給されるときに、前記極性制御信号POLがハイレベルに反転したとき、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV0側である場合には、前記補正制御信号CNTの状態にかかわらずANDゲート2515からは前記V255セレクト信号は出力されず、前記補正制御信号CNTがローレベルの期間中に前記V255セレクト信号がANDゲート2516側から出力されて、前記スイッチ2521がオンして、正規の階調電圧であるV255が選択されて、前記出力AMP27へ出力される。このとき、正規の階調電圧であるV255は低い電圧であるので、プリチャージを行う必要がなく、また、出力AMP27から出力する期間が1Hよりも短い前記補正制御信号CNTがローレベルの期間しかなくても表示データの階調値に応じた正規の表示信号電圧を書き込むことが可能である。

## 【0061】

40

次に、表示データの階調値が最高階調より1階調低い254で、V254セレクト信号がDAC25に供給されるとき、V254セレクト信号はANDゲート2522とANDゲート2523に入力される。前記ANDゲート2522には、更に、前記補正制御信号CNTと、インバータ2524を介して前記極性制御信号POLとが入力され、また、前記ANDゲート2523には、インバータ2525を介して前記補正制御信号CNTが入力される。前記ANDゲート2522の出力は、前記ガンマ回路26で発生されたシフト階調電圧V255+1を前記出力AMP27へ切り替え供給するためのスイッチ2526へ切替補正制御信号として与えられ、また、前記ANDゲート2523の出力は、ORゲート2527を介して、前記ガンマ回路26で発生された階調電圧V254を前記出力AMP27へ切り替え供給するためのスイッチ2528へ切替制御信号として与えられる

50

ように構成されている。

#### 【0062】

従って、前記極性制御信号POLがローレベルの場合、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側である場合には、前記補正制御信号CNTがハイレベルの期間中は、前記V254セレクト信号は、ANDゲート2522側からのみ出力されて、前記スイッチ2526はオン、前記スイッチ2528はオフとなり、結果として、前記出力AMP27へは、表示データの階調値に応じた正規の階調電圧であるV254よりも高い（液晶印加電圧VLCDの絶対値がV254のときより1+1階調差（255階調と254階調の差）分だけ大きい）V255+1のシフト階調電圧が選択されて、補正階調電圧として前記出力AMP27に出力される。そして、前記補正制御信号CNTがローレベルとなると、前記V254セレクト信号は、ANDゲート2523側からのみ出力されて、前記スイッチ2526はオフ、前記スイッチ2528はオンとなり、結果として、前記出力AMP27へは、正規の階調電圧であるV254が選択されて出力される。

。

#### 【0063】

このように、ANDゲート2522, 2523及びスイッチ2526, 2528でなる選択回路により、前記補正制御信号CNTがハイレベルの補正期間に正規の階調電圧V254よりも液晶印加電圧VLCDの絶対値が1+1階調分だけ大きいシフト階調電圧V255+1を出力し、その後の書き込み期間で補正制御信号CNTをローレベルとして正規の階調電圧V254を出力することができる。

20

#### 【0064】

なお、表示データの階調値に応じてV254セレクト信号がDAC25に供給されるときに、前記極性制御信号POLがハイレベルに反転したとき、つまり液晶印加電圧VLCDが高くなる電圧がV0側である場合には、前記補正制御信号CNTの状態にかかわらずANDゲート2522からは前記V254セレクト信号は出力されず、前記補正制御信号CNTがローレベルの期間中に、前記V254セレクト信号がANDゲート2523側から出力されて、前記スイッチ2528がオンして、正規の階調電圧であるV254が選択されて、前記出力AMP27へ出力される。このとき、正規の階調電圧であるV254は低い電圧であるので、プリチャージを行う必要がなく、また、出力AMP27から出力する期間が1Hよりも短い前記補正制御信号CNTがローレベルの期間しかなくても表示データの階調値に応じた正規の表示信号電圧を書き込むことが可能である。

30

#### 【0065】

また、表示データの階調値が最高階調より2階調低い253で、V253セレクト信号がDAC25に供給されるとき、V253セレクト信号はANDゲート2529と、出力が、ORゲートを介して、階調電圧V253を前記出力AMP27へ切り替え供給するためのスイッチ（V253スイッチとする：図示略）へ切替制御信号として与えられるANDゲート（V253ANDゲートとする：図示略）に入力される。前記ANDゲート2529には、更に、前記補正制御信号CNTと、インバータ2530を介して前記極性制御信号POLとが入力され、また、前記V253ANDゲートには、図示しないインバータを介して、前記補正制御信号CNTが入力される。前記ANDゲート2529の出力は、前記ORゲート2520を介して、前記ガンマ回路26で発生された階調電圧V255を前記出力AMP27へ切り替え供給するための前記スイッチ2521へ切替制御信号として与えられる。

40

#### 【0066】

従って、前記極性制御信号POLがローレベルの場合、つまり液晶印加電圧VLCDの絶対値が大きくなる電圧がV255側である場合には、前記補正制御信号CNTがハイレベルの期間中は、前記V253セレクト信号は、ANDゲート2529側からのみ出力されて、前記スイッチ2521はオン、前記図示しないスイッチはオフとなり、結果として、前記出力AMP27へは、表示データの階調値に応じた正規の階調電圧であるV253よりも高い（液晶印加電圧VLCDの絶対値がV253のときより2階調差（255階調

と 253 階調の差) 分だけ大きい) V255 の階調電圧が選択されて、補正階調電圧として前記出力AMP27 に出力される。そして、前記補正制御信号CNT がローレベルとなると、前記V253 セレクト信号は、前記V253AND ゲート側からのみ出力されて、前記スイッチ2521 はオフ、前記V253 スイッチはオンとなり、結果として、前記出力AMP27 へは、正規の階調電圧であるV253 が選択されて出力される。

#### 【0067】

このように、AND ゲート2529 と図示しないAND ゲート及びスイッチ2521 とV253 スイッチでなる選択回路により、前記補正制御信号CNT がハイレベルの補正期間に正規の階調電圧V253 よりも液晶印加電圧VLCD の絶対値が2 階調差分だけ大きい階調電圧V255 を出力し、その後の書き込み期間で補正制御信号CNT をローレベルとして正規の階調電圧V253 を出力することができる。10

#### 【0068】

なお、表示データの階調値が253 で、V253 セレクト信号がDAC25 に供給されるときに、前記極性制御信号POL がハイレベルに反転したとき、つまり液晶印加電圧VLCD が高くなる電圧がV0 側である場合には、前記補正制御信号CNT の状態にかかわらずAND ゲート2529 からは前記V253 セレクト信号は出力されず、前記補正制御信号CNT がローレベルの期間中に、前記V253 セレクト信号が前記図示しないAND ゲート側から出力されて、前記図示しないスイッチがオンして、正規の階調電圧であるV253 が選択されて、前記出力AMP27 へ出力される。このとき、正規の階調電圧であるV253 は比較的低い電圧であるので、プリチャージを行う必要がなく、また、出力AMP27 から出力する期間が1H よりも短い前記補正制御信号CNT がローレベルの期間しかなくても目的の電圧を書き込むことが可能である。20

#### 【0069】

以下、V252 から中間のV128 セレクト信号についても上記と同様に構成されて、前記補正制御信号CNT がハイレベル期間において、デコーダからの各セレクト信号と極性制御信号POL 及び補正制御信号CNT に応じて、書き込みの初期の補正期間にのみ、表示データの階調値に応じた正規の階調電圧よりも高く、液晶印加電圧VLCD の絶対値が2 階調差(自身の階調より2 階調高い階調と自身の階調との差) 分だけ大きい階調電圧が補正階調電圧として出力AMP27 へ出力される。

#### 【0070】

以上のように、本第1 実施形態によれば、補正制御信号CNT をハイレベルとした書き込みの初期の補正期間、表示データの階調値に応じた正規の階調電圧よりも液晶印加電圧VLCD の絶対値が大きい補正階調電圧を出力AMP27 に出力し、その後の補正制御信号CNT がローレベルの期間は正規の階調電圧を出力することで、表示画素の液晶を正規の表示信号電圧に早く到達させることができるようになる。ここで、書き込みの初期の補正期間に出力する補正階調電圧の正規の階調電圧に対する差分の絶対値(シフト量)は、表示データの階調値が最高階調であるとき2 であり、階調値が最高階調より1 階調低いとき1+1 階調差(最高階調と最高階調1 階調との差)であり、階調値が最高階調より2 階調以上低いとき2 階調差(自身の階調より2 階調高い階調と自身の階調との差)に設定される。すなわち、本実施形態においては、表示画素への書き込みを表示データの各階調において良好に行うことができるよう、従来技術にあるように常に最大電圧にプリチャージするのではなく、補正階調電圧の値を表示データの階調値に応じて異なる値とし、シフト量の大きさを表示データの階調値に応じて適宜変えるようにしている。ここで、最高階調時に液晶印加電圧VLCD の絶対値が最も大きくなる構成である場合、最高階調時に出力AMP27 に対する負荷が最も大きいために、シフト量を最も大きくし、最高階調より低くなるにつれて負荷が小さくなるため、補正電圧と目標電圧との差分を最高階調より低くなるにつれて小さくするように設定して、2>1+1 階調差>2 階調差とすることが好ましい。また、階調値が最高階調より2 階調以上低いときに、補正電圧の目標電圧に対する差分を2 階調差としたが、これに限定するものではない。40

#### 【0071】

なお、書き込みの初期の補正期間に補正階調電圧を出力AMP27に出力したとき、信号ラインLdを介した表示画素への書き込みを短時間で行えるようにするために、この期間に出力AMP27の駆動能力を増加させることができが好ましい。そこで、前記補正制御信号CNTに応じて前記出力AMP27のバイアス電流の制御を行うようにして、補正制御信号CNTがハイレベルの期間は出力AMP27に供給するバイアス電流を補正制御信号CNTがローレベル期間のときの数倍にするように制御してもよい。

#### 【0072】

また、前記補正制御信号CNTをハイレベルとして補正電圧を出力する期間は、1Hの半分未満であれば良く、好ましくは1/3程度である。

#### 【0073】

以上のような第1実施形態によれば、DAC25に供給する複数の階調電圧の電圧範囲を表示データのビット数に応じた電圧範囲より広くして設定し、1Hの書き込み期間において、書き込み初期の補正期間に、表示データの階調値に応じた正規の階調電圧よりも液晶印加電圧の絶対値が大きくなる側にシフトした補正階調電圧を出力し、その後、正規の階調電圧を出力するような書き込み回路を備えることで、各階調において液晶の書き込み時間を短縮することができる。これにより、例えば高精細化により1Hの期間が短くなったとしても、書き込み時間が足りずに書き込み不足が生じることを抑制して、正規の表示信号電圧を表示画素の液晶に良好に書き込むことが可能となる。

#### 【0074】

##### 【第2実施形態】

次に、本発明の第2実施形態に係る液晶表示装置を説明する。

#### 【0075】

その全体構成は、前述した第1実施形態に係る液晶表示装置のそれと同様であるので、その説明は省略する。

#### 【0076】

そして、ソースドライバ20は、前述した第1実施形態における図2に示すように、シフトレジスタ21、レベルシフタ22、データレジスタ23、データラッチ24、n個のDAC25(25<sub>1</sub>～25<sub>n</sub>)、ガンマ回路26、及びn個の出力AMP27(27<sub>1</sub>～27<sub>n</sub>)によって構成されるものであるが、本第2実施形態におけるソースドライバ20では、ガンマ回路26が前記第1実施形態のようなV0-2～V255+2の260段階ではなくて、従来と同様に、V0～V255の256段階の階調電圧を発生するものとしている。また、DAC25(25<sub>1</sub>～25<sub>n</sub>)は、各セレクト信号に応じて階調電圧を選択して出力するスイッチを備えるだけの構成となっている。

#### 【0077】

但し、本実施形態においては、ガンマ回路26が発生する256段階の階調電圧を常に一定とするのではなく、その書き込みの初期の補正期間において、階調電圧の液晶印加電圧VLCDの絶対値が大きくなる側の電圧を、液晶印加電圧VLCDの絶対値が大きくなる方向にシフトしたシフト電圧に切り替えて、各階調電圧の値を表示データの階調値に応じた正規の階調電圧より液晶印加電圧VLCDの絶対値が大きくなる側にシフトした、補正階調電圧を発生するように構成している。

#### 【0078】

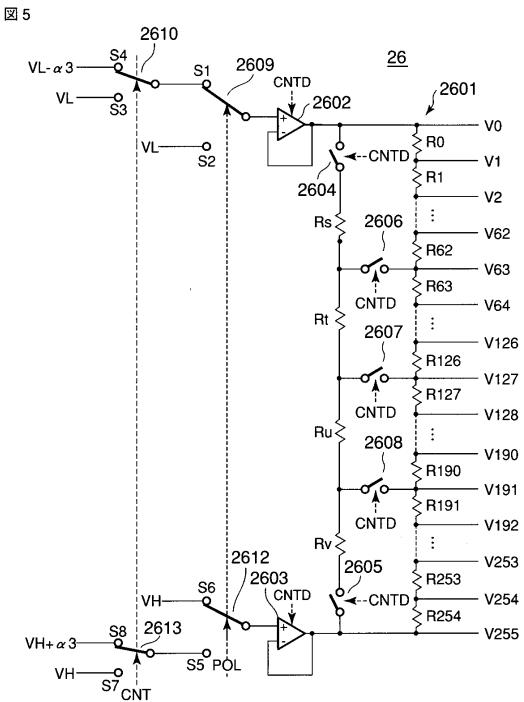

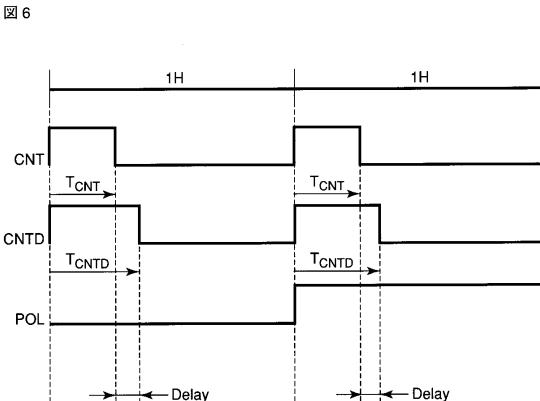

図5は、本第2実施形態におけるガンマ回路26の構成を示す図であり、図6は、前記極性制御信号POLと前記補正制御信号CNTと遅延制御信号CNTDのタイミングチャートである。ここで、補正制御信号CNT、遅延制御信号CNTDは、前記LCDコントローラ40から水平制御信号として供給されるものである。図6に示すように、前記補正制御信号CNTは、上記第1実施形態と同じく、1H期間の初期の補正期間に所定期間(T<sub>CNT</sub>)ハイレベルとなる信号であり、前記遅延制御信号CNTDは、前記補正制御信号CNTと同時にハイレベルとなり、前記補正制御信号CNTがローレベルとなった後、例えば数μ秒の遅延期間Delayを持った期間(T<sub>CNTD</sub>)までハイレベルとなり、その後ローレベルとなる信号である。

10

20

30

40

50

## 【0079】

ガンマ回路26は、通常、図5に示すように、表示データの階調数(256階調)に応じた複数の抵抗(分圧抵抗) $R_1, R_2, \dots, R_{254}$ でなる分圧器(分圧回路)2601と、この分圧器2601の両端に、図示しない電圧発生回路からの電圧(上限電圧) $V_H$ 、電圧(下限電圧) $V_L$ を増幅した電圧を印加するためのアンプ2602及び2603とを備え、前記アンプ2602, 2603からの電圧を前記分圧器2601の両端に印加し、上限電圧 $V_H$ と下限電圧 $V_L$ 間の電位差を抵抗 $R_1, R_2, \dots, R_{254}$ で分圧した電圧を、階調電圧 $V_0, V_1, \dots, V_{255}$ としてD A C 25( $25_1 \sim 25_n$ )に印加するように構成されている。

## 【0080】

そして、本実施形態では、更に、前記分圧器2601の抵抗 $R_1 \sim R_{254}$ に並列に、抵抗(補助抵抗) $R_s, R_t, R_u, R_v$ の直列接続を、前記遅延制御信号C N T Dに応じて切り替えられるスイッチ2604, 2605を介して接続するように構成している。また、抵抗 $R_s$ と抵抗 $R_t$ との接続点を前記遅延制御信号C N T Dに応じて切り替えられるスイッチ2606を介して前記分圧器2601の抵抗 $R_{62}$ と $R_{63}$ との接続点に接続し、抵抗 $R_t$ と抵抗 $R_u$ との接続点を前記遅延制御信号C N T Dに応じて切り替えられるスイッチ2607を介して前記分圧器2601の抵抗 $R_{126}$ と $R_{127}$ との接続点に接続し、抵抗 $R_u$ と抵抗 $R_v$ との接続点を前記遅延制御信号C N T Dに応じて切り替えられるスイッチ2608を介して前記分圧器2601の抵抗 $R_{190}$ と $R_{191}$ との接続点に接続するようにしている。

10

## 【0081】

なお、前記抵抗 $R_s$ は $(R_0 + R_1 + \dots + R_{62}) / 10$ 、前記抵抗 $R_t$ は $(R_{63} + R_{64} + \dots + R_{126}) / 10$ 、前記抵抗 $R_u$ は $(R_{127} + R_{128} + \dots + R_{190}) / 10$ 、前記抵抗 $R_v$ は $(R_{191} + R_{192} + \dots + R_{254}) / 10$ の抵抗値とする。

## 【0082】

また、前記アンプ2602の入力端は、前記極性信号P O Lに応じてS1端子とS2端子を切り替えるスイッチ2609に接続されている。ここで、該スイッチ2609のS1端子は、前記補正制御信号C N Tに応じて、図示しない電圧発生回路からローレベル電圧(下限電圧) $V_L$ が印加されるS3端子と $V_L$ を負電圧側にシフトした電圧(シフト電圧) $V_L - 3$ が印加されるS4端子とを切り替えるスイッチ2610に接続されている。また、前記スイッチ2609のS2端子には、図示しない電圧発生回路からローレベル電圧 $V_L$ が印加されている。

20

## 【0083】

同様に、前記アンプ2603の入力端は、前記極性信号P O Lに応じてS5端子とS6端子を切り替えるスイッチ2612に接続されている。ここで、前記スイッチ2612のS5端子は、前記補正制御信号C N Tに応じて、図示しない電圧発生回路からハイレベル電圧(上限電圧) $V_H$ が印加されるS7端子と $V_H$ を正電圧側にシフトした電圧(シフト電圧) $V_H + 3$ が印加されるS8端子とを切り替えるスイッチ2613に接続されている。また、前記スイッチ2612のS6端子には、図示しない電圧発生回路からハイレベル電圧 $V_H$ が印加されている。ここで、スイッチ2609, 2610, 2612, 2613は、本発明における切替回路を構成する。

30

## 【0084】

従って、このような構成のガンマ回路26では、前記極性信号P O Lがハイレベルの場合、つまり液晶印加電圧 $V_L C D$ が高くなる電圧が $V_0$ 側である場合には、前記スイッチ2609はS1端子側に切り替えられ、前記スイッチ2612はS6端子側に切り替えられる。この状態で、前記補正制御信号C N Tがハイレベルの補正期間中は、前記スイッチ2610はS4端子側に切り替えられるので、アンプ2602には電圧 $V_L - 3$ が、アンプ2603には電圧 $V_H$ が、それぞれ入力される。結果として、補正期間中は、前記分圧器2601に印加する下限電圧を、液晶印加電圧 $V_L C D$ の絶対値が大きくなる負電圧側に電圧 $-3$ 分シフトして、各階調電圧を液晶印加電圧 $V_L C D$ の絶対値が大きくなる側に

40

50

シフトした補正階調電圧とする。そして、前記補正制御信号C N Tがローレベルとなると、前記スイッチ2 6 1 0はS 3端子側に切り替えられるので、アンプ2 6 0 2には電圧V Lが、アンプ2 6 0 3には電圧V Hが、それぞれ入力されて、各階調電圧は正規の階調電圧となる。

#### 【0085】

逆に、前記極性信号P O Lがローベルの場合、つまり液晶印加電圧V L C Dが高くなる電圧がV 2 5 5側である場合には、前記スイッチ2 6 0 9はS 2端子側に切り換えられ、前記スイッチ2 6 1 2はS 5端子側に切り替えられ、この状態で、前記補正制御信号C N Tがハイレベルの期間中は、前記スイッチ2 6 1 3はS 8端子側に切り替えられるので、アンプ2 6 0 2には電圧V Lが、アンプ2 6 0 3には電圧V H + 3が、それぞれ入力される。結果として、補正期間中は、前記分圧器2 6 0 1に印加する上限電圧を正電圧側に電圧 3分シフトして、各階調電圧を液晶印加電圧V L C Dの絶対値が大きくなる側にシフトした補正階調電圧とする。そして、前記補正制御信号C N Tがローレベルとなると、前記スイッチ2 6 1 3はS 7端子側に切り替えられるので、アンプ2 6 0 2には電圧V Lが、アンプ2 6 0 3には電圧V Hが、それぞれ入力されて、各階調電圧は正規の階調電圧となる。

#### 【0086】

このようにして、ガンマ回路2 6において、前記補正制御信号C N Tがハイレベルの補正期間に、液晶印加電圧V L C Dの絶対値が大きくなる側の電圧を、液晶印加電圧V L C Dの絶対値が大きくなる側に電圧 3分、電圧をシフトした補正階調電圧を発生する。このとき、液晶印加電圧V L C Dの絶対値が小さくなる側の電圧はシフトしないため、補正期間における各階調電圧は、液晶印加電圧V L C Dの絶対値が大きくなる側にシフトし、各階調毎のシフト量は階調によって異なり、液晶印加電圧V L C Dの絶対値が大きくなる側の階調電圧のシフト量が大きくなる。ここで、最高階調時に液晶印加電圧V L C Dの絶対値が最も大きくなる構成である場合、液晶印加電圧V L C Dの絶対値が最も大きく出力A M P 2 7に対する負荷が最も大きい最高階調時時に、階調電圧のシフト量を最も大きくし、最高階調より低下し、負荷が次第に小さくなるのに合わせて階調電圧のシフト量を次第に小さくすることができて、各階調において液晶の書き込み時間を短縮して、書き込みを良好に行うようにすることができる。

#### 【0087】

このガンマ回路2 6の分圧器2 6 0 1において、階調電圧V 0 ~ V 2 5 5は直列接続された複数の抵抗R 0 ~ R 2 5 4によってV 0とV 2 5 5間の電圧を分割することによって生成されるが、抵抗R 0 ~ R 2 5 4のみを有している場合に、抵抗R 0 ~ R 2 5 4に流れる電流を比較的小さくして消費電力の増加を抑制するために、各抵抗の抵抗値を比較的大きい値に設定していると、各抵抗とD A C 2 5の入力までの寄生容量による時定数によって、前記補正制御信号C N Tがハイレベル又はローレベルに切り替わってから階調電圧V 0 ~ V 2 5 5の値が安定するまでに有る程度の遅延を生じる。

#### 【0088】

そこで、本実施形態では、更に、分圧器2 6 0 1の前記抵抗R 0 ~ R 2 5 4と並列に前記抵抗R s , R t , R u , R vの直列接続を設けて、これを前記遅延制御信号C N T Dがハイレベルの期間に接続する構成を備える。前記スイッチ2 6 0 4 ~ 2 6 0 8を介して、前記抵抗R sは前記抵抗R 0 ~ R 6 2に並列に接続され、前記抵抗R tは前記抵抗R 6 3 ~ R 1 2 6に並列に接続され、前記抵抗R uは前記抵抗R 1 2 7 ~ R 1 9 0に並列に接続され、前記抵抗R vは前記抵抗R 1 9 1 ~ R 2 5 4に並列に接続される。ここで、例えば、前記抵抗R sは $(R_0 + R_1 + \dots + R_{62}) / 10$ の抵抗値を有し、前記抵抗R tは $(R_{63} + R_{64} + \dots + R_{126}) / 10$ の抵抗値を有し、前記抵抗R uは $(R_{127} + R_{128} + \dots + R_{190}) / 10$ の抵抗値を有し、前記抵抗R vは $(R_{191} + R_{192} + \dots + R_{254}) / 10$ の抵抗値を有する。これにより、前記遅延制御信号C N T Dがハイレベルの期間に前記スイッチ2 6 0 4 ~ 2 6 0 8を介して前記抵抗R s , R t , R u , R vが前記抵抗R 0 ~ R 2 5 4に並列に接続されたとき、階調電圧V 6 3 , V 1 2 7 , V 1

10

20

30

40

50

91, V255に関しては、時定数が、前記抵抗R<sub>s</sub>, R<sub>t</sub>, R<sub>u</sub>, R<sub>v</sub>を接続しないときの概ね1/10にすることができるため、階調電圧V0~V255の値が安定するまでの遅延時間を減らすことができる。但し、前記遅延制御信号CNTDをハイレベルとして抵抗R<sub>s</sub>, R<sub>t</sub>, R<sub>u</sub>, R<sub>v</sub>を接続した状態では、V0とV255間の抵抗が前記抵抗R<sub>s</sub>, R<sub>t</sub>, R<sub>u</sub>, R<sub>v</sub>を接続しないとき概ね1/10になるため、V0とV255間に流れる電流が増加してしまう。これによる消費電力の増加を抑制するために、図6に示すように、前記遅延制御信号CNTDを、前記補正制御信号CNTがローレベルになった後、階調電圧V0~V255の安定時間に相当する遅延期間Delayを待ってローレベルにする。

## 【0089】

10

また、例えば、アンプ2602及び2063のバイアス電流を、前記遅延制御信号CNTDがハイレベルの期間に増やして、階調電圧をシフトしたときの信号ラインLdを介した表示画素への書き込みを短時間で行えるようにしてもよい。

## 【0090】

以上のように、本発明の第2実施形態によれば、ガンマ回路26において、書き込みの初期の補正期間に、階調電圧を液晶印加電圧の絶対値が大きくなる側にシフトさせ、その後、階調電圧を正規の値にすることで、出力AMP27から、書き込みの初期の補正期間において、正規の表示信号電圧を液晶印加電圧の絶対値が大きくなる側にシフトさせた電圧を出力し、その後、正規の表示信号電圧を出力するようにすることができる、前述の第1実施形態と同様に、書き込み時間を短縮することができる。

20

## 【0091】

また、ガンマ回路26が発生する階調電圧の液晶印加電圧VLCDの絶対値が大きくなる側の電圧をシフトするように構成したことにより、回路規模を前記第1実施形態における構成よりも小さくすることができる。

## 【0092】

更に、前記抵抗R<sub>s</sub>, R<sub>t</sub>, R<sub>u</sub>, R<sub>v</sub>を分圧器2601の前記抵抗R0~R254に並列に接続して、時定数を小さくする構成を備えることにより、階調電圧を切り替えた際に階調電圧が安定するまでに要する遅延時間を短縮することができる。

## 【0093】

30

なお、本第2実施形態では、R<sub>x</sub> = R<sub>0</sub> + R<sub>1</sub> + ··· + R<sub>253</sub> + R<sub>254</sub>としたとき、R<sub>s</sub> + R<sub>t</sub> + R<sub>u</sub> + R<sub>v</sub> = R<sub>x</sub> / 10としたが、これに限るものではなく、R<sub>x</sub> / 20、あるいは、R<sub>x</sub> / 30としても良い。

## 【0094】

また、抵抗R0~R254を4ブロックに分けて、各ブロックに抵抗R<sub>s</sub>, R<sub>t</sub>, R<sub>u</sub>, R<sub>v</sub>を並列にスイッチで接続するものとしたが、これに限るものではなく、ブロック数は2ブロックから254ブロックまでなら何ブロックに分けても良い。

## 【0095】

以上、実施形態に基づいて本発明を説明したが、本発明は上述した実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形や応用が可能なことは勿論である。

## 【0096】

40

例えば、前記実施形態は、表示データを8ビット、256階調数とした場合を例に説明したが、他のビット数、階調数であっても本発明は同様に適用可能である。

## 【図面の簡単な説明】

## 【0097】

【図1】図1は、本発明の第1実施形態に係る液晶表示装置の全体構成を示す概略構成図である。

【図2】図2は、図1中のソースドライバの構成を示すブロック構成図である。

【図3】図3は、図2中の各DACの構成を示す図である。

【図4】図4は、極性信号POLと補正制御信号CNTのタイミングチャートを示す図である。

50

【図5】図5は、本発明の第2実施形態に係る液晶表示装置におけるガンマ回路の構成を示す図である。

【図6】図6は、第2実施形態における極性信号POLと補正制御信号CNTと遅延制御信号CNTDのタイミングチャートを示す図である。

【符号の説明】

【0098】

- |                                                                                |    |

|--------------------------------------------------------------------------------|----|

| 10 ... 液晶表示パネル                                                                 | 10 |

| 11 ... 液晶画素                                                                    |    |

| 20 ... ソースドライバ                                                                 |    |

| 21 ... シフトレジスタ                                                                 |    |

| 22 ... レベルシフタ                                                                  |    |

| 23 ... データレジスタ                                                                 |    |

| 24 ... データラッチ                                                                  |    |

| 25 ( 25 <sub>1</sub> ~ 25 <sub>n</sub> ) ... DAC                               |    |

| 26 ... ガンマ回路                                                                   |    |

| 27 ( 27 <sub>1</sub> ~ 27 <sub>n</sub> ) ... 出力AMP                             |    |

| 30 ... ゲートドライバ                                                                 |    |

| 40 ... LCDコントローラ                                                               |    |

| 50 ... システムコントロール回路                                                            |    |

| 2501, 2502, 2507, 2508, 2513, 2515, 2516, 2522<br>, 2523, 2529 ... ANDゲート      | 20 |

| 2503, 2509, 2517, 2518, 2524, 2525, 2530 ... インバータ                             |    |

| 2504, 2506, 2510, 2512, 2514, 2519, 2521, 2526<br>, 2528, 2604 ~ 2614 ... スイッチ |    |

| 2505, 2511, 2520, 2527 ... ORゲート                                               |    |

| 2601 ... 分圧器                                                                   |    |

| 2602, 2603 ... アンプ                                                             |    |

【図1】

図1

【図2】

図2

【図3】

【図4】

図4

【図5】

$$\begin{aligned} R_S &= (R_0 + R_1 + \dots + R_{62})/10 \\ R_t &= (R_{63} + R_{64} + \dots + R_{126})/10 \\ R_u &= (R_{127} + R_{128} + \dots + R_{190})/10 \\ R_v &= (R_{191} + R_{192} + \dots + R_{254})/10 \end{aligned}$$

【図6】

## フロントページの続き

(51)Int.CI.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 1 2 F |

| G 0 2 F | 1/133 | 5 5 0   |

| G 0 2 F | 1/133 | 5 7 5   |

| G 0 2 F | 1/133 | 5 2 5   |

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100092196

弁理士 橋本 良郎

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 順三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 井川 雅視

東京都八王子市石川町2951番地の5 カシオ計算機株式会社八王子技術センター内

審査官 森口 忠紀

(56)参考文献 特開2000-137467(JP,A)

特開2007-108668(JP,A)

特開2008-061216(JP,A)

特開2008-026510(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3 , 5 0 5 - 1 / 1 3 3 , 5 8 0