(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5952771号

(P5952771)

(45) 発行日 平成28年7月13日(2016.7.13)

(24) 登録日 平成28年6月17日(2016.6.17)

(51) Int.Cl.

G 11 C 11/406 (2006.01)

G 06 F 12/00 (2006.01)

F 1

G 11 C 11/34

G 06 F 12/003 6 3 N

5 5 0 B

請求項の数 21 (全 41 頁)

|              |                               |           |                                                                                                                                                          |

|--------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2013-91188 (P2013-91188)    | (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic of Korea |

| (22) 出願日     | 平成25年4月24日 (2013.4.24)        |           |                                                                                                                                                          |

| (65) 公開番号    | 特開2013-229096 (P2013-229096A) |           |                                                                                                                                                          |

| (43) 公開日     | 平成25年11月7日 (2013.11.7)        |           |                                                                                                                                                          |

| 審査請求日        | 平成27年9月11日 (2015.9.11)        |           |                                                                                                                                                          |

| (31) 優先権主張番号 | 10-2012-0042411               | (74) 代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                             |

| (32) 優先日     | 平成24年4月24日 (2012.4.24)        | (72) 発明者  | 金 尚 ユン<br>大韓民国京畿道華城市餅店洞安化洞マウル<br>住公5団地アパートメント501棟404号                                                                                                    |

| (33) 優先権主張国  | 韓国(KR)                        |           |                                                                                                                                                          |

| (31) 優先権主張番号 | 13/720,998                    |           |                                                                                                                                                          |

| (32) 優先日     | 平成24年12月19日 (2012.12.19)      |           |                                                                                                                                                          |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                                                                                                          |

| 早期審査対象出願     |                               |           |                                                                                                                                                          |

最終頁に続く

(54) 【発明の名称】メモリ装置及びメモリコントローラ並びにメモリシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

ウィークセルロウ (weak cell row) とノーマルセルロウ (normal cell row) とを含む複数の揮発性メモリセルのロウ (row) を備えるメモリセルアレイと、

コマンドを受信するコマンドデコーダと、

対応するウィークセルロウを識別する複数のウィークセルロウアドレスを保存するアドレステーブルと、

前記メモリセルアレイの動作を制御して前記複数の揮発性メモリセルのロウを周期的にリフレッシュするリフレッシュ制御回路とを有し、

前記リフレッシュ制御回路は、前記コマンドデコーダが、前記アドレステーブルに保存されたウィークセルロウアドレスによって第1 ウィークセルロウが識別された時、前記第1 ウィークセルロウに書き込むための書き込みコマンドを受信することに応答して前記第1 ウィークセルロウのリフレッシュ動作を行ふことを特徴とするメモリ装置。

## 【請求項 2】

前記リフレッシュ制御回路は、前記第1 ウィークセルロウに書き込むための前記書き込みコマンドを受信した後、第1 時間周期の間、リフレッシュ動作のシークエンスをモニタすることを特徴とする請求項1に記載のメモリ装置。

## 【請求項 3】

前記リフレッシュ制御回路は、前記第1 時間周期の間、前記第1 ウィークセルロウがリ

10

20

フレッシュされなかつたと判断された場合、前記リフレッシュ動作のシークエンスにリフレッシュ動作を追加することを特徴とする請求項 2 に記載のメモリ装置。

**【請求項 4】**

前記リフレッシュ制御回路は、前記第 1 時間周期より長い第 2 時間周期でノーマルセルロウをリフレッシュすることを特徴とする請求項 3 に記載のメモリ装置。

**【請求項 5】**

前記リフレッシュ制御回路は、第 2 ロウのスケジュールされたリフレッシュ動作を前記第 1 ウィークセルロウのリフレッシュ動作に差し替えることを特徴とする請求項 1 に記載のメモリ装置。

**【請求項 6】**

前記リフレッシュ制御回路は、前記第 1 ウィークセルロウのリフレッシュ動作後、直ちに前記第 2 ロウのリフレッシュ動作を行ふことを特徴とする請求項 5 に記載のメモリ装置。

**【請求項 7】**

前記リフレッシュ制御回路は、第 2 ロウのリフレッシュ動作と前記第 1 ウィークセルロウに対するリフレッシュ動作が同時に行われるようにすることを特徴とする請求項 1 に記載のメモリ装置。

**【請求項 8】**

前記リフレッシュ制御回路は、所定の時間内にリフレッシュスケジュールが前記第 1 ウィークセルロウのリフレッシュ動作を含むか否かを判断するために、前記リフレッシュスケジュールを分析することを特徴とする請求項 1 に記載のメモリ装置。

**【請求項 9】**

メモリ装置であつて、

ウィークセルロウ (weak cell row) とノーマルセルロウ (normal cell row) とを含む複数の揮発性メモリセルのロウ (row) を備えるメモリセルアレイと、

第 1 タイムウインドウでの第 1 書き込み動作を示す第 1 書き込みコマンドと、第 2 タイムウインドウでの第 2 書き込み動作を示す第 2 書き込みコマンドを受信し、前記第 1 書き込みコマンドと前記第 2 書き込みコマンドは、それぞれ異なるコマンドコードを含み、前記第 1 書き込みコマンドと前記第 2 書き込みコマンドは、前記メモリ装置に対し外部のソースから受信するコマンドデコーダと、

前記第 1 タイムウインドウでウィークセルロウに対する前記第 1 書き込み動作を遂行し、前記第 1 タイムウインドウより小さい前記第 2 タイムウインドウでノーマルセルロウに対する第 2 書き込み動作を遂行するロウデコーダとを有することを特徴とするメモリ装置。

**【請求項 10】**

前記コマンドデコーダは、前記第 1 及び第 2 書き込みコマンドのそれぞれを受信すると共に、書き込み動作が遂行されるロウを識別するそれぞれのアドレスと、前記識別されたロウに書き込む時に用いられる書き込みタイムを識別するそれぞれのコードとを受信することを特徴とする請求項 9 に記載のメモリ装置。

**【請求項 11】**

前記メモリセルアレイは、対応するウィークセルロウを識別する複数のウィークセルロウアドレスを保存するアドレステーブルをさらに含むことを特徴とする請求項 9 に記載のメモリ装置。

**【請求項 12】**

前記メモリ装置は、前記ウィークセルロウアドレスをメモリコントローラに転送することを特徴とする請求項 11 に記載のメモリ装置。

**【請求項 13】**

メモリコントローラであつて、

メモリ装置に転送されるリフレッシュコマンドと書き込みコマンドとを含む複数のコマ

10

20

30

40

50

ンドを生成する制御回路と、

前記メモリ装置の複数のウィークセルロウアドレスを保存するテーブルと、

前記メモリ装置に転送される第1書き込みコマンドと関連した第1アドレスが前記複数のウィークセルロウアドレスの内のいずれか一つに該当するか否かを判断するアドレス比較部とを有し、

前記制御回路は、前記アドレス比較部の前記判断に応答して前記第1アドレスと関連したリフレッシュ動作を含むようにリフレッシュスケジュールを調整することを特徴とするメモリコントローラ。

#### 【請求項14】

前記メモリコントローラは、前記メモリ装置から前記複数のウィークセルロウアドレスを受信し、前記受信された複数のウィークセルロウアドレスを前記テーブルに保存することを特徴とする請求項13に記載のメモリコントローラ。 10

#### 【請求項15】

前記制御回路は、前記第1アドレスに該当する第1セルロウをリフレッシュする第1リフレッシュコマンドを生成し、

前記第1セルロウは、前記第1セルロウに対する書き込み動作後、第1時間周期内にリフレッシュされることを特徴とする請求項13に記載のメモリコントローラ。

#### 【請求項16】

前記制御回路は、第2時間周期内に第2セルロウをリフレッシュする少なくとも一つの第2リフレッシュコマンドを生成し。 20

前記第2時間周期は前記第1時間周期より大きいことを特徴とする請求項15に記載のメモリコントローラ。

#### 【請求項17】

前記制御回路は、前記アドレス比較部に応答して前記テーブルに保存されたウィークセルロウに対する第1書き込みコマンドと、前記テーブルで識別されなかったノーマルセルロウに対する第2書き込みコマンドとを生成することを特徴とする請求項13に記載のメモリコントローラ。 20

#### 【請求項18】

前記第1書き込みコマンドは、前記メモリ装置が第1時間周期の間、書き込み動作を遂行するようにさせ、前記第2書き込みコマンドは前記メモリ装置が前記第1時間周期より小さい第2時間周期の間、書き込み動作を遂行するようにさせることを特徴とする請求項17に記載のメモリコントローラ。 30

#### 【請求項19】

前記第1書き込みコマンドのコマンドコードは、前記第2書き込みコマンドのコマンドコードと異なることを特徴とする請求項18に記載のメモリコントローラ。

#### 【請求項20】

前記制御回路は、第1時間インジケータを有する前記第1書き込みコマンドと、第2時間インジケータを有する前記第2書き込みコマンドとを生成し、

前記メモリ装置は、前記第1及び第2時間インジケータに応答して前記第1及び第2時間周期の間、それぞれ書き込み動作を行ふことを特徴とする請求項18に記載のメモリコントローラ。 40

#### 【請求項21】

請求項1に記載のメモリ装置と、

前記メモリ装置と通信して前記メモリ装置にコマンドを発行するメモリコントローラとを備えることを特徴とするメモリシステム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は半導体メモリ装置に関し、より詳細には、書き込み特性を向上させることのできる揮発性メモリ装置、メモリコントローラ及びメモリシステムに関する。 50

**【背景技術】****【0002】**

近年、DRAMのような揮発性メモリの動作速度が速くなることによって書き込み動作時に書き込むデータがメモリセルに十分に保存される前に、プリチャージコマンドによってワードラインが非活性化する可能性がある。

またDRAMの製造工程が微細化されるにつれ、書き込みバス上の抵抗成分の増加によって書き込み動作に困難が発生しているという問題がある。

**【先行技術文献】****【特許文献】****【0003】**

10

【特許文献1】米国特許6,058,069号明細書

【特許文献2】米国特許出願公開第2001/0024382号明細書

【特許文献3】米国特許出願公開第2006/0104144号明細書

【特許文献4】米国特許5,909,404号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

本発明は、上記従来の揮発性メモリ装置の問題点に鑑みてなされたものであって、本発明の目的は、書き込み特性を向上させることのできるメモリ装置を提供することにある。

また、本発明の他の目的は、書き込み特性を向上させることのできるメモリコントローラを提供するにある。

20

また、本発明の他の目的は、上記メモリ装置を含むメモリシステムを提供するにある。

**【課題を解決するための手段】****【0005】**

30

上記目的を達成するためになされた本発明によるメモリ装置は、Wiékセルロウ (weak cell row) とノーマルセルロウ (normal cell row) を含む複数の揮発性メモリセルのロウ (row) を備えるメモリセルアレイと、コマンドを受信するコマンドデコーダと、対応するWiékセルロウを識別する複数のWiékセルロウアドレスを保存するアドレステーブルと、前記メモリセルアレイの動作を制御して前記複数の揮発性メモリセルのロウを周期的にリフレッシュするリフレッシュ制御回路とを有し、前記リフレッシュ制御回路は、前記コマンドデコーダが、前記アドレステーブルに保存されたWiékセルロウアドレスによって第1 Wiékセルロウが識別された時、前記第1 Wiékセルロウに書き込むための書き込みコマンドを受信することに応答して前記第1 Wiékセルロウのリフレッシュ動作を行ふことを特徴とする。

**【0006】**

前記リフレッシュ制御回路は、前記第1 Wiékセルロウに書き込むための前記書き込みコマンドを受信した後、第1時間周期の間、リフレッシュ動作のシーケンスをモニタすることが好ましい。

前記リフレッシュ制御回路は、前記第1時間周期の間、前記第1 Wiékセルロウがリフレッシュされなかつたと判断された場合、前記リフレッシュ動作のシーケンスにリフレッシュ動作を追加することが好ましい。

40

前記リフレッシュ制御回路は、前記第1時間周期より長い第2時間周期でノーマルセルロウをリフレッシュすることが好ましい。

前記リフレッシュ制御回路は、第2ロウのスケジュールされたリフレッシュ動作を前記第1 Wiékセルロウのリフレッシュ動作に差し替えることが好ましい。

前記リフレッシュ制御回路は、前記第1 Wiékセルロウのリフレッシュ動作後、直ちに前記第2ロウのリフレッシュ動作を行ふことが好ましい。

前記リフレッシュ制御回路は、第2ロウのリフレッシュ動作と前記第1 Wiékセルロウに対するリフレッシュ動作が同時に行われるようにすることが好ましい。

前記リフレッシュ制御回路は、所定の時間内にリフレッシュスケジュールが前記第1ウ

50

イークセルロウのリフレッシュ動作を含むか否かを判断するために、前記リフレッシュスケジュールを分析することが好ましい。

#### 【0007】

また、上記目的を達成するためになされた本発明によるメモリ装置は、メモリ装置であつて、弱セルロウ (weak cell row)とノーマルセルロウ (normal cell row)とを含む複数の揮発性メモリセルのロウ (row)を備えるメモリセルアレイと、第1タイムウインドウでの第1書き込み動作を示す第1書き込みコマンドと、第2タイムウインドウでの第2書き込み動作を示す第2書き込みコマンドを受信し、前記第1書き込みコマンドと前記第2書き込みコマンドは、それぞれ異なるコマンドコードを含み、前記第1書き込みコマンドと前記第2書き込みコマンドは、前記メモリ装置に対し外部のソースから受信するコマンドデコーダと、前記第1タイムウインドウで弱セルロウに対する前記第1書き込み動作を遂行し、前記第1タイムウインドウより小さい前記第2タイムウインドウでノーマルセルロウに対する第2書き込み動作を遂行するロウデコーダとを有することを特徴とする。

10

#### 【0008】

前記コマンドデコーダは、前記第1及び第2書き込みコマンドのそれぞれを受信すると共に、書き込み動作が遂行されるロウを識別するそれぞれのアドレスと、前記識別されたロウに書き込む時に用いられる書き込みタイムを識別するそれぞれのコードとを受信することが好ましい。

前記メモリセルアレイは、対応する弱セルロウを識別する複数の弱セルロウアドレスを保存するアドレステーブルをさらに含むことが好ましい。

20

前記メモリ装置は、前記弱セルロウアドレスをメモリコントローラに転送することが好ましい。

#### 【0009】

上記目的を達成するためになされた本発明によるメモリコントローラは、メモリコントローラであつて、メモリ装置に転送されるリフレッシュコマンドと書き込みコマンドとを含む複数のコマンドを生成する制御回路と、前記メモリ装置の複数の弱セルロウアドレスを保存するテーブルと、前記メモリ装置に転送される第1書き込みコマンドと関連した第1アドレスが前記複数の弱セルロウアドレスの内のいずれか一つに該当するか否かを判断するアドレス比較部とを有し、前記制御回路は、前記アドレス比較部の前記判断に応答して前記第1アドレスと関連したリフレッシュ動作を含むようにリフレッシュスケジュールを調整することを特徴とする。

30

#### 【0010】

前記メモリコントローラは、前記メモリ装置から前記複数の弱セルロウアドレスを受信し、前記受信された複数の弱セルロウアドレスを前記テーブルに保存することが好ましい。

前記制御回路は、前記第1アドレスに該当する第1セルロウをリフレッシュする第1リフレッシュコマンドを生成し、前記第1セルロウは、前記第1セルロウに対する書き込み動作後、第1時間周期内にリフレッシュされることが好ましい。

前記制御回路は、第2時間周期内に第2セルロウをリフレッシュする少なくとも一つの第2リフレッシュコマンドを生成し、前記第2時間周期は前記第1時間周期より大きいことが好ましい。

40

前記制御回路は、前記アドレス比較部に応答して前記テーブルに保存された弱セルロウに対する第1書き込みコマンドと、前記テーブルで識別されなかったノーマルセルロウに対する第2書き込みコマンドとを生成することが好ましい。

前記第1書き込みコマンドは、前記メモリ装置が第1時間周期の間、書き込み動作を遂行するようにさせ、前記第2書き込みコマンドは前記メモリ装置が前記第1時間周期より小さい第2時間周期の間、書き込み動作を遂行するようにさせることが好ましい。

前記第1書き込みコマンドのコマンドコードは、前記第2書き込みコマンドのコマンドコードと異なることが好ましい。

50

前記制御回路は、第1時間インジケータを有する前記第1書き込みコマンドと、第2時間インジケータを有する前記第2書き込みコマンドとを生成し、前記メモリ装置は、前記第1及び第2時間インジケータに応答して前記第1及び第2時間周期の間、それぞれ書き込み動作を行なうことが好ましい。

#### 【0011】

上記目的を達成するためになされた本発明によるメモリシステムは、上述の本発明によるメモリ装置と、前記メモリ装置と通信して前記メモリ装置にコマンドを発行するメモリコントローラとを備えることを特徴とする。

#### 【発明の効果】

10

#### 【0012】

本発明に係るメモリ装置及びメモリコントローラ並びにメモリシステムによれば、書き込み特性がノーマルセルに比べて良くないウィークセルのポーズタイムを減少させたり、或いは書き込み回復時間を増加させてウィークセルの書き込み特性を向上させることができるという効果がある。

#### 【図面の簡単な説明】

#### 【0013】

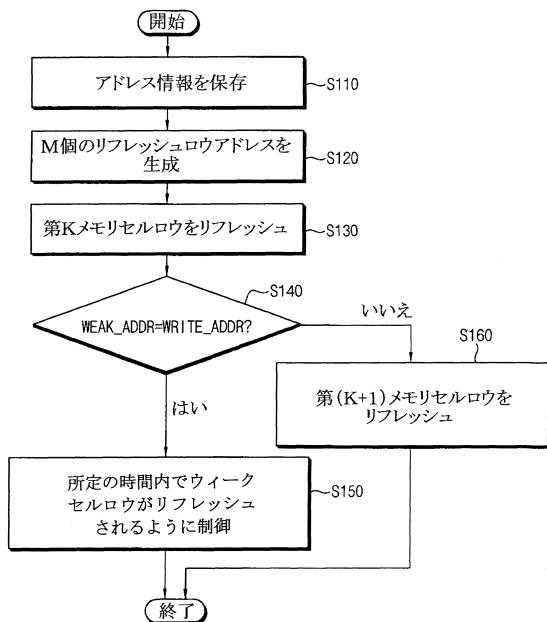

【図1】本発明の一実施形態に係る揮発性メモリ装置の動作方法を説明するためのフローチャートである。

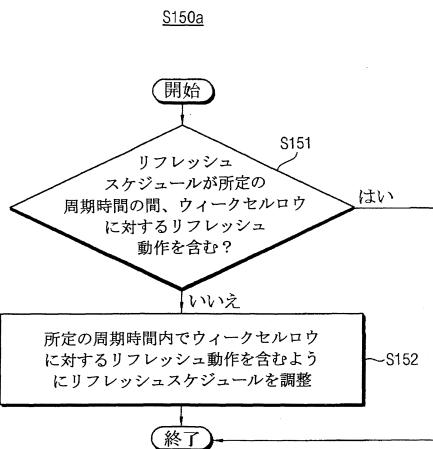

【図2】図1のステップS150の、より詳細な例示的ステップを説明するためのフローチャートである。 20

【図3】図1のステップS150の、より詳細な他の例示的ステップを説明するためのフローチャートである。

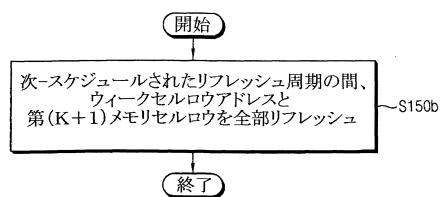

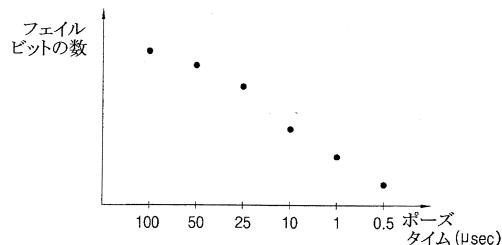

【図4】メモリセルにデータが書き込まれた後、再びリフレッシュされるまでの時間(pause time)とフェイルビット(fail bit)の数の関係を示すグラフである。

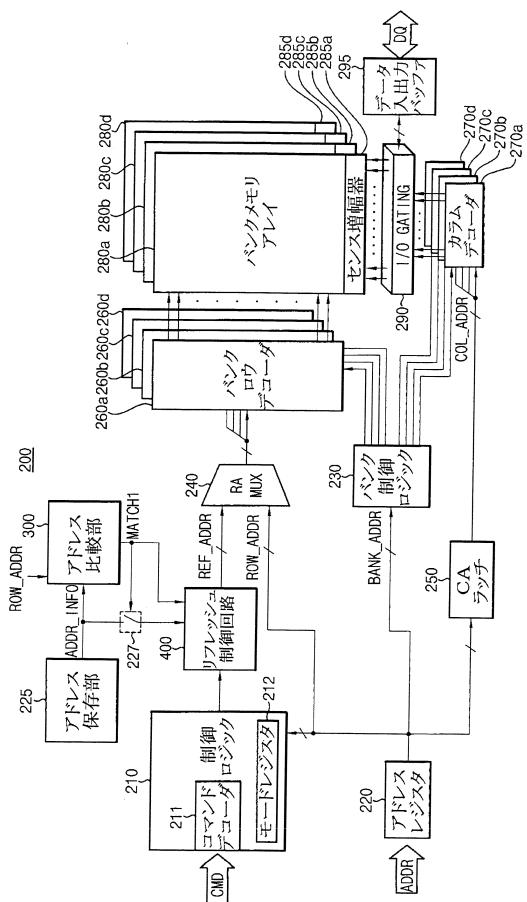

【図5】図1の動作方法を遂行する本発明の実施形態に係る揮発性メモリ装置を示すブロック図である。

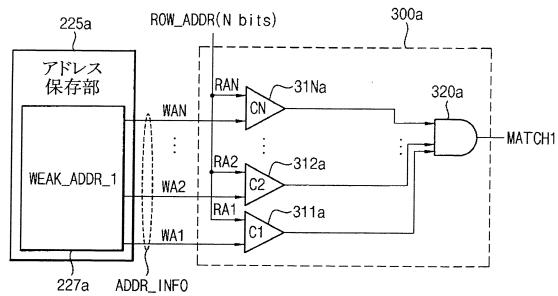

【図6】図5のアドレス保存部とアドレス比較部を例示的に示すブロック図である。

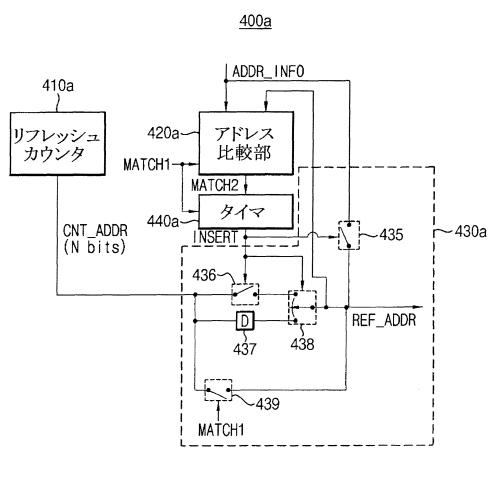

【図7】図5のリフレッシュ制御回路の構成の一例を示すブロック図である。 30

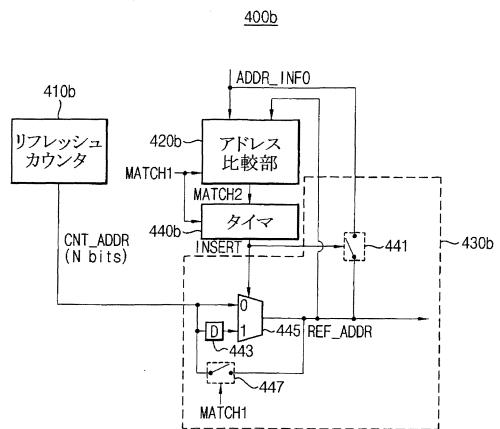

【図8】図5のリフレッシュ制御回路の構成の他の例を示すブロック図である。

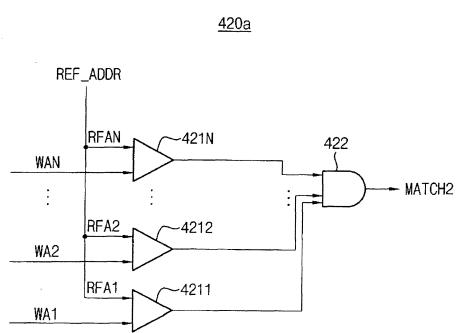

【図9】図7のアドレス比較部の構成を示す回路図である。

【図10】本発明の実施形態に係る揮発性メモリ装置の動作を説明するための図である。

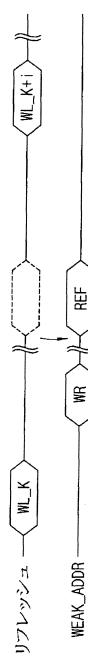

【図11】本発明の実施形態に係る揮発性メモリ装置の動作を説明するための図である。

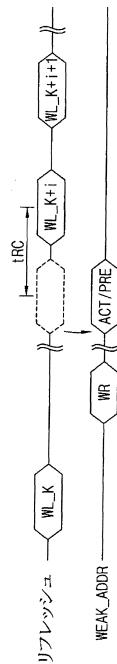

【図12】本発明の実施形態に係る揮発性メモリ装置の動作を説明するための図である。

【図13】本発明の他の実施形態に係る図5のアドレス保存部とアドレス比較部の例を示すブロック図である。

【図14】本発明の一実施形態に係る揮発性メモリ装置の動作方法を説明するためのフローチャートである。

【図15】本発明の他の実施形態に係る図5のアドレス保存部とアドレス比較部の例を示すブロック図である。 40

【図16】本発明の一実施形態に係るメモリシステムの制御方法を説明するためのフローチャートである。

【図17】図16のステップS540をより詳細に説明するためのフローチャートである。

【図18】本発明の一実施形態に係る図17の制御方法を遂行するためのメモリシステムを示すブロック図である。

【図19】本発明の実施形態に係る図18のメモリシステムの動作を説明するための図である。

【図20】本発明の実施形態に係る図18のメモリシステムの動作を説明するための図で 50

ある。

【図21】本発明の他の実施形態に係るメモリシステムの制御方法を説明するためのフローチャートである。

【図22】本発明の一実施形態に係る図21の制御方法を遂行するためのメモリシステムを示すブロック図である。

【図23】揮発性メモリ装置において、書き込み回復時間とフェイルビットの数の関係を示すグラフである。

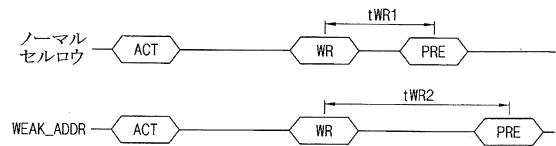

【図24】揮発性メモリ装置において、メモリセルにより書き込み特性が悪くなることを説明するためのタイミング図である。

【図25】図22のメモリシステムで書き込み回復時間が二元化されることを示す図である。10

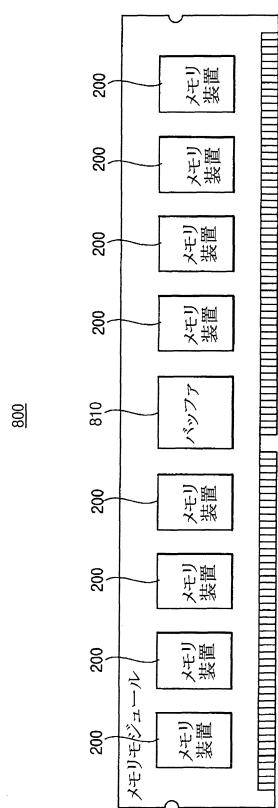

【図26】本発明の実施形態に係る揮発性メモリ装置を含むメモリモジュールを示す図である。

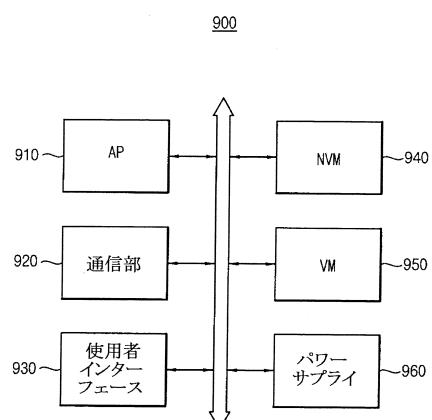

【図27】本発明の実施形態に係る揮発性メモリ装置をモバイルシステムに応用した例を示すブロック図である。

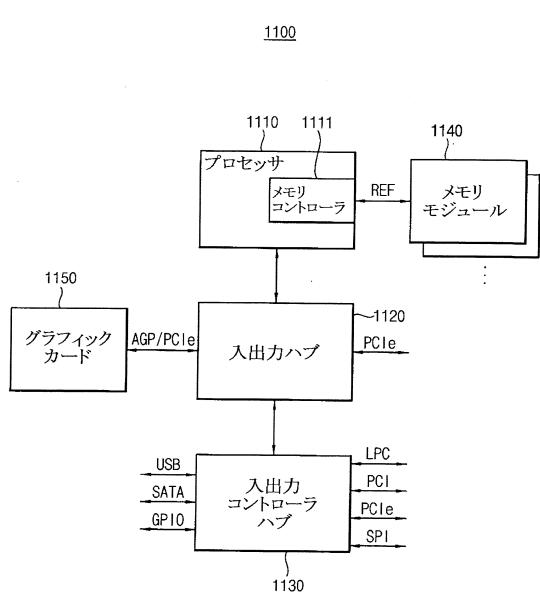

【図28】本発明の実施形態に係る揮発性メモリ装置をコンピューティング システムに応用した例を示すブロック図である。

【発明を実施するための形態】

【0014】

次に、本発明に係るメモリ装置及びメモリコントローラ並びにメモリシステムを実施するための形態の具体例を図面を参照しながら説明する。20

【0015】

本明細書で開示する本発明の実施形態に対して、特定の構造的ないし機能的説明は、単に本発明の実施形態を説明するための目的で例示したものであり、本発明の実施形態は多様な形態で実施することができ、本明細書に説明する実施形態に限定されるものではない。

【0016】

本発明は多様な変更を加えることができ、種々の形態を有することができるが、特定の実施形態を図面に例示して本明細書に詳細に説明する。しかし、これは本発明を特定の開示形態に限定しようとするものではなく、本発明の思想及び技術範囲に含まれるすべての変更、均等物ないし代替物を含むと理解するべきである。30

【0017】

本明細書において、第1、第2等の用語は多様な構成要素を説明するのに使用することができるが、これらの構成要素がこのような用語によって限定されなければならない。前記用語は一つの構成要素を他の構成要素から区別する目的で使われる。例えば、本発明の権利範囲から逸脱せずに第1構成要素は第2構成要素と命名することができ、類似に第2構成要素も第1構成要素と命名することができる。

【0018】

ある構成要素が他の構成要素に「連結されて」いる、または「接続されて」いると言及された場合には、その他の構成要素に直接的に連結されていたり、接続されていることも意味するが、中間に他の構成要素が存在する場合も含むと理解するべきである。一方、ある構成要素が他の構成要素に「直接連結されて」いる、または「直接接続されて」いると言及された場合には、中間に他の構成要素が存在しないと理解すべきである。構成要素の間の関係を説明する他の表現、すなわち「～間に」と「すぐに～間に」または「～に隣接する」と「～に直接隣接する」等も同じように解釈すべきである。40

【0019】

本明細書で使用した用語は単に特定の実施形態を説明するために使用したもので、本発明を限定するものではない。単数の表現は文脈上明白に異なるように意味しない限り、複数の表現を含む。本明細書で、「含む」または「有する」等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部品または、これを組み合わせたのが存在すると50

いうことを示すものであって、一つまたはそれ以上の他の特徴や数字、段階、動作、構成要素、部品または、これを組み合わせたものなどの存在または、付加の可能性を、予め排除するわけではない。

#### 【0020】

また、別に定義しない限り、技術的或いは科学的用語を含み、本明細書中において使用する全ての用語は本発明が属する技術分野で通常の知識を有する者であれば、一般的に理解するのと同一の意味を有する。一般的に使用される辞書において定義する用語と同じ用語は関連技術の文脈上に有する意味と一致する意味を有するものと理解するべきで、本明細書において明白に定義しない限り、理想的或いは形式的な意味として解釈してはならない。

10

#### 【0021】

一方、ある実施形態が別に実現可能な場合に特定ブロック内に明記された機能または動作がフローチャートに明記された順序と異なることもある。例えば、連続する2ブロックが実際には実質的に同時に遂行される事もでき、関連機能または動作によっては前記ブロックが逆に遂行されることもある。

図面上の同一構成要素に対しては同一参照符号を使用し、同一構成要素に対しての重複した説明は省略する。

#### 【0022】

図1は、本発明の一実施形態に係る揮発性メモリ装置の動作方法を説明するためのフローチャートである。

20

図1を参照すると、本発明の一実施形態に係る揮発性メモリ装置の動作方法では、先にアドレス情報を保存する（ステップS110）。

このようなアドレス情報は、揮発性メモリ装置のパッケージングの前又は後に、揮発性メモリ装置に含まれるアドレス保存部に保存することができる。揮発性メモリ装置は半導体メモリチップであってもよい。

#### 【0023】

また、このようなアドレス情報は、それぞれが一つ以上のウィークセルを含むメモリセルロウを表す一つ以上のウィークセルアドレスW E A K \_ A D D R を含むことができる。

ここで、ウィークセルは、書き込み性能がノーマルセルより良くないセルを意味する。

#### 【0024】

30

次に、M個のリフレッシュロウアドレスを生成する（ステップS120）。

M個のリフレッシュロウアドレスは、M個のリフレッシュロウアドレスと関連したメモリセルのリフレッシュ動作の開始以前に生成することができる。

代案としては、M個のリフレッシュロウアドレスはM個のリフレッシュロウアドレスと関連したメモリセルのリフレッシュ動作の開始中に生成することができる。

#### 【0025】

このようなリフレッシュロウアドレス生成によって、対応するローアドレスによって選択されたメモリセルに対するリフレッシュ動作が開始される。

例えば、パワーアップシークエンスが完了した後、リフレッシュ動作を開始することができる。ある実施形態においては、リフレッシュ動作は、実質的に周期的に認可されるメモリコントローラから受信されたリフレッシュコマンドR E Fに応答して内部的にリフレッシュロウアドレスを生成し、リフレッシュロウアドレスに対応するメモリセルロウをリフレッシュするオートリフレッシュ動作であるか、又はセルフリフレッシュ進入コマンドS R E に応答してセルフリフレッシュモードに進入し、セルフリフレッシュモードでビルトインタイマ（b u i l t - i n t i m e r ）を利用してメモリセルロウを周期的にリフレッシュするセルフリフレッシュ動作であってもよい。

40

#### 【0026】

また、他の実施形態においては、リフレッシュ動作は、リフレッシュサイクルが、所定の周期的なリフレッシュ間隔t R E F I を有する分散リフレッシュ（D i s t r i b u t e d R e f r e s h ）を遂行するか、又は、複数のリフレッシュサイクルが連続するバ

50

ーストリフレッシュ (Burst Refresh) を遂行することができる。

リフレッシュロウアドレスは、メモリコントローラによってメモリ装置に提供することができる。

#### 【0027】

ステップS120で生成されたM個のリフレッシュロウアドレスのうち、第Kリフレッシュロウアドレスに該当する第Kメモリセルロウがリフレッシュされる（ステップS130）。

そこで、Kは自然数であってもよい。M個のリフレッシュロウアドレスのメモリセルロウに対するリフレッシュ動作の間に一つのメモリセルロウに対する書き込み動作が発生する可能性がある。例えば、メモリコントローラのような外部のソースから特定のメモリセルロウに対する書き込みコマンドが受信されることがある。10

#### 【0028】

複数のメモリセルロウの内のいずれか一つにデータを書き込むための書き込みローアドレスとウィークセルロウアドレスとを比較する（ステップS140）。

#### 【0029】

上記比較の結果、書き込みローアドレスWRITE\_ADDRESSと、任意のウィークセルロウアドレスWEAK\_ADDRESSとが一致しない場合（ステップS140で「いいえ」）、M個のリフレッシュロウアドレスのうち、次のメモリセルロウがリフレッシュされる。

#### 【0030】

ステップS160では、第(K+1)リフレッシュロウアドレスに対応する第(K+1)20メモリセルロウをリフレッシュすることを示している。

#### 【0031】

上記比較の結果、書き込みローアドレスWRITE\_ADDRESSとウィークセルロウアドレスWEAK\_ADDRESSとが一致する場合（ステップS140で「はい」）、ウィークセルロウに該当する書き込み動作の所定の時間内でウィークセルロウアドレスに対応するウィークセルロウがリフレッシュされるように制御する（ステップS150）。

ここで、所定の時間とは、揮発性メモリ装置のテスト動作の間と同様に予め選択することができる。

所定の時間は、対応するウィークセルロウに保存されたデータが失われることを防止するためを選択されてウィークセルロウの保存特性を回復する（例えば、DRAMウィークセル内部のセルキャパシタにチャージを復元する）リフレッシュ動作が遂行されることを許容する。30

#### 【0032】

所定の時間は、ウィークセルロウのそれぞれに対して個別的に選択できるか、全てのウィークセルロウに対し同一に選択されるか、又は、複数のグループのウィークセルロウに対して複数個が選択できる。

この場合に各グループのウィークセルロウは、互いに同じ所定の時間を設ける。

図1に示したステップの間では揮発性メモリ装置に対するさまざまな違う動作、例えば書き込み動作及び読み出し動作などを遂行することができる。40

#### 【0033】

ステップS150は、ウィークセルロウと同様のリフレッシュ周期の間、第(K+1)メモリセルロウをリフレッシュするステップを含むことができる。（このような同じ周期に遂行されるリフレッシュは、順次に、又は、支援されるならば同時に遂行することができる。ウィークセルロウと第(K+1)メモリセルロウが、揮発性メモリ装置の互いに異なるバンクに含まれて並列的に動作が遂行される場合には、リフレッシュ動作を同時に遂行することができる。）。

代案としては、第(K+1)メモリセルロウに対するリフレッシュ動作は、次のスケジュールのリフレッシュ周期まで遅延されることがある。

#### 【0034】

そこで、揮発性メモリ装置のロードアドレスは、Mビット（Mは2以上の自然数）を有し、Mリフレッシュロウアドレスは、Nビットカウンタのカウント動作で生成することができる。

また、各メモリセルロウは、同じワードラインに接続されたメモリセルのロウを示し、Wiーキセルロウは書き込み特性がノーマルメモリセルに比べて良くないWiーキセルを少なくとも一つ以上含むメモリセルロウを表す。

Wiーキセルロウは、Wiーキセルとノーマルセルを全部含むことができる。

#### 【0035】

図2は、図1のステップS150のより詳細な例示的ステップを説明するためのフロー

チャートである。

10

図2を参照すると、ステップS140の後、リフレッシュスケジュールが所定の周期時間の間に、Wiーキセルロウに対するリフレッシュ動作を含んでいるか（又は、含むか）を判断するためにリフレッシュスケジュールを分析する（ステップS151）。

#### 【0036】

例えば、メモリセルロウを順次にリフレッシュする場合、（アドレスによって）、WiーキセルロウアドレスがリフレッシュロウアドレスREF\_ADDRESSとREF\_ADDRESS+Xとの間にあるか否かを判断するために、Wiーキセルロウアドレスを、リフレッシュロウアドレスREF\_ADDRESS、REF\_ADDRESS+Xと比較する。

そこで、リフレッシュロウアドレスREF\_ADDRESSはリフレッシュ動作に対して現在スケジュールされたロウであり、Xは所定の周期時間の間にリフレッシュ動作がスケジュールされたメモリセルロウの数を表す。

20

#### 【0037】

他の例においては、アドレスによって順次に、又は、非順次にメモリセルロウに対するリフレッシュスケジュールを含むテーブルが検査されて、Wiーキセルロウが所定の周期時間内でリフレッシュがスケジュールされているかを判断する。

もし、リフレッシュスケジュールが所定の周期時間内でWiーキセルロウに対するリフレッシュ動作を含む場合（ステップS151で「はい」）、リフレッシュスケジュールは変動しないで、ステップS150aが完了する（又は、第（K+1）メモリセルロウに対するリフレッシュのような次のスケジュールされたリフレッシュ動作が完了した途端、完了する）。

30

#### 【0038】

もし、リフレッシュスケジュールが所定の周期時間内でWiーキセルロウに対するリフレッシュ動作を含まない場合（ステップS151で「いいえ」）、リフレッシュスケジュールは、所定の周期時間内でWiーキセルロウに対するリフレッシュ動作を含むように調整する（ステップS152）。

例えば、Wiーキセルロウアドレスに対するリフレッシュ動作をリフレッシュスケジュールを含むテーブルに追加することができる。又は、Wiーキセルロウアドレスが次にリフレッシュされるロウとして挿入され、挿入されていなかった場合は、リフレッシュできるようにスケジュールされたロウアドレスを遅延させることができる（例えば、リフレッシュカウンタの出力を「1」リフレッシュサイクル分遅延させてWiーキセルロウアドレスが次にリフレッシュをロウとして挿入することができる）。ステップS150aは、ステップS152後に完了する（又は、第（K+1）メモリセルロウに対するリフレッシュのような次のスケジュールされたリフレッシュ動作が完了した途端、完了する）。

40

#### 【0039】

図3は、図1のステップS150の、より詳細な他の例示的ステップを説明するためのフロー

チャートである。

図3を参照すると、M個のリフレッシュロウアドレスのうち、リフレッシュロウアドレスREF\_ADDRESSに対応する以前の、「次にスケジュールされた」ロウと比較することにより、「次にスケジュールされた」リフレッシュ周期の間、Wiーキセルロウアドレスがリフレッシュされる。例えば、このような以前の、「次にスケジュールされた」ロウア

50

ドレスは、リフレッシュが順次に遂行される場合、第(  $K + 1$  )メモリセルロウであってもよい。

#### 【 0 0 4 0 】

「次にスケジュールされた」ロウアドレスとウィークセルロウは、順次に、又は、同時にリフレッシュできる。

例えば、ウィークセルロウが、直ちにリフレッシュされ、リフレッシュロウアドレス R E F \_ A D D R に対応する以前の「次にスケジュールされた」ロウは、ロウサイクルタイム t R C の後でリフレッシュすることができる。ロウサイクルタイム t R C は、フルサイクルを完了するために必要なクロックサイクルの数に該当する時間であり、一つのロウをプリチャージ実行と活性化実行を含む。

10

#### 【 0 0 4 1 】

ステップ S 1 5 0 b に対する代案的な実施形態として、本発明の方法は「次のスケジュールされた」リフレッシュ動作に該当するリフレッシュロウアドレス R E F \_ A D D R とウィークセルロウアドレスが同一であるか否かが先に判断することができる。

互いに同じである場合に、次のリフレッシュ動作はウィークセルロウに対するリフレッシュ動作であってもよい( 従って、追加的なリフレッシュ動作を避けることができる。 )

。

#### 【 0 0 4 2 】

他の実施形態においては、ウィークセルロウが所定の時間内にリフレッシュされるよう 20 にできる。例えば、書き込み動作後、書き込み動作後の第1期間内に発生する全てのリフレッシュ動作をモニタすることができる。この第1期間内にウィークセルロウがリフレッシュされなければ、メモリ装置又はコントローラがウィークセルロウに対するリフレッシュを発生するようにして所定の時間内にウィークセルロウがリフレッシュされるようにすることができる。例えば、ウィークセルロウが次のリフレッシュアドレスとしてリフレッシュロウアドレスのシークエンスに追加される場合、メモリ装置又はメモリコントローラでメモリ装置に対するリフレッシュコマンドを発行することができる。

#### 【 0 0 4 3 】

即ち、本発明の一実施形態に係る揮発性メモリ装置の動作方法においては、ウィークセルロウアドレス W E A K \_ A A D R と書き込みロウアドレス W R I T E \_ A D D R が一致する場合、即ち、ウィークセルに書き込み動作を遂行する場合にはウィークセルに書き込まれたデータが失われる前の、所定の時間内でウィークセルロウをリフレッシュすることができる。

30

#### 【 0 0 4 4 】

図4は、メモリセルにデータが書き込まれた後、再びリフレッシュされるまでの時間( pause time )とフェイルビット( fail bit )の数との関係を示すグラフである。

#### 【 0 0 4 5 】

図4を参照すると、メモリセルにデータが書き込まれた後、再びリフレッシュされるまでの時間( pause time )が増加する分、フェイルビットの数が増加することがわかる。

40

本発明の実施形態に係る揮発性メモリ装置の動作方法では、このようなフェイルビットの数が増加することを防止するためにウィークセルロウをノーマルセルロウに比べて、最初書き込み後、より早くリフレッシュすることができる。

例えば、ウィークセルロウは、第(  $K + 1$  )メモリセルロウに対するリフレッシュのような、次のスケジュールされたリフレッシュ動作と同時に、又は順次にリフレッシュされるか、或いは、リフレッシュスケジュールが所定の時間内にウィークセルロウに対するリフレッシュ動作が含まれるように修正できる。

#### 【 0 0 4 6 】

図5は、図1の動作方法を遂行する本発明の実施形態に係る揮発性メモリ装置を示すブロック図である。

50

図5を参照すると、揮発性メモリ装置200は、制御ロジック210、アドレスレジスタ220、バンク制御ロジック230、ロウアドレスマルチプレクサ240、カラムアドレスラッチ250、ロウデコーダ、カラムデコーダ、メモリセルアレイ、センスアンプ部、入出力ゲート回路290、データ入出力バッファ295、アドレス保存部225、アドレス比較部(address comparing unit(ACU))300、及びリフレッシュ制御回路(refresh control circuit)400を含む。

#### 【0047】

メモリセルアレイは、第1～第4バンクメモリアレイ(280a、280b、280c、280d)を含む。また、ロウデコーダは、第1～第4バンクメモリアレイ(280a、280b、280c、280d)にそれぞれ接続された第1～第4バンクロウデコーダ(260a、260b、260c、260d)を含み、カラムデコーダは第1～第4バンクメモリアレイ(280a、280b、280c、280d)にそれぞれ接続された第1～第4バンクカラムデコーダ(270a、270b、270c、270d)を含み、センスアンプ部は第1～第4バンクメモリアレイ(280a、280b、280c、280d)にそれぞれ接続された第1～第4センス増幅器(285a、285b、285c、285d)を含むことができる。10

#### 【0048】

第1～第4バンクメモリアレイ(280a、280b、280c、280d)、第1～第4センス増幅器(285a、285b、285c、285d)、第1～第4バンクロウデコーダ(260a、260b、260c、260d)、及び第1～第4バンクカラムデコーダ(270a、270b、270c、270d)は、第1～第4バンクをそれぞれ構成する。20

図4には4個のバンクを含む揮発性メモリ装置200の例を示すが、実施形態により、揮発性メモリ装置200は任意の数のバンクを含むことができる。

#### 【0049】

また、実施形態により、揮発性メモリ装置200は、DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)、LPDDR(Low Power Double Data Rate)SDRAM、GDDR(Graphics Double Data Rate)SDRAM、RDRAM(登録商標)(Rambus(登録商標)Dynamic Random Access Memory)などようなDRAM(Dynamic Random Access Memory)であるか、または、リフレッシュ動作を含む任意の揮発性メモリ装置であってもよい。30

#### 【0050】

アドレスレジスタ220は、メモリコントローラ(図示せず)からバンクアドレスBANK\_ADDRESS、ロウアドレスROW\_ADDRESS、及びカラムアドレスCOL\_ADDRESSを含むアドレスADDRを受信する。

アドレスレジスタ220は、受信されたバンクアドレスBANK\_ADDRESSをバンク制御ロジック230に提供し、受信されたロウアドレスROW\_ADDRESSをロウアドレスマルチプレクサ240に提供し、受信されたカラムアドレスCOL\_ADDRESSをカラムアドレスラッチ250に提供する。40

#### 【0051】

バンク制御ロジック230は、バンクアドレスBANK\_ADDRESSに応答してバンク制御信号を生成する。

バンク制御信号に応答して、第1～第4バンクロウデコーダ(260a、260b、260c、260d)の内の、バンクアドレスBANK\_ADDRESSに対応するバンクロウデコーダが活性化され、第1～第4バンクカラムデコーダ(270a、270b、270c、270d)の内の、バンクアドレスBANK\_ADDRESSに対応するバンクカラムデコーダが活性化される。50

**【0052】**

ロウアドレスマルチプレクサ240は、アドレスレジスタ220からロウアドレスROW\_ADDRESSを受信し、リフレッシュ制御回路400からリフレッシュロウアドレスREF\_ADDRESSを受信する。

ロウアドレスマルチプレクサ240は、ロウアドレスROW\_ADDRESS又はリフレッシュロウアドレスREF\_ADDRESSを選択的に出力することができる。ロウアドレスマルチプレクサ240から出力されたロウアドレスは、第1～第4バンクロウデコーダ(260a、260b、260c、260d)にそれぞれ印加される。

**【0053】**

第1～第4バンクロウデコーダ(260a、260b、260c、260d)の内の、

10

バンク制御ロジック230により活性化されたバンクロウデコーダは、ロウアドレスマルチプレクサ240から出力されたロウアドレスをデコーディングしてロウアドレスに対応するワードラインを活性化する。

例えば、活性化されたバンクロウデコーダは、ロウアドレスに対応するワードラインにワードライン駆動電圧を印加する。ワードライン駆動電圧は対応するワードラインに接続されたメモリセルのアクセストランジスタをターンオンさせ、メモリセルのデータがビットラインの対に転送されて感知増幅器によって増幅することができるようになる。データの感知は知られているようにメモリセルに前記データをリストアしてデータをリフレッシュすることができる。

**【0054】**

カラムアドレスラッチ250は、アドレスレジスタ220からカラムアドレスCOL\_ADDRESSを受信し、受信されたカラムアドレスCOL\_ADDRESSを一時的に保存する。

また、カラムアドレスラッチ250は、バーストモードで、受信されたカラムアドレスCOL\_ADDRESSを徐々に増加させることができる。カラムアドレスラッチ250は、一時的に保存、又は、徐々に増加したカラムアドレスCOL\_ADDRESSを第1～第4バンクカラムデコーダ(270a、270b、270c、270d)にそれぞれ印加する。

**【0055】**

第1～第4バンクカラムデコーダ(270a、270b、270c、270d)の内の、

30

バンク制御ロジック230により活性化されたバンクカラムデコーダは、入出力ゲート回路290を介してンクアドレスBANK\_ADDRESS及びカラムアドレスCOL\_ADDRESSに対応するセンスアンプを活性化させる。

**【0056】**

入出力ゲート回路290は、入出力データをゲーティングする回路と共に、入力データマスクロジック、第1～第4バンクメモリアレイ(280a、280b、280c、280d)から出力されたデータを保存するための読み出しデータラッチ、及び第1～第4バンクメモリアレイ(280a、280b、280c、280d)にデータを書き込むための書き込みドライバを含む。

**【0057】**

第1～第4バンクメモリアレイ(280a、280b、280c、280d)の内の、

40

いずれか一つのバンクメモリアレイから読み出しがれるデータDQは、一つのバンクメモリアレイに対応するセンスアンプによって感知され、読み出しデータラッチに保存される。

読み出しデータラッチに保存されたデータDQは、データ入出力バッファ295を介してメモリコントローラに提供される。第1～第4バンクメモリアレイ(280a、280b、280c、280d)の内のいずれか一つのバンクメモリアレイに書き込みされるデータDQは、メモリコントローラからデータ入出力バッファ295に提供される。データ入出力バッファ295に提供されたデータDQは書き込みドライバを介して一つのバンクメモリアレイに書き込みされる。

**【0058】**

制御ロジック210は、揮発性メモリ装置200の動作を制御する。

10

20

30

40

50

例えば、制御ロジック 210 は、揮発性メモリ装置 200 が書き込み動作又は読み出し動作を遂行するための制御信号を生成する。

制御ロジック 210 は、メモリコントローラから受信されるコマンド CMD をデコードするコマンドデコーダ 211 及び揮発性メモリ装置 200 の動作モードを設定するためのモードレジスタ 212 を含む。例えば、コマンドデコーダ 211 は、書き込みイネーブル信号 ( /WE )、ロウアドレスストローブ信号 ( /RAS )、カラムアドレスストローブ信号 ( /CAS )、チップ選択信号 ( /CS ) などをデコードしてコマンド CMD に対応する制御信号を生成する。また、制御ロジック 210 は、同期方式で揮発性メモリ装置 200 を駆動するためのクロック信号 ( CLK ) 及びクロックイネーブル信号 ( /CKE ) をさらに受信する。また、制御ロジック 210 はリフレッシュコマンド REF に応答してリフレッシュ制御回路 400 がオートリフレッシュ動作を遂行するよう制御したり、セルフリフレッシュ進入口mand SRE に応答してリフレッシュ制御回路 400 がセルフリフレッシュ動作を遂行するよう制御する。

10

#### 【0059】

アドレス保存部 225 は、少なくとも一つのウィークセルロウに対するアドレス情報 ADDR\_INFO を保存する。

アドレス保存部 225 に保存されたアドレス情報 ADDR\_INFO は、メモリセルアレイに含まれたウィークセルロウのロウアドレスである。一実施形態において、アドレス情報 ADDR\_INFO は揮発性メモリ装置のパッケージング前にアドレス保存部 225 に保存させることができる。他の実施形態において、アドレス情報 ADDR\_INFO は揮発性メモリ装置のパッケージング後にアドレス保存部 225 に保存させることもできる。

20

実施形態により、アドレス保存部 225 は電気的プログラマブル・フューズ・メモリ ( programmable fuse memory )、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワンタイム・プログラマブル・メモリ、フラッシュメモリなどの多様な種類の不揮発性メモリ装置で具現できる。

#### 【0060】

ウィークセルロウは、メモリ装置及び / 又はメモリ装置を含む半導体パッケージの製造工程の一部であるテストを介して決定できる。

ウィークセルロウの数は、メモリセルをウィークセルとノーマルセル ( 従って、ウィークセルロウとノーマルセルロウ ) とに区分するメモリセルの最小データ保有時間を決める関数として調節することができる。

30

ウィークセルロウの数は、ウィークセルロウをスペアメモリセルロウに変えて調節することができる。ウィークセルロウの数はメモリセルロウの少なくとも 2 % 又は少なくとも 10 %、或いは、20 % でもある。

#### 【0061】

アドレス比較部 300 は、アドレスレジスタ 220 から受信した ( 接続関係は図 5 に示していない ) ロウアドレス ROW\_ADDRESS をアドレス保存部 225 から読み出されたアドレス情報 ADDR\_INFO と比較する。

アドレス比較部 300 は、上記比較の結果に基づいて、第 1 マッチ信号 MATCH1 を生成する。例えば、メモリセルロウにデータを書き込むための書き込みロウアドレス ROW\_ADDRESS とアドレス情報 ADDR\_INFO に含まれるウィークセルロウアドレスが一致しない場合、アドレス比較部 330 は、第 1 ロジックレベルの第 1 マッチ信号 MATCH1 をスイッチ 227 とリフレッシュ制御回路 400 に提供する。例えば、メモリセルロウにデータを書き込むための書き込みロウアドレス ROW\_ADDRESS とアドレス情報 ADDR\_INFO に含まれるウィークセルロウアドレスが一致する場合、アドレス比較部 330 は第 2 ロジックレベルの第 1 マッチ信号 MATCH1 をスイッチ 227 とリフレッシュ制御回路 400 に提供する。

40

#### 【0062】

スイッチ 227 は、第 1 マッチ信号 MATCH1 の論理レベルによってアドレス保存部

50

225から読み出されたアドレス情報ADDRLINFOを選択的にリフレッシュ制御回路400に提供する。

例えば、書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDRLINFOに含まれるウィークセルロウアドレスが一致しなくて第1マッチ信号MATCH1が第1ロジックレベルを有する場合、スイッチ227はアドレス情報ADDRLINFOをリフレッシュ制御回路400に提供することができないことがある。例えば、書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDRLINFOに含まれるウィークセルロウアドレスが一致して第1マッチ信号MATCH1が第2ロジックレベルを有する場合、スイッチ227はアドレス情報ADDRLINFOをリフレッシュ制御回路400に提供することができる。10

#### 【0063】

例えば、アドレスレジスタ220から受信したロウアドレスROW\_ADDRESSがアドレス保存部225に保存されたアドレスの内のいずれか一つとマッチする場合、第1マッチ信号MATCH1は第1ロジックレベルから第2ロジックレベルに遷移することができる。

第2ロジックレベルに応答してスイッチ227が閉じられて、マッチングされるロウアドレスがリフレッシュ制御回路400に転送される。第1マッチ信号MATCH1が第1ロジックレベルから第2ロジックレベルへ遷移されると、リフレッシュ制御回路400は転送されたマッチングされるロウアドレスをラッチし、処理する。20

#### 【0064】

リフレッシュ制御回路400は、第1マッチ信号MATCH1が表す上記比較の結果に基づき、メモリセルロウを順次にリフレッシュするか、又は、アドレス情報ADDRLINFOに含まれるウィークセルロウアドレスに上昇するウィークセルロウのリフレッシュを制御する。

例えば、書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDRLINFOに含まれるウィークセルロウアドレスが一致しなくて第1マッチ信号MATCH1が第1ロジックレベルを有する場合、アドレス制御回路400はメモリセルロウを順次にリフレッシュする。例えば、書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDRLINFOに含まれるウィークセルロウアドレスが一致して第1マッチ信号MATCH1が第2ロジックレベルを有する場合、リフレッシュ制御回路400はウィークセルロウのボーズタイム(pause time)が短縮するようにウィークセルロウのリフレッシュを制御する。30

#### 【0065】

図6は、図5のアドレス保存部とアドレス比較部を例示的に示すブロック図である。

図6を参照すると、アドレス保存部225aは、一つ以上のウィークセルロウアドレスWEAK\_ADDRESS\_1を保存する第1保存領域227aを含む。

説明の便宜のために、一つのウィークセルロウアドレスWEAK\_ADDRESS\_1を表している。実施形態により、アドレス保存部225は電気的プログラマブル・フューズ・メモリ、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワントライム・プログラマブル・メモリ、フラッシュメモリなどのような多様な種類の不揮発性メモリ装置で具現できる。40

#### 【0066】

アドレス比較部300aは、アドレスレジスタ220からロウアドレスROW\_ADDRESSを受信し、アドレス保存部225aからウィークセルロウアドレスWEAK\_ADDRESS\_1を受信する。

アドレス比較部300aはロウアドレスROW\_ADDRESSとウィークセルロウアドレスWEAK\_ADDRESS\_1を比較して第1マッチ信号MATCH1を生成する。

#### 【0067】

アドレス比較部300aは、複数の比較器(311a、312a、31Na)及びアンドゲート320aを含む。50

第1比較器311aは、ロウアドレスROW\_ADDRESSの第1ビットRA1とウィークセルロウアドレスWEAK\_ADDRESS\_1の第1ビットWA1とを比較し、第2比較器312aはリフレッシュロウアドレスROW\_ADDRESSの第2ビットRA2とウィークセルロウアドレスWEAK\_ADDRESS\_1の第2ビットWA2とを比較し、第N比較器31NaはロウアドレスROW\_ADDRESSの第NビットRANとウィークセルロウアドレスWEAK\_ADDRESS\_1の第NビットWANとを比較し、ANDゲート320aは第1～第N比較器(311a、312a、31Na)の出力信号にAND演算を遂行して第1マッチ信号MATCH1を生成する。従って、第1マッチ信号MATCH1は書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスとが一致しない場合、第1ロジックレベルを有することができ、書き込みロウアドレスROW\_ADDRESSとアドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスとが一致する場合、第2ロジックレベルを有することができる。

10

#### 【0068】

図7は、図5のリフレッシュ制御回路400の構成の一例を示すブロック図である。

図7を参照すると、リフレッシュ制御回路400aは、リフレッシュカウンタ410a、アドレス比較部420a、リフレッシュロウアドレス出力部430a、及びタイマ440aを含んで構成させる。

#### 【0069】

リフレッシュカウンタ410aは、複数のメモリセルロウを順次にリフレッシュするための内部リフレッシュロウアドレスCNT\_ADDRESSを生成する。

20

リフレッシュカウンタ410aは、Nビットカウンタで構成され、Nビットの内部リフレッシュロウアドレスCNT\_ADDRESSを生成する。

#### 【0070】

アドレス比較部420aは、第1マッチ信号MATCH1が第2ロジックレベルを有する場合に活性化し、アドレス保存部225aから読み出されるアドレス情報ADDR\_INFOとリフレッシュロウアドレス出力部430aからロウアレスマルチプレクサ240に提供されるリフレッシュロウアドレスREF\_ADDRESSとを比較し、比較結果による第2マッチ信号MATCH2を生成する。

例えば、アドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスWEAK\_ADDRESS\_1とリフレッシュロウアドレスREF\_ADDRESSとが一致しない場合、アドレス比較部420aは第1ロジックレベルの第2マッチ信号MATCH2を提供する。例えば、アドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスWEAK\_ADDRESS\_1とリフレッシュロウアドレスREF\_ADDRESSとが一致する場合、アドレス比較部420aは第2ロジックレベルの第2マッチ信号MATCH2を提供する。

30

#### 【0071】

タイマ440aは、第1マッチ信号MATCH1が第2ロジックレベルを有する場合活性化する。

第1マッチ信号MATCH1の第1ロジックレベルから第2ロジックレベルへの遷移に応答してタイマ440aは動作を始める(即ち、もしタイマ440aがカウンタである場合にはカウントを始める)。所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信すると(これは、リフレッシュロウアドレスREF\_ADDRESSとアドレス情報ADDR\_INFOとして提供されるウィークセルロウアドレスWEAK\_ADDRESS\_1との間にマッチが発生したことを表す)、タイマ440aはその出力信号であるインサート信号INSERTを第1ロジックレベルに維持する。

40

所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信しないと、タイマ440aはインサート信号INSERTを第2ロジックレベルに出力する。

#### 【0072】

リフレッシュロウアドレス出力部430aは、第1～第4スイッチ(435、436、

50

438、439)、及び、遅延素子437を含んで構成される。

第4スイッチ439は、第1マッチ信号M A T C H 1が第1ロジックレベルを有する場合に接続され、第1マッチ信号M A T C H が第2ロジックレベルを有する場合に切断される。即ち、第4スイッチ439はウィークセルロウアドレスW E A K \_ A D D R \_ 1と書き込みロウアドレスR O W \_ A D D R が一致しない場合、第1ロジックレベルの第1マッチ信号M A T C H に応答して接続され、内部リフレッシュロウアドレスC N T \_ A D D R をリフレッシュロウアドレスR E F \_ A D D R としてアドレスマルチプレクサ240に提供する。

#### 【0073】

第1スイッチ435と第2スイッチ436は、インサート信号I N S E R T が第1ロジックレベルを有する場合に切断され、インサート信号I N S E R T が第2ロジックレベルを有する場合には第1スイッチ435は接続されて第2スイッチ436は切断される。10

遅延素子437は、隣接したメモリセルロウのリフレッシュ間隔分の遅延時間有し、内部リフレッシュロウアドレスC N T \_ A D D R を遅延させる。

第3スイッチ438は、インサート信号I N S E R T が第1ロジックレベルを有する場合、第2スイッチ436に接続され、インサート信号I N S E R T が第2ロジックレベルを有する場合、遅延素子437に接続される。

#### 【0074】

即ち、リフレッシュロウアドレス出力部430aは、ウィークセルロウアドレスW E A K \_ A D D R \_ 1と書き込みロウアドレスR O W \_ A D D R が一致しない場合、第1マッチ信号M A T C H 1が第1ロジックレベルである場合は内部リフレッシュロウアドレスC N T \_ A D D R を、リフレッシュロウアドレスR E F \_ A D D R としてアドレスマルチプレクサ240に提供する。20

第1マッチ信号M A T C H 1が第1ロジックレベルということは、アドレスレジスタ220から受信したロウアドレスとアドレス保存部225に保存されたアドレスとの間にマッチがないということを表す。また、リフレッシュロウアドレス出力部430aは第1マッチ信号M A T C H 1がインサート信号I N S E R T によって第2ロジックレベルの場合、ウィークセルロウアドレスW E A K \_ A D D R \_ 1と内部リフレッシュロウアドレスC N T \_ A D D R の内の一つを選択してリフレッシュロウアドレスR E F \_ A D D R としてアドレスマルチプレクサ240とに提供する。この場合、ウィークセルロウアドレスW E A K \_ A D D R \_ 1に該当する第Kメモリセルロウのワードラインと内部リフレッシュロウアドレスR E F \_ A D D R に該当する第(K+1)メモリセルロウのワードラインが、バンクロウデコーダによって順次に活性化して第Kメモリセルロウと第(K+1)メモリセルロウが順次にリフレッシュされる。30

#### 【0075】

メモリセルアレイの第1～第4バンクメモリアレイ(280a、280b、280c、280d)が互いに並列にリフレッシュを遂行する場合は、ウィークセルロウアドレスと内部リフレッシュロウアドレスC N T \_ A D D R に該当するメモリセルロウが同時にリフレッシュできる。

他の実施形態においては、内部リフレッシュロウアドレスC N T \_ A D D R とウィークセルロウアドレスW E A K \_ A D D R \_ 1が全部それぞれ異なる信号経路を介してロウアドレスマルチプレクサ240に提供され、ロウアドレスマルチプレクサ240は、このロウアドレスを適切なバンクロウデコーダ(260a、260b、260c、260d)に転送することを制御して、同時に又は順次に各自のリフレッシュ動作を遂行するようとする。

また、リフレッシュロウアドレス出力部430aは、第1マッチ信号M A T C H 1が第2ロジックレベルであり、インサート信号I N S E R T が第2ロジックレベルの場合は、遅延された内部的に生成されたリフレッシュロウアドレスが遅延素子437を経由して遅延された後、リフレッシュロウアドレスR E F \_ A D D R として持続的にアドレスマルチプレクサ240に提供する。4050

## 【0076】

図8は、図5のリフレッシュ制御回路の構成の他の例のを示すブロック図である。

図8を参照すると、リフレッシュ制御回路400bは、リフレッシュカウンタ410b、アドレス比較部420b、リフレッシュロウアドレス出力部430b、及びタイマ440bを含んで構成される。

## 【0077】

リフレッシュカウンタ410bは、複数のメモリセルロウを順次にリフレッシュするための内部リフレッシュロウアドレスCNT\_ADDRESSを生成する。

リフレッシュカウンタ410bは、Nビットカウンタで構成されてNビットの内部リフレッシュロウアドレスCNT\_ADDRESSを生成する。

10

## 【0078】

アドレス比較部420bは、第1マッチ信号MATCH1が第2ロジックレベルを有する場合に活性化し、アドレス保存部225aから読み出されるアドレス情報(ADDR\_INFO、例えば、ウィークロウアドレスWEAK\_ADDRESS\_1)とリフレッシュロウアドレス出力部430bからロウアドレスマルチプレクサ240に提供されるリフレッシュロウアドレスREF\_ADDRESSとを比較し、比較結果による第2マッチ信号MATCH2を生成する。

例えば、アドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスWEAK\_ADDRESS\_1とリフレッシュロウアドレスREF\_ADDRESSとが一致しない場合、アドレス比較部420bは第1ロジックレベルの第2マッチ信号MATCH2を提供する。20

例えば、アドレス情報ADDR\_INFOに含まれるウィークセルロウアドレスWEAK\_ADDRESS\_1とリフレッシュロウアドレスREF\_ADDRESSとが一致する場合、アドレス比較部420bは第2ロジックレベルの第2マッチ信号MATCH2を提供する。

20

## 【0079】

タイマ440bは、第1マッチ信号MATCH1が第2ロジックレベルを有する場合にイネーブルされる。

第1マッチ信号MATCH1の第1ロジックレベルから第2ロジックレベルへの遷移に応答してタイマ440bは動作を始める(即ち、タイマ440aがカウンタの場合、カウントを始める)。所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信すると(これは、リフレッシュロウアドレスREF\_ADDRESSとアドレス情報ADDR\_INFOとして提供されるウィークセルロウアドレスWEAK\_ADDRESS\_1との間にマッチが発生したことを表す)、タイマ440bはその出力信号であるインサート信号INSERTを第1ロジックレベルに維持する。

30

所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信しない場合、タイマ440aはインサート信号INSERTを第2ロジックレベルに出力する。

## 【0080】

リフレッシュロウアドレス出力部430bは、第1スイッチ及び第2スイッチ441、447、遅延素子443、及びマルチプレクサ445を含んで構成される。

第2スイッチ447は、第1マッチ信号MATCH1が第1ロジックレベルを有する場合に接続され、第1マッチ信号MATCHが第2ロジックレベルを有する場合に切断される。即ち、第2スイッチ447はウィークセルロウアドレスWEAK\_ADDRESS\_1と書き込みロウアドレスROW\_ADDRESSとが一致しない場合、第1ロジックレベルの第1マッチ信号MATCHに応答して接続され、内部リフレッシュロウアドレスCNT\_ADDRESSをリフレッシュロウアドレスREF\_ADDRESSとしてアドレスマルチプレクサ240に提供する。

40

## 【0081】

第1スイッチ441は、インサート信号INSERTが第1ロジックレベルを有する場合に切断され、インサート信号INSERTがMATCH2が第2ロジックレベルを有する場合に接続される。

50

遅延素子 443 は、tRC (active to active) ほどの遅延時間をして、内部リフレッシュロウアドレス CNT\_ADDR の出力を遅延させる（そして、以後には生成された内部リフレッシュロウアドレス CNT\_ADDR を遅延させる）。

マルチブレクサ 445 は、インサート信号 INSERT が第 1 ロジックレベルを有する場合に内部リフレッシュロウアドレス CNT\_ADDR を選択し、インサート信号 INSERT が第 2 ロジックレベルを有する場合に遅延素子 443 の出力を選択する。

#### 【0082】

即ち、リフレッシュロウアドレス出力部 430b は、wi-クセルロウアドレス WEAK\_ADDR\_1 と書き込みロウアドレス ROW\_ADDR とが一致しない場合に、第 1 マッチ信号 MATCH1 が第 1 ロジックレベルである場合は内部リフレッシュロウアドレス CNT\_ADDR をリフレッシュロウアドレス REF\_ADDR としてアドレスマルチブレクサ 240 に提供する。10

また、リフレッシュロウアドレス出力部 430b は、第 1 マッチ信号 MATCH1 がインサート信号 INSERT によって第 2 ロジックレベルである場合は、wi-クセルロウアドレス WEAK\_ADDR\_1 と内部リフレッシュロウアドレス CNT\_ADDR の内のいずれか一つを選択してリフレッシュロウアドレス REF\_ADDR としてアドレスマルチブレクサ 240 に提供する。

#### 【0083】

また、リフレッシュロウアドレス出力部 430b は、第 1 マッチ信号 MATCH1 が第 2 ロジックレベルであり、インサート信号 INSERT が第 2 ロジックレベルである場合は、遅延された内部リフレッシュロウアドレスをリフレッシュロウアドレス REF\_ADDR としてアドレスマルチブレクサ 240 に提供する。20

ここで、記載した信号 MATCH1、MATCH2、INSERT と関連した第 1 ロジックレベル及び第 2 ロジックレベルと関連して、第 1 ロジックレベルは必ず互いに同一である必要もなく、第 2 ロジックレベルは必ず互いに同一である必要はない。

個別的な信号に対して記述された第 1 ロジックレベルと第 2 ロジックレベルとは、その信号のロジック状態の違い又は変化を意味するものである。

#### 【0084】

図 9 は、図 7 のアドレス比較部の構成の一例を示す回路図である。

図 9 を参照すると、アドレス比較部 420a は、複数の比較器 (4211、4212、421N)、及び、アンドゲート 422 を含む。30

第 1 比較器 4211 は、リフレッシュロウアドレス REF\_ADDR の第 1 ビット RF A1 と wi-クセルロウアドレス WEAK\_ADDR\_1 の第 1 ビット WA1 とを比較し、第 2 比較器 4212 は、リフレッシュロウアドレス ROW\_ADDR の第 2 ビット RF A2 と wi-クセルロウアドレス WEAK\_ADDR\_1 の第 2 ビット WA2 とを比較し、第 N 比較器 421N はロウアドレス ROW\_ADDR の第 N ビット RFAN と wi-クセルロウアドレス WEAK\_ADDR\_1 の第 N ビット WAN とを比較し、AND ゲート 422 は、第 1 ~ 第 N 比較器 (4211、4212、421N) の出力信号に AND 演算を遂行して、第 2 マッチ信号 MATCH2 を生成する。40

#### 【0085】

従って、第 2 マッチ信号 MATCH2 は、リフレッシュロウアドレス REF\_ADDR とアドレス情報 ADDR\_INFO に含まれるwi-クセルロウアドレスとが一致しない場合、第 1 ロジックレベルを有することができ、リフレッシュロウアドレス REF\_ADDR とアドレス情報 ADDR\_INFO に含まれるwi-クセルロウアドレスとが一致する場合、第 2 ロジックレベルを有することができる。

図 9 に示してはしていないが、第 1 マッチ信号 MATCH1 は、アンドゲート 422 に別途の入力端子を介して入力することができ、又は、第 1 ~ 第 N 比較器 (4211、4212、421N) の内のいずれか一つ以上をイネーブルさせるのに用いることができる。

#### 【0086】

他の実施形態においては、アドレス比較部 420a の出力は、セット端子に第 1 マッチ50

信号MATCH1が入力されて出力端子がアンドゲート422に接続されるフリップフロップに入力させることができる。フリップフロップは多様な信号によってリセットできるが、例えば、第2マッチ信号MATCH2又はインサート信号INSERTのそれぞれが遷移に応答して第2ロジックレベルにリセットすることができる。

図9では図7のアドレス比較部420aに対して説明したが、図8のアドレス比較部420bも図7のアドレス比較部420aと実質的に同じ構成を有することができる。

#### 【0087】

図10～図12は、それぞれ本発明の実施形態に係る揮発性メモリ装置の動作を説明するための図である。

図10ではウィークセルロウアドレスWEAK\_ADDRESSとリフレッシュロウアドレスREF\_ADDRESSがそれぞれ異なる場合を説明する。

10

#### 【0088】

図10を参照すると、先に第Kリフレッシュロウアドレスによって第KメモリセルロウWL\_Kに対してリフレッシュが遂行される。

第KメモリセルロウWL\_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK\_ADDRESSに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込まれる。

ここでは、ウィークセルロウアドレスWEAK\_ADDRESSとリフレッシュロウアドレスREF\_ADDRESSとが異なるので所定の時間内で第Kリフレッシュロウアドレス以後のリフレッシュロウアドレスの内のいずれか一つである第(K+i)メモリセルロウ(WL\_K+i)に対してリフレッシュが遂行される時、同時にウィークセルロウアドレスWEAK\_ADDRESSに該当するウィークセルロウをリフレッシュREFする。

20

所定の時間は、書き込み命令WRを受信した後に発生するi番のリフレッシュ動作の数に該当する。次に、第(K+i)リフレッシュロウアドレスに連続する第(K+i+1)リフレッシュロウアドレスに対応する第(K+i+1)メモリセルロウ(WL\_K+i+1)に対してリフレッシュが遂行される。

#### 【0089】

図11及び12ではウィークセルロウアドレスWEAK\_ADDRESSとリフレッシュロウアドレスREF\_ADDRESSが互いに一致する場合を説明する。

図11を参照すると、先ず、第Kリフレッシュロウアドレスによって第KメモリセルロウWL\_Kに対してリフレッシュが遂行される。

30

第KメモリセルロウWL\_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK\_ADDRESSに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込まれる。

ここでは、ウィークセルロウアドレスWEAK\_ADDRESSと書き込みコマンドWRが受信された以後から所定の時間の間、リフレッシュロウアドレスREF\_ADDRESSの内のいずれか一つと互いに一致するので、リフレッシュカウンタによって生成されたリフレッシュアドレスCNT\_ADDRESSのリフレッシュシーケンスは変更される必要がなく、ウィークセルロウに対する追加的なリフレッシュが必要ない。

40

#### 【0090】

図12を参照すると、先に第Kリフレッシュロウアドレスに従って、第KメモリセルロウWL\_Kに対してリフレッシュが遂行される。

第KメモリセルロウWL\_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK\_ADDRESSに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込みされる。

ここでは、ウィークセルロウアドレスWEAK\_ADDRESSと第KリフレッシュロウアドレスREF\_ADDRESSが所定の時間の間、リフレッシュロウアドレスREF\_ADDRESSの内のいずれか一つと互いに一致しないので、リフレッシュカウンタによって生成されたリフレッシュアドレスCNT\_ADDRESSのリフレッシュシーケンスは、ウィークセルロウに対するリフレッシュ動作を含むように変更される。

50

**【0091】**

第(  $K + i$  )メモリセルロウ  $WL_{(K+i)}$  をリフレッシュする動作は、時間  $t_{RC}$  ほど延期される。

ウィークセルロウアドレスに該当するリフレッシュ動作又は第(  $K + i$  )メモリセルロウに対するリフレッシュ動作からのリフレッシュインターバルに対応する時間が経過した後、第(  $K + i$  )メモリセルロウ  $WL_{(K+i)}$  に対するオートリフレッシュ動作が再開される。

リフレッシュインターバルは、ロウサイクルタイム  $t_{RC}$  より実質的により大きい。例えば、ロウサイクルタイム  $t_{RC}$  より、5倍又は10倍又は100倍大きいこともできる。例えば、リフレッシュインターバルがこの時、3.9マイクロ秒と設定されると、ロウサイクルタイム  $t_{RC}$  は、約60ナノ秒と設定され得る。

10

**【0092】**

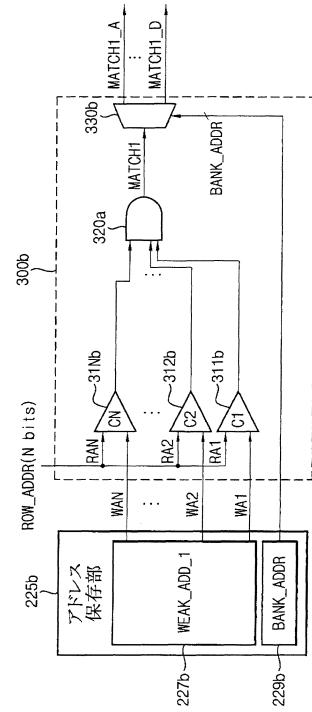

図13は、本発明の他の実施形態に係る図5に含まれるアドレス保存部の例とアドレス比較部の例を示すブロック図である。

図13を参照すると、アドレス保存部225bは、ウィークセルロウアドレス  $WEAK\_ADDR_1$  を保存する第1保存領域227b、及びバンク情報としてバンクアドレス  $BANK\_ADDR$  を保存する第2保存領域229bを含む。

**【0093】**

アドレス比較部300bは、アドレスレジスタ220からロウアドレス  $ROW\_ADDR$  を受信し、アドレス保存部225bからウィークセルロウアドレス  $WEAK\_ADDR_1$  及びバンクアドレス  $BANK\_ADDR$  を受信する。

20

アドレス比較部300bは、ロウアドレス  $ROW\_ADDR$  とウィークセルロウアドレス  $WEAK\_ADDR_1$  とを比較した結果に基づいて第1マッチ信号  $MATCH_1$  をバンク( 265a、365d )のうち、バンクアドレス  $BANK\_ADDR$  に対応するバンクに提供する。

**【0094】**

アドレス比較部300bは、複数の比較器( 311b、312b、31Nb )、アンドゲート320b、及びデマルチプレクサ330bを含む。

複数の比較器( 311b、312b、31Nb )、及びアンドゲート320bは、書き込みロウアドレス  $ROW\_ADDR$  とウィークセルロウアドレス  $WEAK\_ADDR_1$  とが一致する場合、第2ロジックレベルを有する第1マッチ信号  $MATCH_1$  をデマルチプレクサ330bに提供する。

30

デマルチプレクサ330bは、バンクアドレス  $BANK\_ADDR$  に応答して第1マッチ信号  $MATCH_1$  を複数のバンクマッチ信号(  $MATCH_1\_A \sim MATCH_1\_D$  )のうち、バンクアドレス  $BANK\_ADDR$  に対応するバンクマッチ信号として出力する。これにより、複数のバンク( 265a ~ 265d )のうち、バンクアドレス  $BANK\_ADDR$  に対応するバンクに第1マッチ信号  $MATCH_1$  が印加される。

**【0095】**

これにより、バンクマッチ信号(  $MATCH_1\_A \sim MATCH_1\_D$  )のうち、バンクアドレス  $BANK\_ADDR$  に対応するバンクに対するバンクマッチ信号だけが活性化するので、アドレス制御回路400は、上述した一つ以上的方法に従って、ウィークセルロウアドレスに基づいてウィークセルロウのリフレッシュを制御することができる。

40

**【0096】**

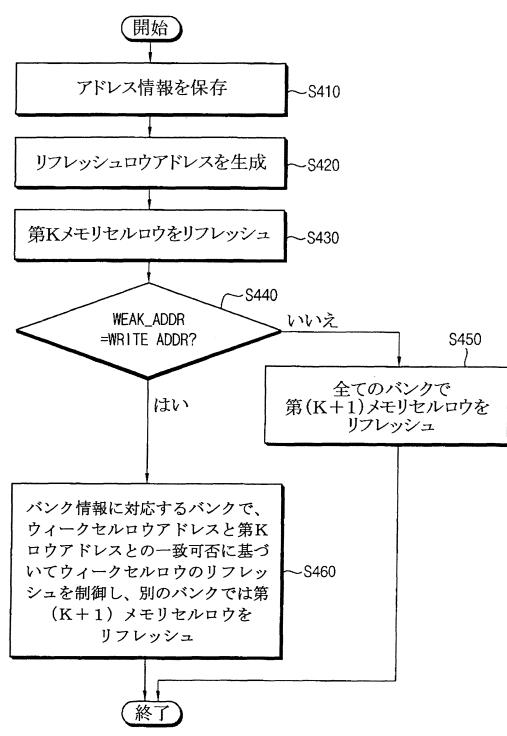

図14は、本発明の一実施形態に係る揮発性メモリ装置の動作方法を説明するためのフローチャートである。

図14のフローチャートは、図13のアドレス保存部225bとアドレス比較部300bが図5の揮発性メモリ装置に含まれる場合の揮発性メモリ装置200の動作方法に適用される。

**【0097】**

図13及び図14を参照すると、先ず、アドレス保存部225bにアドレス情報  $ADD$

50

R\_INF0を保存する(ステップS410)。

ここで、アドレス情報ADDRIINFOは、少なくとも一つのウィークセルロウを含むウィークセルロウアドレスWEAK\_ADDR\_1とバンクアドレスBANK\_ADDRを含む。

このようなアドレス情報ADDRIINFOは、揮発性メモリ装置200のパッケージングの前又は後にアドレス保存部225bに保存することができる。

次に、リフレッシュロウアドレスを生成する(ステップS420)。

このようなリフレッシュロウアドレス生成によってリフレッシュ動作が開始される。

#### 【0098】

生成されたリフレッシュロウアドレスのうち、第Kリフレッシュロウアドレスによって揮発性メモリ装置に含まれる複数のメモリセルロウのうち、第Kメモリセルロウをリフレッシュする(ステップS430)。10

メモリセルロウに対するリフレッシュが遂行されている途中(即ち、第Kリフレッシュロウアドレスに対応する第Kメモリセルロウをリフレッシュした後、第Kメモリセルロウをリフレッシュする前に第Kメモリセルロウに対する書き込み命令によって第Kメモリセルロウにデータを書き込む場合)、次に揮発性メモリ装置に含まれる複数のメモリセルロウの内のいずれか一つのメモリセルロウにデータを書き込むための書き込みロウアドレスとウィークセルロウアドレスとを比較する(ステップS440)。

上記比較の結果、書き込みロウアドレスとセルロウアドレスとが一致しない場合(ステップS440で「いいえ」)、全てのバンク(380a~380d)で第Kリフレッシュロウアドレスに連続する第(K+1)リフレッシュロウアドレスに対応する第(K+1)メモリセルロウをリフレッシュする(S450)。20

#### 【0099】

上記比較の結果、書き込みロウアドレスとウィークセルロウアドレスとが一致する場合(ステップS450で「はい」)、所定の時間内にウィークセルロウがリフレッシュされる。

例えば、バンクアドレスBANK\_ADDRに対応するバンクのウィークセルロウは、他のバンクで第(K+1)リフレッシュロウアドレスに対応する第(K+1)メモリセルロウがリフレッシュされるのと同時にリフレッシュされる(ステップS460)。30

バンクアドレスBANK\_ADDRに対応する第(K+1)メモリセルロウはウィークセルロウのリフレッシュに連続して直ちにリフレッシュされる。

バンクアドレスBANK\_ADDRに対応する第(K+1)メモリセルロウは、ウィークセルロウのリフレッシュ動作の開始後、ロウサイクルタイムtRC後にリフレッシュ動作を始める。

#### 【0100】

また、バンクアドレスBANK\_ADDRを利用してバンクアドレスBANK\_ADDRに対応するバンクにおいてのみ、ウィークセルロウアドレスとスケジュールリングされたりフレッシュロウアドレスとの一致の有無に基づいてウィークセルロウアドレスに対応するウィークセルロウのリフレッシュを制御して(ウィークセルロウを選択的にリフレッシュして)ポーズタイム(pause time)を減少させることができる。40

#### 【0101】

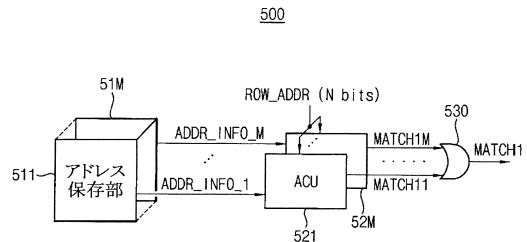

図15は、本発明の他の実施形態に係る図5に含まれるアドレス保存部の例とアドレス比較部の例を示すブロック図である。

図15を参照すると、揮発性メモリ装置500は、複数のアドレス保存部(511~51M)、複数の比較部(521~52M)及び、OR演算部530を含んで構成される。

#### 【0102】

複数のアドレス保存部(511~51M)は、複数のウィークセルロウに対する複数のアドレス情報(ADDR\_INFO\_1~ADDR\_INFO\_M)のそれぞれを保存する。

実施形態により、複数のアドレス保存部(511~51M)は、一つの保存装置で具現50

されるか、又は、複数の保存装置で具現されることができる。例えば、各保存装置は、電気的プログラマブル・フューズ・メモリ、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワンタイム・プログラマブル・メモリ、フラッシュメモリなどのような多様な種類の不揮発性メモリ装置の内のいずれか一つであってもよい。

#### 【0103】

複数の比較部(521～52M)は、複数のアドレス保存部(511～51M)にそれぞれ接続され、アドレスレジスタ220から受信したリフレッシュロウアドレスREF\_ADDRESSを複数のアドレス保存部(511～51M)から読み出された複数のアドレス情報(Address\_INFO\_1～Address\_INFO\_M)とそれぞれ比較する。

複数の比較部(521～52M)は、上記比較の結果に基づいて複数のマッチ信号(MATCH11～MATCH1M)をそれぞれ生成する。10

OR演算部530は、複数の比較部(521～52M)から受信した複数のマッチ信号(MATCH11～MATCH1M)に、OR演算を遂行して第1マッチ信号MATCH1を生成する。

#### 【0104】

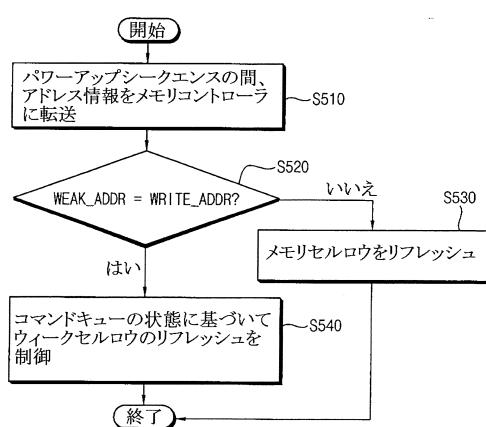

図16は、本発明の一実施形態に係るメモリシステムの制御方法を説明するためのフローチャートである。

図16を参照すると、本発明の一実施形態に係るメモリシステムの制御方法は、メモリシステムのパワーアップシークエンスの間、アドレス情報を揮発性メモリ装置からメモリコントローラに転送する(S510)。20

そこで、アドレス情報は、揮発性メモリ装置のアドレス保存部からメモリコントローラのアドレス比較部に転送する。メモリコントローラのアドレス比較部でアドレス情報に含まれるWi－クセルロウアドレスと揮発性メモリ装置のメモリセルロウをアクセスするための書き込みロウアドレスを比較する(ステップS520)。

#### 【0105】

上記比較の結果として、書き込みロウアドレスとWi－クセルロウアドレスと一致しない場合(ステップS520で「いいえ」)、メモリコントローラが所定のスケジュールに従って(例えば、パターンに従って、相対的な位置に従って、又は、テーブルを参照してメモリセルロウを順次にリフレッシュ)、揮発性メモリ装置を制御してメモリセルロウがリフレッシュされるようにする(ステップS530)。30

上記比較の結果として、書き込みロウアドレスとWi－クセルロウアドレスと一致する場合(ステップS520で「はい」)、メモリコントローラに含まれるコマンドキュー(command queue)がアイドル状態であるか否かに基づいてWi－クセルロウのリフレッシュを制御する(ステップS540)。例えば、メモリコントローラは、リフレッシュ動作のスケジュールを修正してコマンドキューのアイドルタイムの間にWi－クセルロウに対するリフレッシュ動作が含まれるようにする。

#### 【0106】

即ち、本発明の実施形態に係る図16のメモリシステムの制御方法では、書き込みロウアドレスとWi－クセルロウアドレスとが一致する場合、メモリコントローラに含まれるコマンドキューがアイドル状態であるか否かに基づいてWi－クセルロウのリフレッシュを制御する。40

#### 【0107】

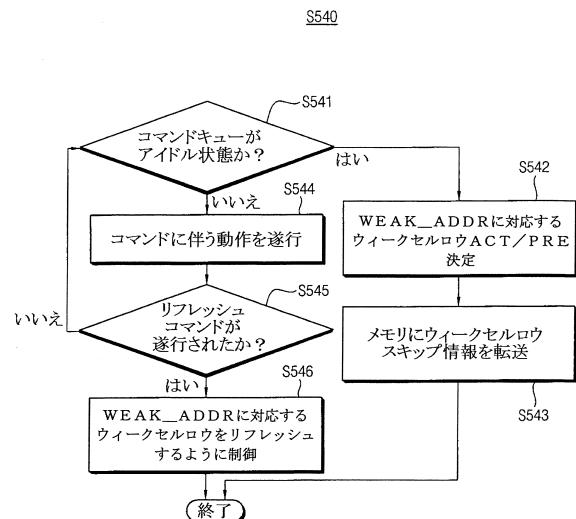

図17は、図16のステップS540をより詳細に説明するためのフローチャートである。

図17を参照すると、書き込みロウアドレスとWi－クセルロウアドレスとが一致する場合、メモリコントローラに含まれるコマンドキューがアイドル状態であるか否かに基づいてWi－クセルロウのアドレスを制御するために、先ず、メモリコントローラのコマンドキューがアイドル状態か否かの第1判断をする(ステップS541)。

ここで、コマンドキューがアイドル状態というのは、メモリコントローラが揮発性メモリ装置に対しいずれの動作も遂行していないことを意味する。50

## 【0108】

第1判断の結果として、コマンドキューがアイドル状態の場合（ステップS541で「はい」）、Wiークセルロウアドレスに対応するWiークセルロウがWiークセルロウに書き込み動作が遂行された後、活性化してプリチャージされたと決定される。

活性化及びプリチャージ動作は、他のメモリ装置でのリフレッシュ動作と等価又は同一である。

メモリコントローラは、揮発性メモリ装置にWiークセルロウに対してリフレッシュを遂行しないというリフレッシュスキップ情報を転送する（ステップS543）。

もし、ステップS542において、Wiークセルロウがプリチャージされないと決定されると、図17には示していないが、本方法はステップS546に進行することができる。

10

## 【0109】

第1判断の結果としてコマンドキューがアイドル状態でなくビジー（busy）状態なら（ステップS541で「いいえ」）、コマンドキューに保存されたコマンドに伴う動作を遂行する（ステップS544）。

次に、遂行されたコマンドにリフレッシュコマンドが含まれているか否かの第2判断をする（ステップS545）。

第2判断の結果として、遂行されたコマンドにリフレッシュコマンドが含まれていなくて、リフレッシュが遂行されない場合（ステップS545で「いいえ」）にはステップS541に戻る。

20

第2判断の結果として、遂行されたコマンドにリフレッシュコマンドが含まれていてリフレッシュが遂行される場合（ステップS545で「はい」）、メモリコントローラは揮発性メモリ装置のアドレス制御回路がWiークセルロウアドレスに対応するWiークセルロウに対してリフレッシュを遂行するように揮発性メモリ装置を制御する（ステップS546）。

## 【0110】

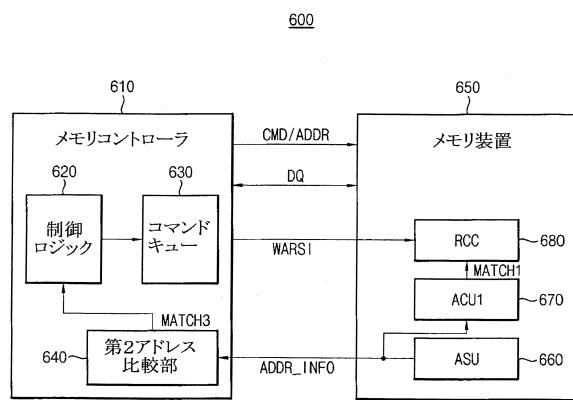

図18は、本発明の一実施形態に係る図17の制御方法を遂行するためのメモリシステムを示すブロック図である。

図18を参照すると、メモリシステム600は、メモリコントローラ610、及び揮発性メモリ装置650を含んで構成される。

30

メモリコントローラ610は、揮発性メモリ装置650にコマンドCMD及びアドレスADDRを転送し、メモリコントローラ610と揮発性メモリ装置610はデータDQを交換する。

## 【0111】

メモリコントローラ610は、制御ロジック620、コマンドキュー630、及び第2アドレス比較部640を含んで構成される。

揮発性メモリ装置650は、アドレス保存部（ASU：address storing unit）660、第1アドレス比較部（ACU1）670、及びリフレッシュ制御回路（RCC：refresh control circuit）680を含んで構成される。

40

第1アドレス比較部670は、アドレス情報ADDR\_INFOとメモリコントローラ610から提供される書き込み口アドレスROW\_ADDRとを比較し、その比較に基づいて第1マッチ信号MATCH1をリフレッシュ制御回路680に提供する。

## 【0112】

メモリシステム600のパワーアップシーケンスの間に揮発性メモリ装置650のアドレス保存部660から第2アドレス比較部640にWiークセルロウアドレスを含むアドレス情報ADDR\_INFOが転送される。

メモリコントローラ610の第2アドレス比較部640は、アドレス情報ADDR\_INFOと揮発性メモリ装置650のメモリセルロウにアクセスするための書き込み口アドレスROW\_ADDRとを比較し、その比較結果に基づいた第3マッチ信号MATCH

50

3を制御ロジック620に転送する。

#### 【0113】

例えば、Wi－eクセルロウアドレスと書き込みロウアドレスROW\_\_ADDRとが一致しない場合、第3マッチ信号MATCH3は、第1ロジックレベルを有する。

第3マッチ信号MATCH3が第1ロジックレベルを有する場合、制御ロジック620は、揮発性メモリ装置650のリフレッシュ制御回路680を制御して、リフレッシュ制御回路680において揮発性メモリ装置650によりリフレッシュ制御回路680内のアドレスカウンタによって、又は、リフレッシュ制御回路680内のテーブルを参照して内部的に生成されるリフレッシュロウアドレスによってメモリセルロウがリフレッシュされるようにする。10

#### 【0114】

例えば、Wi－eクセルロウアドレスと書き込みロウアドレスROW\_\_ADDRが一致する場合、第3マッチ信号MATCH3は、第2ロジックレベルを有する。

第3マッチ信号MATCH3が第2ロジックレベルを有する場合、制御ロジック620は、コマンドキュー630がアイドル状態であるか否かをモニタしてコマンドキューがアイドル状態であるか否かによりリフレッシュ制御回路680がWi－eクセルロウのリフレッシュを制御するようになる。

例えば、メモリコントローラの次のアイドル区間の間又はコマンドキュー630のコマンドの発行を邪魔しないでリフレッシュコマンドを提供することが可能である場合、制御ロジック620は、Wi－eクセルロウに対するリフレッシュコマンドを提供する。20

他の実施形態においては、制御ロジック620はコマンドキューのコマンドの発行をインタラプトしてWi－eクセルロウに対するリフレッシュコマンドを提供することができる。例えば、Wi－eクセルロウに対する書き込み動作後の、所定の時間内でWi－eクセルロウに対するリフレッシュが遂行されるようになる。

#### 【0115】

例えば、コマンドキュー630がアイドル(idle)状態の場合、制御ロジック620は、Wi－eクセルロウアドレスに対応するWi－eクセルロウが活性化且つプリチャージされたと決定されると、Wi－eクセルロウに対するリフレッシュスキップ情報(weak address row refresh skip information(WARI))を揮発性メモリ装置650のリフレッシュ制御回路680に転送する。30

例えば、コマンドキュー630がアイドル状態ではない場合、制御ロジックはコマンドキュー630に保存されたコマンドに伴う動作が遂行されるように揮発性メモリ装置650を制御した後、遂行されたコマンドにリフレッシュコマンドが含まれていると、Wi－eクセルロウがリフレッシュできるようにリフレッシュ制御回路680を制御する。

他の実施形態においては、リフレッシュスケジュールに対する修正は、メモリコントローラ610のみによって遂行することができる。例えば、アドレス比較部670は揮発性メモリ装置650に含まれないようにもできる。

#### 【0116】

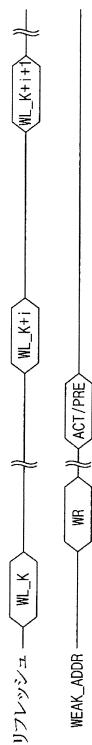

図19及び図20は、それぞれ本発明の実施形態に係る図18のメモリシステムの動作を説明するための図である。40

図19及び図20ではWi－eクセルロウアドレスと書き込みロウアドレスが一致する場合を説明する。

図19では図18のコマンドキュー630がアイドル状態の場合のメモリシステム600の動作を表す。

#### 【0117】

図19を参照すると、先ず、揮発性メモリ装置650で第Kリフレッシュロウアドレスにより、第KメモリセルロウWL\_Kに対してリフレッシュが遂行される。

第KメモリセルロウWL\_Kに対してリフレッシュが遂行された後、Wi－eクセルロウアドレスWEAK\_\_ADDRに該当するWi－eクセルロウに書き込み動作をするための書き込み命令WRが受信される。この時、コマンドキュー630がアイドル状態にあるので50

、制御ロジック 620 は、Wi－クセルロウに対するリフレッシュ動作を挿入するというリフレッシュ情報を転送する。

#### 【0118】

これはリフレッシュ制御回路 680 にノーマルリフレッシュコマンドを提供するか、又は、リフレッシュ動作のスケジュールを修正するというコマンドを提供してWi－クセルロウがリフレッシュ（活性化及びプリチャージ（ACT / PRE））されるように遂行させる。以後、第（K + i + 1）メモリセルロウ（WL\_K + i + 1）がリフレッシュされる）。

第（K + i + 1）メモリセルロウ（WL\_K + i + 1）は、第（K + i）メモリセルロウ（WL\_K + i）がリフレッシュされた後、直ちにリフレッシュされるか、又は、リフレッシュインターバル（ロウサイクルタイム tRC より少なくとも 5 倍、10 倍または、50 倍大きいリフレッシュインターバル）ほど遅延してリフレッシュする。

10

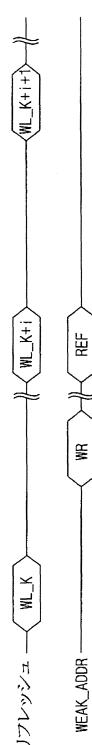

#### 【0119】

図 20 では図 18 のコマンドキュー 630 がアイドル状態ではない場合、メモリシステム 600 の動作を表す。

図 20 を参照すると、第 K リフレッシュロウアドレスによって第 K メモリセルロウ WL\_K をリフレッシュする。

本動作は、Wi－クセルロウと次にリフレッシュされるようスケジュールリングされたロウ（WL\_k + i）が同時にリフレッシュされることを除いては図 19 と同一である。

20

#### 【0120】

従って、図 16 ~ 図 20 を参照して説明したように、書き込みロウアドレスと Wi－クセルロウアドレスとが一致する場合、メモリコントローラに含まれるコマンドキューがアイドル状態であるか否かに基づいて Wi－クセルロウのアドレスを制御して Wi－クセルロウのポーズタイムを減少させて揮発性メモリ装置の書き込み特性を向上させることができる。

#### 【0121】

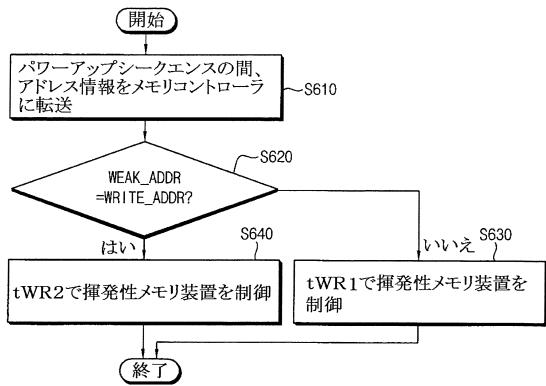

図 21 は、本発明の他の実施形態に係るメモリシステムの制御方法を説明するためのフロー チャートである。

図 21 を参照すると、本発明の他の実施形態に係るメモリシステムの制御方法では、メモリシステムのパワーアップシーケンスの間にアドレス情報を揮発性メモリ装置からメモリコントローラに転送する（ステップ S610）。

30

ここで、アドレス情報は、揮発性メモリ装置のアドレス保存部からメモリコントローラのアドレス比較部に転送する。

メモリコントローラのアドレス比較部において、アドレス情報に含まれる一つ以上の Wi－クセルロウアドレスと揮発性メモリ装置のメモリセルロウをアクセスするための書き込みロウアドレスとを比較する（ステップ S620）。

メモリコントローラのトランザクションプロセッサ（transaction processor）は、上記比較の結果により、ノーマルセルロウに対する第 1 書き込み回復時間に依存する第 1 タイムウインドウとノーマルセル以外の Wi－クセルロウに対する第 2 書き込み回復時間に依存する第 2 タイムウインドウを含む、それぞれ異なるタイムウインドウで揮発性メモリ装置を制御する（ステップ S630、ステップ S640）。

40

#### 【0122】

上記比較の結果として、書き込みロウアドレスと Wi－クセルロウアドレスとが一致しない場合（ステップ S620 で「いいえ」）、トランザクションプロセッサは、第 2 書き込み回復時間が、標準において提案された又は定義された最小書き込み回復時間のような第 1 書き込み回復時間と同一になるように揮発性メモリ装置を制御する（ステップ S630）。

上記比較の結果として、書き込みロウアドレスと Wi－クセルロウアドレスと一致する場合（ステップ S620 で「はい」）、トランザクションプロセッサは、第 2 書き込み回復時間が第 1 書き込み回復時間よりさらに長いように揮発性メモリ装置を制御する（ステ

50

ツブ S 6 4 0 )。

実施形態によっては、ウィークセルロウの第2書き込み回復時間は、ノーマルセルロウの第1書き込み回復時間の少なくとも2倍であってもよい。例えば、標準によりノーマルセルロウに対する書き込み回復時間  $t_{WR}$  が 15 ns である場合、ウィークセルロウの書き込み回復時間は 30 ns であってもよい。

【 0 1 2 3 】

書き込み回復時間  $t_{WR}$  は、メモリセルにデータが書き込みされる時間に該当するので、ウィークセルロウにデータを書き込む時間はノーマルセルロウにデータを書き込む時間の 2 倍になり得る。

例えば、同期式DRAMにおいて、書き込み回復時間tWRは、書き込みコマンドとともにデータの最後の部分が入力された直後のデータラッチングクロックのエッジから同期式DRAMによって、プリチャージコマンドが正しく入力されるまでの時間（図24においてT9からTmまでの時間）に該当する。

書き込み回復時間が長くなるほどウィークセルロウに書き込み動作が正しく遂行される時間がさらに多く確保することができる（例えば、D R A Mのキャパシタが正しく充電され得る。）

[ 0 1 2 4 ]

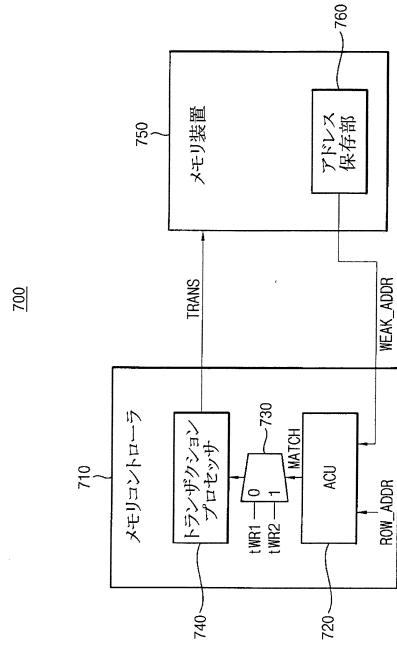

図22は、本発明の一実施形態に係る図21の制御方法を遂行するためのメモリシステムを示すブロック図である。

図22を参照すると、メモリシステム700は、メモリコントローラ710及び揮発性メモリ装置750を含む。

メモリコントローラ 710 は、アドレス比較部 (ACU) 720、マルチプレクサ 730、及びトランザクションプロセッサ 740 を含む。

揮発性メモリ装置 750 は、アドレス情報、即ち、ウィークセルロウアドレス W E A K \_ A D D R を保存するアドレス保存部 760 を含む。ウィークセルロウアドレス W E A K \_ A D D R はメモリシステム 700 のパッケージングの前又は後でアドレス保存部 760 に保存することができる。

[ 0 1 2 5 ]

メモリシステム700のパワーアップシーケンスの間にアドレス保存部760に保存されたウィークセルロウアドレスW E A K \_ A D D Rがアドレス比較部720に転送される。

アドレス比較部720は、ウイークセルロウアドレスW E A K \_ A D D Rと揮発性メモリ装置750のメモリセルロウをアクセスするための書き込みロウアドレスR O W \_ A D D Rを比較し、上記比較の結果に基づいて、マッチ信号M A T C Hをマルチプレクサ730に出力する。

[ 0 1 2 6 ]

例えば、ウィークセルロウアドレスW E A K \_ A D D Rが書き込みロウアドレスR O W A D D Rと一致しない場合、マッチ信号M A T C Hは第1ロジックレベルを有する。

マルチプレクサ730は第1ロジックレベルを有するマッチ信号M A T C Hに応答して第1書き込み回復時間 $t_{W R \: 1}$ と第2書き込み回復時間 $t_{W R \: 2}$ のうち、第1書き込み回復時間 $t_{W R \: 1}$ を選択してトランザクションプロセッサ740に出力する。

トランザクションプロセッサ 740 は、第 1 書き込み回復時間  $t_{WR1}$  を受信し、揮発性メモリ装置 750 にコマンド又はトランザクション T R A N S を提供して揮発性メモリ装置 750 のウィークセルロウ以外にノーマルセルロウが第 1 書き込み回復時間  $t_{WR1}$  を利用して動作するように（即ち、第 1 書き込み回復時間  $t_{WR1}$  を利用して書き込むよう）揮発性メモリ装置 750 を制御する。

[ 0 1 2 7 ]

例えば、ウィークセルロウアドレス W E A K \_ A D D R が書き込みロウアドレス R O W A D D R と一致する場合、マッチ信号 M A T C H は第2ロジックレベルを有する。

マルチプレクサ730は第2口ジックレベルを有するマッチ信号M A T C Hに応答して

第1書き込み回復時間 $t_{WR1}$ と第2書き込み回復時間 $t_{WR2}$ のうち、第2書き込み回復時間 $t_{WR2}$ を選択してトランザクションプロセッサ740に出力する。

トランザクションプロセッサ740は、第2書き込み回復時間 $t_{WR2}$ を受信し、揮発性メモリ装置750にコマンド又はトランザクションTRANSを提供して揮発性メモリ装置750のウィークセルロウが第2書き込み回復時間 $t_{WR2}$ を有するように揮発性メモリ装置750を制御する。

#### 【0128】

ここで、第1書き込み回復時間 $t_{WR1}$ は、揮発性メモリ装置750の標準で定義されたメモリセルロウの書き込み回復時間であり、例えば、DDR3 SDRAMにおいては、15nsecである。10

第2書き込み回復時間 $t_{WR2}$ は、第1書き込み回復時間 $t_{WR1}$ の2倍であってもよい。

本実施形態では、実際の書き込み回復時間はトランザクションプロセッサ740又は揮発性メモリ装置750に提供される必要はなく、それぞれ異なる書き込み回復時間に対応するモードインジケータ及び/又はコマンドを使用することができる。

#### 【0129】

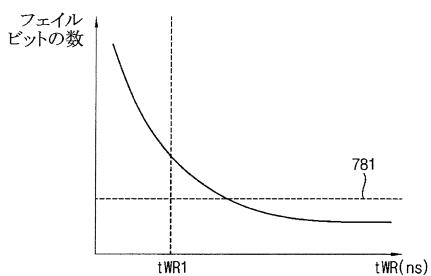

図23は、揮発性メモリ装置で、書き込み回復時間とフェイルビットの数の関係を示すグラフである。

図23を参照すると、書き込み回復時間 $t_{WR}$ が増加するほどフェイルビットの数が減少することがわかる。20

図23において、符号781は、回復可能なフェイルビットの数を表す。

#### 【0130】

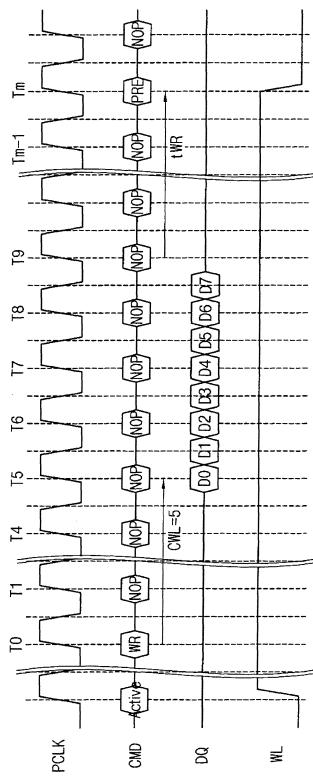

図24は、揮発性メモリ装置でメモリセルにより書き込み特性が悪くなることを説明するためのタイミング図である。

図24は、DDR3 SDRAMにおいて、クロック書き込みレイテンシ(clock write latency)CWLが「5」クロックであり、バースト(burst)の長さが「8」である場合を説明する。

#### 【0131】

図24を参照すると、アクティブコマンドACTによってワードラインWLが活性化され、クロックT0で書き込みコマンドWRが入力され、クロックT1~T4が経過した後にクロックT5~T8でデータD0~D7が書き込まれ、クロックT9~(Tm-1)が経過した後、クロックTmでプリチャージコマンドPREが入力されてワードラインWLが非活性化されることがわかる。30

図24において、最後のデータD7が書き込まれた後、プリチャージコマンドPREが入力される時までの時間T9~Tmが書き込み回復時間 $t_{WR}$ に該当する。

図24に示すように、他のデータに比べて最後のデータD7は受信された後、直ちにワードラインWLが非活性化されるので該当口ウがウィークセルロウの場合にデータD0~D7は、セルに書き込みができる時間が充分でないこともある。従って、書き込み特性とデータ保存が良くなかったり、又は、エラーが発生することがある。

このように書き込み特性が良くなかったり、又は、データ保存能力が良くないセルをウィークセルといい、ウィークセルを少なくとも一つ以上含むメモリセルロウをウィークセルロウという。40

#### 【0132】

図25は、図22のメモリシステムで書き込み回復時間が二元化されることを示す図である。

図25を参照すると、ノーマルセルロウはアクティブコマンドACTが入力されてワードラインが活性化された後、書き込み命令WRが入力されて書き込み動作が遂行された後から第1書き込み回復時間 $t_{WR1}$ 後に、プリチャージコマンドPREが入力されてワードラインが非活性化され、ウィークセルロウはアクティブコマンドACTが入力されてワードラインが活性化された後に書き込み命令WRが入力されて、書き込み動作が遂行され50

た後から第2書き込み回復時間  $t_{WR2}$  の後にプリチャージコマンド P R E が入力され、ワードラインが非活性化されることによって、書き込み特性が良くないウィークセルを少なくとも一つ以上含むウィークセルロウの書き込み回復時間とノーマルセルロウの書き込み回復時間を別にすることが分かる。

#### 【0133】

第2書き込み回復時間  $t_{WR2}$  は、メモリコントローラから転送される他のコマンドの使用に基づいて第1書き込み回復時間  $t_{WR1}$  と差別化される。

他の実施形態においては、揮発性メモリ装置は受信されたコマンドがウィークセルロウに対して書き込み動作を遂行するというコマンドに該当することを認識し、ウィークセルロウに対する第2書き込み回復時間  $t_{WR2}$  を増加させる。10

揮発性メモリ装置は、受信されたコマンドが他の実施形態において記述された方式でウィークセルロウに書き込み動作を遂行するというコマンドであることを認識し得る。

#### 【0134】

上述した図21～図25を参照した実施形態においては、書き込みロウアドレスとウィークセルロウアドレスを比較した結果に基づいてノーマルセルロウとウィークセルロウの書き込み回復時間を別にしてウィークセルロウの書き込み特性を改善させることができる。。20

#### 【0135】

図26は、本発明の実施形態に係る揮発性メモリ装置を含むメモリモジュールを示す図である。20

図26を参照すると、メモリモジュール800は、複数の揮発性メモリ装置200を含む。

実施形態により、メモリモジュール800は、UDIMM(Unbuffered Dual In-line Memory Module)、RDIMM(Registered Dual In-line Memory Module)、FBDIMM(Fully Buffered Dual In-line Memory Module)、LRDIMM(Load Reduced Dual In-line Memory Module)、又は、他のメモリモジュールであってもよい。

#### 【0136】

メモリモジュール800は、メモリコントローラから複数の信号線を介してコマンド、アドレス、及びデータを受信し、コマンド、アドレス、及びデータをバッファリングして揮発性メモリ装置200に提供するバッファ810をさらに含むことができる。30

#### 【0137】

バッファ810と揮発性メモリ装置200との間のデータ転送線は、ポイント・ツー・ポイント方式で接続される。

また、バッファ810と揮発性メモリ装置200との間のコマンド/アドレス転送線は、マルチドロップ方式、デイジーチェーン方式、又は、フライ・バイ・デイジーチェーン方式で接続することができる。

バッファ810が、コマンド、アドレス、及びデータを全部バッファリングするので、メモリコントローラは、バッファ810のロードのみを駆動することによってメモリモジュール800とインターフェースすることができる。これにより、メモリモジュール800は、より多くの数のメモリ装置及びメモリランクを含むことができ、メモリシステムはより多くの数のメモリモジュールを含むことができる。40

#### 【0138】

揮発性メモリ装置200は、ウィークセルロウアドレスをリフレッシュロウアドレスと比較して、その比較結果により、ウィークセルロウのリフレッシュを制御することによってウィークセルロウのポーズタイム増加による書き込み特性が悪くなることを防止することができる。

#### 【0139】

図27は、本発明の実施形態に係る揮発性メモリ装置をモバイルシステムに応用した例50

を示すブロック図である。

#### 【0140】

図27を参照すると、モバイルシステム900は、アプリケーションプロセッサ(AP)910、通信部920、使用者インターフェース930、不揮発性メモリ装置(NVM)940、揮発性メモリ装置(VM)950、及びパワーサプライ960を含む。

実施形態により、モバイルシステム900は、携帯電話(Mobile Phone)、スマートフォン(Smart Phone)、PDA(Personal Digital Assistant)、PMP(Portable Multimedia Player)、デジタルカメラ(Digital Camera)、音楽再生機(Music Player)、携帯用ゲームコンソール(Portable Game Console)、ナビゲーション(Navigation)システムなどの任意のモバイルシステムであることができる。

10

#### 【0141】

アプリケーションプロセッサ910はインターネットブラウザ、ゲーム、動画などを提供するアプリケーションを遂行する。

実施形態により、アプリケーションプロセッサ910は、一つのプロセッサコア(Single Core)を含むか或いは複数のプロセッサコア(Multi-Core)を含むことができる。例えば、アプリケーションプロセッサ910はデュアルコア(Dual-Core)、クアッドコア(Quad-Core)、ヘキサコア(Hexa-Core)などのマルチコア(Multi-Core)を含むことができる。また、実施形態により、アプリケーションプロセッサ910は、内部又は外部に位置したキャッシュメモリ(Cache Memory)をさらに含むことができる。

20

#### 【0142】

通信部920は、外部装置と無線通信又は有線通信を遂行する。

例えば、通信部920は、イーサネット(登録商標)(Ethernet(登録商標))通信、NFC(Near Field Communication)、RFID(Radio Frequency Identification)通信、移動通信(Mobile Telecommunication)、メモリカード通信、USB(Universal Serial Bus)通信などを遂行できる。例えば、通信部1420は、ベースバンドチップセット(Baseband Chipset)を含むことができる、GSM(登録商標)、GPRS、WCDMA(登録商標)、HSxPAなどの通信を支援することができる。

30

#### 【0143】

揮発性メモリ装置950は、アプリケーションプロセッサ910により処理されるデータを保存したり、又は、ワーキングメモリ(Working Memory)として作動する。

例えば、揮発性メモリ装置950は、DDR SDRAM、LPDDR SDRAM、GDDR SDRAM、RDRAMなどの動的ランダムアクセスメモリ、又は、リフレッシュ動作が必要な任意の揮発性メモリ装置であってもよい。揮発性メモリ装置950はウィークセルロウアドレスをリフレッシュロウアドレスと比較して、その比較結果により、ウィークセルロウアドレスのリフレッシュを制御することによってウィークセルロウのポーズタイム増加による書き込み特性が悪くなることを防止できる。

40

#### 【0144】

不揮発性メモリ装置950は、モバイルシステム900をブーティングするためのブートイメージを保存することができる。例えば、不揮発性メモリ装置950は、EEPROM(Electrically Erasable Programmable Read-Only Memory)、フラッシュメモリ(Flash Memory)、PRAM(Phase Change Random Access Memory)、RRAM(登録商標)(Resistance Random Access Memory)、NFGM(Nano Floating Gate Memory)、PoRAM(

50

Polymer Random Access Memory)、MRAM(Magnetic Random Access Memory)、FRAM(登録商標)(Ferroelectric Random Access Memory)、又は、これと類似のメモリで具現できる。

#### 【0145】

ユーザインターフェース930は、キーパッド、タッチスクリーンのような一つ以上の入力装置、及び／又は、スピーカー、ディスプレイ装置のような一つ以上の出力装置を含む。

パワーサプライ960は、モバイルシステム900の動作電圧を供給する。

また、実施形態により、モバイルシステム900は、CIS(Camera Image Processor)をさらに包含でき、メモリカード(Memory Card)、SSD(Solid State Drive)、HDD(Hard Disk Drive)、CD-ROMなどのような保存装置をさらに含むことができる。

10

#### 【0146】

モバイルシステム900、または、モバイルシステム900の構成要素は、多様な形態のパッケージを利用して実装されるが、例えば、POP(Package on Package)、BGAs(Ball grid arrays)、CSPs(Chip scale packages)、PLCC(Plastic Leaded Chip Carrier)、PDIP(Plastic Dual In-Line Package)、Die in Waffle Pack、Die in Wafer Form 20

、COB(Chip On Board)、CERDIP(Ceramic Dual In-Line Package)、MQFP(Plastic Metric Quad Flat Pack)、TQFP(Thin Quad Flat-Pack)、SOIC(Small Outline Integrated Circuit)、SSOP(Shrink Small Outline Package)、TSOP(Thin Small Outline Package)、TQFP(Thin Quad Flat-Pack)、SIP(System In Package)、MCP(Multi Chip Package)、WFP(Wafer-level Fabricated Package)、WSP(Wafer-Level Processed Stack Package)などのようなパッケージを利用して実装することができる。

30

#### 【0147】

図28は、本発明の実施形態に係る揮発性メモリ装置をコンピューティングシステムに応用した例を示すブロック図である。

図28を参照すると、コンピューティングシステム1100は、プロセッサ1110、入出力ハブ1120、入出力コントローラハブ1130、少なくとも一つのメモリモジュール1140、及びグラフィックカード1150を含む。

#### 【0148】

実施形態により、コンピューティングシステム1100は、PC(Personal Computer)、サーバーコンピュータ(Server Computer)、ワークステーション(Workstation)、ノートパソコン(Laptop)、携帯電話(Mobile Phone)、スマートフォン(Smart Phone)、PDA(personal digital assistant)、PMP(portable multimedia player)、デジタルカメラ(Digital Camera)、デジタルTV(Digital Television)、STB(Set-Top Box)、音楽再生機(Music Player)、携帯用ゲームコンソール(portable game console)、ナビゲーション(Navigation)システムなどの任意のコンピューティングシステムであってもよい。

40

#### 【0149】

プロセッサ1110は、特定計算又はタスクのような多様なコンピューティング機能を

遂行する。例えば、プロセッサ 1110 は、マイクロプロセッサー又は CPU ( C e n t r a l P r o c e s s i n g U n i t ) であってもよい。

実施形態により、プロセッサ 1110 は一つのプロセッサコア ( S i n g l e C o r e ) を含むか、又は、複数のプロセッサコア ( M u l t i - C o r e ) を含むことができる。例えば、プロセッサ 1510 はデュアルコア ( D u a l - C o r e ) 、クアッドコア ( Q u a d - C o r e ) 、ヘキサコア ( H e x a - C o r e ) などのマルチコア ( M u l t i - C o r e ) を含むことができる。

また、図 28 には一つのプロセッサ 1110 を含むコンピューティングシステム 1100 を示しているが、実施形態により、コンピューティングシステム 1100 は、複数のプロセッサを含むことができる。また、実施形態により、プロセッサ 1110 は、内部又は外部に位置したキャッシュメモリ ( C a c h e M e m o r y ) をさらに含むことができる。

10

#### 【 0150 】

プロセッサ 1110 は、メモリモジュール 1140 の動作を制御するメモリコントローラ 1111 を含む。

プロセッサ 1110 に含まれたメモリコントローラ 1111 は、IMC ( I n t e g r a t e d M e m o r y C o n t r o l l e r ) と呼ばれる。

メモリコントローラ 1111 は上述した一つ以上の実施形態の構造を含むか、又は、制御方法を遂行できる。メモリコントローラ 1111 とメモリモジュール 1140 との間のメモリインターフェースは、複数の信号線を含む一つのチャネルで具現されるか、又は、複数のチャネルで具現されることができる。また、各チャネルには一つ以上のメモリモジュール 1140 が接続されることができる。実施形態により、メモリコントローラ 1111 は、入出力ハブ 1120 内に位置することができる。メモリコントローラ 1111 を含む入出力ハブ 1120 は、MCH ( M e m o r y C o n t r o l l e r H u b ) と呼ばれる。

20

#### 【 0151 】

メモリモジュール 1140 は、メモリコントローラ 1111 から提供されたデータを保存する複数の揮発性メモリ装置を含む。

揮発性メモリ装置は、リフレッシュ動作の遂行途中でメモリコントローラから書き込みコマンドが入力される場合、リフレッシュロウアドレスとウィークセルロウアドレスとを比較し、比較結果により、ウィークセルロウアドレスのリフレッシュを制御することによってウィークセルロウのポーズタイム増加による書き込み特性が悪くなることを防止することができる。

30

代案的な、及び／または、追加的な実施形態において、メモリコントローラは、個別的なウィークセルロウベイス ( b a s i s ) よりは、メモリセルグループをウィークセルロウグループで処理することができる。例えば、メモリモジュールのうちいずれか一つのメモリチップのうちいずれか一つのバンクがウィークセルバンクとして考慮され、ウィークセルバンクは他のバンクよりさらに短いリフレッシュサイクル、及び／又は、さらに長い書き込み時間（書き込み回復時間）を有する。

#### 【 0152 】

入出力ハブ 1120 は、グラフィックカード 1150 のような装置とプロセッサ 1110 との間のデータ転送を管理する。

40

入出力ハブ 1120 は、多様な方式のインターフェースを介してプロセッサ 1110 に接続され得る。例えば、入出力ハブ 1120 とプロセッサ 1110 は、FSB ( F r o n t S i d e B u s ) 、システムバス ( S y s t e m B u s ) 、ハイパートランSPORT ( H y p e r T r a n s p o r t ) 、LDT ( L i g h t n i n g D a t a T r a n s p o r t ) 、QPI ( Q u i c k P a t h I n t e r c o n n e c t ) 、CSI ( C o m m o n S y s t e m I n t e r f a c e ) などの多様な標準インターフェースで接続され得る。図 28 には一つの入出力ハブ 1120 を含むコンピューティングシステム 1100 を示したが、実施形態によって、コンピューティングシステム 1100 は

50

複数の入出力ハブを含むことができる。

#### 【0153】

入出力ハブ1120は、装置との多様なインターフェースを提供することができる。例えば、入出力ハブ1120は、AGP(Accelerated Graphics Port)インターフェース、PCIe(Peripheral Component Interface-Express)、CSA(Communications Streaming Architecture)インターフェースなどを提供することができる。

#### 【0154】

グラフィックカード1150は、AGP又はPCIeを介して入出力ハブ1120と接続される。10

グラフィックカード1150は、画像を表示するためのディスプレイ装置(図示せず)を制御する。グラフィックカード1150は、イメージデータ処理のための内部プロセッサ及び内部半導体メモリ装置を含むことができる。実施形態により、入出力ハブ1120は、入出力ハブ1120の外部に位置したグラフィックカード1150とともに、又は、グラフィックカード1150の代わりに入出力ハブ1120の内部にグラフィック装置を含むことができる。

入出力ハブ1120に含まれたグラフィック装置は、集積グラフィック(Integrated Graphics)と呼ばれる。また、メモリコントローラ及びグラフィック装置を含む入出力ハブ1120は、GMCH(Graphics and Memory Controller Hub)と呼ばれる。20

#### 【0155】

入出力コントローラハブ1130は、多様なシステムインターフェースが効率的に動作するようにデータバッファリング及びインターフェース仲裁(interface arbitration)を遂行できる。入出力コントローラハブ1130は、内部バスを介して入出力ハブ1120と接続される。例えば、入出力ハブ1120と入出力コントローラハブ1130は、DMI(Direct Media Interface)、ハブインターフェース、ESI(Enterprise Southbridge Interface)、PCIeなどを介して接続される。30

#### 【0156】

入出力コントローラハブ1130は、周辺装置との多様なインターフェースを提供することができる。例えば、入出力コントローラハブ1130は、USB(Universal Serial Bus)ポート、SATA(Serial Advanced Technology Attachment)ポート、GPIO(General Purpose Input/Output)、LPC(Low Pin Count)バス、SPI(Serial Peripheral Interface)、PCI、PCIeなどを提供することができる。30

#### 【0157】

実施形態により、プロセッサ1110、入出力ハブ1120、及び入出力コントローラハブ1130は、それぞれ分離したチップセット又は集積回路で具現されたり、或いは、プロセッサ1110、入出力ハブ1120、又は入出力コントローラハブ1130のうち、2つ以上の構成要素が一つのチップセットで具現することができる。40

#### 【0158】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【産業上の利用可能性】

#### 【0159】

本発明は、書き込み特性の改善が必要な任意の揮発性メモリ装置及びそれを含むシステムに好適に使用される。

本発明の概念はまた、不揮発性メモリ装置にも適用できる。例えば、不揮発性メモリ装50

置において読み出しディスタンスエラー (disturbance errors) は、メモリの特定ロウで頻繁に発生する可能性があり、このようなロウは、より速いコピー・バックサイクルタイム (copy-back cycle times) を必要とする。

このようなより速いコピー・バックサイクルタイムは、ここに記載した実施形態の、修正済みのリフレッシュサイクルタイムと類似方式で遂行されるか、或いは具現することができる。

また、不揮発性メモリ装置もさらに長い書き込み時間を必要とするメモリセルロウを含むことができ、ノーマルセルロウよりもさらに長い書き込み回復時間の提供を受けることができるが、このような長い書き込み回復時間は、ここに記載した実施形態の、修正済みの書き込み回復時間と類似方式で遂行されるか、或いは具現することができる。

10

#### 【符号の説明】

##### 【0160】

|                         |                    |    |

|-------------------------|--------------------|----|

| 200                     | 揮発性メモリ装置           |    |

| 210                     | 制御ロジック             |    |

| 220                     | アドレスレジスタ           |    |

| 225                     | アドレス保存部            |    |

| 230                     | バンク制御ロジック          |    |

| 240                     | ロウアドレスマルチプレクサ      |    |

| 250                     | カラムアドレスラッチ         | 20 |

| 260 a、260 b、260 c、260 d | (第1～第4) バンクロウデコーダ  |    |

| 270 a、270 b、270 c、270 d | (第1～第4) バンクカラムデコーダ |    |

| 280 a、280 b、280 c、280 d | (第1～第4) バンクメモリアレイ  |    |

| 290                     | 入出力ゲート回路           |    |

| 295                     | データ入出力バッファ         |    |

| 300                     | アドレス比較部            |    |

| 400                     | リフレッシュ制御回路         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

【図25】

【図26】

【図27】

【図28】

---

フロントページの続き

(72)発明者 孫 鍾 弼

大韓民国京畿道城南市盆唐区亭子洞ハンソルマウル青丘アパートメント102棟603号

(72)発明者 金 秀 娥

大韓民国京畿道城南市盆唐区書ヒヨン洞示範団地現代アパートメント416棟601号

(72)発明者 朴 哲 佑

大韓民国京畿道龍仁市器興区靈徳洞興徳マウル慶南アヌスピルアパートメント1101棟101号

(72)発明者 黄 泓 善

大韓民国京畿道水原市靈通区網浦洞双龍アパートメント106棟303号

審査官 堀田 和義

(56)参考文献 米国特許出願公開第2010/0271891(US, A1)

特表2007-510254(JP, A)

米国特許出願公開第2005/0099868(US, A1)

特開2012-248265(JP, A)

米国特許出願公開第2012/0300568(US, A1)

米国特許出願公開第2013/0159617(US, A1)

米国特許出願公開第2013/0279284(US, A1)

米国特許出願公開第2014/0085999(US, A1)

米国特許出願公開第2014/0169114(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 406

G 06 F 12 / 00