(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-92549

(P2008-92549A)

(43) 公開日 平成20年4月17日(2008.4.17)

| (51) Int.Cl.                 | F 1        |   | テーマコード (参考) |

|------------------------------|------------|---|-------------|

| <b>H03K 5/00</b> (2006.01)   | H03K 5/00  | H | 5 J 0 4 3   |

| <b>H03K 3/03</b> (2006.01)   | H03K 3/03  |   | 5 K 0 2 2   |

| <b>H03K 3/0231</b> (2006.01) | H03K 3/023 | A | 5 K 0 2 9   |

| <b>H04L 25/49</b> (2006.01)  | H04L 25/49 | J |             |

| <b>H04J 13/00</b> (2006.01)  | H04J 13/00 | Z |             |

審査請求 未請求 請求項の数 17 O L (全 24 頁)

(21) 出願番号 特願2007-170080 (P2007-170080)

(22) 出願日 平成19年6月28日 (2007. 6. 28)

(31) 優先権主張番号 特願2006-242418 (P2006-242418)

(32) 優先日 平成18年9月7日 (2006. 9. 7)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 飯田 泉

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム (参考) 5J043 AA03 EE00 FF03 GG02 GG08

LL01 MM00

5K022 EE01 EE14 EE21

5K029 AA11 EE11 GG03

(54) 【発明の名称】バースト制御パルス発生回路、バースト制御パルス発生回路を備えたデジタル変調回路及び電子機器

## (57) 【要約】

【課題】低消費電力で動作するバースト制御パルス発生回路。

【解決手段】通信に用いるパルス信号を発生するバースト制御パルス発生回路100であって、バースト制御パルス発生回路100は、通信のオン／オフを制御するバースト信号Burstに基づき周期信号を発振するタイミング発生回路200と、タイミング発生回路200から出力される周期信号に基づきパルス信号Pulseを生成するパルス発生論理回路300と、を有し、バースト信号Burstがオン状態のとき1回以上のパルス信号Pulseを発生し、バースト信号Burstがオフ状態のときパルス信号Pulseの発生を停止する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

通信に用いるパルス信号を発生するバースト制御パルス発生回路であって、

前記バースト制御パルス発生回路は、

前記通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振

回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路

と、

前記複数のタイミング信号に基づき前記パルス信号を生成するパルス発生論理回路と、

を有し、

前記バースト信号がオン状態のとき 1 回以上の前記パルス信号を発生し、前記バースト

信号がオフ状態のとき前記パルス信号の発生を停止する、

ことを特徴とするバースト制御パルス発生回路。 10

**【請求項 2】**

請求項 1 に記載のバースト制御パルス発生回路において、

前記リング発振回路が発振する前記周期信号の発振周期は、前記パルス信号のパルス幅

よりも長い、

ことを特徴とするバースト制御パルス発生回路。

**【請求項 3】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路と前記タイミング発生回路とは、各々を構成する素子の少なくとも

1 個以上を共有している、

ことを特徴とするバースト制御パルス発生回路。 20

**【請求項 4】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路は、前記周期信号の発振周期を制御可能な論理回路を含んでいる、

ことを特徴とするバースト制御パルス発生回路。

**【請求項 5】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記タイミング発生回路は、前記タイミング信号を制御可能な論理回路を含んでいる、

ことを特徴とするバースト制御パルス発生回路。 30

**【請求項 6】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路は、2 入力論理回路と、前記 2 入力論理回路の出力端子に直列に接

続された n 個 (n は 2 以上の自然数) の NOT 回路と、を含み、n 個目の前記 NOT 回路

の出力端子は前記 2 入力論理回路の一方の入力端子に接続され、前記 2 入力論理回路の他

方の入力端子に前記バースト信号が入力され、

前記タイミング発生回路は、前記リング発振回路と、n 個目の前記 NOT 回路の出力端

子に直列に接続された m 個 (m は n 以下の自然数) の前記 NOT 回路と、を含む、

ことを特徴とするバースト制御パルス発生回路。

**【請求項 7】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路は、2 入力論理回路と、前記 2 入力論理回路の出力端子に直列に接

続された n 個 (n は 2 以上の自然数) の NOT 回路と、を含み、

前記タイミング発生回路は、前記リング発振回路と、n 個目の前記 NOT 回路の出力端

子に直列に接続された  $2 \times m$  個 (m は  $n \div 2$  の自然数) の前記 NOT 回路と、を含み

、

前記 2 入力論理回路の一方の入力端子には、 $n + (2 \times i)$  個目 (i は 0 ~ m の整

数) の前記 NOT 回路の出力端子が接続されるように切り換える切換回路が接続され、前

記 2 入力論理回路の他方の入力端子には前記バースト信号が入力されている、

ことを特徴とするバースト制御パルス発生回路。 40

10

20

30

40

50

**【請求項 8】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）のNOT回路と、を含み、n個目の前記NOT回路の出力端子は前記2入力論理回路の一方の入力端子に接続され、前記2入力論理回路の他方の入力端子に前記バースト信号が入力され、

前記タイミング発生回路は、前記リング発振回路と、前記2入力論理回路の出力端子に直列に接続されたn+m個（mはn以下の自然数）の遅延制御信号により遅延時間を制御可能な遅延制御NOT回路と、を含む、

ことを特徴とするバースト制御パルス発生回路。

10

**【請求項 9】**

請求項 2 に記載のバースト制御パルス発生回路において、

前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）の遅延制御信号により遅延時間を制御可能な遅延制御NOT回路と、遅延回路と、を含み、n個目の前記遅延制御NOT回路の出力端子は前記遅延回路を介して前記2入力論理回路の一方の入力端子に接続され、前記2入力論理回路の他方の入力端子に前記バースト信号が入力され、

前記タイミング発生回路は、前記リング発振回路を含む、

ことを特徴とするバースト制御パルス発生回路。

20

**【請求項 10】**

請求項 2 に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をPPM (Pulse Position Modulation) 変調して出力することを特徴とするデジタル変調回路。

**【請求項 11】**

請求項 2 に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号の出力を切断する切換回路と、を有し、入力されたパラレル信号をOOK (On-Off Keying) 変調して出力することを特徴とするデジタル変調回路。

30

**【請求項 12】**

請求項 2 に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号をNOT回路を介して出力する切換回路と、を有し、入力されたパラレル信号をBPM (Bi-Phase Modulation) 変調して出力することを特徴とするデジタル変調回路。

40

**【請求項 13】**

請求項 2 に記載のバースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記第1のバースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記第2のバースト制御パルス発生回路が発生する前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をFSK (Frequency Shift Keying) 変調して出力することを特徴とするデジタル変調回路。

**【請求項 14】**

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路

50

を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、

パラレル／シリアル変換回路と、

前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号を出力する切換回路と、

10

を有し、入力されたパラレル信号をPPM(Pulse Position Modulation)変調して出力するデジタル変調回路を有する送信装置と、

前記バースト制御パルス発生回路を有する受信装置と、

から構成されることを特徴とする電子機器。

#### 【請求項15】

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、

20

パラレル／シリアル変換回路と、

前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号をNOT回路を介して出力する切換回路と、

を有し、入力されたパラレル信号をBPM(Bi-Phase Modulation)変調して出力するデジタル変調回路を有する送信装置と、

30

前記バースト制御パルス発生回路を有する受信装置と、

から構成されることを特徴とする電子機器。

#### 【請求項16】

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、

40

パラレル／シリアル変換回路と、

前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号の出力を切断する切換回路と、

を有し、入力されたパラレル信号をOOK(On-Off Keying)変調して出力するデジタル変調回路を有する送信装置と、

受信装置と、

から構成されることを特徴とする電子機器。

#### 【請求項17】

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路

50

を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路と、

パラレル／シリアル変換回路と、

前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記第1のバースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記第2のバースト制御パルス発生回路が発生する前記パルス信号を出力する切換回路と、

を有し、入力されたパラレル信号をF S K (Frequency Shift Keying)変調して出力するデジタル変調回路を有する送信装置と、

前記バースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路とを有する受信装置と、

から構成されることを特徴とする電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、通信に用いるパルスを発生するバースト制御パルス発生回路、バースト制御パルス発生回路を備えたデジタル変調回路及び電子機器に関する。

#### 【背景技術】

#### 【0002】

U W B (Ultra Wide Band)通信は非常に広い周波数帯域を利用して高速大容量のデータ通信を行う通信方式である。広帯域の信号を利用する通信方式には従来のスペクトル拡散による方法や直交周波数分割多重(O F D M)があるが、U W Bは非常に短時間のパルスを利用したさらに広帯域の通信方式であり、インパルスラジオ(I R)方式の通信とも呼ばれている。I R方式では従来の変調によらない時間軸操作のみで変復調が可能であり回路の簡略化や低消費電力化が期待できるとされている。

#### 【0003】

この問題を解決するために、例えば特許文献1には、U W Bパルス通信において受信器の増幅器をO N - O F F制御することで低消費電力を得る方法が記載されている。

#### 【0004】

#### 【特許文献1】特開2005-217899号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

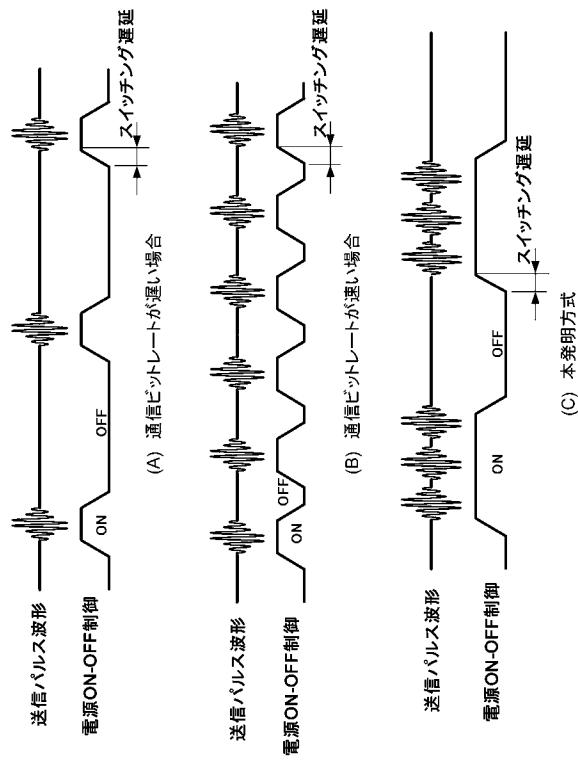

しかしながら、特許文献1では、O N - O F Fスイッチング遅延に関して考慮されていない。図1(A)に示すように通信ビットレートが遅い場合には、O N - O F Fスイッチング遅延の影響は小さいが、図1(B)に示すように通信ビットレートが速い場合には、O N - O F Fスイッチング遅延に起因する余分な消費電力が全体の消費電力の中で大きなウェイトを占めるようになってしまうという課題がある。

#### 【0006】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

#### 【課題を解決するための手段】

#### 【0007】

#### [適用例1]

通信に用いるパルス信号を発生するバースト制御パルス発生回路であって、前記バース

10

20

30

40

50

ト制御パルス発生回路は、前記通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記パルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止する、ことを特徴とするバースト制御パルス発生回路。

#### 【0008】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。 10

#### 【0009】

##### [適用例2]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路が発振する前記周期信号の発振周期は、前記パルス信号のパルス幅よりも長い、ことを特徴とするバースト制御パルス発生回路。

#### 【0010】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0011】

##### [適用例3]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路と前記タイミング発生回路とは、各々を構成する素子の少なくとも1個以上を共有している、ことを特徴とするバースト制御パルス発生回路。

#### 【0012】

この構成によれば、パルス発生回路とリング発振回路とが共有している素子を調整することにより、パルス発生回路の周波数とリング発振回路の周期を同時に調整することができ、個別に調整する場合に比べて正確な調整ができる。また、回路規模を縮小させることもできる。 20

#### 【0013】

##### [適用例4]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路は、前記周期信号の発振周期を制御可能な論理回路を含んでいる、ことを特徴とするバースト制御パルス発生回路。

#### 【0014】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。さらに、遅延時間を制御可能な論理回路によりリング発振回路の周期幅を可変にできるので、マルチパス等の伝播路の影響や、フィルタやアンテナ等の群遅延特性の影響に応じて最適な周期幅に設定できる。 40

#### 【0015】

##### [適用例5]

上記に記載のバースト制御パルス発生回路において、前記タイミング発生回路は、前記タイミング信号を制御可能な論理回路を含んでいる、ことを特徴とするバースト制御パルス発生回路。

#### 【0016】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。さら 50

に、遅延時間を制御可能な論理回路によりリング発振回路の周期幅を可変にできるので、マルチパス等の伝播路の影響や、フィルタやアンテナ等の群遅延特性の影響に応じて最適な周期幅に設定できる。また、リング発振回路の周期幅を固定にしたまま、出力されるパルス信号の変調周波数を遅延時間を制御可能な論理回路により連続的に変えることができる。

#### 【0017】

##### [適用例6]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）のNOT回路と、を含み、n個目の前記NOT回路の出力端子は前記2入力論理回路の一方の入力端子に接続され、前記2入力論理回路の他方の入力端子に前記バースト信号が入力され、前記タイミング発生回路は、前記リング発振回路と、n個目の前記NOT回路の出力端子に直列に接続されたm個（mはn以下の自然数）の前記NOT回路と、を含む、ことを特徴とするバースト制御パルス発生回路。

10

#### 【0018】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0019】

##### [適用例7]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）のNOT回路と、を含み、前記タイミング発生回路は、前記リング発振回路と、n個目の前記NOT回路の出力端子に直列に接続された $2 \times m$ 個（mはm  $\leq n/2$ の自然数）の前記NOT回路と、を含み、前記2入力論理回路の一方の入力端子には、 $n + (2 \times i)$ 個目（iは0  $\leq i < m$ の整数）の前記NOT回路の出力端子が接続されるように切り換える切換回路が接続され、前記2入力論理回路の他方の入力端子には前記バースト信号が入力されている、ことを特徴とするバースト制御パルス発生回路。

20

#### 【0020】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。さらに、切換回路によりリング発振回路の周期幅を可変にできるので、マルチパス等の伝播路の影響や、フィルタやアンテナ等の群遅延特性の影響に応じて最適な周期幅に設定できる。

30

#### 【0021】

##### [適用例8]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）のNOT回路と、を含み、n個目の前記NOT回路の出力端子は前記2入力論理回路の一方の入力端子に接続され、前記2入力論理回路の他方の入力端子に前記バースト信号が入力され、前記タイミング発生回路は、前記リング発振回路と、前記2入力論理回路の出力端子に直列に接続されたn+m個（mはn以下の自然数）の遅延制御信号により遅延時間を制御可能な遅延制御NOT回路と、を含む、ことを特徴とするバースト制御パルス発生回路。

40

#### 【0022】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。さらに、リング発振回路の周期幅を固定にしたまま、出力されるパルス信号の変調周波数を遅

50

延制御信号により連続的に変えることができる。

【0023】

[適用例9]

上記に記載のバースト制御パルス発生回路において、前記リング発振回路は、2入力論理回路と、前記2入力論理回路の出力端子に直列に接続されたn個（nは2以上の自然数）の遅延制御信号により遅延時間を制御可能な遅延制御NOT回路と、遅延回路と、を含み、n個目の前記遅延制御NOT回路の出力端子は前記遅延回路を介して前記2入力論理回路の一方の入力端子に接続され、前記2入力論理回路の他方の入力端子に前記バースト信号が入力され、前記タイミング発生回路は、前記リング発振回路を含む、ことを特徴とするバースト制御パルス発生回路。

10

【0024】

この構成によれば、バースト信号がオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。さらに、出力されるパルス信号間の間隔を一定にしたまま、遅延制御信号によりパルス信号の周期幅を変えることができる。

【0025】

[適用例10]

上記に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をPPM(Pulse Position Modulation)変調して出力することを特徴とするデジタル変調回路。

20

【0026】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をPPM変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

【0027】

[適用例11]

上記に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号の出力を切断する切換回路と、を有し、入力されたパラレル信号をOOK(On-Off Keying)変調して出力することを特徴とするデジタル変調回路。

30

【0028】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をOOK変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

40

【0029】

[適用例12]

上記に記載のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号をNOT回路を介して出力する切換回路と、を有し、入力されたパラレル信号をBPM(Bi-Phase Modulation)変調して出力することを特徴とするデジタル変調回路。

【0030】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をBPM変

50

調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0031】

##### [適用例13]

上記に記載のバースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記第1のバースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記第2のバースト制御パルス発生回路が発生する前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をFSK(Frequency Shift Keying)変調して出力することを特徴とするデジタル変調回路。10

#### 【0032】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をFSK変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0033】

##### [適用例14]

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をPPM(Pulse Position Modulation)変調して出力するデジタル変調回路を有する送信装置と、前記バースト制御パルス発生回路を有する受信装置と、から構成されることを特徴とする電子機器。20

#### 【0034】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をPPM変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0035】

##### [適用例15]

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を遅延回路を介して出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号をNOT回路を介して出力する切換回路と、を有し、入力されたパラレル信号をBPM(Bi-Phase Modulation)変調して出力するデジタル変調回路を有する送信装置と、前記バースト制御パルス発生回路を有する受信装置と、から構成されることを特徴とする電子機器。40

#### 【0036】

10

20

30

40

50

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をBPM変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

#### 【0037】

##### [適用例16]

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記バースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記パルス信号の出力を切断する切換回路と、を有し、入力されたパラレル信号をOK(On-Off Keying)変調して出力するデジタル変調回路を有する送信装置と、受信装置と、から構成されることを特徴とする電子機器。

10

#### 【0038】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をOK変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

20

#### 【0039】

##### [適用例17]

通信のオンとオフを制御するバースト信号に基づき周期信号を発振するリング発振回路を含み、前記周期信号に基づき複数のタイミング信号を出力するタイミング発生回路と、前記複数のタイミング信号に基づき前記通信に用いるパルス信号を生成するパルス発生論理回路と、を有し、前記バースト信号がオン状態のとき1回以上の前記パルス信号を発生し、前記バースト信号がオフ状態のとき前記パルス信号の発生を停止し、前記リング発振回路が発振する前記周期信号の発振周期が前記パルス信号のパルス幅よりも長い、バースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路と、パラレル／シリアル変換回路と、前記パラレル／シリアル変換回路が出力するシリアル信号が第1の電位のとき前記第1のバースト制御パルス発生回路が発生する前記パルス信号を出力し、前記シリアル信号が前記第1の電位と異なる第2の電位のとき前記第2のバースト制御パルス発生回路が発生する前記パルス信号を出力する切換回路と、を有し、入力されたパラレル信号をFSK(Frequency Shift Keying)変調して出力するデジタル変調回路を有する送信装置と、前記バースト制御パルス発生回路である第1のバースト制御パルス発生回路及び第2のバースト制御パルス発生回路とを有する受信装置と、から構成されることを特徴とする電子機器。

30

#### 【0040】

この構成によれば、バースト信号がオン状態のとき入力されたパラレル信号をFSK変調して出力し、バースト信号がオフ状態のとき停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。

40

#### 【発明を実施するための最良の形態】

#### 【0041】

以下、バースト制御パルス発生回路の実施形態について図面に従って説明する。

#### 【0042】

##### (第1実施形態)

##### <バースト制御パルス発生回路の構成>

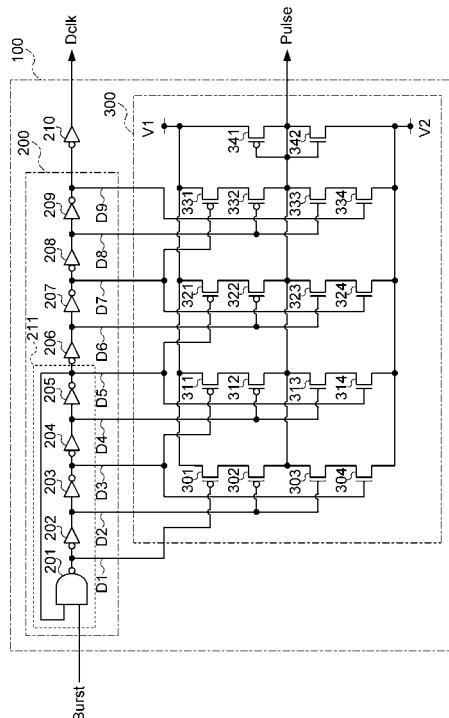

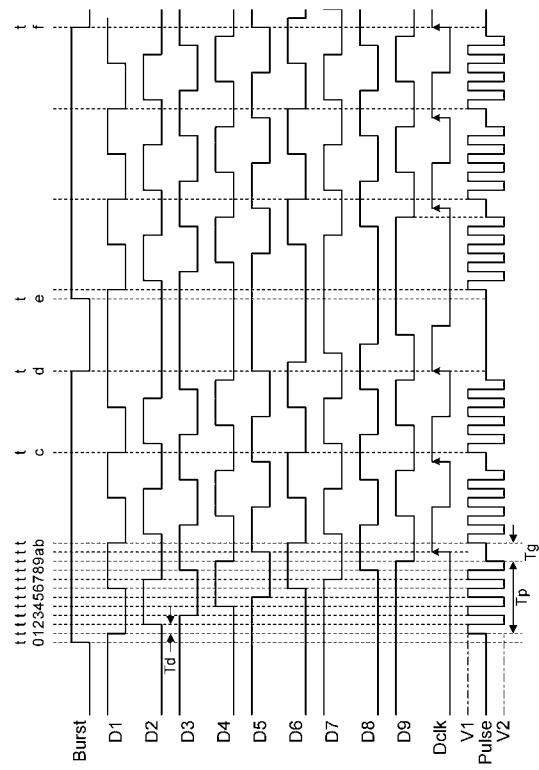

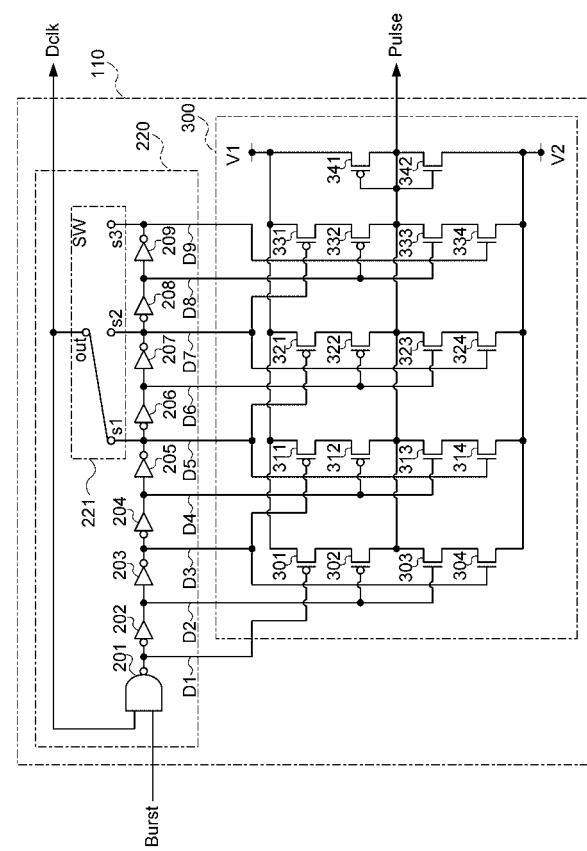

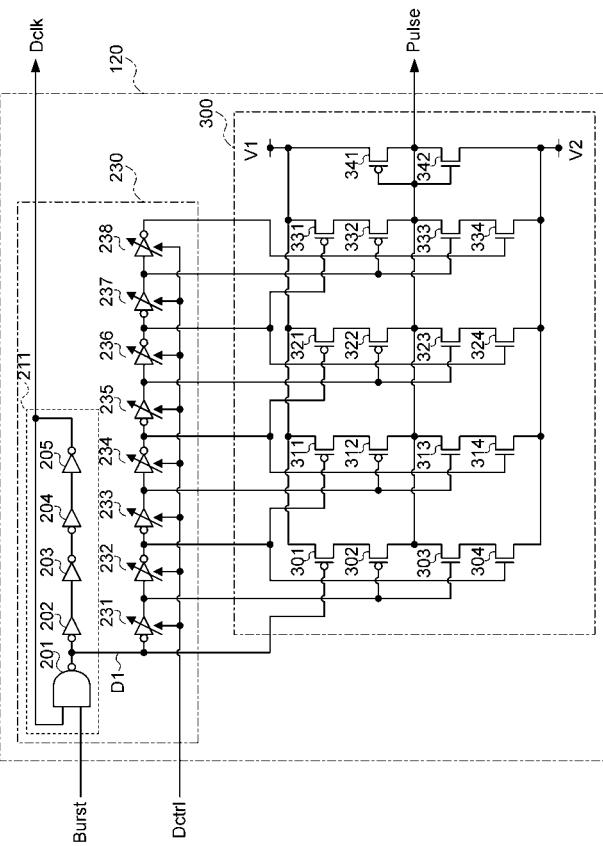

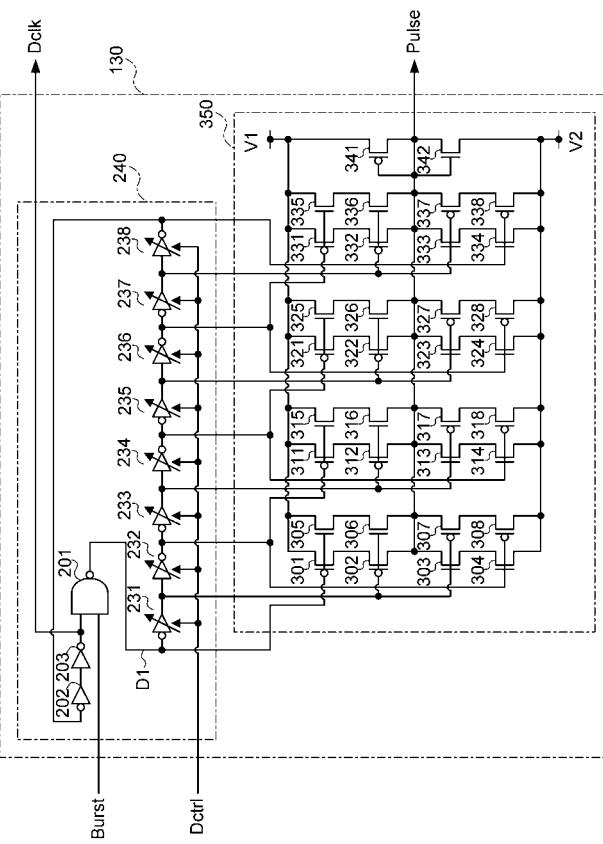

先ず、第1実施形態に係るバースト制御パルス発生回路の構成について、図2及び図3を参照して説明する。図2は、第1実施形態に係るバースト制御パルス発生回路の構成を

50

示す回路図である。図3は、第1実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャートである。

【0043】

図2に示すように、バースト制御パルス発生回路100は、タイミング発生回路200とパルス発生論理回路300とから構成されている。なお、本第1実施形態では、 $n = 4$ かつ $m = 4$ の場合について説明するが、この数に限定するものではない。

【0044】

タイミング発生回路200は、2入力論理回路である2入力NAND201と、NOT回路であるインバータ202～209とから構成されている。2入力NAND201の出力端子には、4個( $n = 4$ )のインバータ202～205が直列に接続され、4個目のインバータ205の出力端子と2入力NAND201の一方の入力端子が接続され、2入力NAND201の他方の入力端子には、バースト信号Burstが入力されている。タイミング発生回路200に含まれる2入力NAND201とインバータ202～205とが、リング発振回路211を構成している。

10

【0045】

さらに4個目のインバータ205の出力端子には、4個( $m = 4$ )のインバータ206～209が直列に接続されている。また、インバータ209の出力端子には、インバータ210が接続され、インバータ210の出力端子からクロック信号Clockが出力される。

20

【0046】

ここで、2入力NAND201の出力信号をD1、インバータ202～209の出力信号をそれぞれD2～D9、とする。

【0047】

次に、パルス発生論理回路300は、高電位側の電位V1と、低電位側の電位V2の間に、Pchトランジスタ301, 302と、Nchトランジスタ303, 304が直列に接続され、Pchトランジスタ301のゲートには出力信号D1が、Pchトランジスタ302のゲートとNchトランジスタ303のゲートには出力信号D2が、Nchトランジスタ304のゲートには出力信号D3が、それぞれ入力され、Pchトランジスタ302のドレインとNchトランジスタ303のドレインの接続点からは、パルス信号Pulseが出力される。

30

【0048】

また、パルス発生論理回路300は、高電位側の電位V1と、低電位側の電位V2の間に、Pchトランジスタ311, 312と、Nchトランジスタ313, 314が直列に接続され、Pchトランジスタ311のゲートには出力信号D3が、Pchトランジスタ312のゲートとNchトランジスタ313のゲートには出力信号D4が、Nchトランジスタ314のゲートには出力信号D5が、それぞれ入力され、Pchトランジスタ312のドレインとNchトランジスタ313のドレインの接続点からは、パルス信号Pulseが出力される。

【0049】

また、パルス発生論理回路300は、高電位側の電位V1と、低電位側の電位V2の間に、Pchトランジスタ321, 322と、Nchトランジスタ323, 324が直列に接続され、Pchトランジスタ321のゲートには出力信号D5が、Pchトランジスタ322のゲートとNchトランジスタ323のゲートには出力信号D6が、Nchトランジスタ324のゲートには出力信号D7が、それぞれ入力され、Pchトランジスタ322のドレインとNchトランジスタ323のドレインの接続点からは、パルス信号Pulseが出力される。

40

【0050】

また、パルス発生論理回路300は、高電位側の電位V1と、低電位側の電位V2の間に、Pchトランジスタ331, 332と、Nchトランジスタ333, 334が直列に接続され、Pchトランジスタ331のゲートには出力信号D7が、Pchトランジスタ

10

20

30

40

50

332のゲートとNchトランジスタ333のゲートには出力信号D8が、Nchトランジスタ334のゲートには出力信号D9が、それぞれ入力され、Pchトランジスタ332のドレインとNchトランジスタ333のドレインの接続点からは、パルス信号Pulseが出力される。

#### 【0051】

さらに、パルス発生論理回路300は、高電位側の電位V1と、低電位側の電位V2の間に、Pchトランジスタ341と、Nchトランジスタ342が直列に接続され、Pchトランジスタ341のゲートとNchトランジスタ342のゲート、及び、Pchトランジスタ341のドレインとNchトランジスタ342のドレインの接続点からは、パルス信号Pulseが出力される。10

#### 【0052】

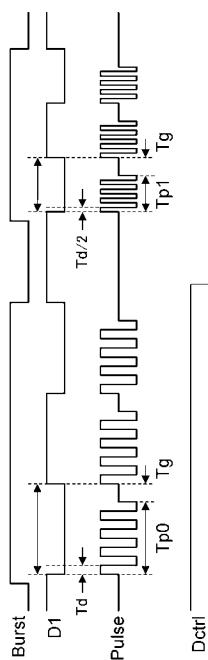

<バースト制御パルス発生回路の動作>

次に、図3を参照してバースト制御パルス発生回路100の動作を説明する。なお、2入力NAND201及びインバータ202～210は、同じ遅延時間Tdを有するものとする。また、バースト信号Burstは、図示しない制御回路により制御されているものとする。

#### 【0053】

図3に示すように、バースト信号BurstがLレベル(オフ状態)を保っている時点 $t_0$ までの期間では、2入力NAND201の出力信号D1は、Hレベルに保たれるので、出力信号D2, D4, D6, D8は、それぞれLレベルを保ち、出力信号D3, D5, D7, D9は、それぞれHレベルを保つ。また、パルス発生論理回路300は、Pchトランジスタ301, 311, 321, 331のゲートがそれぞれHレベルでオフ状態あり、Nchトランジスタ303, 313, 323, 333のゲートがそれぞれLレベルでオフ状態であるので、パルス信号Pulseの電位は、電位V1とV2の中間の電位となる。20

#### 【0054】

次に、時点 $t_0$ でバースト信号BurstがLレベルからHレベル(オン状態)に遷移すると、遅延時間Td後の時点 $t_1$ で2入力NAND201の出力信号D1がHレベルからLレベルに遷移する。この時点 $t_1$ で、パルス発生論理回路300は、Pchトランジスタ301, 302のゲートが共にLレベルでオン状態となるので、パルス信号Pulseの電位は、電位V1となる。30

#### 【0055】

次に、時点 $t_1$ から遅延時間Td後の時点 $t_2$ で出力信号D2がLレベルからHレベルに遷移する。この時点 $t_2$ で、パルス発生論理回路300は、Pchトランジスタ302のゲートがHレベルでオフ状態となり、さらにNchトランジスタ303, 304のゲートが共にHレベルでオン状態となるので、パルス信号Pulseの電位は、電位V2となる。

#### 【0056】

次に、時点 $t_2$ から遅延時間Td後の時点 $t_3$ で出力信号D3がHレベルからLレベルに遷移する。この時点 $t_3$ で、パルス発生論理回路300は、Pchトランジスタ311、312のゲートが共にLレベルでオン状態となるので、パルス信号Pulseの電位は、電位V1となる。40

#### 【0057】

次に、時点 $t_3$ から遅延時間Td後の時点 $t_4$ で出力信号D4がLレベルからHレベルに遷移する。この時点 $t_4$ で、パルス発生論理回路300は、Pchトランジスタ312のゲートがHレベルでオフ状態となり、さらにNchトランジスタ313, 314のゲートが共にHレベルでオン状態となるので、パルス信号Pulseの電位は、電位V2となる。

#### 【0058】

次に、時点 $t_4$ から遅延時間Td後の時点 $t_5$ で出力信号D5がHレベルからLレベル

10

20

30

40

50

に遷移する。この時点  $t_5$  で、パルス発生論理回路 300 は、Pchトランジスタ 321、322 のゲートが共に L レベルでオン状態となるので、パルス信号 Pulse の電位は、電位 V1 となる。

#### 【0059】

次に、時点  $t_5$  から遅延時間  $T_d$  後の時点  $t_6$  で出力信号 D6 が L レベルから H レベルに遷移する。この時点  $t_6$  で、パルス発生論理回路 300 は、Pchトランジスタ 322 のゲートが H レベルでオフ状態となり、さらに Nchトランジスタ 323, 324 のゲートが共に H レベルでオン状態となるので、パルス信号 Pulse の電位は、電位 V2 となる。さらに、時点  $t_5$  で出力信号 D5 が L レベルとなつたので、時点  $t_6$  で 2 入力 NAND 20 D201 の出力信号 D1 は、H レベルとなる。

10

#### 【0060】

次に、時点  $t_6$  から遅延時間  $T_d$  後の時点  $t_7$  で出力信号 D7 が H レベルから L レベルに遷移する。この時点  $t_7$  で、パルス発生論理回路 300 は、Pchトランジスタ 331、332 のゲートが共に L レベルでオン状態となるので、パルス信号 Pulse の電位は、電位 V1 となる。さらに、時点  $t_6$  で出力信号 D1 が H レベルとなつたので、時点  $t_7$  で出力信号 D2 は、L レベルとなる。

#### 【0061】

次に、時点  $t_7$  から遅延時間  $T_d$  後の時点  $t_8$  で出力信号 D8 が L レベルから H レベルに遷移する。この時点  $t_8$  で、パルス発生論理回路 300 は、Pchトランジスタ 332 のゲートが H レベルでオフ状態となり、さらに Nchトランジスタ 333, 334 のゲートが共に H レベルでオン状態となるので、パルス信号 Pulse の電位は、電位 V2 となる。さらに、時点  $t_7$  で出力信号 D2 が L レベルとなつたので、時点  $t_8$  で出力信号 D3 は、H レベルとなる。

20

#### 【0062】

次に、時点  $t_8$  から遅延時間  $T_d$  後の時点  $t_9$  で出力信号 D9 が H レベルから L レベルに遷移する。この時点  $t_9$  で、パルス発生論理回路 300 は、Pchトランジスタ 332 のゲートが H レベルでオフ状態であり、さらに Nchトランジスタ 334 のゲートが L レベルでオフ状態となるので、パルス信号 Pulse の電位は、電位 V1 と V2 の中間の電位となる。さらに、時点  $t_8$  で出力信号 D3 が H レベルとなつたので、時点  $t_9$  で出力信号 D4 は、L レベルとなる。

30

#### 【0063】

次に、時点  $t_9$  から遅延時間  $T_d$  後の時点  $t_a$  でクロック信号 CLK が L レベルから H レベルに遷移する。さらに、時点  $t_9$  で出力信号 D4 が H レベルとなつたので、時点  $t_a$  で出力信号 D5 は、H レベルとなる。

#### 【0064】

時点  $t_a$  で出力信号 D5 が H レベルとなつたので、次の時点  $t_b$  で出力信号 D1 が L レベルとなり、以降、バースト信号 Burst が H レベルの間、時点  $t_1 \sim t_b$  の動作が繰り返される。

#### 【0065】

つまり、図 3 に示すように、バースト制御パルス発生回路 100 は、バースト信号 Burst が H レベルの期間に、時点  $t_1 \sim t_9$  の期間の 4 つのパルスからなる変調パルス（幅  $T_p = T_d \times 8$ ）を時点  $t_9 \sim t_b$  の期間の中間電位からなるパルス間隔（幅  $T_g = T_d \times 2$ ）を設けてパルス信号 Pulse として繰り返し発生する。また、バースト信号 Burst が L レベルの間、パルス信号 Pulse は、電位 V1 と V2 の中間の電位となる。図 3 では、バースト信号 Burst が H レベルの期間（時点  $t_0 \sim t_d$ ）に、変調パルスを 3 回発生させている。

40

#### 【0066】

以降、上述した時点  $t_0 \sim t_d$ までの動作が、時点  $t_e \sim t_f$  までの期間も同様に繰り返される。

#### 【0067】

50

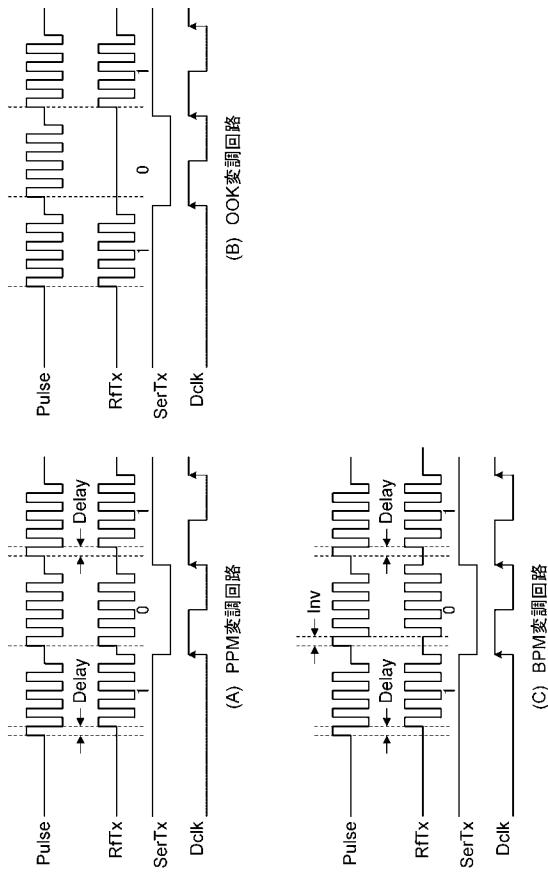

## &lt;デジタル変調回路の構成&gt;

次に、バースト制御パルス発生回路を使ったデジタル変調回路の構成について、図4及び図5を参照して説明する。図4は、バースト制御パルス発生回路を使ったデジタル変調回路の構成を示す回路図である。図5は、バースト制御パルス発生回路を使ったデジタル変調回路の動作を説明するタイミングチャートである。

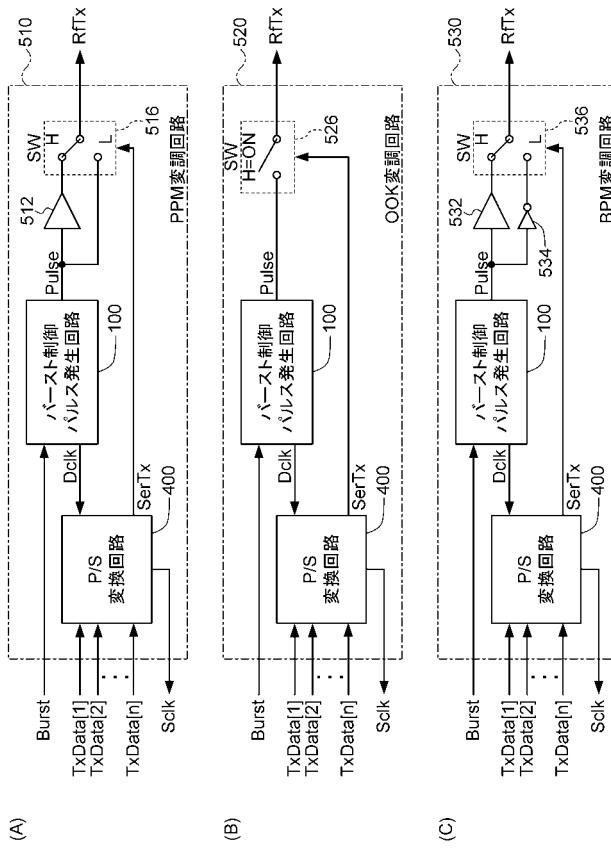

## 【0068】

先ず、図4(A)は、入力されたパラレル信号をPPM(Pulse Position Modulation)変調して出力するPPM変調回路510である。PPM変調回路510は、バースト制御パルス発生回路100と、パラレル/シリアル変換回路400と、遅延回路512と、切換回路516と、から構成されている。

10

## 【0069】

バースト制御パルス発生回路100は、図示しない制御回路からのバースト信号Burstを入力し、パルス信号Pulseとクロック信号Clockを出力する。パラレル/シリアル変換回路400は、パラレル信号TxData[1]~[n]とクロック信号Clockを入力し、シリアル信号Sertxとクロック信号Clockを出力する。切換回路516は、シリアル信号Sertxにより制御され、シリアル信号SertxがHレベル(第1の電位)の時は、遅延回路512を介してパルス信号Pulseを出力端子Rftxから出力し、シリアル信号SertxがLレベル(第2の電位)の時は、パルス信号Pulseを出力端子Rftxから出力する。

20

## 【0070】

図5(A)は、PPM変調回路510の動作を説明するタイミングチャートである。PPM変調回路510は、シリアル信号SertxがHレベルの時、遅延回路512の遅延時間Delay分遅くパルス信号Pulseを出力端子Rftxから出力し、シリアル信号SertxがLレベルの時、パルス信号Pulseを出力端子Rftxから出力する。

## 【0071】

次に、図4(B)は、入力されたパラレル信号をOOK(On-Off Keying)変調して出力するOOK変調回路520である。OOK変調回路520は、バースト制御パルス発生回路100と、パラレル/シリアル変換回路400と、切換回路526と、から構成されている。

30

## 【0072】

切換回路526は、シリアル信号Sertxにより制御され、シリアル信号SertxがHレベル(第1の電位)の時は、パルス信号Pulseを出力端子Rftxから出力し、シリアル信号SertxがLレベル(第2の電位)の時は、パルス信号Pulseと出力端子Rftxを切り離す。

## 【0073】

図5(B)は、OOK変調回路520の動作を説明するタイミングチャートである。OOK変調回路520は、シリアル信号SertxがHレベル(第1の電位)の時、パルス信号Pulseを出力端子Rftxから出力し、シリアル信号SertxがLレベル(第2の電位)の時、出力端子Rftxからの出力は、ハイ・インピーダンスとなる。

40

## 【0074】

次に、図4(C)は、入力されたパラレル信号をBPM(Bi-Phase Modulation)変調して出力するBPM変調回路530である。BPM変調回路530は、バースト制御パルス発生回路100と、パラレル/シリアル変換回路400と、遅延回路532と、インバータ534と、切換回路536と、から構成されている。

## 【0075】

切換回路536は、シリアル信号Sertxにより制御され、シリアル信号SertxがHレベルの時は、遅延回路532を介してパルス信号Pulseを出力端子Rftxから出力し、シリアル信号SertxがLレベルの時は、インバータ534を介してパルス信号Pulseを出力端子Rftxから出力する。

50

## 【0076】

図5(C)は、BPM変調回路530の動作を説明するタイミングチャートである。BPM変調回路530は、シリアル信号S<sub>er</sub>T<sub>x</sub>がHレベルの時、遅延回路512の遅延時間Delay分遅くパルス信号Pulseを出力端子R<sub>f</sub>T<sub>x</sub>から出力し、シリアル信号S<sub>er</sub>T<sub>x</sub>がLレベルの時、パルス信号Pulseを反転させインバータ534の遅延時間Inv分遅く出力端子R<sub>f</sub>T<sub>x</sub>から出力する。

#### 【0077】

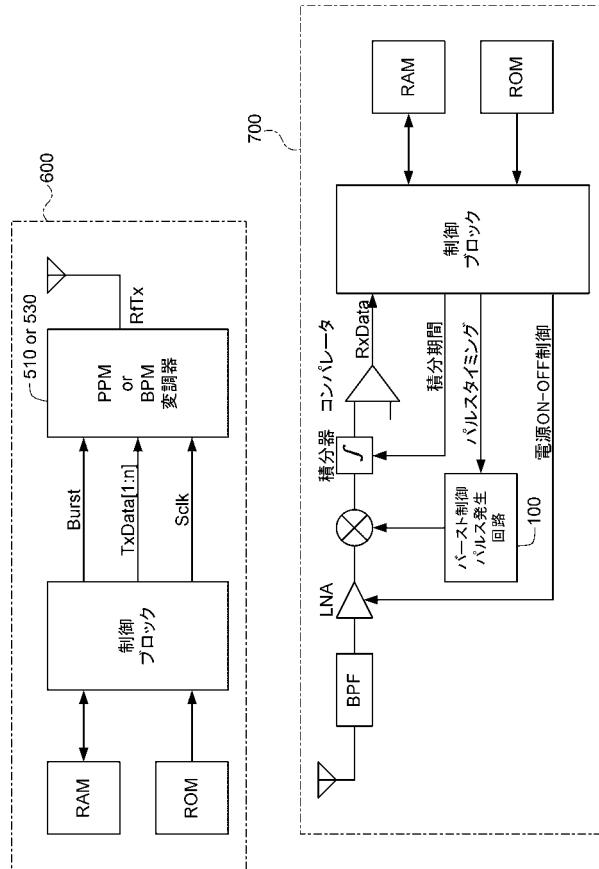

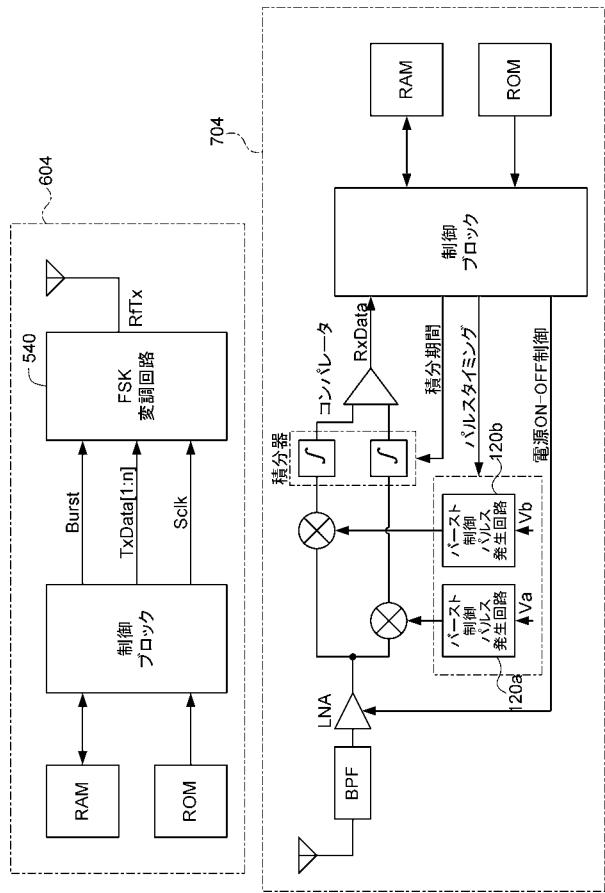

<送受信回路の構成>

次に、デジタル変調回路を使った送受信回路の構成例を、図12及び図13を参照して説明する。図12は、PPM変調回路またはBPM変調回路を使った送受信回路の構成を示す回路図である。図13は、OOK変調回路を使った送受信回路の構成を示す回路図である。

10

#### 【0078】

図12に示すように、送信回路600には、PPM変調回路510またはBPM変調回路530が使われ、受信回路700には、バースト制御パルス発生回路100が使われている。図5(A)に示すように、PPM変調の“1”と“0”が、同じパルスの変調周波数の半周期(Delay)だけずれている場合には、PPM変調とBPM変調は、同じ受信回路構成で検波することができる。

20

#### 【0079】

また、図13に示すように、送信回路602は、OOK変調回路520が使われるが、受信回路702には、バースト制御パルス発生回路100は使われない。OOK変調回路520を使った場合、自乗検波を用いて電力検出ができる。

20

#### 【0080】

以上に述べた前記実施形態によれば、以下の効果が得られる。

#### 【0081】

本実施形態では、バースト信号Burstがオン状態のとき1回以上のパルス信号を発生し、バースト信号がオフ状態のときパルス信号の発生を停止することができるので、ON-OFFスイッチング遅延の影響を実質的に低減し、低消費電力を実現することができる。なお、n及びmの数を増やすことにより、発生する1つのパルス信号Pulseの波数が増えるので帯域幅が狭くなりピットレートは落ちるが干渉に強いパルス信号Pulseを発生することができる。

30

#### 【0082】

(第2実施形態)

次に、バースト制御パルス発生回路の第2実施形態について説明する。第1実施形態においては、バースト制御パルス発生回路100は、マルチパスなどの伝搬路の影響や、フィルタやアンテナなどの群遅延特性の影響などで受信パルスの収束が遅くなることで、パルス同士の時間間隔が短い場合には、符号間干渉を引き起こす場合がある。第2実施形態では、受信状態によりパルス間隔Tgを調整することができるバースト制御パルス発生回路110を提案する。なお、本第2実施形態では、n=4かつm=4の場合について説明するが、この数に限定するものではない。

30

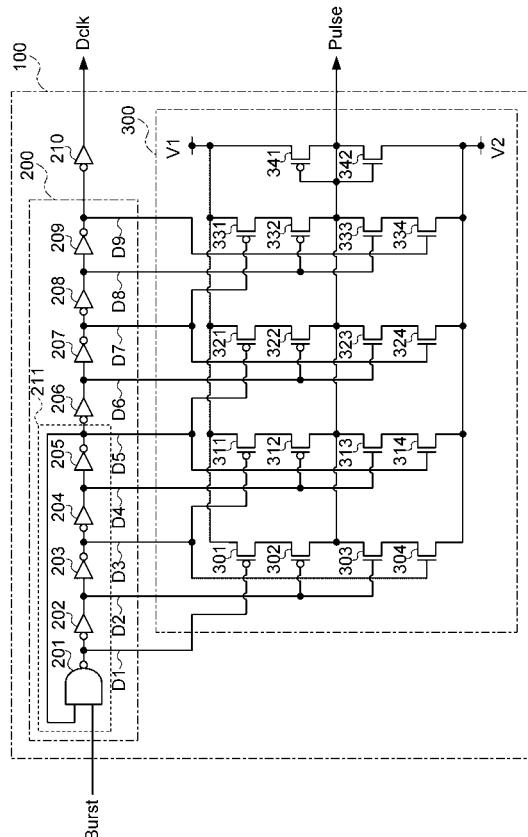

#### 【0083】

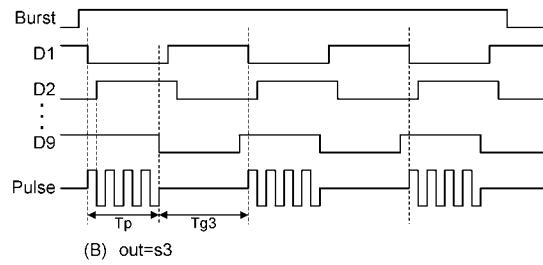

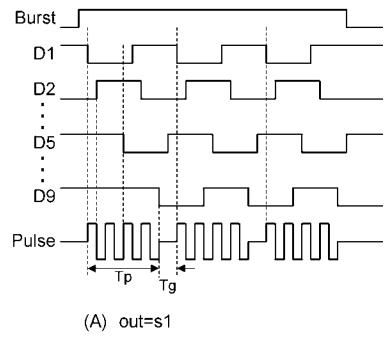

第2実施形態に係るバースト制御パルス発生回路の構成について、図6及び図7を参照して説明する。図6は、第2実施形態に係るバースト制御パルス発生回路の構成を示す回路図である。図7は、第2実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャートである。

40

#### 【0084】

図6に示すように、バースト制御パルス発生回路110は、リング発振周期を切り換える可能なタイミング発生回路220とパルス発生論理回路300とから構成されている。

#### 【0085】

タイミング発生回路220は、2入力論理回路である2入力NAND201と、NOT回路であるインバータ202～209と、切換回路221と、から構成されている。2入

50

力NAND201出力端子には、4個( $n = 4$ )のインバータ202～205が直列に接続され、さらに4個目のインバータ205の出力端子には、4個( $m = 4$ )のインバータ206～209が直列に接続されている。

#### 【0086】

切換回路221は、出力端子outと、入力端子s1, s2, s3とから構成され、出力端子outと入力端子s1、または、出力端子outと入力端子s2、または、出力端子outと入力端子s3、を接続するように切り換えられるようになっている。出力端子outは、2入力NAND201の一方の入力端子に接続され、さらに、クロック信号Dclkとして外部に出力されるようになっている。

#### 【0087】

入力端子s1は、インバータ205の出力端子と接続され、入力端子s2は、インバータ207の出力端子と接続され、入力端子s3は、インバータ209の出力端子と接続されている。切換回路221の出力端子outと入力端子s1が接続されると、2入力NAND201と4個のインバータ202～205によるリング発振が行われる。また、切換回路221の出力端子outと入力端子s2が接続されると、2入力NAND201と6個のインバータ202～207によるリング発振が行われる。また、切換回路221の出力端子outと入力端子s3が接続されると、2入力NAND201と8個のインバータ202～209によるリング発振が行われる。

#### 【0088】

図7(A)は、切換回路221の出力端子outと入力端子s1が接続された状態でのタイミング発生回路220の動作を説明するタイミングチャートであり、図7(B)は、切換回路221の出力端子outと入力端子s3が接続された状態でのタイミング発生回路220の動作を説明するタイミングチャートである。

#### 【0089】

図7(A)に示すように、切換回路221の出力端子outと入力端子s1が接続された状態では、変調パルス幅Tp = Td × 8、パルス間隔幅Tg = Td × 2である。また、図7(B)に示すように、切換回路221の出力端子outと入力端子s3が接続された状態では、変調パルス幅Tp = Td × 8、パルス間隔Tg3 = Td × 10である。

#### 【0090】

以上に述べた第2実施形態のバースト制御パルス発生回路110によれば、変調パルス幅を一定のまま、パルス間隔を切換回路221によって切り換えることができるので、符号間干渉の影響を低減しながら電源ON時間を最低限に抑えることができ、符号間干渉の影響を予め考慮して大きな固定パルス間隔に設定した場合に比べ、消費電力を低減することができる。

#### 【0091】

(第3実施形態)

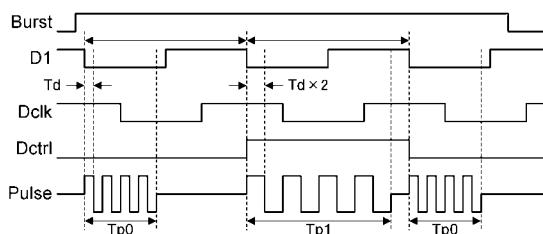

次に、バースト制御パルス発生回路の第3実施形態について説明する。第3実施形態では、変調パルス幅を可変としながら一定のビット送信速度を保つことができるバースト制御パルス発生回路120を提案する。なお、本第3実施形態では、 $n = 4$ かつ $m = 4$ の場合について説明するが、この数に限定するものではない。

#### 【0092】

第3実施形態に係るバースト制御パルス発生回路の構成について、図8及び図9を参照して説明する。図8は、第3実施形態に係るバースト制御パルス発生回路の構成を示す回路図である。図9は、第3実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャートである。

#### 【0093】

図8に示すように、バースト制御パルス発生回路120は、変調パルス幅を可変としながら一定のビット送信速度を保つタイミング発生回路230とパルス発生論理回路300とから構成されている。

#### 【0094】

10

20

30

40

50

タイミング発生回路 230 は、2 入力論理回路である 2 入力 NAND 201 と、NOT 回路であるインバータ 202 ~ 205 と、遅延制御信号 Dctr1 により遅延時間を制御可能な遅延制御 NOT 回路である遅延制御インバータ 231 ~ 238 と、から構成されている。2 入力 NAND 201 出力端子には、4 個 ( $n = 4$ ) のインバータ 202 ~ 205 が直列に接続され、4 個目のインバータ 205 の出力端子と 2 入力 NAND 201 の一方の入力端子が接続され、2 入力 NAND 201 の他方の入力端子には、バースト信号 Burst が入力されている。また、インバータ 205 の出力端子からクロック信号 Dclk が出力される。

#### 【0095】

2 入力 NAND 201 の出力端子には、遅延制御インバータ 231 ~ 238 が直列に接続され、遅延制御信号 Dctr1 により遅延時間が制御される。図 9 のタイミングチャートに示すように、遅延制御信号 Dctr1 が L レベルの時は、遅延制御インバータ 231 ~ 238 の遅延時間はそれぞれ  $T_d$  となり、遅延制御信号 Dctr1 が H レベルの時は、遅延制御インバータ 231 ~ 238 の遅延時間はそれ  $T_d \times 2$  となるように設定されているものとする。

#### 【0096】

タイミング発生回路 230 は、バースト信号 Burst がオン状態の期間中、遅延制御信号 Dctr1 を切り換えることにより、変調パルス幅（変調周波数）を連続的に変えることができる。つまり、パルスの変調周波数を変化させる FSK (Frequency Shift Keying) 変調を実現できる。

#### 【0097】

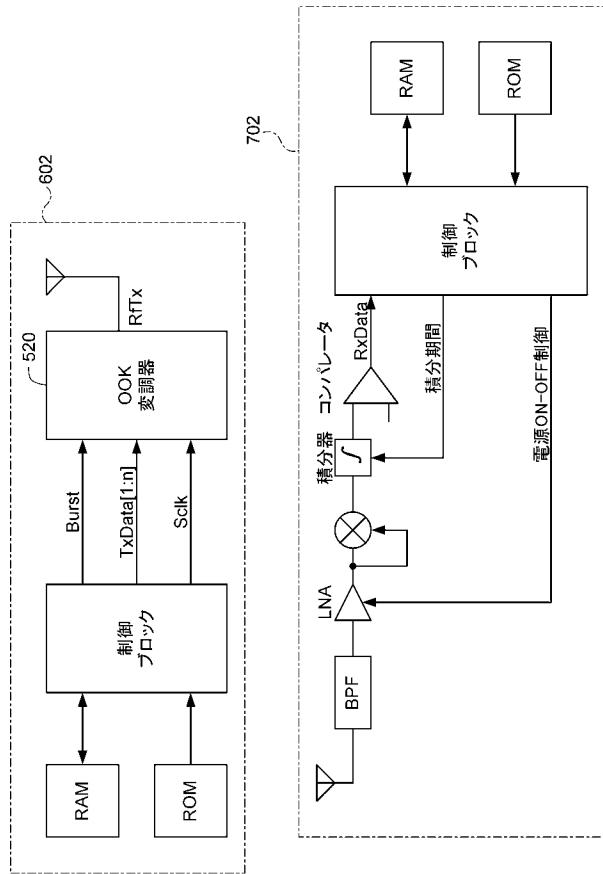

##### < FSK 変調回路の構成 >

次に、バースト制御パルス発生回路を使った FSK 変調回路の構成について、図 14 を参照して説明する。図 14 は、バースト制御パルス発生回路を使った FSK 変調回路の構成を示す回路図である。

#### 【0098】

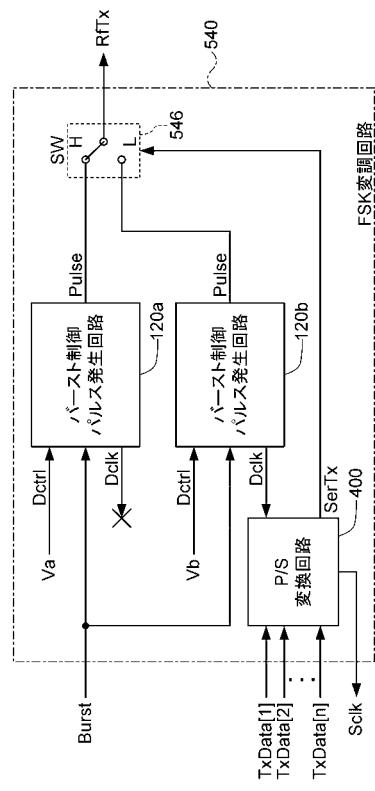

図 14 に示すように、FSK 変調回路 540 は、2 つのバースト制御パルス発生回路 120a、120b と、パラレル / シリアル変換回路 400 と、切換回路 546 と、から構成されている。

#### 【0099】

2 つのバースト制御パルス発生回路 120a、120b は、それぞれ異なる遅延制御信号 Dctr1 である  $V_a$  と  $V_b$  で制御される。切換回路 546 は、シリアル信号 SerTx により制御され、シリアル信号 SerTx が H レベル（第 1 の電位）の時は、バースト制御パルス発生回路 120a のパルス信号 Pulse を出力端子 Rftx から出力し、シリアル信号 SerTx が L レベル（第 2 の電位）の時は、バースト制御パルス発生回路 120b のパルス信号 Pulse を出力端子 Rftx から出力する。

#### 【0100】

図 9 では、ビット毎にパルスの変調周波数を調整する例を示したが、遅延制御の応答速度が間に合わない場合には、予め遅延制御信号 Dctr1 に  $V_a$  もしくは  $V_b$  を設定したバースト制御パルス発生回路 120a、120b を用意して、ビットデータに応じて切換回路 546 で切り換えている。この例では、2 つのバースト制御パルス発生回路 120a、120b を用いているが、より多くのバースト制御パルス発生回路 120 を組み合わせてもよい。

#### 【0101】

##### < FSK 変調回路を使った送受信回路の構成 >

次に、FSK 変調回路を使った送受信回路の構成例を、図 15 を参照して説明する。図 15 は、FSK 変調回路を使った送受信回路の構成を示す回路図である。

#### 【0102】

図 15 に示すように、送信回路 604 には、FSK 変調回路 540 が使われ、受信回路 704 には、予め遅延制御信号 Dctr1 に  $V_a$  もしくは  $V_b$  を設定した 2 つのバースト

10

20

30

40

50

制御パルス発生回路 120a, 120b を基準信号源として用意し、受信信号との相関を算出することでビット判定を行っている。

#### 【0103】

以上に述べた第3実施形態のバースト制御パルス発生回路 120 によれば、リング発振周期を一定にしたままなので、受信側ではパルスの変調周波数に関わらず一定のビット間隔で受信できる。従って、回路構成が複雑にならないという利点がある。さらに、他システムからの干渉や他システムへの干渉を低減する目的で周波数を可変にする周波数分割多重通信を実現することで、同時通信可能な通信数を増やしたり、通信速度を向上させたりすることができる。

#### 【0104】

##### (第4実施形態)

次に、バースト制御パルス発生回路の第4実施形態について説明する。第4実施形態では、パルス間隔を一定に保ちながら変調パルス幅を変えることができるバースト制御パルス発生回路 130 を提案する。

#### 【0105】

第4実施形態に係るバースト制御パルス発生回路の構成について、図 10 及び図 11 を参照して説明する。図 10 は、第4実施形態に係るバースト制御パルス発生回路の構成を示す回路図である。図 11 は、第4実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャートである。

#### 【0106】

図 10 に示すように、バースト制御パルス発生回路 130 は、パルス間隔を一定に保ちながら変調パルス幅を変えるタイミング発生回路 240 とパルス発生論理回路 350 とから構成されている。

#### 【0107】

タイミング発生回路 240 は、2 入力論理回路である 2 入力 NAND 201 と、インバータ 202, 203 と、遅延制御信号 Dctr1 により遅延時間を制御可能な遅延制御 NOT 回路である遅延制御インバータ 231 ~ 238 と、から構成されている。2 入力 NAND 201 出力端子には、遅延制御インバータ 231 ~ 238 が直列に接続され、遅延制御信号 Dctr1 により遅延時間が制御される。遅延制御インバータ 238 の出力端子は、2 つのインバータ 202, 203 を介して 2 入力 NAND 201 の一方の入力端子に接続され、2 入力 NAND 201 の他方の入力端子には、バースト信号 Burst が入力されている。また、インバータ 203 の出力端子からクロック信号 Dclk が出力される。

#### 【0108】

図 11 のタイミングチャートに示すように、遅延制御信号 Dctr1 が H レベルの時は、遅延制御インバータ 231 ~ 238 の遅延時間はそれぞれ Td、遅延制御信号 Dctr1 が L レベルの時は、遅延制御インバータ 231 ~ 238 の遅延時間はそれぞれ Td ÷ 2 となるように設定されているものとする。

#### 【0109】

タイミング発生回路 240 は、バースト信号 Burst がオン状態の期間中、遅延制御信号 Dctr1 を切り換えることにより、変調パルス幅（変調周波数）を連続的に変えることができるが、パルス間隔 Tg を一定に保つことができる。

#### 【0110】

以上に述べた第4実施形態のバースト制御パルス発生回路 130 によれば、パルス間隔 Tg を一定に保ちながら変調パルス幅を変えることができるので、符号間干渉の課題がある場合に、パルスの変調周波数に関わらず符号間干渉の影響を抑制できる。

#### 【0111】

以上、バースト制御パルス発生回路の実施形態を説明したが、こうした実施の形態に何ら限定されるものではなく、趣旨を逸脱しない範囲内において様々な形態で実施し得ることができる。

#### 【0112】

10

20

30

40

50

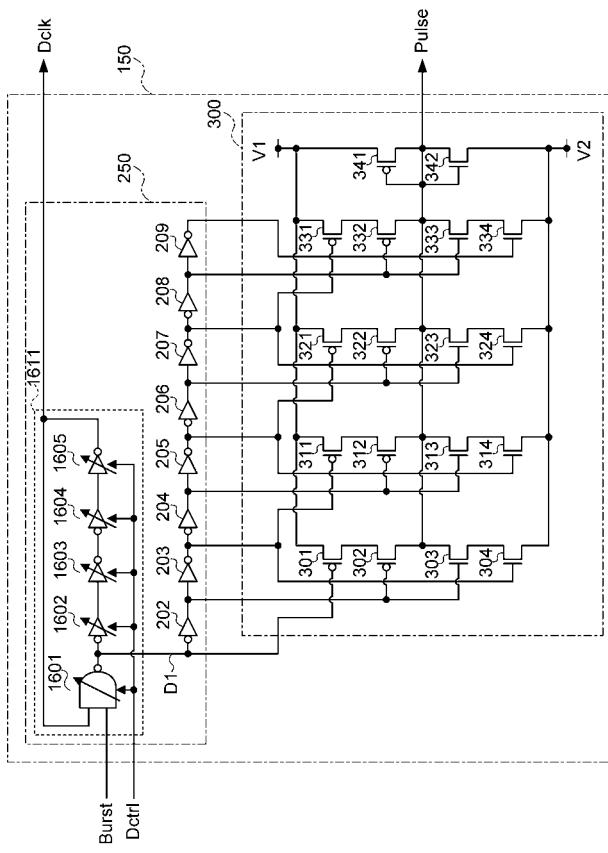

(変形例1) バースト制御パルス発生回路の変形例1について説明する。図16は、変形例1に係るバースト制御パルス発生回路の構成を示す回路図である。前記第3実施形態では、図8に示すようなタイミング発生回路230で説明したが、図16に示すようなタイミング発生回路250にしてもよい。図8の2入力NAND201の替わりに図16では遅延制御2入力NAND1601が使われ、図8のインバータ202～205の替わりに図16では遅延制御インバータ1602～1605が使われている。逆に、図8の遅延制御インバータ231～238の替わりに図16ではインバータ202～209が使われている。なお、インバータ202～209を遅延制御インバータ231～238に置き換え、タイミング発生回路250のすべての回路を遅延制御の論理回路にしてもよい。本変形例1によれば、パルスの変調周波数を一定に保ったまま、パルスの発生間隔を変えることができるため、符号間干渉の影響を状況に応じて低減することができる。

10

## 【0113】

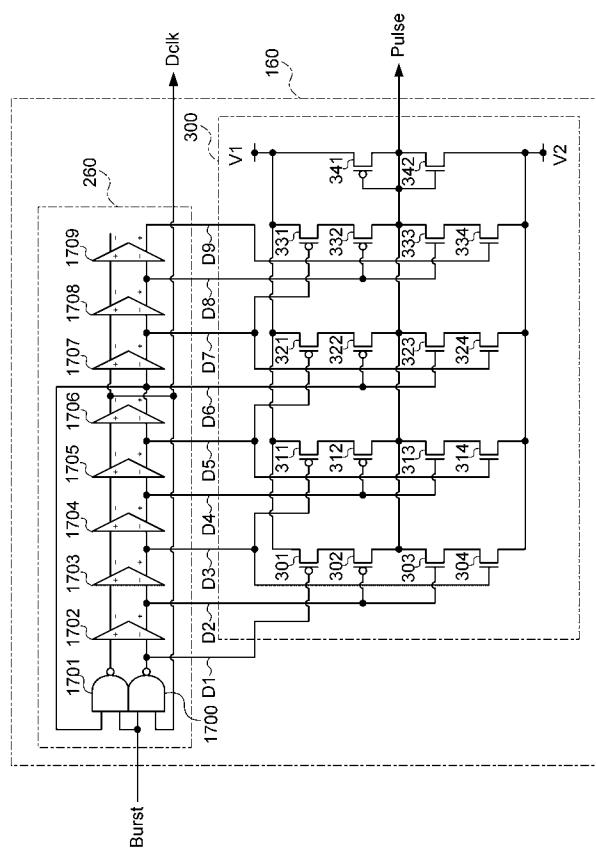

(変形例2) バースト制御パルス発生回路の変形例2について説明する。図17は、変形例2に係るバースト制御パルス発生回路の構成を示す回路図である。前記第1実施形態では、図2に示すようなタイミング発生回路200で説明したが、図17に示すようなタイミング発生回路260にしてもよい。図2のインバータ202～209の替わりに図17では差動インバータ1702～1709が使われている。また、図2の2入力NAND201の替わりに図17では2つの2入力NAND1700, 1701が使われている。本変形例2によれば、タイミング発生回路260で発生させる周期信号の周期の自由度を高めることができ、差動動作なためタイミング発生回路260が発生するノイズや外部から受けるノイズの影響を低減できる。

20

## 【0114】

(変形例3) バースト制御パルス発生回路を使った電子機器の例について説明する。図18は、変形例3に係る電子機器である携帯電話1800の構成を示す概略図である。携帯電話1800は、操作ボタンなどを備えた本体部1810と、液晶パネルなどを備えた表示部1820とが、ヒンジ部1830によって折りたたみ可能なように接続されている。本体部1810には、図12に示す送信回路600が内蔵され、表示部1820には、図12に示す受信回路700が内蔵され、無線通信により本体部1810から表示部1820に動画や静止画や音声などのデータが送受信される。送信回路600及び受信回路700で携帯電話1800を構成することにより、本体部1810から表示部1820に高速に動画や静止画や音声などのデータを転送することができる。

30

## 【図面の簡単な説明】

## 【0115】

【図1】従来のON-OFFスイッチング遅延を説明するタイミングチャート。

【図2】第1実施形態に係るバースト制御パルス発生回路の構成を示す回路図。

【図3】第1実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャート。

【図4】バースト制御パルス発生回路を使ったデジタル変調回路の構成を示す回路図。

【図5】バースト制御パルス発生回路を使ったデジタル変調回路の動作を説明するタイミングチャート。

40

【図6】第2実施形態に係るバースト制御パルス発生回路の構成を示す回路図。

【図7】第2実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャート。

【図8】第3実施形態に係るバースト制御パルス発生回路の構成を示す回路図。

【図9】第3実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャート。

【図10】第4実施形態に係るバースト制御パルス発生回路の構成を示す回路図。

【図11】第4実施形態に係るバースト制御パルス発生回路の動作を説明するタイミングチャート。

【図12】PPM変調回路またはBPM変調回路を使った送受信回路の構成を示す回路図

50

【図13】OOK変調回路を使った送受信回路の構成を示す回路図。

【図14】バースト制御パルスを使ったFSK変調回路の構成を示す回路図。

【図15】FSK変調回路を使った送受信回路の構成を示す回路図。

【図16】変形例1に係るバースト制御パルス発生回路の構成を示す回路図。

【図17】変形例2に係るバースト制御パルス発生回路の構成を示す回路図。

【図18】変形例3に係る電子機器である携帯電話の構成を示す概略図。

#### 【符号の説明】

##### 【0116】

100...バースト制御パルス発生回路、110...バースト制御パルス発生回路、120...バースト制御パルス発生回路、120a...バースト制御パルス発生回路、120b...バースト制御パルス発生回路、130...バースト制御パルス発生回路、200...タイミング発生回路、201...2入力NAND、202~210...インバータ、220...タイミング発生回路、221...切換回路、230...タイミング発生回路、231~238...遅延制御インバータ、240...タイミング発生回路、300...パルス発生論理回路、400...パラレル/シリアル変換回路、510...PPM変調回路、512...遅延回路、516...切換回路、520...OOK変調回路、526...切換回路、530...BPM変調回路、532...遅延回路、534...インバータ、536...切換回路、540...FSK変調回路、546...切換回路、600...送信回路、602...送信回路、604...送信回路、700...受信回路、702...受信回路、704...受信回路。

10

20

【図1】

【図2】

【 四 3 】

【 図 5 】

【 四 4 】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【 図 1 5 】

【 図 1 6 】

【図17】

【 図 1 8 】