(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년07월26일

(11) 등록번호 10-1288438

(24) 등록일자 2013년07월16일

- (51) 국제특허분류(Int. C1..)

G09G 3/30 (2006.01)

- (21) 출원번호 10-2010-7008465

- (22) 출원일자(국제) 2008년09월16일

심사청구일자 2012년08월29일

- (85) 번역문제출일자 2010년04월19일

- (65) 공개번호 10-2010-0072031

- (43) 공개일자 2010년06월29일

- (86) 국제출원번호 PCT/US2008/010753

- (87) 국제공개번호 WO 2009/038688

국제공개일자 2009년03월26일

- (30) 우선권주장

11/857,634 2007년09월19일 미국(US)

- (56) 선행기술조사문현

KR1020050067097 A

KR1020050077488 A

KR1020040032787 A

KR1020080041264 A

- (73) 특허권자

글로벌 오엘아이디 테크놀러지 엘엘씨

미국 베지니아 20171 헌던 스위트 330 13873 파크

센터 로드

- (72) 발명자

밀러 마이클 유진

미국 뉴욕 14650 로체스터 343 스테이트 스트리트

아놀드 앤드류 다니엘

미국 뉴욕 14650 로체스터 343 스테이트 스트리트

해밀턴 쥬니어 존 프랭클린

미국 뉴욕 14650 로체스터 343 스테이트 스트리트

- (74) 대리인

김용인, 석혜선

전체 청구항 수 : 총 17 항

심사관 : 조기덕

(54) 발명의 명칭 타일형 패시브 매트릭스 전계발광 디스플레이

**(57) 요약**

타일형 패시브 매트릭스 EL 디스플레이는 행 및 열 전극의 직교 어레이 사이에 끼여 있는 발광층으로부터 각각 형성되는 발광 소자의 행 및 열의 어레이를 각각 포함하는 2 개 이상의 타일; 발광 소자의 각각으로부터 광의 방출을 제어하기 위해 행 전극과 열 전극 사이의 전자의 흐름을 제어하도록 각각의 적어도 하나의 행 드라이버와 함께 동작하는 적어도 하나의 열 드라이버를 포함하고, 각각의 2 개 이상의 EL 타일은 적어도 하나의 행 드라이버를 더 포함하며, 2 개 타일 사이의 경계가 조명되려는 경우, 하나의 타일 내의 발광 소자의 동시에 조명된 행의 행 개수가 기결정된 개수보다 적은 제 1 예외를 가진다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

- a) 행 및 열 전극의 직교 어레이 사이에 끼여 있는 발광층으로부터 각각 형성되는 발광 소자의 행 및 열의 어레이를 각각 포함하는 2 개 이상의 EL 타일;

- b) 발광 소자의 각각으로부터 광의 방출을 제어하기 위해 행 전극과 열 전극 사이의 전자의 흐름을 제어하도록 각각의 적어도 하나의 행 드라이버와 함께 동작하는 적어도 하나의 열 드라이버; 및

- c) 입력 이미지 신호를 수신하고, 시간 구간 동안 각각의 EL 타일 내의 발광 소자의 기결정된 개수의 행의 그룹을 동시에 조명하기 위해 행 및 열 전극을 통해 전자의 흐름을 제어하도록 2 개 이상의 EL 타일 내의 2 개 이상의 드라이버에 행 구동 신호를 동시에 제공하는 행 드라이버 및 열 드라이버(들)에 결합된 하나 이상의 제어기를 포함하며,

각각의 2 개 이상의 EL 타일은 적어도 하나의 행 드라이버를 더 포함하고,

각각의 EL 타일에서, 이어지는 2 개의 시간 구간 동안 발광 소자의 조명되는 행의 그룹들은 오버랩 없이 선택되나, 2 개 EL 타일 사이의 경계가 조명되려는 경우에는 현재 시간 구간의 그룹에서 발광 소자의 조명되는 행의 개수가 기결정된 개수보다 적고, 현재 시간 구간의 그룹의 발광 소자의 조명되는 행이 이전 시간 구간의 그룹의 발광 소자의 조명된 행과 오버랩되는 제 1 예외를 가지는 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 2

제 1 항에 있어서,

적어도 2 개의 EL 타일 사이의 경계를 가지는 적어도 2 개의 EL 타일이 있으며 2 개의 EL 타일은 경계 반대편의 가장자리를 가지고, 각각의 EL 타일의 반대편 가장자리들을 동시에 조명하는 경우 행 구동 신호의 개수가 하나의 EL 타일 내에서의 기결정된 개수보다 적은 제 2 예외를 가지는 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 3

제 1 항에 있어서,

각각의 제어기는 행 및 열 드라이버에 입력 이미지 신호를 적용하기 전에 입력 이미지 신호를 처리하는 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 4

제 3 항에 있어서,

각각의 제어기는 이미지 신호를 샤프닝하거나 또는 분해하는 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 5

제 1 항에 있어서,

동시에 활성된 발광 소자의 그룹 내에서 복수의 행 전극과 하나의 열 전극의 교차에 해당하는 발광 소자의 휘도 레벨은 동일한 그룹 내의 다른 발광 소자의 휘도 레벨보다 더 밝은 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 6

제 1 항에 있어서,

각각의 이미지에 대한 복수의 필드가 존재하며 각각의 필드 동안 광을 방출하는 각각의 EL 타일 내의 적어도 하나의 발광 소자가 존재하는 타일형 패시브-매트릭스 EL 디스플레이.

### 청구항 7

제 1 항에 있어서,

EL 디스플레이는 하나의 제어기를 포함하는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 8**

제 1 항에 있어서,

제어기(들)는 입력 이미지 신호를 수신하고 행 구동 신호와 열 구동 신호를 결정하기 전에 인접한 EL 타일 사이의, 휙도 또는 색 변화에 대한 보정을 적용하는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 9**

제 1 항에 있어서,

디스플레이 상에 동시에 조명되는 발광 소자의 행의 전체 개수는 경계가 조명되는 경우 행 구동 신호의 기결정된 개수와 동일한 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 10**

제 1 항에 있어서,

2 개 이상의 EL 타일의 적어도 일부는 단일 기판 상에 형성되는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 11**

제 10 항에 있어서,

2 개 이상의 EL 타일은 기판의 하나의 가장자리에서 열 커넥터를 제공하는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 12**

제 10 항에 있어서,

디스플레이는 열 드라이버로의 연결을 제공하기 위해 EL 타일을 통해 확장하는, 적어도 하나의 금속 타일 커넥터를 포함하는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 13**

제 10 항에 있어서,

디스플레이는 적어도 3 개의 타일로 구성되는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 14**

제 10 항에 있어서,

타일형 패시브-매트릭스 EL 디스플레이에는 단일 열 드라이버로 2 개 이상의 EL 타일을 연결하기 위한 금속 타일 커넥터를 포함하는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 15**

제 10 항에 있어서,

2 개 이상의 타일이 동시에 코팅되는 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 16**

제 10 항에 있어서,

다른 EL 타일을 연결하기 위한 금속 타일 커넥터의 너비는 열 드라이버로부터 EL 타일의 길이의 함수로서 다양한 타일형 패시브-매트릭스 EL 디스플레이.

#### **청구항 17**

제 10 항에 있어서,

타일형 패시브-매트릭스 EL 디스플레이에는 3 개 이상의 타일로 구성되는 타일형 패시브-매트릭스 EL 디스플레이.

## 명세서

### 기술분야

[0001] 본 발명은 패시브 매트릭스 전계발광 디스플레이, 더 구체적으로는 인접한 타일들 사이의 가시적 경계 없이 구동되는 타일형 패시브 매트릭스 디스플레이에 관한 것이다.

### 배경기술

[0002] 현재 많은 디스플레이 장치가 시장에 존재한다. 이용 가능한 디스플레이 중에는 OLED 디스플레이와 같은, 박막, 코팅된, EL(Electro-Luminescent) 디스플레이가 있다. 이들 디스플레이들은 액티브 회로의 어레이를 이용하는, 액티브 매트릭스 백플레인(backplane)을 사용하여 구동될 수 있다. 이들 액티브 회로는 디스플레이의 각각의 발광 소자로의 전류의 흐름을 제어한다. 그러나, 이들 디스플레이들은 각각의 발광 소자에서 액티브 회로를 형성하는 복잡성에 기인하여 비교적 비쌀 수 있고 이들 액티브 구동 회로 내에 종종 사용되는 박막 트랜지스터는 시간상의 역치 이동 또는 균일성의 결핍을 가져오는, 결점을 가지기 쉬어, 이는 디스플레이의 품질을 저하시킨다.

[0003] 패시브 매트릭스 박막, 코팅, 전계발광 디스플레이가 또한 공지되어 있다. 유감스럽게도, 이들 디스플레이들은 전형적으로 펄스 폭 변조를 사용하는, 디스플레이의 하나의 라인만이 동시에 구동되도록 한다. 또한, 이들 장치에서 각각의 발광 주기 전에 각각의 발광 소자의 커패시턴스를 방전하고 충전하는 것이 일반적으로 필요하다. 이 때문에, 패시브 매트릭스, 박막, 코팅된 전계발광 디스플레이들은 전형적으로 초과된 양의 전력을 이끌어내며 디스플레이가 현재 2 대각선 인치보다 적은, 소정의 치수를 초과할 때마다 저가의 실리콘 제조 공정을 사용하여 제조되는 행(row) 및 열(column) 드라이버에 의해 제공될 수 있는 것보다 더 큰 구동 전압을 종종 요구한다.

[0004] 최근에, EL 디스플레이에 적용 가능한 멀티라인 패시브 매트릭스 구동 방법이 또한 문헌들에 논의되어왔다. 이들 접근들 중에서, "Image Display Apparatus"란 명칭의, 미국 특허 출원 제 10/680,221호에 Yamazaki 등에 의한 방법이 설명되어 있으며, "Multi-line Addressing Methods and Apparatus"란 명칭의 PCT 출원 WO 2006/035246 호, "Multi-line Addressing Methods and Apparatus"란 명칭의 PCT 출원 WO 2006/035248호, 및 "Digital Signal Processing Methods and Apparatus"란 명칭의 PCT 출원 WO 2006/067520호에서 Smith 등에 의해, 개별 방법이 설명되어 있다. 이들 방법의 각각은 EL 디스플레이 내의 각각의 발광 소자를 통해 전류를 상당히 감소시키고 개별 행 라인상의 피크 전류를 잠재적으로 감소시키는데 사용될 수 있다. 이는 이들 디스플레이 내의 행 및 열 전극의 저항에 기인하여 전력 손실을 감소시키며, 소정의 구동 조건하에, 또한 타당한 전력 소모를 가지는 더 큰 패시브 매트릭스 EL 디스플레이를 만들 수 있는, 디스플레이의 커패시턴스를 충전하고 방전하도록 소모된 전력을 감소시킬 수 있다. 유감스럽게도, 이들 방법은 종종 데이터 신호로 몇 가지 오류가 도입되어, 소정의 조건 하에서 이미지 아트팩트(image artifact)를 가져올 수 있다. 또한, 이들은 패시브 매트릭스 EL 디스플레이의 크기가, 요구되는 바와 같이 10 이상의 인자(factor) 보다는 차라리, 약간의 인자에 의해 증가되도록 할 뿐이다.

[0005] 더 큰 패시브 매트릭스 디스플레이를 형성하는 또 다른 방법은 더 큰 EL 디스플레이를 형성하기 위해 함께 결합되는 타일의 역할을 하는, 다수의 행 및 열 드라이버를 가지는 복수의 개별 디스플레이들 또는 디스플레이들을 형성하는 것이다. 이와 같은 타일형 디스플레이가 당해 기술에 공지되어 있다. 예를 들어, "Display System"란 명칭의 미국 특허 제 6,980,182호에서 Nimmer 등, 및 "Tiled OLED Display"란 명칭의 미국 공보 제 2006/0108918호에서 Cok 등은 단일 행 및 열 드라이버를 이용하는 단일 디스플레이를 사용하여 달성될 수 있는 것보다 더 큰 영역을 타일형 디스플레이에 제공하기 위해 다중 행 및 열 드라이버가 부착될 수 있는 단일 디스플레이 기판을 형성하는 것을 각각 논의하였다. 이와 같은 방법은 균일한 발광 층을 코팅하고, 타일들 사이의 비-균일성의 중요한 근원을 제거함으로써 다수의 EL 타일들이 형성되도록 한다. 각각의 행 드라이버가 최종 타일형 디스플레이 내의 행 전극들의 서브세트에만 신호를 제공하기 때문에 이와 같은 배열은 패시브-매트릭스 EL 디스플레이에 유리하다. 이와 같은 디스플레이의 커패시턴스가 충전되고 방전되어야 하는 시간의 양이 한번에 하나의 라인을 사용하여 패시브 매트릭스 구동 방법이 구동되는 라인의 개수의 대략 제곱만큼 증가하는 경우 이와 같은 디스플레이에 의해 소모되는 전력 및 구동되는 라인의 개수에 비례하기 때문에, 이와 같은 방법은 드라이버가 디스플레이에서 전체 라인의 반절을 구동하도록 하여 그러므로 디스플레이의 전력 소비를 상당히 감소시킬 수 있고, 다시 합리적인 전력 소비를 가지는 디스플레이의 크기가 2 또는 3 %의 인자에 의해 증가되도록 한

다. 이들 내용에는 패시브 매트릭스 EL 디스플레이의 타일링(tiling)과 함께 멀티-라인 구동 방법의 조합이 개시되어 있지 않다. Freidhoff 및 Phelan은 "Light-Producing Display Having High Aperture Ratio Pixels"란 명칭의 미국 특허 제 6,509,941호 및 "Light-Producing High Aperture Ratio Displays Having Aligned Tiles"란 명칭의 미국 특허 제 6,853,411호에서 다른 타일형 EL 디스플레이를 논의하였다.

[0006] 타일형 디스플레이의 하나의 쟁점은 입력 이미지 신호(122)가, 이미지의 상부 좌측 모서리에서의 데이터 포인트에서 시작하여 이어서 디스플레이의 각 행에서 픽셀에 대해 데이터를 제공하는, 래스터(raster) 방식으로 이와 같은 디스플레이로 일반적으로 스트림된다. 그러나, 디스플레이가 각각의 타일에 대해 각각 행 및 열 드라이버를 가지기 때문에, 더 높은 레벨의 제어기가 수신되는 경우 이 입력 이미지 신호를 저장하고, 입력 데이터를 독립적인 블록으로 분할하고, 입력 이미지 신호 데이터의 각각의 블록이 디스플레이 내의 타일의 물리적 위치에 대응하는 입력 이미지 신호의 부분을 독립적으로 렌더링하도록 각각의 타일에 연결된 행 및 열 드라이버에 의해 사용될 행 및 열 드라이버에 입력 이미지 신호 데이터의 각각의 독립적 블록을 제공하는 것이 전형적으로 필요하다. 예를 들어, Koester 등에 의한 미국 특허 출원 10/158,321호, 및 Lin에 의한 미국 특허 출원 10/249,954호에서, 각각의 블록이 각각의 타일에 대한 행 및 열 드라이버에 독립적으로 분배되어 있는 다수의 독립적 블록으로 입력 이미지 신호를 저장하고 재조직하기 위해 프로세서를 사용하는 것을 설명하고 있다.

[0007] 인간의 시각 시스템(human visual system)이 인접한 타일 사이의 경계 가까이에서 발생하는 인공 휘도 가장자리 또는 휘도에서의 변화에 매우 민감하기 때문에 이와 같은 디스플레이에서의 지배적인 문제점들 중 하나가 발생한다. "Tiled, Flat-Panels Displays with Luminance-Correcting Capability"란 명칭의, 미국 특허 5,668,569, "Flat-panel Display Assembled from Pre-sorted Tiles Having Matching Color Characteristics and Color Correction Capability"란 명칭의, 미국 특허 6,292,157에서 Greene 등에 의해 논의된 바와 같이, 휘도 차를 감소시키기 위한 타일을 분류하는 것이 공지되어 있다. 또한, "Correction Methods for Brightness in Electronic Display"란 명칭의, 미국 특허 6,271,825에 Green 등에 의해 논의된 바와 같이 인접한 타일의 가장자리 사이의 경계에서 이미지의 휘도 또는 색에서의 차를 감소시키기 위해 입력 이미지 신호를 조절하는 것이 공지되어 있다. 이들 특허에 논의된 색 및 휘도 보정 방법에서, 디스플레이를 형성하는 타일이 각각의 방사측정(radiometric) 성능을 설명하는 데이터는 입력 이미지 신호가 각각의 행 및 열 드라이버에 제공되기 전에 입력 이미지 신호를 조절하는데 사용된다. 이들 접근이 이웃하는 타일의 광학 성능의 차만을 보정하는 것은 주목할만하다. 이들 내용에 설명된 실시예에서의 행 및 열 드라이버는 각각 수신하고 입력 이미지 신호의 개별 블록에 응답함에 따라 서로 독립적으로 동작한다.

## 발명의 내용

### 해결하려는 과제

[0008] 본 발명의 내용에 포함되어 있음.

### 과제의 해결 수단

[0009] 본 발명에 따라, 다음을 포함하는 타일형 패시브-매트릭스가 제공되어 있다:

[0010] a) 행 및 열 전극의 직교 어레이 사이에 끼여 있는 발광층으로부터 각각 형성되는 발광 소자의 행 및 열의 어레이를 각각 포함하는 2 개 이상의 타일;

[0011] b) 발광 소자의 각각으로부터 광의 방출을 제어하기 위해 행 전극과 열 전극 사이의 전자의 흐름을 제어하기 위해 각각의 적어도 하나의 행 드라이버와 함께 동작하는 적어도 하나의 열 드라이버; 및

[0012] c) 2 개 타일 사이의 경계가 조명되려는 경우, 하나의 타일 내의 발광 소자의 동시에 조명된 행의 행 개수가 기 결정된 개수보다 작은 제 1 예외를 가지는, 입력 이미지 신호를 수신하고 2 개 이상의 EL 타일 내의 발광 소자의 기결정된 개수의 행을 동시에 조명하기 위해 행 및 열 전극을 통해 전자의 흐름을 제어하도록 2 개 이상의 EL 타일 내의 2 개 이상의 드라이버에 행 구동 신호를 동기에 제공하는 행 드라이버 및 열 드라이버(들)에 결합된 하나 이상의 제어기;

[0013] 여기서 각각의 2 개 이상의 EL 타일은 적어도 하나의 행 드라이버를 더 포함한다.

## 발명의 효과

[0014] 패시브 매트릭스 EL 디스플레이에 대한 타일링(tiling) 및 멀티라인 구동 방법의 조합을 이용하도록 시도하는

동안, 현존하는 멀티라인 구동 방법이 인접한 타일 사이의 경계에서 시각적 휘도 아티팩트를 발생함을 발견하였다. 본 발명은 이를 시각적 아티팩트를 도입하지 않고 이를 방법 각각의 조합된 이점을 얻기 위해 EL 디스플레이를 타일링하기 위한 방법과 함께 패시브 매트릭스 EL 디스플레이의 다수의 라인을 구동하기 위한 방법을 이용하도록 한다. 타일링 및 멀티라인 구동 방법 모두의 사용이, 한번에 패시브 매트릭스 EL 디스플레이를 생산하는데 사용될 수 있음에 따라, 상기 조합은 더 큰 패시브 매트릭스 EL 디스플레이가 적절한 전력 소모로 형성되도록 한다. 그러므로 본 발명은 타일 사이의 경계에서 유해한 휘도 아티팩트를 발생하지 않고, 타일링 또는 멀티라인 어드레싱을 단독으로 적용함으로써 생산될 수 있는 것보다 더 높은 해상도, 더 크고 더 높은 가치의 패시브 매트릭스 EL 디스플레이를 가능하게 한다.

### 도면의 간단한 설명

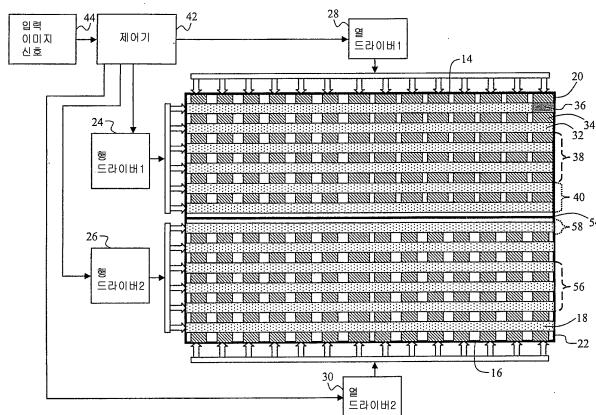

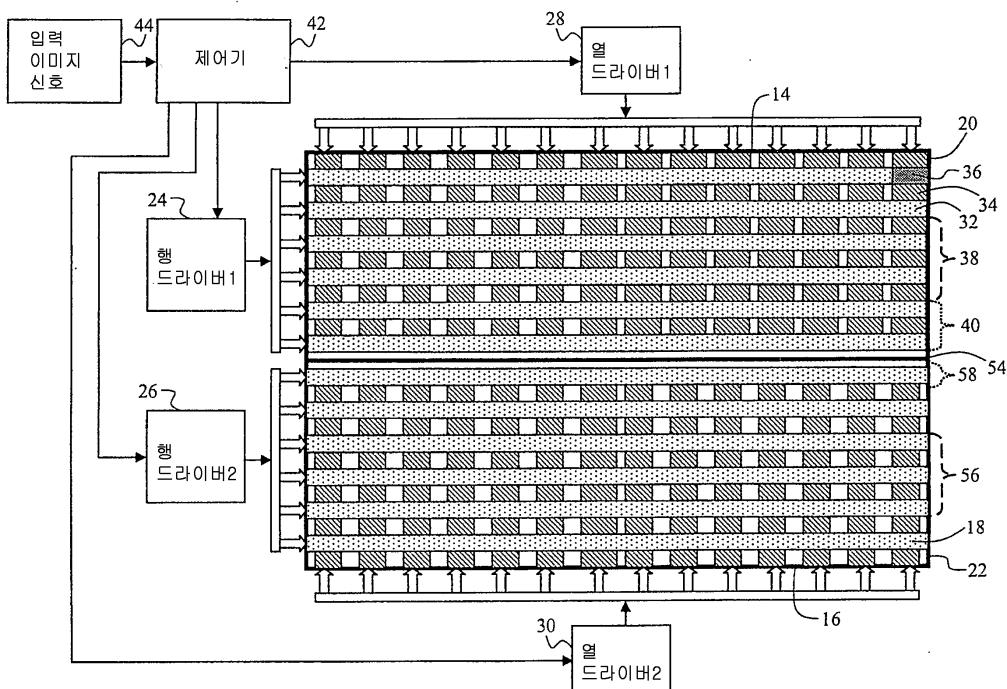

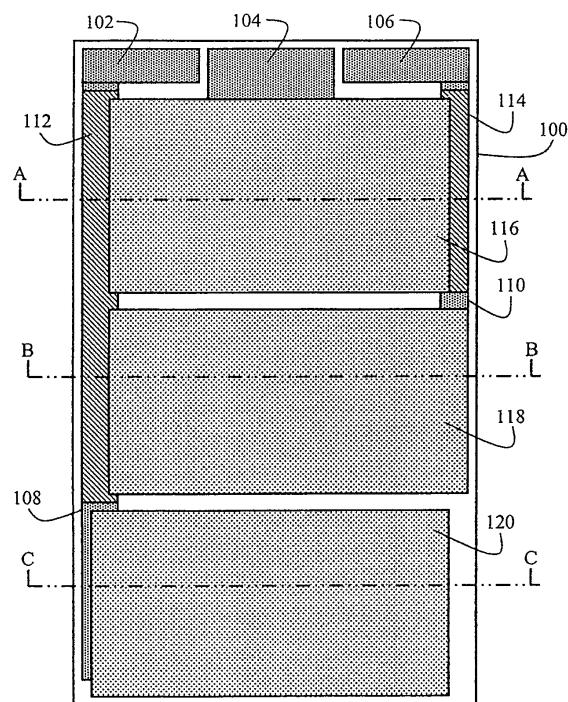

- [0015] 도 1은 본 발명의 일 실시예에 따른 타일형, 패시브-매트릭스, EL 디스플레이에 관한 개략적 도면이고;

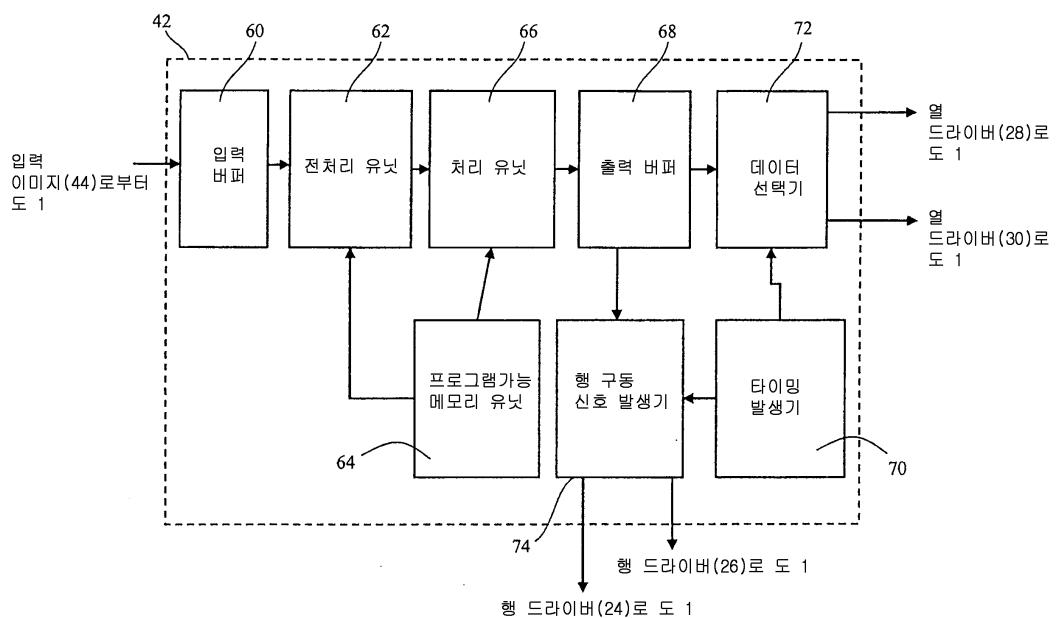

- 도 2는 본 발명의 일 실시예에서 유용한 제어기에 관한 개략적 도면이고;

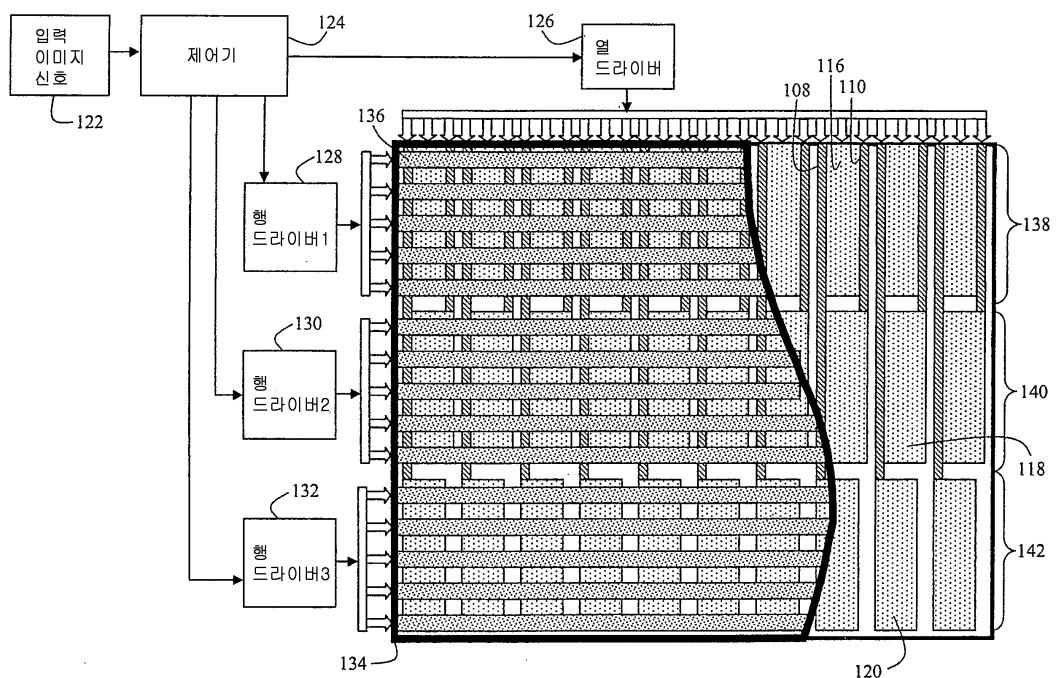

- 도 3은 단일 기판상에 3 개의 EL 타일을 포함하는 타일형, 패시브 매트릭스, EL 디스플레이의 하나의 열의 개략적 도면이고;

- 도 4는 도 3에 도시된 바와 같은 단일 기판 상에 구성된 3 개의 EL 타일을 이용하는 디스플레이에 관한 개략적 도면이고;

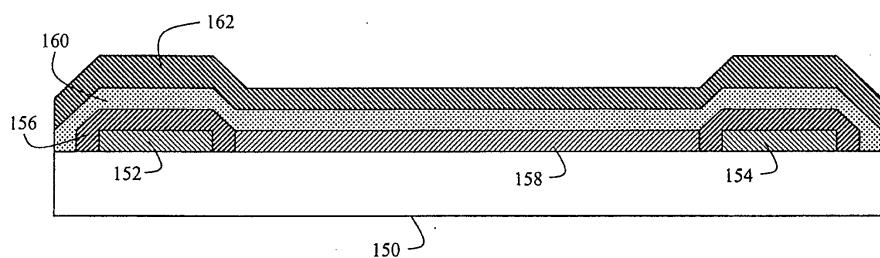

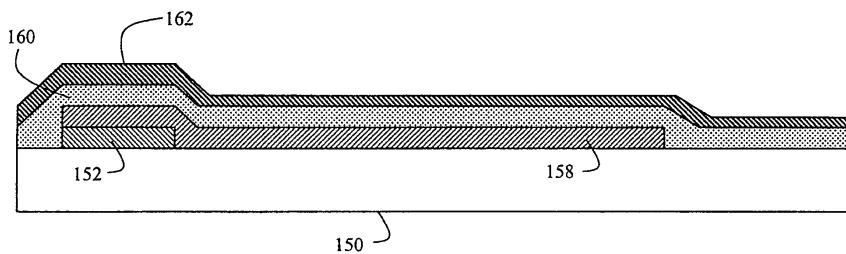

- 도 5a는 도 3의 A-A 선을 따라 취해진 열에 관한 단면도이고;

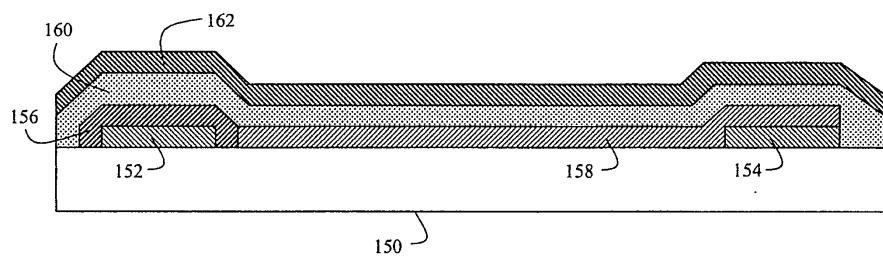

- 도 5b는 도 3의 B-B 선을 따라 취해진 열에 관한 단면도이고;

- 도 5c는 도 3의 C-C 선을 따라 취해진 열에 관한 단면도이고;

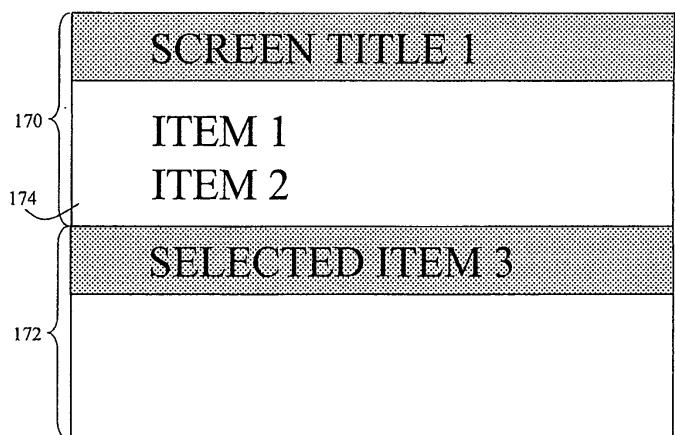

- 도 6은 종래 기술에 언급된 멀티라인 어드레싱을 이용하는 타일형 수동-매트릭스 EL 디스플레이에 관한 시뮬레이션 이미지이고;

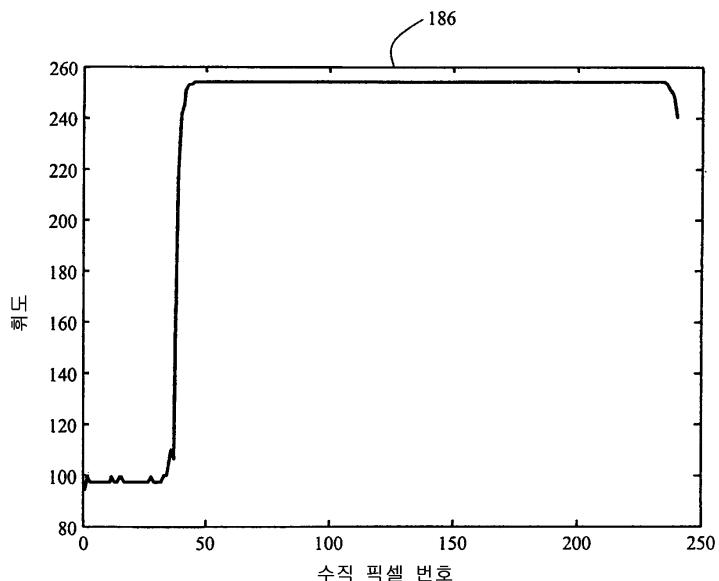

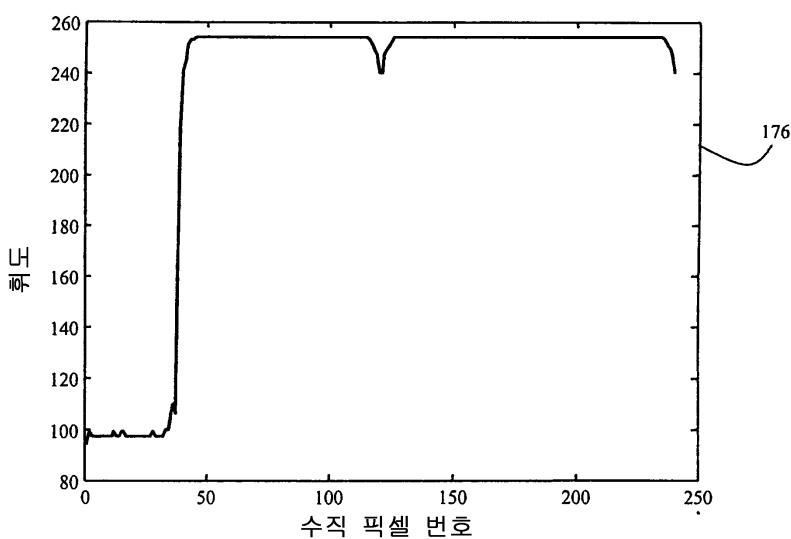

- 도 7은 의도되지 않은 휘도 골(luminance trough)을 나타내는 도 6에서의 이미지의 제 1 열의 휘도 트레이스(trace)이고;

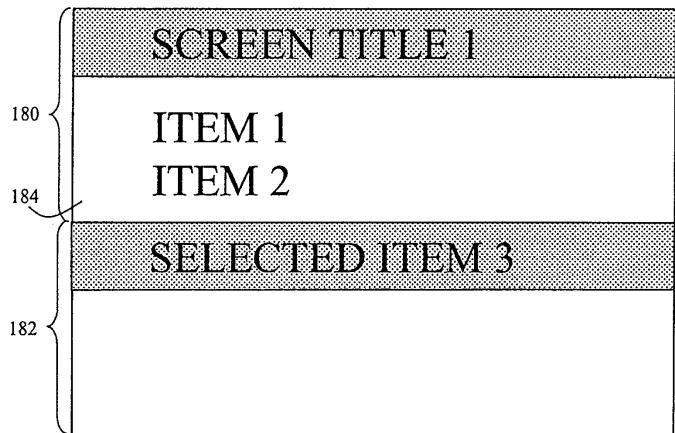

- 도 8은 본 발명의 일 실시예에 따른 멀티라인 어드레싱을 이용하는 타일형 패시브-패트릭스 EL 디스플레이에 관한 시뮬레이션 이미지이고;

- 도 9는 의도되지 않은 휘도 골이 없는 도 8에서의 이미지의 제 1 열의 휘도 트레이스이다.

### 발명을 실시하기 위한 구체적인 내용

- [0016] 본 발명의 타일형, 패시브-매트릭스 EL 디스플레이를 제공함으로써, 타일형 패시브-매트릭스 EL 디스플레이를 구동하기 위해 멀티라인 구동 방법을 사용하는 경우에 발생하는 인접한 타일 사이의 경계에서의 시각적 휘도 아티팩트가 2 개 이상의 인접한 타일 사이의 경계 전체에 걸쳐 분산되고, 2 개 이상의 인접한 타일의 경계 근처에 집중되는 것이 아니라 발광 소자의 다수의 행에 걸쳐 공유된다. 이는 2 개의 이상의 EL 타일(20, 22)을 포함하는, 도 1에 도시된 타일형, 패시브-매트릭스 EL 디스플레이를 적용함으로써 달성될 수 있는데, 각각의 EL 타일(20, 22)은 발광 소자(36)의 행 및 열의 어레이를 포함하며, 각각의 발광 소자(36)는 행 전극(32) 및 열 전극(34)의 직교 어레이 사이에 끼여 있는 발광 층으로부터 형성된다. 각각의 EL 타일(20, 22)은 적어도 하나의 행 드라이버(24, 26)를 더 포함한다. 타일형, 패시브-매트릭스 EL 디스플레이의 추가로 발광 소자(36)의 각각으로부터 발광을 제어하기 위해 행 및 열 전극(32, 34) 사이의 전자의 흐름을 제어하도록 각각의 EL 타일(20, 22)에서 적어도 하나의 행 드라이버(24, 26)의 각각과 함께 동작하기 위한 적어도 열 드라이버(28, 30)를 포함한다. 타일형, 패시브-매트릭스 EL 디스플레이의 2 개의 이상의 EL 타일 내에서, 도 1에서 그룹(38)으로 표시된, 입력 이미지 신호(44)를 수신하고, 기결정된 개수의 발광 소자의 행을 동시에 조명하기 위해 2 개 이상의 EL 타일(20, 22) 내의 2 개 이상의 행 드라이버(24, 26)로 기결정된 개수의 행 구동 신호를 동시에 제공하기 위한 행 드라이버(24, 26) 및 열 드라이버(28, 30)에 결합된, 하나 이상의 제어기(42)를 더 포함한다. 그러나 제어기는, 발광 소자의 행의 그룹(40)으로 도시된 바와 같이, 2 개의 타일(20, 22) 사이의 경계(54)가 조명되려는 경우, 하나의 타일 내의 발광 소자의 동시에 조명된 행의 행 개수가 기결정된 개수보다 적은 예외를 가지며, 각각의 프레임 동안의 발광 소자의 기결정된 개수의 행을 조명한다.

- [0017] "경계(boundary)"란 용어의 사용을 정의하고 경계를 조명하는 것이 무엇을 의미하는지를 정의하는 것은 중요하다. 본 명세서 내에서, "경계"(54)는 2 개의 인접한 행 전극 사이의 영역을 말하며, 이는 이웃하는 EL 타일(20, 22)의 인접한 가장자리 상에 있다. 이웃하는 EL 타일의 인접한 가장자리 상의 2 개의 인접한 행 전극의 각각이 동시에 발광하는 경우 이 경계(54)는 일반적으로 조명될 것이다. 그러나, 이들 2 개의 인접한 행 전극이 조명되는 경계에 대해 동시에 발광한다는 것이 엄격히 요구되지 않는다. 그러나, 이 경계로부터 하나의 타일 내 동시에 조명되는 발광 소자의 행 개수는 경계로부터 발광 소자의 행의 기결정된 수보다 더 적을 필요가 있다. 행 전극의 임의 그룹이 여기되는(energized) 시간 간격은 "필드(field)"로 언급될 것이다. 전통적 패시브 매트릭스 구동 방법에서, 이 시간 간격은 디스플레이의 EL 발광 소자의 커페시턴스를 충전하기 위한 선충전 시간, 발광 소자가 광을 방출하는 활성 시간, 및 발광 소자의 커페시턴스가 방전되는 방전 시간을 일반적으로 포함한다. 그러나, 필드는 발광 소자의 행의 하나의 그룹이 조명되는 시간과 발광소자의 행의 제 2 그룹이 조명되는 시간 사이의 시간만을 포함할 수 있다.

- [0018] 본 발명의 제어기는 도 2에 도시된 바와 같은 구성요소들을 일반적으로 포함할 것이다. 먼저, 제어기는 입력 이미지 신호(44)를 수신하기 위한 소자를 포함한다. 제어기(42)는 입력 이미지 신호의 적어도 일부를 저장하기 위한 입력 버퍼(60)를 더 포함한다. 전형적으로는, 이 입력 버퍼(60)는 이미지 정보의 하나의 전체 프레임까지 저장할 수 있다. 제어기(42)는 전처리 유닛(62)을 포함할 수 있다. 이 전처리 유닛(62)은 인접한 EL 타일(20, 22) 사이의 휘도 출력에서의 차를 보상하기 위해 입력 이미지 신호(44)를 선형화하고 입력 이미지 신호(44)를 보정하는 것과 같은, 몇 개의 잠재적 이미지 조작을 수행할 수 있다. 이와 같은 보정은 앞에서 언급된 바와 같은 기술에 공지되어 있다. 프로그램가능 메모리 유닛(64)은 각각의 EL 유닛의 성능과 관련한 정보를 저장하는데 이용 가능하며, 이는 전처리 유닛(62)이 인접한 EL 타일 상의 휘도 출력에서의 차를 보정하도록 하기 위해 요구된다.

- [0019] 제어기(42)는 타일형, 패시브-매트릭스, EL 디스플레이 내의 다수의 행 전극을 동시에 적절한 신호를 형성하기 위해 전처리된 입력 이미지 신호를 변환하기 위한 처리 유닛(66)을 포함한다. 이들 신호는 행 및 열 드라이버 모두를 구동하기 위한 신호를 포함할 것이다. 이 처리 유닛(66)은 이 처리를 용이하게 하기 위해 프로그램가능 메모리로부터, 샤프닝 커널(sharpening kernel)과 같은, 다른 정보 및 행 구동 값을 획득할 수 있다. 그러므로 제어기(42) 내의 이 처리 유닛(66)은 행 및 열 드라이버로 적용하기 전에 입력 이미지 신호를 처리한다. 이 처리 유닛(66)은 "Passive Matrix Electro-luminescent display system"이란 명칭의 2007년 4월 20일에 출원된 USSN 11/737,786, 또는 Yamazaki 등에 의한 "Image Display Apparatus"란 명칭의 미국 특허 출원 제 10/680,221호에 설명된 바와 같이 멀티라인 어드레싱을 용이하게 하기 위해 샤프닝과 같은 단계를 수행할 수 있으며, 이들 각각은 본 발명에 참고로서 그대로 포함되어 있다. 대안으로는, 처리 유닛(66)은 이미지 분해와 같은, 멀티라인 어드레싱에 적절한 신호를 생성하기 위한 다른 이미지 처리 동작을 수행할 수 있다. Smith 등은 "Multi-line addressing methods and apparatus"란 명칭의 PCT 출원 WO 2006/035246에서 이미지 분해 방법을 설명하였다.

- [0020] 제어기(42) 내의 출력 버퍼(68)는 처리된 데이터를 저장한다. 타이밍 발생기(70)는 행 구동 신호 발생기(74) 및 데이터 선택기(72) 모두에 타이밍 신호를 제공한다. 데이터 선택기(72)는 출력 버퍼(68)로부터 데이터를 획득하고 이를 열 드라이버(28, 30)에 제공한다. 동시에, 행 구동 신호 발생기(74)는 출력 버퍼(68)로부터 데이터를 획득하여 이를 행 드라이버(24, 26)로 제공한다. 이들 구성요소를 적용하면, 제어기(42)는 입력 이미지 신호를 획득하며 가변 구동 신호를 본 발명에 따른 디스플레이를 구동하기 위해 행 및 열 드라이버 모두에 제공할 수 있다.

- [0021] 전형적인 실시예에서, 제어기(42)는 행 드라이버(24, 26) 및 열 드라이버(28, 30)를 제어하여, 기결정된 개수의 행 구동 신호가 각각의 EL 타일 내의 발광 소자의 2 개 이상의 행의 그룹(38, 56)을 조명하기 위해 2 개 이상의 EL 타일(20, 22) 내에 제공될 수 있다. 발광 소자의 행들의 이 그룹이 디스플레이의 타일 각각 내에서 동시에 활성되는 것이 바람직하다. 예를 들어, 디스플레이의 각 타일의 상부에서 시작하면, 발광 소자의 이 기결정된 개수의 행이 활성될 수 있다. 다음 필드에서, 발광 소자의 기결정된 개수의 행의 다른 그룹이 각각의 타일 내에서 활성될 것이다. 발광 소자의 행의 이 다른 그룹은 예를 들어, 하나의 행을 제외한 모든 행에 의해 발광 소자의 행의 제 1 그룹과 겹칠 수 있다. 연이은 필드에서, 발광 소자의 행의 새로운 그룹이 각 타일 아래에서 스캔되는 경우 하나의 행에 의해 간단히 오프셋되며, 각각의 필드 동안 활성될 수 있다. 대안으로는, 다음 그룹은 2 개의 연이은 필드 내에서 조명된 발광 소자의 행들 사이에서 어떠한 겹침도 없거나 또는 중간 정도의 겹침이 있도록 선택될 수 있다. EL 타일(20, 22)의 각각에서 마지막 행 전극이 처음 시간 동안 활성화된다면, 제 1 예외가 발생한다. 이 시간 동안, 발광 소자의 행의 더 작은 그룹은 제 1 타일(20) 내에서 조명될 수 있고, 이전 필드로부터의 발광 소자의 상부 행이 조명되지 않은 예외를 가지며 이전 그룹과 겹친다. 동시에, 제 2 EL 타일

(22)에서의 발광 소자의 제 1 행만이 전형적으로 조명될 것이다. 이는 발광 소자의 행의 하나의 그룹으로부터 휘도가 2 개의 타일 사이의 경계에 걸쳐 휘도를 발생하도록 하여, 그러므로 이 경계에 걸쳐 휘도를 분배한다. 이 예외동안, 제 1 열 드라이버(28) 및 제 2 열 드라이버(30)가 제 1 타일(20)에서의 열 전극 및 제 2 타일(22)에서의 열 전극에 세이브 구동 값을 정확하게 제공한다는 것이 중요하다. 비록, 발광 소자의 활성 행들이 2 개의 타일(20, 22) 사이의 경계를 브리지(bridge)하더라도, 이는 발광 소자의 행들의 하나의, 연속하는 그룹으로 간주될 수 있다. 그러므로, 발광 소자의 다수의 그룹(38, 56)이 타일 내에 완전히 포함되는 경우, 디스플레이에는 각각의 타일 내의 하나의, 발광 소자의 다수의 그룹(38, 56)을 활성화할 것이지만 그러나 발광 소자의 행의 하나의 그룹이 2 개의 인접한 타일의 경계를 브리지할 때마다 발광 소자의 행의 하나의 그룹만을 활성화하는 것이 관측될 수 있다.

[0022] 이런 방식으로 구동되는 경우, 2 개의 타일을 포함하는 디스플레이 상에 동시에 조명된 발광 소자의 행의 전체 개수는 경계가 조명되는 경우 기결정된 행 구동 신호와 동일하다. 예를 들어, 2 개의 인접한 타일 사이의 경계를 브리지하는 그룹은 그룹(58)에서의 발광 소자의 행을 포함할 수 있다. 임의 타일의 하나의 경계만이 전형적으로 동시에 조명될 것임을 주목한다. 그러므로, 타일(22) 아래의 제 3 타일이 있다면, 이는 한 세트의 필드에서 타일(20, 22) 사이의 경계(54)를 조명할 수 있지만 개별 세트의 필드에서 타일(22)과 (도시되지 않은) 제 3 타일 사이의 경계를 조명할 수 있다. 경계의 조명은 발광 소자의 행들의 그룹이 제 1 타일로부터 제 2 타일로 스캔되는 경우 진행할 것이다.

[0023] 전형적으로는, 디스플레이의 하부 행 전극(18)에 의해 구동되는, 발광 소자의 하부 행 및 디스플레이의 상부 행 전극(32)에 의해 구동되는, 발광 소자의 상부 행 상으로 전체 이미지 정보를 제공하는 것이 바람직함에 따라, 제 2 예외는 이와 같은 디스플레이에서 또한 발생할 것이다. 도 1에 도시된 바와 같이, 적어도 2 개의 EL 타일(20, 22) 사이의 경계(54)를 가지는 적어도 2 개의 EL 타일이 있으며, 또한 2 개의 타일(20, 22) 각각은 경계 반대 편에 가장자리(14, 16)를 가짐을 주목한다. 각각의 타일의 대향하는 가장자리를 동시에 조명하는 경우, 적어도 하나의 EL 타일 내의 2 개 이상의 행 드라이버에 제공된 행 구동 신호의 개수는 하나의 타일 내의 기결정된 개수보다 적다. 이 시간 동안, 경계를 조명하는 경우, 동시에 광을 발생하는 발광 소자의 행의 개수는 행 전극에 평행한 타일의 가장자리에 인접하지 않은 발광 소자의 행을 조명하는 경우보다 임의 타일 내에서 더 적을 것이다.

[0024] 이전 예에서, 각각의 타일 내의 적어도 하나의 발광 소자가 각각의 필드 동안 광을 방출하도록 제어됨은 주목할 만하다. 발광 소자의 행의 그룹이 행 전극에 평행한 타일의 가장자리에 인접하지 않은 경우, 발광 소자의 기결정된 개수의 행은 일반적으로 EL 타일 각각 내에서 활성된다. 각각의 타일 내의 발광 소자의 행의 그룹이 행 전극에 평행한 타일의 가장자리 인접한 경우, 발광 소자의 더 적은 개수의 행이 조명될 것이다. 그러나, 이미지를 형성하기 위해 나타내져야 하는 필드의 개수가 감소됨에 따라 각각의 타일에서의 몇 개의 발광 소자가 각 필드 동안 활성되는 사실은 중요하며, 바람직한 조명을 발생하기 위해 필요한 전류는 필요한 필드의 개수에 비례하고 디스플레이의 전력 소모는 필요한 필드의 개수의 제곱에 대체로 비례한다. 그러므로, 각각의 타일 내의 적어도 하나의 발광 소자가 각각의 필드 동안 광을 방출하도록 제어된다는 사실은, 디스플레이의 전력 소모를 감소시킨다.

[0025] 본 발명의 바람직한 실시예 내에서, 행 및 열 드라이버 모두는 행 전극의 임의 그룹(38) 내에서 행 전극에 다른 구동 신호를 제공할 것이다. 다수의 동시에 제어된 행 전극들과 하나의 열 전극의 교차에 의해 정의되는 동시에 조명된 발광 소자의 임의 그룹은 다른 휘도 레벨을 가질 것이다. 그러므로, 복수의 행 전극과 하나의 열 전극의 교차에 대응하는 동시에 활성된 발광 소자의 그룹 내에서 발광 소자의 휘도 레벨은 그룹 내의 다른 발광 소자보다 더 밝다.

[0026] 도 1에 도시된 바와 같이, 타일형 패시브-매트릭스 EL 디스플레이는 하나의 제어기를 포함한다. 이는 전체 시스템의 비용을 절감시키기 위해 종종 바람직할 것이다. 그러나, 이는 요구되지 않는다. 각각의 타일 또는 타일의 서브세트는 각각 자신의 제어기를 가질 수 있다. 그러나, 이들 실시예에서, 추가 제어기에 제공하기 전에 입력 이미지 신호를 버퍼링하고 파싱하기 위해 하나의 제어기를 제공하는 것은 중요할 것이다. 이와 같은 시스템에서, 타일의 서브세트 또는 각각의 타일을 위한 제어기가 전체 디스플레이 내에서 타일의 공간적 위치에 대응하는 입력 이미지 신호의 일부를 인식하는 것이 중요할 뿐만 아니라 제어기는 또한 이웃하는 타일 내의 경계에 가까운 발광 소자의 공간적 위치에 대응하는 입력 이미지 신호의 일부를 인지해야 한다. 이와 같은 시스템에서, 임의 주어진 타일에 대한 제어기는 본 발명에 따른 경계를 적절히 조명하기 위해 이웃하는 타일 내의 경계에 가까운 발광 소자의 공간적 위치에 대응하는 정보를 사용할 수 있다.

- [0027] 한번에 하나를 제조하는, 개별 기판들상에 타일(20, 22)을 형성하거나, 또는 단일 기판상에 타일(20, 22)을 형성할 수 있다. 변화가 종종 개별 EL 타일을 형성하는데 사용될 수 있는 코팅 공정에 존재함에 따라 일반적으로는 단일 기판 상에 2 개 이상의 타일의 적어도 일부를 형성하는 것이 바람직하다. 이 변화는 이웃하는 타일 사이의 휘도차를 발생할 수 있고, 이는 타일 경계와 가시적 아티팩트(visible artifact)를 피하기 위해 어떻게든 보상되어야 한다. 추가로, 타일이 개별 기판들 상에 형성된다면, 최종 디스플레이로 이들 타일을 조립하기 전에 개별 타일을 캡슐화하는 것이 유리할 수 있다. 이와 같은 캡슐화 공정은 전형적으로는 타일의 가장자리로의 접근을 필요로 하고, 이는 종종 타일 경계에서 이웃하는 발광 소자 사이의 거리가 임의 타일 내의 이웃하는 발광 소자들보다 더 멀리 떨어져 있도록 종종 할 것이다. 단일 기판 상에 다수의 타일을 형성하는 것은 이러한 문제를 제거할 수 있다.

- [0028] 단일 기판 상의 다수의 타일의 형성은 다양한 방식으로 수행될 수 있다. 도 3은 다수의 EL 타일을 가지는 디스플레이를 형성하기 위한 기판의 일부를 도시한다. 이 구조의 이해를 돋기 위해, 이 구조를 이용하는 디스플레이의 3 개의 단면도는 디스플레이가 A-A, B-B, C-C 분할선에서 잘려 있는 도 5a, 5b, 5c에 도시되어 있다. 구체적으로는, 이 도면은 이와 같은 기판의 하나의 열을 도시한다. 이 도면은 일정 비율로 그려져 있지 않고 대신에 행의 너비가 이 기판의 특징이 보여지도록 높이보다 훨씬 더 확대되어 있다. 기판은 유리와 같은 베이스 기판(100) 물질로 시작하여 형성될 것이다. 이 베이스 기판상에, 금속 타일 커넥터(108, 110) 뿐만 아니라, 다수의 드라이버 연결부(102, 104, 106)를 제공하도록 패터닝된 금속 층이 형성될 것이다. 구동 연결부(102, 104, 106)는 열 전극의 상부로부터 드라이버로 높은 도전성 금속 트레이스(metal trace)를 제공한다. 이 목적은 열 드라이버의 낮은 저항성 연결부를 열 전극에 제공하는 것이다. 금속 타일 커넥터(108, 110)는 디스플레이 내의 개별 EL 타일로 전류를 제공하기 위한 상대적으로 좁지만 높은 전도성의 트레이스를 제공한다. 절연층(112, 114)은 금속 타일 커넥터(108, 110)의 적어도 하나의 일부 상에 패터닝된다. 이들 절연층은 장치 구조의 다음 층들로부터 금속 타일 커넥터(108, 110)의 적어도 하나의 적어도 일부를 절연한다. ITO(Indium Tin Oxide)와 같은 또 다른 전도성 물질은, 이상적으로 투명한 전도성 물질이 기판상으로 증착된다. 바람직하게는 이 ITO 필름은 다수의 아일랜드(island)를 형성하도록 패터닝되고, 각각의 아일랜드는 금속 타일 커넥터 또는 구동 커넥터 중 하나에만 전기적으로 연결된다. 이 도면에 도시된 바와 같이, 이 하나의 열 내에서, 116, 118 및 120을 포함하는, IOP의 3 개의 아일랜드가 형성된다. 도시된 바와 같이, ITO 아일랜드(116)는 드라이버 연결부(104)에 전기 연결되고 절연층(112, 114)에 의해 금속 타일 커넥터(108, 110)로부터 절연된다. ITO 아일랜드(118)는 금속 타일 커넥터(110)과 전기적으로 접촉하지만 절연층(112)에 의해 금속 타일 커넥터(108)로부터 절연된다. ITO 아일랜드가 도 3에 도시된 열 내에 남아 있도록 패터닝되는 경우 각각의 ITO 아일랜드가 다른 열로부터 절연됨을 주목한다. 이 도면에 도시되지 않았더라도, 전계 발광층은 이 기판상에 형성되며 행 전극의 어레이는 각각의 ITO 아일랜드(116, 118, 120) 상에 패터닝된다. 패시브 매트릭스 EL 디스플레이가 하부발광 디스플레이로서 전형적으로 형성되며 유리 기판을 통해 발광함을 주목한다. 그러므로, 금속 층의 존재는 사용자가 볼 수 있는 발광 소자의 영역을 감소시킬 것이다. 그러나, 임의 열에서의 발광 소자의 서브세트가 시간의 임의 점에서 활성되어, 발광 소자의 열을 구동하는데 필요한 전류가 상대적으로 작도록 패시브 매트릭스 디스플레이는 전형적으로 설계된다. 또한, 패시브 매트릭스 디스플레이에 열 전극을 형성하는 데 전형적으로 사용되는, 금속은 종종 ITO보다 대략 100 배의 도전성을 가진다. 그러므로, 금속 타일 커넥터(108, 110)는 픽셀 영역 내의 ITO 보다 상당히 더 좁을 수 있다. 예를 들어 이들 금속 타일 커넥터는 임의 2 개의 이웃하는 발광 소자들 사이의 가시적 가장자리 사이의 분리의 1/10 보다 작을 수 있다.

- [0029] 도 3에 도시된 바와 같은 타일형 배열을 사용하는 디스플레이는 입력 이미지 신호를 수신하고 행 및 열 드라이버를 제어하기 위해 신호를 생성하는 제어기(124), 열 드라이버(126), 및 다수의 행 드라이버(128, 130, 132)를 도 4에 도시된 바와 같이 포함한다. 그러나, 디스플레이는 3 개의 타일을 포함할 것이고, ITO 아일랜드(116, 118, 120)가 각각 독립적으로 어드레스 가능한 열 전극의 역할을 함에 따라 다수의 독립적으로 어드레스 가능한 행 전극(136)은 이들 어드레스 가능한 열 전극에 수직하여 형성될 것이며 그래서 최종 디스플레이(134)는 행 및 열 전극의 독립적 그룹에 의해 어드레스되는 발광 소자의 3 개의 개별 타일(138, 140, 142)을 포함할 것이다. 도 4에 도시된 바와 같이, 각각의 3 개의 타일(138, 140, 142)은 디스플레이(134) 만큼 넓고 ITO 아일랜드(116, 118, 120) 만큼 높이가 크다.

- [0030] 도 3 및 도 4를 보면, 3 개의 타일을 가지는 타일형 패시브 매트릭스 EL 디스플레이가 하나의 열 드라이버(126)를 가지고 구동되도록 하며, 열 드라이버가 디스플레이의 한 측면에만 부착되어 있음을 중요하다. 이 배열에서, 타일형 패시브 매트릭스 EL 디스플레이의 상부 하부 모두에 열 드라이버를 부착하는 것을 제외하고 유사한 전극 레이아웃을 사용하는 것에 의해 더 큰 디스플레이를 형성하는 것이 가능하다. 이와 같은 배열에서, 디

스플레이이는 도 3에 도시된 바와 같이 동일한 배열에서 금속 타일 커넥터(108, 110)를 사용하는 반면 6 개의 수직으로 배열된 타일을 가지도록 확장될 수 있다. 또한, 이들 금속 타일 커넥터(108, 110) 및 절연층(112, 114)은 이들 각각의 개수에 상관없이, 공통의 패터닝 단계로 각각 패터닝될 수 있다. 추가 금속 타일 커넥터를 형성함으로써 또 다른 타일을 형성하는 것이 가능함을 또한 주목할 수 있다. 도 3이 열의 양 가장자리 상에 하나의 이와 같은 금속 타일 커넥터를 도시하는 반면, 2 개 이상의 금속 타일 커넥터는 열의 양 가장자리에 포함될 수 있고, 기판 당 타일의 개수에 있어 더 증가된다.

[0031] 도 3에 도시된 디스플레이의 단면은 도 5a, 5b 및 5c에 도시되어 있다. 도 5a는 도 5a에서의 단면을 나타낸다. 이 도면에 도시된 바와 같이, 구조는 2 개의 금속 타일 커넥터(152, 154)가 중착되어 있는 기판에서 시작한다. 전형적으로는, 전체 기판 상에 금속 층을 스퍼터링하고 이후 금속의 이들 선을 제외하고 모두를 제거하기 위한 포토리소그래피의 적용은 이들을 중착할 것이다. 이 제 1 타일 내에서, 이들 금속 타일 커넥터(152, 154) 중 어느 것도 전류를 열 전극에 제공하지 않으며 그래서 절연층(156)은 이들 금속 타일 커넥터 상에 중착된다. 한번 더, 이 절연층은 중기 중착 또는 스퍼터링과 같은 코팅 방법을 사용하여 시트(sheet)로서 중착된다. 이 층은 도시된 바와 같은 포토리소그래피를 사용하여 패터닝될 수 있지만 그러나 전체 기판을 덮기 위해 남아있을 수 있다. ITO 층(158)은 중착되고 아일랜드를 형성하기 위해 패터닝되며, 전형적으로는 포토리소그래피를 사용한다. 이 층은 열 전극으로 기능할 것이다. 전계발광층(160)은 적어도 ITO 층(158) 상에 중착된다. 마지막으로, 금속 층(162)은 행 전극을 형성하기 위해 적용된다. 이 부분에 비록 도시되지 않았더라도, 다른 구조들은 다른 분할선(parting line)에 형성될 수 있다. 예를 들어 필러(pillar) 구조는 행전극에 평행하게 형성될 수 있으며, 이는 개별 행 라인을 형성하기 위해 금속 층(162) 내에 분리를 형성하기에 충분히 높이가 높다. 이와 같은 필러구조는 패시브 매트릭스 OLED 디스플레이의 제조에 통상적으로 적용되며 당해 기술에 공지되어 있다.

[0032] 도 5b는 분할선 B-B에서 도 3에 도시된 장치 구조의 단면을 나타낸다. 이 도면은 도 5a의 단면도와 매우 유사하다. 그러나, 2 개의 상당한 차이점이 존재한다. 먼저 절연층(156)이 금속 타일 커넥터(154) 위에서 제거되어 있음을 주목한다. 두 번째로 ITO층(158)은 금속 타일 커넥터(154) 상으로 확장하여 이 금속 타일 커넥터와 ITO의 아일랜드(118) 사이의 전기 연결을 가능하게 한다. 이와 같이, 도 3의 금속 타일 커넥터(110) 상에 제공되어 있는 구동 신호는 이 타일 내의 열 전극을 위한 구동 신호의 역할을 한다.

[0033] 도 5c는 분할선 C-C에서 도 3에 도시된 장치 구조에 관한 단면도를 나타낸다. 이 위치에서, 도 3에서의 제 3 ITO 아일랜드(120)가 임의 다른 금속 타일 커넥터가 아니라 금속 타일 커넥터(108)에 연결되는 것이 중요하다. 도 5c에 도시된 바와 같이, 이 영역 내에 하나의 금속 타일 커넥터(152)만을 중착하고 전체 절연층(156)을 제거하여 이를 수행할 수 있다. 마지막으로, ITO층(158)은 금속 타일 커넥터(152)와 전기 접촉하여 형성될 수 있다.

[0034] 대부분의 디스플레이에서, 다른 이미지 처리가 설명되어 있는 것에 추가로 또한 수행되어야 함을 유의해야 한다. 예를 들어, 미국 특허 출원 10/320,195에 설명되어 있는 바와 같이 RGBW 발광 소자의 어레이를 활용하는 디스플레이에서, 전처리 유닛이 RGB 입력 이미지 신호를 수신하고, 디스플레이 회도를 목표로 하는 것에 대하여 RGB 입력 신호를 선형화하며, 선형화된 RGB 입력 이미지 신호를 선형화된 RGBW 입력 신호로 변환하는 것이 유리하다.

[0035] 본 발명의 실시예 내에서, 제어기(42)는 일반적으로는 하나 이상의 디지털 프로세서일 것이다. 이 제어기(42)는 전용 장치로서 형성될 수 있거나 또는 디스플레이를 이용하는 장치 내에서 다른 디지털 프로세서 내에 내장될 수 있다.

[0036] 행 및 열 드라이버는 일반적으로 제어기(42)로부터 디지털 신호를 수신하고 이 신호를 행 전극(32) 및 열 전극(34)을 따라 그리고 각각의 발광 소자(36)를 통해 전자의 흐름을 제어하는데 적절한 아날로그 전압 또는 전류 신호로 변환하기 위한 몇 가지 방법을 이용할 것이다. 바람직한 실시예에서, 행 또는 열 드라이버는 다른 드라이버가 각각의 전극을 따르는 전류의 흐름을 단순히 활성 또는 불활성 하기 위한 능력을 제공하는 동안 시-다중화(time-multiplexed) 신호를 제공할 것이다. 다른 바람직한 실시예에서, 행 또는 열 드라이버 중 적어도 하나는 행 또는 열 전극의 각각을 통해 전압 또는 전류 흐름의 아날로그 제어를 제공할 것이다.

[0037] 타일형 패시브 매트릭스 EL 디스플레이에는 한 쌍의 전극 사이의 어드레스가능 소자의 2 차원 어레이를 형성하기 위해 사용될 수 있는 임의 전계발광 디스플레이일 수 있다. 이들 장치는 Tang 등에 의해 1988년 9월 6일에 발행된, US 4,769,292, 및 VanSlyke 등에 의해 1991년 10월 29일에 발행된 US 5,061,569를 포함하는, 종래 기술에 설명된 바와 같이 유기 정공 수송, 유기 발광 및 유기 전자 수송 층을 전형적으로 포함하는, 순수 유기 소분자 또는 중합체성 재료를 이용하는 전계발광층(160)을 포함할 수 있다. 전계 발광층(160)은 대안으로 Bawendi 등에 의해 2005년 3월 1일에 발행된 US 6,861,155에 설명된 발광층과 같은, 무기 발광층과 함께 유기 전공 수송 및

전자 수송층을 전형적으로 포함하는, 유기 및 무기 재료의 조합으로부터 형성될 수 있다. 대안으로는, 전계발광층(160)은 "Quantum Dot Light Emitting Layer"란 명칭의, 2005년 9월 14일 출원된, 동시 계류중인 USSN 11/226,622에 설명된 장치와 같은 완전히 무기 재료로부터 형성될 수 있다.

[0038] 디스플레이의 재료의 어레이로부터 형성되는, 열 및 행 전극을 더 이용할 수 있다. 전형적으로, 열 전극보다, 동시에 빛나는 더 많은 발광 소자에 전류를 전달하는 행 전극은 금속으로 형성될 것이다. 흔히 공지되어 있고 적용된 본 발명의 금속 전극(32, 34) 및 금속 타일 커넥터(108, 110)는 은 또는 알루미늄으로부터 전형적으로 형성되지만, 구리와 같은 다른 도전성 물질로부터 형성될 수 있다. 전극이 캐소드로 기능하는 경우, 이들 금속은 낮은 일함수 금속과 합금될 수 있거나 또는 낮은 일함수 전자 주입층과 함께 사용될 수 있다. 행 또는 열 전극 중 적어도 하나는 투명하거나 또는 반투명한 물질로 형성되어야 한다. 적절한 전극은 은으로 된 얇은 층과 같은, 매우 얇은 금속 또는 ITO 및 IZO와 같은 금속 산화물을 포함한다. 이들 전극의 저항성을 감소시키기 위해, 추가적인 불투명한 전도성 버스 바(bus bar)는 이들 전극과 전기적으로 접촉하며 형성될 수 있다.

[0039] 기판은 다양한 종류의 물질로 또한 형성될 수 있다. 투명한 또는 반투명한 전극이 기판 위에 직접적으로 형성되는 경우, 기판이 유리 또는 투명 플라스틱과 같은, 투명한 물질로부터 형성되는 것이 바람직하다. 다른 방법으로, 기판은 투명하거나 또는 불투명할 수 있다. 비록 도시되지 않았더라도, 이와 같은 디스플레이에는 기계적인, 산소, 및 습기 보호를 위해 추가 층을 일반적으로 포함할 것이다. 이런 유형의 보호를 제공하는 방법은 당해 기술에 공지되어 있다. 기판으로부터 가장 먼 전극의 패터닝을 가능하게 하는 패시브 매트릭스 OLED 디스플레이의 제조 동안 보통 이용되는 필러와 같은, 기계적 구조는 또한 본 발명의 도면에 도시되어 있지 않다.

[0040] 비록, 현재 발명이 EL 디스플레이에 대해 구체적으로 설명되고 있더라도, 본 발명의 방법은 대안의 디스플레이 기술로 유용하게 활용될 수 있다. 특히 필드 방출 또는 표면-전도형-전자-방출 디스플레이를 포함하는, 최상의 발광형 디스플레이 기술에 전형적인, 전류의 흐름을 필요로 하는 임의 디스플레이 기술은 본 발명의 태양으로부터 유리할 수 있다. 본 발명에 논의된 바와 같이 다수의 행 전극의 다수의 그룹을 동시에 구동하기 위한 능력이 디스플레이의 커패시턴스를 충전하고 방전하는 것과 관련된 손실을 감소시킴에 따라 개별 발광 소자를 켜고 끄는 순환하는 경우 용량성 손실을 제공하기에 충분히 얇은 셀을 가지는 디스플레이 기술에서 더 많은 이점을 가질 것이다. 본 발명 내에서 용량성 손실은 피크 순간 전류로 감소되고, 그러므로 멀티 라인의 다수 그룹이 설명된 것과 같이 구동되지 않았다면 가능한 것보다 더 긴 시간 주기 동안 각각의 발광 소자가 발광하기 때문에, 임의 발광 소자로부터 바람직한 휘도를 생성하기 위해 필요한, 임의 커패시터에 걸친 피크 순간 전압은 감소된다.

[0041] 본 발명의 영향을 설명하기 위해, 다음의 예들을 제공한다.

[0042] 예 1 : 비교예

[0043] 이 예에서, 행 전극(32)과 열 전극(34)을 각각 가지는, 2 개의 타일(20, 22)을 가지는 디스플레이를 가정한다. 또한, 각각의 타일이 자신의 행 드라이버 및 열 드라이버를 가진다고 가정한다. 또한, 각각의 타일은 자신의 제어기(42)를 가지고 각각의 제어기는 타일(20, 22) 내에 발광 소자(36)의 공간 위치에 대응하는 입력 이미지 신호(44)의 일부만을 수신한다고 가정한다. 그러므로, 2 개의 제어기는 인접한 타일의 발광 소자의 공간 위치에 대응하는 입력 이미지 신호에서 발생하는 입력 이미지 신호 내의 휘도에서의 변화에 반응할 수 없다. 이 설계는 종래 기술의 실시예와 일치하며, 입력 이미지 신호는 파싱되며 렌더링(rendering)을 위해 각각의 타일에 전달된다.

[0044] 입력 이미지 신호(44)는 흰 배경에 2 개의 어두운 회색 바(bar)를 렌더링하기 위한 정보를 포함할 것이다. 어두운 회색의 바는 문자(text)의 라인을 각각 포함할 것이고 제 2의 어두운 회색의 바는 2 개의 인접한 EL 타일 사이의 경계 아래의 소수의 행이 바로 시작할 것이다. 그러므로, 2 개의 타일(20, 22) 사이의 경계(54) 매우 가까이에 갑작스런 휘도 변화가 있을 것이다. 이 예에서, 2 개의 제어기의 각각에서의 처리 유닛이 멀티라인 어드레싱된 EL 디스플레이 상에 입력 이미지 신호를 디스플레이에 제공하기 위해 처리 단계 동안 입력 이미지 신호(44)를 샤프닝한다고 가정한다. 행 및 열 드라이버가 한번에 다수의 행 전극을 활성화시킴으로써, 한번에 이 처리된 입력 이미지 신호 한 행을 디스플레이한다고 가정한다. 이 예에서, 샤프닝 단계는 각각의 제어기에 의해 개별적으로 완료될 것이며, 입력 이미지 신호에 요소(element) -1, 2, 1, -2, 0, -18, -9, -18, -2, 1, 2, -1을 포함하는 15 요소 커널(element kernel)을 적용한다. 이 이미지는 행 드라이버가 동시에 9 개의 행 전극을 각각 활성화하고 전류의 0.16, 0.32, 0.52, 0.200, 0.400, 0.200, 0.052, 0.032, 0.16 비율이 9 개의 행 전극의 각각을 통해 흐르도록 디스플레이될 것이다. 이 방식으로, 디스플레이에는 한 번에 이미지 9 행을 그린다. 또한, 정확하게 9 개의 행 전극은 매 필드 동안 각각의 타일 내에서 활성화되며, 그러므로 이 실시예는 본 발명의 제 1 예 외를 이용하지 않는다. 각각의 이미지의 적절한 비율이 동시에 각 타일 내에 그려진다고 가정한다.

[0045] 도 6에 결과 이미지가 도시되어 있다. 이 이미지는 제 1 타일 상에 렌더링된 제 1 부분(170) 및 제 2 타일 상에 렌더링된 제 2 부분(172)을 포함한다. 종래 기술의 시스템이 이웃하는 타일 상의 내용을 알지 않고, 2 개의 타일 상의 입력 이미지 신호의 정보를 독립적으로 렌더링하기 때문에, 부정확한 휘도의 라인(174)이 2 개의 타일 사이의 경계 가까이에 렌더링된다. 시야 상태(viewing condition) 및 이미지 내용에 따라, 이 의도되지 않은 라인과 같은, 아티팩트는 꽤 유해하다. 이 오류를 더 설명하기 위해, 도 7은 디스플레이의 제 1 열을 따른 휘도의 트레이스를 나타낸다. 이상적으로는, 휘도는 저레벨에서 수직 픽셀 번호 0부터 40에서 일정하며 고레벨에서 수직 픽셀 번호 41에서 240 상에서 일정하다. 그러나, 이 도면에서, 휘도 트레이스는 2 개의 타일 사이의 경계 가까이에 있는, 의도되지 않은 휘도 골(176)을 가진다. 이 휘도 골은 의도되지 않은 휘도 변화를 형성하며 2 개의 타일 사이의 경계 가까이의 아티팩트를 형성한다.

[0046] 예 2 : 본 발명

[0047] 이 예에서, 타일형 패시브-매트릭스, EL 디스플레이는 본 발명의 실시예에 따라 생성된다. 2 개의 타일을 포함하며, 각각의 EL 타일은 발광 소자의 120 행 및 240 열의 어레이를 포함하고, 각각의 발광 소자는 행 및 열 전극의 직교 어레이 사이에 끼여 있는 발광 층으로부터 형성된다. 타일형 패시브-매트릭스 EL 디스플레이는 각각의 타일 내의 발광 소자의 각각으로부터 광의 방출을 제어하기 위해 각각의 타일 내의 행 및 열 전극 사이의 전자의 흐름을 제어하기 위한 적어도 하나의 행 및 열 드라이버를 포함한다. 타일형 패시브-매트릭스 EL 디스플레이에는 또한 입력 이미지 신호를 수신하고 2 개 이상의 EL 타일 내에 2 개 이상의 행 드라이버에 기결정된 개수의 행 구동 신호를 동시에 제공하기 위한 행 및 열 드라이버에 결합된 하나의 제어기를 포함한다고 가정되며, 2 개의 타일 사이의 경계가 조명되는 경우, 행 구동 신호의 개수가 하나의 타일 내의 기결정된 개수보다 적은 제 1 예외를 가진다.

[0048] 그러므로, 이 디스플레이는 각각의 타일이 이웃하는 EL 타일 내의 발광 소자의 공간 위치에 대응하는 입력 이미지 신호에 좌우되도록 구동된다는 것을 제외하고는, 이전 예의 디스플레이와 유사하다. 또한, 가끔은, 이미지의 일부는 이전 예의 경우와 같이, 매 필드 동안 독립적인 각각의 EL 타일 내에 9 개의 활성 행 전극을 가지는 것과 대조적으로, 필드의 서브세트에서 2 개의 타일 사이에 9 개의 활성 행 전극을 공유하여 디스플레이된다. 2 개의 타일 사이의 경계가 조명되는 경우 동시에 구동되는 활성 행의 개수가 임의 타일 내보다 적은 것을 제외하고는, 동일한 샤프닝 및 행 구동이 계획된다.

[0049] 결과 이미지가 도 8에 도시되어 있다. 이 이미지는 제 1 타일 상에 렌더링된 제 1 부분(180) 및 제 2 타일 상에 렌더링된 제 2 부분(182)을 가진다. 비교 예에서 존재하는 아티팩트가 본 발명의 이 실시예에 나타나지 않도록, 상부 환색 필드의 휘도가 경계(184)에서 일정함을 주목한다. 휘도 아티팩트가 존재하지 않음을 더 설명하기 위해, 도 9는 디스플레이의 제 1 열에 따른 휘도의 트레이스를 도시한다. 이상적으로는, 휘도는 저 레벨에서 수직 픽셀 번호 0에서 40 상에서 일정하며 고 레벨에서 수직 픽셀 번호 41에서 240에서 일정하다. 이 도면에서 나타난 바와 같이, 휘도는 수직 픽셀 번호 40과 적어도 230에서 사이에서 일정하다. 그러므로, 도 7에 나타나 있는 의도되지 않은 휘도 골은 이 실시예의 2 개의 타일 사이의 경계의 위치(186) 가까이에서 나타나지 않는다.

## 부호의 설명

- [0050] 14 경계 반대편 가장자리

- 16 경계 반대편 가장자리

- 18 하부 행 전극

- 20 EL 타일

- 22 EL 타일

- 24 행 드라이버

- 26 행 드라이버

- 28 열 드라이버

- 30 열 드라이버

- 32 행 전극

- 34 행 전극

- 36 발광 소자

- 38 발광 소자의 2 개 이상의 행의 그룹

- 40 발광 소자의 그룹

- 42 제어기

- 44 입력 이미지 신호

- 54 경계

- 56 발광 소자의 2 개 이상의 행의 그룹

- 58 인접한 타일 사이의 경계를 브리지하는 그룹

- 60 입력 버퍼

- 62 전처리 유닛

- 64 프로그램가능 메모리 유닛

- 66 처리 유닛

- 68 출력 버퍼

- 70 타이밍 발생기

- 72 데이터 선택기

- 74 행 구동 신호 발생기

- 100 기판

- 102 드라이버 연결부

- 104 드라이버 연결부

- 106 드라이버 연결부

- 108 금속 타일 커넥터

- 110 금속 타일 커넥터

- 112 절연층

- 114 절연층

- 116 ITO의 아일랜드

- 118 ITO의 아일랜드

- 120 ITO의 아일랜드

- 122 입력 이미지 신호

- 124 제어기

- 126 열 드라이버

- 128 행 드라이버

- 130 행 드라이버

- 132 행 드라이버

- 134 디스플레이

- 136 행 전극

- 138 EL 타일

140 EL 타일

142 EL 타일

150 기판

152 금속 타일 커넥터

154 금속 타일 커넥터

156 절연층

158 ITO 층

160 전계발광 층

162 금속 층

170 제 1 부분

172 제 2 부분

174 라인 아티팩트

176 의도되지 않은 휘도 골

180 제 1 부분

182 제 2 부분

184 경계

186 경계 위치

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5a

## 도면5b

도면5c

도면6

도면7

도면8

도면9