(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6066392号

(P6066392)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 06 F 12/16 (2006.01)G 11 C 17/00 614

G 11 C 17/00 601C

G 11 C 17/00 601D

G 06 F 12/16 310A

請求項の数 13 外国語出願 (全 10 頁)

(21) 出願番号 特願2010-134480 (P2010-134480)

(22) 出願日 平成22年5月26日 (2010.5.26)

(65) 公開番号 特開2010-277685 (P2010-277685A)

(43) 公開日 平成22年12月9日 (2010.12.9)

審査請求日 平成25年5月27日 (2013.5.27)

審判番号 不服2015-106 (P2015-106/J1)

審判請求日 平成27年1月5日 (2015.1.5)

(31) 優先権主張番号 12/472,153

(32) 優先日 平成21年5月26日 (2009.5.26)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ボイズ, サウス フェデ

ラル ウエイ 8000

(74) 代理人 100092093

弁理士 辻居 幸一

(74) 代理人 100082005

弁理士 熊倉 賢男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100086771

弁理士 西島 孝喜

(74) 代理人 100109070

弁理士 須田 洋之

最終頁に続く

(54) 【発明の名称】電力損失を制御するための方法及びデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性メモリ(NVM)デバイスであって、

データを格納するためのNVMアレイと、

制御された電力遮断コマンドをホストコントローラから受信するための、前記NVMア

レイに結合されたコマンド・インターフェースと、

前記NVMデバイスがバックグラウンド動作を実施しているかどうかを示す情報を格納するための、前記NVMアレイに結合された状況レジスタ・ユニットと、を含み、

前記情報は前記制御された電力遮断コマンドが受信された後前記ホストコントローラによって読まれるようになっており、かつ前記NVMデバイスが前記バックグラウンド動作を実施していると判断される場合に、供給電力の損失より前に前記制御された電力遮断コマンドに応答して前記NVMデバイスが前記バックグラウンド動作を安全に一時停止するようになっており、

前記NVMデバイスは前記供給電力が再供給された後前記停止されたバックグラウンド動作を完了するようになっており、かつ前記コマンド・インターフェースは、前記制御された電力遮断コマンドに応答して、状況レジスタを通してメモリ肯定応答を前記ホストコントローラに送るように構成されているデバイス。

## 【請求項 2】

前記バックグラウンド動作は、前記供給電力の損失に先立って、安全に自動的に一時停止されることを特徴とする、請求項1に記載のデバイス。

10

20

**【請求項 3】**

前記バックグラウンド動作は、メモリアレイのリフレッシュ又はウェアアレベリング・アルゴリズムをさらに含むことを特徴とする、請求項1に記載のデバイス。

**【請求項 4】**

前記状況レジスタ・ユニットは、前記NVMデバイスが前記バックグラウンド動作を安全に一時停止又は完了したかどうかを示す情報を格納するように構成されたことを特徴とする請求項1に記載のデバイス。

**【請求項 5】**

前記状況レジスタ・ユニットは、前記供給電力の復旧時に前記一時停止されたバックグラウンド動作を再開する際に前記NVMデバイスによって用いられる情報を格納するように構成されたことを特徴とする、請求項1に記載のデバイス。 10

**【請求項 6】**

データ処理デバイスであって、

1つ又はそれ以上のプロセッサコアを有する処理ユニットと、

不揮発性メモリ(NVM)デバイスを有する、前記処理ユニットに結合されたシステムメモリとを含み、前記不揮発性メモリ(NVM)デバイスは、

データを格納するためのNVMアレイと、

制御された電力遮断コマンドを前記処理ユニットから受信するための、NVMアレイに結合されたコマンド・インターフェースと、

前記NVMデバイスがバックグラウンド動作を実施しているかどうかを示す情報を格納するための、前記NVMアレイに結合された状況レジスタ・ユニットと、 20

を含み、

前記情報は前記制御された電力遮断コマンドが受信された後前記処理ユニットによって読みられるようになっており、かつ前記NVMデバイスが前記バックグラウンド動作を実施していると判断される場合に、供給電力の損失より前に前記制御された電力遮断コマンドに応答して前記NVMデバイスが前記バックグラウンド動作を安全に一時停止するようになっており、

前記NVMデバイスは前記供給電力が再供給された後前記停止されたバックグラウンド動作を完了するように構成されており、前記コマンド・インターフェースは、前記制御された電力遮断コマンドに応答して、状況レジスタを通してメモリ肯定応答を前記処理ユニットに送るように構成されていることを特徴とするデータ処理デバイス。 30

**【請求項 7】**

前記バックグラウンド動作が安全に完了された又は一時停止された後に前記NVMデバイスから前記供給電力を除去するための、前記処理ユニットに結合された電力管理ユニットをさらに含むことを特徴とする、請求項6に記載のデータ処理デバイス。

**【請求項 8】**

前記データ処理デバイスは、

無線信号を受信するための、前記処理ユニットに結合された送受信機をさらに含む無線通信デバイスであることを特徴とする、請求項6に記載のデータ処理デバイス。 40

**【請求項 9】**

ホストコントローラを用いて、制御された電力遮断コマンドをメモリデバイスに出力し、

ホストコントローラを用いて、前記メモリデバイスの状況レジスタ・ユニットを読み取り、

前記メモリデバイスがバックグラウンド動作を実行しているかどうかを示す情報を格納する、前記メモリデバイスの状況レジスタ・ユニットの読み取りに基づいて、ホストコントローラを用いて、前記メモリデバイスがバックグラウンド動作を実行しているかどうかを判断し、

前記メモリデバイスが前記バックグラウンド動作を実施していると判断される場合に、コマンド・インターフェースを用いて、前記制御された電力遮断コマンドに応答して状況 50

レジスタを通してメモリ肯定応答を前記ホストコントローラに送ると共に、メモリデバイスを用いて、前記制御された電力遮断コマンドに応答して前記バックグラウンド動作を安全に一時停止し、

電力管理ユニットを用いて、安全に電力供給を除去し、

その後、電力管理ユニットを用いて、前記メモリデバイスに前記供給電力を再供給し、

前記メモリデバイスへの供給電力の再供給の後、メモリデバイスを用いて、停止されたバックグラウンド動作を完了する、ステップを含むことを特徴とする、方法。

#### 【請求項 10】

前記「ホストコントローラを用いて、制御された電力遮断コマンドをメモリデバイスに出力する」ステップは、電力損失イベントの検出に応答して、前記ホストコントローラを用いて、制御された電力遮断コマンドをメモリデバイスに出力するステップを含むことを特徴とする、請求項 9 に記載の方法。

10

#### 【請求項 11】

前記「コマンド・インターフェースを用いて、前記制御された電力遮断コマンドに応答して状況レジスタを通してメモリ肯定応答を前記ホストコントローラに送ると共に、メモリデバイスを用いて、前記制御された電力遮断コマンドに応答して前記バックグラウンド動作を安全に一時停止する」ステップは、前記制御された電力遮断コマンドに応答して前記メモリデバイスから前記コントローラにおけるメモリ肯定応答を受信するステップ、又は、前記バックグラウンド動作を安全に一時停止する前又は該バックグラウンド動作を完了する前に一定の時間待つステップを含むことを特徴とする、請求項 9 に記載の方法。

20

#### 【請求項 12】

前記「前記メモリデバイスがバックグラウンド動作を実行しているかどうかを示す情報を格納する、前記メモリデバイスの状況レジスタ・ユニットの読み取りに基づいて、ホストコントローラを用いて、前記メモリデバイスがバックグラウンド動作を実行しているかどうかを判断する」ステップにおいて、前記メモリデバイスが前記バックグラウンド動作を実行していないと判断された場合、電力管理ユニットを用いて、前記供給電力が安全に除去されることを特徴とする、請求項 9 に記載の方法。

#### 【請求項 13】

前記メモリデバイスは、前記メモリデバイスの前記状況レジスタ・ユニットを読み取るまで、前記バックグラウンド動作を認識する前記ホストコントローラなしで、前記バックグラウンドタスクを実施するように構成されている、請求項 9 に記載の方法。

30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の実施形態は、一般に、不揮発性メモリを有するデバイスにおける電力損失を制御する分野に関する。

##### 【背景技術】

##### 【0002】

コンピュータ、携帯電話、スマートフォン、携帯情報端末（PDA）及び他の電子デバイスは、制御可能な電力を失う場合がある。例えば、バッテリ電源が徐々に放電して、デバイスを遮断するレベルに達することがある。こうしたデバイス内に配置された不揮発性メモリは、コントローラが認識することなく開始され実行されるバックグラウンド動作を実施することができる。バックグラウンド動作の例は、電圧応力又は温度応力に起因するセルレベルのドリフトから回復するように、メモリアレイのコンテンツが周期的に書き換えられる、メモリアレイのリフレッシュである。別の例は、内蔵されたウェアレベリング・アルゴリズムの実装である。

40

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

電子デバイスにおける電力損失に対する従来の手法は、結果として電力供給の除去をも

50

たらし、このことは、バックグラウンドタスクの完了を中断し、危険にさらす。後に電力が復旧されたとき、バックグラウンド動作の中止がデータの完全性の問題又は信頼性の問題をもたらすことがある。

#### 【課題を解決するための手段】

##### 【0004】

電力損失を制御するための方法及びデバイスがここに説明される。1つの実施形態において、この方法は、コントローラにより制御された電力遮断コマンドを出すことを含む。この方法は、メモリデバイスがバックグラウンド動作を実行しているかどうかを判断することを含む。この方法は、メモリデバイスがバックグラウンド動作を実行している場合に、バックグラウンド動作を安全に一時停止(suspend)すること、又は、バックグラウンド動作を完了することを含む。この方法は、供給電力を安全に除去することを含む。

10

##### 【0005】

供給電力が後に復旧されたときに、一時停止されたバックグラウンド動作を再開することができる。バックグラウンド動作は、メモリアレイのリフレッシュ又はウェアレベリング・アルゴリズムを含むことができる。一時停止されたバックグラウンド動作を安全に完了し又は再開することにより、従来の手法と比較してメモリの信頼性及びデータの完全性が向上する。

##### 【0006】

本発明の1つ又はそれ以上の実施形態は、例として示されるものであり、同様の参照番号が類似の要素を示す添付図面の図に制限されるものではない。

20

#### 【図面の簡単な説明】

##### 【0007】

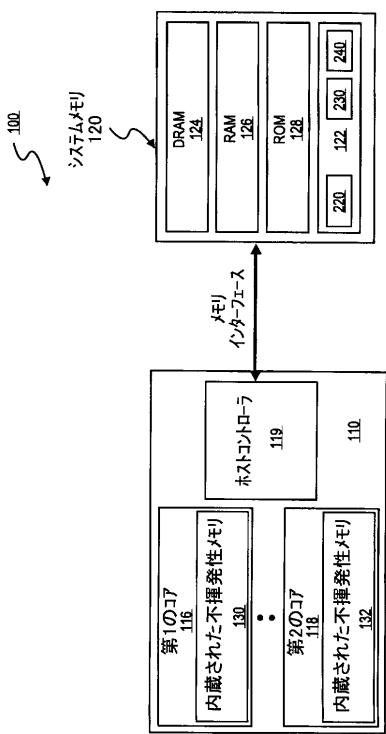

【図1】1つの実施形態による、制御可能な電力損失対処能力を有するデータ処理デバイスを示す。

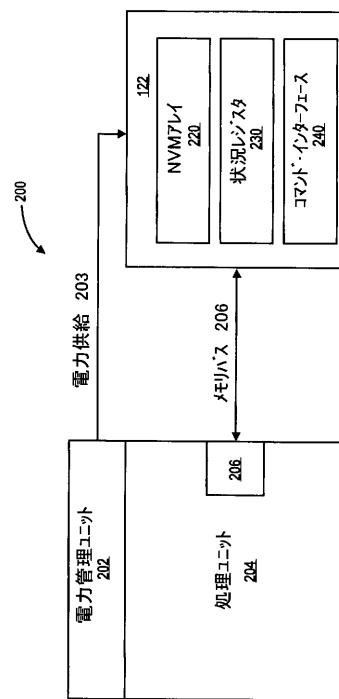

【図2】1つの実施形態による、電力管理ユニットに結合された不揮発性メモリ(NVM)デバイスを示す。

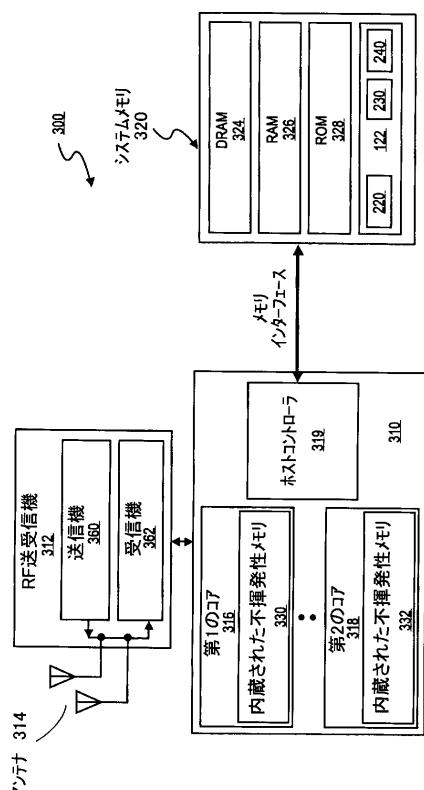

【図3】1つの実施形態による、制御可能な電力損失対処能力を有する無線通信デバイスを示す。

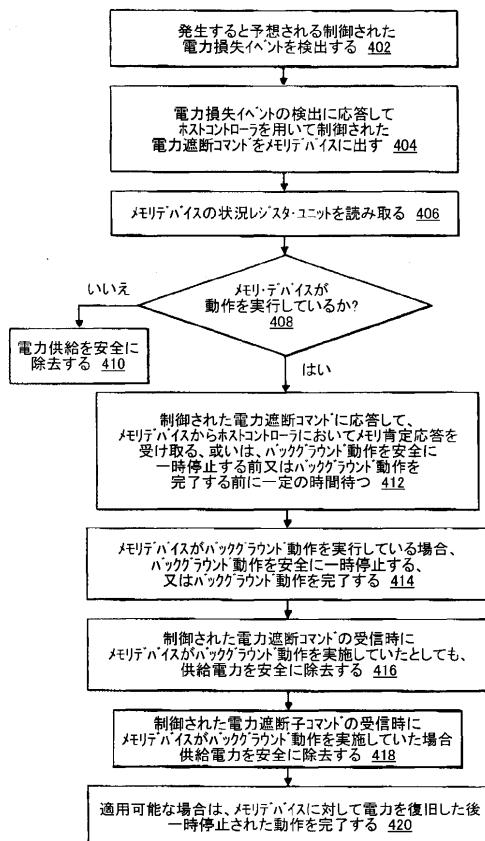

【図4】1つの実施形態による、制御された電力遮断シーケンスを実行するための方法を示す。

30

#### 【発明を実施するための形態】

##### 【0008】

図1は、1つの実施形態による制御可能な電力損失対処能力(controlable power loss capability)を有するデータ処理デバイスを示す。データ処理デバイス100は、第1及び第2のプロセッサコア116及び118を有する処理ユニット110、ホストコントローラ119、並びに処理ユニット110に結合されたシステムメモリ120を含む。ホストコントローラ119は、処理ユニット110の内部にあっても、又は処理ユニット110の外部にあってもよい。第1及び第2のプロセッサコア116及び118は、それぞれ、内蔵された不揮発性メモリ130及び132を含む。システムメモリ120は、不揮発性メモリ(NVM)デバイス122及び種々の形式のメモリ(例えば、DRAM124、RAM126、ROM128)を含む。NVMデバイス122は、バックグラウンド動作を実施し、データを格納するための不揮発性メモリアレイ120を含む。NVMデバイス122はまた、1つ又はそれ以上のレジスタを有する状況レジスタ・ユニット230と、コマンド・インターフェース240とを含む。NVMデバイス122は、図2と併せてより詳細に説明される。

40

##### 【0009】

図2は、1つの実施形態による、電力管理ユニット202に結合されたNVMデバイス122を示す。NVMデバイス122は、バックグラウンド動作(例えば、メモリアレイのリフレッシュ、内蔵されたウェアレベリング・アルゴリズム)を実施し、データを格納

50

するための不揮発性メモリ（NVM）アレイ220（例えば、NANDフラッシュ技術、 NORフラッシュ技術、PCM技術に基づいた）を含む。NVMデバイス122はまた、1つ又はそれ以上のレジスタを有する状況レジスタ・ユニット230と、コマンド・インターフェース240とを含む。コマンド・インターフェース240は、NVMアレイ220に結合され、処理ユニット204に結合された又はその内部に配置されたコントローラ206から、制御された電力遮断コマンドを受信する。コントローラ206は、メモリバス208を介してNVMデバイス122に結合される。コマンド・インターフェースは、有限状態機械として実装することができ、モードレジスタ（例えば、状況レジスタ・ユニット230）、又は、NVMアレイ220内にマッピングされた1組のレジスタと関連付けられたオーバーレイウィンドウ内のレジスタを含むことができる。NVMアレイ220に結合された状況レジスタ・ユニット230は、NVMデバイス122がバックグラウンド動作を実施しているかどうかを示す情報を格納する。NVMデバイス122は、制御された電力遮断コマンドをコントローラ206から受信したときに、NVMデバイス122がバックグラウンド動作を実施している場合、供給電力の損失に先立って、バックグラウンド動作を安全に一時停止するか、又はバックグラウンド動作を完了する。

#### 【0010】

1つの実施形態において、バックグラウンド動作は、供給電力の損失に先立って、安全に完了されるか、又は自動的に一時停止される。NVMデバイス122は、電力が復旧された後に、一時停止されたバックグラウンド動作を完了するように構成される。

#### 【0011】

1つの実施形態について、状況レジスタは、制御された電力遮断コマンドに応答して、メモリ肯定応答をコントローラ206に与える。コントローラ206がメモリ肯定応答を受信した後、電力管理ユニット202は、NVMデバイス122からの電力の除去に進むことができる。代替的に、コントローラ206が一定の期間内にメモリ肯定応答を受信しなかった場合、コントローラ206は、続けて、電力管理ユニット202にNVMデバイス122から電力を除去させることができる。一定の期間とは、NVMデバイス122が、バックグラウンド動作を一時停止又は完了するのに十分な時間である。状況レジスタ・ユニット230は、NVMデバイス122がバックグラウンド動作を安全に一時停止又は完了したかどうかを示す情報を格納する。状況レジスタ・ユニット230はまた、供給電力の復旧時に一時停止されたバックグラウンド動作を再開する際に、NVMデバイス122によって使用される情報を格納する。幾つかの実施形態において、NVMデバイス122は、NVMデバイス122の状況レジスタ・ユニット230を読み取るまで、バックグラウンド動作を認識するコントローラ206なしで、バックグラウンドタスクを実施する。1つの実施形態において、NVMデバイスは集積回路デバイスである。

#### 【0012】

図3は、1つの実施形態による、制御可能な電力損失対処能力を有する無線通信デバイスを示す。無線通信デバイス300は、該無線通信デバイス300が処理ユニット310に結合された送受信機312も含むことを除いて、データ処理デバイス100に類似している。送受信機312は、アンテナ314で無線信号を受信し、送信機360及び受信機362を含む。この無線の実施形態に示されるように、通信デバイス300は、無線により他の無線通信デバイスと通信するのを可能にするための1つ又はそれ以上のアンテナ構造体314を含む。従って、通信デバイス300は、携帯電話デバイス又は無線ネットワーク内で動作するデバイスとして動作することができる。通信デバイス300の同じプラットフォーム内に配置された無線サブシステムは、RF / 位置空間における異なる周波数帯域と通信する能力を、ネットワーク内の他のデバイスに与える。本発明の範囲は、通信デバイス300が用いることができる通信プロトコルの形式、数、又は周波数によって制限されないことを理解するべきである。

#### 【0013】

実施形態は、アンテナ構造体314を送受信機312に結合して、変調 / 復調に適合させることを示す。一般に、アナログ・フロントエンド送受信機312は、独立型無線周波

10

20

30

40

50

数（R F）の別個の離散又は集積アナログ回路とすることができる、或いは、送受信機 3 1 2 を、1つ又はそれ以上のプロセッサコア 3 1 6 及び 3 1 8 を有するプロセッサに埋め込むことができる。複数のコアにより、コア全体にわたって処理の作業負荷を共有し、ベースバンド機能及びアプリケーション機能を処理することが可能になる。インターフェースを使用して、プロセッサとシステムメモリ 3 2 0 内の記憶装置との間に通信又は情報を提供する。本発明の範囲はこの点に制限されるものではないが、インターフェースは、プロセッサとシステムメモリ 3 2 0 との間にハンドシェイキングを提供するために用いられる制御信号ラインと共に情報を共有するために、シリアルバス及び／又はパラレルバスを含むことができる。

## 【0014】

10

システムメモリ 3 2 0 を随意的に用いて、無線通信デバイス 3 0 0 の動作中、プロセッサによって実行される命令を格納することができ、また、システムメモリ 3 2 0 を用いて、メッセージが無線通信デバイス 3 0 0 によって伝送されるとき、又は実際のデータが伝送されるときの条件のようなユーザデータを格納することができる。例えば、システムメモリ 3 2 0 内に格納された命令を使用して、無線通信を実行し、通信デバイス 3 0 0 のための安全機能を与え、スケジュール調整、e メール、インターネットの閲覧等のユーザ機能を与えることができる。

## 【0015】

システムメモリ 3 2 0 は、1つ又はそれ以上の異なる形式のメモリによって提供することができ、随意的なDRAM、RAM及び／又はROM、並びに、NVMアレイ 2 2 0 を有するNVMデバイス 1 2 2 を含むことができる。NVMアレイ 2 2 0 は、相変化材料を含むことができる。NVMアレイ 2 2 0 は、相変化メモリ（PCM）、相変化ランダム・アクセス・メモリ（PRAM又はPCRAM）、Ovonic Unified Memory（OUM）、又はカルコゲナイト・ランダム・アクセス・メモリ（C-RAM）と呼ぶことができる。NVMアレイ 2 2 0 は、フラッシュメモリ（例えば、NOR、NAND）を含むことができる。

20

## 【0016】

NVMデバイス 1 2 2 はまた、1つ又はそれ以上のレジスタを有する状況レジスタ・ユニット 2 3 0 と、コマンド・インターフェース 2 4 0 とを含む。NVMデバイス 1 2 2 は、図 2 と併せて上記により詳細に説明される。

30

## 【0017】

揮発性メモリ及び不揮発性メモリを、スタッキングプロセスで組み合わせて基板上のフットプリントを減少させ、別個にパッケージ化し、又はプロセッサの上部に配置されたメモリ・コンポーネントと共にマルチチップ・パッケージ内に配置することができる。実施形態はまた、プロセッサコアのうちの1つ又はそれ以上を不揮発性メモリ 3 3 0 及び 3 3 2 と共に埋め込むことも示す。

## 【0018】

図 4 は、1つの実施形態による、制御された電力遮断シーケンスを実行するための方法を示す。方法は、ブロック 4 0 2 において発生すると予想される制御された電力損失イベントを検出することを含む。例えば、メモリデバイス（例えば、NVMデバイス）に結合されたホストコントローラは、バッテリ電源が完全な放電状態に近づいており、よってデバイスの遮断を要求していることを検出することができる。方法は、ブロック 4 0 4 において、電力損失イベントの検出に応答して、ホストコントローラを用いて制御された電力遮断コマンドをメモリデバイスに出すことを含む。方法は、ブロック 4 0 6 において、メモリデバイスの状況レジスタ・ユニットを読み取ることを含む。方法は、ブロック 4 0 8 において、メモリデバイスが動作を実行しているかどうかを判断することを含む。メモリデバイスが動作を実行していない場合には、ブロック 4 1 0 において、電力供給が安全に除去される。

40

## 【0019】

メモリデバイスが動作を実行している場合には、状況レジスタ・ユニットにアクセスし

50

て、動作をいつ完了又は一時停止させるかを決定することができる。方法は、ブロック 4

12において、制御された電力遮断コマンドに応答して、メモリデバイスからホストコン

トローラにおいてメモリ肯定応答を受信すること、或いは、バックグラウンド動作を安全

に一時停止する前又はバックグラウンド動作を完了する前に一定時間待つことを含む。方

法は、ブロック 414において、メモリデバイスがバックグラウンド動作を実行している

場合、バックグラウンド動作を安全に一時停止する又はバックグランド動作を完了するこ

とを含む。方法は、制御された電力遮断コマンドの受信時にメモリデバイスがバックグラ

ウンド動作を実施していたとしても、ブロック 416において、供給電力を安全に除去す

ることを含む。方法は、ブロック 418において、メモリデバイスへの電力を後で復旧す

ることを含む。方法は、ブロック 420において、適用可能な場合には、メモリデバイス

への電力を復旧した後、一時停止されたバックグラウンド動作を完了することを含む。

10

#### 【0020】

詳細な説明の幾つかの部分は、コンピュータメモリ内のデータビット又は2値デジタル

信号の動作のアルゴリズム及び記号的表現に関して表される。これらのアルゴリズム記述

及び表現は、データ処理技術の当業者が、他の当業者にその仕事の内容を伝えるのに使用

する技術とすることができます。

#### 【0021】

アルゴリズムは、ここでは、一般的に、所望の結果をもたらす首尾一貫した行為又は動作

のシーケンスであると考えられる。これらは、物理量の物理的操作を含む。通常、必ず

しもではないが、これらの量は、格納され、転送され、組み合わされ、比較され、他の方

法で操作することができる電気信号又は磁気信号の形態をとる。主として一般的な慣習上

、時として、これらの信号をビット、値、要素、記号、文字、用語、数字等と呼ぶことが

便利であることが分かっている。しかしながら、これら及び類似した用語の全ては、適切

な物理量と関連付けられるべきであり、これらの量に適用される便利なラベルにすぎない

ことを理解すべきである。

#### 【0022】

特にことわらない限り、明細書全体にわたって、「処理」、「コンピューティング」、

「計算」、「判断」等のような用語を用いる説明は、コンピューティング・システムのレ

ジスタ及び/又はメモリ内の、電子量のような物理量として表されるデータを、コンピュ

ーティング・システムのメモリ、レジスタ又は他の情報格納部、伝送又は表示装置内の物

理量として同様に表される他のデータに操作及び/又は変換する、コンピュータ又はコン

ピュータ・システム、或いは類似した電子コンピューティング・デバイスの動作及び/又

はプロセスを示すことが理解される。

#### 【0023】

本発明の実施形態は、本明細書での動作を実行するための装置を含むことができる。装

置は、所望の目的のために特に構築することができ、又はデバイス内に格納されたプログラ

ムによって選択的に作動又は再構成される汎用コンピューティング・デバイスを含むこ

とができる。このようなプログラムは、これらに限定されるものではないが、フロッピー

ディスク、光学ディスク、コンパクトディスク読み取り専用メモリ(CD-ROM)、光

磁気ディスク、読み取り専用メモリ(ROM)、ランダム・アクセス・メモリ(RAM)

、電気的プログラマブル読み取り専用メモリ(E PROM)、電気的消去可能プログラマ

ブル読み取り専用メモリ(EEPROM)、磁気又は光学カード、或いは、電子命令を格

納するのに好適であり、かつ、コンピューティング・デバイスのためにシステムバスに結

合することが可能な他のあらゆる形式の媒体を含む、任意の形式のディスクのような記憶

媒体上に格納することができる。

#### 【0024】

本明細書に提示されるプロセス及び表示は、本質的に、いずれの特定のコンピューティ

ング・デバイス又は他の装置に関連するものではない。種々の汎用システムを、本明細書

での教示に従ったプログラムと共に用いることができ、或いは、所望の方法を実行するた

めに、より特化した装置を構築することが便利であることが分かっている。種々のこれら

40

30

20

10

のシステムのための所望の構造は、下記の説明から明らかになるであろう。さらに、本発明の実施形態は、任意の特定のプログラミング言語を参照して説明されてはいない。種々のプログラミング言語を用いて、本明細書に記載される本発明の教示を実施できることが理解されるであろう。さらに、本明細書に説明される動作、能力及び特徴を、ハードウェア（離散回路又は集積回路）及びソフトウェアの任意の組み合わせを用いて実施できることを理解すべきである。

#### 【0025】

上記の説明は、限定ではなく、例示を目的としていることを理解すべきである。当業者には、上記の説明を読んで理解するときに、多くの他の実施形態が明らかになるであろう。従って、本発明の範囲は、添付の特許請求の範囲を参照することにより、このような特許請求の範囲が権利を有する同等物の完全な範囲と共に決定されるべきである。10

#### 【符号の説明】

#### 【0026】

100：データ処理デバイス

110、204、310：処理ユニット

116、316：第1のプロセッサコア

118、318：第2のプロセッサコア

119、319：ホストコントローラ

120、320：システムメモリ

122：不揮発性メモリ（NVM）デバイス

130、132、330、332：内蔵された不揮発性メモリ

202：電力管理ユニット

203：電力供給

206：コントローラ

208：メモリバス

220：不揮発性メモリ（NVM）アレイ

230：状況レジスタ・ユニット

240：コマンド・インターフェース

300：無線通信デバイス

314：アンテナ

312：送受信機

360：送信機

362：受信機

10

20

30

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100120525

弁理士 近藤 直樹

(72)発明者 コラド ヴィラ

イタリア 20050 ソヴィコ (ミラノ) ヴィア エッセ フランチェスコ 31

(72)発明者 ダニエレ バルキ

イタリア ヴィメルカーテ (ミラノ) ヴィア カヴォウル 63

(72)発明者 グラツィアノ ミリキニ

イタリア 64047 ピエトラカメラ (テラモ) ヴィア ヴェンティチンクエ ルグリオ

13

合議体

審判長 飯田 清司

審判官 鈴木 匡明

審判官 加藤 浩一

(56)参考文献 特開2002-074999 (JP, A)

特表2009-503738 (JP, A)

特開2004-199121 (JP, A)

特開2003-223792 (JP, A)

特開2003-233994 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/00

G06F 12/16