(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6406888号

(P6406888)

(45) 発行日 平成30年10月17日(2018.10.17)

(24) 登録日 平成30年9月28日(2018.9.28)

|                      |            |   |

|----------------------|------------|---|

| (51) Int.Cl.         | F 1        |   |

| HO3M 1/10 (2006.01)  | HO3M 1/10  | C |

| HO3M 1/56 (2006.01)  | HO3M 1/56  |   |

| HO4N 5/378 (2011.01) | HO4N 5/378 |   |

| HO4N 5/374 (2011.01) | HO4N 5/374 |   |

| GO1R 31/28 (2006.01) | GO1R 31/28 | B |

請求項の数 18 (全 21 頁)

|           |                              |                                                      |

|-----------|------------------------------|------------------------------------------------------|

| (21) 出願番号 | 特願2014-124751 (P2014-124751) | (73) 特許権者 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成26年6月17日(2014.6.17)        | (74) 代理人 100126240<br>弁理士 阿部 琢磨                      |

| (65) 公開番号 | 特開2016-5147 (P2016-5147A)    | (74) 代理人 100124442<br>弁理士 黒岩 創吾                      |

| (43) 公開日  | 平成28年1月12日(2016.1.12)        | (72) 発明者 亀山 弘明<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内     |

| 審査請求日     | 平成29年6月13日(2017.6.13)        | (72) 発明者 樋山 拓己<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内     |

最終頁に続く

(54) 【発明の名称】アナログデジタル変換回路の駆動方法、アナログデジタル変換回路、撮像装置、撮像システム、アナログデジタル変換回路の検査方法

## (57) 【特許請求の範囲】

## 【請求項 1】

信号レベルが変化する第1信号が入力されるとともに、前記第1信号に同期して、もしくは前記第1信号に対して遅延して、信号レベルが変化する第2信号と、前記第2信号に対して遅延して信号レベルが変化する第3信号のそれぞれを、前記第1信号を用いて生成する回路と、

メモリとを有し、

前記回路が前記第2信号の信号レベルを変化させる前に、前記メモリが前記第2信号のサンプリングを開始し、

前記メモリが前記サンプリングを行っている期間に、前記回路は前記第2信号の信号レベルを変化させ、

前記回路による前記第3信号の信号レベルの変化によって、前記メモリが前記第2信号をホールドすることを特徴とするアナログデジタル変換回路。

## 【請求項 2】

アナログ信号と参照信号とを比較した結果を示す比較結果信号を出力する比較器と、クロックを計数したカウント信号を出力するカウンタをさらに有し、

前記メモリは、前記比較結果信号の信号レベルの変化によって、前記カウント信号をホールドすることを特徴とする請求項1に記載のアナログデジタル変換回路。

## 【請求項 3】

前記メモリを含み、各々が前記第2信号または前記カウント信号をホールドする複数の

メモリと、を備え、

前記複数のメモリの各々が、N個（N > 1）のビットメモリを有し、

前記カウント信号が、Mビット（M < N）のデジタル信号であり、

前記N個のビットメモリが前記第2信号をホールドすることを特徴とする請求項2に記載のアナログデジタル変換回路。

【請求項4】

前記複数のメモリのうちの、前記第2信号の信号レベルとは異なる信号レベルの信号をホールドしたメモリにおいて、

前記第2信号の信号レベルとは異なる信号レベルをホールドしたビットメモリの数が、前記Nと前記Mとの差以下の場合に、

10

前記N個のビットメモリのうちの、前記第2信号の信号レベルとは異なる信号レベルをホールドした前記ビットメモリの代わりに、前記N個のビットメモリのうちの前記第2信号の信号レベルと同じ信号レベルをホールドした前記ビットメモリを用いて、前記カウント信号をホールドすることを特徴とする請求項3に記載のアナログデジタル変換回路。

【請求項5】

前記メモリを含み、各々が前記第2信号または前記カウント信号をホールドする複数のメモリを備え、

前記複数のメモリの各々が、N個（N > 1）のビットメモリを有し、

前記N個のうちのM個（N > M - 1）のビットメモリが前記第2信号をホールドすることを特徴とする請求項2に記載のアナログデジタル変換回路。

20

【請求項6】

前記複数のメモリのうちの、前記第2信号の信号レベルとは異なる信号レベルの信号をホールドした前記メモリにおいて、

前記M個のビットメモリのうちの、前記第2信号の信号レベルとは異なる信号レベルをホールドしたビットメモリの代わりに、N - M個のビットメモリの少なくとも1つを用いて、前記カウント信号をホールドすることを特徴とする請求項5に記載のアナログデジタル変換回路。

【請求項7】

前記回路は、

前記第2信号を、第1の信号レベルから第2の信号レベルへ変化させることと、

30

前記第2信号を、前記第2の信号レベルから前記第1の信号レベルへ変化させることと、の両方を行うことを特徴とする請求項1～6のいずれかに記載のアナログデジタル変換回路。

【請求項8】

前記回路が、前記第2信号の信号レベルを変化させてから、前記第3信号の信号レベルを変化させるまでの期間が可変であることを特徴とする請求項1～7のいずれかに記載のアナログデジタル変換回路。

【請求項9】

前記第1信号がクロック信号に同期していることを特徴とする請求項1～8のいずれかに記載のアナログデジタル変換回路。

40

【請求項10】

前記第3信号の信号レベルの変化時に前記回路が供給する前記第2信号の信号レベルと、前記メモリがホールドした信号の信号レベルと、を比較することを特徴とする請求項1～9のいずれかに記載のアナログデジタル変換回路。

【請求項11】

前記比較の結果、前記第3信号の信号レベルの変化時に前記回路が供給する前記第2信号の信号レベルと、前記メモリがホールドした信号の信号レベルとが一致しない場合には前記メモリを不良と判定することを特徴とする請求項10に記載のアナログデジタル変換回路。

【請求項12】

50

前記回路は、前記第1信号を遅延させることで前記第3信号を生成する遅延回路と、前記第1信号が入力される第1バッファと、前記遅延回路から前記第3信号が入力される第2バッファとを備え、

前記第1バッファが前記第2信号を前記メモリに出力し、

前記第2バッファが前記第3信号を前記メモリに出力することを特徴とする請求項1～11のいずれかに記載のアナログデジタル変換回路。

**【請求項13】**

前記回路は、前記第1信号が入力される遅延回路を有し、

前記遅延回路が、前記第2信号と前記第3信号のそれぞれを生成することを特徴とする請求項1～11のいずれかに記載のアナログデジタル変換回路。

10

**【請求項14】**

前記遅延回路がフリップフロップ回路であることを特徴とする請求項13に記載のアナログデジタル変換回路。

**【請求項15】**

請求項1～14のいずれかに記載のアナログデジタル変換回路と、

行列状に配された複数の画素と、を有し、

前記複数の画素の一部に対応して、前記メモリが配されていることを特徴とする撮像装置。

**【請求項16】**

前記撮像装置は、信号処理部をさらに有し、

前記第3信号の信号レベルの変化時に前記回路が供給する前記第2信号の信号レベルと、前記メモリがホールドした信号の信号レベルとを前記信号処理部が比較することを特徴とする請求項15に記載の撮像装置。

20

**【請求項17】**

前記第3信号の信号レベルの変化時に前記回路が供給する前記第2信号の信号レベルと、前記メモリがホールドした信号の信号レベルとが一致しない場合、前記信号処理部は前記メモリを不良と判定することを特徴とする請求項16に記載の撮像装置。

**【請求項18】**

請求項15～17のいずれかに記載の撮像装置と、

信号処理部と、を有し、

前記信号処理部は、前記撮像装置が出力する信号に基づいて画像を生成することを特徴とする撮像システム。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、アナログデジタル変換回路の駆動方法、アナログデジタル変換回路、撮像装置、撮像システム、アナログデジタル変換回路の検査方法に関する。

**【背景技術】**

**【0002】**

複数の比較器と、複数の比較器の各々に、各々が対応して設けられた複数のメモリとを有するアナログデジタル変換回路が知られている。複数の比較器の各々は、アナログ信号と、参照信号との信号レベルを比較した結果を示す比較結果信号を、比較器に対応して設けられたメモリに供給する。

40

**【0003】**

特許文献1に記載のアナログデジタル変換回路は、複数のメモリに対して共通のカウント信号を供給するカウントタを有する。各メモリは、対応する比較器の供給する比較結果信号の信号レベルが変化したタイミングから、カウント信号の信号レベルのサンプリングを開始する。そして、比較結果信号の信号レベルが変化したタイミングから所定の期間が経過した後、カウント信号の信号レベルをホールドする。これにより、メモリに入力されたカウント信号を、比較器に入力されたアナログ信号に基づくデジタル信号として、複数の

50

メモリの各々がホールドする。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2013-65924号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1では、メモリに入力されるカウント信号の信号レベルの変化に対する応答性が所望の特性を満足しないメモリを検出する検討が為されていなかった。

10

【課題を解決するための手段】

【0006】

本発明の一の態様は、アナログ信号と、時間の経過にともなって信号レベルが変化する参照信号とを比較した結果を示す比較結果信号を各々が output する複数の比較器と、前記参照信号が信号レベルの変化を開始してから前記比較結果信号の信号レベルが変化するまでの期間に基づく第1のデジタル信号を各々がホールドするとともに、前記複数の比較器の各々に対応して各々が設けられた複数のメモリと、第2のデジタル信号を前記複数のメモリに供給する信号生成部と、を有し、前記信号生成部は、前記複数のメモリが前記第2のデジタル信号をサンプリングしている期間に前記第2のデジタル信号の信号レベルを変化させた後、前記信号生成部はさらに、前記複数のメモリがサンプリングしている前記第2のデジタル信号を前記複数のメモリにホールドさせる信号を、前記複数のメモリに供給することを特徴とするアナログデジタル変換回路である。

20

【0007】

また、別の態様は、アナログ信号と、時間の経過にともなって信号レベルが変化する参照信号とを比較した結果を示す比較結果信号を各々が output する複数の比較器と、前記参照信号が信号レベルの変化を開始してから前記比較結果信号の信号レベルが変化するまでの期間に基づく第1のデジタル信号を各々がホールドするとともに、前記複数の比較器の各々に対応して各々が設けられた複数のメモリと、を有するアナログデジタル変換回路の検査方法であって、第2のデジタル信号を前記複数のメモリに供給し、前記複数のメモリが前記第2のデジタル信号をサンプリングしている期間に前記第2のデジタル信号の信号レベルを変化させた後、前記複数のメモリがサンプリングしている前記第2のデジタル信号を前記複数のメモリにホールドさせる信号を、前記複数のメモリに供給することを特徴とするアナログデジタル変換回路の検査方法である。

30

【発明の効果】

【0008】

メモリに入力されるカウント信号の信号レベルの変化に対する応答性が所望の特性を満足しないメモリを検出することができる。

【図面の簡単な説明】

【0009】

【図1】A/D変換回路および撮像装置の構成の一例を示した図

40

【図2】テスト信号生成回路の構成の一例を示した図と、選択回路の構成の一例を示した図

【図3】A/D変換回路および撮像装置の動作の一例を示した図

【図4】検査モードの一例のフローチャートを示した図

【図5】A/D変換回路および撮像装置の動作の一例を示した図

【図6】A/D変換回路および撮像装置の構成の一例を示した図

【図7】テスト信号生成回路の構成の一例を示した図と、テスト信号生成回路の動作の一例を示した図

【図8】A/D変換回路および撮像装置の構成の一例を示した図

【図9】A/D変換回路および撮像装置の構成の一例を示した図

50

【図10】検査モードの一例のフローチャートを示した図

【図11】撮像システムの一例を示した図

【発明を実施するための形態】

【0010】

以下、図面を参照しながら各実施例を説明する。

【0011】

(実施例1)

アナログデジタル変換回路を有する装置の一例である撮像装置を例として、本実施例を説明する。

【0012】

10

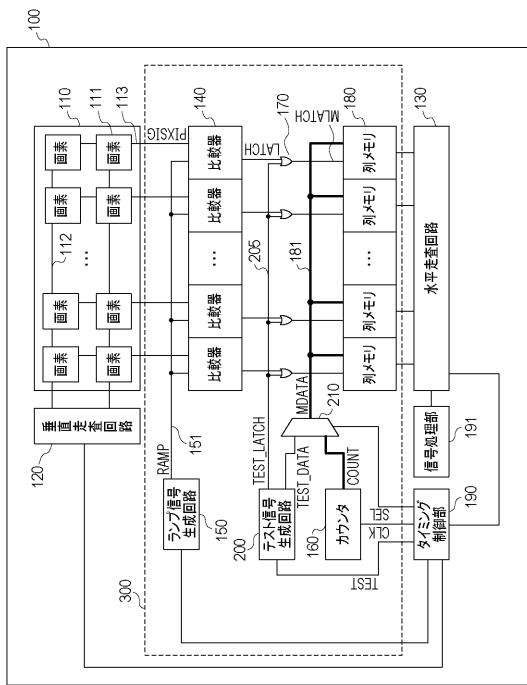

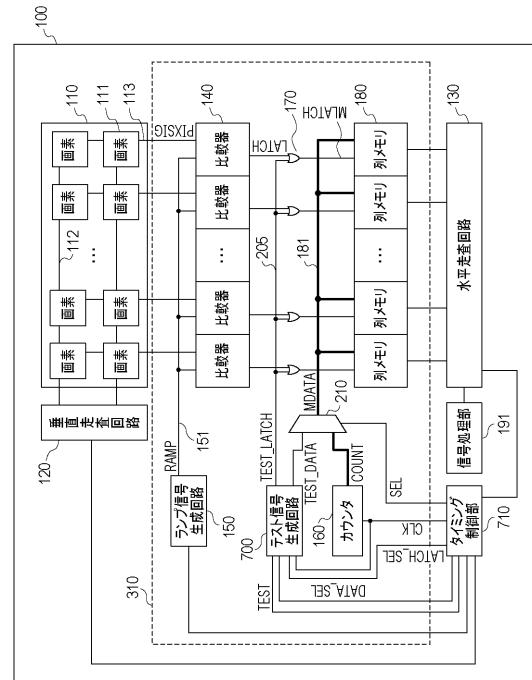

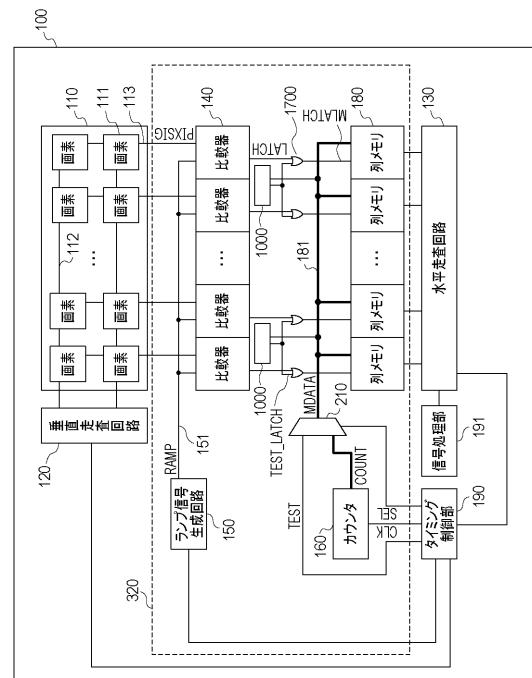

図1は、本実施例の撮像装置の構成を示した図である。

【0013】

撮像装置100は、入射光を光電変換し、得られた電気信号をデジタル信号として外部に出力する。撮像装置100は、画素アレイ110、垂直走査回路120、水平走査回路130、比較器140、ランプ信号生成回路150、カウンタ160、OR回路170、列メモリ180、タイミング制御部190、信号処理部191を有する。また、撮像装置100は、行制御線112と垂直信号線113を有する。また、撮像装置100は、テスト信号生成回路200、選択回路210を有する。

【0014】

20

画素アレイ110は、光電変換素子を含む複数の画素111を有する。複数の画素111は、画素アレイ110に行列状に配置されている。図1では、2行分の画素111を示しているが、画素111の行数はこれに限るものではない。

【0015】

垂直走査回路120は、複数の行制御線112を介して、複数の画素111に電気的に接続されている。1つの行制御線112は、1行の画素111に対応して設けられている。垂直走査回路120は、タイミング制御部190に電気的に接続されている。垂直走査回路120はタイミング制御部190から供給される信号に基づいて、複数の行制御線112の各々に供給する信号レベルをHiとする。画素111に電気的に接続された行制御線112の信号レベルがHiとなると、当該画素111は垂直信号線113に、入射光に基づく信号であるPIXSIG信号を出力する。

30

【0016】

ランプ信号生成回路150は、ランプ信号RAMPを生成する。ランプ信号RAMPは、時間の経過とともに信号レベルが単調に増加、あるいは単調に減少する参照信号である。ランプ信号生成回路150は、ランプ信号RAMPを、ランプ信号線151を介して、複数の比較器140の各々に供給する。ランプ信号生成回路150は、タイミング制御部190に電気的に接続されている。ランプ信号生成回路150は、タイミング制御部190から供給される信号に基づいて、ランプ信号RAMPの時間の経過とともに信号レベルの変化を開始する。

【0017】

40

複数の比較器140の各々は、画素アレイ110の複数の垂直信号線113の各々に対応して設けられている。さらに言えば、1つの比較器140は、1列の画素111に対応して設けられている。複数の比較器140の各々は、ランプ信号生成回路150と、1つの垂直信号線113と、に電気的に接続されている。また、複数の比較器140の各々は、複数のOR回路170の各々に電気的に接続されている。複数の比較器140の各々は、複数のOR回路170の各々に、信号LATCHを出力する。信号LATCHは、PIXSIG信号の信号レベルよりもランプ信号RAMPの信号レベルが大きくなったタイミングから所定の期間、Hiとなる信号である。つまり、信号LATCHは、比較器140が行う比較の結果の変化によって、信号レベルが変化する信号である。

【0018】

また、複数のOR回路170は、テスト信号生成回路200に、テスト信号供給線20

50

5を介して、電気的に接続されている。テスト信号生成回路200は、テスト信号供給線205を介して、複数のOR回路170に、信号TEST\_LATCHを供給する。信号TEST\_LATCHは、テストラッチ信号である。

【0019】

複数のOR回路170の各々は、信号LATCHと信号TEST\_LATCHの一方がHiとなると、Hiの信号MLATCHを、対応して設けられた列メモリ180に供給する。

【0020】

テスト信号生成回路200は、選択回路210に電気的に接続されている。テスト信号生成回路200は、選択回路210に、信号TEST\_DATAを供給する。テスト信号生成回路200は、タイミング制御部190に電気的に接続されている。また、テスト信号生成回路200は、タイミング制御部190から供給される信号TESTがHiとなると、まず信号TEST\_DATAをHiとし、その後に、信号TEST\_DATAをHiとする。

10

【0021】

選択回路210は、カウンタ160に電気的に接続されている。カウンタ160は、選択回路210に信号COUNTを供給する。この信号COUNTは、タイミング制御部190からカウンタ160に供給される信号CLKを、カウンタ160が計数することで生成するカウント信号である。信号CLKは、クロック信号である。また、テスト信号生成回路200は、複数の列メモリ180に信号TEST\_DATAと信号TEST\_LATCHを供給する信号生成部である。

20

【0022】

また、選択回路210は、タイミング制御部190に電気的に接続されている。タイミング制御部190は、選択回路210に信号SELを供給する。

【0023】

また、選択回路210は、複数の列メモリ180に、データ信号線181を介して、電気的に接続されている。選択回路210は、データ信号線181に供給する信号MDATAとして、信号SELの信号レベルに基づいて、信号TEST\_DATAと信号COUNTのいずれか一方を選択する。

30

【0024】

複数の列メモリ180の各々は、複数のOR回路170の各々に電気的に接続されている。複数の列メモリ180の各々は、水平走査回路130に電気的に接続されている。

【0025】

水平走査回路130は、タイミング制御部190に電気的に接続されている。水平走査回路130は、タイミング制御部190から供給される信号に基づいて、複数の列メモリ180を順次選択する。これにより、複数の列メモリ180の各々がホールドした信号は、信号処理部191に順次、転送される。

【0026】

アナログデジタル変換回路（以下、AD変換回路と表記する。）300は、複数の比較器140、ランプ信号生成回路150、カウンタ160、複数のOR回路170、複数の列メモリ180、テスト信号生成回路200、選択回路210を有する。

40

【0027】

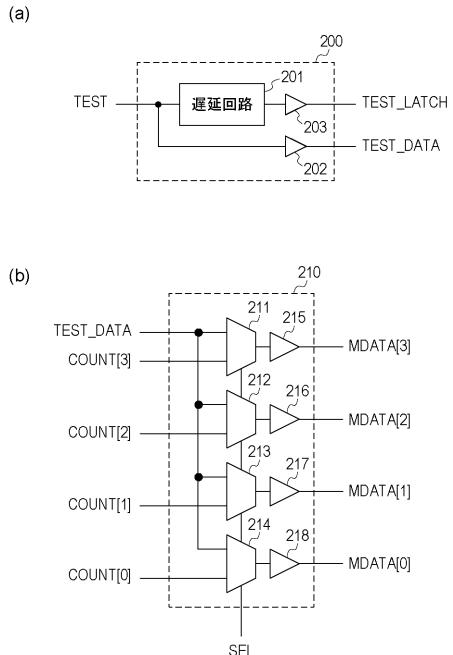

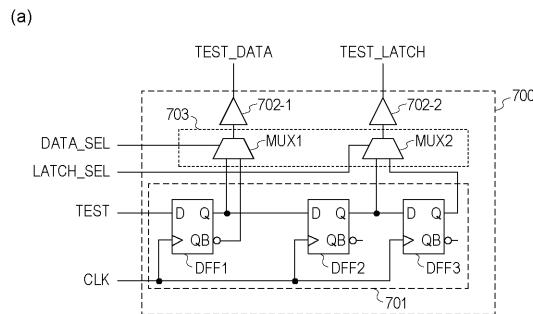

図2(a)は、テスト信号生成回路200の構成を示した図である。テスト信号生成回路200は、遅延回路201、バッファ202、バッファ203を有する。タイミング制御部190が供給する信号TESTは、遅延回路201と、バッファ202とに入力される。遅延回路201は、信号TESTの信号レベルがHiとなってから、所定の期間t delayの経過後にHiとなる信号を、バッファ203に供給する。バッファ203が供給する信号が、信号TEST\_LATCHである。バッファ202が供給する信号が、信号TEST\_DATAである。

【0028】

50

図2(b)は、選択回路210の構成を示した図である。選択回路210は、複数のビット信号選択回路211～214、複数のバッファ215～218を有する。複数のビット信号選択回路211～214のそれぞれには、信号COUNTの各ビットの信号である信号COUNT[0]～[3]のそれぞれと、信号TEST\_DATAとが選択的に入力される。複数のビット信号選択回路211～214の各々は、タイミング制御部190から供給される信号SELの信号レベルがLoの場合には、信号COUNT[3]～[0]を複数のバッファ215～218の各々に出力する。一方、複数のビット信号選択回路211～214の各々は、タイミング制御部190から供給される信号SELの信号レベルがHiの場合には、信号TEST\_DATAを複数のバッファ215～218の各々に出力する。そして、複数のビット信号選択回路211～214の各々は、対応する複数のバッファ215～218の各々に信号を供給する。複数のバッファ215～218の各々は、各々に対応する複数のビット信号選択回路211～214の各々から出力される信号をバッファした信号を、信号MDATA[3]～[0]として出力する。図2(b)の信号MDATA[3]～[0]が、図1で示した信号MDATAに相当する。

#### 【0029】

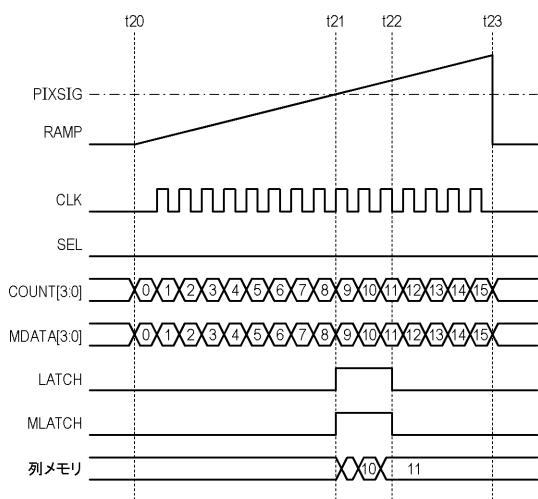

次に、図3を参照しながら、図1に示した撮像装置の動作を説明する。図3に示した各信号は、図1に示した各信号に対応している。図3は、撮像装置が通常動作として、入射光に基づくデジタル信号を生成する場合のタイミング図である。図3には示していない信号TEST\_LATCHの信号レベルは、図3に示した動作の間、Loである。尚、図3に示した信号COUNTおよび信号MDATAのそれぞれは、4ビットのデジタル信号である。図3に示した「列メモリ」とは、列メモリ180がホールドするデジタル信号を表している。図3では、説明を簡単にするために、信号COUNT、信号MDATA、列メモリ180がホールドする信号のそれぞれをバイナリ値で表している。図3においてバイナリ値で表記したそれぞれの信号は、実際には、2進数で表される信号である。

#### 【0030】

時刻t20において、タイミング制御部190は、信号SELの信号レベルをLoとしている。また、時刻t20において、Hiの信号が供給されている行信号線112に電気的に接続された画素111は、垂直信号線113に、PIXSIG信号を出力している。

#### 【0031】

時刻t20に、タイミング制御部190の制御によって、ランプ信号生成回路150は、ランプ信号RAMPの時間にともなった信号レベルの変化を開始する。

#### 【0032】

また、時刻t20に、カウンタ160は、タイミング制御部190から供給される信号CLKの係数を開始する。

#### 【0033】

信号SELの信号レベルがLoであるため、選択回路210は、カウンタ160が供給する信号COUNTを、データ信号線181を介して、複数の列メモリ180の各々に供給する。

#### 【0034】

時刻t21に、画素111が垂直信号線113に出力しているPIXSIG信号とランプ信号RAMPとの信号レベルの大小関係が逆転する。これにより、信号LATCHの信号レベルがHiになる。これにより、信号MLATCHの信号レベルがHiとなる。そして、信号LATCHの信号レベルは、所定の期間、Hiとなった後の時刻t22に、Loとなる。これにより、信号MLATCHの信号レベルもLoとなる。列メモリ180は、信号MLATCHの信号レベルがLoとなった時の信号COUNTの信号レベルをホールドする。複数の列メモリ180の各々は、アナログ信号に基づくデジタル信号をホールドするメモリである。参照信号であるランプ信号RAMPが信号レベルの変化を開始してから、比較結果信号の信号レベルが変化するまでの期間に基づく信号COUNTは、時刻t20から時刻t22までの期間に基づくカウント信号である。

#### 【0035】

10

20

30

40

50

時刻  $t_{23}$  に、ランプ信号生成回路 150 は、ランプ信号 RAMP の時間にともなった信号レベルの変化を終了する。

【0036】

その後、水平走査回路 130 は、複数の列メモリ 180 を順次走査する。これにより、複数の列メモリ 180 の各々から、複数の列メモリ 180 の各々がホールドした信号が、順次、信号処理部 191 に出力される。

【0037】

次に、複数の列メモリ 180 を検査する動作について説明する。

【0038】

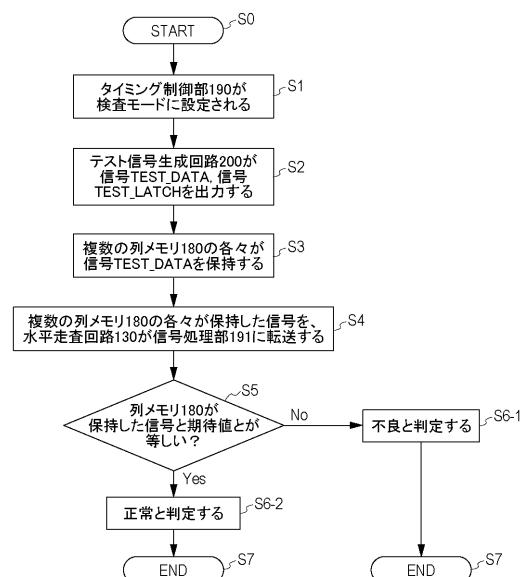

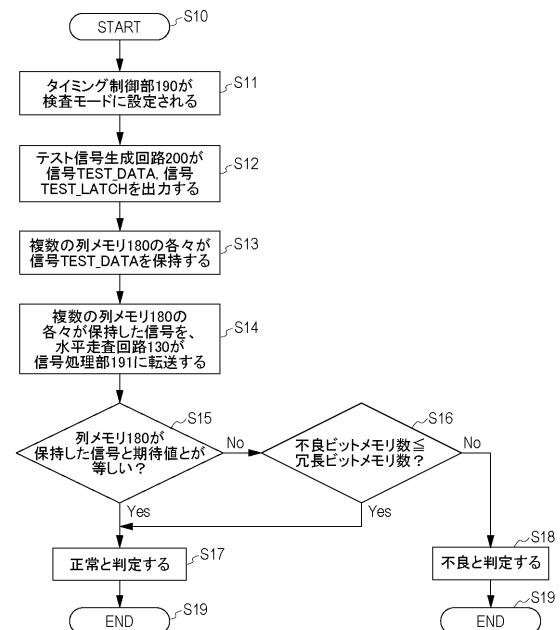

図 4 は、複数の列メモリ 180 の検査に関する動作を示したフローチャートである。

10

【0039】

ステップ S1 は、撮像装置 100 の外部からの指示信号により、タイミング制御部 190 が、検査モードに設定されるステップである。

【0040】

ステップ S2 は、テスト信号生成回路 200 が、複数の列メモリ 180 の各々が期待値をホールドするように、信号 TEST\_DATA と信号 TEST\_LATCH をそれぞれ供給するステップである。信号 TEST\_DATA と信号 TEST\_LATCH は、複数の列メモリ 180 の検査に用いる検査信号である。

【0041】

ステップ S3 は、複数の列メモリ 180 の各々が、検査信号に基づいて、信号 TEST\_DATA をホールドするステップである。

20

【0042】

ステップ S4 は、水平走査回路 130 が、複数の列メモリ 180 の各々がホールドした信号を、複数の列メモリ 180 の各々から、信号処理部 191 に転送するステップである。

【0043】

ステップ S5 は、信号処理部 191 が、複数の列メモリ 180 の各々がホールドすべき信号レベルである期待値と、複数の列メモリ 180 の各々がホールドした実際の信号レベルとを比較するステップである。信号処理部 191 は、列メモリ 180 がホールドした実際の信号レベルと期待値とが一致する場合には、ステップ S6-1 のステップに進み、期待値と同じ信号レベルをホールドした列メモリ 180 を「正常」と判定する。一方、複数の列メモリ 180 の各々がホールドした信号の信号値と期待値とが一致しない場合には、ステップ S6-2 のステップに進み、期待値と異なる信号値の信号をホールドした列メモリ 180 を「不良」と判定する。

30

【0044】

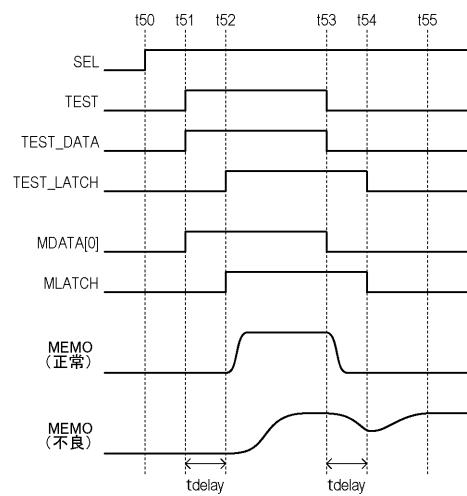

図 5 は、複数の列メモリ 180 の検査に関わる動作を示したタイミング図である。図 5 に示した MEMO は、列メモリ 180 がホールドする信号のうち、最下位ビットの信号を示している。

【0045】

時刻  $t_{50}$  において、図 4 に示したステップ S2 まで完了している。

40

【0046】

時刻  $t_{50}$  に、タイミング制御部 190 は、信号 SEL の信号レベルを Hi とする。これにより、選択回路 210 は、信号 TEST\_DATA によって生成した信号 MDATA を、データ信号線 181 を介して、複数の列メモリ 180 に供給する。

【0047】

時刻  $t_{51}$  に、タイミング制御部 190 は、信号 TEST の信号レベルを Hi とする。これにより、テスト信号生成回路 200 が供給する信号 TEST\_DATA の信号レベルが Hi となる。これにより、信号 MDATA の信号レベルが Hi となる。図 5 では、信号 MDATA の最下位ビットである信号 MDATA[0] を示している。

【0048】

50

テスト信号生成回路 200 が供給する信号 TEST\_LATCH は、遅延回路 201 の動作によって、信号 TEST\_DATA の信号レベルが Hi となってから所定の期間 t delay の経過後の時刻 t52 に、信号レベルが Hi となる。これにより、複数の OR 回路 170 の各々が供給する信号 MATCH の信号レベルが Hi となる。Hi の信号レベルの信号 TEST\_LATCH は、列メモリ 180 に、選択回路 210 が供給する、信号 TEST\_DATA によって生成した信号 DATA のサンプリングを開始させる信号である。

#### 【0049】

時刻 t53 に、タイミング制御部 190 は、信号 TEST の信号レベルを Lo とする。これにより、信号 TEST\_DATA の信号レベルが Lo となる。テスト信号生成回路 200 が供給する信号 TEST\_LATCH は、遅延回路 201 の動作によって、信号 TEST\_DATA の信号レベルが Lo となってから所定の期間 t delay の経過後の時刻 t54 に、信号レベルが Lo となる。これにより、時刻 t54 に、信号 MATCH の信号レベルが Lo となる。Hi から Lo に信号レベルが遷移した信号 TEST\_LATCH は、列メモリ 180 に、選択回路 210 が供給する信号 TEST\_DATA によって生成した信号 DATA をホールドさせる信号である。

#### 【0050】

列メモリ 180 の応答性が良好の場合について述べる。時刻 t53 に信号 TEST\_DATA が Lo となってから、時刻 t54 に信号 MATCH が Lo となるまでの期間に、列メモリ 180 は、Lo の信号レベルの信号 TEST\_DATA に対応して、MEMO の信号レベルが Lo となるように応答する。

#### 【0051】

列メモリ 180 の応答性が充分でない場合には、時刻 t53 に信号 TEST\_DATA が Lo となってから、時刻 t54 に信号 MATCH が Lo となるまでの期間に、MEMO の信号レベルが Lo にならない。よって、列メモリ 180 の応答性が充分でない場合には、当該列メモリの MEMO は、Hi の信号レベルとなる。

#### 【0052】

その後、水平走査回路 130 は、複数の列メモリ 180 を順次走査する。これにより、複数の列メモリ 180 の各々から、複数の列メモリ 180 の各々がホールドした信号が、順次、信号処理部 191 に出力される。

#### 【0053】

信号処理部 191 は、複数の列メモリ 180 の各々がホールドすべき信号レベルである期待値と、複数の列メモリ 180 の各々から実際に出力された信号レベルとを比較する。期待値は、予め、撮像装置 100 の外部からの制御信号によって信号処理部 191 に設定されている値である。そして、信号処理部 191 は、ホールドすべき信号レベルとは異なる信号値の信号を出力した列メモリ 180 を、「不良」と判定する。一方、信号処理部 191 は、ホールドすべき信号値と同じ信号レベルの信号を出力した列メモリ 180 を、「正常」と判定する。

#### 【0054】

本実施例の AD 変換回路 300 は、信号 TEST\_DATA の信号レベルを Hi から Lo としてから、所定の期間 t delay である第 1 の期間の経過後に、信号 MATCH を Hi から Lo とする。これにより、ホールドする信号が第 1 の期間に、Hi から Lo に遷移しない不良の列メモリ 180 と、ホールドする信号が第 1 の期間に Hi から Lo に遷移する正常の列メモリ 180 とを識別することができる。これにより、本実施例の AD 変換回路 300 は、カウント信号である信号 COUNT の信号レベルの変化に対する応答性が低い列メモリ 180 を検出することができる。尚、第 1 の期間である所定の期間 t delay は、任意の長さに設定することができる。たとえば、AD 変換回路 300 が複数の動作モードを備える場合において、信号 MATCH が Hi となる期間が最も短いモードに合わせて、所定の期間 t delay の長さを設定するようにしても良い。

#### 【0055】

10

20

30

40

50

A D変換期間の短縮を行うために、信号C L Kの周波数の増加が行われることがある。そして、A D変換回路3 0 0では、ランプ信号R A M PとP I X S I G信号との大小関係が逆転した後に、信号L A T C Hの信号レベルをL oからH iとして再びL oにするまでの期間を、信号C L Kの周期で決定していることがある。この場合には、信号C L Kの周波数の増加に伴って、信号L A T C Hの信号レベルがH iである期間が短くなる。信号L A T C Hの信号レベルがH iである期間が短くなると、不良の列メモリ1 8 0では、本来ホールドすべき信号とは異なる信号値の信号をホールドすることになる。

#### 【0 0 5 6】

本実施例のA D変換回路3 0 0は、このように、A D変換回路3 0 0のクロック周波数が増加した場合においても、不良の列メモリ1 8 0の検出を行うことができる。

10

#### 【0 0 5 7】

尚、本実施例の撮像装置1 0 0は、垂直信号線1 1 3に出力されたP I X S I G信号を増幅した信号を比較器1 4 0に出力する増幅部をさらに有していても良い。

#### 【0 0 5 8】

また、本実施例では、ランプ信号R A M Pが、時間の経過にともなってスロープ状に信号レベルが変化する信号であった。ランプ信号R A M Pは、時間の経過にともなって階段状に信号レベルが変化する信号であっても良い。このように階段状に信号レベルが変化するランプ信号R A M Pも、時間の経過にともなって信号レベルが変化する参照信号である。

20

#### 【0 0 5 9】

尚、本実施例では、列メモリ1 8 0がホールドする信号のうち、最下位ビットの信号に着目して説明した。列メモリ1 8 0の検査は、列メモリ1 8 0の全ビットに対して行うようにしても良い。ただし、列メモリ1 8 0において、最下位ビットをホールドするビットメモリは、他のビットをホールドするビットメモリに比して、信号レベルのH iとL oとの間の遷移の周期が短い。従って、列メモリ1 8 0の検査は、最下位ビットの信号をホールドするビットメモリに対して行うことが好ましい。

#### 【0 0 6 0】

本実施例では、列メモリ1 8 0の正常と不良との判定を行う信号処理部1 9 1が、撮像装置1 0 0に設けられている例を説明した。列メモリ1 8 0の正常と不良との判定を行う信号処理部1 9 1は、A D変換回路3 0 0が有していても良いし、撮像装置1 0 0の外部に設けられていても良い。

30

#### 【0 0 6 1】

尚、本実施例では、選択回路2 1 0は、タイミング制御部1 9 0から入力される信号T E S Tに基づく信号M D A T Aを供給していた。他の例として、カウンタ1 6 0から入力される信号C O U N Tを、検査信号の一つである信号T E S T \_ D A T Aの代わりに、データ信号線1 8 1に供給するようにしても良い。

#### 【0 0 6 2】

尚、本実施例では、期待値は、撮像装置1 0 0の外部からの制御信号によって設定されている信号であった。期待値は、予め信号処理部1 9 1に固定値として書き込まれた値であっても良いし、撮像装置1 0 0の外部からの制御信号によって様々に設定される値であっても良い。

40

#### 【0 0 6 3】

(実施例2)

本実施例のA D変換回路3 1 0、およびA D変換回路3 1 0を有する撮像装置1 0 0について、実施例1と異なる点を中心に説明する。

#### 【0 0 6 4】

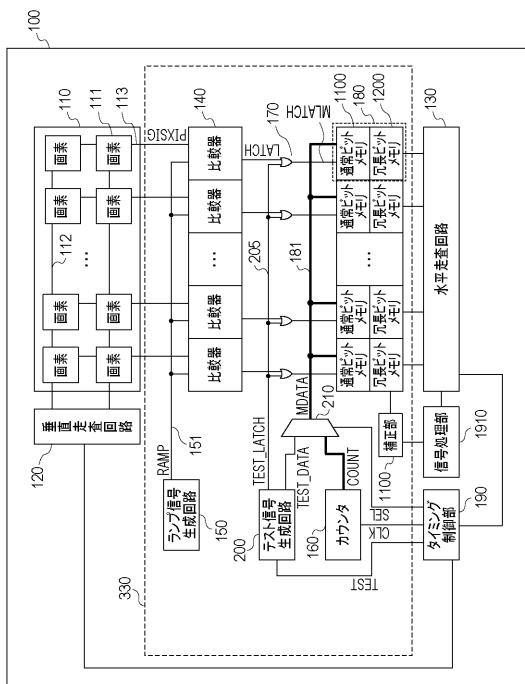

図6は、本実施例の撮像装置1 0 0の構成を示した図である。図1に示した部材と同じ機能を有する部材は、図6においても、図1で付した符号と同じ符号が付されている。

#### 【0 0 6 5】

本実施例の撮像装置1 0 0は、タイミング制御部7 1 0が、テスト信号生成回路7 0 0

50

に、信号 DATA\_SEL、信号 LATCH\_SEL をそれぞれ供給する。また、タイミング制御部 710 は、カウンタ 160 に供給する信号 CLK を、テスト信号生成回路 700 にも供給する。つまり、カウンタ 160 に供給される信号 CLK と同一の信号 CLK がテスト信号生成回路 700 に供給される。これにより、本実施例の撮像装置 100 は、テスト信号生成回路 700 の動作と、カウンタ 160 の動作との同期を行うことができる。

#### 【0066】

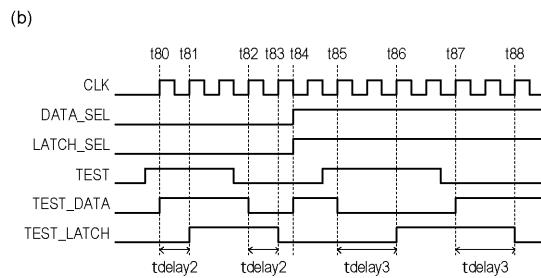

図 7 (a) は、本実施例のテスト信号生成回路 700 の構成を示した図である。遅延回路 701 は、フリップフロップ回路（以下、FF 回路と表記する。）DFF1、FF 回路 DFF2、FF 回路 DFF3 を有する。FF 回路 DFF2 の出力 Q の信号レベルは、FF 回路 DFF1 の出力 Q の信号レベルが Hi となってから、信号 CLK の 1 周期分遅れて Hi となる。また、FF 回路 DFF3 の出力 Q の信号レベルは、FF 回路 DFF2 の出力 Q の信号レベルが Hi となってから、信号 CLK の 1 周期分遅れて Hi となる。つまり、FF 回路 DFF3 の出力 Q の信号レベルは、FF 回路 DFF1 の出力 Q の信号レベルが Hi となってから、信号 CLK の 2 周期分遅れて Hi となる。

#### 【0067】

テスト信号生成回路 700 は、それがマルチプレクサ回路である MUX1、MUX2 を有する。また、テスト信号生成回路 700 は、出力バッファ 702-1、出力バッファ 702-2 を有する。タイミング制御部 710 が供給する信号 DATA\_SEL は、選択回路 703 が有する MUX1 に入力される。また、タイミング制御部 710 が供給する信号 LATCH\_SEL は、選択回路 703 が有する MUX2 に入力される。MUX1 は、信号 DATA\_SEL の信号レベルが Lo の場合には、FF 回路 DFF1 の出力 Q を出力バッファ 702-1 に供給する。また、MUX1 は、信号 DATA\_SEL の信号レベルが Hi の場合には、FF 回路 DFF1 の出力 Q を反転した信号である、FF 回路 DFF1 の出力 QB を出力バッファ 702-1 に供給する。また、MUX2 は、信号 LATCH\_SEL の信号レベルが Lo の場合には、FF 回路 DFF2 の出力 Q を、出力バッファ 702-2 に供給する。また、信号 LATCH\_SEL の信号レベルが Hi の場合には、FF 回路 DFF3 の出力 Q を、出力バッファ 702-2 に供給する。

#### 【0068】

図 7 (b) は、図 7 (a) に示したテスト信号生成回路 700 の動作を示したタイミング図である。図 7 (b) に示した各信号は、図 7 (a) に示した各信号に対応している。尚、図 7 (b) のタイミング図は、図 7 (a) に示したテスト信号生成回路 700 に入力される信号と、テスト信号生成回路 700 の動作との関係を説明するための図である。

#### 【0069】

時刻 t80において、タイミング制御部 710 は、信号 TEST の信号レベルを Hi としている。また、タイミング制御部 710 は、時刻 t80 に、信号 CLK の発振を開始する。これにより、FF 回路 DFF1 の出力 Q の信号レベルは、時刻 t80 に Hi となる。タイミング制御部 710 は、信号 DATA\_SEL の信号レベルを Lo としている。よって、MUX1 は、FF 回路 DFF1 の出力 Q を出力バッファ 702-1 に供給する。従って、出力バッファ 702-1 が output する信号 TEST\_DATA の信号レベルは、時刻 t80 に、Hi となる。

#### 【0070】

FF 回路 DFF2 の出力 Q の信号レベルは、時刻 t81 に Hi となる。タイミング制御部 710 は、時刻 t81 において、信号 LATCH\_SEL の信号レベルを Lo としている。これにより、MUX2 は、FF 回路 DFF2 の出力 Q を出力バッファ 702-2 に供給する。従って、出力バッファ 702-2 が output する信号 TEST\_LATCH の信号レベルは、時刻 t81 に、Hi となる。

#### 【0071】

その後、タイミング制御部 710 は、信号 TEST の信号レベルを Lo とする。これにより、時刻 t82 に信号 TEST\_DATA の信号レベルが Lo となる。そして、時刻 t83 に、信号 TEST\_LATCH の信号レベルが Lo となる。時刻 t80 から時刻 t8

10

20

30

40

50

1までの期間と、時刻  $t_{8.2}$  から時刻  $t_{8.3}$  までの期間は同じ長さの期間  $t_{de1ay2}$  である。

【0072】

時刻  $t_{8.4}$  に、タイミング制御部710は、信号DATA\_SELをHiとする。これにより、MUX1は、FF回路DFF1の出力QBを、出力バッファ702-1に供給する。信号TESTの信号レベルがLoであるため、FF回路DFF1の出力QBの信号レベルはHiである。従って、信号TEST\_DATAの信号レベルは、時刻  $t_{8.4}$  にHiとなる。

【0073】

その後、タイミング制御部710は、信号TESTの信号レベルをHiとする。その後、信号CLKの信号レベルがHiとなる時刻  $t_{8.5}$  に、FF回路DFF1の出力QBの信号レベルはLoとなる。これにより、出力バッファ702-1が出力する信号TEST\_DATAの信号レベルは、Loとなる。

【0074】

また、タイミング制御部710は、時刻  $t_{8.4}$  に、信号LATCH\_SELの信号レベルをHiとする。これにより、MUX2は、FF回路DFF3の出力Qを、出力バッファ702-2に供給する。

【0075】

信号TESTの信号レベルがLoであることにより、時刻  $t_{8.5}$  に、FF回路DFF1の出力Qの信号レベルはHiとなる。これにより、信号TEST\_LATCHの信号レベルであるFF回路DFF3の出力Qは、時刻  $t_{8.5}$  から信号CLKの2周期分遅れた時刻  $t_{8.6}$  に、Hiとなる。

【0076】

その後、タイミング制御部710は、信号TESTの信号レベルをLoとする。その後、信号CLKの信号レベルがHiとなる時刻  $t_{8.7}$  に、FF回路DFF1の出力QBの信号レベルはHiとなる。これにより、出力バッファ702-1が出力する信号TEST\_DATAの信号レベルは、Hiとなる。

【0077】

また、時刻  $t_{8.7}$  に、FF回路DFF1の出力Qの信号レベルはLoとなる。これにより、信号TEST\_LATCHの信号レベルであるFF回路DFF3の出力Qの信号レベルは、時刻  $t_{8.7}$  から信号CLKの2周期分遅れた時刻  $t_{8.8}$  に、Loとなる。

【0078】

時刻  $t_{8.5}$  から時刻  $t_{8.6}$  までの期間と、時刻  $t_{8.7}$  から時刻  $t_{8.8}$  までの期間はともに同じ長さの期間  $t_{de1ay3}$  である。期間  $t_{de1ay3}$  は、期間  $t_{de1ay2}$  に対して、信号CLKの1周期分、期間が長い。尚、本実施例では、期間  $t_{de1ay3}$  は、期間  $t_{de1ay2}$  の2倍の長さの期間である。

【0079】

信号DATA\_SELと信号LATCH\_SELの信号レベルがともにLoの場合には、信号TEST\_DATAの信号レベルがLoとなってから、期間  $t_{de1ay2}$  の経過後に、信号TEST\_LATCHの信号レベルがLoとなる。これにより、本実施例のAD変換回路310は、列メモリ180がホールドする信号であるMEMOの信号レベルが、期間  $t_{de1ay2}$  のうちに、HiからLoに遷移するか否かを検査することができる。

【0080】

また、信号DATA\_SELと信号LATCH\_SELの信号レベルがともにHiの場合には、信号TEST\_DATAの信号レベルがHiとなってから、期間  $t_{de1ay3}$  の経過後に、信号TEST\_LATCHの信号レベルがLoとなる。これにより、期間  $t_{de1ay3}$  のうちに、列メモリ180がホールドする信号であるMEMOの信号レベルがLoからHiに遷移するか否かを検査することができる。

【0081】

10

20

30

40

50

信号DATA\_SELと信号LATCH\_SELの信号レベルの組み合わせにより、列メモリ180について、種々の検査が可能である。以下に示す表1は、信号DATA\_SELの信号レベルと、信号LATCH\_SELの信号レベルと、列メモリ180の検査との関係を示したものである。表1の表記について述べる。表1では、例えば、信号DATA\_SELの信号レベルと信号LATCH\_SELの信号レベルが共にHiの場合の欄に、「期間t delay3 Lo Hi」と記載している。この記載は、期間t delay3のうちに、列メモリ180がホールドする信号であるMEMOの信号レベルがHiからLoに遷移するか否かを検査することを示している。

【0082】

【表1】

|                   |    | 信号DATA_SELの信号レベル    |                     |

|-------------------|----|---------------------|---------------------|

|                   |    | Hi                  | Lo                  |

| 信号LATCH_SELの信号レベル | Hi | 期間t delay3<br>Lo→Hi | 期間t delay3<br>Hi→Lo |

|                   | Lo | 期間t delay2<br>Lo→Hi | 期間t delay2<br>Hi→Lo |

10

【0083】

本実施例の図6に示した撮像装置100における、列メモリ180の検査に関わる動作については、図5に示した動作と同じとすることができる。列メモリ180の検査は、上記した表1の通り、列メモリ180の検査の内容に応じて、信号DATA\_SELと信号LATCH\_SELのそれぞれの信号レベルを選択して行えばよい。

【0084】

このように、本実施例のAD変換回路310は、列メモリ180のLoからHiへの信号レベルの遷移と、HiからLoへの信号レベルの遷移との両方で、複数の列メモリ180を検査することができる。また、本実施例のAD変換回路310は、本実施例の第1の期間の期間t delay2と、第1の期間よりも長い第2の期間の期間t delay3とのそれぞれで、複数の列メモリ180がホールドする信号の信号レベルが遷移するか否かを検査することができる。

30

【0085】

尚、本実施例では、期間t delay2は信号CLKの1周期分、期間t delay3は信号CLKの2周期分に相当する長さとした。期間t delay2と期間t delay3の長さはこの例に限定されるものではなく、期間t delay3は期間t delay2に対して長い期間とすることができます。例えば、テスト信号生成回路700は、FF回路DFD3の出力QをD端子に受けるFF回路をさらに有するものとする。MUX2が、このFF回路DFD3の出力QをD端子に受けるFF回路の出力Qを出力バッファ702-2に供給するようにすることで、期間t delay3を信号CLKの3周期分の長さとすることができる。

40

【0086】

(実施例3)

本実施例のAD変換回路、およびAD変換回路を有する撮像装置について、実施例1と異なる点を中心に説明する。

【0087】

図8は本実施例の撮像装置の構成を示した図である。図1に示した部材と同じ機能を有する部材は、図8においても、図1で付した符号と同じ符号が付されている。選択回路210の構成は、図2(b)の構成に対し、信号TEST DATAの代わりに、タイミング制御部190から信号TESTが入力される点を除いて、同じである。

50

## 【0088】

A D変換部320は、テスト信号生成回路1000と、OR回路1700を有する。OR回路1000は、テスト信号生成回路1000が出力する信号TEST\_LATCHと、比較器140が出力する信号LATCHの一方がHiとなると、Hiの信号MLATCHを列メモリ180に供給する。また、テスト信号生成回路1000には選択回路210が供給する信号MDATAが入力される。本実施例のA D変換回路320は、2列の比較器140に対応して1つのテスト信号生成回路1000が設けられた組を、複数有する。各々が、対応する列メモリ180に信号TEST\_LATCHを供給する複数のテスト信号生成回路1000と、タイミング制御部190が供給する信号TESTに基づいて、信号MDATAを供給する選択回路210とが、本実施例の信号生成部である。また、テストラッチ信号である信号TEST\_LATCHを各々が供給する複数のテスト信号生成回路1000の各々が、本実施例のテストラッチ信号供給部である。また、テストデジタル信号である信号MDATAを供給する選択回路210は、本実施例のテストデジタル信号供給部である。10

## 【0089】

図8に示したA D変換回路320は、タイミング制御部190が供給する信号TESTは、選択回路210に入力される。

## 【0090】

本実施例のA D変換回路320の動作は、列メモリ180の検査に関し、図5に示した動作と同じとすることができます。テスト信号生成回路1000は、信号MDATAの信号レベルがHiからLoに遷移してから期間t delayの経過後、信号TEST\_LATCHの信号レベルをHiからLoとする。これにより、本実施例のA D変換回路320は、実施例1と同じ効果を得ることができます。20

## 【0091】

さらに本実施例のA D変換回路320は、2列の比較器140に対応して1つのテスト信号生成回路1000が設けられた組を、複数有する。実施例1のA D変換回路320では、1つのテスト信号生成回路200が複数の列メモリ180の全てに共通の信号TEST\_LATCHを供給していた。テスト信号供給線205には寄生容量と寄生抵抗が存在する。従って、信号TEST\_LATCHの伝送経路の長い列メモリ180は、信号TEST\_LATCHの伝送経路の短い列メモリ180に比して、信号TEST\_LATCHがHiからLoに遷移するタイミングが遅くなる。同じく、データ信号線181も、寄生容量と寄生抵抗を有している。よって、信号MDATAの伝送経路の長い列メモリ180は、信号MDATAの伝送経路の短い列メモリ180に対して、時刻t53の信号MDATAがHiからLoに遷移するタイミングが遅くなる。従って、実施例1のA D変換回路300では、テスト信号供給線205と、データ信号線181とで、信号の遅延の度合いが異なると、複数の列メモリ180の間で、期間t delayの長さが異なる。これにより、実施例1のA D変換回路300では、列メモリ180の検査の精度が低下することができた。30

## 【0092】

一方、本実施例のA D変換回路320では、複数の信号生成回路1000の各々が、各々に対応する列メモリ180に供給される信号MDATAを用いて、信号MLATCHを生成する。これにより、本実施例のA D変換回路320は、複数の列メモリ180の間で、期間t delayの長さを揃えやすくすることができる。よって、本実施例のA D変換回路320は、実施例1のA D変換回路300に対して、列メモリ180の検査の精度を向上させることができる。40

## 【0093】

尚、本実施例のA D変換回路320は、2列の列メモリ180に対し、1つのテスト信号生成回路1000が設けられていた。A D変換回路320は、1列の列メモリ180に対し、1つのテスト信号生成回路1000が設けられていても良い。また、A D変換回路320は、少なくとも2つのテスト信号生成回路1000を有していれば良い。つまり、50

A D 変換回路 320 に配された複数の列メモリ 180 の列数が A ( A は 2 以上の整数 ) であって、1つのテスト信号生成回路 1000 が、A - B 列 ( B は 1 以上の整数 ) の列メモリ 180 に対応して設けられている。そして、他の 1 つのテスト信号生成回路 1000 が B 列の列メモリ 180 に対応して設けられていても良い。この構成であっても、実施例 1 の A D 変換回路 300 に対して、列メモリ 180 の検査の精度の向上の効果を得ることができる。

#### 【 0094 】

##### ( 実施例 4 )

本実施例の A D 変換回路、および A D 変換回路を有する撮像装置について、実施例 1 と異なる点を中心に説明する。

10

#### 【 0095 】

図 9 は、本実施例の撮像装置 100 の構成を示した図である。本実施例の撮像装置 100 は、A D 変換回路 330 を有する。A D 変換回路 330 は、複数の列メモリ 180 の各々が、通常ビットメモリ 1100 に加えて、冗長ビットメモリ 1200 を有する。また、A D 変換回路 330 は、補正部 1110 を有する。撮像装置 100 は、信号処理部 1910 を有する。信号処理部 1910 の機能は、補正部 1110 に信号を供給する点を除き、実施例 1 の信号処理部 191 と同じ機能を有する。

#### 【 0096 】

本実施例の A D 変換回路 330 の列メモリ 180 の検査の動作は、図 5 に示した動作と同じとすることができる。

20

#### 【 0097 】

図 10 は、本実施例の A D 変換回路 330 の列メモリ 180 の検査のフローチャートである。ステップ S10 からステップ S15 までの各々のステップは、図 4 に示した、ステップ S0 からステップ S5 までの各々のステップと同じである。

#### 【 0098 】

ステップ S16 に、信号処理部 1910 は、複数の列メモリ 180 の各々において、通常ビットメモリ 1100 のうち、所定の期間  $t_{delay}$  に信号レベルが変化しなかった不良ビットメモリの数を検出する。そして、ステップ S16 において、その不良ビットメモリの数が、冗長ビットメモリ 1200 の数以下であるか否かを判定する。不良ビットメモリの数が、冗長ビットメモリ 1200 の数以下の列メモリ 180 については、信号処理部 1910 は、補正部 1110 に、当該列メモリ 180 において使用する冗長ビットメモリ 1200 の数を指示する制御信号を供給する。補正部 1110 は、不良ビットメモリの数が、冗長ビットメモリ 1200 の数以下の列メモリ 180 に対して、冗長ビットメモリ 1200 の使用を指示する信号を供給する。この信号を補正部 1110 から受けた列メモリ 180 は、不良ビットメモリの代わりに冗長ビットメモリ 1200 を用いて、選択回路 210 が供給する信号 M DATA をホールドする。

30

#### 【 0099 】

本実施例の A D 変換回路 330 は、通常ビットメモリ 1100 と冗長ビットメモリ 1200 とを合わせて、N 個 ( $N > 1$ ) のビットメモリを、複数の列メモリ 180 の各々が有する。通常ビットメモリ 1100 は、複数の列メモリ 180 の各々において、M ビット ( $M < N$ ) のデジタル信号をホールドするために、M 個設けられている。信号処理部 1910 は、複数の列メモリ 180 の各々について、M 個の通常ビットメモリ 1100 のうちの不良ビットメモリの数を検出する。そして、信号処理部 1910 は、検出した不良ビットメモリの数の検出結果を補正部 1110 に出力する。そして、補正部 1110 は、N 個と M 個の差の個数の冗長ビットメモリ 1200 の少なくとも 1 つに、不良ビットメモリの代わりに、アナログ信号に基づくデジタル信号をホールドするように動作させる。

40

#### 【 0100 】

実施例 1 の A D 変換回路 300 では、不良ビットメモリを有する列メモリ 180 が存在すると、A D 変換回路 300 を製造工程に戻し、列メモリ 180 の修復を行うことがある。この場合には、列メモリ 180 の修復を行う分、A D 変換回路 300 の歩留まりが低下

50

する。

【0101】

一方、本実施例のA D変換回路320は、複数の列メモリ180の各々が冗長ビットメモリ1200を有する。これにより、列メモリ180に不良ビットメモリが存在しても、不良ビットメモリの代わりに冗長ビットメモリ1200を使用することによって、列メモリ180は良好に動作することができる。従って、本実施例のA D変換回路320は実施例1のA D変換回路300に対して、列メモリ180の修復の機会を減らすことができる。これにより、本実施例のA D変換回路320は、実施例1のA D変換回路300に対して、歩留まりを向上させることができる。

【0102】

尚、本実施例では、冗長ビットメモリ1200の検査を省略する例を説明した。別の例として、冗長ビットメモリ1200と通常ビットメモリ1100とを検査する例について説明する。

【0103】

A D変換回路320は、図10で述べたステップS10からステップS12まで行う。その後のステップS13において、複数の列メモリ180の各々は、通常ビット1100と冗長ビットメモリ1200の両方を用いて、信号TEST\_D A T Aを保持する。その後、A D変換回路320はステップS14を行う。そして、信号処理部1910は、ステップS15に、複数の列メモリ180の各々について、複数の列メモリ180の各々が保持した信号の信号レベルと期待値とが等しいか否か判定する。そして、期待値とは異なる信号レベルの信号を保持した列メモリ180について、信号処理部1910は、図10のステップS16の代わりに、次に述べる動作を行う。信号処理部1910は、通常ビットメモリ1100のビット数と冗長ビットメモリ1200のビット数との和から、不良ビットメモリのビット数を引いた数が、冗長ビットメモリ1200のビット数以下であるか否かを判定する。この判定結果が「Yes」である場合には、信号処理部1910は、図10に示したステップS17として、「Yes」の判定結果を受けた列メモリ180を正常と判定する。一方、判定結果が「No」である場合には、信号処理部1910は、図10に示したステップS18として、「No」の判定結果を受けた列メモリ180を不良と判定する。

【0104】

この検査により、A D変換回路320は、通常ビットメモリ1100に加えて、冗長ビットメモリ1200においても、不良ビットメモリが無いか検査することができる。

【0105】

(実施例5)

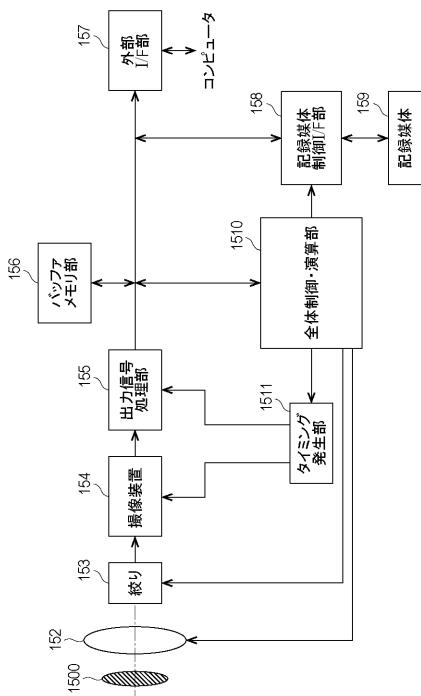

上記の実施例1から実施例4で述べた撮像装置は種々の撮像システムに適用可能である。撮像システムの一例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラなどがあげられる。図11に、撮像システムの一例としてデジタルスチルカメラに本発明の実施例1から実施例4のいずれかの撮像装置を適用した撮像システムの模式図を示す。

【0106】

図11に例示した撮像システムは、撮像装置154、レンズの保護のためのバリア1500、被写体の光学像を撮像装置154に結像させるレンズ152及びレンズ152を通過する光量を可変にするための絞り153を有する。レンズ152及び絞り153は撮像装置154に光を集光する光学系である。また、図11に例示した撮像システムは撮像装置154より出力される出力信号の処理を行う出力信号処理部155を有する。

【0107】

出力信号処理部155は、撮像装置154が出力するアナログ信号をデジタル信号に変換するA D変換を行う。また、出力信号処理部155はその他、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。図11に例示した撮像システムはさらに、画像データを一時的に記憶するためのバッファメモリ部156、外部コンピュータ等

10

20

30

40

50

と通信するための外部インターフェース部（外部I/F部）157を有する。さらに撮像システムは、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体159、記録媒体159に記録又は読み出しを行うための記録媒体制御インターフェース部（記録媒体制御I/F部）158を有する。なお、記録媒体159は撮像システムに内蔵されてもよく、着脱可能であってもよい。

#### 【0108】

さらに撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510、撮像装置154と出力信号処理部155に各種タイミング信号を出力するタイミング発生部1511を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置154と、撮像装置154から出力された出力信号を処理する出力信号処理部155とを有すればよい。以上のように、本実施例の撮像システムは、撮像装置154を適用して撮像動作を行うことが可能である。

10

#### 【符号の説明】

#### 【0109】

- |     |           |

|-----|-----------|

| 100 | 撮像装置      |

| 110 | 画素アレイ     |

| 120 | 垂直走査回路    |

| 130 | 水平走査回路    |

| 140 | 比較器       |

| 150 | ランプ信号生成回路 |

| 160 | カウンタ      |

| 170 | OR回路      |

| 180 | 列メモリ      |

| 190 | タイミング制御部  |

| 191 | 信号処理部     |

| 200 | テスト信号生成回路 |

| 210 | 選択回路      |

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 中村 恒一

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 斎藤 正貴

(56)参考文献 特開2013-026932(JP, A)

特開2011-034642(JP, A)

特開平09-251796(JP, A)

特開2013-065924(JP, A)

特開2013-085109(JP, A)

米国特許出願公開第2005/0219107(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03M 1/10

G01R 31/28

H03M 1/56

H04N 5/374

H04N 5/378

JSTPlus/JMEDPlus/JST7580(JDreamIII)