(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2023-99382

(P2023-99382A)

(43)公開日 令和5年7月13日(2023.7.13)

## (51)国際特許分類

H 01 L 27/146 (2006.01)

H 04 N 25/70 (2023.01)

F I

H 01 L 27/146

H 01 L 27/146

H 04 N 5/369テーマコード(参考)

4 M 1 1 8

5 C 0 2 4

審査請求 未請求 請求項の数 27 O L (全34頁)

(21)出願番号 特願2022-9(P2022-9)

(22)出願日 令和4年1月1日(2022.1.1)

(71)出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

(72)発明者 関根 寛

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 森本 和浩

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

Fターム(参考) 4M118 AA05 AB01 BA19 CA03

最終頁に続く

## (54)【発明の名称】 光電変換装置および光電変換システム

## (57)【要約】

【課題】光電変換装置の周辺領域に入射した光による影響を低減するために有利な技術を提供する。

【解決手段】光電変換装置は、複数の画素を有する画素アレイ領域と、前記画素アレイ領域の周辺に配置された周辺領域とを含む半導体層を有し、前記半導体層は、第1面および第2面を有し、前記画素アレイ領域の各画素は、前記第1面の側に配置された第1導電型の第1半導体領域と、前記第2面の側に配置された第2導電型の第2半導体領域と、を含み、前記第1半導体領域と前記第2半導体領域との間に、アバランシェ倍増動作を引き起こしうる所定電圧が供給され、前記周辺領域は、前記第1面の側に配置された前記第1導電型の第3半導体領域と、前記第3半導体領域から離隔して配置された前記第2導電型の第4半導体領域と、を含み、前記第4半導体領域は、前記第2面に対して平行に延びた延設部を含み、前記第3半導体領域と前記第4半導体領域との間に電圧が供給される。

【選択図】図11

**【特許請求の範囲】****【請求項 1】**

複数の画素を有する画素アレイ領域と、前記画素アレイ領域の周辺に配置された周辺領域とを含む半導体層を有する光電変換装置であって、

前記半導体層は、第1面および第2面を有し、

前記画素アレイ領域の各画素は、前記第1面の側に配置された第1導電型の第1半導体領域と、前記第2面の側に配置された第2導電型の第2半導体領域と、を含み、前記第1半導体領域と前記第2半導体領域との間に、アバランシェ倍増動作を引き起こしうる所定電圧が供給され、

前記周辺領域は、前記第1面の側に配置された前記第1導電型の第3半導体領域と、前記第3半導体領域から離隔して配置された前記第2導電型の第4半導体領域と、を含み、前記第4半導体領域は、前記第2面に対して平行に延びた延設部を含み、前記第3半導体領域と前記第4半導体領域との間に電圧が供給される、

ことを特徴とする光電変換装置。

**【請求項 2】**

前記第3半導体領域と前記第4半導体領域との間に供給される電圧が前記所定電圧である、

ことを特徴とする請求項1に記載の光電変換装置。

**【請求項 3】**

前記第1面からの前記延設部の深さは、前記第1面からの前記第2半導体領域の深さと等しい、

ことを特徴とする請求項1又は2に記載の光電変換装置。

**【請求項 4】**

前記第2半導体領域および前記延設部に接するように配置されたピニング層を更に備える、

ことを特徴とする請求項1乃至3のいずれか1項に記載の光電変換装置。

**【請求項 5】**

前記第1面からの前記第3半導体領域の深さは、前記第1面からの前記第1半導体領域の深さと等しい、

ことを特徴とする請求項1又は2に記載の光電変換装置。

**【請求項 6】**

前記画素アレイ領域と前記周辺領域との間に前記第2導電型の分離領域が配置されている、

ことを特徴とする請求項1乃至4のいずれか1項に記載の光電変換装置。

**【請求項 7】**

前記第4半導体領域と前記分離領域とが電気的に接続されている、

ことを特徴とする請求項6に記載の光電変換装置。

**【請求項 8】**

前記分離領域の中に溝が設けられ、少なくとも前記溝の表面を覆うように絶縁体が配置されている、

ことを特徴とする請求項6又は7に記載の光電変換装置。

**【請求項 9】**

前記溝は、前記半導体層を貫通するように配置されている、

ことを特徴とする請求項8に記載の光電変換装置。

**【請求項 10】**

前記溝は、前記分離領域を前記画素アレイ領域の側の第1分離領域と前記周辺領域の側の第2分離領域とに電気的に分離するように配置されている、

ことを特徴とする請求項9に記載の光電変換装置。

**【請求項 11】**

前記第1分離領域に対して電位を与える第1導電路、および、前記第2分離領域に対し

10

20

30

40

50

て電位を与える第2導電路が前記半導体層に対して積層された配線構造の中に設けられている、

ことを特徴とする請求項10に記載の光電変換装置。

**【請求項12】**

前記第1導電路と前記第2導電路とは、前記配線構造の中において電気的に接続されている、

ことを特徴とすることを特徴とする請求項11に記載の光電変換装置。

**【請求項13】**

前記分離領域の中に溝が設けられ、

前記第2半導体領域および前記第4半導体領域に接するように、かつ、前記溝の表面を覆うように配置されたピニング層を更に備える、10

ことを特徴とする請求項6又は7に記載の光電変換装置。

**【請求項14】**

前記複数の画素における互いに隣り合う画素の間に前記第2導電型の分離領域が配置されている、

ことを特徴とする請求項6乃至13のいずれか1項に記載の光電変換装置。

**【請求項15】**

前記第2面の上に配置された遮光膜を更に備え、

前記遮光膜は、前記第4半導体領域と電気的に接続されている、

ことを特徴とする請求項1乃至14のいずれか1項に記載の光電変換装置。20

**【請求項16】**

前記周辺領域には、前記第3半導体領域を含む複数の第3半導体領域が所定ピッチで配置され、

前記所定ピッチは、前記複数の画素の配列ピッチよりも大きい、

ことを特徴とする請求項1乃至15のいずれか1項に記載の光電変換装置。

**【請求項17】**

前記第4半導体領域は、前記延設部から前記第1面に向かって突出した突出部を更に含む、

ことを特徴とする請求項1乃至16のいずれか1項に記載の光電変換装置。

**【請求項18】**

前記延設部には、前記第3半導体領域を含む複数の第3半導体領域が所定ピッチで配置され、30

前記第4半導体領域は、前記延設部から前記第1面に向かって突出した複数の突出部を更に含み、

前記複数の突出部は、前記所定ピッチで配置されている、

ことを特徴とする請求項1乃至15のいずれか1項に記載の光電変換装置。

**【請求項19】**

前記複数の第3半導体領域および前記複数の突出部は、平面視において交互に配置されている、

ことを特徴とする請求項18に記載の光電変換装置。40

**【請求項20】**

前記第4半導体領域は、前記延設部から前記第1面に向かって突出した複数の第2突出部を更に含み、

前記複数の第2突出部は、前記所定ピッチで配置され、

前記複数の突出部および前記複数の第2突出部は、平面視において交互に配置されている、

ことを特徴とする請求項18に記載の光電変換装置。

**【請求項21】**

前記複数の第2突出部は、前記第2面からの深さが前記複数の突出部より小さく、平面視において前記複数の第3半導体領域と重なるように配置されている、50

ことを特徴とする請求項 20 に記載の光電変換装置。

**【請求項 22】**

前記複数の画素における互いに隣り合う画素の間に前記第 2 導電型の画素分離領域が配置され、

前記第 1 面に平行かつ前記複数の突出部の配列方向において、前記複数の突出部の各々の幅は、前記画素分離領域の幅より大きい、

ことを特徴とする請求項 18 乃至 21 のいずれか 1 項に記載の光電変換装置。

**【請求項 23】**

前記第 4 半導体領域は、前記延設部に接するように前記延設部と前記第 1 面との間に前記延設部に沿って配置された少なくとも 1 つの第 2 延設部を更に含む、

10

ことを特徴とする請求項 18 乃至 22 のいずれか 1 項に記載の光電変換装置。

**【請求項 24】**

前記周辺領域は、前記第 3 半導体領域と前記第 4 半導体領域との間に、前記第 3 半導体領域に近接して配置され、前記第 1 半導体領域よりも前記第 1 導電型の不純物濃度が低い前記第 1 導電型の第 5 半導体領域を更に含む、

ことを特徴とする請求項 1 乃至 23 のいずれか 1 項に記載の光電変換装置。

**【請求項 25】**

前記第 2 導電型の前記第 4 半導体領域は、前記第 2 面に沿って配置されたピニング層によって前記半導体層における前記第 2 面の近傍に誘起される電荷によって形成される、

20

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の光電変換装置。

**【請求項 26】**

前記第 5 半導体領域は、前記第 3 半導体領域を取り囲むように配置されている、

ことを特徴とする請求項 24 に記載の光電変換装置。

**【請求項 27】**

請求項 1 乃至 26 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置が出力する信号を処理する信号処理部と、を有することを特徴とする光電変換システム。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、光電変換装置および光電変換システムに関する。

30

**【背景技術】**

**【0002】**

特許文献 1 には、画素からのクロストークを低減し、D C R (ダークカウントレート) を抑制することを目的とする A P D (アバランシェフォトダイオード) が記載されている。該 A P D は、高電界領域と、隣接する画素と分離するための分離領域と、該分離領域の側壁に電子をトラップするホール蓄積領域とを備え、該ホール蓄積領域がアノードと電気的に接続された構成を有する。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【特許文献 1】特開 2018 - 201005 号公報**

40

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

光電変換装置の半導体基板は、画素アレイ領域と、画素アレイ領域の周辺に配置された周辺領域を有しうる。周辺領域に対して意図せず光が入射すると、光電変換によって電荷 (電子および正孔) が発生し、これが画素アレイの画素に入りうる。あるいは、光電変換によって発生した電荷が再結合して光を発生すると、これが画素アレイの画素、例えば遮光画素 (O B 画素) によって検出されうる。

50

**【 0 0 0 5 】**

本発明は、光電変換装置の周辺領域に入射した光による影響を低減するために有利な技術を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 6 】**

本発明の1つの側面は、複数の画素を有する画素アレイ領域と、前記画素アレイ領域の周辺に配置された周辺領域とを含む半導体層を有する光電変換装置に係り、前記半導体層は、第1面および第2面を有し、前記画素アレイ領域の各画素は、前記第1面の側に配置された第1導電型の第1半導体領域と、前記第2面の側に配置された第2導電型の第2半導体領域と、を含み、前記第1半導体領域と前記第2半導体領域との間に、アバランシェ倍増動作を引き起こしうる所定電圧が供給され、前記周辺領域は、前記第1面の側に配置された前記第1導電型の第3半導体領域と、前記第3半導体領域から離隔して配置された前記第2導電型の第4半導体領域と、を含み、前記第4半導体領域は、前記第2面に対して平行に延びた延設部を含み、前記第3半導体領域と前記第4半導体領域との間に電圧が供給される。

10

**【発明の効果】****【 0 0 0 7 】**

本発明によれば、光電変換装置の周辺領域に入射した光による影響を低減するために有利な技術が提供される。

**【図面の簡単な説明】**

20

**【 0 0 0 8 】**

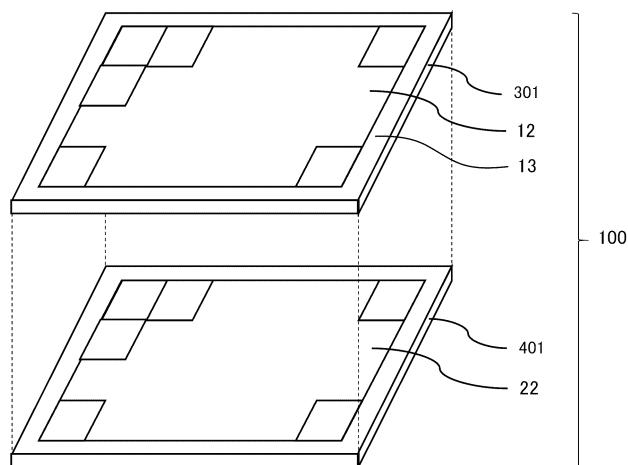

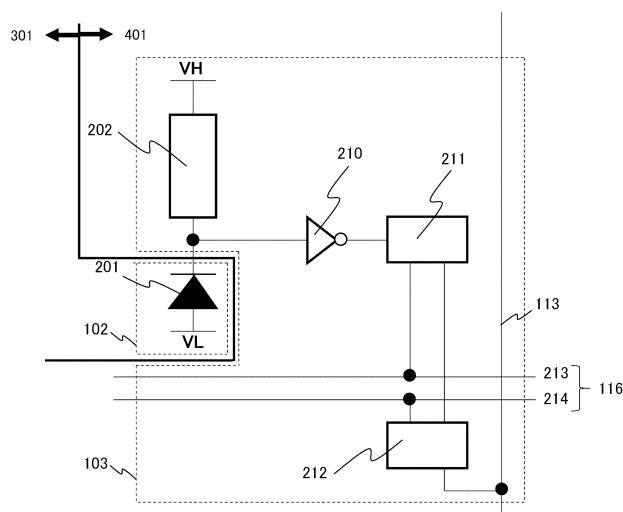

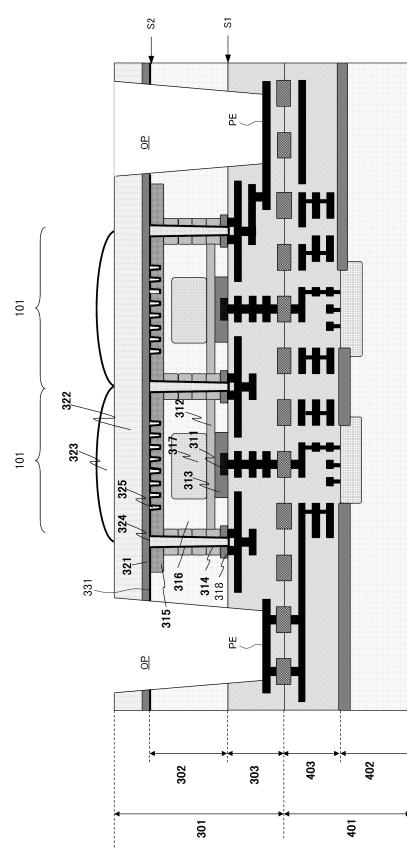

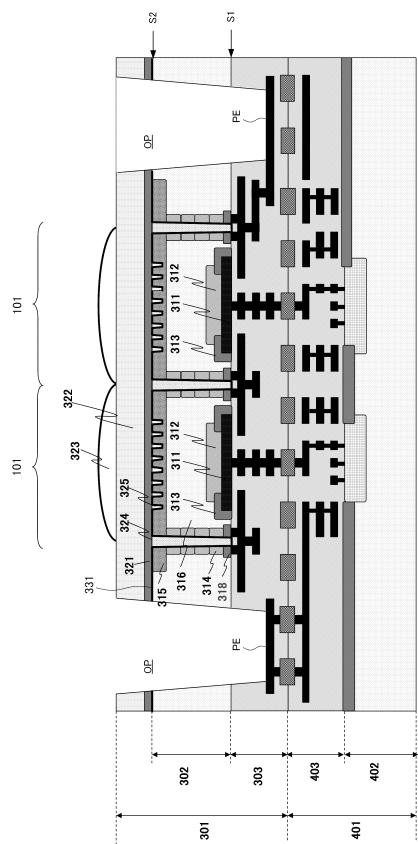

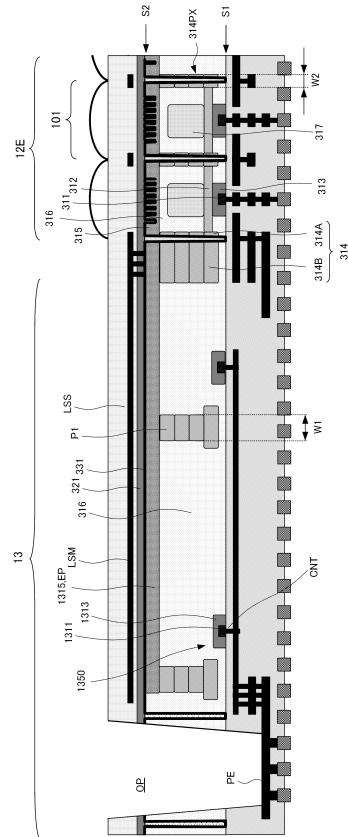

【図1】実施形態の光電変換装置の基本的な構成を示す図。

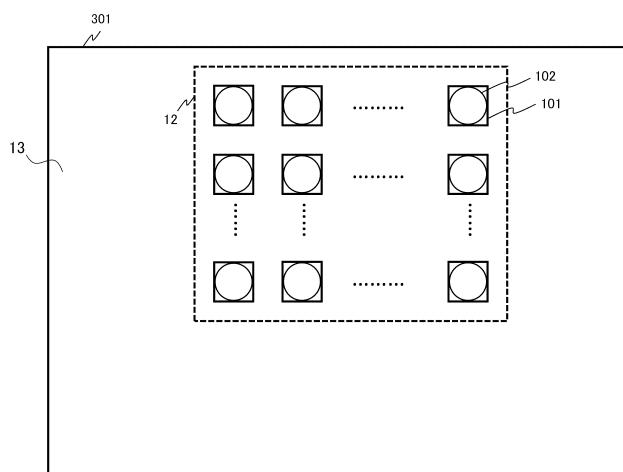

【図2】センサ基板の構成例を示す図。

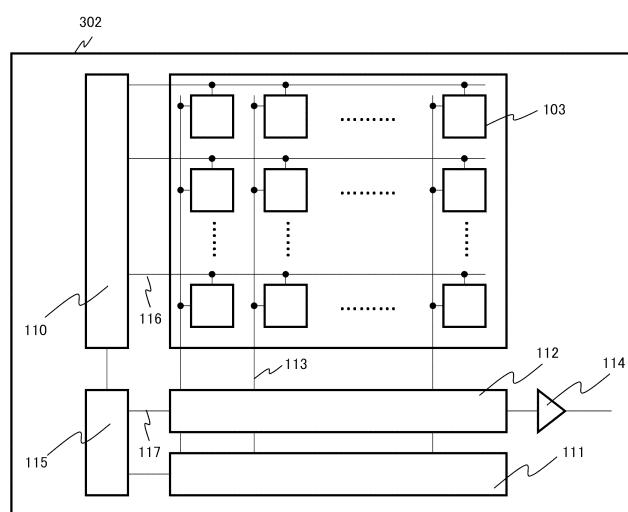

【図3】回路基板の構成例を示す図。

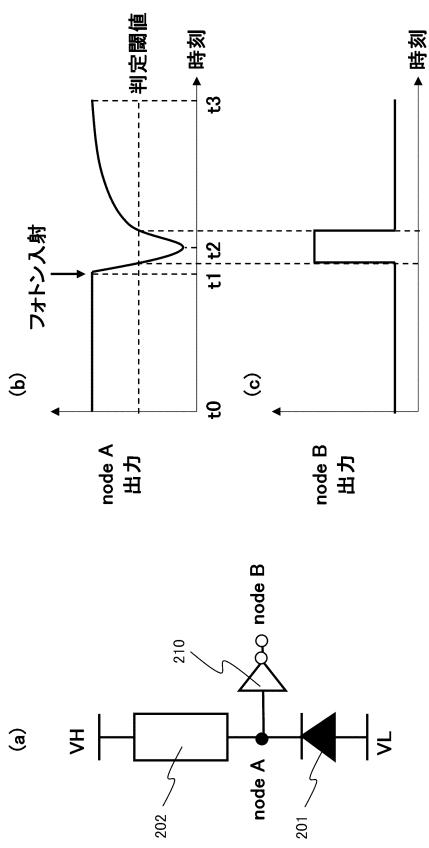

【図4】1つの画素及びの信号処理部の等価回路図。

【図5】画素の動作を説明する図。

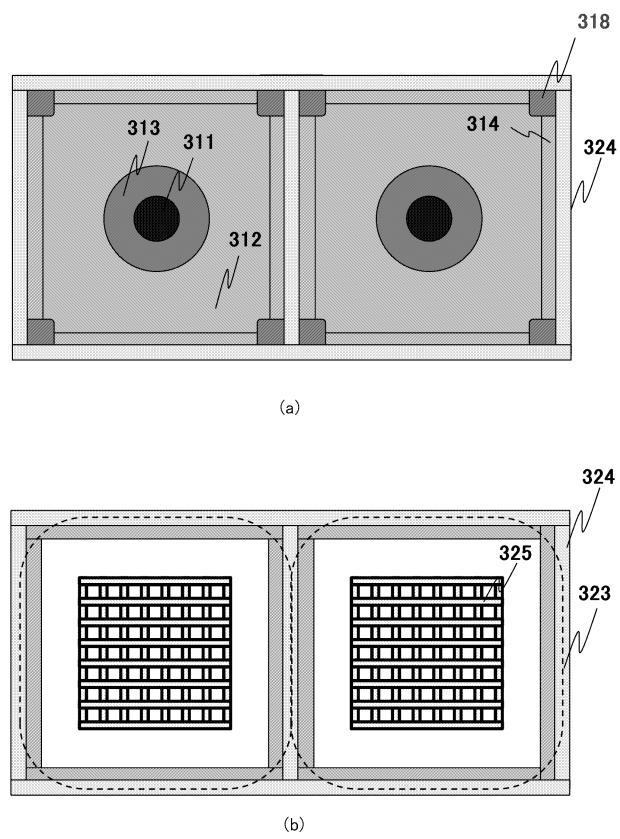

【図6】画素の第1構成例を示す図。

【図7A】画素の第1構成例を示す図。

【図7B】画素の第1構成例を示す図。

【図8】画素の第2構成例を示す図。

30

【図9A】画素の第2構成例を示す図。

【図9B】画素の第2構成例を示す図。

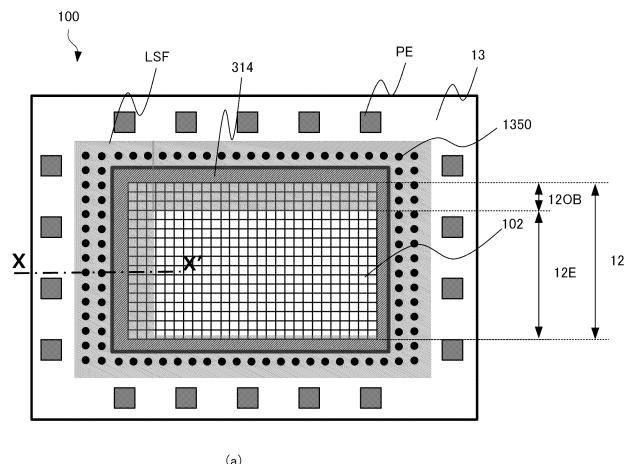

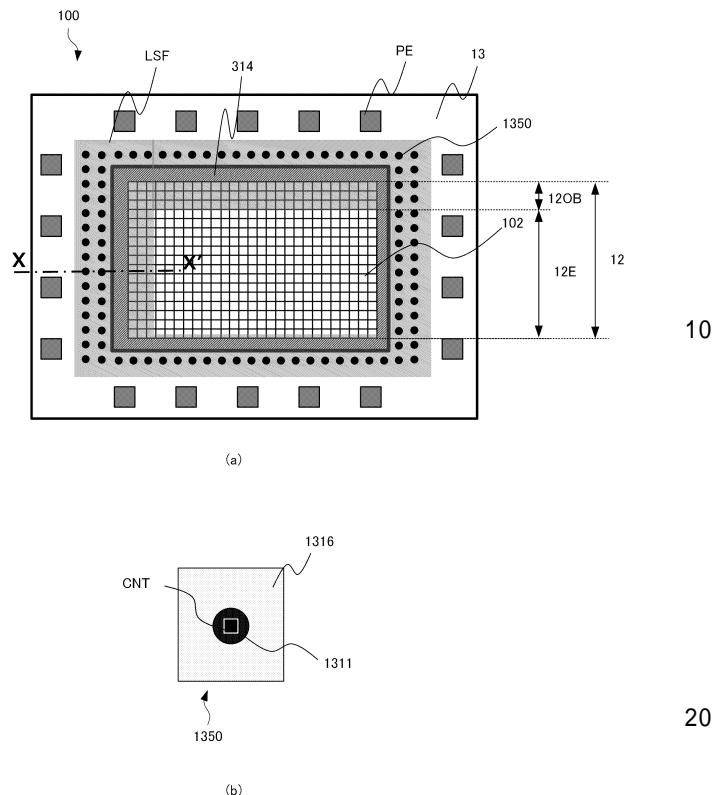

【図10】第1実施形態の光電変換装置の構成を示す平面図。

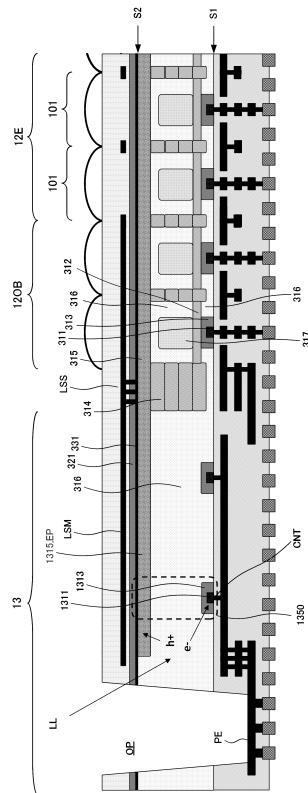

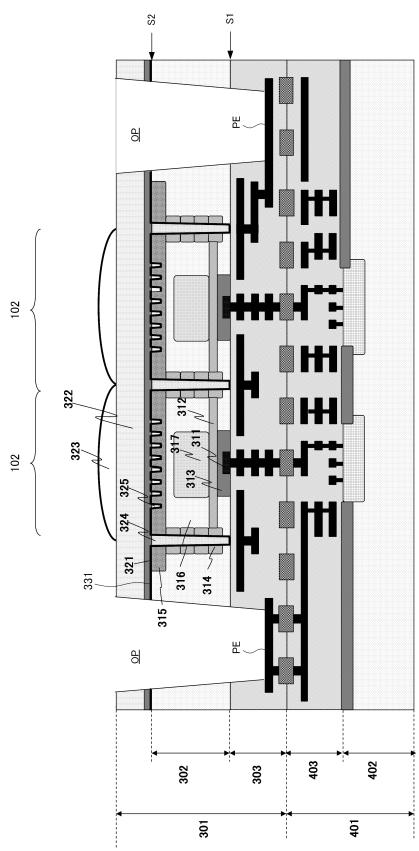

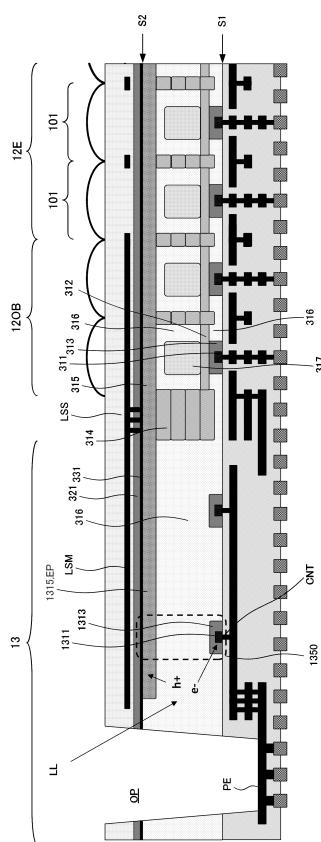

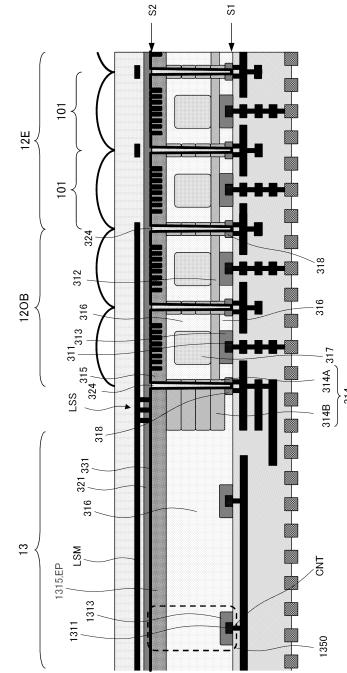

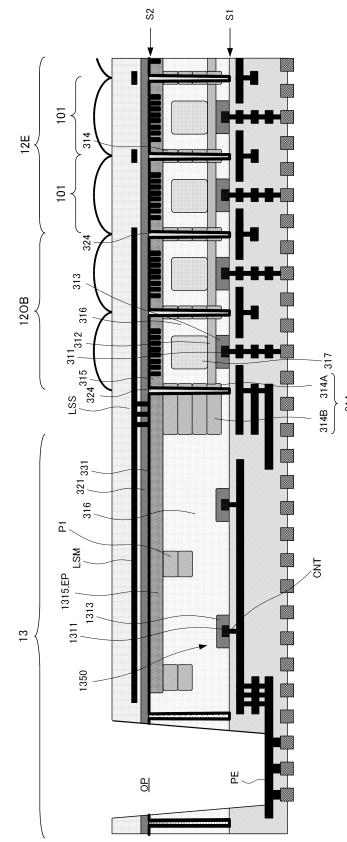

【図11】第1実施形態の光電変換装置の構成を示す断面図。

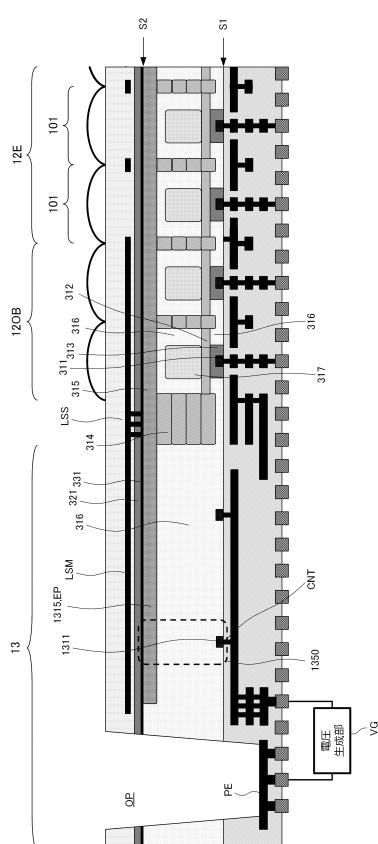

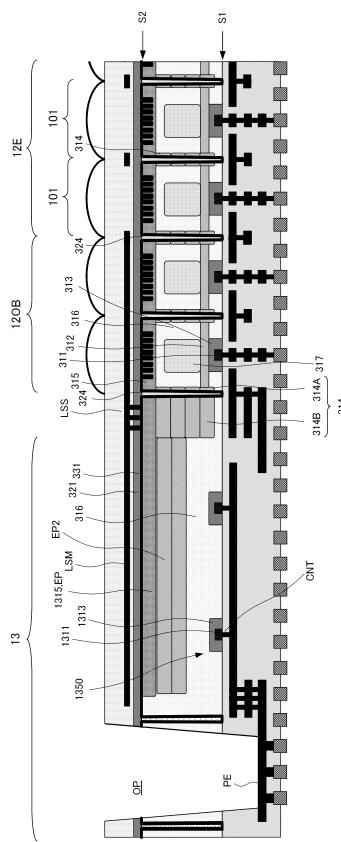

【図12】第2実施形態の光電変換装置の構成を示す平面図。

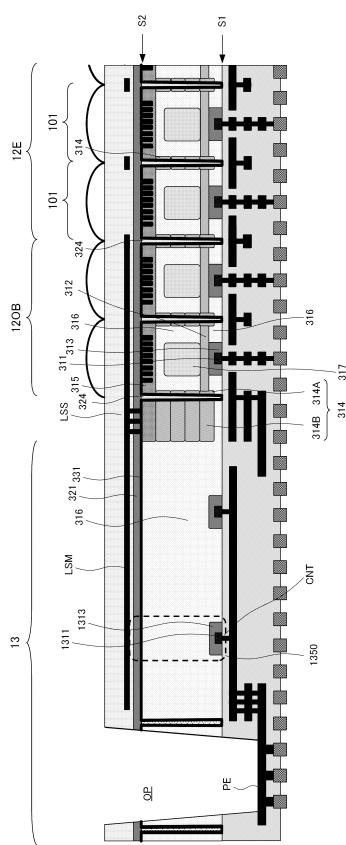

【図13】第2実施形態の光電変換装置の構成を示す断面図。

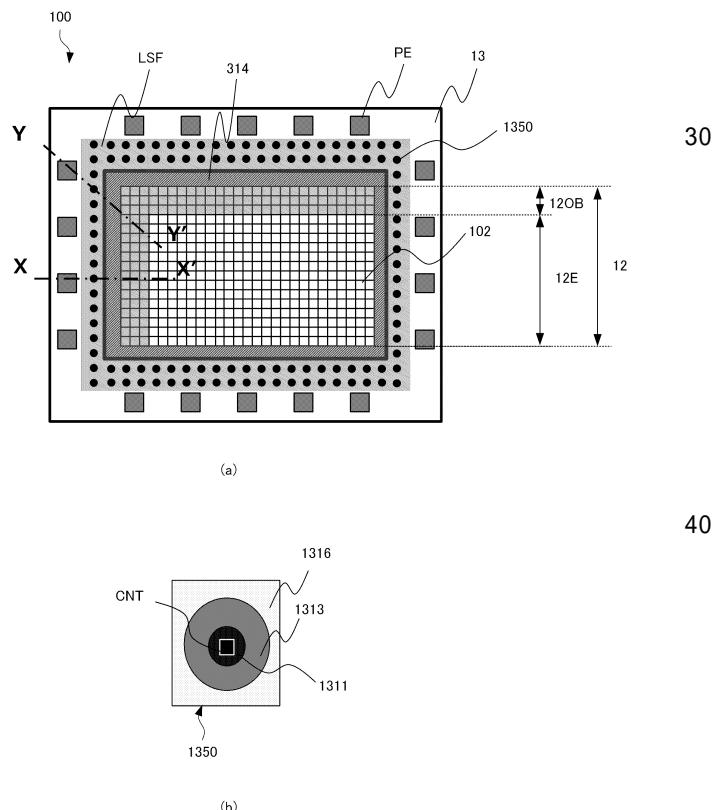

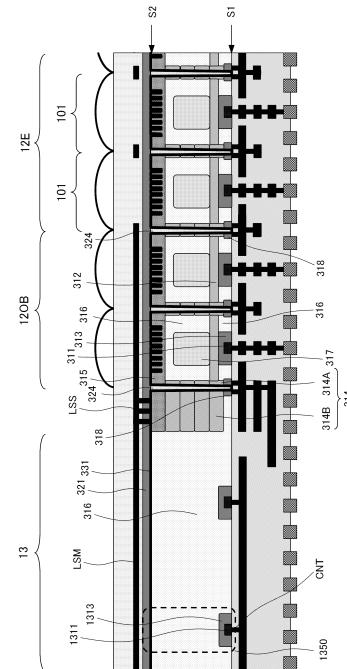

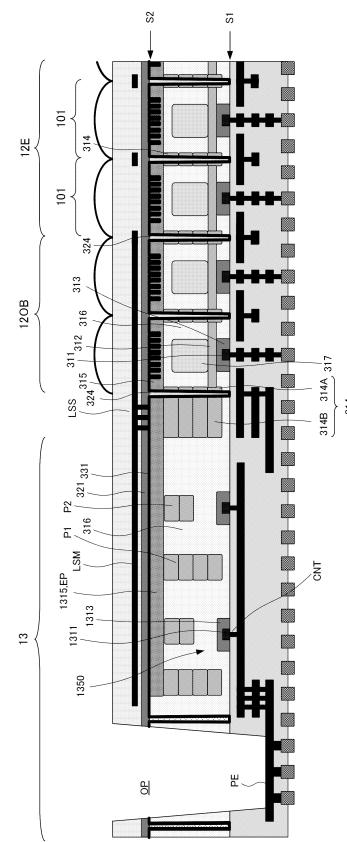

【図14】第3実施形態の光電変換装置の構成を示す平面図。

【図15A】第3実施形態の光電変換装置の構成を示す断面図。

【図15B】第3実施形態の光電変換装置の構成を示す断面図。

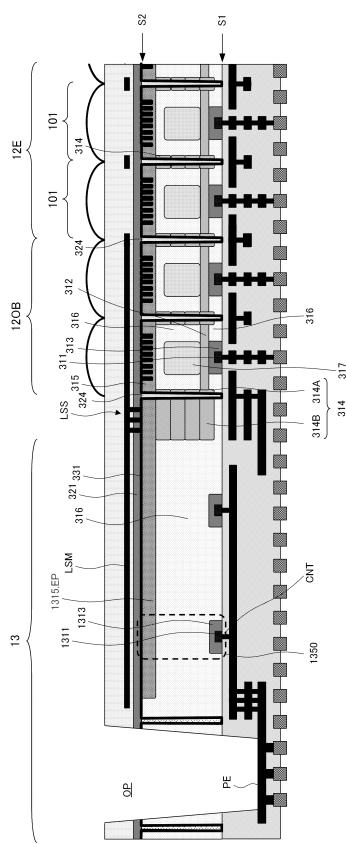

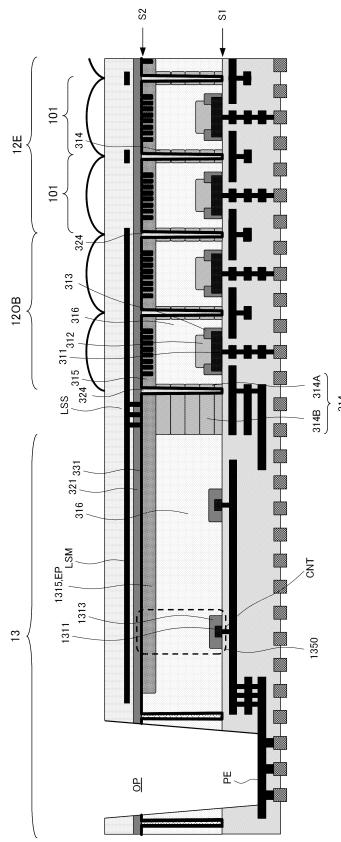

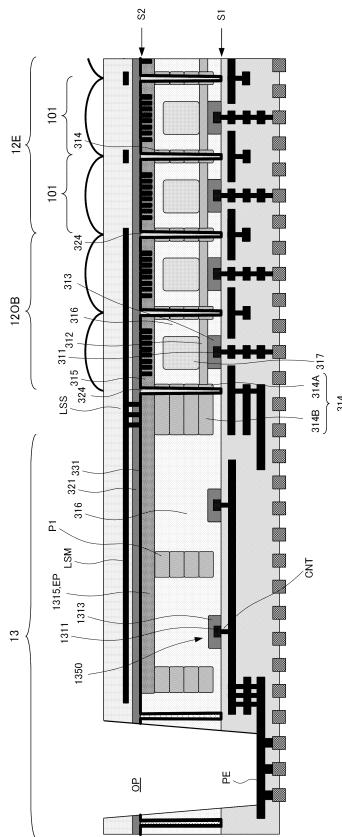

【図16A】第4実施形態の光電変換装置の構成を示す断面図。

【図16B】第4実施形態の光電変換装置の構成を示す断面図。

40

【図17】第5実施形態の光電変換装置の構成を示す断面図。

【図18】第6実施形態の光電変換装置の構成を示す断面図。

【図19】第7実施形態の光電変換装置の構成を示す断面図。

【図20】第8実施形態の光電変換装置の構成を示す断面図。

【図21】第9実施形態の光電変換装置の構成を示す断面図。

【図22】第10実施形態の光電変換装置の構成を示す断面図。

【図23】光電変換システムの構成を示す図。

【図24】光電変換システムの構成を示す図。

【図25】光電変換システムの構成を示す図。

50

【図26】光電変換システムの構成を示す図。

【図27】光電変換システムの構成を示す図。

【図28】光電変換システムの構成を示す図。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

10

【0010】

以下、図面に基づいて本発明の実施の形態を詳細に説明する。なお、以下の説明では、必要に応じて特定の方向や位置を示す用語（例えば、「上」、「下」、「右」、「左」及び、それらの用語を含む別の用語）を用いる。それらの用語の使用は図面を参照した実施形態の理解を容易にするためであって、それらの用語の意味によって本発明の技術的範囲が限定されるものではない。

【0011】

本明細書において、平面視とは、半導体層の光入射面に対して垂直な方向から視ることである。また、断面視とは、半導体層の光入射面と垂直な方向における面をいう。なお、微視的に見て半導体層の光入射面が粗面である場合は、巨視的に見たときの半導体層の光入射面を基準として平面視を定義する。

20

【0012】

以下の説明において、アバランシェフォトダイオード（A P D）のアノードを固定電位とし、カソード側から信号を取り出している。したがって、信号電荷と同じ極性の電荷を多数キャリアとする第1導電型の半導体領域とはN型半導体領域であり、信号電荷と異なる極性の電荷を多数キャリアとする第2導電型の半導体領域とはP型半導体領域である。なお、A P Dのカソードを固定電位とし、アノード側から信号を取り出す場合でも本発明は成立する。この場合は、信号電荷と同じ極性の電荷を多数キャリアとする第1導電型の半導体領域はP型半導体領域であり、信号電荷と異なる極性の電荷を多数キャリアとする第2導電型の半導体領域とはN型半導体領域である。以下では、A P Dの一方のノードを固定電位とする場合について説明するが、両方のノードの電位が変動してもよい。

30

【0013】

本明細書において、単に「不純物濃度」という用語が使われた場合、逆導電型の不純物によって補償された分を差し引いた正味の不純物濃度を意味している。つまり、「不純物濃度」とは、NETドーピング濃度を指す。P型の添加不純物濃度がN型の添加不純物濃度より高い領域はP型半導体領域である。反対に、N型の添加不純物濃度がP型の添加不純物濃度より高い領域はN型半導体領域である。

【0014】

まず、後述する複数の実施形態の光電変換装置及びその駆動方法において共通する基本的な構成および駆動方法について、図1、図2、図3、図4、図5を参照しながら説明する。

40

【0015】

図1は、実施形態の光電変換装置100の基本構成を示す図である。ここでは、光電変換装置100が積層型の光電変換装置として構成された例を説明するが、本発明は、積層型以外の光電変換装置にも適用可能である。光電変換装置100は、例えば、センサ基板301と、回路基板401とを含む複数の基板が積層され、且つ、該複数の基板が電気的に接続されることにより構成されうる。センサ基板301は、後述する光電変換素子102を有する第1半導体層と、第1配線構造と、を有しうる。回路基板401は、後述する信号処理部103等の回路を有する第2半導体層と、第2配線構造と、を有しうる。光電変換装置100は、例えば、第2半導体層、第2配線構造、第1配線構造、第1半導体層

50

の順に積層して構成されうる。以下の実施形態として説明される光電変換装置は、例えば、裏面照射型の光電変換装置でありうるが、本発明に係る光電変換装置は、表面照射型の光電変換装置として構成されてもよい。

#### 【0016】

センサ基板301および回路基板401は、それぞれ、ウエハからダイシングされたチップであるうるが、これらの基板は、チップに限定されるものではない。例えば、各基板はウエハであってもよい。また、複数の基板はウエハ状態で積層された後にダイシングされていてもよいし、チップ化された後に複数のチップが積層あるいは接合されてもよい。

#### 【0017】

センサ基板301は、複数の画素を有する画素アレイ領域12と、画素アレイ領域12の周辺に配置された周辺領域13とを含む半導体層を含みうる。画素アレイ領域12の外縁とセンサ基板301の外縁との間の領域は、周辺領域13でありうる。周辺領域13には、能動素子等の回路素子が配置されてもよいし、能動素子等の回路素子が配置されなくてもよい。回路基板401は、画素アレイ領域12の画素によって検出された信号を処理する回路領域22を含む半導体層を含みうる。

#### 【0018】

図2は、センサ基板301の構成例を示す図である。画素アレイ領域12には、複数の画素101が複数の行および複数の列を構成するように2次元状アレイ状に配置されうる。各画素101は、アバランシェフォトダイオード(以下、APD)を含む光電変換素子102を含みうる。

#### 【0019】

画素アレイ領域12に配置された画素101は、画像を形成するための画素でありうる。しかし、センサ基板301あるいは光電変換装置100がTOF(Time of Flight)に適用される場合には、各画素101は、必ずしも画像を形成するための画素でなくてもよい。すなわち、画素101は、光が到達した時刻と光量を測定するための画素であってもよい。

#### 【0020】

図3は、回路基板401の構成を示す図である。回路基板401は、例えば、光電変換素子102で光電変換によって生成された電荷を処理する信号処理部103、読出回路112、制御パルス生成部115、水平走査回路部111、信号線113、垂直走査回路部110を含みうる。1つの信号処理部103は、1つの画素101に対して設けられうる。図2の光電変換素子102と図3の信号処理部103とは、画素101毎に設けられた接続配線を介して電気的に接続されうる。

#### 【0021】

垂直走査回路部110は、例えば、制御パルス生成部115から供給された第1制御パルスを受けて第2制御パルスを生成し、各画素101に第2制御パルスを供給するよう構成されうる。垂直走査回路部110は、例えば、シフトレジスタおよびアドレスデコーダ等の論理回路を含みうる。画素101の光電変換素子102から出力された信号は、その画素101に対応して設けられた信号処理部103で処理されうる。信号処理部103は、カウンタおよびメモリ等を含むことができ、メモリはデジタル値を保持しうる。

#### 【0022】

水平走査回路部111は、デジタル信号を保持した各画素101のメモリから信号を読み出すために、各列を順次に選択する第3制御パルスを信号処理部103に供給するよう構成されうる。回路基板401は、複数の信号線113を有しうる。複数の信号線113には、垂直走査回路部110により選択された行の画素101に割り当てられた信号処理部103から信号が出力される。複数の信号線113に出力された信号は、出回路114を介して、光電変換装置100の外部の記録部または信号処理部に出力されうる。

#### 【0023】

図2において、画素アレイ領域12における光電変換素子102あるいは画素101の配列は1次元状であってもよい。各信号処理部103は、少なくとも2つの光電変換素子

10

20

30

40

50

102あるいは画素101に対して割り当てられてもよい。

#### 【0024】

図2および図3に示すように、平面視で画素アレイ領域12に重なる領域に、複数の信号処理部103が配されうる。そして、平面視で、センサ基板301の外縁と画素アレイ領域12の外縁との間の領域に重なるように、垂直走査回路部110、水平走査回路部111、読出回路112、出力回路114、制御パルス生成部115が配されうる。言い換えると、平面視において、センサ基板301の周辺領域13に重なる領域に、垂直走査回路部110、水平走査回路部111、読出回路112、出力回路114、制御パルス生成部115が配置されうる。

#### 【0025】

図4は、図2における1つの画素101及び図3における1つの信号処理部103の等価回路が例示されている。APD201は、光電変換により入射光に応じた電荷対を生成する。APD201のアノードには、電圧VL(第1電圧)が供給される。また、APD201のカソードには、アノードに供給される電圧VLよりも高い電圧VH(第2電圧)が供給されうる。アノードとカソードとの間には、APD201がアバランシェ増倍動作を引き起こしうる逆バイアス電圧(所定電圧)が供給されうる。アノードとカソードとの間にそのような逆バイアス電圧が供給された状態とすることで、入射光によって生じた電荷がアバランシェ増倍動作を引き起こし、アバランシェ電流が発生しうる。

#### 【0026】

アノードとカソードとの間の電圧が降伏電圧より大きい電圧でAPDを動作させるモードは、ガイガーモードと呼ばれる。アノードとカソードとの間の電圧が降伏電圧近傍またはそれ以下の電圧でAPDを動作させるモードは、リニアモードと呼ばれる。ガイガーモードで動作させるAPDは、SPADは呼ばれる。例えば、電圧VL(第1電圧)は-30V、電圧VH(第2電圧)は1Vである。APD201は、リニアモードで動作させてもよいし、ガイガーモードで動作させてもよい。

#### 【0027】

クエンチ素子202は、電圧VHを供給する電源とAPD201とを接続するように配置されうる。クエンチ素子202は、アバランシェ増倍動作による信号増倍時に負荷回路(クエンチ回路)として機能し、APD201に供給する電圧を抑制して、アバランシェ増倍を抑制する働きを持つ(クエンチ動作)。また、クエンチ素子202は、クエンチ動作で電圧降下した分の電流を流すことにより、APD201に供給する電圧を電圧VHへと戻す働きを持つ(リチャージ動作)。

#### 【0028】

信号処理部103は、波形整形部210、カウンタ回路211、選択回路212を含みうる。信号処理部103は、波形整形部210、カウンタ回路211、選択回路212の少なくとも1つを含む回路であってよい。波形整形部210は、光子検出時に得られるAPD201のカソードの電位変化を整形して、パルス信号を出力しうる。波形整形部210としては、例えば、インバータ回路が用いられうる。図4では、波形整形部210が1つのインバータで構成されているが、波形整形部210は、複数のインバータの直列接続を含んでもよいし、波形整形効果がある他の回路を含んでもよい。

#### 【0029】

カウンタ回路211は、波形整形部210から出力されたパルス信号をカウントし、カウント値を保持しうる。また、カウンタ回路211は、駆動線213を介して制御パルスpRESが供給されることによって、カウンタ回路211に保持された信号をリセットするように構成されうる。選択回路212には、図3の垂直走査回路部110から、図4の駆動線214(図3では不図示)を介して制御パルスpSELが供給され、カウンタ回路211と信号線113との電気的な接続、非接続を切り替えうる。選択回路212は、例えば、信号を出力するためのバッファ回路などを含みうる。

#### 【0030】

クエンチ素子202とAPD201との間、および/または、光電変換素子102と信

10

20

30

40

50

号処理部 103との間にトランジスタ等のスイッチを配して、スイッチによって電気的な接続を制御してもよい。同様に、光電変換素子 102に対する電圧 V<sub>H</sub>および／または電圧 V<sub>L</sub>の供給をトランジスタ等のスイッチによって制御してもよい。

#### 【0031】

光電変換装置 100は、カウンタ回路 211の代わりに、時間・デジタル変換回路（Time to Digital Converter：以下、TDC）、およびメモリを用いて、パルス検出タイミングを取得するように構成されてもよい。波形整形部 210から出力されたパルス信号の発生タイミングは、TDCによってデジタル信号に変換される。TDCには、パルス信号のタイミングの測定のために、図 1 の垂直走査回路部 110から駆動線を介して、制御パルス pREF（参照信号）が供給されうる。TDCは、制御パルス pREFを基準として、波形整形部 210を介して各画素から出力された信号の入力タイミングを相対的な時間としたときの信号をデジタル信号として取得しうる。

10

#### 【0032】

図 5 は、APD201の動作と出力信号との関係を模式的に示した図である。図 5 (a) は、図 4 から APD201、クエンチ素子 202、波形整形部 210 を抜粋して示した図である。ここで、波形整形部 210 の入力側を node A、出力側を node B とする。図 5 (b) は、図 5 (a) の node A の波形変化を示し、図 5 (c) は、図 5 (a) の node B の波形変化を示す。

#### 【0033】

時刻 t<sub>0</sub> から時刻 t<sub>1</sub> の間において、図 5 (a) の APD201 には、V<sub>H</sub> - V<sub>L</sub> の電位差が印加されている。時刻 t<sub>1</sub> において光子が APD201 に入射すると、APD201 でアバランシェ増倍動作が引き起こされ、クエンチ素子 202 にアバランシェ増倍電流が流れ、node A の電圧は降下する。電圧降下量がさらに大きくなり、APD201 に印加される電位差が小さくなると、時刻 t<sub>2</sub> のように APD201 のアバランシェ増倍動作が停止し、node A の電圧レベルはある一定値以上降下しなくなる。その後、時刻 t<sub>2</sub> から時刻 t<sub>3</sub> の間において、node A には電圧 V<sub>L</sub> から電圧降下分を補う電流が流れ、時刻 t<sub>3</sub> において node A は元の電位レベルに静定する。このとき、node A において出力波形がある閾値を越えた部分は、波形整形部 210 で波形整形され、node B で信号として出力される。

20

#### 【0034】

なお、信号線 113 の配置、読出回路 112、出力回路 114 の配置は図 3 に限定されない。例えば、信号線 113 が行方向に延びて配され、読出回路 112 が信号線 113 の延びる先に配されていてもよい。

30

#### 【0035】

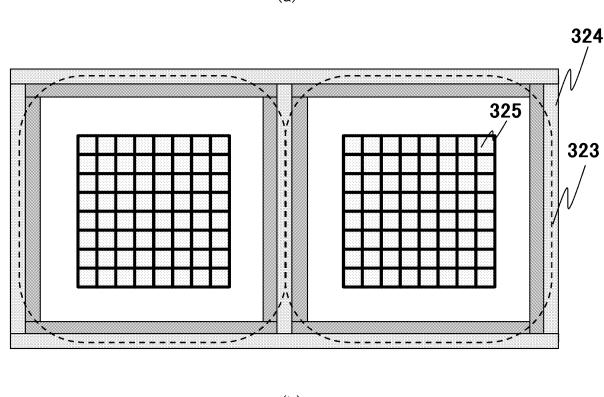

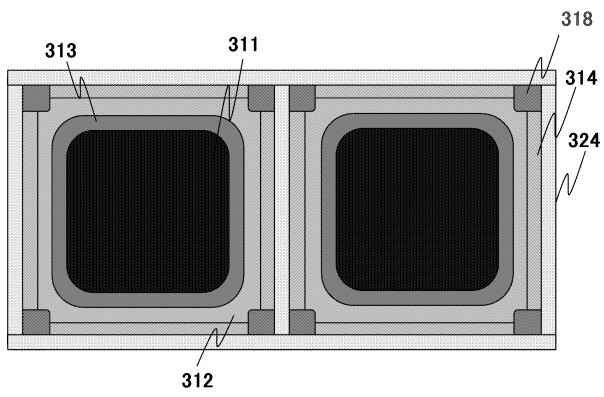

ここで、図 6、図 7A、図 7B を参照しながら画素 101 の第 1 構成例を説明する。なお、便宜的に、図 7A、図 7B には、画素アレイ領域が 2 行 × 2 列の 4 画素で構成された例が示されている。画素アレイ領域の周辺には、開口 OP が設けられ、開口 OP にパッド電極 PE が配置されている。図 6 (a) には、2 つの画素 101 のカソードおよびその周辺の平面視が模式的に示され、図 6 (b) には、2 つの画素 101 のアノードおよびその周辺の平面視が模式的に示されている。図 7A には、図 6 (a)、(b) の 2 つの画素 101 の対辺方向の断面視が模式的に示され、図 7B には、図 6 (a)、(b) の 2 つの画素 101 の対角方向の断面視が模式的に示されている。

40

#### 【0036】

センサ基板 301 は、第 1 面 S<sub>1</sub> および第 2 面 S<sub>2</sub> を有する第 1 半導体層 302 と、第 1 配線構造 303 とを含みうる。回路基板 401 は、第 2 半導体層 402 と、第 2 配線構造 403 とを含みうる。第 1 配線構造 303 は、第 1 半導体層 302 の第 1 面 S<sub>1</sub> と回路基板 401 との間に配置されうる。第 2 配線構造 403 は、センサ基板 301 と第 2 半導体層 402 との間に配置されうる。

#### 【0037】

各画素 101 は、APD201 のカソードとしての第 1 導電型の第 1 半導体領域 311

50

と、A P D 2 0 1 のアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 を含みうる。第 1 導電型の第 1 半導体領域 3 1 1 は、第 1 半導体層 3 0 2 の第 1 面 S 1 の側に配置され、第 2 導電型の第 2 半導体領域 3 1 5 は、第 1 半導体層 3 0 2 の第 2 面 S 2 の側に配置されうる。第 1 半導体領域 3 1 1 と第 2 半導体領域 3 1 5 との間には、アバランシェ倍増動作を引き起こしうる所定電圧が供給されうる。各画素 1 0 1 は、カソードとしての第 1 半導体領域 3 1 1 とアノードとしての第 2 半導体領域 3 1 5 との間に、第 1 半導体領域 3 1 1 と近接して配置された第 1 導電型の半導体領域 3 1 3 を含みうる。半導体領域 3 1 3 における第 1 導電型の不純物濃度は、カソードとしての第 1 導電型の第 1 半導体領域 3 1 1 における第 1 導電型の不純物濃度より低い。

## 【 0 0 3 8 】

10

各画素 1 0 1 は、カソードとしての第 1 導電型の第 1 半導体領域 3 1 1 とアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 との間に第 2 導電型の半導体領域 3 1 2 を含みうる。例えば、半導体領域 3 1 2 はアノードとしての第 2 半導体領域 3 1 5 と同一のノードとなっている場合、半導体領域 3 1 2 もアノードとして機能しうる。そして、第 1 半導体領域 3 1 1 と半導体領域 3 1 2 との間の領域がアバランシェ倍増領域となりうる。第 1 面 S 1 と第 2 導電型の半導体領域 3 1 2 との間には、カソードとしての第 1 導電型の第 1 半導体領域 3 1 1 を取り囲むように、第 1 導電型または第 2 導電型の半導体領域 3 1 6 が配置されうる。半導体領域 3 1 6 が第 1 導電型を有する場合、半導体領域 3 1 6 における第 1 導電型の不純物濃度は、カソードとしての半導体領域 3 1 3 の第 1 導電型の不純物濃度よりも低い。半導体領域 3 1 6 が第 2 導電型を有する場合、半導体領域 3 1 6 における第 2 導電型の不純物濃度は、第 2 導電型の半導体領域 3 1 2 の第 2 導電型の不純物濃度よりも低い。

20

## 【 0 0 3 9 】

第 2 導電型の半導体領域 3 1 2 とアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 との間には、第 1 導電型または第 2 導電型の半導体領域 3 1 6 が配置されうる。半導体領域 3 1 6 が第 1 導電型を有する場合、半導体領域 3 1 6 における第 1 導電型の不純物濃度は、半導体領域 3 1 3 の第 1 導電型の不純物濃度よりも低くてよい。半導体領域 3 1 6 が第 2 導電型を有する場合、半導体領域 3 1 6 における第 2 導電型の不純物濃度は、第 2 導電型の半導体領域 3 1 2 の第 2 導電型の不純物濃度よりも低くてよい。

## 【 0 0 4 0 】

30

アノードとしての第 2 導電型の第 2 半導体領域 3 1 5 と第 2 導電型の半導体領域 3 1 2 との間には、第 1 導電型の半導体領域 3 1 7 が配置されてもよい。半導体領域 3 1 6 は、アノードとしての第 2 導電型の第 2 半導体領域 3 1 5 と第 1 導電型の半導体領域 3 1 7 との間に配置された部分、および、第 1 導電型の半導体領域 3 1 7 の側面を取り囲む部分を含みうる。

## 【 0 0 4 1 】

複数の画素 1 0 1 における互いに隣り合う画素 1 0 1 の間には、第 2 導電型の分離領域 3 1 4 が配置されうる。第 2 導電型の分離領域 3 1 4 と第 1 面 S 1 との間には、第 2 導電型の分離領域 3 1 4 に電気的に接続されるように第 2 導電型のコンタクト領域 3 1 8 が配置されうる。第 2 導電型のコンタクト領域 3 1 8 における第 2 導電型の不純物濃度は、第 2 導電型の分離領域 3 1 4 における第 2 導電型の不純物濃度よりも高い。第 2 導電型の分離領域 3 1 4 は、アノードとしての第 2 導電型の第 2 半導体領域 3 1 5 と電気的に接続されるように配置されうる。第 2 導電型のコンタクト領域 3 1 8 には、第 1 配線構造 3 0 3 に配置された導電経路を介してアノード電圧（アノード電位）が供給され、これによりアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 にアノード電圧（アノード電位）が供給されうる。図 6 の例では、1 つの画素 1 0 1 に対して 4 つのコンタクト領域 3 1 8 が設けられているが、1 つの画素 1 0 1 に対して任意個数のコンタクト領域 3 1 8 が設けられうる。あるいは、2 以上の画素 1 0 1 をグループとして、各グループに対して 1 又は複数のコンタクト領域 3 1 8 が設けられてもよい。

40

## 【 0 0 4 2 】

50

第2導電型の分離領域314の中に絶縁分離部324が配置されてもよい。絶縁分離部324は、分離領域314に設けられた溝と、少なくとも該溝の表面(内面)を覆うように配置された絶縁体とを含みうる。該絶縁体は、膜でもよく、該膜の内側には、絶縁材料または導電材料が充填されうる。絶縁分離部324は、DTI(Deep Trench Isolation)と呼ばれうる。絶縁分離部324あるいは溝は、第1半導体層302を貫通するように配置されてもよいし、第1半導体層302を貫通しないように配置されてもよい。絶縁分離部324あるいは溝は、第2導電型の分離領域314を1つの画素101の側の分離領域とその隣の画素101の側の分離領域とに電気的に分離しうる。また、絶縁分離部324は、溝と、溝の内面を覆うように配置された絶縁体と、絶縁体の内部に配された金属や遮光体からなる構成でありうる。また、絶縁分離部324は、半導体層を貫通していなくてもよい。

10

#### 【0043】

アノードとしての第2導電型の第2半導体領域315の第2面S2の側には、ピニング層331(太線で図示)が配置されうる。ピニング層331は、固定電荷膜とも呼ばれうる。ピニング層331は、第2面S2に接触するように配置され、例えば、ALD(Automatic Layer Deposition)によって形成されうる。ピニング層331は、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコニウム、酸化チタン、酸化タンタル、酸化ルテニウムから選択される材料で構成されうる。ピニング層331は、複数の層からなっていてもよい。分離領域314に設けられた溝の表面(内面)を覆う前述の膜は、ピニング層331であってもよい。

20

#### 【0044】

ピニング層331、および、第2面S2は、絶縁膜321で覆われうる。絶縁膜321は、例えば、酸化シリコン膜、窒化シリコン膜または窒化酸化シリコン膜でありうる。絶縁膜321は複数の膜によって構成されていてもよい。アノードとしての第2導電型の第2半導体領域315には、凹凸構造325が設けられてもよい。凹凸構造325の表面は、ピニング層331で覆われうる。凹凸構造325は、入射光を回折させ、半導体層302内の光路を長くするように機能する。これは、近赤外感度を向上させるために有利である。凹凸構造325は、半導体層302に設けられた溝と、溝に配されたピニング層331と絶縁体によって構成されうる。ピニング層331は、半導体層302の露出面を覆うように設けられうる。つまり、ピニング層331は、凹凸構造の溝と第2面S2とに沿って配される。溝に配される絶縁体は、絶縁膜321によって構成されていてもよい。

30

#### 【0045】

絶縁膜321は、平坦化層322で覆われうる。平坦化層322の上には、マイクロレンズ323が配置されうる。図7A、図7Bに示された例は、半導体層302の第2面Sに対してマイクロレンズ323を通して外部から光が入射する裏面照射型であるが、光電変換装置100は、表面照射型として構成されてもよい。なお、図示されていないが、半導体層302の第2面S2側には、平坦化層322に加え、カラーフィルタや赤外光カットフィルタなどのフィルタ層を設けてもよい。

#### 【0046】

以下、図8、図9A、図9Bを参照しながら画素101の第2構成例を説明する。なお、便宜的に、図9A、図9Bには、画素アレイ領域が2行×2列の4画素で構成された例が示されている。画素アレイ領域の周辺には、開口OPが設けられ、開口OPにパッド電極PEが配置されている。図8(a)には、2つの画素101のカソードおよびその周辺の平面視が模式的に示され、図8(b)には、2つの画素101のアノードおよびその周辺の平面視が模式的に示されている。図9Aには、図8(a)、(b)の2つの画素101の対辺方向の断面視が模式的に示され、図9Bには、図8(a)、(b)の2つの画素101の対角方向の断面視が模式的に示されている。

40

#### 【0047】

センサ基板301は、第1面S1および第2面S2を有する第1半導体層302と、第1配線構造303とを含みうる。回路基板401は、第2半導体層402と、第2配線構

50

造 4 0 3 とを含みうる。第 1 配線構造 3 0 3 は、第 1 半導体層 3 0 2 の第 1 面 S 1 と回路基板 4 0 1 との間に配置されうる。第 2 配線構造 4 0 3 は、センサ基板 3 0 1 と第 2 半導体層 4 0 2 との間に配置されうる。

#### 【 0 0 4 8 】

各画素 1 0 1 は、A P D 2 0 1 のカソードとしての第 1 導電型の第 1 半導体領域 3 1 1 と、A P D 2 0 1 のアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 とを含みうる。第 1 導電型の第 1 半導体領域 3 1 1 は、第 1 半導体層 3 0 2 の第 1 面 S 1 の側に配置され、第 2 導電型の第 2 半導体領域 3 1 5 は、第 1 半導体層 3 0 2 の第 2 面 S 2 の側に配置されうる。第 1 半導体領域 3 1 1 と第 2 半導体領域 3 1 5 との間には、アバランシェ倍増動作を引き起こしうる所定電圧が供給されうる。各画素 1 0 1 は、カソードとしての第 1 半導体領域 3 1 1 とアノードとしての第 2 半導体領域 3 1 5 との間に、第 1 半導体領域 3 1 1 における周辺部分と近接して配置されたリング状の第 1 導電型の半導体領域 3 1 3 を含みうる。半導体領域 3 1 3 の第 1 導電型の不純物濃度は、カソードとしての第 1 導電型の第 1 半導体領域 3 1 1 の第 1 導電型の不純物濃度より低い。

10

#### 【 0 0 4 9 】

各画素 1 0 1 は、カソードとしての第 1 導電型の第 1 半導体領域 3 1 1 とアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 との間に、第 1 半導体領域 3 1 1 における中央部分と近接して第 2 導電型の半導体領域 3 1 2 を含みうる。例えば、半導体領域 3 1 2 はアノードとしての第 2 半導体領域 3 1 5 と同一のノードとなっている場合、半導体領域 3 1 2 もアノードとして機能しうる。そして、第 1 半導体領域 3 1 1 と半導体領域 3 1 2 との間の領域がアバランシェ倍増領域となりうる。第 2 導電型の半導体領域 3 1 2 とアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 との間には、第 1 導電型または第 2 導電型の半導体領域 3 1 6 が配置されうる。半導体領域 3 1 6 が第 1 導電型を有する場合、半導体領域 3 1 6 における第 1 導電型の不純物濃度は、半導体領域 3 1 3 の第 1 導電型の不純物濃度よりも低くてよい。半導体領域 3 1 6 が第 2 導電型を有する場合、半導体領域 3 1 6 における第 2 導電型の不純物濃度は、第 2 導電型の半導体領域 3 1 2 の第 2 導電型の不純物濃度よりも低くてよい。半導体領域 3 1 6 は、第 1 導電型の半導体領域 3 1 3 の周囲を取り囲むように配置されうる。また、半導体領域 3 1 6 は、第 1 導電型の半導体領域 3 1 3 とアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 との間に配置された部分を含みうる。

20

#### 【 0 0 5 0 】

複数の画素 1 0 1 における互いに隣り合う画素 1 0 1 の間には、第 2 導電型の分離領域 3 1 4 が配置されうる。第 2 導電型の分離領域 3 1 4 と第 1 面 S 1 との間には、第 2 導電型の分離領域 3 1 4 に電気的に接続されるように第 2 導電型のコンタクト領域 3 1 8 が配置されうる。第 2 導電型のコンタクト領域 3 1 8 における第 2 導電型の不純物濃度は、第 2 導電型の分離領域 3 1 4 における第 2 導電型の不純物濃度よりも高い。第 2 導電型の分離領域 3 1 4 は、アノードとしての第 2 導電型の第 2 半導体領域 3 1 5 と電気的に接続されるように配置されうる。第 2 導電型のコンタクト領域 3 1 8 には、第 1 配線構造 3 0 3 に配置された導電経路を介してアノード電圧（アノード電位）が供給され、これによりアノードとしての第 2 導電型の第 2 半導体領域 3 1 5 にアノード電圧（アノード電位）が供給されうる。図 8 の例では、1 つの画素 1 0 1 に対して 4 つのコンタクト領域 3 1 8 が設けられているが、1 つの画素 1 0 1 に対して任意個数のコンタクト領域 3 1 8 が設けられる。あるいは、2 以上の画素 1 0 1 をグループとして、各グループに対して 1 又は複数のコンタクト領域 3 1 8 が設けられてもよい。

30

#### 【 0 0 5 1 】

第 2 導電型の分離領域 3 1 4 の中に絶縁分離部 3 2 4 が配置されてもよい。絶縁分離部 3 2 4 は、分離領域 3 1 4 に設けられた溝と、少なくとも該溝の表面（内面）を覆うように配置された絶縁体とを含みうる。該絶縁体は、膜でもよく、該膜の内側には、絶縁材料または導電材料が充填されうる。絶縁分離部 3 2 4 は、D T I ( Deep T r e n c h I s o l a t i o n ) と呼ばれうる。絶縁分離部 3 2 4 あるいは溝は、第 1 半導体層 3 0

40

50

2を貫通するように配置されてもよいし、第1半導体層302を貫通しないように配置されてもよい。絶縁分離部324あるいは溝は、第2導電型の分離領域314を1つの画素101の側の分離領域とその隣の画素101の側の分離領域とに電気的に分離しうる。

#### 【0052】

アノードとしての第2導電型の第2半導体領域315の第2面S2の側には、ピニング層331(太線で図示)が配置されうる。ピニング層331は、固定電荷膜とも呼ばれうる。ピニング層331は、第2面S2に接触するように配置され、例えば、ALD(A atomic Layer Deposition)によって形成されうる。ピニング層331は、例えば、多結晶シリコン、酸化ハフニウム膜または酸化アルミニウム膜等によって形成されうる。ピニング層331、および、第2面S2は、絶縁膜321で覆われうる。絶縁膜321は、例えば、SiO膜、SiN膜またはSiON膜でありうる。アノードとしての第2導電型の第2半導体領域315には、凹凸構造325が設けられてもよい。凹凸構造325の表面は、ピニング層331で覆われうる。凹凸構造325は、入射光を回折させ、半導体層302内の光路を長くするように機能する。これは、近赤外感度を向上させるために有利である。

#### 【0053】

絶縁膜321は、平坦化層322で覆われうる。平坦化層322の上には、マイクロレンズ323が配置されうる。図9A、図9Bに示された例は、半導体層302の第2面Sに対してマイクロレンズ323を通して外部から光が入射する裏面照射型であるが、光電変換装置100は、表面照射型として構成されてもよい。

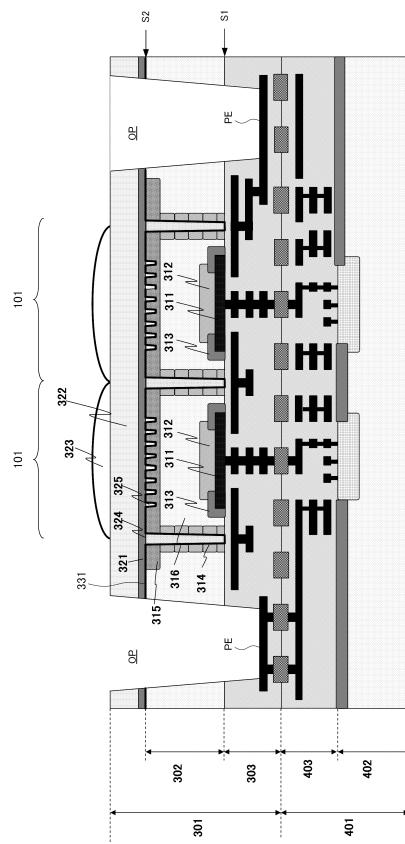

#### 【0054】

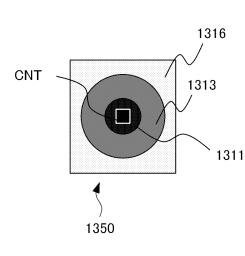

以下、図10、図11を参照しながら第1実施形態の光電変換装置100の構成を説明する。第1実施形態の光電変換装置100は、図6、図7A、図7Bを参照して説明された第1構成例に係る構成を有する光電変換装置100に電荷排出部1350を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。詳細には、第1実施形態の光電変換装置は、例えば、絶縁分離部や凹凸構造を備えていない点で第1構成例とは異なる。

#### 【0055】

第1実施形態の光電変換装置100は、複数の画素101を有する画素アレイ領域12と、画素アレイ領域12の周辺に配置された周辺領域13とを含む半導体層302(あるいは、他の観点では、センサ基板301)を有する。画素アレイ領域12は、入射した光に応じた信号を出力する画素(有効画素)102が配置された有効画素領域12Eと、遮光された画素(OB画素、あるいは遮光画素)102が配置されたOB画素領域12OBとを含みうる。OB画素領域12OBは、有効画素領域12Eの外周の少なくとも一部に沿って配置されうる。OB画素領域12OBは、典型的には、有効画素領域12Eを取り囲むように配置されうる。周辺領域13には、少なくとも1つ、典型的には、複数のパッド電極PEが配置されうる。OB画素101では、アノードおよびカソードを含んで構成されるAPD201が遮光膜LSMによって遮光される。OB画素領域12OBの画素101は、APD201が遮光膜LSMによって遮光されることを除いて、有効画素領域12Eの画素101と同様の構成を有しうる。

#### 【0056】

周辺領域13には、1又は複数の電荷排出部1350が配置されうる。図10(a)では、1つの電荷排出部1350は、黒丸で示されている。図10(b)は、1つの電荷排出部1350の模式的な平面図である。ここで、複数の電荷排出部1350が画素アレイ領域12の4つの辺のそれぞれに沿って所定ピッチで配置されることが好ましい。該所定ピッチは、画素アレイ領域12における複数の画素101の配列ピッチよりも大きいことが好ましい。複数の電荷排出部1350は、画素アレイ領域12の4つの辺のそれぞれに沿って複数の列を構成するように配置されうる。複数の電荷排出部1350は、画素アレイ領域12の4つの辺のそれぞれに沿って、千鳥格子状に配置されてもよい。

#### 【0057】

10

20

30

40

50

図11に例示されるように、半導体層302は、第1面S1および第2面S2を有する。画素アレイ領域12(有効画素領域12E、OB画素領域12OB)に配置された各画素101は、図6、図7A、図7Bを参照して説明された第1構成例と同様の構造を有し10う。以降、図11、図6、図7A、図7Bを相互に参照して説明する。

各画素101は、APD201のカソードとしての第1導電型の第1半導体領域311と、APD201のアノードとしての第2導電型の第2半導体領域315とを含みうる。第1導電型の第1半導体領域311は、第1半導体層302の第1面S1の側に配置され、第2導電型の第2半導体領域315は、第1半導体層302の第2面S2の側に配置されうる。第1半導体領域311と第2半導体領域315との間には、アバランシェ倍増動作を引き起こしうる所定電圧が供給されうる。各画素101は、カソードとしての第1半導体領域311とアノードとしての第2半導体領域315との間に、第1半導体領域311と近接して配置された第1導電型の半導体領域313を含みうる。半導体領域313の第1導電型の不純物濃度は、カソードとしての第1導電型の第1半導体領域311の第1導電型の不純物濃度より低い。

#### 【0058】

各画素101は、カソードとしての第1導電型の第1半導体領域311とアノードとしての第2導電型の第2半導体領域315との間に第2導電型の半導体領域312を含みうる。第1面S1と第2導電型の半導体領域312との間には、カソードとしての第1導電型の第1半導体領域311を取り囲むように、第1導電型または第2導電型の半導体領域316が配置されうる。半導体領域316が第1導電型を有する場合、半導体領域316における第1導電型の不純物濃度は、カソードとしての半導体領域313の第1導電型の不純物濃度よりも低い。半導体領域316が第2導電型を有する場合、半導体領域316における第2導電型の不純物濃度は、第2導電型の半導体領域312の第2導電型の不純物濃度よりも低い。

#### 【0059】

第2導電型の半導体領域312とアノードとしての第2導電型の第2半導体領域315との間には、第1導電型または第2導電型の半導体領域316が配置されうる。半導体領域316が第1導電型を有する場合、半導体領域316における第1導電型の不純物濃度は、半導体領域313の第1導電型の不純物濃度よりも低くてよい。半導体領域316が第2導電型を有する場合、半導体領域316における第2導電型の不純物濃度は、第2導電型の半導体領域312の第2導電型の不純物濃度よりも低くてよい。

#### 【0060】

アノードとしての第2導電型の第2半導体領域315と第2導電型の半導体領域312との間には、第1導電型の半導体領域317が配置されてもよい。半導体領域316は、アノードとしての第2導電型の第2半導体領域315と第1導電型の半導体領域317との間に配置された部分、および、第1導電型の半導体領域317の側面を取り囲む部分を含みうる。

#### 【0061】

複数の画素101における互いに隣り合う画素101の間には、第2導電型の分離領域314が配置されうる。第2導電型の分離領域314と第1面S1との間には、第2導電型の分離領域314に電気的に接続されるように第2導電型のコンタクト領域318が配置されうる。第2導電型のコンタクト領域318における第2導電型の不純物濃度は、第2導電型の分離領域314における第2導電型の不純物濃度よりも高い。第2導電型の分離領域314は、アノードとしての第2導電型の第2半導体領域315と電気的に接続されるように配置されうる。第2導電型のコンタクト領域318には、第1配線構造303に配置された導電経路を介してアノード電圧(アノード電位)が供給され、これによりアノードとしての第2導電型の第2半導体領域315にアノード電圧(アノード電位)が供給されうる。

#### 【0062】

第2導電型の分離領域314の中に絶縁分離部324が配置されてもよい。絶縁分離部

10

20

30

40

50

324は、分離領域314に設けられた溝と、少なくとも該溝の表面（内面）を覆うように配置された絶縁体とを含みうる。該絶縁体は、膜でもよく、該膜の内側には、絶縁材料または導電材料が充填されうる。絶縁分離部324は、DTI（Deep Trench Isolation）と呼ばれうる。絶縁分離部324あるいは溝は、第1半導体層302を貫通するように配置されてもよいし、第1半導体層302を貫通しないように配置されてもよい。絶縁分離部324あるいは溝は、第2導電型の分離領域314を1つの画素101の側の分離領域と隣の画素101の側の分離領域とに電気的に分離しうる。

#### 【0063】

アノードとしての第2導電型の第2半導体領域315の第2面S2の側には、ピニング層331（太線で図示）が配置されうる。ピニング層331は、固定電荷膜とも呼ばれうる。ピニング層331は、第2面S2に接触するように配置され、例えば、ALD（Atomic Layer Deposition）によって形成されうる。ピニング層331は、例えば、多結晶シリコン、酸化ハフニウムまたは酸化アルミニウム等によって形成されうる。ピニング層331、および、第2面S2は、絶縁膜321で覆われうる。

#### 【0064】

周辺領域13は、第1面S1の側に配置された第1導電型の第3半導体領域1311と、第3半導体領域1311から離隔して配置された第2導電型の第4半導体領域1315とを含みうる。第4半導体領域1315は、第2面S2に対して平行に延びた延設部EPを含みうる。第3半導体領域1311と第4半導体領域1315との間には、所定電圧が供給されうる。第3半導体領域1311と第4半導体領域1315との間に供給される電圧は、アノードとしての第1半導体領域311とカソードとしての第2半導体領域315との間に供給される電圧と同一であってもよい。第1導電型の第3半導体領域1311と第2導電型の第4半導体領域1315との間には、pn接合が構成され、第3半導体領域1311と第4半導体領域1315との間に供給される電圧によって逆バイアスされ、フォトダイオードとして機能しうる。

#### 【0065】

周辺領域13はまた、第1導電型の第3半導体領域1311と第2導電型の第4半導体領域1315との間に、第3半導体領域1311よりも第1導電型の不純物濃度が低い第1導電型の第5半導体領域1313を含みうる。第5半導体領域1313は、第3半導体領域1311に近接して配置されうる。第1導電型の第5半導体領域1313は、第3半導体領域1311の側面を取り囲むように配置される。第1導電型の第5半導体領域1313は、第3半導体領域1311と第4半導体領域1315との間に、第3半導体領域1311と接触するように配置された部分を含みうる。第1導電型の第3半導体領域1311、第2導電型の第4半導体領域1315、および、第1導電型の第5半導体領域1313は、電荷排出部1350を構成しうる。第1導電型の第5半導体領域1313は、第1導電型の第3半導体領域1311の近傍における電界を緩和するように機能しうる。

#### 【0066】

第1導電型の第3半導体領域1311は、画素アレイ領域12の画素101のカソードとしての第1導電型の第1半導体領域311と同一深さ（例えば、第1面S1からの深さ）の領域に形成されうる。また、第1半導体領域311と第3半導体領域1311は第1面S1と第1深さの間に配されうる。第3半導体領域1311における第1導電型の不純物濃度は、画素アレイ領域12の画素101の第1半導体領域311における第1導電型の不純物濃度と同一でありうる。第1導電型の第3半導体領域1311は、画素アレイ領域12の画素101の第1導電型の第1半導体領域311と同時に形成されうる。

#### 【0067】

第2導電型の第4半導体領域1315は、画素アレイ領域12の画素101のアノードとしての第2導電型の第2半導体領域315と同一深さ（例えば、第1面S1からの深さ）の領域に形成されうる。また、第2半導体領域315と第4半導体領域1315は第2面S2と第2深さの間に配されうる。第4半導体領域1315における第2導電型の不純物濃度は、画素アレイ領域12の画素101の第2半導体領域315における第2導電型

10

20

30

40

50

の不純物濃度と同一でありうる。第2導電型の第4半導体領域1315は、画素アレイ領域12の画素101の第2導電型の第2半導体領域315と同時に形成されうる。周辺領域13における第2導電型の第4半導体領域1315は、画素アレイ領域12における第2導電型の第2半導体領域315と一体的に形成されうる。

#### 【0068】

第1導電型の第5半導体領域1313と第2導電型の第4半導体領域1315との間に、第1導電型または第2導電型の半導体領域316が配置されうる。半導体領域316が第1導電型を有する場合、半導体領域316における第1導電型の不純物濃度は、半導体領域1313の第1導電型の不純物濃度よりも低い。半導体領域316が第2導電型を有する場合、半導体領域316における第2導電型の不純物濃度は、第2導電型の半導体領域1315の第2導電型の不純物濃度よりも低い。周辺領域13における半導体領域316は、画素アレイ領域12における半導体領域316と同一の導電型および同一の不純物濃度を有しうる。半導体領域316は、エピタキシャル成長層でありうる。

#### 【0069】

周辺領域13の半導体領域316には、例えば、パッド電極P Eのための開口O Pを通して、あるいは、遮光膜L S Mがない領域を通して、光(あるいは光子)L Lが入射しうる。周辺領域13の半導体領域316に入射した光L Lは、光電変換によって電子(e-)および正孔(h+)を発生させうる。周辺領域13に電荷排出部1350が存在しない場合、周辺領域13に入射した光によって発生した電子および正孔が画素アレイ領域12に移動してアバランシェ増倍動作を引き起こしうる。あるいは、周辺領域13に入射した光によって発生した電子および正孔が再結合して光を発生し、これが画素アレイ領域12の画素101によって検出される可能性がある。あるいは、周辺領域13に入射した光によってアバランシェ増倍動作が引き起こされる可能性もある。これらは、光電変換装置100によって検出される画像あるいは信号の品質を低下させうる。

#### 【0070】

第1実施形態では、周辺領域13に設けられた電荷排出部1350は、周辺領域13に入射した光によって発生した電子および正孔を排出するように動作しうる。ここで、第1導電型がn型であり、第2導電型がp型である場合、発生した電子は第1導電型の第3半導体領域1311に引き込まれ、発生した正孔は第2導電型の第4半導体領域1315に引き込まれる。

#### 【0071】

周辺領域13において、第2導電型の第4半導体領域1315の第2面S2の側には、ピニング層331(太線で図示)が配置されうる。ピニング層331は、第2面S2に接触するように配置され、例えば、A L D(A t o m i c L a y e r D e p o s i t i o n)によって形成されうる。ピニング層331は、例えば、多結晶シリコン、酸化ハフニウムまたは酸化アルミニウム等によって形成されうる。ピニング層331、および、第2面S2は、S i N膜等の絶縁膜321で覆われうる。周辺領域13におけるピニング層331は、画素アレイ領域12におけるピニング層331と同一の組成を有してよく、画素アレイ領域12におけるピニング層331と同時に形成されうる。

#### 【0072】

半導体層302は、画素アレイ領域12と周辺領域13との境界領域に第2導電型の分離領域314を有しうる。分離領域314は、第2導電型の第2半導体領域315に電気的に接続され、第2導電型の第2半導体領域315と同一の電位が供給されうる。画素アレイ領域12と周辺領域13との境界領域に配置された第2導電型の分離領域314も、電荷排出部1350を構成しうる。

#### 【0073】

遮光膜L S Mは、画素アレイ領域12と周辺領域13との境界領域、例えば、平面視における分離領域314に、遮光構造L S Sを含んでもよい。一例において、遮光膜L S Mは、遮光構造L S Sを介して第2導電型の第2半導体領域315および/または第2導電型の第4半導体領域1315に電気的に接続されうる。遮光構造L S Sは、例えば、1又

10

20

30

40

50

は複数の壁を含みうる。該 1 又は複数の壁は、ピニング層 331 を貫通して第 2 導電型の第 2 半導体領域 315 および / または第 2 導電型の第 4 半導体領域 1315 に電気的に接続されうる。

#### 【 0074 】

以下、図 12、図 13 を参照しながら第 2 実施形態の光電変換装置 100 の構成を説明する。第 2 実施形態の光電変換装置 100 は、図 6、図 7A、図 7B を参照して説明された第 1 構成例に係る構成を有する光電変換装置 100 に電荷排出部 1350 を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。第 2 実施形態の光電変換装置 100 は、電荷排出部 1350 の構成、および / または、電荷排出部 1350 に供給される電圧が第 1 実施形態の光電変換装置 100 と異なる。

10

#### 【 0075 】

第 2 実施形態の光電変換装置 100 は、電圧生成部 VG を備えうる。電圧生成部 VG は、第 1 導電型の第 3 半導体領域 1311 に供給される電圧（電位）を生成しうる。他の観点において、電圧生成部 VG は、第 1 導電型の第 3 半導体領域 1311 と第 2 導電型の第 4 半導体領域 1315 との間に供給される電圧を生成しうる。電圧生成部 VG は、例えば、複数のパッド電極 PE のうちの 1 つのパッド電極 PE に供給される電圧を変圧することによって、第 1 導電型の第 3 半導体領域 1311 に供給される電圧（電位）を生成しうる。電圧生成部 VG は、例えば、回路基板 401 に配置されうる。このような構成に代えて、第 1 導電型の第 3 半導体領域 1311 に供給される電圧（電位）は、光電変換装置 100 の外部から供給されてもよい。

20

#### 【 0076 】

電荷排出部 1350 に供給される電圧、換言すると、第 1 導電型の第 3 半導体領域 1311 と第 2 導電型の第 4 半導体領域 1315 との間に供給される電圧は、画素アレイ領域 12 のアノードとカソードとの間に供給される電圧よりも小さい。一例において、電荷排出部 1350 に供給される電圧は、画素アレイ領域 12 のアノードとカソードとの間に供給される電圧の 1 / 2 以下でありうる。あるいは、第 1 導電型の第 3 半導体領域 1311 に供給される電圧（電位）は、光電変換装置 100 における接地電位であってもよい。これは、光電変換装置 100 の構造の単純化に有利である。

#### 【 0077 】

第 1 導電型の第 3 半導体領域 1311 の周囲に発生する電界が十分に弱い場合、第 1 実施形態における電荷排出部 1350 に設けられたような第 5 半導体領域 1313 は取り除かれてもよい。図 12、図 13 には、第 5 半導体領域 1313 は取り除かれた電荷排出部 1350 が例示されている。また、本電圧を図 7A および図 7B に示すような絶縁分離部を有する構成に適用することもできる。

30

#### 【 0078 】

以下、図 14、図 15A、図 15B を参照しながら第 3 実施形態の光電変換装置 100 の構成を説明する。第 3 実施形態の光電変換装置 100 は、図 6、図 7A、図 7B を参照して説明された第 1 構成例に係る構成を有する光電変換装置 100 に電荷排出部 1350 を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。第 3 実施形態の光電変換装置 100 は、絶縁分離部 324 を備える点で第 1 実施形態の光電変換装置 100 と異なる。また、例えば、第 3 実施形態の光電変換装置 100 は、凹凸構造 325 を備える点で第 1 実施形態の光電変換装置 100 と異なる。なお、図 15A および図 15B に示す凹凸構造 325 は、図 7A および図 7B と同様である。

40

#### 【 0079 】

複数の画素 101 における互いに隣り合う画素 101 の間には、第 2 導電型の分離領域 314 が配置されうる。同様に、画素アレイ領域 12 と周辺領域 13 との間に第 2 導電型の分離領域 314 が配置されうる。第 2 導電型の分離領域 314 と第 1 面 S1 との間には、第 2 導電型の分離領域 314 に電気的に接続されるように第 2 導電型のコンタクト領域 318 が配置されうる。第 2 導電型のコンタクト領域 318 における第 2 導電型の不純物濃度は、第 2 導電型の分離領域 314 における第 2 導電型の不純物濃度よりも高い。第 2

50

導電型の分離領域 314 は、アノードとしての第2導電型の第2半導体領域 315 と電気的に接続されるように配置されうる。第2導電型のコンタクト領域 318 には、第1配線構造 303 に配置された導電経路を介してアノード電圧（アノード電位）が供給され、これによりアノードとしての第2導電型の第2半導体領域 315 にアノード電圧（アノード電位）が供給されうる。

#### 【0080】

画素アレイ領域 12において、第2導電型の分離領域 314 の中に絶縁分離部 324 が配置されてもよい。同様に、周辺領域 13 において、第2導電型の分離領域 314 の中に絶縁分離部 324 が配置されてもよい。絶縁分離部 324 は、分離領域 314 に設けられた溝と、少なくとも該溝の表面（内面）を覆うように配置された絶縁体とを含みうる。該絶縁体は、膜でもよく、該膜の内側には、絶縁材料または導電材料が充填されうる。そのような膜は、ピニング層 331 であってもよい。絶縁分離部 324 は、DTI（Deep Trench Isolation）と呼ばれうる。絶縁分離部 324 あるいは溝は、第1半導体層 302 を貫通するように配置されてもよいし、第1半導体層 302 を貫通しないように配置されてもよい。また、図 15A に示すように、開口 OP を挟むように複数の絶縁分離部を設けてもよい。絶縁分離部の絶縁材料と第1半導体層 302 との屈折率差によって、開口 OP からの光の入射を低減することができる。

10

#### 【0081】

画素アレイ領域 12において、絶縁分離部 324 あるいは溝は、第2導電型の分離領域 314 を1つの画素 101 の側の分離領域と隣の画素 101 の側の分離領域とに電気的に分離しうる。同様に、周辺領域 13 において、絶縁分離部 324 あるいは溝は、第2導電型の分離領域 314 を画素アレイ領域 12 の側の第1分離領域 314A と周辺領域 13 の側の第2分離領域 314B とに電気的に分離するように配置されうる。第1半導体層 302 に対して積層された第1配線構造 303 は、第1分離領域に 314A に対して電位を与える第1導電路、および、第2分離領域 314B に対して電位を与える第2導電路を有しうる。該第1導電路と該第2導電路とは、第1配線構造 303 の中において電気的に接続されてよい。導電路は、例えば、コンタクトプラグ、配線などを含みうる。

20

#### 【0082】

以下、図 16A、図 16B を参照しながら第4実施形態の光電変換装置 100 の構成を説明する。第4実施形態の光電変換装置 100 は、図 6、図 7A、図 7B を参照して説明された第1構成例に係る構成を有する光電変換装置 100 に電荷排出部 1350 を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。第4実施形態の光電変換装置 100 は、第3実施形態の光電変換装置 100 から第2導電型の半導体領域 1315 を除去した構成を有する。なお、図 16A および図 16B に示す凹凸構造 325 は、図 7A および図 7B と同様である。

30

#### 【0083】

第4実施形態においても、周辺領域 13 に設けられた電荷排出部 1350 は、周辺領域 13 に入射した光によって発生した電子および正孔を排出するように動作しうる。ここで、第1導電型が n 型であり、第2導電型が p 型である場合、発生した電子は第1導電型の第3半導体領域 1311 に引き込まれて排出されうる。一方、発生した正孔はピニング層 331 によって半導体領域 316 の表面近傍（第2面 S2 の近傍）に誘起される電荷によって該表面近傍に形成される第2導電型の半導体領域、分離領域 314 および第2導電型の第2半導体領域 315 を通して排出されうる。このようにピニング層 331 によって誘起される電荷によって半導体領域 316 の表面領域に形成される第2導電型の半導体領域は、前述の第4半導体領域 1315（延設部 EP）と同様に機能する。第2導電型が p 型である場合、ピニング層 331 によって誘起される電荷は、正孔である。

40

#### 【0084】

以下、図 17 を参照しながら第5実施形態の光電変換装置 100 の構成を説明する。第7実施形態の光電変換装置 100 は、図 8、図 9A、図 9B を参照して説明された第2構成例に係る構成を有する光電変換装置 100 に電荷排出部 1350 を適用した例を提供す

50

る。既に説明した事項と重複した事項については説明を省略する。第1乃至第4実施形態も、図8、図9A、図9Bを参照して説明された第2構成例に係る構成を有する光電変換装置100に適用することができる。なお、図17に示す凹凸構造325は、図9Aおよび図9Bと同様である。

#### 【0085】

以下、図18を参照しながら第6実施形態の光電変換装置100の構成を説明する。第6実施形態の光電変換装置100は、図6、図7A、図7Bを参照して説明された第1構成例に係る構成を有する光電変換装置100に電荷排出部1350を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。図18に示す凹凸構造325は、図7Aおよび図7Bに示す凹凸構造325と同様であるため説明を省略する。10

#### 【0086】

電荷排出部1350の一部を構成する第2導電型の第4半導体領域1315は、延設部EPから第1面S1に向かって突出した1又は複数の突出部P1を含みうる。1又は複数の突出部P1は、第2導電型の半導体領域である。1又は複数の突出部P1における第2導電型の不純物濃度は、延設部EPにおける第2導電型の不純物濃度より低くてもよいし、延設部EPにおける第2導電型の不純物濃度と同じであってもよい。

#### 【0087】

第2導電型の第4半導体領域1315が複数の突出部P1を含む場合において、複数の突出部P1は、所定ピッチで配置されうる。該所定ピッチの方向は、例えば、画素アレイ領域12の辺に垂直な方向、または、画素アレイ領域12の辺に平行な方向である。該所定ピッチは、画素アレイ領域12における複数の画素101の配列ピッチよりも大きいことが好ましい。複数の突出部P1の配列ピッチと複数の第3半導体領域1311の配列ピッチとは同じであってもよいし、異なってもよい。複数の突出部P1および複数の第3半導体領域1311は、平面視において交互に配置されうる。20

#### 【0088】

以下、図19を参照しながら第7実施形態の光電変換装置100の構成を説明する。第7実施形態の光電変換装置100は、図6、図7A、図7Bを参照して説明された第1構成例に係る構成を有する光電変換装置100に電荷排出部1350を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。図19に示す凹凸構造325は、図7Aおよび図7Bに示す凹凸構造325と同様であるため説明を省略する。30

#### 【0089】

電荷排出部1350の一部を構成する第2導電型の第4半導体領域1315は、延設部EPに接するように、延設部EPと第1面S1との間に、延設部EPに沿って配置された少なくとも1つの第2延設部EP2を含みうる。第2延設部EP2は、第2導電型の半導体領域である。第2延設部EP2における第2導電型の不純物濃度は、延設部EPにおける第2導電型の不純物濃度より低くてもよいし、延設部EPにおける第2導電型の不純物濃度と同じであってもよい。第2導電型の第4半導体領域1315が複数の第2延設部EP2を含む場合、複数の第2延設部EP2における第2導電型の不純物濃度は、第2面S2から離れる従って段階的に低下されうる。

#### 【0090】

以下、図20を参照しながら第8実施形態の光電変換装置100の構成を説明する。第8実施形態の光電変換装置100は、図6、図7A、図7Bを参照して説明された第1構成例に係る構成を有する光電変換装置100に電荷排出部1350を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。図20に示す凹凸構造325は、図7Aおよび図7Bに示す凹凸構造325と同様であるため説明を省略する。40

#### 【0091】

電荷排出部1350の一部を構成する第2導電型の第4半導体領域1315は、延設部EPから第1面S1に向かって突出した複数の第1突出部P1を含みうる。複数の第1突出部P1は、第2導電型の半導体領域である。複数の第1突出部P1における第2導電型の不純物濃度は、延設部EPにおける第2導電型の不純物濃度より低くてもよいし、延設

10

20

30

40

50

部 E P における第 2 導電型の不純物濃度と同じであってもよい。

#### 【 0 0 9 2 】

複数の第 1 突出部 P 1 は、所定ピッチで配置されうる。該所定ピッチの方向は、例えば、画素アレイ領域 1 2 の辺に垂直な方向、または、画素アレイ領域 1 2 の辺に平行な方向である。該所定ピッチは、画素アレイ領域 1 2 における複数の画素 1 0 1 の配列ピッチよりも大きいことが好ましい。複数の第 1 突出部 P 1 の配列ピッチと複数の第 3 半導体領域 1 3 1 1 の配列ピッチとは同じであってもよいし、異なってもよい。複数の第 1 突出部 P 1 および複数の第 3 半導体領域 1 3 1 1 は、平面視において交互に配置されうる。

#### 【 0 0 9 3 】

電荷排出部 1 3 5 0 の一部を構成する第 2 導電型の第 4 半導体領域 1 3 1 5 は、延設部 E P から第 1 面 S 1 に向かって突出した複数の第 2 突出部 P 2 を更に含みうる。複数の第 2 突出部 P 2 は、第 2 導電型の半導体領域である。複数の第 2 突出部 P 2 における第 2 導電型の不純物濃度は、延設部 E P における第 2 導電型の不純物濃度より低くてもよいし、延設部 E P における第 2 導電型の不純物濃度と同じであってもよい。

#### 【 0 0 9 4 】

複数の第 2 突出部 P 2 は、所定ピッチで配置されうる。該所定ピッチの方向は、例えば、画素アレイ領域 1 2 の辺に垂直な方向、または、画素アレイ領域 1 2 の辺に平行な方向である。該所定ピッチは、画素アレイ領域 1 2 における複数の画素 1 0 1 の配列ピッチよりも大きいことが好ましい。複数の第 2 突出部 P 2 の配列ピッチと複数の第 3 半導体領域 1 3 1 1 の配列ピッチとは同じであってもよいし、異なってもよい。複数の第 2 突出部 P 2 および複数の第 3 半導体領域 1 3 1 1 は、平面視において交互に配置されうる。複数の第 1 突出部 P 1 および複数の第 2 突出部 P 2 は、平面視において交互に配置されうる。

#### 【 0 0 9 5 】

複数の第 2 突出部 P 2 は、第 2 面 S 2 からの深さが複数の第 1 突出部 P 1 より小さく、平面視において複数の第 3 半導体領域 1 3 1 1 と重なるように配置されうる。

#### 【 0 0 9 6 】

以下、図 2 1 を参照しながら第 9 実施形態の光電変換装置 1 0 0 の構成を説明する。第 9 実施形態の光電変換装置 1 0 0 は、図 6、図 7 A、図 7 B を参照して説明された第 1 構成例に係る構成を有する光電変換装置 1 0 0 に電荷排出部 1 3 5 0 を適用した例を提供する。既に説明した事項と重複した事項については説明を省略する。図 2 1 に示す凹凸構造 3 2 5 は、図 7 A および図 7 B に示す凹凸構造 3 2 5 と同様であるため説明を省略する。

#### 【 0 0 9 7 】

電荷排出部 1 3 5 0 の一部を構成する第 2 導電型の第 4 半導体領域 1 3 1 5 は、延設部 E P から第 1 面 S 1 に向かって突出した複数の突出部 P 1 を含みうる。複数の突出部 P 1 は、第 2 導電型の半導体領域である。複数の突出部 P 1 における第 2 導電型の不純物濃度は、延設部 E P における第 2 導電型の不純物濃度より低くてもよいし、延設部 E P における第 2 導電型の不純物濃度と同じであってもよい。

#### 【 0 0 9 8 】

複数の突出部 P 1 は、所定ピッチで配置されうる。該所定ピッチの方向は、例えば、画素アレイ領域 1 2 の辺に垂直な方向、または、画素アレイ領域 1 2 の辺に平行な方向である。該所定ピッチは、画素アレイ領域 1 2 における複数の画素 1 0 1 の配列ピッチよりも大きいことが好ましい。複数の突出部 P 1 の配列ピッチと複数の第 3 半導体領域 1 3 1 1 の配列ピッチとは同じであってもよいし、異なってもよい。複数の突出部 P 1 および複数の第 3 半導体領域 1 3 1 1 は、平面視において交互に配置されうる。一例において、複数の第 3 半導体領域 1 3 1 1 と第 1 面 S 1 との最短距離は、第 1 面 S 1 からの第 1 導電型の第 5 半導体領域 1 3 1 3 の最大深さより小さい。

#### 【 0 0 9 9 】

以下、図 2 2 を参照しながら第 10 実施形態の光電変換装置 1 0 0 の構成を説明する。第 10 実施形態の光電変換装置 1 0 0 は、図 6、図 7 A、図 7 B を参照して説明された第 1 構成例に係る構成を有する光電変換装置 1 0 0 に電荷排出部 1 3 5 0 を適用した例を提供

10

20

30

40

50

する。既に説明した事項と重複した事項については説明を省略する。図22に示す凹凸構造325は、図7Aおよび図7Bに示す凹凸構造325と同様であるため説明を省略する。

#### 【0100】

電荷排出部1350の一部を構成する第2導電型の第4半導体領域1315は、延設部EPから第1面S1に向かって突出した複数の突出部P1を含みうる。1又は複数の突出部P1は、第2導電型の半導体領域である。1又は複数の突出部P1における第2導電型の不純物濃度は、延設部EPにおける第2導電型の不純物濃度より低くてもよいし、延設部EPにおける第2導電型の不純物濃度と同じであってもよい。

#### 【0101】

第1面S1に平行かつ複数の突出部P1の配列方向において、複数の突出部P1の各々の幅W1は、複数の画素101における互いに隣り合う画素101の間に配置された第2導電型の画素分離領域314PXの幅W2より大きい。あるいは、該配列方向において、複数の突出部P1の各々の最大幅は、複数の画素101における互いに隣り合う画素101の間に配置された第2導電型の画素分離領域314PXの最大幅より大きい。あるいは、該配列方向において、複数の突出部P1の各々最小幅は、複数の画素101における互いに隣り合う画素101の間に配置された第2導電型の画素分離領域314PXの最小幅より大きい。

#### 【0102】

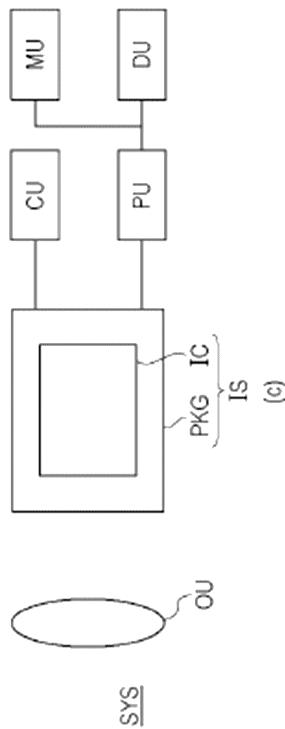

以下、第1乃至第5実施形態を通して例示的に説明された光電変換装置が組み込まれた光電変換システムについて例示的に説明する。図23には、光電変換システムの一例が示されている。第1乃至第5実施形態で述べた光電変換装置は、種々の光電変換システムに適用可能である。適用可能な光電変換システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、光電変換システムに含まれる。光電変換システムは、例えば、撮像システムSYSとして構成される。撮像システムSYSは、カメラや撮影機能を有する情報端末である。撮像装置ISは、撮像デバイスICとして構成された光電変換装置100を収容するパッケージPKGをさらに備えることもできる。パッケージPKGは、撮像デバイスICが固定された基体と、撮像デバイスICに対向する蓋体と、基体に設けられた端子と撮像デバイスICに設けられた端子とを接続する接続部材と、を含みうる。撮像装置ISは共通のパッケージPKGに複数の撮像デバイスICを並べて搭載することもできる。また、撮像装置ISは共通のパッケージPKGに撮像デバイスICと他の半導体デバイスICとを重ねて搭載することもできる。

#### 【0103】

撮像システムSYSは、撮像装置ISに結像する光学系OUを備え得る。また、撮像システムSYSは、撮像装置ISを制御する制御装置CU、撮像装置ISから得られた信号を処理する処理装置PU、撮像装置ISから得られた画像を表示する表示装置DUの少なくともいずれかを備え得る。また、撮像システムSYSは、撮像装置ISから得られた画像を記憶する記憶装置MUを備えてもよい。

#### 【0104】

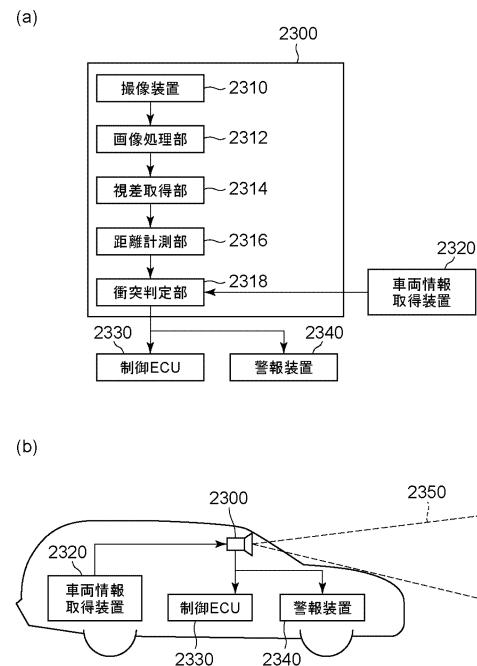

図24(a)には、車載カメラに適用された光電変換システムの構成が例示されている。光電変換システム2300は、撮像装置2310として構成された光電変換装置100を有しうる。光電変換システム2300は、撮像装置2310により取得された複数の画像データに対し画像処理を行う画像処理部2312と、光電変換システム2300により取得された複数の画像データから視差(視差画像の位相差)を算出する視差取得部2314を有する。また、光電変換システム2300は、算出された視差に基づいて対象物までの距離を算出する距離取得部2316と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部2318と、を有する。ここで、視差取得部2314や距離取得部2316は、対象物までの距離情報を取得する距離情報取得手段の一例である。すな

10

20

30

40

50

わち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 2318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。光電変換システム 2300 は車両情報取得装置 2320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、光電変換システム 2300 は、衝突判定部 2318 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御部である制御 ECU 2330 が接続されている。また、光電変換システム 2300 は、衝突判定部 2318 での判定結果に基づいて、ドライバーへ警報を発する警報装置 2340 とも接続されている。例えば、衝突判定部 2318 の判定結果として衝突可能性が高い場合、制御 ECU 2330 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 2340 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザーに警告を行う。本実施形態では、車両の周囲、例えば前方又は後方を光電変換システム 2300 で撮像する。図 24 (b) には、車両前方 (撮像範囲 2350) を撮像するように構成された光電変換システムが示されている。車両情報取得装置 2320 は、光電変換システム 2300 ないしは撮像装置 2310 に指示を送る。このような構成により、測距の精度をより向上させることができる。上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、光電変換システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体 (移動装置) に適用することができる。加えて、移動体に限らず、高度道路交通システム (ITS) 等、広く物体認識を利用する機器に適用することができる。

10

20

30

40

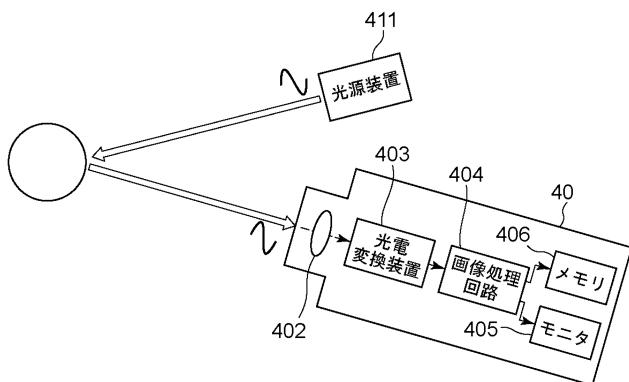

#### 【0105】

図 25 には、距離画像センサとして構成された光電変換システムの構成が例示されている。距離画像センサ 40 は、光学系 407、光電変換装置 408、画像処理回路 404、モニタ 405、およびメモリ 406 を備えて構成される。そして、距離画像センサ 40 は、光源装置 409 から被写体に向かって投光され、被写体の表面で反射された光 (変調光やパルス光) を受光することにより、被写体までの距離に応じた距離画像を取得することができる。

#### 【0106】

光学系 407 は、1枚または複数枚のレンズを有して構成され、被写体からの像光 (入射光) を光電変換装置 408 に導き、光電変換装置 408 の受光面 (センサ部) に結像させる。光電変換装置 408 としては、上述した各実施形態の光電変換装置が適用され、光電変換装置 408 から出力される受光信号から求められる距離を示す距離信号が画像処理回路 404 に供給される。

#### 【0107】

画像処理回路 404 は、光電変換装置 408 から供給された距離信号に基づいて距離画像を構築する画像処理を行う。そして、その画像処理により得られた距離画像 (画像データ) は、モニタ 405 に供給されて表示されたり、メモリ 406 に供給されて記憶 (記録) されたりする。このように構成されている距離画像センサ 40 では、上述した光電変換装置を適用することで、画素の特性向上に伴って、例えば、より正確な距離画像を取得することができる。

#### 【0108】

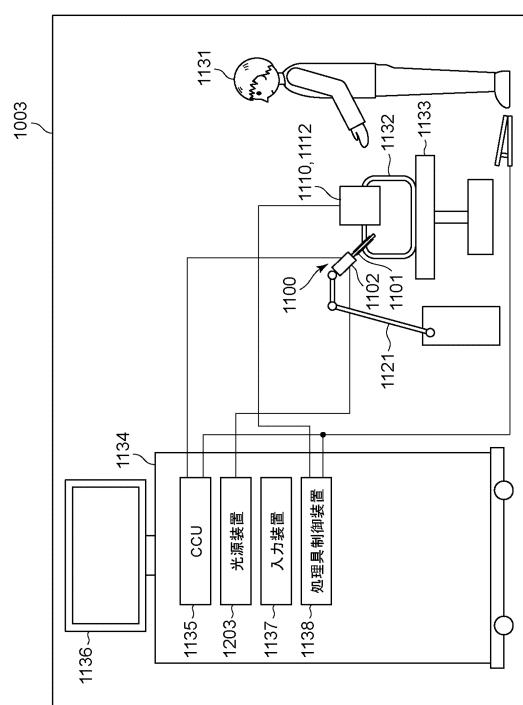

図 26 には、内視鏡手術システムとして構成された光電変換システムの構成が例示されている。図 26 には、術者 (医師) 1131 が、内視鏡手術システム 1150 を用いて、患者ベッド 1133 上の患者 1132 に手術を行っている様子が図示されている。図示す

50

るようすに、内視鏡手術システム 1150 は、内視鏡 1100 と、術具 1110 と、内視鏡下手術のための各種の装置が搭載されたカート 1134 と、から構成される。

#### 【0109】

内視鏡 1100 は、先端から所定の長さの領域が患者 1132 の体腔内に挿入される鏡筒 1101 と、鏡筒 1101 の基端に接続されるカメラヘッド 1102 と、から構成される。図示する例では、硬性の鏡筒 1101 を有するいわゆる硬性鏡として構成される内視鏡 1100 を図示しているが、内視鏡 1100 は、軟性の鏡筒を有するいわゆる軟性鏡として構成されてもよい。

#### 【0110】

鏡筒 1101 の先端には、対物レンズが嵌め込まれた開口部が設けられている。内視鏡 1100 には光源装置 1203 が接続されており、光源装置 1203 によって生成された光が、鏡筒 1101 の内部に延設されるライトガイドによって当該鏡筒の先端まで導光され、対物レンズを介して患者 1132 の体腔内の観察対象に向かって照射される。なお、内視鏡 1100 は、直視鏡であってもよいし、斜視鏡又は側視鏡であってもよい。

#### 【0111】

カメラヘッド 1102 の内部には光学系及び光電変換装置が設けられており、観察対象からの反射光（観察光）は当該光学系によって当該光電変換装置に集光される。当該光電変換装置によって観察光が光電変換され、観察光に対応する電気信号、すなわち観察像に対応する画像信号が生成される。当該光電変換装置としては、前述の各実施形態に記載の光電変換装置を用いることができる。当該画像信号は、RAWデータとしてカメラコントロールユニット（CCU： Camera Control Unit）1135 に送信される。

#### 【0112】

CCU1135 は、CPU（Central Processing Unit）や GPU（Graphics Processing Unit）等によって構成され、内視鏡 1100 及び表示装置 1136 の動作を統括的に制御する。さらに、CCU1135 は、カメラヘッド 1102 から画像信号を受け取り、その画像信号に対して、例えば現像処理（デモザイク処理）等の、当該画像信号に基づく画像を表示するための各種の画像処理を施す。

#### 【0113】

表示装置 1136 は、CCU1135 からの制御により、当該 CCU1135 によって画像処理が施された画像信号に基づく画像を表示する。光源装置 1203 は、例えば LED（Light Emitting Diode）等の光源から構成され、術部等を撮影する際の照射光を内視鏡 1100 に供給する。入力装置 1137 は、内視鏡手術システム 1150 に対する入力インターフェースである。ユーザーは、入力装置 1137 を介して、内視鏡手術システム 1150 に対して各種の情報の入力や指示入力を行うことができる。処置具制御装置 1138 は、組織の焼灼、切開又は血管の封止等のためのエネルギー処置具 1112 の駆動を制御する。

#### 【0114】

内視鏡 1100 に術部を撮影する際の照射光を供給する光源装置 1203 は、例えば LED、レーザ光源又はこれらの組み合わせによって構成される白色光源から構成することができる。RGB レーザ光源の組み合わせにより白色光源が構成される場合には、各色（各波長）の出力強度及び出力タイミングを高精度に制御することができるため、光源装置 1203 において撮像画像のホワイトバランスの調整を行うことができる。また、この場合には、RGB レーザ光源それぞれからのレーザ光を時分割で観察対象に照射し、その照射タイミングに同期してカメラヘッド 1102 の撮像素子の駆動を制御することにより、RGB それぞれに対応した画像を時分割で撮像することも可能である。当該方法によれば、当該撮像素子にカラーフィルタを設けなくても、カラー画像を得ることができる。

#### 【0115】

また、光源装置 1203 は、出力する光の強度を所定の時間ごとに変更するようにその

10

20

30

40

50

駆動が制御されてもよい。その光の強度の変更のタイミングに同期してカメラヘッド 1102 の撮像素子の駆動を制御して時分割で画像を取得し、その画像を合成することにより、いわゆる黒つぶれ及び白とびのない高ダイナミックレンジの画像を生成することができる。

#### 【 0 1 1 6 】

また、光源装置 1203 は、特殊光観察に対応した所定の波長帯域の光を供給可能に構成されてもよい。特殊光観察では、例えば、体組織における光の吸収の波長依存性を利用する。具体的には、通常の観察時における照射光（すなわち、白色光）に比べて狭帯域の光を照射することにより、粘膜表層の血管等の所定の組織を高コントラストで撮影する。あるいは、特殊光観察では、励起光を照射することにより発生する蛍光により画像を得る蛍光観察が行われてもよい。蛍光観察では、体組織に励起光を照射し当該体組織からの蛍光を観察すること、又はインドシアニングリーン（ I C G ）等の試薬を体組織に局注するとともに当該体組織にその試薬の蛍光波長に対応した励起光を照射し蛍光像を得ること等を行うことができる。光源装置 1203 は、このような特殊光観察に対応した狭帯域光及び／又は励起光を供給可能に構成され得る。10

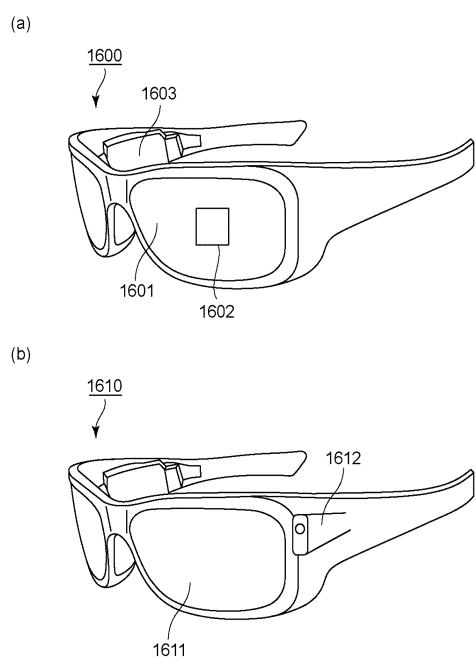

#### 【 0 1 1 7 】

図 27 ( a ) には、眼鏡 1600 (スマートグラス) として構成された構成された光電変換システムの構成が例示されている。眼鏡 1600 は、光電変換装置 100 が適用された光電変換装置 1602 を有する。光電変換装置 1602 は、上記の各実施形態に記載の光電変換装置である。また、レンズ 1601 の裏面側には、O L E D や L E D 等の発光装置を含む表示装置が設けられていてもよい。光電変換装置 1602 は 1 つでもよいし、複数でもよい。また、複数種類の光電変換装置を組み合わせて用いてもよい。光電変換装置 1602 の配置位置は、図 27 ( a ) に限定されない。20

#### 【 0 1 1 8 】

眼鏡 1600 は、制御装置 1603 をさらに備える。制御装置 1603 は、光電変換装置 1602 と上記の表示装置に電力を供給する電源として機能する。また、制御装置 1603 は、光電変換装置 1602 と表示装置の動作を制御する。レンズ 1601 には、光電変換装置 1602 に光を集光するための光学系が形成されている。

#### 【 0 1 1 9 】

図 27 ( b ) には、眼鏡 1610 (スマートグラス) 構成された光電変換システムの構成が例示されている。眼鏡 1610 は、制御装置 1612 を有しており、制御装置 1612 に、光電変換装置 1602 に相当する光電変換装置と、表示装置が搭載される。レンズ 1611 には、制御装置 1612 内の光電変換装置と、表示装置からの発光を投影するための光学系が形成されており、レンズ 1611 には画像が投影される。制御装置 1612 は、光電変換装置および表示装置に電力を供給する電源として機能するとともに、光電変換装置および表示装置の動作を制御する。制御装置は、装着者の視線を検知する視線検知部を有してもよい。視線の検知は赤外線を用いてよい。赤外発光部は、表示画像を注視しているユーザーの眼球に対して、赤外光を発する。発せられた赤外光の眼球からの反射光を、受光素子を有する撮像部が検出することで眼球の撮像画像が得られる。平面視における赤外発光部から表示部への光を低減する低減手段を有することで、画像品位の低下を低減する。3040

#### 【 0 1 2 0 】

赤外光の撮像により得られた眼球の撮像画像から表示画像に対するユーザーの視線を検出する。眼球の撮像画像を用いた視線検出には任意の公知の手法が適用できる。一例として、角膜での照射光の反射によるブルキニ工像に基づく視線検出方法を用いることができる。より具体的には、瞳孔角膜反射法に基づく視線検出処理が行われる。瞳孔角膜反射法を用いて、眼球の撮像画像に含まれる瞳孔の像とブルキニ工像とに基づいて、眼球の向き（回転角度）を表す視線ベクトルが算出されることにより、ユーザーの視線が検出される。

#### 【 0 1 2 1 】

本実施形態の表示装置は、受光素子を有する光電変換装置を有し、光電変換装置からのユーザーの視線情報に基づいて表示装置の表示画像を制御してよい。

#### 【0122】

具体的には、表示装置は、視線情報に基づいて、ユーザーが注視する第1の視界領域と、第1の視界領域以外の第2の視界領域とを決定される。第1の視界領域、第2の視界領域は、表示装置の制御装置が決定してもよいし、外部の制御装置が決定したものを受けしてもよい。表示装置の表示領域において、第1の視界領域の表示解像度を第2の視界領域の表示解像度よりも高く制御してよい。つまり、第2の視界領域の解像度を第1の視界領域よりも低くしてよい。

#### 【0123】

また、表示領域は、第1の表示領域、第1の表示領域とは異なる第2の表示領域とを有し、視線情報に基づいて、第1の表示領域および第2の表示領域から優先度が高い領域を決定されてよい。第1の視界領域、第2の視界領域は、表示装置の制御装置が決定してもよいし、外部の制御装置が決定したものを受けしてもよい。優先度の高い領域の解像度を、優先度が高い領域以外の領域の解像度よりも高く制御してよい。つまり優先度が相対的に低い領域の解像度を低くしてよい。

#### 【0124】

なお、第1の視界領域や優先度が高い領域の決定には、AIを用いてもよい。AIは、眼球の画像と当該画像の眼球が実際に見ていた方向とを教師データとして、眼球の画像から視線の角度、視線の先の目的物までの距離を推定するよう構成されたモデルであってよい。AIプログラムは、表示装置が有しても、光電変換装置が有しても、外部装置が有してもよい。外部装置が有する場合は、通信を介して、表示装置に伝えられる。

#### 【0125】

視認検知に基づいて表示制御する場合、外部を撮像する光電変換装置を更に有するスマートグラスに好ましく適用できる。スマートグラスは、撮像した外部情報をリアルタイムで表示することができる。

#### 【0126】

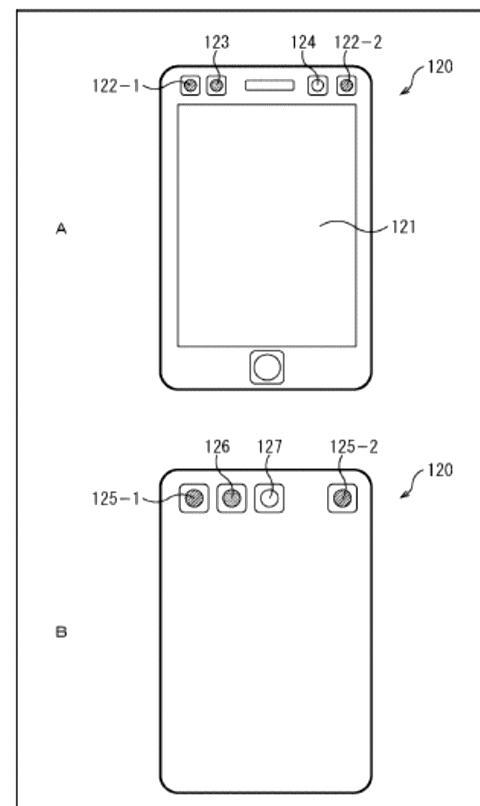

上記の実施形態の光電変換装置100は、以下に例示されるようなスマートフォンやタブレットなどの電子機器に適用されてもよい。図28には、固体撮像装置として構成された光電変換装置100が搭載された電子機器120の外観の一例を示す図である。図28のAには、電子機器120の表面側が示されており、図28のBには、電子機器120の背面側が示されている。

#### 【0127】

図28のAに示すように、電子機器120の表面の中央には、画像を表示するディスプレイ121が配置されている。そして、電子機器120の表面の上辺に沿って、光電変換装置100が用いられるフロントカメラ122-1および122-2、赤外光を発光するIR光源123、並びに、可視光を発光する可視光源124が配置されている。

#### 【0128】

また、図28のBに示すように、電子機器120の背面の上辺に沿って、光電変換装置100が用いられるリアカメラ125-1および125-2、赤外光を発光するIR光源126、並びに、可視光を発光する可視光源127が配置されている。

#### 【0129】

このように構成されている電子機器120では、上述した光電変換装置100を適用することで、例えば、より高感度な画像を撮像することができる。なお、光電変換装置100は、その他、赤外線センサや、アクティブ赤外線光源を用いた測距センサ、セキュリティカメラ、個人または生体認証カメラなどの電子機器に適用することができる。これにより、それらの電子機器の感度や性能などの向上を図ることができる。また、光源電力の削減によるシステムの低消費電力化を実現することができる。

#### 【0130】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱すること

10

20

30

40

50

なく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

**【符号の説明】**

**【0 1 3 1】**

1 2 : 画素アレイ領域、1 3 : 周辺領域、3 0 1 : センサ基板、3 0 2 : 第 1 半導体層、3 0 3 : 第 1 配線構造、S 1 : 第 1 面、S 2 : 第 2 面、3 1 1 : 第 1 半導体領域、3 1 5 : 第 2 半導体領域、1 3 1 1 : 第 3 半導体領域、1 3 1 5 : 第 4 半導体領域、1 3 1 3 : 第 5 半導体領域

**【図面】**

**【図 1】**

**【図 2】**

10

20

30

40

**【図 3】**

**【図 4】**

50

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9A】

【図9B】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15A】

【図15B】

10

20

【図16A】

【図16B】

30

40

50

【図17】

【 図 1 8 】

【 図 1 9 】

【 図 2 0 】

10

20

30

40

50

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【 図 2 4 】

10

20

30

40

50

【図25】

【図26】

10

20

30

40

【図27】

【図28】

50

---

フロントページの続き

F ターム（参考） CB13 FA06 FA08 FA14 FA26 FA27 FA28 GA02 GB07 GC07

GC11 GD03 GD04 HA22 HA25 HA30

5C024 CX11 EX03 GX03 GY39 GY41 GY45