(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

20 January 2011 (20.01.2011)

(10) International Publication Number

**WO 2011/007682 A1**

(51) International Patent Classification:

*H01L 29/786* (2006.01)   *H01L 21/428* (2006.01)

*G02F 1/1368* (2006.01)   *H01L 21/477* (2006.01)

*H01L 21/336* (2006.01)

(21) International Application Number:

PCT/JP2010/061293

(22) International Filing Date:

25 June 2010 (25.06.2010)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

2009-168650   17 July 2009 (17.07.2009)   JP

(71) Applicant (for all designated States except US): SEMICONDUCTOR ENERGY LABORATORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) Inventor; and

(75) Inventor/Applicant (for US only): MIYANAGA, Akiharu [JP/JP]; c/o SEMICONDUCTOR ENERGY LABO-

RATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK,

*[Continued on next page]*

(54) Title: METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE

(57) Abstract: An object is to provide a method for manufacturing a highly reliable semiconductor device including a transistor with stable electric characteristics. A method for manufacturing a semiconductor device includes the steps of: forming a gate electrode over a substrate having an insulating surface; forming a gate insulating film over the gate electrode; forming an oxide semiconductor film over the gate insulating film; irradiating the oxide semiconductor film with an electromagnetic wave such as a microwave or a high frequency; forming a source electrode and a drain electrode over the oxide semiconductor film irradiated with the electromagnetic wave; and forming an oxide insulating film, which is in contact with part of the oxide semiconductor film, over the gate insulating film, the oxide semiconductor film, the source electrode, and the drain electrode.

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, **Published:**

GW, ML, MR, NE, SN, TD, TG).

— *with international search report (Art. 21(3))*

## DESCRIPTION

**METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE**5 **TECHNICAL FIELD**

[0001]

The present invention relates to a method for manufacturing a semiconductor device including an oxide semiconductor.

10 **BACKGROUND ART**

[0002]

Thin film transistors (TFTs) are one of field effect transistors and include a semiconductor film with a thickness of approximately several to several hundreds of nanometers, which is formed over an insulating surface, as an active layer. The thin film transistors are widely applied to flat panel displays such as liquid crystal display devices and light-emitting devices and electronic devices such as integrated circuits (ICs).

[0003]

In recent years, transistors including a metal oxide as an active layer as well as silicon or germanium have developed. The metal oxide is used for various applications. For example, indium oxide is a well-known metal oxide and used as a material of a transparent electrode included in a liquid crystal display device or the like. Some metal oxides have semiconductor characteristics and are called oxide semiconductors. The examples of such metal oxides having semiconductor characteristics are a tungsten oxide, a tin oxide, an indium oxide, a zinc oxide, and the like. A transistor in which a channel formation region is formed using such a metal oxide having semiconductor characteristics is known (Patent Documents 1 to 4 and Non-Patent Document 1).

[0004]

As metal oxides, not only single-component oxides but also multi-component oxides are known. For example,  $\text{InGaO}_3(\text{ZnO})_m$  ( $m$  is natural number) having a homologous phase is known as a multi-component oxide semiconductor including In,

Ga, and Zn (Non-Patent Documents 2 to 4). Furthermore, it is confirmed that an oxide semiconductor including such an In-Ga-Zn-based oxide is applicable to a channel layer of a transistor (Patent Document 5 and Non-Patent Documents 5 and 6).

[References]

5 [Patent Documents]

[0005]

[Patent Document 1] Japanese Published Patent Application No. S60-198861

[Patent Document 2] Japanese Published Patent Application No. H8-264794

[Patent Document 3] Japanese Translation of PCT International Application No.

10 H11-505377

[Patent Document 4] Japanese Published Patent Application No. 2000-150900

[Patent Document 5] Japanese Published Patent Application No. 2004-103957

[Non-Patent Documents]

[0006]

15 [Non-Patent Document 1] M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cillessen,

J. B. Giesbers, R. P. Weening, and R. M. Wolf, "A ferroelectric transparent thin-film

transistor", *Appl. Phys. Lett.*, 17 June 1996, Vol. 68, pp. 3650-3652

[Non-Patent Document 2] M. Nakamura, N. Kimizuka, and T. Mohri, "The Phase

Relations in the  $\text{In}_2\text{O}_3$ - $\text{Ga}_2\text{ZnO}_4$ - $\text{ZnO}$  System at 1350 °C", *J. Solid State Chem.*, 1991,

20 Vol. 93, pp. 298-315

[Non-Patent Document 3] N. Kimizuka, M. Isobe, and M. Nakamura, "Syntheses and

Single-Crystal Data of Homologous Compounds,  $\text{In}_2\text{O}_3(\text{ZnO})_m$  ( $m$  = 3, 4, and 5),

$\text{InGaO}_3(\text{ZnO})_3$ , and  $\text{Ga}_2\text{O}_3(\text{ZnO})_m$  ( $m$  = 7, 8, 9, and 16) in the  $\text{In}_2\text{O}_3$ - $\text{ZnGa}_2\text{O}_4$ - $\text{ZnO}$

System", *J. Solid State Chem.*, 1995, Vol. 116, pp. 170-178

25 [Non-Patent Document 4]

M. Nakamura, N. Kimizuka, T. Mohri, and M. Isobe, "Syntheses and crystal structures

of new homologous compound, indium iron zinc oxides ( $\text{InFeO}_3(\text{ZnO})_m$  ( $m$ : natural

number) and related compounds", *KOTAI BUTSURI (SOLID STATE PHYSICS)*, 1993,

Vol. 28, No. 5, pp. 317-327

30 [Non-Patent Document 5] K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H.

Hosono, "Thin-film transistor fabricated in single-crystalline transparent oxide

semiconductor", *SCIENCE*, 2003, Vol. 300, pp. 1269-1272

[Non-Patent Document 6] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors", *NATURE*, 2004, Vol. 432, pp. 488-492

5 [0007]

It is an object to provide a method for manufacturing a highly reliable semiconductor device including a transistor with stable electric characteristics.

[0008]

In a method for manufacturing a semiconductor device including a transistor in

10 which a channel formation region is formed using an oxide semiconductor, irradiation

with an electromagnetic wave such as a microwave or a high frequency is performed to

reduce impurities including a polar molecule such as moisture in an oxide

semiconductor film and increase purity of the oxide semiconductor film. Further,

irradiation with an electromagnetic wave is performed to reduce impurities such as

15 moisture which exists in a gate insulating film as well as an oxide semiconductor film

and to reduce impurities such as moisture which exists at interfaces between the oxide

semiconductor film and upper and lower films provided in contact therewith.

[0009]

Specifically, in order to reduce impurities such as moisture, after the formation

20 of the oxide semiconductor film, the oxide semiconductor film is irradiated with an

electromagnetic wave with a frequency which is easily absorbed into water (the

frequency of a microwave is greater than or equal to 300 MHz and less than or equal to

3 THz, and the frequency of a high frequency is greater than or equal to 1 MHz and less

than or equal to 300 MHz) under a nitrogen atmosphere, an inert gas atmosphere such

25 as a rare gas (for example, argon or helium) atmosphere, or reduced pressure while the

oxide semiconductor film is exposed. As a result, moisture included in the oxide

semiconductor film is reduced. Note that it can be considered that since the oxide

semiconductor film also include hydrogen and OH, desorption of hydrogen and OH

from the oxide semiconductor film is caused by the irradiation with an electromagnetic

30 wave.

[0010]

Irradiation of the oxide semiconductor film with an electromagnetic wave and

heat treatment may be performed at the same time. When the irradiation with an electromagnetic wave is performed at the same time as the heat treatment, impurities such as moisture in the oxide semiconductor film can be reduced more effectively in a short time. Note that the heat treatment is performed at a temperature where a metal 5 having a low melting point such as Zn included in the oxide semiconductor is evaporated as less as possible, for example, higher than or equal to 100 °C and lower than 350 °C, preferably higher than or equal to 150 °C and lower than 250 °C. Note that even when the oxide semiconductor film is irradiated with an electromagnetic wave at room temperature, a water molecule absorbs electromagnetic wave energy and 10 vibrates. Thus, it can be expected that the temperature of the oxide semiconductor film becomes higher than room temperature as a result. When the heat treatment is performed at the same time as the irradiation with an electromagnetic wave, the temperature of the oxide semiconductor film is desirably controlled in consideration of the amount of increase in the temperature due to the irradiation with an electromagnetic 15 wave. Moreover, when the irradiation with an electromagnetic wave is performed in combination with the heat treatment, the temperature of the oxide semiconductor film is increased to the heat treatment temperature and then the irradiation with an electromagnetic wave is performed. After that, the oxide semiconductor film is slowly cooled to a temperature ranging from higher than or equal to room temperature and 20 lower than 100 °C.

[0011]

In order to remove impurities such as moisture which exists in an oxide semiconductor film only by heat treatment in a short time, it is more effective to heat the oxide semiconductor film to a temperature higher than the above temperature range. 25 However, according to an embodiment of the present invention, with the irradiation with an electromagnetic wave, impurities such as moisture can be removed effectively in a short time even at a temperature within the above temperature range or a temperature lower than the above temperature range. Therefore, the composition ratio of the oxide semiconductor can be prevented from changing due to evaporation of a 30 metal having a low melting point such as Zn in removal of impurities such as moisture, and thus deterioration in characteristics of the transistor manufactured using the oxide

semiconductor can be prevented.

[0012]

An oxide semiconductor highly purified by desorption of impurities such as moisture, hydrogen, or OH which serves as an electron donor (donor) (a purified OS) is an intrinsic semiconductor (an i-type semiconductor) or a substantially intrinsic semiconductor. When the above oxide semiconductor is included in a transistor, deterioration in characteristics of the transistor due to impurities, for example, variation in the threshold voltage, can be prevented, which can improve reliability.

[0013]

Moreover, after the oxide semiconductor film is irradiated with an electromagnetic wave to remove impurities such as moisture, an oxide insulating film may be formed in contact with the oxide semiconductor film. With the above structure, oxygen is supplied to an oxide semiconductor film even when an oxygen vacancy occurs in the oxide semiconductor film due to irradiation with an electromagnetic wave or heat treatment performed at the same time as the irradiation with an electromagnetic wave. Therefore, a vacancy of oxygen serving as a donor can be reduced in part of the oxide semiconductor film, which is in contact with the oxide insulating film, and thus the stoichiometric proportion can be satisfied. As a result, an oxide semiconductor film can be made to be an intrinsic semiconductor film or a substantially intrinsic semiconductor film. Accordingly, electric characteristics of the transistor can be improved and variation in the electric characteristics thereof can be reduced.

[0014]

Specifically, the concentration of hydrogen in the highly purified oxide semiconductor, which is measured by secondary ion mass spectrometry (SIMS), is  $5 \times 10^{19}/\text{cm}^3$  or less, preferably  $5 \times 10^{18}/\text{cm}^3$  or less, more preferably  $5 \times 10^{17}/\text{cm}^3$  or less, still more preferably less than  $1 \times 10^{16}/\text{cm}^3$ . In addition, the carrier density of the oxide semiconductor film, which is measured by Hall effect measurement, is less than  $1 \times 10^{14}/\text{cm}^3$ , preferably less than  $1 \times 10^{12}/\text{cm}^3$ , more preferably less than  $1 \times 10^{11}/\text{cm}^3$ . Furthermore, the band gap of the oxide semiconductor is 2 eV or more, preferably 2.5 eV or more, more preferably 3 eV or more.

[0015]

The analysis of the concentration of hydrogen in the oxide semiconductor film is described here. The concentrations of hydrogen in the oxide semiconductor film and a conductive film are measured by secondary ion mass spectrometry (SIMS). It is known that it is difficult to obtain data in the proximity of a surface of a sample or in the 5 proximity of an interface between stacked films formed using different materials by the SIMS analysis in principle. Thus, in the case where distributions of the hydrogen concentrations of the films in thickness directions are analyzed by SIMS, an average value in a region where the films are provided, the value is not greatly changed, and almost the same value can be obtained are employed as the hydrogen concentration. 10 Further, in the case where the thickness of the film is small, a region where almost the same value can be obtained cannot be found in some cases due to the influence of the hydrogen concentration of the films adjacent to each other. In this case, the maximum value or the minimum value of the hydrogen concentration of a region where the films are provided is employed as the hydrogen concentration of the film. Furthermore, in 15 the case where a mountain-shaped peak having the maximum value and a valley-shaped peak having the minimum value do not exist in the region where the films are provided, the value of the inflection point is employed as the hydrogen concentration.

[0016]

As the oxide semiconductor, a four-component metal oxide such as an 20 In-Sn-Ga-Zn-O-based oxide semiconductor, a three-component metal oxide such as an In-Ga-Zn-O-based oxide semiconductor, an In-Sn-Zn-O-based oxide semiconductor, an In-Al-Zn-O-based oxide semiconductor, a Sn-Ga-Zn-O-based oxide semiconductor, an Al-Ga-Zn-O-based oxide semiconductor, and a Sn-Al-Zn-O-based oxide semiconductor, or a two-component metal oxide such as an In-Zn-O-based oxide semiconductor, a 25 Sn-Zn-O-based oxide semiconductor, an Al-Zn-O-based oxide semiconductor, a Zn-Mg-O-based oxide semiconductor, a Sn-Mg-O-based oxide semiconductor, an In-Mg-O-based oxide semiconductor, an In-Ga-O-based oxide semiconductor, an In-O-based oxide semiconductor, a Sn-O-based oxide semiconductor, and a Zn-O-based oxide semiconductor and be used. Note that in this specification, for example, an 30 In-Sn-Ga-Zn-O-based oxide semiconductor means a metal oxide including indium (In), tin (Sn), gallium (Ga), and zinc (Zn). There is no particular limitation on the stoichiometric proportion. The above oxide semiconductor may include silicon.

[0017]

Moreover, oxide semiconductors can be represented by the chemical formula,  $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ). Here, M represents one or more metal elements selected from Ga, Al, Mn, and Co.

5 [0018]

Note that as the oxide insulating film formed in contact with the oxide semiconductor film, an inorganic insulating film which blocks entry of impurities such as moisture, a hydrogen ion, and  $\text{OH}^-$ , specifically, a silicon oxide film or a silicon nitride oxide film is used.

10 [0019]

Moreover, after the oxide insulating film is formed in contact with the oxide semiconductor film, irradiation with an electromagnetic wave may be performed again. When irradiation with an electromagnetic wave is performed again after the oxide insulating film is formed in contact with the oxide semiconductor film, variation in 15 electric characteristics of the transistor can be reduced.

[0020]

A transistor having stable electric characteristics can be manufactured and provided. In addition, a semiconductor device which includes a highly reliable transistor having favorable electric characteristics can be provided.

20

## BRIEF DESCRIPTION OF DRAWINGS

[0021]

In the accompanying drawings:

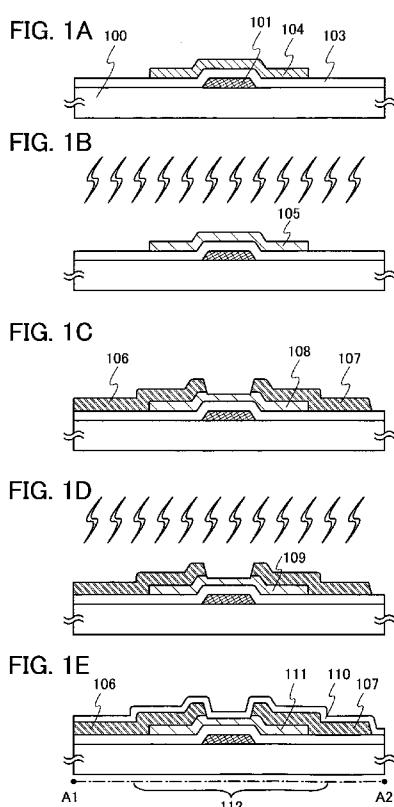

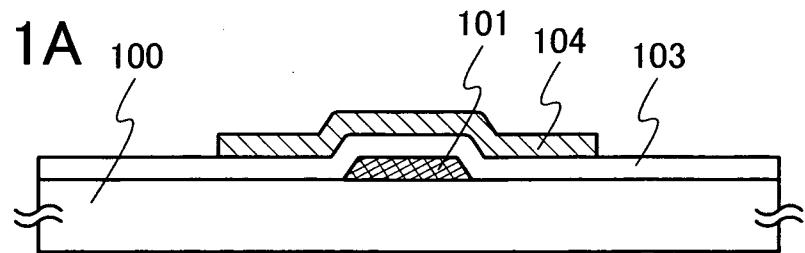

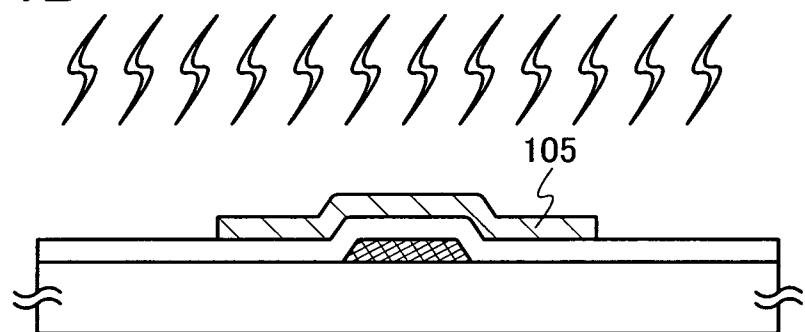

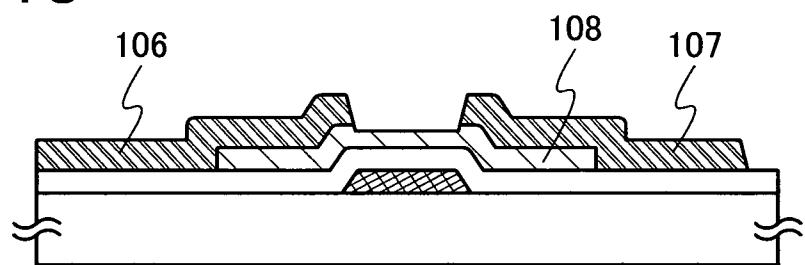

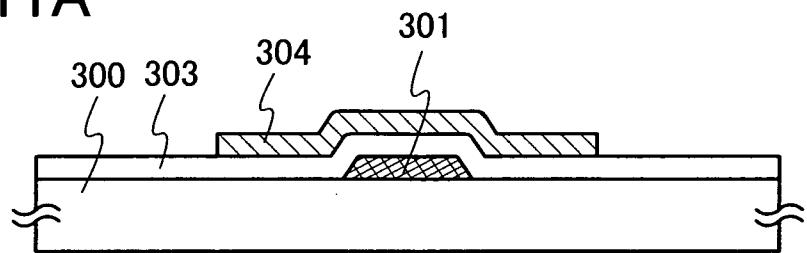

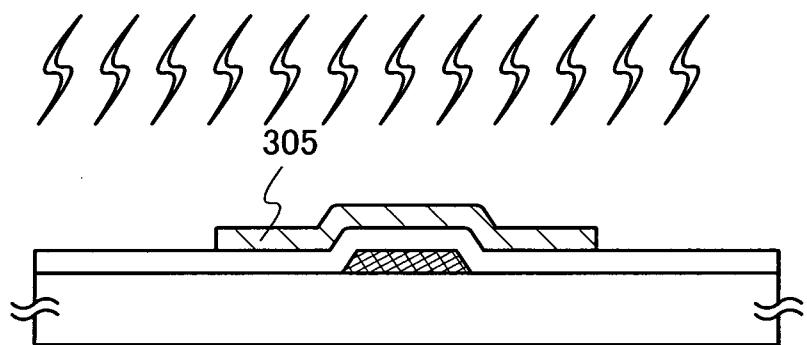

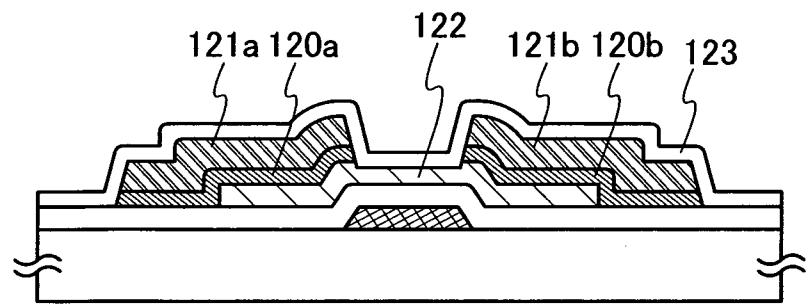

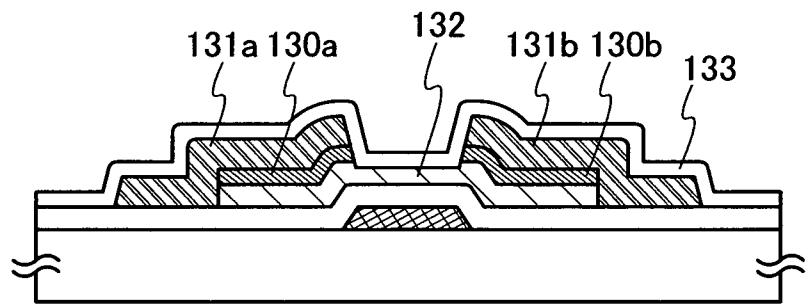

FIGS. 1A to 1E are views illustrating a method for manufacturing a 25 semiconductor device;

FIG. 2 is a top view of a manufactured transistor;

FIGS. 3A to 3D are views illustrating a method for manufacturing a semiconductor device;

FIG. 4 is a top view of a manufactured transistor;

FIGS. 5A to 5C are views illustrating a method for manufacturing a 30 semiconductor device;

FIGS. 6A to 6C are views illustrating a method for manufacturing a semiconductor device;

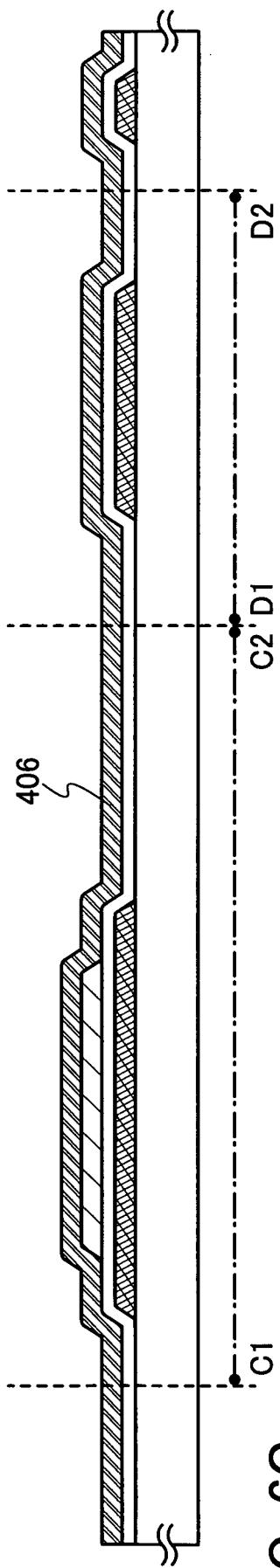

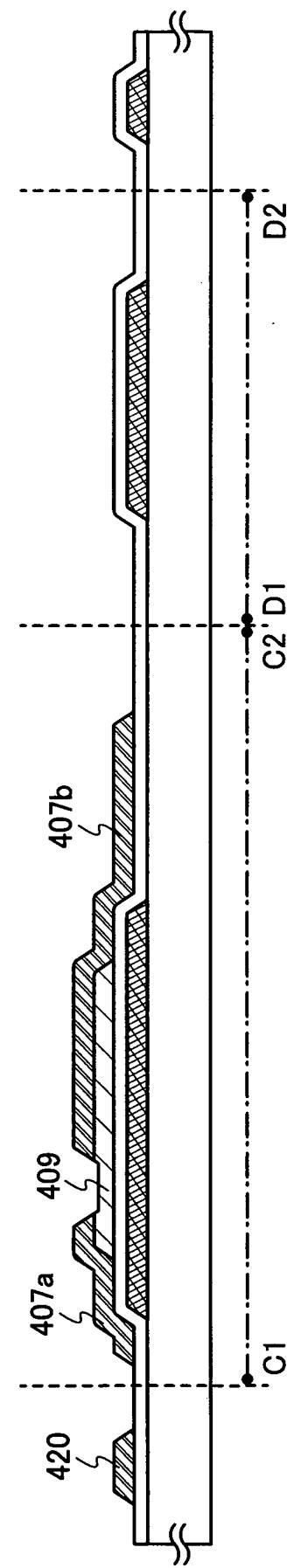

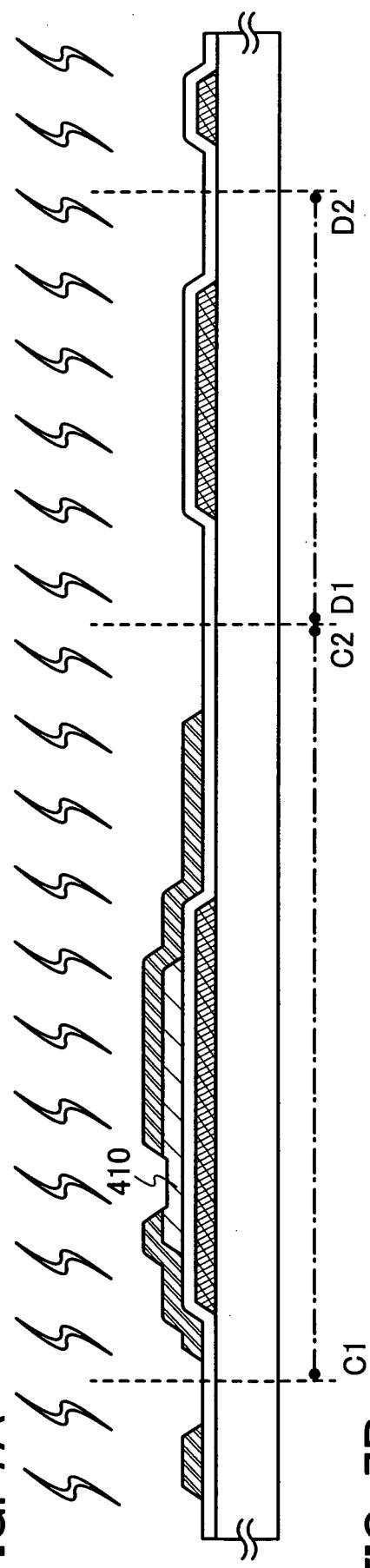

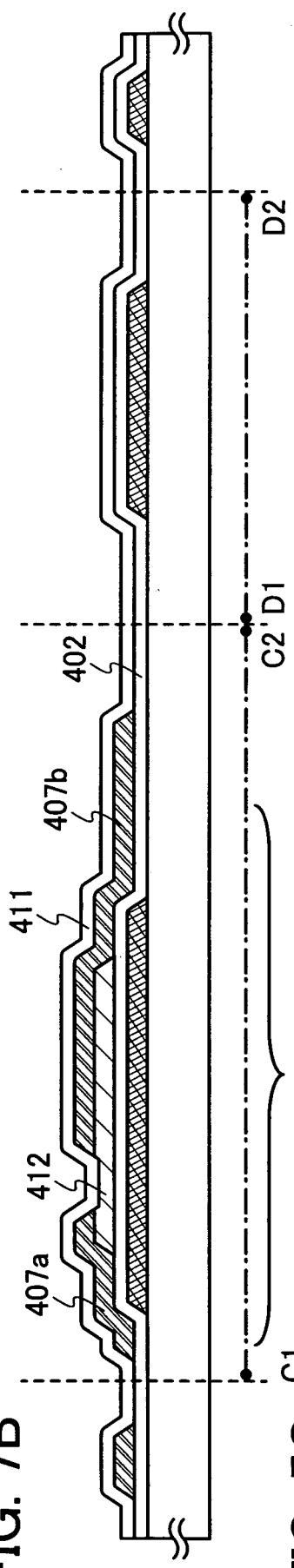

FIGS. 7A to 7C are views illustrating a method for manufacturing a semiconductor device;

5 FIG. 8 is a view illustrating a method for manufacturing a semiconductor device;

FIG. 9 is a view illustrating a method for manufacturing a semiconductor device;

10 FIG. 10 is a view illustrating a method for manufacturing a semiconductor device;

FIGS. 11A to 11D are views illustrating a method for manufacturing a semiconductor device;

FIG. 12 is a top view of a manufactured transistor;

FIGS. 13A to 13C are cross-sectional views of manufactured transistors;

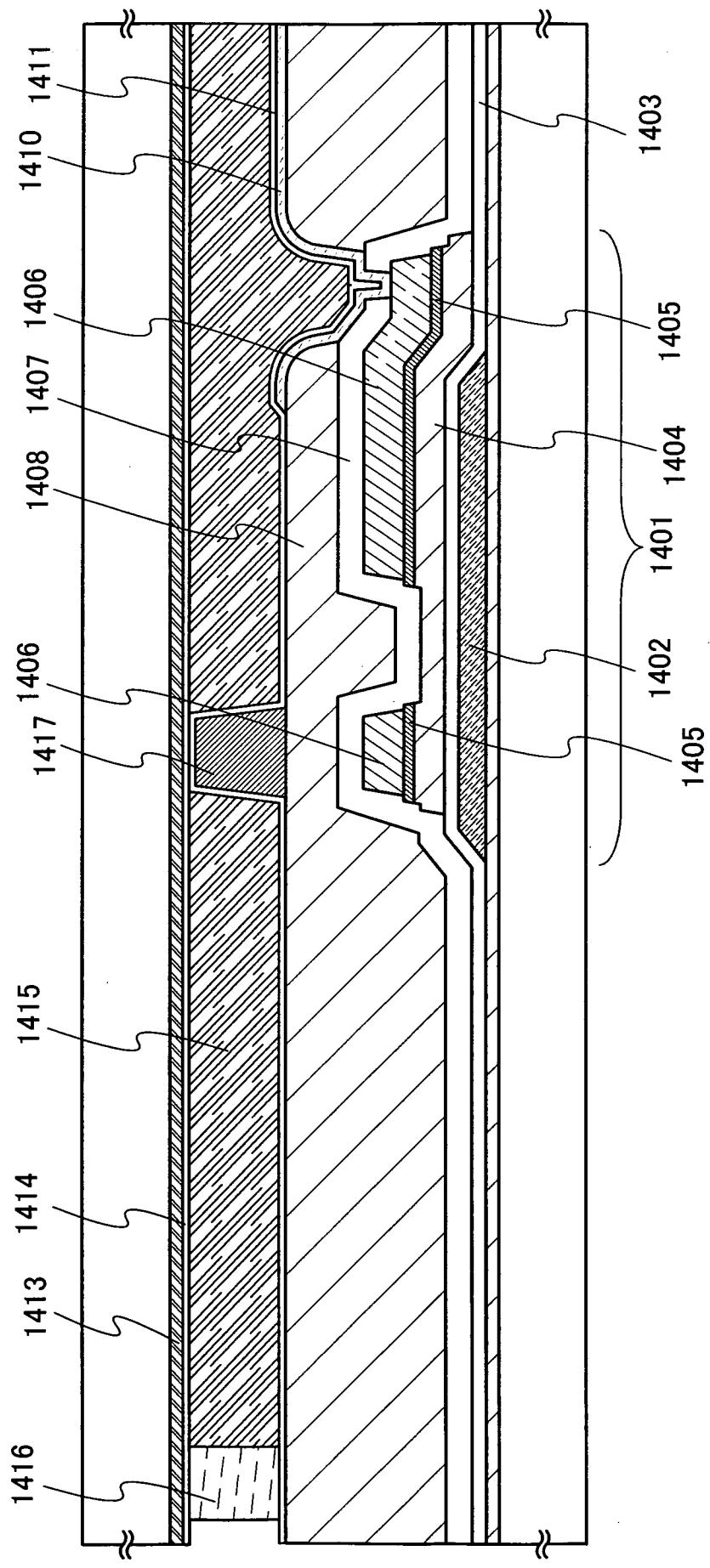

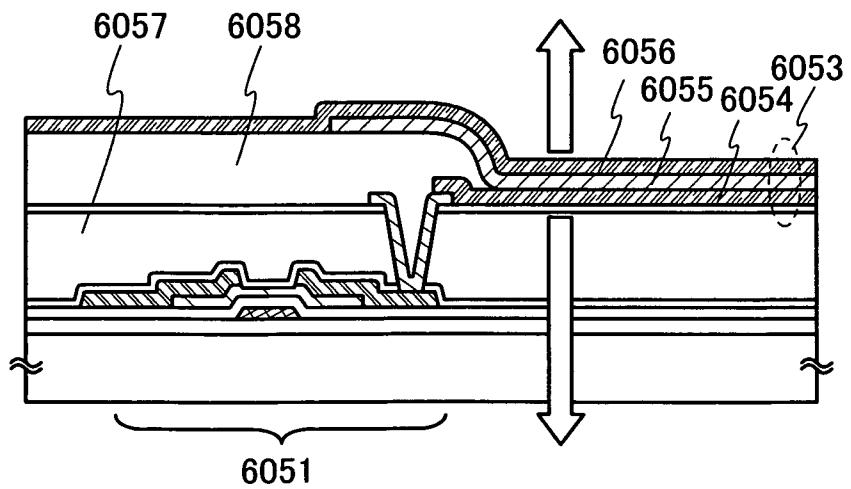

15 FIG. 14 is a cross-sectional view of a liquid crystal display device;

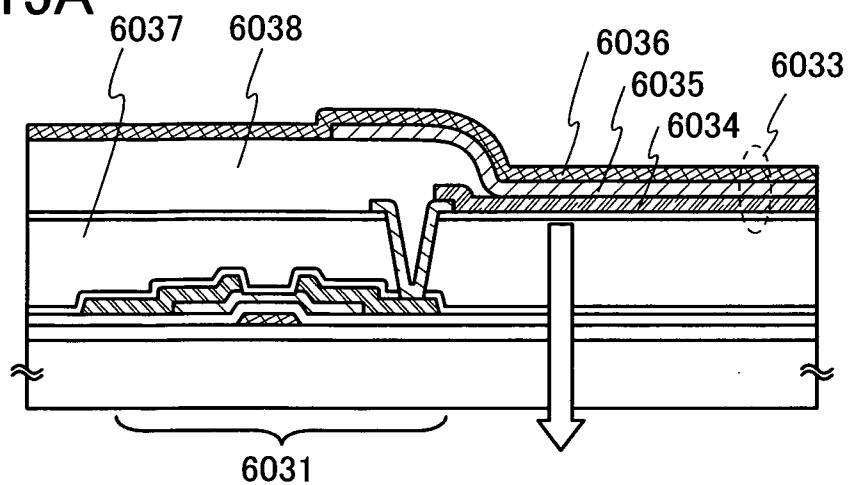

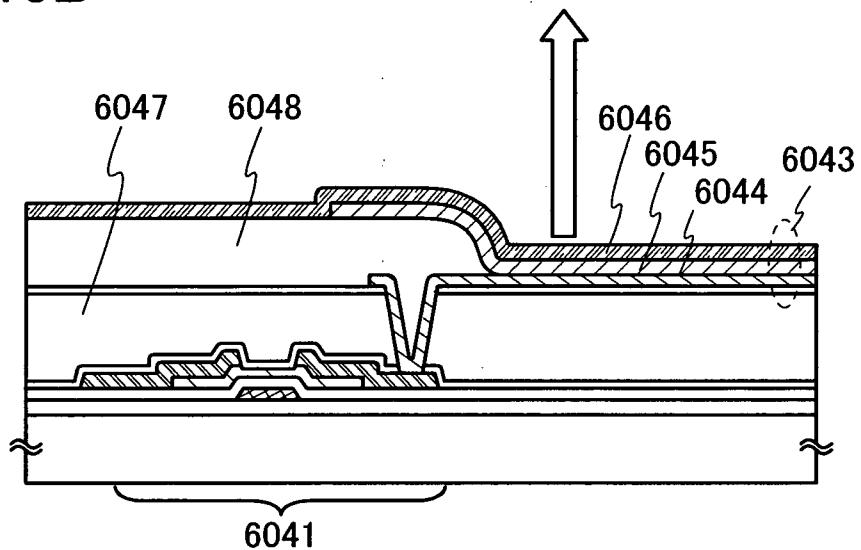

FIGS. 15A to 15C are cross-sectional views of light-emitting devices;

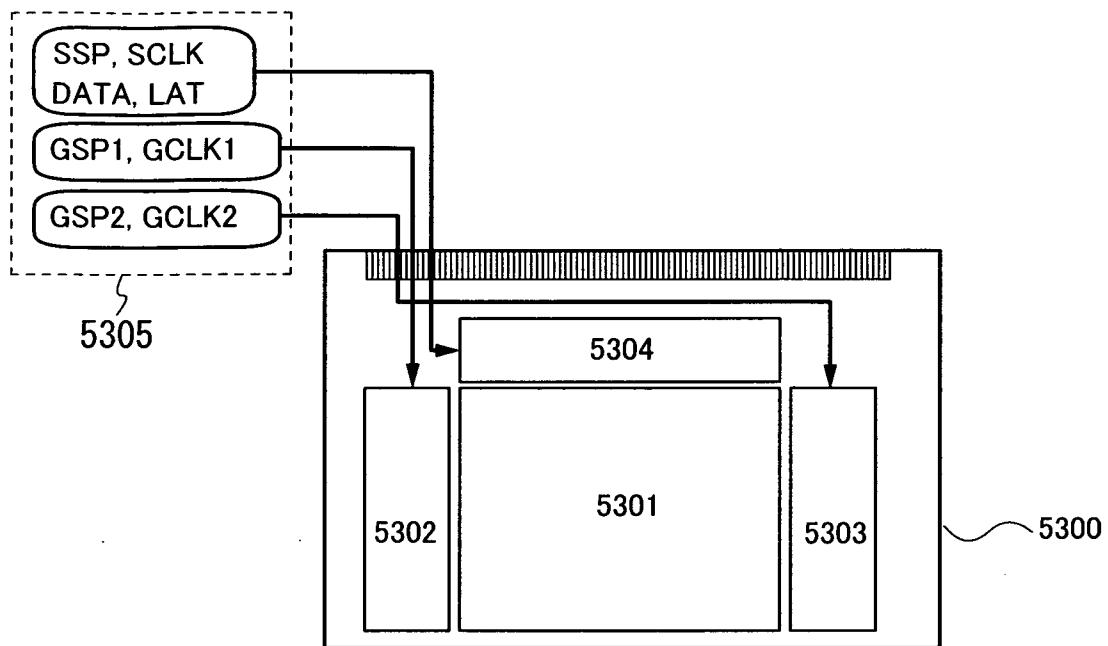

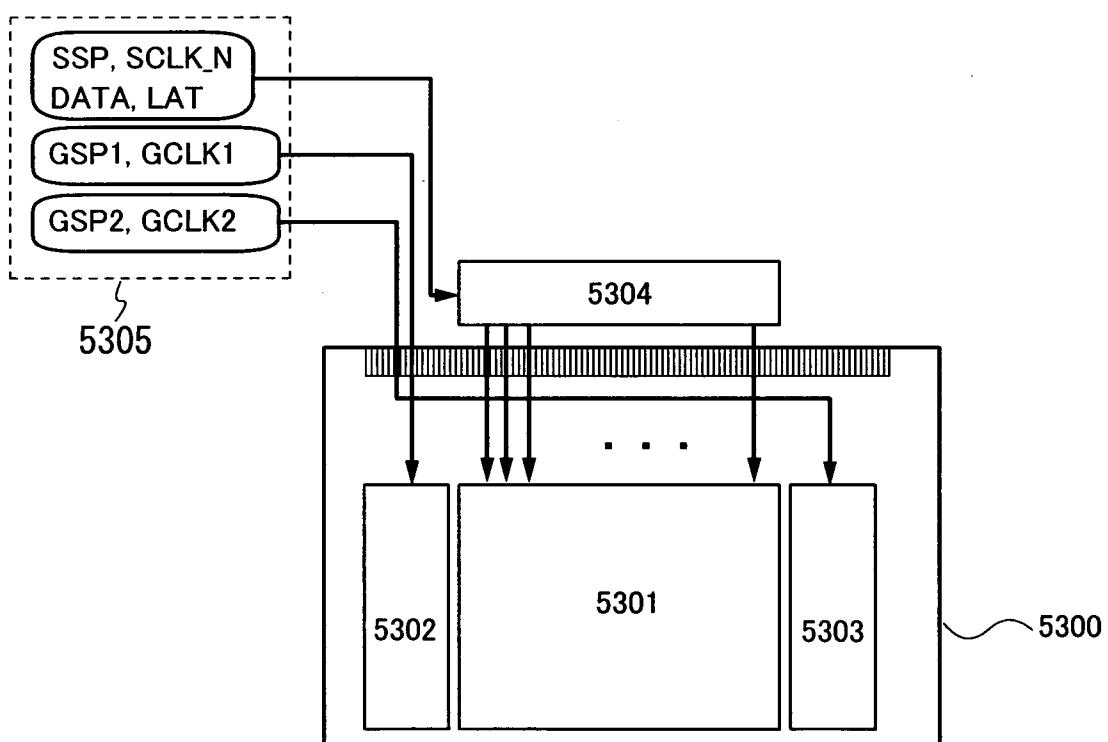

FIGS. 16A and 16B are block diagrams each illustrating a display device;

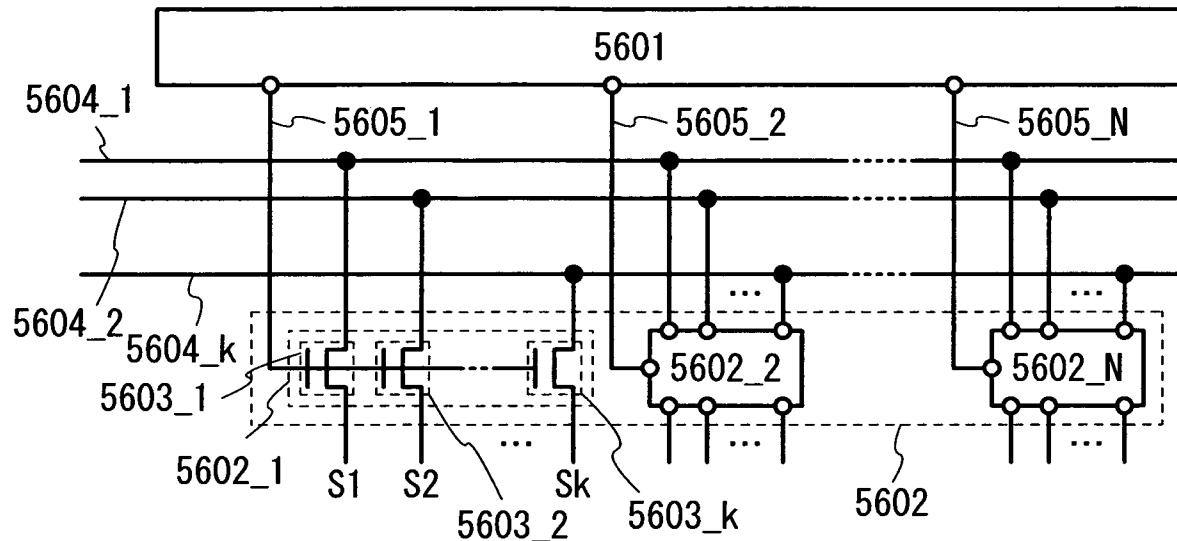

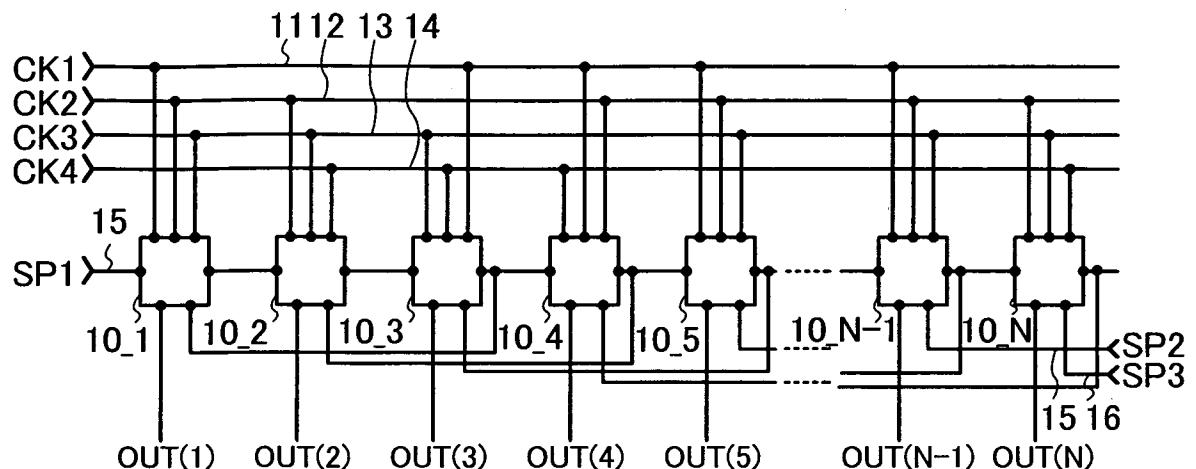

FIGS. 17A and 17B are views each illustrating a structure of a signal line driver circuit;

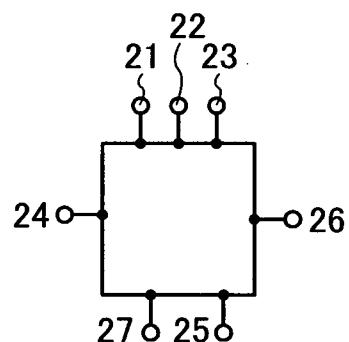

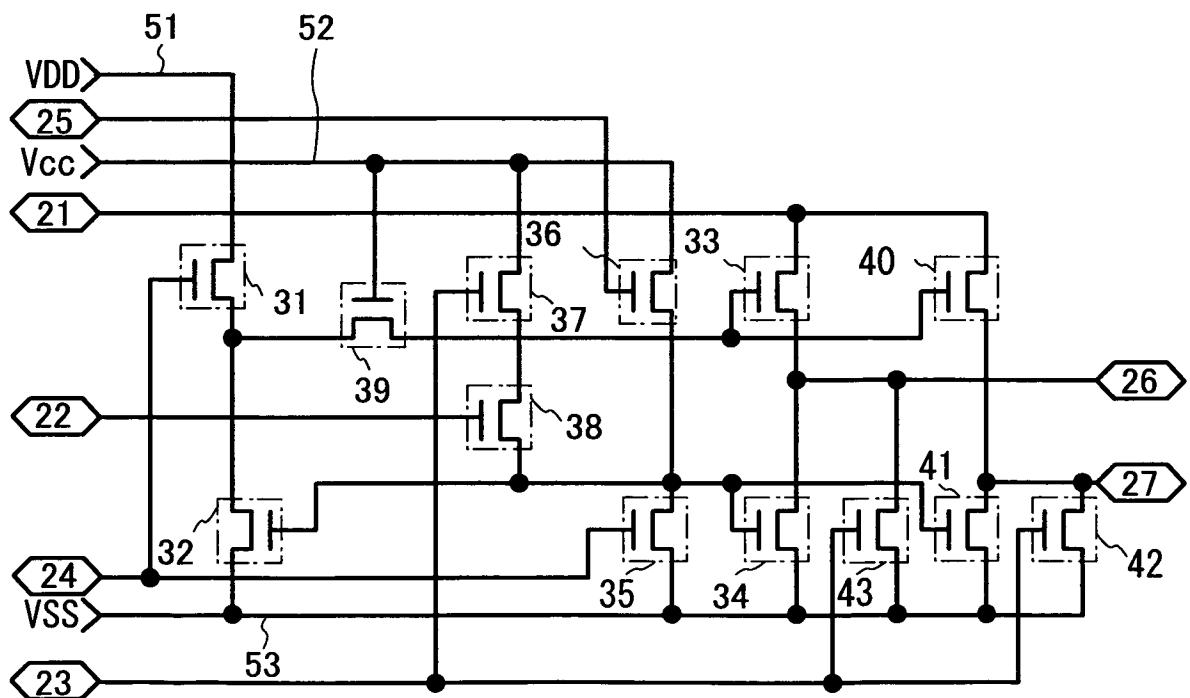

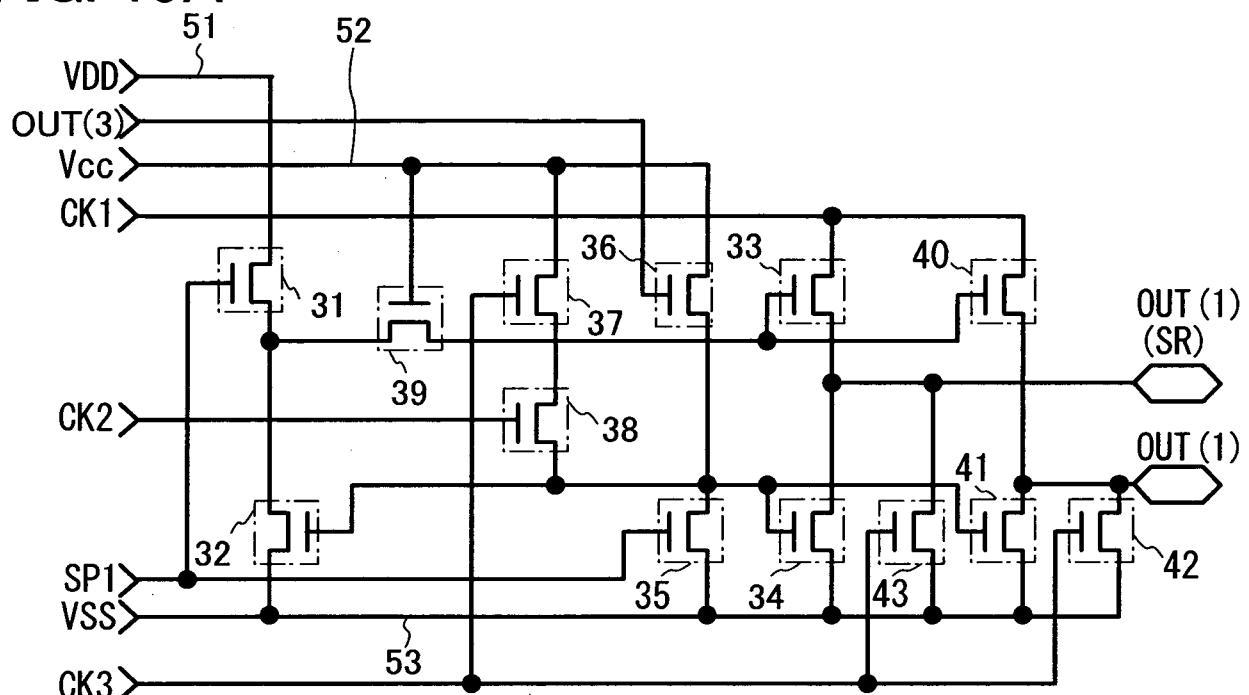

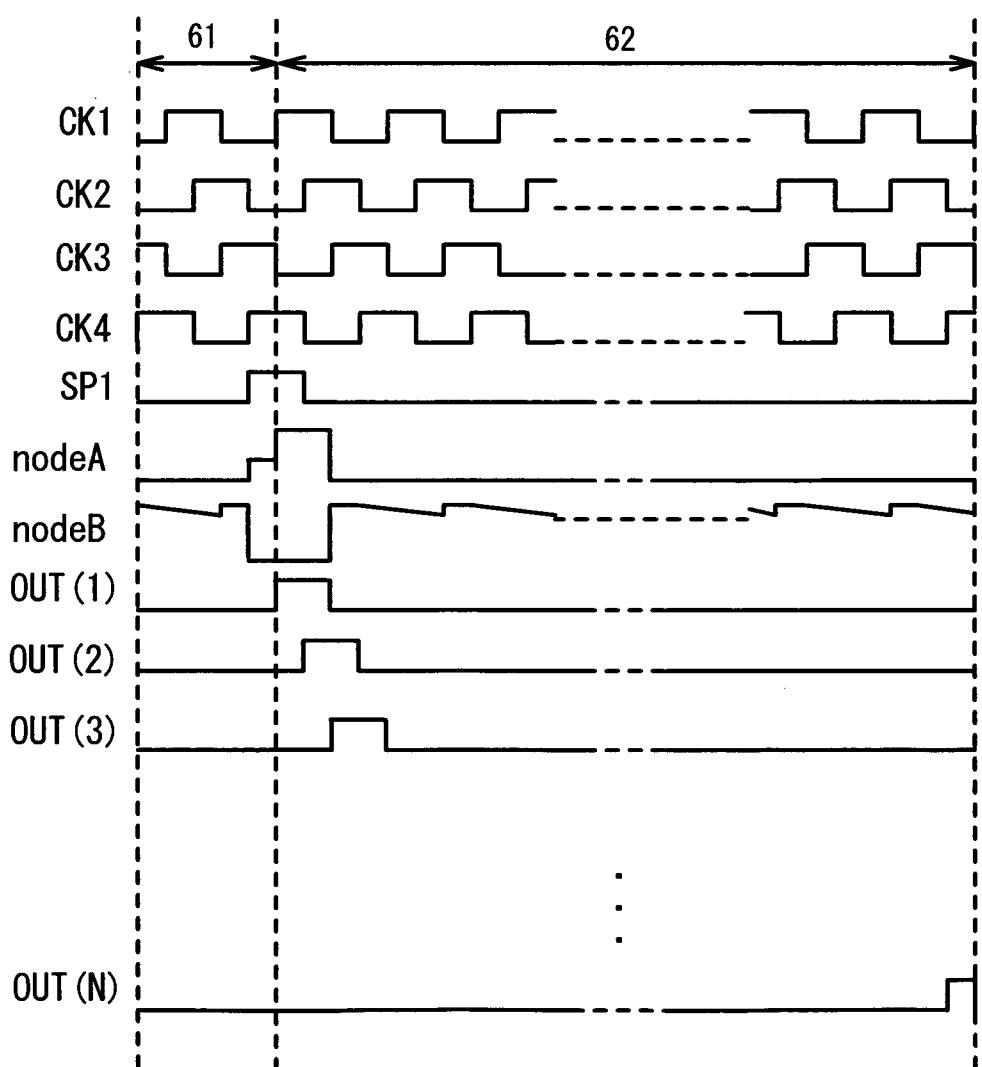

20 FIGS. 18A to 18C are circuit diagrams each illustrating a structure of a shift register;

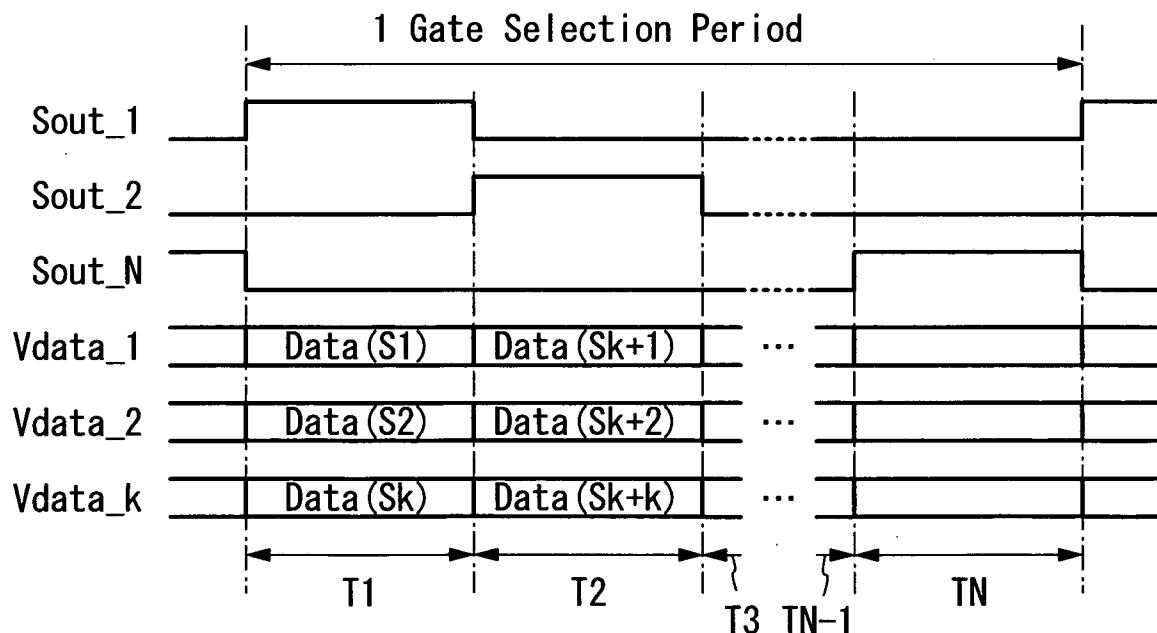

FIG. 19A is a circuit diagram illustrating a structure of a shift register and FIG. 19B is a timing chart illustrating an operation of the shift register;

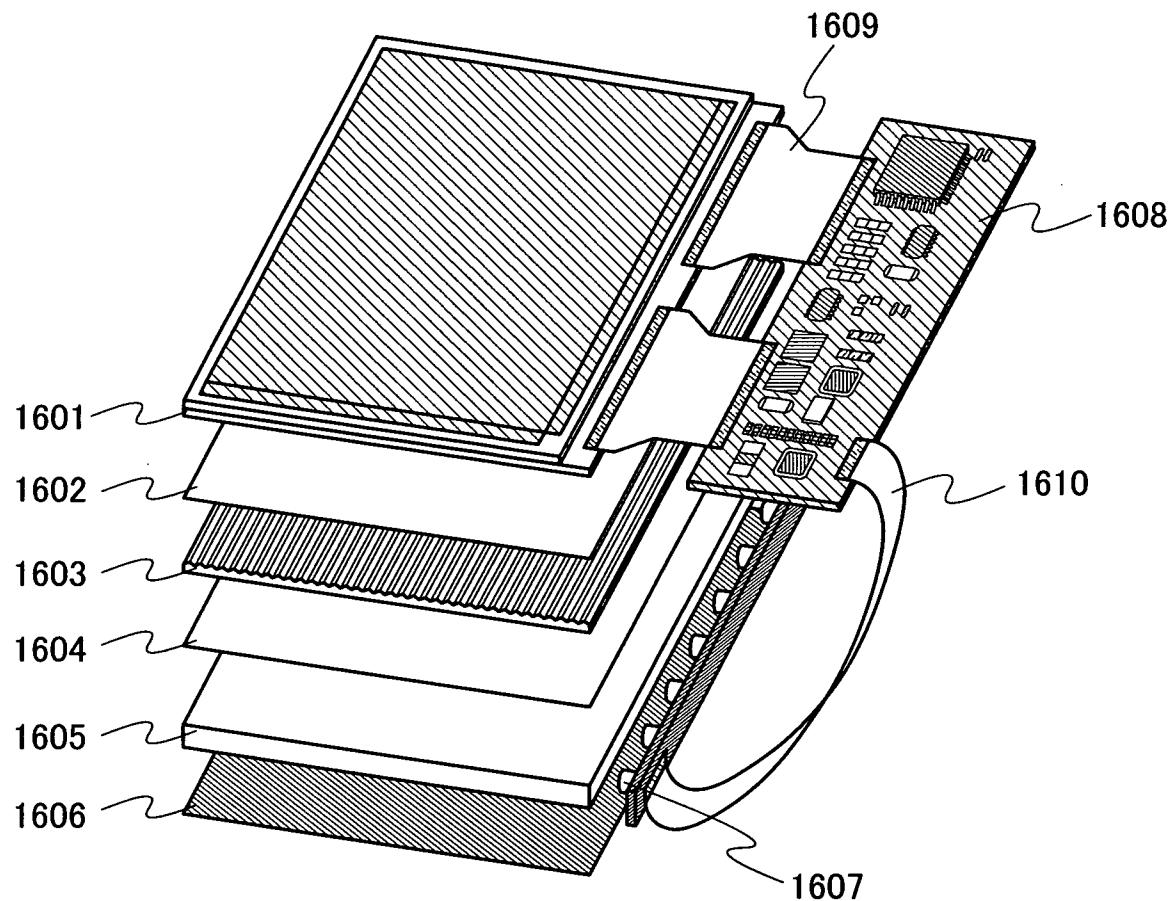

25 FIG. 20 is a view illustrating a structure of a liquid crystal display device module;

FIGS. 21A to 21D are views each illustrating an electronic device including a semiconductor device;

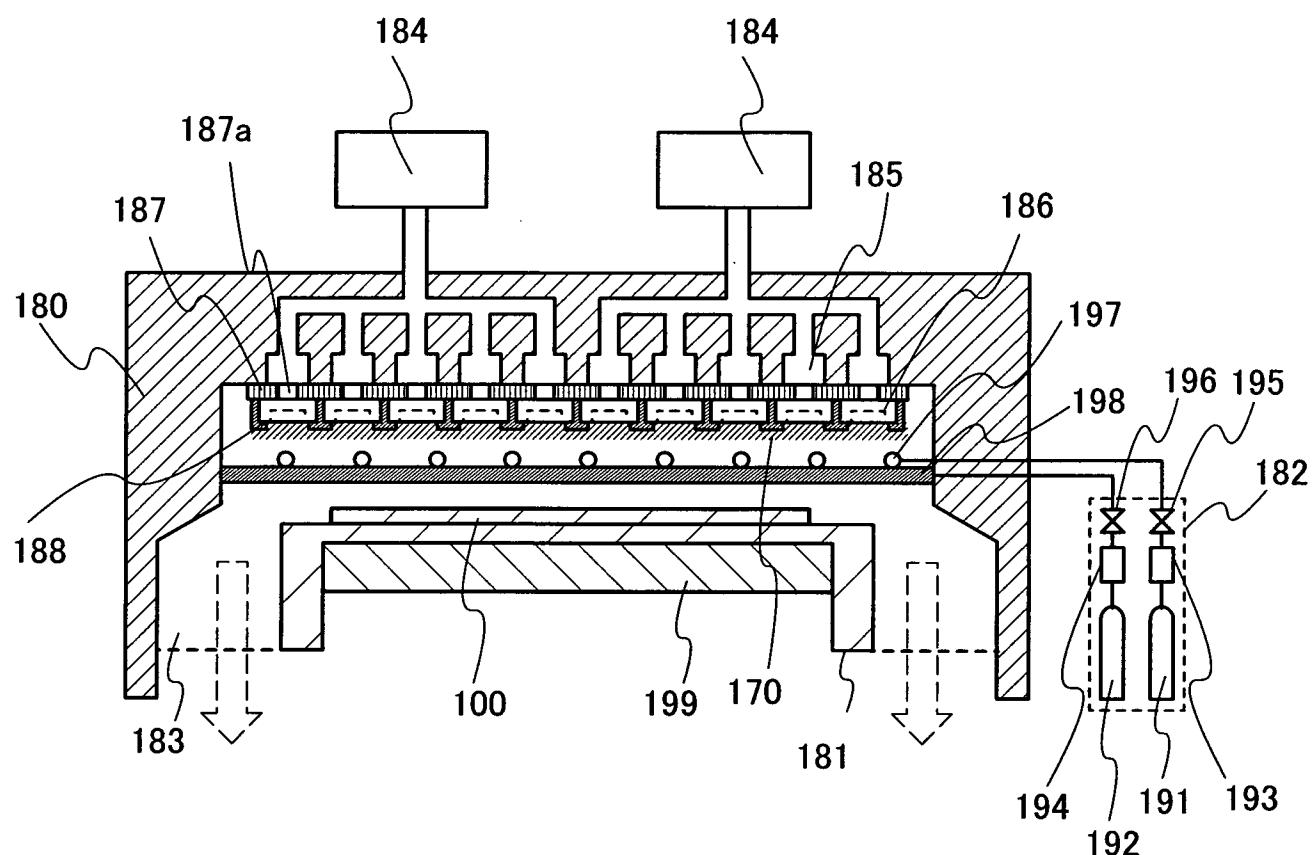

FIG. 22 is a cross-sectional view of a microwave plasma CVD apparatus;

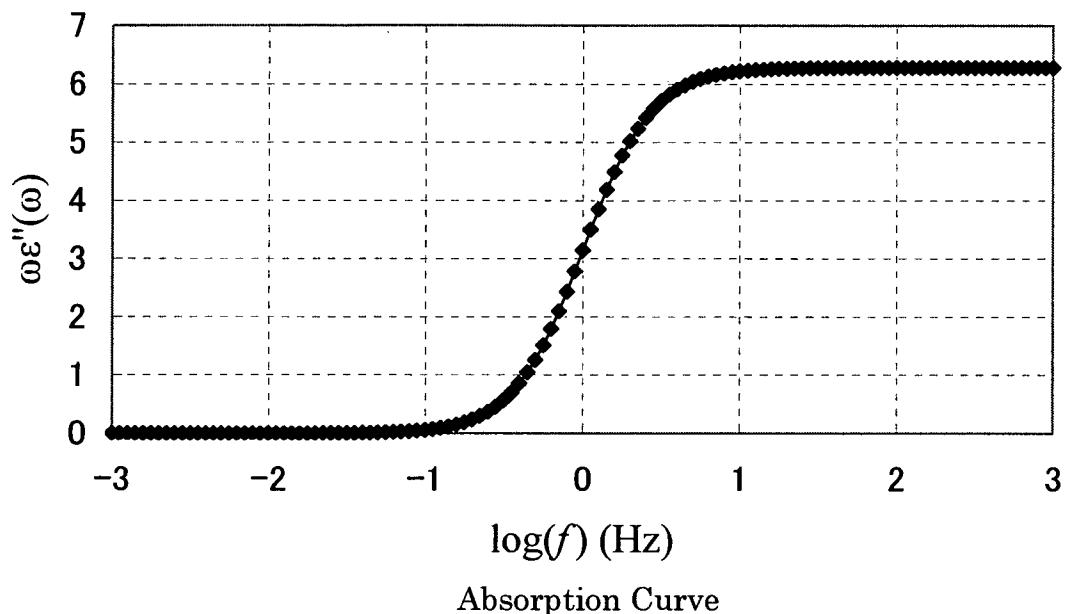

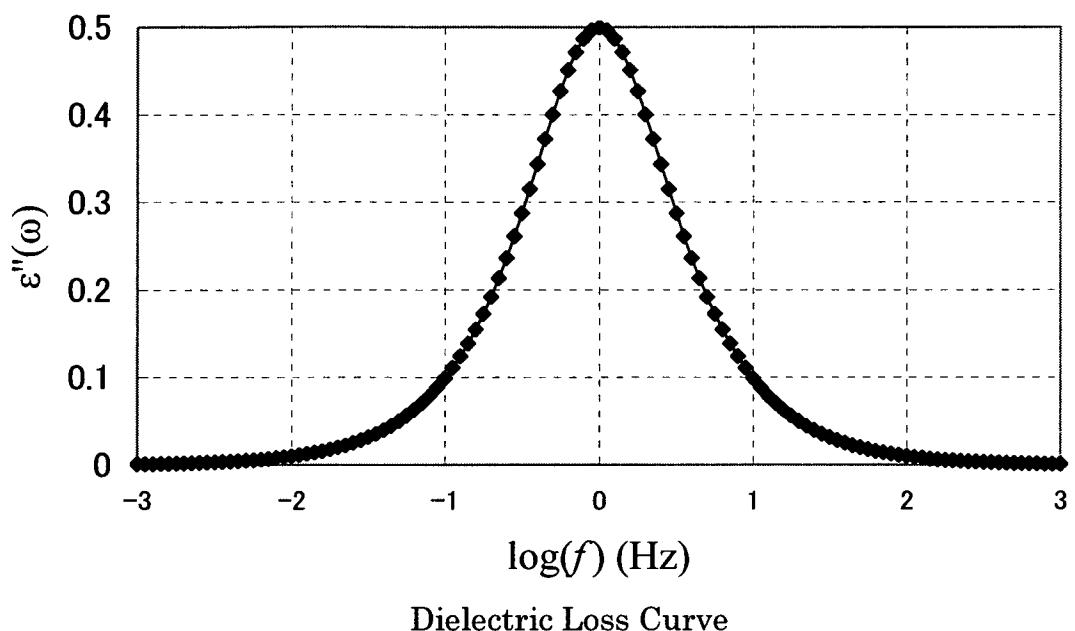

30 FIG. 23 is a graph showing an absorption curve of water with respect to a frequency of an electromagnetic wave in accordance with calculation results; and

FIG. 24 is a graph showing dielectric loss of water with respect to a frequency of an electromagnetic wave in accordance with calculation results.

## [0022]

Embodiments of the present invention will be described below with reference to the accompanying drawings. Note that the present invention is not limited to the following description of the embodiments, and it is readily appreciated by those skilled in the art that modes and details of the present invention can be modified in a variety of ways without departing from the spirit and scope of the present invention. Accordingly, the present invention should not be interpreted as being limited to the following description of the embodiments.

## [0023]

The present invention can be applied to manufacture of any kind of semiconductor devices including microprocessors, integrated circuits such as image processing circuits, RF tags, semiconductor display devices, and the like. A semiconductor device means any device which can function by utilizing semiconductor characteristics, and a semiconductor display device, a semiconductor circuit, and an electronic device are all included in the category of the semiconductor device. The semiconductor display devices include the following in its category: liquid crystal display devices, light-emitting devices in which a light-emitting element typified by an organic light-emitting element (OLED) is provided for each pixel, digital micromirror devices (DMDs), plasma display panels (PDPs), field emission displays (FEDs), and other semiconductor display devices in which a circuit element using a semiconductor film is included in a driver circuit.

## [0024]

## (Embodiment 1)

A method for manufacturing a semiconductor device is described with reference to FIGS. 1A to 1E and FIG. 2.

## [0025]

As illustrated in FIG. 1A, a gate electrode 101 is provided over a substrate 100 having an insulating surface. An insulating film serving as a base film may be provided between the substrate 100 and the gate electrode 101. The base film can be formed to have a single layer or a stacked layer using one or more of insulating films which prevent diffusion of impurity elements from the substrate 100, specifically, a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, or a silicon

oxynitride film. The gate electrode 101 can be formed with a single layer or a stacked layer using one or more of conductive films using a metal material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, or an alloy material which includes any of these materials as a main component.

5 [0026]

For example, as a two-layer structure of the gate electrode 101, the following structures are preferable: a two-layer structure in which a molybdenum film is stacked over an aluminum film, a two-layer structure in which a molybdenum film is stacked over a copper film, a two-layer structure in which a titanium nitride film or a tantalum nitride film is stacked over a copper film, and a two-layer structure in which a titanium nitride film and a molybdenum film are stacked. Further, as a three-layer structure, it is preferable to stack a tungsten film or a tungsten nitride film, an alloy film of aluminum and silicon or an alloy film of aluminum and titanium, and a titanium nitride film or a titanium film.

10 [0027]

In this specification, oxynitride refers to a substance which includes more oxygen than nitrogen, and nitride oxide refers to a substance which includes more nitrogen than oxygen. For example, silicon oxynitride is a substance including oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from 50 atomic% to 70 atomic%, 0.5 atomic% to 15 atomic%, 25 atomic% to 35 atomic%, and 0.1 atomic% to 10 atomic%, respectively. Further, silicon nitride oxide is a substance which includes oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from 5 atomic% to 30 atomic%, 20 atomic% to 55 atomic%, 25 atomic% to 35 atomic%, and 10 atomic% to 30 atomic%, respectively. Note that the above concentration ranges are obtained when 20 measurements are performed using Rutherford backscattering spectrometry (RBS) or 25 hydrogen forward scattering (HFS). In addition, the total of the percentages of the hydrogen forward scattering (HFS). In addition, the total of the percentages of the constituent elements does not exceed 100 atomic%.

[0028]

Next, a gate insulating film 103 is formed over the gate electrode 101. The 30 gate insulating film 103 can be formed using a single layer or a stacked layer selected from a silicon oxide film, a silicon nitride film, a silicon oxynitride film, and a silicon

nitride oxide film by a plasma CVD method, a sputtering method, or the like. For example, a silicon oxynitride film may be formed using a deposition gas including silane (for example, monosilane), oxygen, and nitrogen by a plasma CVD method.

[0029]

5 Next, an oxide semiconductor film is formed over the gate insulating film 103. Note that before the oxide semiconductor film is formed by a sputtering method, dust attached to a surface of the gate insulating film 103 is preferably removed by reverse sputtering in which an argon gas is introduced and plasma is generated. The reverse sputtering refers to a method in which, without application of a voltage to a target side, 10 an RF power source is used for application of a voltage to a substrate side for formation of plasma in proximity to the substrate under an argon atmosphere to modify a surface. Note that instead of an argon atmosphere, a nitrogen atmosphere, a helium atmosphere, or the like may be used. Alternatively, an argon atmosphere to which oxygen, nitrous oxide, or the like is added may be used. Alternatively, an argon atmosphere to which 15 chlorine, carbon tetrafluoride, or the like is added may be used.

[0030]

An oxide semiconductor film for formation of a channel formation region can be formed using an oxide material having semiconductor characteristics, for example, an In-Ga-Zn-O-based non-single-crystal film. The oxide semiconductor film is formed 20 by a sputtering method with use of an In-Ga-Zn-O-based oxide semiconductor target. Moreover, the oxide semiconductor film can be formed by a sputtering method under a rare gas (for example, argon) atmosphere, an oxygen atmosphere, or an atmosphere including a rare gas (for example, argon) and oxygen.

[0031]

25 The gate insulating film 103 and the oxide semiconductor film may be formed successively without exposure to air. Successive film formation without exposure to air makes it possible to obtain each interface between stacked layers, which is not contaminated by atmospheric components or impurity elements floating in air, such as water, hydrocarbon, or the like. Therefore, variation in characteristics of the transistor 30 can be reduced.

[0032]

Next, the oxide semiconductor film is processed (patterned) into a desired

shape by etching or the like to form an island-shaped oxide semiconductor film 104 (a first oxide semiconductor film). Note that it is found that the oxide semiconductor film formed by sputtering or the like includes large amount of impurities such as moisture or hydrogen. Moisture and hydrogen easily form a donor level and thus serve 5 as impurities in the oxide semiconductor. Therefore, as illustrated in FIG. 1B, the island-shaped oxide semiconductor film 104 is irradiated with an electromagnetic wave such as a microwave or a high frequency under an inert gas (for example, nitrogen, helium, neon, or argon) atmosphere, an oxygen atmosphere, an ultra-dry air atmosphere, or reduced pressure to reduce impurities such as moisture or hydrogen which exists in 10 the oxide semiconductor film, so that a highly purified island-shaped oxide semiconductor film 105 (a second oxide semiconductor film) is formed. It is desirable that the content of water in the gas be 20 ppm or less, preferably 1 ppm or less, and more preferably 10 ppb or less.

[0033]

15 In the case where irradiation with a microwave is performed, the frequency of the microwave is greater than or equal 300 MHz and less than or equal to 3 THz, and preferably greater than or equal 300 MHz and less than or equal to 300 GHz. Further, in the case where irradiation with a high frequency is performed, the frequency of the high frequency is greater than or equal 1 MHz and less than or equal to 300 MHz, 20 preferably greater than or equal 4 MHz and less than or equal to 80 MHz. In particular, the microwave with a frequency of 915 MHz or 2.45 GHz which is generally used for an electromagnetic wave generator such as a microwave oven easily resonates with a polarized water molecule. Thus, the microwave with the above frequency has a high water loss coefficient and thus is useful for effective desorption of water in the 25 island-shaped oxide semiconductor film 104. For example, in the case of using an microwave with a frequency of 2.45 GHz, irradiation is performed for approximately five minutes under the condition of the output of 600 W. As a result, the highly purified island-shaped oxide semiconductor film 105 can be formed.

[0034]

30 The effect of using a microwave is that water is uniformly and rapidly heated with the use of the heating effect of the microwave, which causes a chemical reaction which is different from that in so-called general heating. The molecular motion which

occurs in a microwave region is a random motion in which molecules rotate and diffuse, which leads to heating effects. On the other hand, it is needless to say that there are also nonthermal effects. The dielectric relaxation characterizing water occurs at approximately 25 GHz. When the complex dielectric constant is  $\epsilon^* = \epsilon' - i\epsilon''$ , an 5 imaginary part  $\epsilon''$  is called dielectric loss. When irradiation with an electromagnetic wave with a frequency where the value of the imaginary part  $\epsilon''$  is not zero is performed, the electromagnetic wave is absorbed into a dielectric. The frequency of the microwave oven is 2.4 GHz which is smaller than that in the peak of the dielectric loss of water by approximately one digit. The peak of the dielectric loss of water expands 10 from several GHz or lower, which is lower part, to an ultraviolet region, which is higher part. Thus, the electromagnetic wave in this region is absorbed into water and the temperature of water can be increased. In the microwave oven, heating is performed by giving energy at the base of the lower value of the dielectric loss of water. It is known that water is represented by Debye relaxation. FIG. 23 shows an absorption 15 curve in the case of using Debye relaxation. In FIG. 23, the horizontal axis represents the logarithm of the frequency (f) of the electromagnetic wave, and the vertical axis represents the value obtained by multiplying a dielectric loss (an imaginary part  $\epsilon''$ ) by an angular frequency  $\omega$ . FIG. 24 shows a dielectric loss of a frequency of the corresponding electromagnetic wave. The value of the absorption curve with a 20 frequency in the peak of the dielectric loss is approximately half the maximum value. The absorption coefficient is saturated at the base of a loss spectrum on a high frequency side. It can be found that power with a frequency with which the absorption curve shown in FIG. 23 is somewhat large is preferably applied in consideration of effective heating.

25 [0035]

Irradiation with a microwave can be performed in a treatment chamber where an inner wall is formed using a metal which can reflect the microwave. In this case, the microwave is generated in the microwave generation unit using magnetron or the like and then introduced into the treatment chamber through a waveguide. After that, 30 the microwave is used for irradiation of an object to be processed. The microwave can be freely conveyed to the treatment chamber, like the case of light because the

wavelength of the microwave is shorter than that of a high frequency. The microwave which is not absorbed into the object to be processed and used for irradiation of the inner wall of the treatment chamber is diffusely reflected in the inner wall and thus likely to be absorbed into the object to be processed finally.

5 [0036]

Irradiation with a high frequency can be performed in such a manner that an object to be processed is provided between a pair of electrodes in a treatment chamber, and a high-frequency voltage is applied between the electrodes with the use of a high-frequency generation circuit.

10 [0037]

Note that it is preferable that water, hydrogen, or the like be not included in nitrogen or a rare gas such as helium, neon, or argon which is introduced into the treatment chamber. Specifically, nitrogen or a rare gas such as helium, neon, or argon which is introduced into the treatment chamber preferably has a purity of 6N (99.9999 %) or higher, more preferably 7N (99.99999 %) or higher (that is, the concentration of impurities is 1 ppm or lower, preferably 0.1 ppm or lower).

[0038]

Alternatively, irradiation with an electromagnetic wave may be performed in air where the dew point under an atmospheric pressure is -60 °C or lower and the moisture content is small, instead of an inert gas atmosphere such as a nitrogen atmosphere or a rare gas atmosphere.

[0039]

Desorption of moisture, hydrogen, or OH by irradiation with an electromagnetic wave such as a microwave or a high frequency is performed in such a manner that molecular association in water molecules included in an oxide semiconductor film, molecular association of hydrogen and an oxide semiconductor, molecular association of a hydroxyl group and an oxide semiconductor, or the like absorbs energy of the electromagnetic wave and vibrates to be cut. Therefore, the above molecular association can be cut more efficiently as compared to the case of performing external heating where heat is gradually conveyed from an outside of the oxide semiconductor film to an inside of the oxide semiconductor film through thermal

conductivity or the like. Thus, moisture, hydrogen, or OH can be desorbed from the oxide semiconductor film while increase in the temperature of the oxide semiconductor film is suppressed.

[0040]

5 In a transistor including the oxide semiconductor highly purified by desorption of moisture, hydrogen, OH, or the like as a channel formation region, deterioration in characteristics of the transistor due to impurities, for example, variation in the threshold voltage, can be suppressed, whereby high reliability can be obtained.

[0041]

10 Moreover, heat treatment may be performed on the island-shaped oxide semiconductor film 104 at the same time as irradiation with an electromagnetic wave. In the case where heat treatment is performed in combination with irradiation with an electromagnetic wave, the irradiation with an electromagnetic wave is desirably performed in such a manner that after the temperature of the island-shaped oxide 15 semiconductor film 104 is increased to a heat treatment temperature under an inert gas (for example, nitrogen, helium, neon, or argon) atmosphere, an oxygen atmosphere, an ultra-dry air atmosphere, or reduced pressure, and then the above irradiation with an electromagnetic wave is performed, and after that, the island-shaped oxide semiconductor film 104 is slowly cooled to a temperature ranging from higher than or 20 equal to room temperature and lower than 100 °C. In the case where heat treatment is performed under reduced pressure, the reduced pressure state is changed back to the atmospheric pressure state by supplying an inert gas after the heating, and then the island-shaped oxide semiconductor film 104 may be cooled under atmospheric pressure. It is desirable that the content of water in the gas be 20 ppm or less, preferably 1 ppm or 25 less, and more preferably 10 ppb or less.

[0042]

30 The heat treatment is performed at a temperature where a metal having a low melting point such as Zn included in the oxide semiconductor is evaporated as less as possible, for example, higher than or equal to 100 °C and lower than 350 °C, preferably higher than or equal to 150 °C and lower than 250 °C. When irradiation with an electromagnetic wave is performed at the same time as heat treatment, impurities such

as moisture included in the oxide semiconductor film can be reduced more effectively in a short time.

[0043]

Note that even when the oxide semiconductor film is irradiated with an electromagnetic wave at room temperature, a water molecule absorbs electromagnetic wave energy and vibrates. Thus, it can be expected that the temperature of the oxide semiconductor film becomes higher than room temperature as a result. When heat treatment is performed at the same time as irradiation with an electromagnetic wave, the temperature of the oxide semiconductor film is desirably controlled in consideration of the amount of increase in the temperature due to the irradiation with an electromagnetic wave.

[0044]

Further, in the heat treatment, a heating method using an electric furnace or an instantaneous heating method such as a gas rapid thermal anneal (GRTA) method using a heated gas or a lamp rapid thermal anneal (LRTA) method using lamp light can be used. For example, in the case of performing heat treatment using an electric furnace, the temperature rise characteristics is preferably set at higher than or equal to 0.1 °C/min and lower than or equal to 20 °C/min and the temperature drop characteristics is preferably set at higher than or equal to 0.1 °C/min and lower than or equal to 15 °C/min.

[0045]

The island-shaped oxide semiconductor film 105 after the heat treatment is preferably in an amorphous state, but may be partly crystallized.

[0046]

Note that after the irradiation with an electromagnetic wave is performed on the oxide semiconductor film, heat treatment is performed on the oxide semiconductor film under an oxygen atmosphere, whereby impurities such as water included in the oxide semiconductor film can be removed. In addition, the heat treatment is performed under an oxygen atmosphere in order that the oxide semiconductor film may include excessive oxygen, whereby resistance thereof can be increased. The heat treatment is performed at a temperature where a metal having a low melting point such as Zn

included in the oxide semiconductor is evaporated as less as possible, for example, higher than or equal to 100 °C and lower than 350 °C, preferably higher than or equal to 150 °C and lower than 250 °C. It is preferable that an oxygen gas used for the heat treatment under an oxygen atmosphere do not include water, hydrogen, or the like.

5 Alternatively, an oxygen gas which is introduced into a heat treatment apparatus preferably has a purity of 6N (99.9999 %) or higher, more preferably 7N (99.99999 %) or higher (that is, the concentration of impurities in oxygen is 1 ppm or lower, preferably 0.1 ppm or lower).

[0047]

10 Next, a conductive film is formed over the gate insulating film 103 and the island-shaped oxide semiconductor film 105. The conductive film is formed using a material such as an element selected from aluminum, chromium, tantalum, titanium, manganese, magnesium, molybdenum, tungsten, zirconium, beryllium, and thorium; an alloy including one or more of these elements as a component; or the like.

15 [0048]

Note that in the case where heat treatment is performed after the formation of the conductive film, the conductive film preferably has heat resistance enough to withstand the heat treatment. In the case of performing heat treatment after the formation of the conductive film, the conductive film is formed using the low-resistant conductive material in combination with aluminum because aluminum alone has problems of low heat resistance, being easily corroded, and the like. As the low-resistant conductive material which is combined with aluminum, the following material is preferably used: an element selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, or scandium; an alloy including one or more of these elements as a component; a nitride including any of these elements as a component; or the like.

[0049]

30 Next, as illustrated in FIG. 1C, the conductive film is processed (patterned) into a desired shape by etching or the like, thereby forming a source electrode 106 and a drain electrode 107. Note that in the patterning, the source electrode 106 and the drain electrode 107 are formed, so that part of the exposed portion of the island-shaped oxide

semiconductor film is etched, whereby an island-shaped oxide semiconductor film 108 having a groove (a recessed portion) is formed.

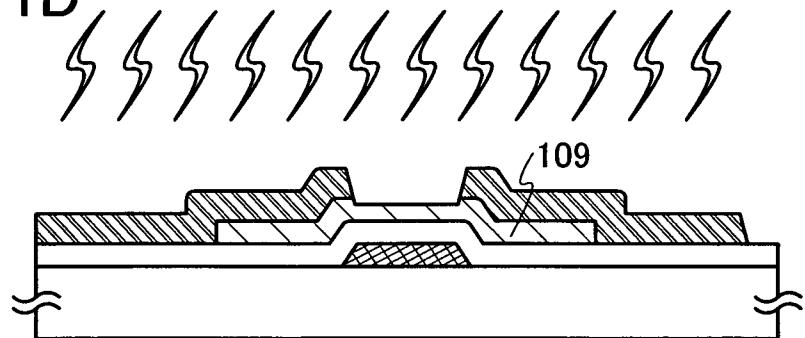

[0050]

Then, as illustrated in FIG. 1D, the island-shaped oxide semiconductor film 108 is irradiated with an electromagnetic wave such as a microwave or a high frequency under an inert gas (for example, nitrogen, helium, neon, or argon) atmosphere, an oxygen atmosphere, an ultra-dry air atmosphere, or reduced pressure, whereby a highly purified island-shaped oxide semiconductor film 109 is formed. It is desirable that the content of water in the gas be 20 ppm or less, preferably 1 ppm or less, and more preferably 10 ppb or less. The description of the irradiation with an electromagnetic wave such as a microwave or a high frequency, which is performed on the island-shaped oxide semiconductor film 104, can be referred to for implementation of the irradiation with an electromagnetic wave such as a microwave or a high frequency, which is performed on the island-shaped oxide semiconductor film 108 and the heat treatment performed in combination with the irradiation with an electromagnetic wave.

[0051]

According to an embodiment of the present invention, even when high-temperature heat treatment using irradiation with an electromagnetic wave is not performed, desorption of impurities such as water, hydrogen, or OH in an oxide semiconductor can be performed at a lower temperature in a shorter time. Therefore, a metal included in the source electrode 106 and the drain electrode 107 can be prevented from entering the island-shaped oxide semiconductor film 108 through heat treatment for desorption of impurities such as water, hydrogen, or OH, and deterioration in characteristics of the transistor, for example, off-state current can be prevented.

[0052]

Moreover, in this embodiment, the island-shaped oxide semiconductor film 104 formed by patterning is irradiated with an electromagnetic wave. In addition, the island-shaped oxide semiconductor film 108 formed at the same time as the source electrode 106 and the drain electrode 107 are irradiated with an electromagnetic wave again. However, irradiation with an electromagnetic wave does not always need to be performed twice. Irradiation with an electromagnetic wave may be performed on either one of the island-shaped oxide semiconductor film 104 formed by patterning or

the island-shaped oxide semiconductor film 108 formed at the same time as the source electrode 106 and the drain electrode 107. Alternatively, instead of the irradiation with an electromagnetic wave performed on the island-shaped oxide semiconductor film 104 formed by patterning, which is one of the two irradiation treatments with an electromagnetic wave, irradiation with an electromagnetic wave may be performed on the oxide semiconductor film before the formation of the island-shaped oxide semiconductor film 104 by patterning. Still alternatively, in addition to the two irradiation treatments with an electromagnetic wave, irradiation with an electromagnetic wave may be performed on the oxide semiconductor film before the formation of the island-shaped oxide semiconductor film 104 by patterning. Further still alternatively, irradiation with an electromagnetic wave may be performed only on the oxide semiconductor film before the formation of the island-shaped oxide semiconductor film 104 by patterning.

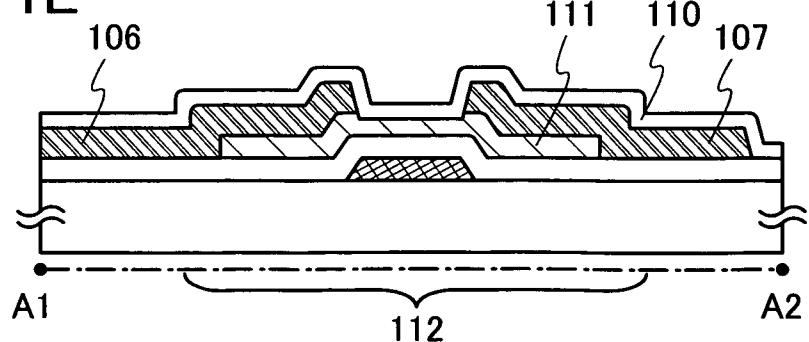

[0053]

Next, as illustrated in FIG. 1E, an oxide insulating film 110 is formed in contact with the island-shaped oxide semiconductor film 109 by a sputtering method. The oxide insulating film 110 is formed in contact with the highly purified island-shaped oxide semiconductor film 109 and formed using an inorganic insulating film which includes impurities such as moisture, hydrogen, and OH as little as possible and blocks entry of these impurities from the outside, specifically, a silicon oxide film, a silicon nitride oxide film, or the like.

[0054]

In this embodiment, a 300-nm-thick silicon oxide film is formed as the oxide insulating film 110. The substrate temperature in the film formation may be higher than or equal to room temperature and lower than or equal to 300 °C, and is set at 100 °C in this embodiment. Formation of the silicon oxide film with a sputtering method can be performed under a rare gas (for example, argon) atmosphere, an oxygen atmosphere, or an atmosphere including a rare gas (for example, argon) and oxygen. Further, either a silicon oxide target or a silicon target may be used as a target. For example, the silicon oxide film can be formed by a sputtering method using a silicon target under an atmosphere including oxygen and nitrogen.

## [0055]

When the oxide insulating film 110 is formed in contact with the highly purified oxide semiconductor film 105 by a sputtering method, a PCVD method, or the like, oxygen is supplied to the oxide semiconductor film 105 even if oxygen vacancy 5 occurs in the oxide semiconductor film 105 due to irradiation with an electromagnetic wave or heat treatment performed at the same time as the irradiation with an electromagnetic wave. Therefore, a vacancy of oxygen serving as a donor can be reduced in part of the oxide semiconductor film 105, which is in contact with the oxide insulating film 110, and thus the stoichiometric proportion can be satisfied. As a result, 10 the oxide semiconductor film 105 can be made to be an intrinsic semiconductor film or a substantially intrinsic semiconductor film, so that an oxide semiconductor film 111 (a third oxide semiconductor film) can be formed. Accordingly, electric characteristics of the transistor can be improved and variation in the electric characteristics thereof can be reduced.

## 15 [0056]

FIG. 2 is a top view of a transistor 112 manufactured in this embodiment. FIG. 1E is a cross-sectional view taken along dashed line A1–A2 in FIG. 2. The transistor 112 includes the gate electrode 101, the gate insulating film 103 over the gate electrode 101, the oxide semiconductor film 111 over the gate insulating film 103, and the source 20 electrode 106 and the drain electrode 107 over the oxide semiconductor film 111.

## [0057]

Further, after the oxide insulating film 110 is formed, the transistor 112 may be subjected to heat treatment (preferably at higher than or equal to 150 °C and lower than 350 °C) under a nitrogen atmosphere or an air atmosphere (in air). For example, heat 25 treatment is performed at 250 °C for one hour under a nitrogen atmosphere. By the heat treatment, the oxide semiconductor film 105 is heated while being in contact with the oxide insulating film 110. Accordingly, variation in electric characteristics of the transistor 112 can be reduced. There is no particular limitation on when to perform this heat treatment (preferably at higher than or equal to 150 °C and lower than 350 °C) 30 as long as it is performed after the formation of the oxide insulating film 110. When this heat treatment also serves as heat treatment in another step, for example, heat

treatment in formation of a resin film or heat treatment for reducing resistance of a transparent conductive film, the number of steps can be prevented from increasing.

[0058]

Note that a step of forming the island-shaped oxide semiconductor film 109 by 5 irradiating the island-shaped oxide semiconductor film 108 with an electromagnetic wave after forming the source electrode 106 and the drain electrode 107 and a step of forming the oxide insulating film 110 in contact with the oxide semiconductor film 109 are successively performed (also referred to as successive treatment or an insitu process) without exposure to air, whereby impurities such as moisture, hydrogen, or OH included 10 in the oxide semiconductor film 111 which is finally formed can be further reduced. As a result, reliability of the transistor 112 can be more improved.

[0059]

Note that in the manufacturing process, a step of forming the island-shaped oxide semiconductor film 109 by irradiating the island-shaped oxide semiconductor film 108 with an electromagnetic wave, a step of forming the oxide insulating film 110, a substrate transfer step, an alignment step, a heating or slow-cooling step, or the like 15 may be included. Such a process is also within the scope of the successive processing in this specification. However, the following case is not within the scope of the successive treatment in this specification: there is a step in which liquid is used, such as 20 a cleaning step, a wet etching step, or a resist formation step between the above two steps.

[0060]

The successive treatment can be performed by, for example, a microwave plasma CVD apparatus. FIG. 22 is a cross-sectional view illustrating a structure of a 25 reaction chamber of a microwave plasma CVD apparatus. The reaction chamber of the microwave plasma CVD apparatus includes a treatment container 180, a support 181 which is provided in the treatment container 180 and on which the substrate 100 is disposed, a gas supply unit 182 for introducing a gas into the treatment container 180, an exhaust port 183 which is connected to a vacuum pump for exhausting a gas in the 30 treatment container 180, a microwave generation unit 184 for supplying microwaves for generating plasma, a waveguide 185 for introducing the microwaves from the microwave generation unit 184 into the treatment container 180, a top plate 187 which

is in contact with the waveguide 185 and has an opening 187a, and a plurality of dielectric plates 186 fixed to the top plate 187 with a fixing member 188.

[0061]

Moreover, a gas pipe 197 through which a non-source gas flows and a gas pipe 198 through which a source gas flows are provided between the substrate 100 and the dielectric plate 186. The gas pipes 197 and 198 are connected to the gas supply unit 182. Specifically, the gas pipe 197 through which a non-source gas flows is connected to a non-source gas supply source 191 via a valve 195 and a mass flow controller 193. Further, the gas pipe 198 through which a source gas flows is connected to a non-source gas supply source 192 via a valve 196 and a mass flow controller 194. By provision of a temperature controller 199 for the support 181, the temperature of the substrate 100 can be controlled. A high-frequency power source may be connected to the support 181, so that predetermined bias voltage may be applied to the support 181 by high-frequency voltage output from the high-frequency power source. Note that the gas supply unit 182 and the microwave generation unit 184 are provided outside the reaction chamber.

[0062]

The microwave generation unit 184 can supply microwaves with a frequency of 1 GHz, 2.45 GHz, or 8.3 GHz. By provision of the plurality of microwave generation units 184, irradiation with a microwave can be uniformly performed on a large-sized substrate with one side of over 1000 mm, and the highly uniform oxide insulating film 110 can be formed by a plasma CVD method at a high film-formation rate.

[0063]

The treatment container 180 and the top plate 187 are formed of a metal whose surface is covered with an insulating film such as alumina, silicon oxide, or a fluorine resin, for example, an alloy including aluminum. In addition, the fixing member 188 is formed using a metal such as an alloy including aluminum.

[0064]

The dielectric plate 186 is provided so as to be in close contact with the opening of the top plate 187. The microwaves generated in the microwave generation unit 184 are propagated to the dielectric plate 186 by passing through the waveguide

185 and the opening of the top plate 187 and transmitted through the dielectric plate 186 to be released into the treatment container 180.

[0065]

The dielectric plate 186 is formed using ceramics such as sapphire, quartz glass, 5 alumina, silicon oxide, or silicon nitride. The dielectric plate 186 may have a recessed portion on the side where a plasma 700 is generated. By the recessed portion, stable plasma can be generated. Irradiation with a microwave can be uniformly performed on a large-sized substrate with one side of over 1000 mm, and the highly uniform oxide insulating film 110 can be formed by a plasma CVD method at a high film-formation 10 rate.

[0066]

The gas pipe 197 through which a non-source gas flows and the gas pipe 198 through which a source gas flows are provided to intersect with each other. A nozzle of the gas pipe 197 through which a non-source gas flows is provided on the dielectric 15 plate 186 side, and a nozzle of the gas pipe 198 through which a source gas flows is provided on the substrate 100 side. By release of the non-source gas to the dielectric plate 186 side, a plasma 170 can be generated while formation of the film on the surface of the dielectric plate 186 is prevented. Further, the source gas can be released at a position which is closer to the substrate 100, and a deposition rate can be increased. 20 The gas pipes 197 and 198 are formed using ceramics such as alumina or aluminum nitride. Transmissivity of the microwaves is high in the ceramics; therefore, when the gas pipes 197 and 198 are formed using ceramics, distribution of the plasma can be uniform without an electric field being disturbed, even when the gas pipe is provided right under the dielectric plate 186.

25 [0067]

In the case where irradiation with a microwave is performed using a microwave plasma CVD apparatus, after the inside of the treatment container 180 is made into a vacuum state, an inert gas such as nitrogen, helium, neon, or argon is introduced into the treatment container 180 from the non-source gas supply source 191. In the case where 30 heat treatment is performed at the same time as the irradiation with a microwave, the temperature of the support 181 is controlled by the temperature controller 199 such that the temperature of the substrate 100 reaches to a predetermined temperature before the

irradiation with a microwave. Note that by field effect energy of the microwaves released into the treatment container 180, the non-source gas is made into a plasma state. The plasma 170 has higher density on the surface of the dielectric plate 186; thus, damage to the substrate 100 can be reduced.

5 [0068]

After the irradiation with a microwave, first, the temperature of the substrate 100 is controlled in order to form the oxide insulating film 110 using silicon oxide. The substrate 100 is at room temperature or heated by the temperature controller 199 to 100 °C to 350 °C. Then, the inside of the treatment container 180 is made into a 10 vacuum state, and one or more rare gases such as helium, argon, neon, xenon, and krypton, and an oxygen gas are introduced into the treatment container 180 in order to generate plasma. By introducing the oxygen gas together with the rare gas into the treatment container 180, plasma ignition can be facilitated.

[0069]

15 Note that in the case where, at a step of irradiation with a microwave, helium, neon, or argon is already introduced into the treatment container 180, a gas in the treatment container 180 does not need to be changed in the formation of the oxide insulating film 110. Further, in the case where the irradiation with a microwave is performed at the same time as heat treatment, the temperature of the substrate 100 is not 20 necessarily reduced after the heat treatment, and then a step of forming the oxide insulating film 110 may be performed.

[0070]

25 The distance between the substrate 100 and the dielectric plate 186 is approximately 10 mm to 80 mm (preferably, 10 mm to 30 mm). The pressure in the treatment container 180 is set at predetermined pressure, 1 Pa to 200 Pa, preferably 1 Pa to 100 Pa. Then, the microwave generation unit 184 is turned on, and the microwaves are supplied from the microwave generation unit 184 to the waveguide 185, so that the plasma is generated in the treatment container 180. The output power of the microwave generation unit is set at 500 W to 6000 W, preferably 4000 W to 6000 W. 30 By excitation of plasma by introducing the microwaves, plasma with low electron temperature (greater than or equal to 0.7 eV and less than or equal to 3 eV, preferably greater than or equal to 0.7 eV and less than or equal to 1.5 eV) and high electron

density ( $1 \times 10^{11} \text{ cm}^{-3}$  to  $1 \times 10^{13} \text{ cm}^{-3}$ ) can be generated. Next, a source gas is introduced from the gas pipe 198 into the treatment container 180. Specifically, supply of the oxygen gas is halted, and silane and oxygen are introduced as a source gas, whereby the oxide insulating film 110 including silicon oxide can be formed over the 5 substrate 100. Then, supply of the source gas is halted, the pressure in the treatment container 180 is lowered, and the microwave generation unit 184 is turned off.

[0071]

Although FIG. 22 illustrates an example of a reaction chamber of a microwave plasma CVD apparatus, the microwave plasma CVD apparatus may include a plurality 10 of reaction chambers, and the plurality of reaction chambers may be directly connected to each other or may be to a common chamber.

[0072]

(Embodiment 2)

In this embodiment, a method for manufacturing a semiconductor device 15 including a transistor of which structure is different from that of the transistor 112 described in Embodiment 1 is described. Note that the same portions as Embodiment 1 or portions having functions similar to those of Embodiment 1 can be formed in a manner similar to that of Embodiment 1, and also the same steps as Embodiment 1 or the steps similar to those of Embodiment 1 can be performed in a manner similar to 20 those of Embodiment 1; therefore, and repetitive description thereof is omitted.

[0073]

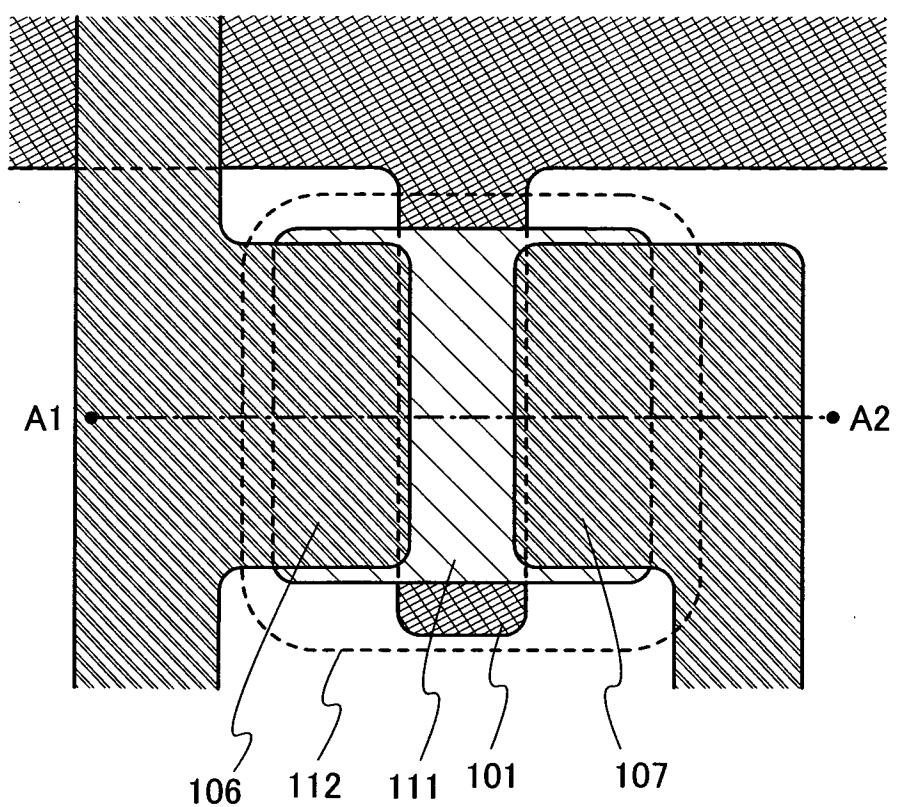

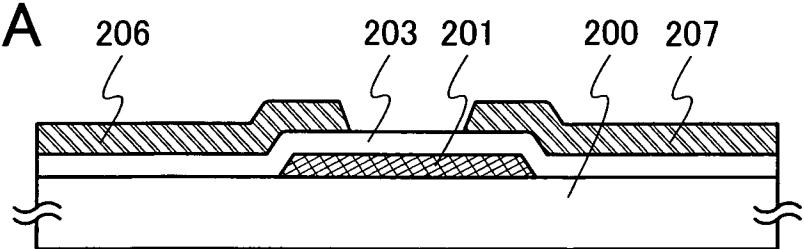

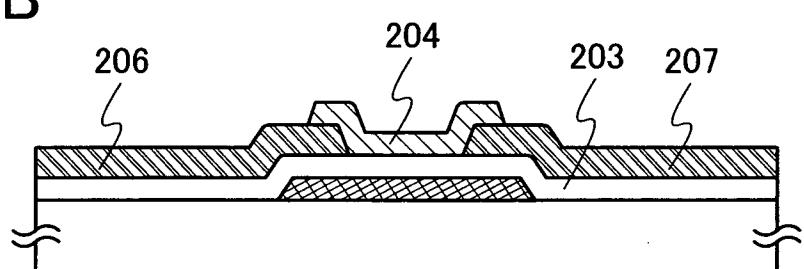

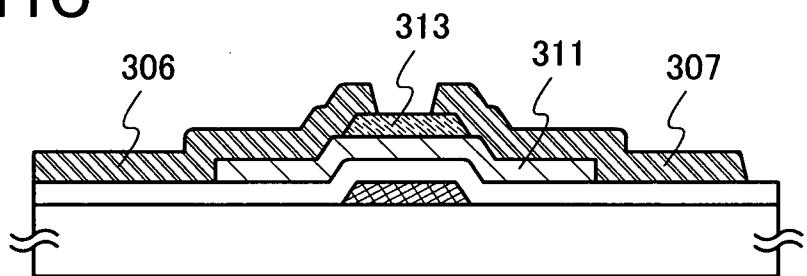

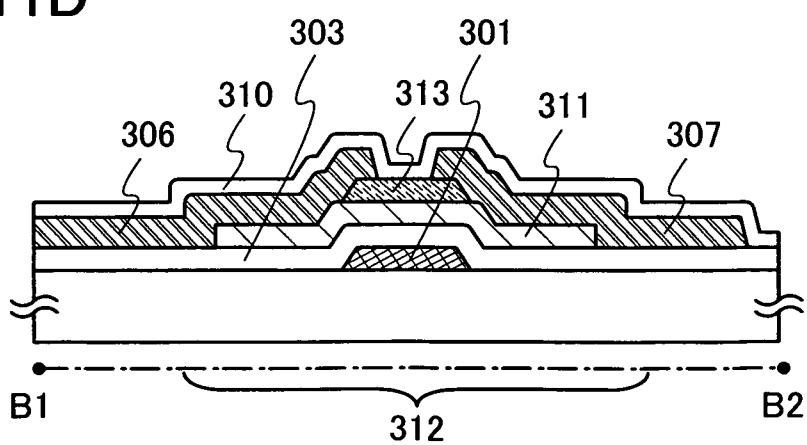

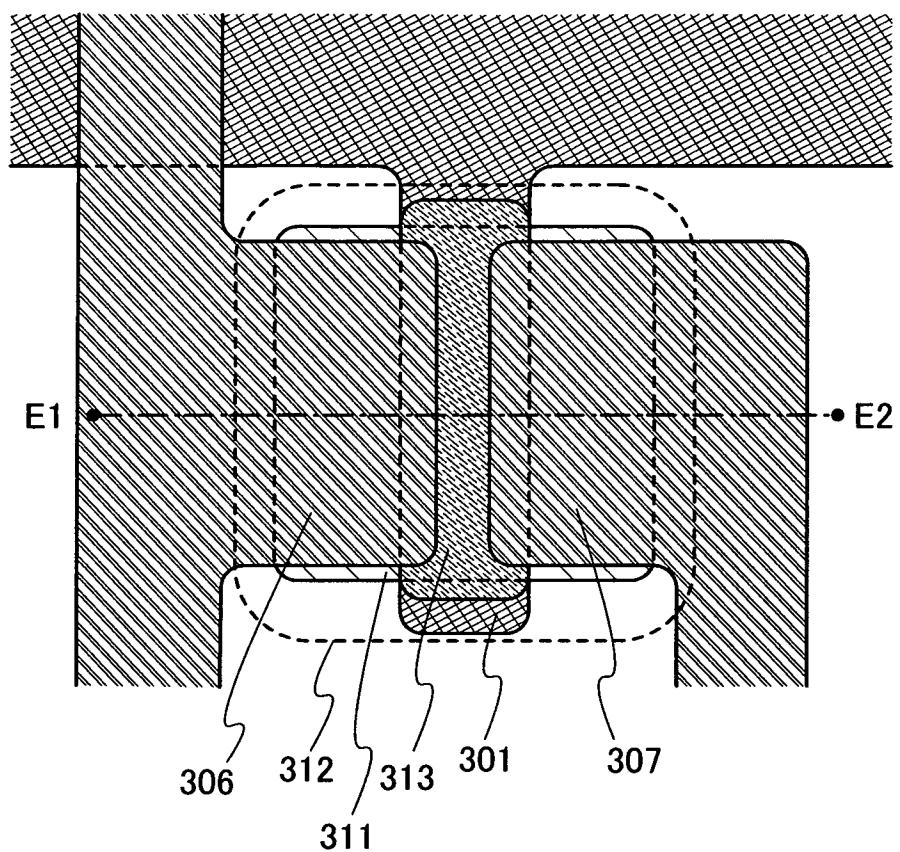

A method for manufacturing a semiconductor device is described with reference to FIGS. 3A to 3D and FIG. 4.

[0074]

As illustrated in FIG. 3A, a gate electrode 201 is provided over a substrate 200 25 having an insulating surface. An insulating film serving as a base film may be provided between the substrate 200 and the gate electrode 201. The descriptions of the material and the structure of the gate electrode 101 in Embodiment 1 may be referred to for details of the material and the structure of the gate electrode 201. The base film 30 has a function of preventing diffusion of an impurity element from the substrate 200, and can be formed to have a single layer or stacked layer using one or more films selected from a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and

a silicon oxynitride film.

[0075]

Next, a gate insulating film 203 is formed over the gate electrode 201. The gate insulating film 203 can be formed to have a single layer or stacked layer using one or more films selected from a silicon oxide film, a silicon nitride film, a silicon oxynitride film, and a silicon nitride oxide film by a plasma CVD method, a sputtering method, or the like. For example, a silicon oxynitride film may be formed using a deposition gas including silane (for example, monosilane), oxygen, and nitrogen by a plasma CVD method

10 [0076]

Next, a conductive film is formed over the gate insulating film 203. Then, the conductive film is processed (patterned) into a desired shape by etching or the like, so that a source electrode 206 and a drain electrode 207 are formed. The description of the material of the conductive film patterned in the formation of the source electrode 106 and the drain electrode 107 in Embodiment 1 may be referred to for details of the material of the conductive film.

[0077]

Next, an oxide semiconductor film is formed over the source electrode 206 and the drain electrode 207 and the gate insulating film 203. Then, as illustrated in FIG. 20 3B, the oxide semiconductor film is processed (patterned) into a desired shape by etching or the like, so that an island-shaped oxide semiconductor film 204 (a first oxide semiconductor film) is formed.

[0078]

An oxide semiconductor film for forming a channel formation region may be formed using an oxide material having semiconductor characteristics described in Embodiment 1. The oxide semiconductor film can be formed by a sputtering method under a rare gas (for example, argon) atmosphere, an oxygen atmosphere, or an atmosphere including a rare gas (for example, argon) and oxygen. Note that before the oxide semiconductor film is formed by a sputtering method, dust attached to a surface 30 of the gate insulating film 203 is preferably removed by reverse sputtering in which an argon gas is introduced and plasma is generated.

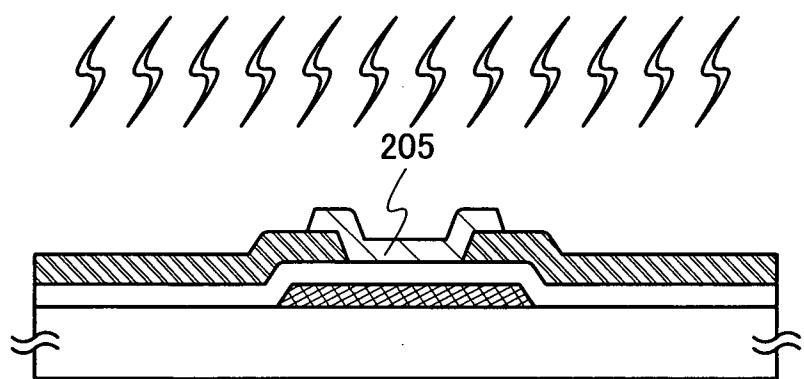

[0079]

Next, as illustrated in FIG. 3C, the island-shaped oxide semiconductor film 204 is irradiated with an electromagnetic wave such as a microwave or a high frequency under an inert gas (for example, nitrogen, helium, neon, or argon) atmosphere, an oxygen atmosphere, an ultra-dry air atmosphere, or reduced pressure, so that moisture, 5 hydrogen, or OH is desorbed. Thus, a highly purified island-shaped oxide semiconductor film 205 (a second oxide semiconductor film) is formed. It is desirable that the content of water in the gas be 20 ppm or less, preferably 1 ppm or less, and more preferably 10 ppb or less. Heat treatment may be performed on the island-shaped oxide semiconductor film 204 at the same time as the irradiation with an 10 electromagnetic wave.

[0080]

The descriptions of the irradiation with an electromagnetic wave and heat treatment performed on the oxide semiconductor film 104 in Embodiment 1 may be referred to for details of the irradiation with an electromagnetic wave and heat treatment 15 performed on the oxide semiconductor film 204.

[0081]

In a transistor including the oxide semiconductor highly purified by desorption of moisture, hydrogen, OH, or the like as a channel formation region, deterioration in characteristics of the transistor due to impurities, for example, variation in the threshold 20 voltage, can be suppressed, whereby high reliability can be obtained.

[0082]

In addition, according to an embodiment of the present invention, even when high-temperature heat treatment using irradiation with an electromagnetic wave is not performed, desorption of impurities such as water, hydrogen, or OH in an oxide 25 semiconductor can be performed at a lower temperature in a shorter time. Therefore, a metal included in the source electrode 206 and the drain electrode 207 can be prevented from entering the island-shaped oxide semiconductor film 205 through heat treatment for desorption of impurities such as water, hydrogen, or OH, and deterioration in characteristics of the transistor, for example, off-state current can be prevented.

[0083]

Moreover, although the irradiation with an electromagnetic wave is performed on the island-shaped oxide semiconductor film 204 formed by patterning in this

embodiment, irradiation with an electromagnetic wave may be performed on the oxide semiconductor film not after patterning but before patterning. Alternatively, irradiation with an electromagnetic wave may be performed both before and after patterning.

5 [0084]

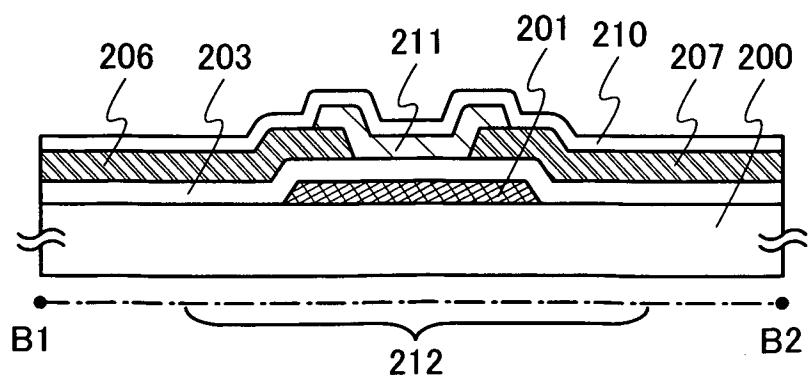

Next, as illustrated in FIG. 3D, an oxide insulating film 210 is formed in contact with the island-shaped oxide semiconductor film 205 by a sputtering method. The oxide insulating film 210 is formed in contact with the highly purified island-shaped oxide semiconductor film 205 and formed using an inorganic insulating film which includes impurities such as moisture, hydrogen, and OH as little as possible and blocks entry of these impurities from the outside, specifically, a silicon oxide film, a silicon nitride oxide film, or the like.

[0085]

In this embodiment, a 300-nm-thick silicon oxide film is formed as the oxide insulating film 210. The substrate temperature in the film formation may be higher than or equal to room temperature and lower than or equal to 300 °C, and is set at 100 °C in this embodiment. When the oxide insulating film 210 is formed in contact with the highly purified island-shaped oxide semiconductor film 205 by a sputtering method, a PCVD method, or the like, oxygen is supplied to the oxide semiconductor film 205 even when an oxygen vacancy occurs in the oxide semiconductor film 205 due to irradiation with an electromagnetic wave or heat treatment performed at the same time as the irradiation with an electromagnetic wave. Therefore, a vacancy of oxygen serving as a donor can be reduced in part of the oxide semiconductor film 205, which is in contact with the oxide insulating film 210, and thus the stoichiometric proportion can be satisfied. As a result, the oxide semiconductor film 205 can be made to be an intrinsic semiconductor film or a substantially intrinsic semiconductor film, so that an oxide semiconductor film 211 (a third oxide semiconductor film) can be formed. Accordingly, electric characteristics of the transistor can be improved and variation in the electric characteristics thereof can be reduced.

30 [0086]

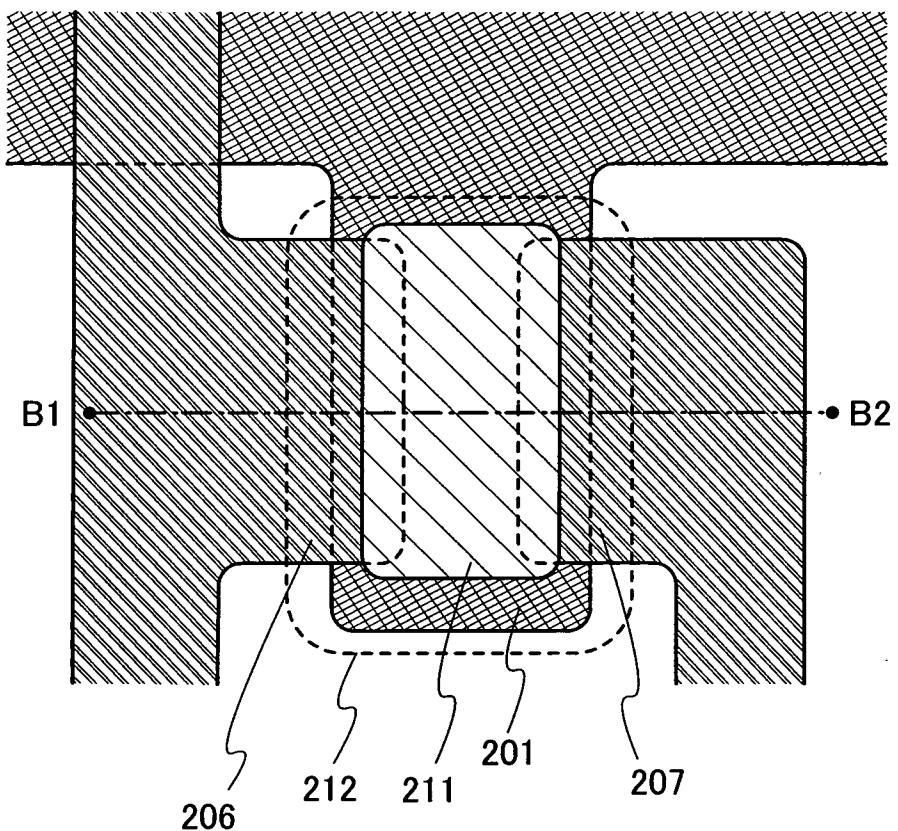

FIG. 4 is a top view of a transistor 212 manufactured in this embodiment. FIG.

3D is a cross-sectional view taken along dashed line B1– B1 in FIG. 4. The transistor 212 includes the gate electrode 201, the gate insulating film 203 over the gate electrode 201, the source electrode 206 and the drain electrode 207 over the gate insulating film 203, and the oxide semiconductor film 211 over the gate insulating film 203, and the 5 source electrode 206 and the drain electrode 207.

[0087]

Further, after the formation of the oxide insulating film 210, heat treatment may be performed on the transistor 212 under a nitrogen atmosphere or an air atmosphere (in air) (preferably at a temperature higher than or equal to 150 °C and 10 lower than 350 °C). For example, heat treatment is performed under a nitrogen atmosphere at 250 °C for one hour. In such heat treatment, the oxide semiconductor film 205 in a condition being in contact with the oxide insulating film 210 is heated; thus, variation in electric characteristics of the transistor 212 can be reduced. There is no particular limitation on when to perform this heat treatment (preferably at higher 15 than or equal to 150 °C and lower than 350 °C) as long as it is performed after the formation of the oxide insulating film 210. When this heat treatment also serves as heat treatment in another step, for example, heat treatment in formation of a resin film or heat treatment for reducing resistance of a transparent conductive film, the number of steps can be prevented from increasing.

20 [0088].

Note that a step of forming the island-shaped oxide semiconductor film 205 by irradiating the island-shaped oxide semiconductor film 204 with an electromagnetic wave after forming the source electrode 206 and the drain electrode 207 and a step of forming the oxide insulating film 210 in contact with the oxide semiconductor film 205 25 are successively performed (also referred to as successive treatment or an insitu process) without exposure to air, whereby impurities such as moisture, hydrogen, or OH included in the oxide semiconductor film 205 which is finally formed can be further reduced. As a result, reliability of the transistor 212 can be more improved.

[0089]

30 This embodiment can be freely combined with any of the other embodiments.

[0090]

## (Embodiment 3)

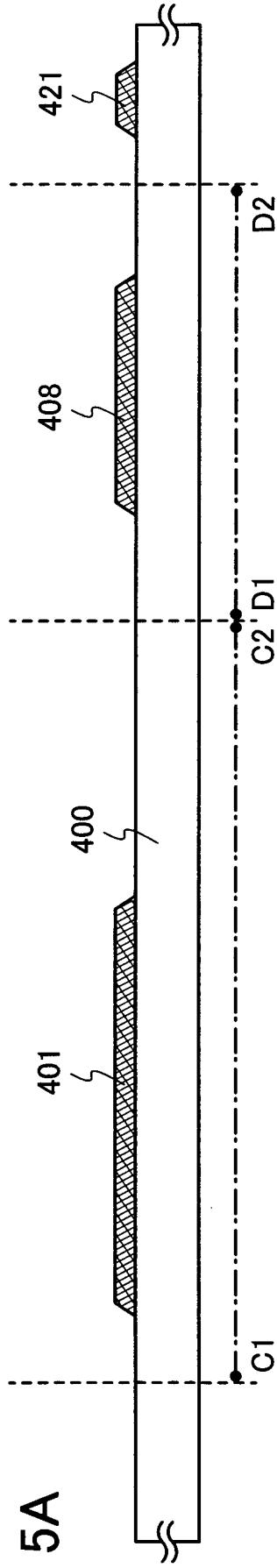

A method for manufacturing a semiconductor device including a transistor is described with reference to FIGS. 5A to 5C, FIGS. 6A to 6C, FIGS. 7A to 7C, FIG. 8, FIG. 9, and FIG. 10.

5 [0091]

In FIG. 5A, as a substrate 400 having a light-transmitting property, a glass substrate of barium borosilicate glass, aluminoborosilicate glass, or the like typified by 7059 glass, 1737 glass, or the like manufactured by Corning Incorporated can be used.

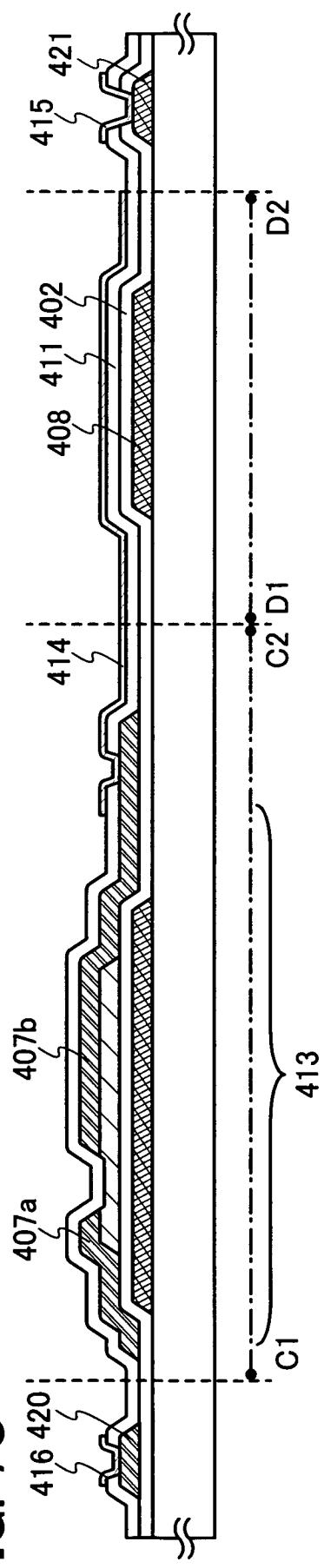

[0092]

10 Next, a conductive layer is formed entirely over a surface of the substrate 400, and then a first photolithography step is performed in such a manner that a resist mask is formed and unnecessary portions are removed by etching, so that wirings and an electrode (a gate wiring including a gate electrode 401, a capacitor wiring 408, and a first terminal 421) are formed. At this time, the etching is performed so that at least 15 end portions of the gate electrode 401 are tapered.

[0093]

20 Each of the gate wiring including the gate electrode 401, the capacitor wiring 408, and the first terminal 421 in a terminal portion is preferably formed using a heat-resistant conductive material such as an element selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, and scandium; an alloy including any 25 of these elements as a component; an alloy film including a combination of any of the above elements; or a nitride including any of the above elements as a component.

[0094]

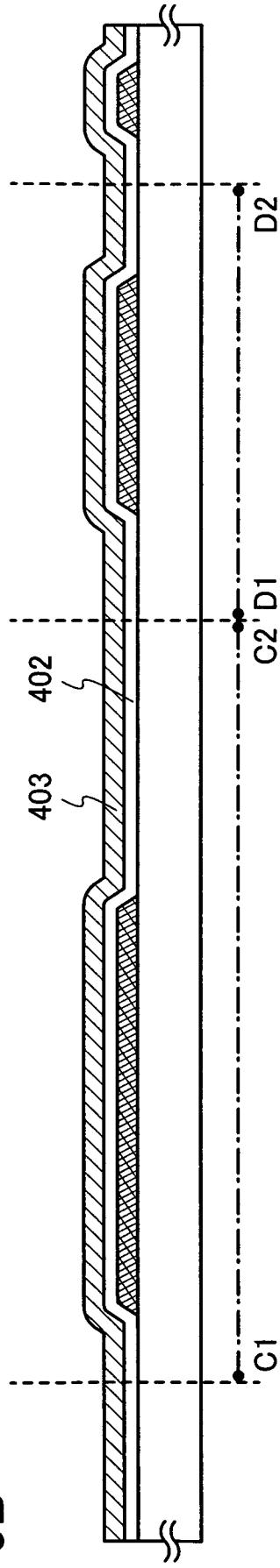

25 Next, a gate insulating film 402 is formed entirely over surfaces of the gate electrode 401, the capacitor wiring 408, the first terminal 421 as illustrated in FIG. 5B. The gate insulating film 402 is formed to a thickness of 50 nm to 250 nm by a sputtering method, a PCVD method, or the like.

[0095]

30 For example, as the gate insulating film 402, a silicon oxide film is formed to a thickness of 100 nm by a sputtering method. Needless to say, the gate insulating film 402 is not limited to such a silicon oxide film and may be formed to have a single-layer structure or a stacked-layer structure using another insulating film such as a silicon

oxynitride film, a silicon nitride film, an aluminum oxide film, or a tantalum oxide film.

[0096]

Next, an oxide semiconductor film 403 (an In-Ga-Zn-O-based non-single-crystal film) is formed over the gate insulating film 402. The oxide semiconductor film 403 is formed without exposure to air after plasma treatment, which is advantageous in that dust or moisture is not attached to an interface between the gate insulating film 402 and the oxide semiconductor film 403. Here, the oxide semiconductor film 403 is formed under an oxygen atmosphere, an argon atmosphere, or an atmosphere including argon and oxygen using an oxide semiconductor target 10 having a diameter of 8 inches and including In, Ga, and Zn (an In-Ga-Zn-O-based oxide semiconductor target ( $In_2O_3 : Ga_2O_3 : ZnO = 1:1:1$ )), with the distance between the substrate 400 and the target set to 170 mm, under a pressure of 0.4 Pa, and with a direct current (DC) power source of 0.5 kW. Note that a pulse direct current (DC) power source is preferable because dust can be reduced and the film thickness can be uniform. 15 The thickness of the In-Ga-Zn-O-based non-single-crystal film is set to 5 nm to 200 nm. In this embodiment, for example, as the oxide semiconductor film 403, an In-Ga-Zn-O-based non-single-crystal film is formed to a thickness of 50 nm by a sputtering method using an In-Ga-Zn-O-based oxide semiconductor target.

[0097]

20 Examples of a sputtering method include an RF sputtering method in which a high-frequency power source is used as a sputtering power source, a DC sputtering method, and a pulsed DC sputtering method in which a bias is applied in a pulsed manner. An RF sputtering method is mainly used in the case where an insulating film is formed, and a DC sputtering method is mainly used in the case where a metal film is 25 formed.

[0098]

In addition, there is also a multi-source sputtering apparatus in which a plurality of targets of different materials can be set. With the multi-source sputtering apparatus, films of different materials can be formed to be stacked in the same chamber, 30 or a film of plural kinds of materials can be formed by electric discharge at the same time in the same chamber.

[0099]

In addition, there are a sputtering apparatus provided with a magnet system inside the chamber and used for a magnetron sputtering method, and a sputtering apparatus used for an ECR sputtering method in which plasma generated with the use of microwaves is used without using glow discharge.

5 [0100]

Furthermore, as a film formation method with a sputtering method, there are also a reactive sputtering method in which a target substance and a sputtering gas component are chemically reacted with each other during film formation to form a thin compound film thereof, and a bias sputtering method in which voltage is also applied to 10 a substrate during film formation.

[0101]

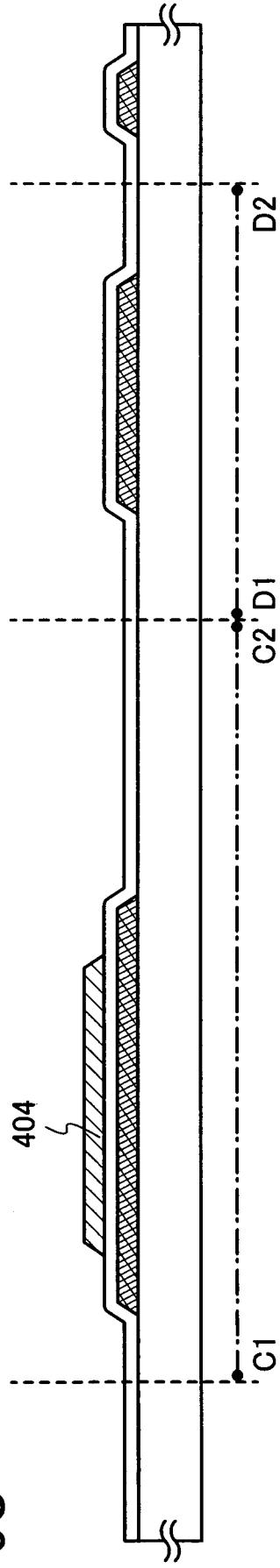

Next, as illustrated in FIG. 5C, a second photolithography step is performed in such a manner that a resist mask is formed and the oxide semiconductor film 403 is etched. For example, unnecessary portions are removed by wet etching using a mixed 15 solution of phosphoric acid, acetic acid, and nitric acid, so that an island-shaped oxide semiconductor film 404 is formed so as to overlap with the gate electrode 401. Note that etching here is not limited to wet etching, and dry etching may also be performed.

[0102]

As an etching gas for dry etching, a gas including chlorine (a chlorine-based 20 gas such as chlorine (Cl<sub>2</sub>), boron chloride (BCl<sub>3</sub>), silicon chloride (SiCl<sub>4</sub>), or carbon tetrachloride (CCl<sub>4</sub>)) is preferably used.

[0103]

Alternatively, a gas including fluorine (a fluorine-based gas such as carbon 25 tetrafluoride (CF<sub>4</sub>), sulfur fluoride (SF<sub>6</sub>), nitrogen fluoride (NF<sub>3</sub>), or trifluoromethane (CHF<sub>3</sub>)); hydrogen bromide (HBr); oxygen (O<sub>2</sub>); any of these gases to which a rare gas such as helium (He) or argon (Ar) is added; or the like can be used.

[0104]

As the dry etching method, a parallel plate reactive ion etching (RIE) method or an inductively coupled plasma (ICP) etching method can be used. In order to etch 30 the films into desired shapes, the etching condition (the amount of electric power applied to a coil-shaped electrode, the amount of electric power applied to an electrode on a substrate side, the temperature of the electrode on the substrate side, or the like) is

adjusted as appropriate.

[0105]

As an etchant used for wet etching, a mixed solution of phosphoric acid, acetic acid, and nitric acid, or the like can be used. Alternatively, ITO-07N (produced by 5 KANTO CHEMICAL CO., INC.) may be used.

[0106]

Furthermore, the etchant after the wet etching is removed together with the etched material by cleaning. The waste liquid of the etchant including the material etched off may be purified and the material may be reused. When a material such as 10 indium included in the oxide semiconductor film is collected from the waste liquid after the etching and reused, the resources can be efficiently used and the cost can be reduced.

[0107]

In order to obtain a desired shape by etching, the etching conditions (such as an 15 etchant, etching time, and temperature) are adjusted as appropriate depending on the material.

[0108]

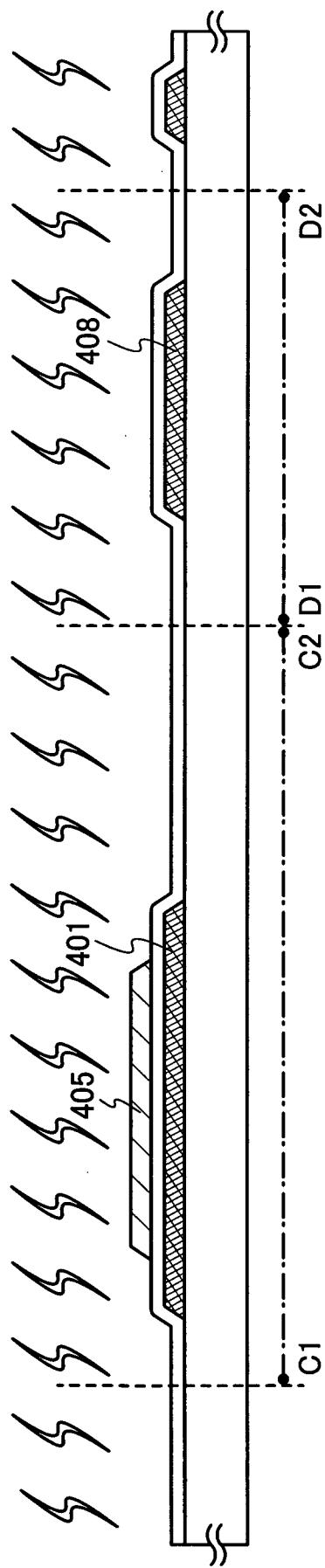

Next, as illustrated in FIG. 6A, the oxide semiconductor film 404 is irradiated with an electromagnetic wave under an inert gas (for example, nitrogen, helium, neon, 20 or argon) atmosphere, an oxygen atmosphere, an ultra-dry air atmosphere, or reduced pressure. Heat treatment may be performed at the same time as the irradiation with an electromagnetic wave. It is desirable that the content of water in the gas be 20 ppm or less, preferably 1 ppm or less, and more preferably 10 ppb or less. Impurities such as moisture, hydrogen, or OH are desorbed by the irradiation with an electromagnetic 25 wave, so that a highly purified oxide semiconductor film 405 is formed.

[0109]

For example, the highly purified island-shaped oxide semiconductor film 405 can be formed in such a manner that irradiation is performed under a nitrogen atmosphere with a microwave of 2.45 GHz at 600 W for about 5 minutes. In the case 30 where heat treatment is performed at the same time as the irradiation, the irradiation is performed at a temperature where a metal having a low melting point such as Zn included in the oxide semiconductor is evaporated as less as possible, for example,

higher than or equal to 100 °C and lower than 350 °C, preferably higher than or equal to 150 °C and lower than 250 °C. When the irradiation with an electromagnetic wave is performed at the same time as the heat treatment, impurities such as moisture in the oxide semiconductor film can be reduced more effectively in a short time. In this case, 5 the irradiation with an electromagnetic wave is performed in a state where the temperature of the substrate 400 reaches a heat treatment temperature.

[0110]

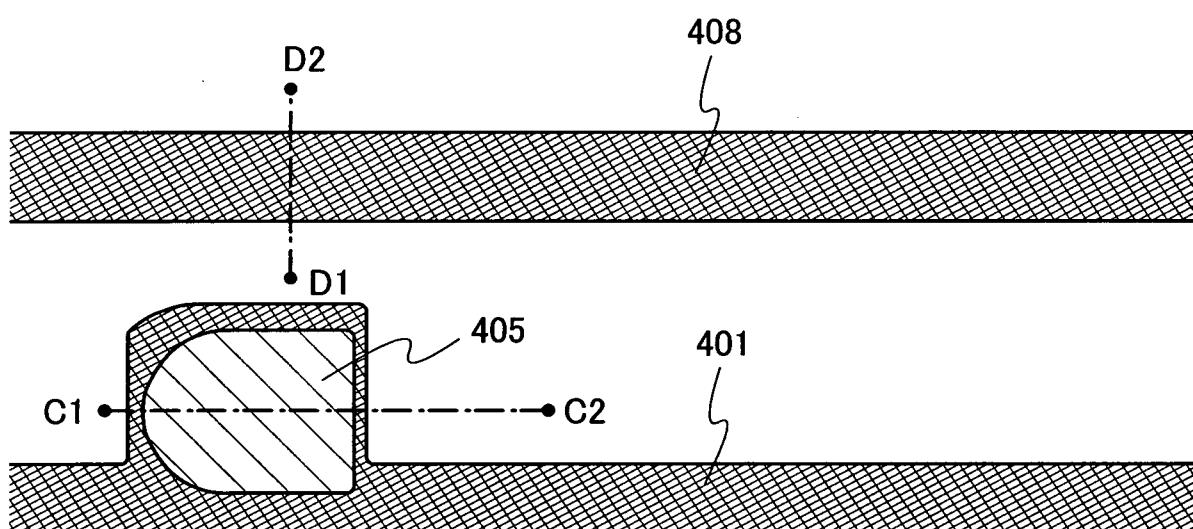

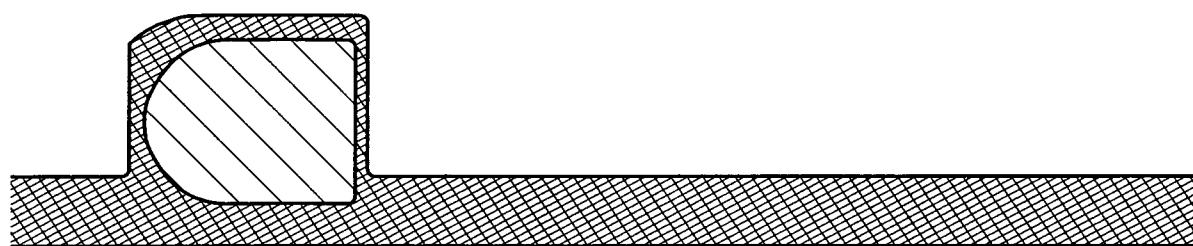

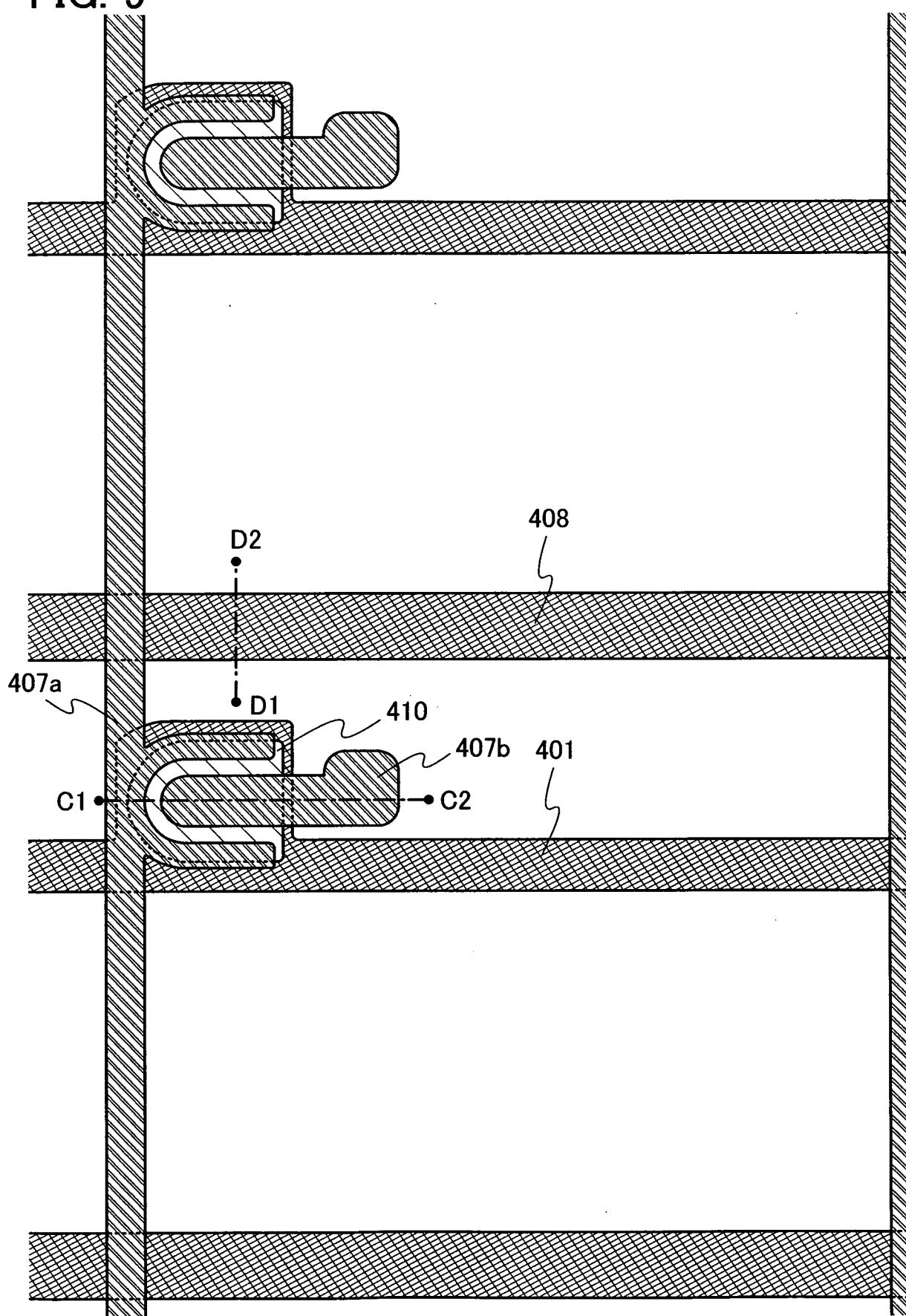

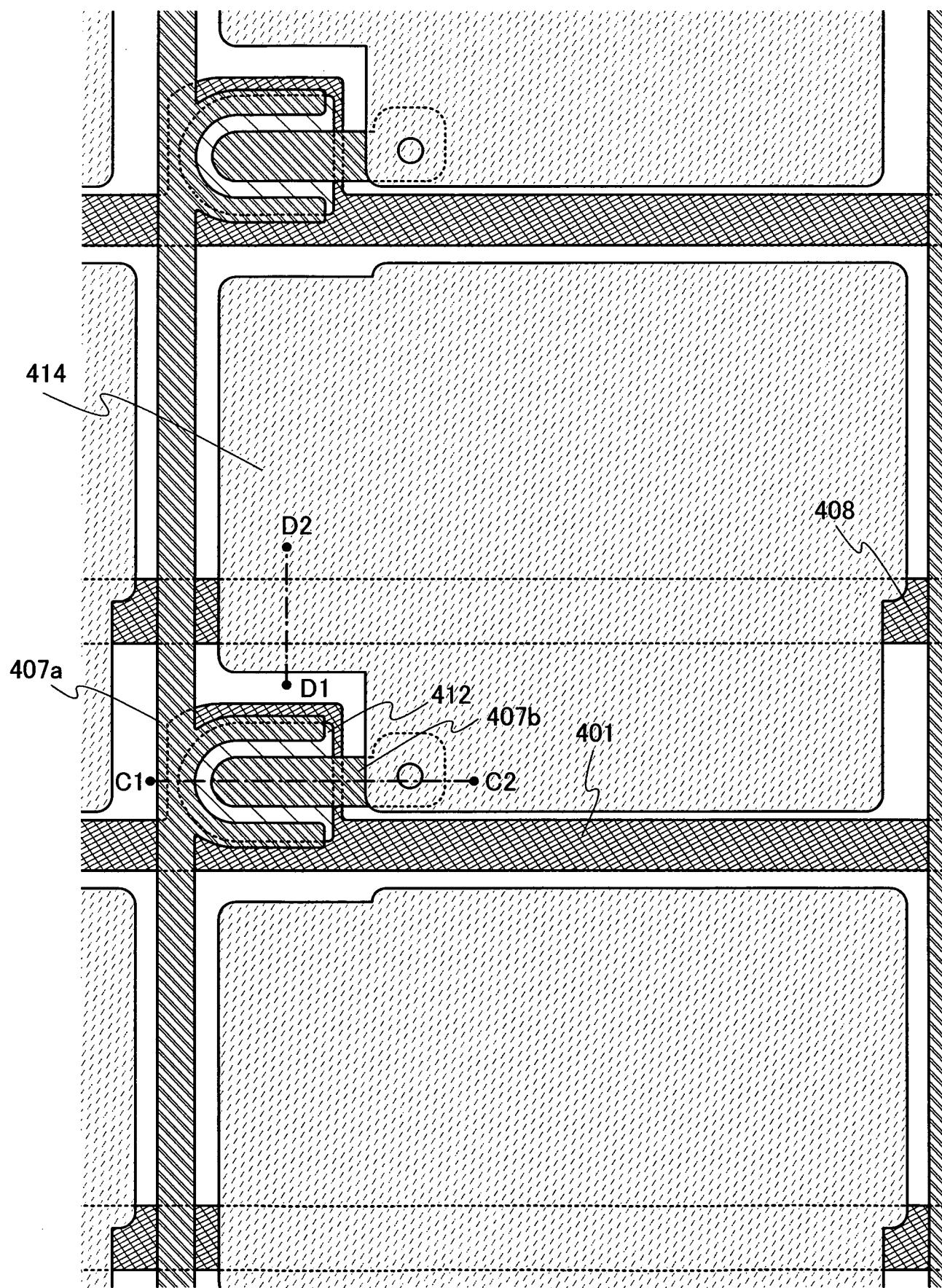

Cross-sectional views taken along dashed lines C1–C2 and D1–D2 in FIG. 6A correspond to cross-sectional views taken along dashed lines C1–C2 and D1–D2 in a 10 plan view illustrated in FIG. 8, respectively.

[0111]

Next, as illustrated in FIG. 6B, a conductive film 406 is formed using a metal material over the oxide semiconductor film 405 by a sputtering method or a vacuum evaporation method. As the material of the conductive film 406, there are an element 15 selected from aluminum, chromium, tantalum, titanium, molybdenum, and tungsten, an alloy including any of these elements as a component, an alloy film including a combination of any of these elements, and the like.

[0112]

In the case where heat treatment is performed after the formation of the 20 conductive film 406, it is preferable that the conductive film have heat resistance enough to withstand the heat treatment.

[0113]