(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5562329号

(P5562329)

(45) 発行日 平成26年7月30日(2014.7.30)

(24) 登録日 平成26年6月20日(2014.6.20)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 16/02 | (2006.01) | G 11 C 17/00 | 6 1 1 G |

| G 11 C 29/42 | (2006.01) | G 11 C 29/00 | 6 3 1 Z |

| G 11 C 16/04 | (2006.01) | G 11 C 17/00 | 6 2 2 E |

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 6 3 9 C |

| G 06 F 12/00 | (2006.01) | G 11 C 17/00 | 6 4 1   |

請求項の数 10 (全 20 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-516837 (P2011-516837)  |

| (86) (22) 出願日 | 平成21年6月30日 (2009.6.30)        |

| (65) 公表番号     | 特表2011-528154 (P2011-528154A) |

| (43) 公表日      | 平成23年11月10日 (2011.11.10)      |

| (86) 國際出願番号   | PCT/US2009/049328             |

| (87) 國際公開番号   | W02010/002943                 |

| (87) 國際公開日    | 平成22年1月7日 (2010.1.7)          |

| 審査請求日         | 平成24年6月29日 (2012.6.29)        |

| (31) 優先権主張番号  | 61/133, 921                   |

| (32) 優先日      | 平成20年7月7日 (2008.7.7)          |

| (33) 優先権主張国   | 米国 (US)                       |

| (31) 優先権主張番号  | 61/134, 688                   |

| (32) 優先日      | 平成20年7月10日 (2008.7.10)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                |

|-----------|--------------------------------------------------------------------------------|

| (73) 特許権者 | 508243639<br>エルエスアイ コーポレーション<br>アメリカ合衆国カリフォルニア州95131, サンノゼ, リッダー・パーク・ドライヴ 1320 |

| (74) 代理人  | 100094112<br>弁理士 岡部 譲                                                          |

| (74) 代理人  | 100104352<br>弁理士 朝日 伸光                                                         |

| (74) 代理人  | 100128657<br>弁理士 三山 勝巳                                                         |

| (74) 代理人  | 100160967<br>弁理士 ▲濱▼口 岳久                                                       |

最終頁に続く

(54) 【発明の名称】 フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインターフェースをとるための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

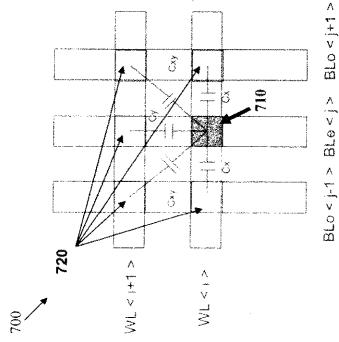

フラッシュ・メモリ・コントローラ(120)とフラッシュ・メモリ・アレイ(160)の間でインターフェースをとるための方法であって、

クロック信号の第1のエッジを使用して前記フラッシュ・メモリ・アレイにおけるターゲット・セル(710)に関するデータを伝送すること、および

前記クロック信号の第2のエッジを使用して前記ターゲット・セルに関するさらなる情報を伝送することを特徴とし、

前記クロック信号の各々のエッジの種類は、立ち下りエッジと立ち上りエッジの内のひとつであり、前記クロック信号の前記第1のエッジの前記種類は、前記クロック信号の前記第2のエッジの前記種類とは異なり、前記データは前記さらなる情報とは異なった種類の情報である、方法。

## 【請求項 2】

前記伝送するステップは、書き込みアクセスを備え、さらに前記さらなる情報は、前記ターゲット・セルに関する1つまたは複数のアグレッサ・セル(720)についての情報を備える請求項1に記載の方法。

## 【請求項 3】

前記1つまたは複数のアグレッサ・セルについての前記情報は、前記1つまたは複数のアグレッサ・セルに関するプログラム・データの1つまたは複数のビットを備える請求項2に記載の方法。

**【請求項 4】**

前記伝送するステップは、読み取りアクセスを備え、さらに前記さらなる情報は、前記第1のエッジで伝送される前記ターゲット・セルに関する前記データに関するソフト情報を備える請求項1に記載の方法。

**【請求項 5】**

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインターフェースをとるための方法であって、

クロック信号の第1のエッジで前記フラッシュ・メモリ・アレイにおけるターゲット・セルに関するデータを受け取ること、および

前記クロック信号の第2のエッジで前記ターゲット・セルに関するさらなる情報を受け取ることを特徴とし、10

前記クロック信号の各々のエッジの種類は、立ち下りエッジと立ち上りエッジの内のひとつであり、前記クロック信号の前記第1のエッジの前記種類は、前記クロック信号の前記第2のエッジの前記種類とは異なり、前記データは前記さらなる情報とは異なった種類の情報である、方法。

**【請求項 6】**

前記受け取るステップは、書き込みアクセスを備え、さらに前記さらなる情報は、前記ターゲット・セルに関する1つまたは複数のアグレッサ・セルについての情報を備える請求項5に記載の方法。20

**【請求項 7】**

前記1つまたは複数のアグレッサ・セルについての前記情報は、前記1つまたは複数のアグレッサ・セルに関するプログラム・データの1つまたは複数のビットを備える請求項6に記載の方法。20

**【請求項 8】**

前記受け取るステップは、読み取りアクセスを備え、さらに前記さらなる情報は、前記第1のエッジで伝送される前記ターゲット・セルに関する前記データに関するソフト情報を備える請求項5に記載の方法。

**【請求項 9】**

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインターフェースをとるためのインターフェースであって、30

前記フラッシュ・メモリ・コントローラと前記フラッシュ・メモリ・アレイの間の通信チャネルを特徴とし、前記通信チャネルは、クロック信号の第1のエッジで前記フラッシュ・メモリ・アレイにおけるターゲット・セルに関するデータを伝送し、さらに前記通信チャネルは、前記クロック信号の第2のエッジで前記ターゲット・セルに関するさらなる情報を伝送し、前記クロック信号の各々のエッジの種類は、立ち下りエッジと立ち上りエッジの内のひとつであり、前記クロック信号の前記第1のエッジの前記種類は、前記クロック信号の前記第2のエッジの前記種類とは異なり、前記データは前記さらなる情報とは異なった種類の情報である、インターフェース。

**【請求項 10】**

前記さらなる情報は、前記ターゲット・セルに関する1つまたは複数のアグレッサ・セルについての情報、及び前記第1のエッジで伝送される前記ターゲット・セルに関する前記データに関するソフト情報の内のひとつ又は複数を備える請求項9に記載のインターフェース。40

**【発明の詳細な説明】****【技術分野】****【0001】****(関連出願の相互参照)**

本出願は、参照によりそれぞれ本明細書に組み込まれている、2008年7月1日に出願した米国仮特許出願第61/133,675号、2008年7月3日に出願した米国仮特許出願第61/133,921号、および2008年7月10日に出願した米国仮特許50

出願第61/134,688号の優先権を主張する。

【0002】

本出願は、2009年3月11日に出願した、「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」という名称の国際特許出願第PCT/US09/36810号、ならびに本出願とそれぞれ同時に出願し、参照により本明細書に組み込まれている「Methods and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memories」<sup>10</sup>という名称の国際特許出願、「Methods and Apparatus for Write-Side Inter-cell Interference Mitigation in Flash Memories」という名称の国際特許出願、「Methods and Apparatus for Inter-cell Interference Mitigation Using Modulation Coding」という名称の国際特許出願、および「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」という名称の国際特許出願と関連する。

【0003】<sup>20</sup>

本発明は、一般に、フラッシュ・メモリ・デバイスに関し、より詳細には、そのようなフラッシュ・メモリ・デバイスにおけるコントローラとメモリ・アレイの間でインタフェースをとるための技術に関する。

【背景技術】

【0004】

フラッシュ・メモリ・デバイスなどのいくつかのメモリ・デバイスは、データを格納するのにアナログ・メモリ・セルを使用する。各メモリ・セルは、格納値とも呼ばれるアナログ値を格納する。格納値は、セルの中に格納された情報を表す。例えば、フラッシュ・メモリ・デバイスにおいて、各アナログ・メモリ・セルは、通常、或る電圧を格納する。各セルに関する可能なアナログ値の範囲は、通常、複数のしきい値領域に分割され、各領域は、1つまたは複数のデータ・ビット値に対応する。データは、所望される1つまたは複数のビットに対応する公称アナログ値を書き込むことによって、アナログ・メモリ・セルに書き込まれる。<sup>30</sup>

【0005】

例えば、SLC(シングルレベル・セル)フラッシュ・メモリ・デバイスは、1メモリ・セル当り1ビット(または可能な2つのメモリ状態)を格納する。他方、MLC(マルチレベル・セル)フラッシュ・メモリ・デバイスは、1メモリ・セル当り2ビット以上を格納する(すなわち、各セルは、4つ以上のプログラミング可能な状態を有する)。マルチレベル・セル・デバイスにおいて、異なる4つ以上のしきい値状態を定義するのに少なくとも3つのしきい値レベルが使用される。このため、個別のセルの動作範囲は、シングルレベル・セル・デバイスの場合と比べて、より多い数の状態に分割され、各状態の範囲は、より小さい。このため、マルチレベル・セル・デバイスにおける任意の単一のビットの信頼性は、一般に、シングルレベル・セル・デバイスの信頼性より低い。マルチレベル・コードのより詳細な説明に関しては、例えば、参照により本明細書に組み込まれている、U.Wachsmann他、「Multi-level Codes: Theoretical Concepts and Practical Design Rules」、IEEE Trans. on Information Theory、Vol. 45、No. 5、1361~91頁(1999年)を参照されたい。<sup>40</sup>

【0006】

フラッシュ・メモリは、通常、フラッシュ・メモリ・アレイと、フラッシュ・コントロ

<sup>50</sup>

ーラと、フラッシュ・メモリ・アレイとフラッシュ・コントローラの間の通信のためのインターフェースとを備える。ONFI(Open NAND Flash Interface Working Group)は、NANDフラッシュ・メモリ・デバイス、ならびにNANDフラッシュ・メモリ・デバイスと通信するデバイスに関するオープン標準を開発している業界コンソーシアムである。ONFIは、NANDフラッシュ・チップに対する標準インターフェースに関する仕様をもたらした。ONFIバージョン2.0は、DDR(ダブル・データレート)技術を使用して、クロック信号の立ち上りエッジと立ち下りエッジの両方でデータを転送する。ONFIバージョン2.0は、NANDフラッシュ・インターフェースのデータ伝送容量を増加させたが、パフォーマンスを向上させることができさらなる情報を伝送するためのさらなる帯域幅はもたらさない。

10

#### 【先行技術文献】

##### 【特許文献】

###### 【0007】

【特許文献1】米国仮特許出願第61/133,675号

【特許文献2】米国仮特許出願第61/133,921号

【特許文献3】米国仮特許出願第61/134,688号

【特許文献4】国際特許出願第PCT/US09/36810号

【特許文献5】国際特許出願「Methods and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memories」

20

【特許文献6】国際特許出願「Methods and Apparatus for Write-Side Inter-cell Interference Mitigation in Flash Memories」

【特許文献7】国際特許出願、「Methods and Apparatus for Inter-cell Interference Mitigation Using Modulation Coding」

【特許文献8】国際特許出願「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」

【特許文献9】米国特許第6,522,580号

30

##### 【非特許文献】

###### 【0008】

【非特許文献1】U.Wachsmann他、「Multilevel Codes: Theoretical Concepts and Practical Design Rules」、IEEE Trans. on Information Theory、Vol. 45、No. 5、1361~91頁(1999年)

【非特許文献2】Ki-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE J. of Solid State Circuits、Vol. 43、No. 4、919~928頁、(2008年4月)

40

##### 【発明の概要】

##### 【発明が解決しようとする課題】

###### 【0009】

したがって、フラッシュ・メモリ・デバイスにおけるコントローラとメモリ・アレイの間の改良されたインターフェースの必要性が存在する。伝送されるデータについてのさらなる情報のためのさらなる帯域幅をもたらす、フラッシュ・メモリ・デバイスにおけるコントローラとメモリ・アレイの間の改良されたインターフェースのさらに別の必要性が存在する。消費電力または表面積を大幅に増加させることなしに、さらなる帯域幅をもたらす、

50

フラッシュ・メモリ・デバイスにおけるコントローラとメモリ・アレイの間の改良されたインターフェースのさらなる必要性が存在する。

【課題を解決するための手段】

【0010】

概して、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインターフェースをとるための方法および装置が提供される。本発明の一態様によれば、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間で使用するためのインターフェースが提供される。このインターフェースは、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間の通信チャネルを備え、この通信チャネルは、クロック信号の第1のエッジでフラッシュ・メモリ・アレイにおけるターゲット・セルに関するデータを伝送し、さらにこの通信チャネルは、クロック信号の第2のエッジで、そのターゲット・セルに関するさらなる情報を伝送する。

10

【0011】

例示的な書き込みアクセスの場合、さらなる情報は、例えば、ターゲット・セルに関する1つまたは複数のアグレッサ・セルについての情報を備える。例えば、1つまたは複数のアグレッサ・セルについての情報は、その1つまたは複数のアグレッサ・セルに関するプログラム・データの1つまたは複数のビットを備える。例示的な読み取りアクセスの場合、さらなる情報は、例えば、第1のエッジで伝送されるターゲット・セルに関するデータに関するソフト情報を備える。

【0012】

20

本発明のより完全な理解、ならびに本発明のさらなる特徴および利点は、後段の詳細な説明および図面を参照することによって得られる。

【図面の簡単な説明】

【0013】

【図1】従来のフラッシュ・メモリ・システムを示す概略ブロック図である。

【図2】図1の例示的なマルチレベル・セル・フラッシュ・メモリに関する例示的なしきい値電圧分布を示す図である。

【図3】MLC(マルチレベル・セル)フラッシュ・メモリ・デバイスにおける例示的なフラッシュ・セル・アレイのアーキテクチャを示す図である。

30

【図4】図2の電圧割当てスキームに関する例示的な2段階MLCプログラミング・スキームを示す図である。

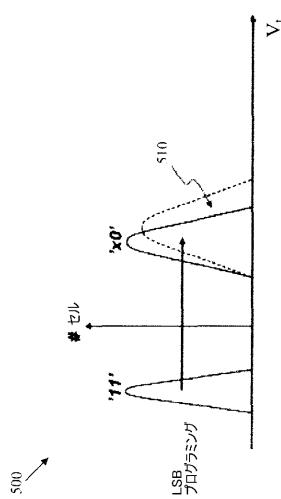

【図5A】隣接セルに加えられるICLを低減する代替のMLCプログラミング・スキームを示す図である。

【図5B】隣接セルに加えられるICLを低減する代替のMLCプログラミング・スキームを示す図である。

【図6】MLC(マルチレベル・セル)フラッシュ・メモリ・デバイスにおける例示的なフラッシュ・セル・アレイをさらに詳細に示す図である。

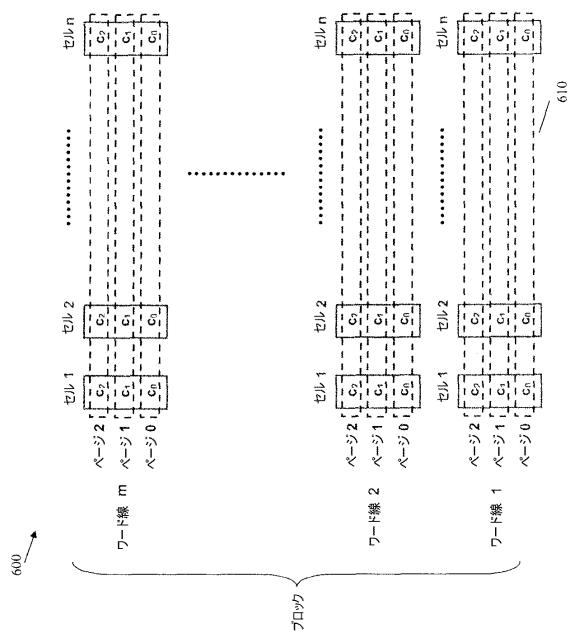

【図7】いくつかの例示的なアグレッサ・セルからの寄生静電容量に起因してターゲット・セルに関して存在するICLを示す図である。

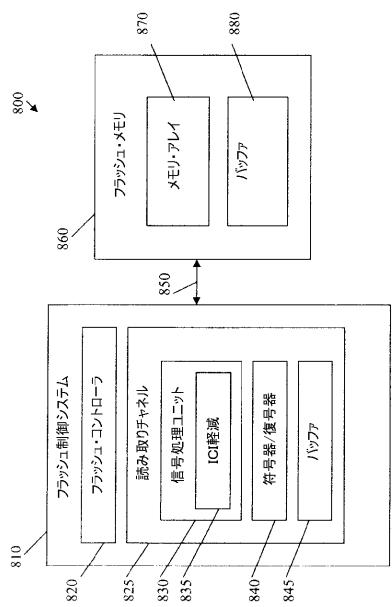

【図8】本発明によるコントローラ・ベースのICL軽減技術を組み込む例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

40

【図9】本発明の代替実施形態によるメモリ・ベースのICL軽減技術を組み込む例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

【図10】本発明による書き込みアクセスのための該当する波形を示す図である。

【図11】本発明による読み取りアクセスのための該当する波形を示す図である。

【発明を実施するための形態】

【0014】

本発明は、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間で改良されたインターフェースを提供する。開示されるインターフェースは、消費電力または表面積を大幅に増加させることなしに、伝送されるデータについてのさらなる情報のためのさ

50

らなる帯域幅を提供する。本発明は、伝送されるさらなる情報が、例えば、伝送されるターゲット・セル・データと関係する1つまたは複数の隣接セルの伝送されるデータまたは値についてのソフト情報を備える、I C I軽減のコンテキストで説明されるが、当業者には明白なとおり、本発明は、他の用途のためにさらなる情報を転送するように適用されることも可能である。本発明の一態様によれば、データが、クロック信号の第1のエッジ(立ち上りエッジなどの)で転送され、さらにその転送されるデータについてのさらなる情報が、クロック信号の第2のエッジ(立ち下りエッジなどの)で伝送される。

#### 【0015】

本発明の様々な態様は、シングルレベル・セルN A N Dフラッシュ・メモリ・デバイスまたはM L C(マルチレベル・セル)N A N Dフラッシュ・メモリ・デバイスなどのメモリ・デバイスにおいてI C Iを軽減するための信号処理技術を対象とする。本明細書で使用される、マルチレベル・セル・フラッシュ・メモリは、各メモリ・セルが2ビット以上を格納するメモリを備える。通常、1つのフラッシュ・セルの中に格納された複数のビットは、異なるページに属する。本発明は、アナログ値を電圧として格納するメモリ・セルを使用して本明細書で説明されるが、本発明は、当業者には明白なとおり、格納されたデータを表すのに電圧または電流を使用するなどの、フラッシュ・メモリに関する任意の格納機構と共に使用され得る。

#### 【0016】

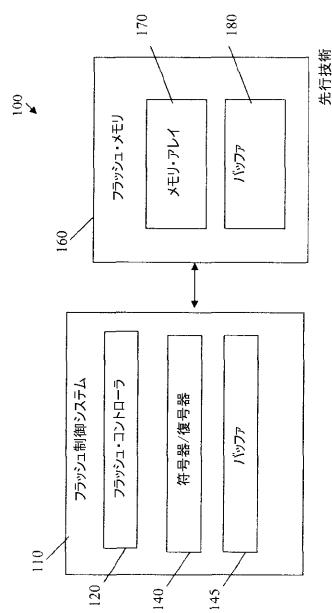

図1は、従来のフラッシュ・メモリ・システム100の概略ブロック図である。図1に示されるとおり、例示的なフラッシュ・メモリ・システム100は、フラッシュ制御システム110と、フラッシュ・メモリ・ブロック160とを備える。例示的なフラッシュ制御システム110は、フラッシュ・コントローラ120と、符号器/復号器ブロック140と、1つまたは複数のバッファ145とを備える。代替の実施形態において、符号器/復号器ブロック140およびいくつかのバッファ145は、フラッシュ・コントローラ120内部に実装されてもよい。符号器/復号器ブロック140およびバッファ145は、例えば、よく知られた市販の技術および/または製品を使用して実施されることが可能である。

#### 【0017】

例示的なフラッシュ・メモリ・ブロック160は、よく知られた市販の技術および/または製品を使用して、それぞれ実施されることが可能なメモリ・アレイ170と、1つまたは複数のバッファ180とを備える。メモリ・アレイ170は、N A N Dフラッシュ・メモリ、P C M(相変化メモリ)、M R A Mメモリ、N O Rフラッシュ・メモリ、または別の不揮発性フラッシュ・メモリなどのシングルレベル・セル・フラッシュ・メモリまたはマルチレベル・セル・フラッシュ・メモリとして実施されることが可能である。本発明は、主に、マルチレベル・セルN A N Dフラッシュ・メモリのコンテキストにおいて例示されるが、本発明は、当業者には明白なとおり、シングルレベル・セル・フラッシュ・メモリおよびその他の不揮発性メモリにも適用され得る。

#### 【0018】

(マルチレベル・セル・フラッシュ・メモリ)

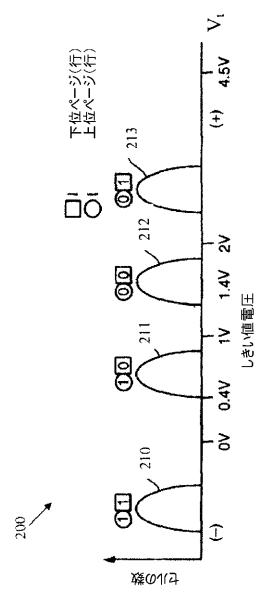

マルチレベル・セルN A N Dフラッシュ・メモリにおいて、しきい値検出器が、或る特定のセルに関連する電圧値を、事前定義されたメモリ状態に変換するのに通常、使用される。図2は、参照により本明細書に組み込まれている米国特許第6,522,580号の教示に基づく、図1の例示的なマルチレベル・セル・フラッシュ・メモリ170に関する例示的なしきい値電圧分布を示す。一般に、セルのしきい値電圧は、セルが或る量の電流を伝導するようにセルに印加される必要がある電圧である。しきい値電圧は、セルの中に格納されたデータに関する測度である。

#### 【0019】

図2に示される例示的な実施形態において、各格納要素は、可能な4つのデータ状態を使用して、各メモリ・セルの中に2ビットのデータを格納する。図2は、4つのピーク210~213を示し、各ピークは、1つの状態に対応する。マルチレベル・セル・フラッ

10

20

30

40

50

シュー・デバイスにおいて、しきい値電圧分布グラフ 200 の異なるピーク 210 ~ 213 が、セルの中に 2 ビットを格納するために使用される。

#### 【0020】

しきい値電圧分布グラフ 200 のピーク 210 ~ 213 には、対応する 2 進値でラベルが付けられる。このため、セルが第 1 の状態 210 にある場合、セルは、低い方のビット（最下位ビット、LSB としても知られる）に関して「1」を表し、高い方のビット（最上位ビット、MSB としても知られる）に関して「1」を表す。状態 210 は、一般に、セルの初期の未だにプログラミングされていない状態、または消去された状態である。同様に、セルが第 2 の状態 211 にある場合、セルは、低い方のビットに関して「0」を表し、高い方のビットに関して「1」を表す。セルが第 3 の状態 212 にある場合、セルは、低い方のビットに関して「0」を表し、高い方のビットに関して「0」を表す。最後に、セルが第 4 の状態 213 にある場合、セルは、低い方のビットに関して「1」を表し、高い方のビットに関して「0」を表す。10

#### 【0021】

しきい値電圧分布 210 は、0 ボルトを下回る負のしきい値電圧レベルで、消去された状態（「11」データ状態）にあるアレイ内のセルのしきい値電圧  $V_t$  の分布を表す。「10」ユーザ・データを格納するメモリ・セルのしきい値電圧分布 211 が、0 ボルトから 1 ボルトまでの範囲内にあるように示され、「00」ユーザ・データを格納するメモリ・セルのしきい値電圧分布 212 が、1 ボルトから 2 ボルトまでの範囲内にあるように示される。しきい値電圧分布 213 は、しきい値電圧レベルが 2 ボルトから 4.5 ボルトまでの範囲内の読み取り走査電圧に設定された、「01」データ状態にプログラミングされているセルの分布を示す。20

#### 【0022】

このように、図 2 の例示的な実施形態において、0 ボルト、1 ボルト、および 2 ボルトが、各レベルまたは各状態の間の電圧レベルしきい値として使用され得る。これらの電圧レベルしきい値は、フラッシュ・メモリ 160（例えば、フラッシュ・メモリ 160 における感知回路）によって、所与のセルの電圧レベルまたは電圧状態を判定するのに使用される。フラッシュ・メモリ 160 は、測定された電圧を電圧レベルしきい値と比較することに基づいて、各セルに 1 つまたは複数のビットを割り当て、これらの割当ては、次に、ハード判定としてフラッシュ制御システム 110 に伝送される。さらに、または代替として、ソフト情報を使用する実施例において、フラッシュ・メモリ 160 は、メモリ・セルの中に格納されたビットの数より多くのビットが、測定された電圧を表すのに使用される場合に、測定された電圧、または測定された電圧の量子化されたバージョンをソフト情報としてフラッシュ制御システム 110 に伝送することが可能である。30

#### 【0023】

セルは、通常、よく知られたプログラミング / 検証技術を使用してプログラミングされることがさらに注目される。一般に、プログラミング / 検証サイクル中、フラッシュ・メモリ 160 は、最小限のターゲットしきい値電圧を超えるまで、高まる電圧を徐々に印加して、セル・トランジスタの中に電荷を格納する。例えば、図 2 の例における「10」データ状態をプログラミングする際、フラッシュ・メモリ 160 は、0.4 ボルトという最小限のターゲットしきい値電圧を超えるまで、高まる電圧を徐々に印加して、セル・トランジスタの中に電荷を格納する。40

#### 【0024】

後段でさらに説明するとおり、シングル・メモリ・セルの中に格納される 2 ビットのそれぞれは、異なるページからである。つまり、各メモリ・セルの中に格納された 2 ビットの各ビットには、異なるページ・アドレスが付いている。図 2 に示される右側のビットは、下位のページ・アドレスが入力されると、アクセスされる。左側のビットは、上位のページ・アドレスが入力されると、アクセスされる。

#### 【0025】

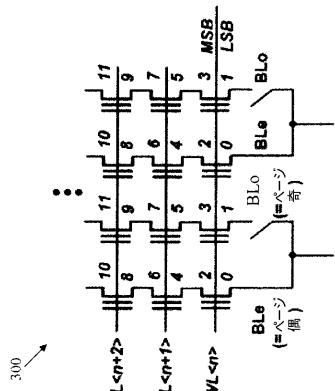

図 3 は、MLC（マルチレベル・セル）フラッシュ・メモリ・デバイス 160 における

例示的なフラッシュ・セル・アレイ 300 のアーキテクチャを示し、それぞれの例示的なセルは、通常、2ビットを格納する浮動ゲート・トランジスタに対応する。図3で、各セルは、その2ビットが属する2つのページに関する2つの番号に関連する。例示的なセル・アレイ・セクション300は、ワード線n乃至n+2、および4つのビット線を示す。例示的なフラッシュ・セル・アレイ300は、偶ページと奇ページに分割され、ただし、例えば、偶数番号を有するセル（番号0および2を有するセルなどの）は、偶ページに対応し、奇数番号を有するセル（番号1および3を有するセルなどの）は、奇ページに対応する。ワード線nは、例えば、偶ビット線の中に偶ページ0および2を格納し、奇ビット線の中に奇ページ1および3を格納する。

## 【0026】

10

さらに、図3は、偶ビット線または奇ビット線が、示された順序で順次に（ボトムアップで）選択され、プログラミングされる例示的なプログラミング・シーケンスを示す。番号は、それらのページがプログラミングされる順序を示す。例えば、ページ0は、ページ1より前にプログラミングされる。偶ページおよび奇ページのプログラミングのさらなる説明に関しては、例えば、参考により本明細書に組み込まれている、Ki-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits、Vol. 43、No. 4、919～928頁、（2008年4月）を参照されたい。

## 【0027】

20

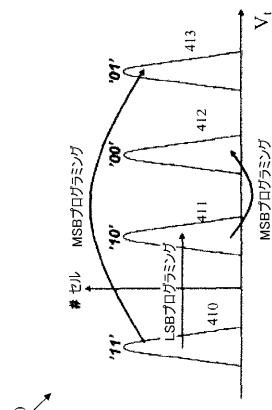

図4は、図2の電圧割当てスキームに関する例示的な2段階MLCプログラミング・スキーム400を示す。図4に示されるとおり、LSBプログラミング段階中、消去された状態410にある選択されたセルの状態は、LSBがゼロである場合、プログラミングされた最低の状態411に移る。このため、LSBプログラミング段階で、メモリ・セルは、消去された状態「11」から「10」にプログラミングされる。次に、MSBプログラミング段階中、2つの状態、状態「00」（412）および状態「10」（413）が、前のLSBデータに依存して順次に形成される。一般に、MSBプログラミング段階中、「10」状態は、「00」にプログラミングされ、状態「11」は、「01」にプログラミングされる。

30

## 【0028】

図4のプログラミング・スキーム400は、状態410から状態413への状態の変化に関連する最大電圧シフトを例示することが注目される。状態の変化に関連する最大電圧シフトを低減し、その結果、電圧シフトによって生じるIClを低減する、いくつかのプログラミング・スキームが提案または示唆されている。

## 【0029】

40

図5Aおよび図5Bは一緒にになって、隣接セルに加えられるIClを低減する代替のMLCプログラミング・スキーム500を示す。図5Aに示されるとおり、LSBプログラミング段階中、メモリ・セルが、SLCプログラミングと同様の仕方で、状態「11」から、一時的（または中間）状態として状態「x0」にプログラミングされる。同一のワード線における隣接セルもLSBプログラミングされた後、分布は、IClに起因して、図5Aにおけるピーク510によって示されるとおり、場合により、広くなっている。その後、図5Bに示されるMSBプログラミング段階で、「x0」状態が、入力データに対応する最終段階として「00」または「10」にプログラミングされ、さもなければ、「11」状態が、最終の「01」状態にプログラミングされる。一般に、「11」セルを除くすべてのメモリは、隣接セルによって生じるIClが大きく低減され得るように、LSBデータに関する一時的にプログラミングされた状態から、MSBプログラミング状態における最終状態に再プログラミングされる。最終状態におけるセルは、最終状態に再プログラミングされているので、中間状態にある間にセルが経験したIClを被らない。最終状

50

態におけるセルは、最終状態になってからセルが経験した I C I だけしか被らない。前述したとおり、中間プログラミング段階を使用する図 5 A および図 5 B のマルチステップ・プログラミング・シーケンスは、最大電圧変化を低減し、したがって、これらの電圧変化によって生じる I C I を低減する。図 5 B で、例えば、M S B プログラミング段階中の最大電圧シフトは、状態「1 1」から「0 1」への遷移、および状態「x 0」から「1 0」への遷移にそれぞれ関連することを見て取ることができる。これらの電圧シフトは、図 4 における状態「1 1」から「0 1」への最大電圧シフトと比べて、相當に小さい。

#### 【0030】

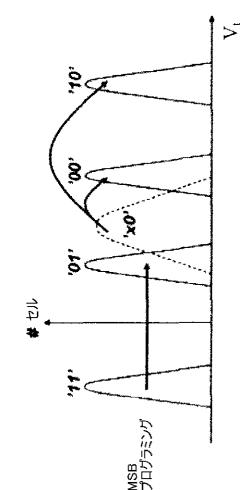

図 6 は、M L C (マルチレベル・セル) フラッシュ・メモリ・デバイス 130 における例示的なフラッシュ・セル・アレイ 600 をさらに詳細に示す。図 6 に示されるとおり、フラッシュ・セル・アレイ 600 は、1 フラッシュ・セル、c<sub>i</sub> 当り 3 ビットを格納する。図 6 は、1 ブロックに関するフラッシュ・セル・アレイ・アーキテクチャを示し、ただし、それぞれの例示的なセルは、3 ビットを格納する浮動ゲート・トランジスタに通常、対応する。例示的なセル・アレイ 600 は、m 個のワード線と、n 個のビット線とから成る。通常、現行のマルチページ・セル・フラッシュ・メモリにおいて、単一のセル内の複数のビットは、異なるページに属する。図 6 の例において、各セルに関する 3 ビットは、異なる 3 つのページに対応し、各ワード線が、3 つのページを格納する。以下の説明において、ページ 0、1、および 2 は、ワード線内で低ページ・レベル、中ページ・レベル、および高ページ・レベルと呼ばれる。

#### 【0031】

前述したとおり、フラッシュ・セル・アレイは、偶ページと奇ページにさらに分割されることが可能であり、ただし、例えば、偶数番号を有するセル(図 6 のセル 2 および 4 などの)は、偶ページに対応し、奇数番号を有するセル(図 6 のセル 1 および 3 などの)は、奇ページに対応する。この場合、或るページ(ページ 0 などの)は、偶セルにおいて偶ページ(偶ページ 0 )を含み、奇セルにおいて奇ページ(奇ページ 0 )を含む。

#### 【0032】

##### (セル間干渉)

前述したとおり、I C I は、セル間の寄生静電容量の結果であり、一般に、歪みの最も顕著な原因の 1 つであると考えられる。図 7 は、いくつかの例示的なアグレッサ・セル 720 からの寄生静電容量に起因してターゲット・セル 710 に関して存在する I C I を示す。以下の表記が図 7 において使用される。

W L : ワード線

B L : ビット線

B L<sub>o</sub> : 奇ビット線

B L<sub>e</sub> : 偶ビット線、および

C : 静電容量。

#### 【0033】

本発明は、I C I が、ターゲット・セル 710 がプログラミングされた後にプログラミングされるアグレッサ・セル 720 によってもたらされることを認識する。I C I は、ターゲット・セル 710 の電圧、V<sub>t</sub> を変化させる。例示的な実施形態において、「ボトムアップ」プログラミング・スキームが想定され、ワード線 i および i + 1 における隣接するアグレッサ・セルが、ターゲット・セル 710 に関する I C I を生じさせる。ブロックのそのようなボトムアップ・プログラミングでは、下位のワード線 i - 1 からの I C I は、除去され、5 つまでの隣接セルが、図 7 に示されるとおり、アグレッサ・セル 720 として I C I に寄与する。しかし、本明細書で開示される技術は、当業者には明白なとおり、ワード線 i - 1 などの他のワード線からのアグレッサ・セルも I C I に寄与する事例にまで一般化され得ることが注目される。ワード線 i - 1、i、および i + 1 からのアグレッサ・セルが I C I に寄与する場合、最も近い 8 つまでの隣接セルが考慮される必要がある。ターゲット・セルからより離れている他のセルは、それらのセルの、I C I への寄与がごくわずかである場合、無視され得る。一般に、アグレッサ・セル 720 は、プログラ

10

20

30

40

50

ミング・シーケンス・スキーム（ボトムアップ技術または偶／奇技術などの）を分析して、所与のターゲット・セル 710 の後にプログラミングされるアグレッサ・セル 720 を識別することによって、識別される。

## 【0034】

ターゲット・セル 710 上にアグレッサ・セル 720 によってもたらされる ICI は、以下のとおり、例示的な実施形態においてモデル化され得る。すなわち、

## 【0035】

## 【数1】

$$\Delta V_{ICI}^{(i,j)} = k_x \Delta V_t^{(i,j-1)} + k_x \Delta V_t^{(i,j+1)} + k_y \Delta V_t^{(i+1,j)} + \\ k_{xy} \Delta V_t^{(i+1,j-1)} + k_{xy} \Delta V_t^{(i+1,j+1)} \quad (1)$$

ただし、

## 【0036】

## 【数2】

$$\Delta V_t^{(w,b)}$$

は、アグレッサ・セル ( w , b ) の  $V_t$  電圧の変化であり、

## 【0037】

## 【数3】

$$(w,b), \Delta V_{ICI}^{(i,j)}$$

は、ICI に起因するターゲット・セル ( i , j ) の  $V_t$  電圧の変化であり、  $k_x$  、  $k_y$  および  $k_{xy}$  は、静電容量結合係数である。

## 【0038】

一般に、  $V_t$  は、セル上に格納され、読み取り動作中に獲得されるデータを表す電圧である。  $V_t$  は、例えば、1セル当たり格納されたビットの数より高い精度でソフト電圧値、または1セル当たり格納されたビットの数（例えば、1セル当たり3ビットのフラッシュの場合、3ビット）と同一の分解能でハード電圧レベルに量子化された値であり得る。

## 【0039】

## (システム・レベルの考慮事項)

図8は、本発明によるコントローラ・ベースの ICI 軽減技術を組み込む例示的なフラッシュ・メモリ・システム800の概略ブロック図である。図8に示されるとおり、例示的なフラッシュ・メモリ・システム800は、インターフェース850によって接続された、フラッシュ制御システム810と、フラッシュ・メモリ・ブロック860とを備える。例示的なフラッシュ制御システム810は、通常、1つまたは複数の集積回路上に、フラッシュ・コントローラ820と、読み取りチャネル825とを備える。例示的なフラッシュ・コントローラ820は、本発明の特徴および機能をサポートするようにこの場合、変形される、例えば、よく知られた市販の技術および／または製品を使用して実施されることが可能である。

## 【0040】

例示的な読み取りチャネル825は、信号処理ユニット830と、符号器／復号器ブロック840と、1つまたは複数のバッファ845とを備える。「読み取りチャネル」という用語は、書き込みチャネルも包含し得ることが注目される。代替の実施形態において、符号器／復号器ブロック840およびいくつかのバッファ845は、フラッシュ・コントローラ820内部に実装されてもよい。符号器／復号器ブロック840およびバッファ845は、本発明の特徴および機能を提供するようにこの場合、変形される、例えば、よく

10

20

30

40

50

知られた市販の技術および／または製品を使用して実施されることが可能である。

**【0041】**

例示的な信号処理ユニット830は、例えば、図10～図12に関連して後段でさらに説明される、1つまたは複数のICI軽減プロセス835を実施する1つまたは複数のプロセッサを備える。さらに、図8に示される様々なブロックの間のデータ・フローも、例えば、図10～図12に関連して後段でさらに説明される。一般に、図11および図12に関連して後段でさらに説明されるとおり、読み取り動作中にICI軽減を実行するのに、1つまたは複数のICI軽減プロセス835は、ハード読み取り値またはソフト読み取り値に基づいて、新たな読み取り値を計算する。同様に、図10に関連して後段でさらに説明されるとおり、書き込み動作中にICI軽減を実行するのに、1つまたは複数のICI軽減プロセス835は、ターゲット・セルおよびアグレッサ・セルに関するプログラム・データに基づいて、メモリ・アレイ870の中に格納されるべき事前補償されたプログラム値を生成する。

10

**【0042】**

例示的なフラッシュ・メモリ・ブロック860は、メモリ・アレイ870と、よく知られた市販の技術および／または製品を使用してそれぞれ実施されることが可能な1つまたは複数のバッファ880とを備える。

**【0043】**

図10および図11に関連して後段でさらに説明される本発明の一態様によれば、例示的なインターフェース850は、アグレッサ・セルに関する情報を表す値などの、従来のフラッシュ・メモリ・システムと関係するさらなる情報を伝える必要がある可能性がある。このため、インターフェース850は、従来のフラッシュ・メモリ・システムにおけるインターフェースと比べて、より大きい容量（例えば、より多くの入力ピンまたは出力ピン）、またはより高速のレートを有する必要がある可能性がある。

20

**【0044】**

書き込み動作中、インターフェース850は、ページ・レベル・アクセス技術またはワード線レベル・アクセス技術を通常、使用して、ターゲット・セルの中に格納されるように、事前補償されたプログラム値を転送する。例示的なページ・レベル・アクセス技術またはワード線レベル・アクセス技術のより詳細な説明に関しては、例えば、参照により本明細書に組み込まれている、2009年3月11日に出願した、「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」という名称の国際特許出願PCT/US09/36810号を参照されたい。事前補償されたプログラム値の数は、通常、元のプログラム値の数より多いので、通常、元のプログラム値を表すのと比べて、事前補償されたプログラム値を表すのに、より多くのビットが要求される。したがって、書き込み側ICI軽減に関して、インターフェース850は、従来のインターフェースと比べて、より多くのデータを転送する必要がある。

30

**【0045】**

読み取り動作中、インターフェース850は、ターゲット・セルおよびアグレッサ・セルに関してメモリ・アレイ870から獲得されたハード読み取り値および／またはソフト読み取り値を転送する。例えば、ターゲット・セルに関するページの読み取り値に加えて、上位／下位のワード線、あるいは隣接する偶ビット線または奇ビット線における1つまたは複数の隣接ページの読み取り値が、インターフェース・バスを介して転送される。

40

**【0046】**

図8の実施形態において、開示される書き込みまたは読み取り側ICI軽減技術は、通常、最小の面積を実現するように論理回路に合わせて最適化されたプロセス技術で、フラッシュ・メモリの外部に実装される。しかし、このことは、インターフェース850上でさらなるアグレッサ・セル・データが転送されなければならないという犠牲を払う。

50

## 【0047】

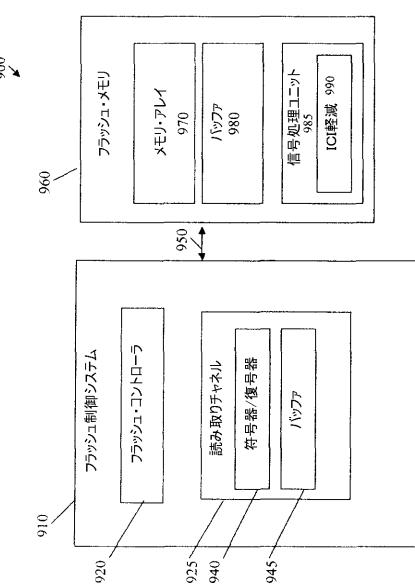

図9は、本発明の代替の実施形態による、メモリ・ベースのI C I軽減技術を組み込む例示的なフラッシュ・メモリ・システム900の概略ブロック図である。図9に示されるおり、例示的なフラッシュ・メモリ・システム900は、インタフェース950によって接続された、フラッシュ制御システム910と、フラッシュ・メモリ・ブロック960とを備える。例示的なフラッシュ制御システム910は、通常、1つまたは複数の集積回路上に、フラッシュ・コントローラ920と、オプションの読み取りチャネル925とを備える。例示的な読み取りチャネル925は、符号器/復号器ブロック940と、1つまたは複数のバッファ945とを備える。代替の実施形態において、符号器/復号器ブロック940およびいくつかのバッファ945は、フラッシュ・コントローラ920内部に実装されてもよい。例示的なフラッシュ・コントローラ920は、本発明の特徴および機能をサポートするようにこの場合、変形される、例えば、よく知られた市販の技術および/または製品を使用して実施されることが可能である。符号器/復号器ブロック940およびバッファ945は、よく知られた市販の技術および/または製品を使用して実施されることが可能である。10

## 【0048】

例示的なフラッシュ・メモリ・ブロック960は、メモリ・アレイ970と、よく知られた市販の技術および/または製品を使用してそれぞれ実施されることが可能な1つまたは複数のバッファ980とを備える。さらに、例示的なフラッシュ・メモリ・ブロック960は、1つまたは複数のI C I軽減プロセス990を実施する1つまたは複数のプロセッサを備える例示的な信号処理ユニット985を備える。一般に、読み取り動作中にI C I軽減を実行するのに、1つまたは複数のI C I軽減プロセス990は、メモリ・アレイ970からのハード読み取り値またはソフト読み取り値に基づいて、新たな読み取り値を計算する。同様に、書き込み動作中にI C I軽減を実行するのに、1つまたは複数のI C I軽減プロセス990は、ターゲット・セルおよびアグレッサ・セルに関してフラッシュ・コントローラ910から受け取られたプログラム・データに基づいて、事前補償されたプログラム値を生成する。20

## 【0049】

図10および図11に関連して後段でさらに説明される本発明の一態様によれば、例示的なインタフェース950は、アグレッサ・セルに関する情報を表す値などの、従来のフラッシュ・メモリ・システムと関係するさらなる情報を伝える必要がある可能性がある。このため、インタフェース950は、従来のフラッシュ・メモリ・システムにおけるインタフェースと比べて、より大きい容量(例えば、より多くの入力ピンまたは出力ピン)、またはより高速のレートを有する必要がある可能性がある。30

## 【0050】

書き込み動作中、インタフェース950は、ターゲット・セルおよびアグレッサ・セルの中に格納されるようにプログラム・データを転送し、事前補償されたプログラム値が、フラッシュ・メモリ960内部で計算される。インタフェース950は、例えば、従来のフラッシュ・メモリ・システムの場合と同様にターゲット・セルに対するページのためのプログラム・データを転送し、さらに、アグレッサ・セルに対する隣接するワード線、または偶ビット線もしくは奇ビット線のためのプログラム・データを転送する。通常、事前補償されたプログラム値を表すのと比べて、このプログラム・データを表すのに要求されるビットは、より少ない。したがって、書き込み側I C I軽減に関して、インタフェース950は、通常、インタフェース850と比べて、より小さい帯域幅しか要求しない。しかし、このことは、論理回路ではなく、メモリに合わせて通常、最適化されるフラッシュ・メモリを製造するのに使用されるメモリ・プロセス技術を使用して、メモリ内部に書き込み側I C I軽減プロセスを実装するという犠牲を払う。40

## 【0051】

読み取り動作中、インタフェース950は、ターゲット・セルに関して、ならびにオプションとしてアグレッサ・セルに関してI C I軽減プロセス990によって計算された新50

たなハード読み取り値もしくはハード読み取りデータ、および／またはソフト読み取り値もしくはソフト読み取りデータを転送する。通常、単一回の読み取りアクセスに関して伝えられる情報は、データのページまたはワード線である。論理回路にではなく、メモリに合わせて通常、最適化されるフラッシュ・メモリを製造するのに使用されるメモリ・プロセス技術を使用して、メモリ内部に読み取り側 I C I 軽減プロセスを実装するという犠牲を払って、ターゲット・セルに関するデータだけを送ることは、インターフェース 850 の帯域幅要件を小さくすることが注目される。

#### 【0052】

図 8 および図 9 の I C I 軽減技術の様々な実施形態において使用される静電容量結合係数  $k_x$ 、 $k_y$  および  $k_{xy}$  は、フラッシュ制御システム 810、910 および／またはフラッシュ・メモリ・ブロック 860、960 において計算され得ることが注目される。静電容量結合係数  $k_x$ 、 $k_y$  および  $k_{xy}$  は、それぞれのインターフェース 850、950 上で転送されることが必要である可能性がある。静電容量結合係数は、適応性であることが可能であり、絶えず、時々、または定期的に更新されることが可能であることが注目される。

10

#### 【0053】

例示的な I C I 軽減プロセス 835、990 のより詳細な説明に関しては、例えば、本出願とそれぞれ同時に出願し、参照により本明細書に組み込まれている「Methods and Apparatus for Write-Side Inter-cell Interference Mitigation in Flash Memories」という名称の PCT 特許出願、および「Methods and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memories」という名称の PCT 特許出願を参照されたい。

20

#### 【0054】

(改良されたインターフェース 850、950)

前述したとおり、本発明は、フラッシュ・メモリ・コントローラ 820、920 とフラッシュ・メモリ・アレイ 870、970 の間で改良されたインターフェース 850、950 を提供する。本発明の一態様によれば、ターゲット・セル 710 に関するデータが、クロック信号の第 1 のエッジ（立ち上りエッジなどの）で転送され、さらにその転送されるデータについてのさらなる情報が、クロック信号の第 2 のエッジ（立ち下りエッジなどの）で伝送される。開示されるインターフェースは、消費電力または表面積を大幅に増加させることなしに、伝送されるデータについてのさらなる情報のためのさらなる帯域幅を提供する。

30

#### 【0055】

一般に、インターフェース 850、950 は、本発明の特徴および機能を提供するようにこの場合、変形される、例えば、参照により本明細書に組み込まれている ONFI 2.0 標準に従って実施されることが可能である。このようにして、同一のインターフェース 850、950 が、ソフトデータを処理して、さらなる書き込みデータを送る能力を有さないレガシー・フラッシュ・コントローラ 820、920 のために使用されることが可能である。レガシー・フラッシュ・コントローラ 820、920 は、本発明に従って立ち下りエッジで伝送されるさらなるデータを無視することができる。

40

#### 【0056】

前述したとおり、ONFI バージョン 2.0 は、DDR（ダブル・データレート）技術を使用して、クロック信号の立ち上りエッジと立ち下りエッジの両方でデータを転送する。ONFI バージョン 2.0 は、NAND フラッシュ・インターフェースのデータ伝送容量を増加させたが、パフォーマンスを向上させることができたさらなる情報を伝送するためのさらなる帯域幅はもたらさない。例示的な一実施形態において、ターゲット・セル 710 に関するデータが、クロック信号の第 1 のエッジ（立ち上りエッジなどの）で転送され、さらにソフト読み取りデータおよび隣接する書き込みデータなどの、転送されるデータ

50

についてのさらなる情報が、クロック信号の第2のエッジ（立ち下りエッジなどの）で伝送される。

### 【0057】

#### (A. 書き込みアクセス)

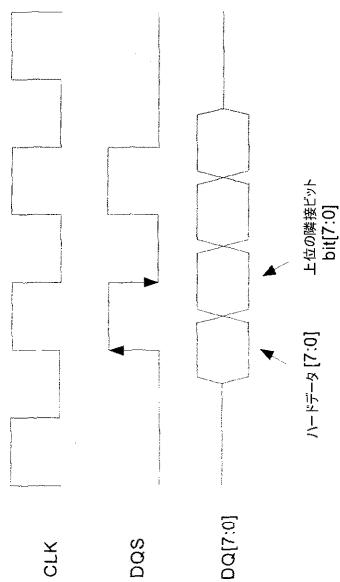

図10は、本発明による書き込みアクセスのための該当する波形を示す。図10に示されるとおり、フラッシュ・メモリのDQSバス上のデータは、通常、CLK信号もしくはDQS（ストローブ）信号、またはその両方を使用してクロック制御される。一般に、DQS信号がイネーブルにされる場合、DQS信号は、CLK信号の各立ち上りエッジ、および各立ち下りエッジにそれぞれ対応する立ち上りエッジおよび立ち下りエッジを有する。

### 【0058】

ONFIバージョン2.0は、クロック信号の立ち上りエッジと立ち下りエッジの両方でデータを転送する。本発明は、ターゲット・セル710に関するデータを、CLK信号の第1のエッジ（立ち上りエッジなどの）で転送し、さらにターゲット・セル710に関する転送されるデータについてのさらなる情報が、CLK信号の第2のエッジ（立ち下りエッジなどの）で伝送される。書き込みアクセスにおいて、立ち下りエッジにおける増加した帯域幅が、フラッシュ・メモリ・コントローラ820、920からフラッシュ・メモリ・アレイ870、970にそれぞれ、さらなる情報（アグレッサ・データ情報などの）を転送するのに使用されることが可能である。例示的な一応用例において、改良されたインターフェース850、950は、IIC軽減のためにターゲット・セル710のアグレッサ・セル720に関する情報の転送を可能にするさらなる帯域幅を提供する。例えば、CLK（またはDQS）信号の立ち下りエッジでラッチされたデータが、ターゲット・セル710に関する上位の隣接ビットを転送することが可能であり、このビットが、IIC軽減プロセス835、990によって、セル間干渉を軽減するように、プログラミングされる電圧を調節するのに使用されることが可能である。

### 【0059】

#### (B. 読み取りアクセス)

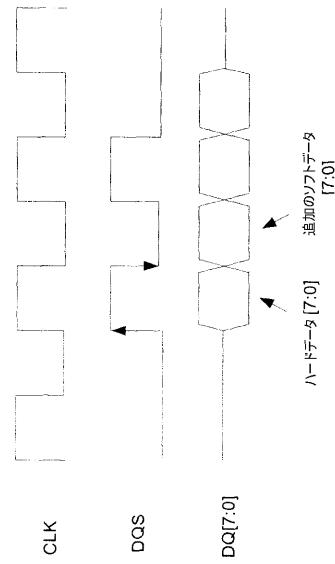

図11は、本発明による読み取りアクセスのための該当する波形を示す。図11に示されるとおり、フラッシュ・メモリのDQSバス上のデータは、通常、CLK信号もしくはDQS（ストローブ）信号、またはその両方を使用してクロック制御される。一般に、DQS信号がイネーブルにされる場合、DQS信号は、CLK信号の各立ち上りエッジ、および各立ち下りエッジにそれぞれ対応する立ち上りエッジおよび立ち下りエッジを有する。

### 【0060】

ONFIバージョン2.0は、クロック信号の立ち上りエッジと立ち下りエッジの両方でデータを転送する。本発明は、ターゲット・セル710に関するデータを、CLK信号の第1のエッジ（立ち上りエッジなどの）で転送し、さらにターゲット・セル710に関して転送されるデータについてのさらなる情報が、CLK信号の第2のエッジ（立ち下りエッジなどの）で伝送される。読み取りアクセスにおいて、立ち下りエッジにおける増加した帯域幅が、立ち上りエッジで伝送されたターゲット・セル710に関するハードデータに関連するターゲット・セル710に関するソフトデータ（例えば、確率情報）を転送するのに使用されることが可能である。この転送は、フラッシュ・メモリ・アレイ870、970からフラッシュ・メモリ・コントローラ820、920に、それぞれ行われる。例示的な一応用例において、改良されたインターフェース850、950は、IIC軽減のためにターゲット・セル710のソフト情報の転送を可能にするさらなる帯域幅を提供する。例えば、CLK（またはDQS）信号の立ち下りエッジでラッチされたデータが、ターゲット・セル710に関するソフトデータを転送することが可能であり、このデータが、IIC軽減プロセス835、990によって、向上した誤り訂正およびセル間干渉軽減のために使用されることが可能である。

### 【0061】

#### (プロセス、システム、および製造品の詳細)

本明細書のいくつかの流れ図は、ステップの例示的な順序を説明するが、その順序が変

10

20

30

40

50

更され得ることも本発明の実施形態である。本発明の代替の実施形態として、アルゴリズムの様々な置換が企図される。本発明の例示的な実施形態は、ソフトウェア・プログラムにおける処理ステップに関連して説明されてきたが、当業者には明白なとおり、様々な機能が、デジタル領域で、ソフトウェア・プログラムにおいて、回路要素もしくは状態マシンによってハードウェアにおいて、またはソフトウェアとハードウェアの両方の組合せにおいて、処理ステップとして実施されることが可能である。そのようなソフトウェアは、例えば、デジタルシグナルプロセッサ、特定用途向け集積回路、マイクロコントローラ、または汎用コンピュータにおいて使用されることが可能である。そのようなハードウェアおよびソフトウェアは、集積回路内で実施される回路内で実施されることが可能である。

## 【0062】

10

このため、本発明の機能は、方法の形態、およびそれらの方法を実施するための装置の形態で実施されることが可能である。本発明の1つまたは複数の態様は、例えば、記憶媒体の中に格納され、マシンにロードされ、さらに／またはマシンによって実行されるか、何らかの伝送媒体を介して伝送されるかにかかわらず、プログラム・コードの形態で実施されることが可能であり、このプログラム・コードが、コンピュータなどのマシンにロードされ、マシンによって実行されると、そのマシンが、本発明を実施するための装置となる。汎用プロセッサ上で実施される場合、それらのプログラム・コード・セグメントは、プロセッサと一緒にになって、特定の論理回路と同様に動作するデバイスを提供する。また、本発明は、集積回路、デジタルシグナルプロセッサ、マイクロプロセッサ、およびマイクロコントローラの1つまたは複数において実施されることも可能である。

20

## 【0063】

当技術分野で知られているとおり、本明細書で説明される方法および装置は、コンピュータ可読媒体を自ら備え、その媒体上にコンピュータ可読コード手段が実現されている製造品として配布されることが可能である。このコンピュータ可読プログラム・コード手段は、コンピュータ・システムと連携して、本明細書で説明される方法を実行する、または本明細書で説明される装置を作成するステップのすべて、または一部を実行するように動作可能である。このコンピュータ可読媒体は、記録可能な媒体（例えば、フロッピー・ディスク、ハードドライブ、コンパクト・ディスク、メモリ・カード、半導体デバイス、チップ、A S I C（特定用途向け集積回路））であっても、伝送媒体（例えば、光ファイバ、ワールド・ワイド・ウェブ、ケーブル、あるいは時分割多元接続チャネル、符号分割多元接続チャネル、または他の無線周波数チャネルを使用する無線チャネルを備えるネットワーク）であってもよい。コンピュータ・システムで使用するのに適した、情報を格納することができる、知られている、または開発される任意の媒体が、使用されることが可能である。コンピュータ可読コード手段は、磁気媒体上の磁気変化、またはコンパクト・ディスクの表面上の高さ変化などの、命令およびデータをコンピュータが読み取ることを許すための任意の機構である。

30

## 【0064】

本明細書で説明されるコンピュータ・システムおよびサーバはそれぞれ、本明細書で開示される方法、ステップ、および機能を実施するように関連するプロセッサを構成するメモリを含む。これらのメモリは、分散型であることも、ローカル型であることも可能であり、これらのプロセッサは、分散型であることも、単体であることも可能である。これらのメモリは、電気メモリ、磁気メモリ、または光メモリとして、あるいは以上のタイプまたは他のタイプの格納デバイスの任意の組合せとして実施されることが可能である。さらに、「メモリ」という用語は、関連するプロセッサによってアクセスされるアドレス指定可能な空間内のアドレスから読み取られる、またはそのようなアドレスに書き込まれることが可能な任意の情報を含するように十分に広く解釈されなければならない。この定義で、ネットワーク上の情報は、関連するプロセッサが、ネットワークからその情報を取得することができるため、やはりメモリの範囲内にある。

40

## 【0065】

本明細書で示され、説明される実施形態および変形形態は、本発明の原理を単に例示す

50

るに過ぎないこと、ならびに様々な変形が、本発明の趣旨および範囲を逸脱することなく、当業者によって実施されることが可能であることを理解されたい。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 1 1 C | 17/00 | 6 1 1 Z |

| G 1 1 C | 17/00 | 6 1 3   |

| G 0 6 F | 12/00 | 5 6 4 A |

(31)優先権主張番号 61/133,675

(32)優先日 平成20年7月1日(2008.7.1)

(33)優先権主張国 米国(US)

(72)発明者 イエン , ジョンソン

アメリカ合衆国 9 4 5 3 9 カリフォルニア , フレモント , ローラル グレン テラス 6 0 0

審査官 菅原 浩二

(56)参考文献 國際公開第2007 / 127678 (WO , A1 )

特開2007 - 207332 (JP , A)

特開平03 - 142800 (JP , A)

特開2002 - 007200 (JP , A)

特表2009 - 510657 (JP , A)

特開2002 - 251886 (JP , A)

特開2006 - 228394 (JP , A)

特開2002 - 324400 (JP , A)

特表2009 - 545093 (JP , A)

特開2007 - 207333 (JP , A)

特開2005 - 025898 (JP , A)

特開2007 - 226853 (JP , A)

特表2010 - 514016 (JP , A)

特表2007 - 500916 (JP , A)

特表2007 - 531959 (JP , A)

特表2009 - 516318 (JP , A)

特開2007 - 157234 (JP , A)

特開平11 - 149786 (JP , A)

特開2002 - 093175 (JP , A)

特開2007 - 018708 (JP , A)

特表2009 - 534785 (JP , A)

特開2007 - 200530 (JP , A)

國際公開第2008 / 019347 (WO , A2 )

特開2008 - 92426 (JP , A)

國際公開第2007 / 132456 (WO , A2 )

特表2003 - 523548 (JP , A)

(58)調査した分野(Int.Cl. , DB名)

G 1 1 C 1 6 / 0 2

G 0 6 F 1 2 / 0 0

G 1 1 C 1 6 / 0 4

G 1 1 C 1 6 / 0 6

G 1 1 C 2 9 / 4 2