(19) 日本国特許庁 (JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2005-294888

(P2005-294888A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H04N 5/335

F 1

HO4N 5/335

HO4N 5/335

テーマコード (参考)

5C024

審査請求 未請求 請求項の数 6 OJ (全 11 頁)

(21) 出願番号 特願2004-102448 (P2004-102448)

(22) 出願日 平成16年3月31日 (2004. 3. 31)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100105924

弁理士 森下 賢樹

(72) 発明者 中森 隆文

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

F ターム (参考) 5C024 AX01 CX13 GY03 HX18 HX23

HX29 HX57

(54) 【発明の名称】 信号処理回路

(57) 【要約】

【課題】 不要な変動信号が存在する状況にあっても効果的な信号処理回路を提供する。

【解決手段】 ディジタル回路部 120 で雑音を適応的に予測し、これを減算信号としてアナログ回路部 110 に出力する。減算信号は D/A 変換器 114 を通して減算回路 111 に入力され、減算回路 111 でアナログ入力信号から雑音が除去される。そして、減算回路 111 の出力が可変増幅回路 112 で増幅され、A/D 変換器 113 でディジタル信号に変換される。

【選択図】 図 2

**【特許請求の範囲】****【請求項 1】**

アナログ信号である入力信号から減算処理を行う減算回路と、

前記減算回路の出力を増幅する増幅回路と、

前記増幅回路の出力をデジタル信号に変換するA / D変換器と、

前記A / D変換器で生成されたデジタル信号を処理するデジタル回路部と、

を具備し、

前記デジタル回路部は、前記入力信号の属性によって変化する不要な信号を生成し、

この不要な信号はアナログ信号に変換された後、前記減算回路に入力されることを特徴とした信号処理回路。

10

**【請求項 2】**

前記デジタル回路部は、前記増幅回路の増幅度を表す増幅度信号を更に生成し、前記増幅度信号の値は、前記増幅回路の出力振幅が前記A / D変換器の入力レベル範囲を超えない範囲で決定されることを特徴とした請求項1に記載の信号処理回路。

**【請求項 3】**

前記不要な信号は、前記入力信号に含まれる雑音に相当する信号を含むことを特徴とする請求項1又は2に記載の信号処理回路。

**【請求項 4】**

前記入力信号はフレーム転送方式CCDから出力された信号であり、前記雑音はスミア雑音を含み、前記デジタル回路部において、前記フレーム転送方式CCDにおける撮像時間と転送時間をもとに前記スミア雑音に相当する信号を生成することを特徴とする請求項3に記載の信号処理回路。

20

**【請求項 5】**

前記デジタル回路部は論理回路とメモリとを備え、

前記メモリに複数枚の画像データを参照画像データとして記憶し、

前記論理回路は前記参照画像データから予測画像データを生成し、

前記不要な信号はこの予測画像データに相当する信号が含まれることを特徴とする請求項1又は2に記載の信号処理回路。

**【請求項 6】**

アナログ信号である入力信号から雑音に相当する信号を減算する減算回路と、

前記減算回路の出力を増幅する増幅回路と、

前記雑音に相当する信号を生成する雑音予測回路と、

を備え、前記雑音予測回路は、前記雑音に相当する信号を、前記入力信号を発生した系に応じて定めることを特徴とする信号処理回路。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像装置等から出力されたアナログ信号を増幅後、デジタル信号に変換する信号処理回路に関する。

40

**【背景技術】****【0002】**

従来より、撮像装置からの入力信号のように、使用条件によりダイナミックレンジが大きく増減するようなアナログ信号をアナログ / デジタル変換 (A / D変換) する場合、A / D変換回路の前段に可変増幅回路を配置し、アナログ信号振幅がA / D変換回路の入力電圧範囲を超えない範囲で、可変増幅回路の増幅度を制御することが一般的である (例えば、特許文献1参照)。これは、デジタル信号へ変換する際の擬似的な分解能を、向上させるためである。

**【0003】**

例えば、A / D変換回路の分解能を10ビット、入力電圧範囲を1Vとする。今、外部からのアナログ入力信号振幅が0.5Vであるとした場合、可変増幅回路の増幅度を2倍

50

に制御し、その信号振幅を1Vに増幅してA/D変換回路に入力する。A/D変換回路は、信号振幅が1Vに増幅されたアナログ信号を10ビットの分解能でデジタル信号に変換する。これは、0.5Vの振幅を持つアナログ信号を擬似的に11ビットの分解能でデジタル信号に変換したことと等価である。

#### 【0004】

また、外部からのアナログ入力信号振幅が0.25Vであった場合、可変増幅回路の増幅度を4倍に制御し、その信号振幅を1Vに増幅して、A/D変換回路で10ビットの分解能でデジタル信号に変換する。この場合、0.25Vの振幅を持つアナログ信号は、擬似的に12ビットの分解能でデジタル信号に変換したことと等価である。このように、入力されたアナログ信号振幅が小さいほど、可変増幅回路の増幅度を上げることにより、その擬似的な分解能を向上させることができる。

#### 【0005】

さて、外部より入力されるアナログ入力信号には、後段のデジタル回路部で必要とする情報（例えば、画素電荷信号など）の他に、オフセット信号や、雑音などの不要な信号が含まれる。一般的に、アナログ入力信号はこの不要な信号を含んだまま可変増幅回路で増幅され、増幅後のアナログ信号がA/D変換回路でデジタル信号に変換される。そして、不要な信号はデジタル回路部で除去される。しかし、このような構成は、擬似的な分解能の向上を無意味に妨げることになる。

#### 【0006】

これに対し、不要な信号を可変増幅回路の前段に設けた減算回路で除去できる構成が非特許文献1のFigure 1.に開示されている。これは、あらかじめ定めた黒レベル・オフセット信号を、アナログ入力信号から減算する構成となっている。

#### 【特許文献1】特開平5-41797号公報

【非特許文献1】Y. Fujimoto et al, "A Switched-Capacitor Variable Gain Amplifier for CCD Image Sensor Interface System", ESSCIRC 2002, pp.363-366, 2002

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

非特許文献1で開示された構成において、可変増幅回路の前段で除去できるのはあらかじめ定められた固定値であり、変動値を除去することはできない。すなわち、不要な変動信号（例えば、固定パターン雑音やスミア雑音といった雑音、もしくは入力画像データと予測画像データとの差分画像データを算出する際の予測画像データに相当する信号など）については、これを含んだまま可変増幅回路で増幅し、A/D変換回路でデジタル信号に変換することになるため、擬似的な分解能の向上が妨げられることになる。

#### 【0008】

本発明はこうした課題に鑑みてなされたものであり、その目的は、不要な変動信号が存在する状況にあっても効果的な信号処理回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

本発明のある態様は、信号処理回路に関する。この回路は、アナログ信号である入力信号から減算処理を行う減算回路と、前記減算回路の出力を増幅する増幅回路と、前記増幅回路の出力をデジタル信号に変換するA/D変換器と、前記A/D変換器で生成されたデジタル信号を処理するデジタル回路部と、を具備し、前記デジタル回路部は、前記入力信号の属性によって変化する不要な信号を生成し、この不要な信号はアナログ信号に変換された後、前記減算回路に入力されることを特徴とする。この態様によれば、不要な信号を増幅回路の前段で減算することができ、より精度の高い信号処理が実現できる。

#### 【0010】

前記入力信号の属性とは、例えば、現在入力されている入力信号が前記撮像装置のどの領域から出力されたか、を表すものを含んでよく、また、現在入力されている入力信号が前記撮像装置のどの画素から出力されたか、を表すものを含んでもよい。その他、入力信

10

20

30

40

50

号の大きさや入力された時間など、入力信号に係わる任意の情報を含めてよい。

#### 【0011】

前記ディジタル回路部は、前記増幅回路の増幅度を表す増幅度信号を更に生成してもよく、この場合、前記増幅度信号の値は、前記増幅回路の出力振幅が前記A/D変換器の入力レベル範囲を超えない範囲で決定されてもよい。これによると、不要な信号が取り除かれた信号に対して、擬似的な分解能をより大きくすることができる。

#### 【0012】

前記不要な信号は、前記入力信号に含まれる雑音に相当する信号を含んでもよい。これによると、入力信号より雑音を除去して増幅回路で増幅するので、雑音を含む入力信号に対し、より精度の高い信号処理が実現できる。

10

#### 【0013】

前記入力信号はフレーム転送方式CCDから出力された信号であってもよく、この場合、前記雑音はスミア雑音を含み、前記ディジタル回路部において、前記フレーム転送方式CCDにおける撮像時間と転送時間をもとに前記スミア雑音に相当する信号を生成してもよい。これによると、フレーム転送方式CCDに特有のスミア雑音を増幅前に除去できるので、フレーム転送方式CCDから出力された信号に対しより精度の高い信号処理が実現できる。

#### 【0014】

前記ディジタル回路部は論理回路とメモリとを備えてもよく、この場合、前記メモリに複数枚の画像データを参照画像データとして記憶し、前記論理回路は前記参照画像データから予測画像データを生成し、前記不要な信号はこの予測画像データに相当する信号が含まれるようにしてよい。これによると、入力信号から予測画像データを減算して得られる差分画像データに対して、より精度の高い信号処理が実現できる。

20

#### 【0015】

本発明の別の態様も、信号処理回路に関する。この回路は、アナログ信号である入力信号から雑音に相当する信号を減算する減算回路と、前記減算回路の出力を増幅する増幅回路と、前記雑音に相当する信号を生成する雑音予測回路と、を備え、前記雑音予測回路は、前記雑音に相当する信号を、前記入力信号を発生した系に応じて定めることを特徴とする。この態様によれば、処理系に応じて雑音信号を予測するので、様々な入力に対してより精度の高い信号処理が実現できる。

30

#### 【0016】

なお、以上の構成要素の任意の組合せや、本発明の構成要素や表現を回路、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

#### 【0017】

本発明によれば、不要な変動信号を可変増幅回路の前段で減算することにより、より精度の高い信号処理が実現できる。

#### 【発明を実施するための最良の形態】

#### 【0018】

以下、本発明の好適な実施の形態をもとに説明する。この実施形態は、撮像装置であるフレーム転送方式CCDより入力されたアナログ入力信号から、ディジタル回路部で予測したスミア雑音を減算した上で増幅し、ディジタル信号に変換する信号処理回路に関する。

40

#### 【0019】

スミア雑音は、撮像装置に強い光が入射された時に、撮像装置の撮像部で発生した電荷が電荷転送部に漏れ、縦方向に光の筋が発生する現象のことである。また、フレーム転送方式CCDにおいては、その構成からさらに特有のスミア雑音が発生する。

#### 【0020】

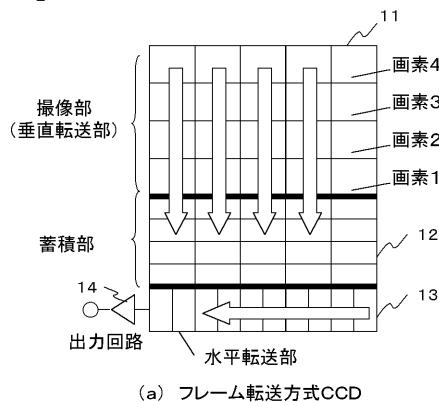

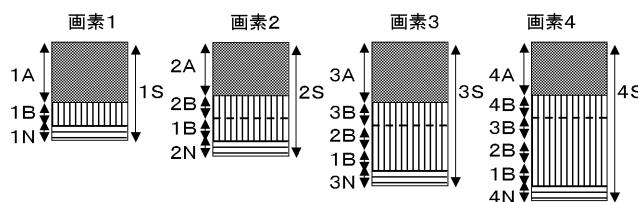

図1(a)は、フレーム転送方式CCDの構成を示した図である。フレーム転送方式CCDは、入射された光を電荷に変換する撮像部11と、光が遮蔽された蓄積部12と、蓄

50

積部から転送された電荷を出力回路14へ転送する水平転送部13と、電荷を電圧に変換し外部へ出力する出力回路14とからなる。撮像部11は垂直転送部を兼ねており、撮像期間に撮像部11で変換された電荷は、撮像期間後に素早く蓄積部12に転送され、これ以上光が入射されるのを防ぐ構造になっている。

【0021】

図1(b)は、蓄積部12に蓄積された各画素における信号電荷の内訳を示した図である。蓄積部12に蓄積された各画素における信号電荷は、画素電荷、スミア雑音、その他の雑音に分けられる。画素電荷は、撮像期間に入射された光によって発生した電荷量であり、これが真の画像情報である。

【0022】

スミア雑音は、撮像期間直後、撮像部11から蓄積部12へ電荷が転送される転送期間中に、撮像部11に入射された光によって生成された電荷が蓄積されたものである。すなわち、このスミア雑音は、フレーム転送方式CCDの撮像部11が垂直転送部を兼用する構造のために発生するもので、撮像期間外に発生した不要な信号電荷である。

その他の雑音は、CCD内で発生する様々な雑音であり、製造プロセスや基板の結晶品質などに起因する固定パターン雑音や、各素子の揺らぎによるランダム雑音を含む。

【0023】

図1(c)は、図1(a)に示した画素1、画素2、画素3、画素4それぞれにおいて、図1(b)の各信号電荷の占める割合を示した図である。この図から撮像部11から蓄積部12へ転送する距離が長くなるほど、スミア雑音が多くなることが見て取れる。これは、転送距離が長ければ転送期間中に光にさらされる時間も長くなるからである。

【0024】

先に説明したように、画素電荷は、撮像期間中に入射された光に応じて発生するのに対し、スミア雑音は、転送期間中に入射された光に応じて発生する。したがって、スミア雑音の大きさは、出力された信号電荷から撮像時間と転送時間とをもとに予測することが可能である。

【0025】

以下、図1(c)を用いて、各画素のスミア雑音の予測方法について説明する。ここでは、撮像期間と転送期間で同じ強度の光が撮像部11に入射されていると仮定する。スミア雑音を予測する場合、蓄積部12に最も近い画素1から予測する。画素1の画素電荷の大きさ1Aとスミア雑音の大きさ1Bとの比(1A:1B)は、撮像時間TAと1画素分を垂直転送するのにかかる時間TBとの比(TA:TB)で表すことができる。したがって、画素1の信号電荷の大きさを1S、他の雑音の大きさを1Nとすると、画素1におけるスミア雑音の大きさ1Bは次式のようになる。

$$1B = TB \cdot (1S - 1N) / (TA + TB) \quad \dots \quad (1)$$

【0026】

次に、画素2のスミア雑音を予測する。画素2に蓄積された電荷は、撮像部11の画素1を通じて蓄積部12に転送される。したがって、蓄積部12に転送された段階で画素2の信号電荷2Sには、画素1のスミア雑音も含まれる。一方、画素2の画素電荷の大きさ2Aと画素2で発生するスミア雑音の大きさ2Bとの比は、画素1と同様、撮像時間TAと1画素分を垂直転送するのにかかる時間TBとの比(TA:TB)で表すことができる。したがって、他の雑音の大きさを2Nとすると、画素2におけるスミア雑音の大きさ2Bは次式のようになる。

$$2B = TB \cdot (2S - 2N - 1B) / (TA + TB) \quad \dots \quad (2)$$

【0027】

画素3についても画素2と同様に求めることができる。すなわち、画素3は、撮像部11の画素1、画素2を通じて蓄積部12に転送されるため、画素1と画素2のスミア雑音1B、2Bが画素3の信号電荷3Sに含まれる。そして、画素3の画素電荷の大きさ3Aと画素3で発生するスミア雑音の大きさ3Bとの比は、撮像時間TAと1画素分を垂直転送するのにかかる時間TBとの比(TA:TB)で表すことできるので、画素3における

10

20

30

40

50

その他の雑音の大きさを  $3N$  とすると、画素 3 におけるスミア雑音の大きさ  $3B$  は次式のようになる。

$$3B = TB \cdot (3S - 3N - 1B - 2B) / (TA + TB) \quad \dots \quad (3)$$

【0028】

以後、垂直方向に順次、各画素のスミア雑音を予測していく。予測の方法は、予測対象となる画素の信号電荷から、その画素のその他の雑音と、蓄積部 12 まで転送される間に通過する撮像部 11 の各画素のスミア雑音とを差し引き、差し引いた値に対して、撮像時間  $TA$  と 1 画素分を垂直転送するのにかかる時間  $TB$  との比 ( $TA : TB$ ) で比例配分する。

【0029】

なお、以上の説明の中で、その他の雑音を差し引いたが、その他の雑音は、予測値として任意に設定した値を差し引いてもよい。この任意に値はゼロも含まれる。また、その他の雑音のうち、固定パターン雑音については測定することが可能であるため、測定によって求められた固定パターン雑音をその他の雑音として差し引いてもよい。もしくは、測定によって求められた固定パターン雑音に、ランダム雑音として任意に設定された値が足し合わされたものを、その他の雑音として差し引いてもよい。これにより、予測したスミア雑音は正確な値ではない可能性もあるが、本発明の実施形態では、スミア雑音の予測値を求めることが重要であり、正確な値を求める必要はない。

【0030】

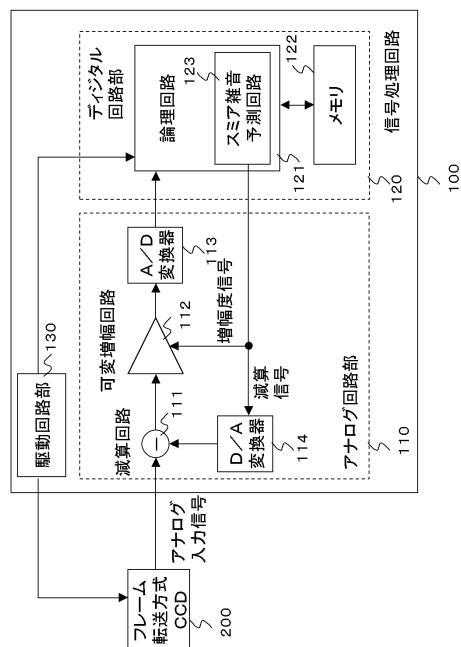

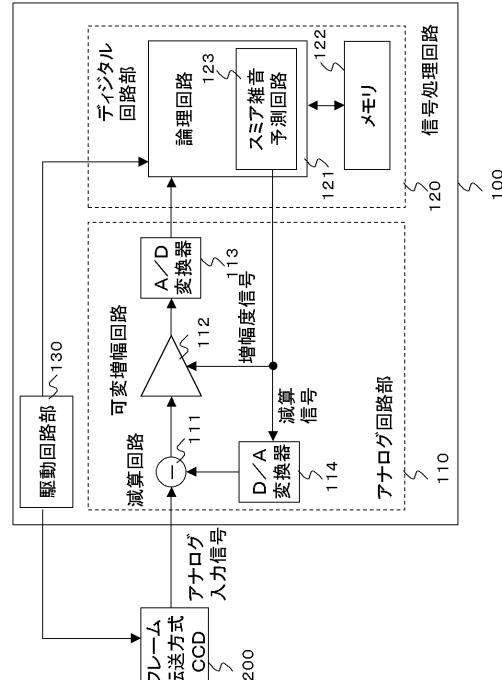

次に、本発明の実施の形態に係る信号処理回路 100 について説明する。図 2 は、本発明の実施の形態に係る信号処理回路 100 の構成を示すブロック図である。信号処理回路 100 は、フレーム転送方式 CCD200 から入力されたアナログ入力信号を増幅し、デジタル信号に変換するアナログ回路部 110 と、アナログ回路部で変換されたデジタル信号に対しデジタル処理を行うデジタル回路部 120 と、フレーム転送方式 CCD200 を駆動する駆動回路部 130 を具備している。なお、信号処理回路 100 とフレーム転送方式 CCD200 により、デジタルカメラを構成することができる。

【0031】

アナログ回路部 110 は、アナログ入力信号を被減算数として減算処理を行う減算回路 111 と、増幅率が変更可能で、減算回路 111 で減算処理されたアナログ信号を増幅する可変増幅回路 112 と、可変増幅回路 112 で増幅されたアナログ信号をデジタル信号に変換する A/D 変換器 113 と、を具備している。また、デジタル回路部 120 より入力された減算信号をアナログ信号に変換する D/A 変換器 114 も備え、D/A 変換器 114 の出力は減算数として減算回路 111 に入力される。さらに、デジタル回路部 120 より入力された増幅度信号が可変増幅回路 112 に入力され、可変増幅回路 112 は増幅度信号で示された増幅度に従って増幅処理を行う。

【0032】

デジタル回路部 120 は、アナログ回路部より入力されたデジタル信号やその他のデジタル信号に対し、所定の処理を施す論理回路 121 と、一時的にデータを記憶するメモリ 122 と、を備える。また、論理回路 121 は、スミア雑音予測回路 123 を含み、スミア雑音の大きさを予測する。スミア雑音予測回路 123 で予測された値は、減算信号としてアナログ回路部 110 へ出力される。また、スミア雑音の予測値にもとに、増幅度回路の出力振幅が前記 A/D 変換器の入力レベル範囲を超えない範囲で増幅度信号の値が決定される。

【0033】

駆動回路部 130 は、フレーム転送方式 CCD200 の駆動信号を生成するほか、フレーム転送方式 CCD200 から出力されているデータがどの画素位置のものであるかを示すアドレスも生成する。このアドレスはデジタル回路部 120 に入力される。また、フレーム転送方式 CCD200 を駆動するためのパラメータである撮像時間  $TA$  と転送時間  $TB$  も駆動回路部 130 からデジタル回路部 120 へ入力される。

【0034】

10

20

30

40

50

信号処理回路 100 の動作を説明する。まず、駆動回路部 130 の駆動信号に従って、フレーム転送方式 CCD200 で撮像が行われた後、フレーム転送方式 CCD200 内で信号電荷が信号電圧に変換され、この信号電圧がアナログ入力信号として 1 画素ずつ出力される。そして、このアナログ入力信号は、はじめは減算回路 111 による減算処理がなされずに可変増幅回路 112 によって増幅され、A / D 変換器によってデジタル信号に変換された後、デジタル回路部 120 に入力される。

#### 【0035】

論理回路 121 に備えられたスミア雑音予測回路 123 は、アナログ回路部 110 より入力されたデジタル信号と、駆動回路部 130 から入力された撮像時間 TA 及び転送時間 TB をもとに、先に述べたスミア雑音の予測方法により、各画素のスミア雑音を予測する。このスミア雑音の予測値は一旦メモリ 122 に記憶される。

#### 【0036】

以上の動作は、フレーム転送方式 CCD のすべての画素について、その信号電圧が読み出されるまで行われ、最終的に全画素のスミア雑音の予測値がメモリ 122 に記憶される。

#### 【0037】

次に、駆動回路部 130 の駆動信号に従って、再度フレーム転送方式 CCD200 で撮像が行われ、各画素の信号電圧がアナログ入力信号として出力される。この時、論理回路 121 は、駆動回路部 130 から出力されるアドレスにしたがって、フレーム転送方式 CCD200 から出力されているアナログ入力信号の画素と同じ画素のスミア雑音を、メモリ 122 から読み出し、それを減算信号として出力する。すなわち、信号電荷の大きさと撮像時間、転送時間に基いて求めた各画素のスミア雑音を、現在入力されているアナログ入力信号がフレーム転送方式 CCD200 のどの画素から出力されたかに応じて選択し、減算信号として出力することになる。つまり、減算信号は、アナログ入力信号の属性である、信号電荷の大きさ、撮像時間、転送時間、及び現在入力されているアナログ入力信号がフレーム転送方式 CCD200 のどの画素から出力されたかによって、適応的に変化する。

#### 【0038】

減算信号は D / A 変換器 114 によってアナログ信号に変換され、このアナログ信号を減算数として

減算回路 111 に入力する。減算回路は被減算数であるアナログ入力信号から減算数を減算する。すなわち、アナログ入力信号からスミア雑音が除去されることになり、減算後のアナログ信号は、ほぼ真の画像情報を表す画素電荷信号で構成される。

#### 【0039】

減算後のアナログ信号は、可変増幅回路 112 に入力され、可変増幅回路 112 の出力が A / D 変換器 113 の入力範囲を超えない範囲で決定された増幅度に従って増幅される。そして、増幅されたアナログ信号を A / D 変換器 113 によってデジタル信号に変換し、デジタル回路部 120 へ出力され、所定の画像処理演算が施される。

このように、不要な変動信号を可変増幅回路の前段で減算することにより、より精度の高い信号処理が実現できる。

#### 【0040】

したがって、以上の構成によれば、信号電荷の大きさ、撮像時間、転送時間、及び現在入力されているアナログ入力信号が撮像装置のどの画素から出力されたかによって変化するスミア雑音を適応的に予測し、これを可変増幅回路で増幅する前にアナログ入力信号から除去できる。これにより、可変増幅回路で増幅する信号は、真の画像情報を表す画素電荷信号でほぼ構成された信号となるため、より精度の高い信号処理が実現できる。

#### 【0041】

なお、この実施の形態において、フレーム転送方式 CCD について説明したが、これに限るものではなく、他の撮像装置で発生したスミア雑音を予測し、アナログ入力信号から減算するように構成してもよい。この場合、スミア雑音の予測方法は、撮像装置の構成に

10

20

30

40

50

合わせて決定される。

【0042】

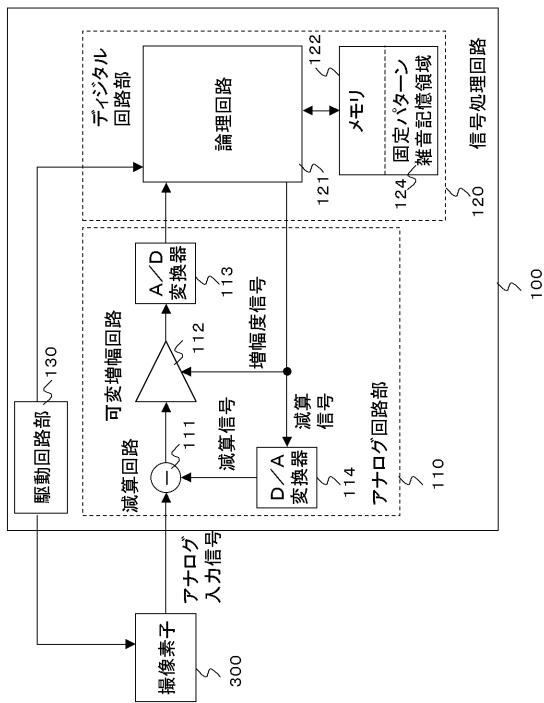

図3は、別の実施の形態に係る信号処理回路100の構成を示したブロック図である。この信号処理回路100は、撮像素子300から入力されたアナログ信号を、デジタル回路部で予測した固定パターン雑音を減算した上で増幅し、デジタル信号に変換する信号処理回路に関する。この構成は、図2に示した信号処理回路100の構成と類似しているので、この実施の形態に特徴的な点のみを説明し、それ以外の説明は省略する。なお、本実施の形態においても、信号処理回路100と撮像素子300により、デジタルカメラを構成することができる。

【0043】

光を遮蔽した状態で、駆動回路部130により生成された駆動信号により、撮像素子300が駆動されると、撮像素子300から出力されるアナログ入力信号は、固定パターン雑音とランダム雑音とが足し合わされたものになる。そこで、まずこのようなアナログ入力信号をアナログ回路部110に入力し、減算回路111による減算処理は行わず、可変増幅回路112、A/D変換器113を通して、デジタル信号に変換して、デジタル回路部120に入力する。

【0044】

論理回路121では、撮像素子300の全画素に対して、入力されたデジタル信号から固定パターン雑音を予測し、メモリ122の固定パターン雑音記憶領域124に記憶する。固定パターン雑音の予測方法としては、ランダム雑音をある一定の値と仮定してデジタル信号から差し引く方法がある。また、入力されたデジタル信号をそのまま固定パターン雑音の予測値としてもよい。また、光を遮蔽した状態のまま、撮像素子300を複数回撮像し、固定パターン雑音とランダム雑音からなる複数枚の画像データを取得した上で、複数の画像データにL P F (Low Path Filter)を通すことにより、ランダム雑音を除去して固定パターン雑音を予測してもよい。

【0045】

つづいて、撮像素子300によって画像を撮像する場合、論理回路121は駆動回路部130から出力されるアドレスにしたがって、撮像素子300から出力されているアナログ入力信号の画素と同じ画素の固定パターン雑音を固定パターン雑音記憶領域124から読み出し、それを減算信号として出力する。すなわち、減算信号は、現在入力されているアナログ入力信号が撮像素子300のどの画素から出力されたか、というアナログ入力信号の属性によって、適応的に変化する。

【0046】

この減算信号はD/A変換器114を通して減算数として減算回路に入力され、減算回路でアナログ入力信号から不要な信号（この実施の形態では固定パターン雑音）を減算した後、減算後のアナログ信号が、可変増幅回路112でA/D変換器113の入力範囲を超えない範囲で決定された増幅度信号に基いて増幅され、A/D変換器113によってデジタル信号に変換されて、デジタル回路部120に出力される。

【0047】

したがって、以上の構成によれば、撮像素子300に固有の固定パターン雑音を適応的に予測し、これを可変増幅回路で増幅する前にアナログ入力信号から除去できる。これにより、可変増幅回路で増幅する信号は、真の画像情報を表す画素電荷信号でほぼ構成された信号となるため、より精度の高い信号処理が実現できる。

【0048】

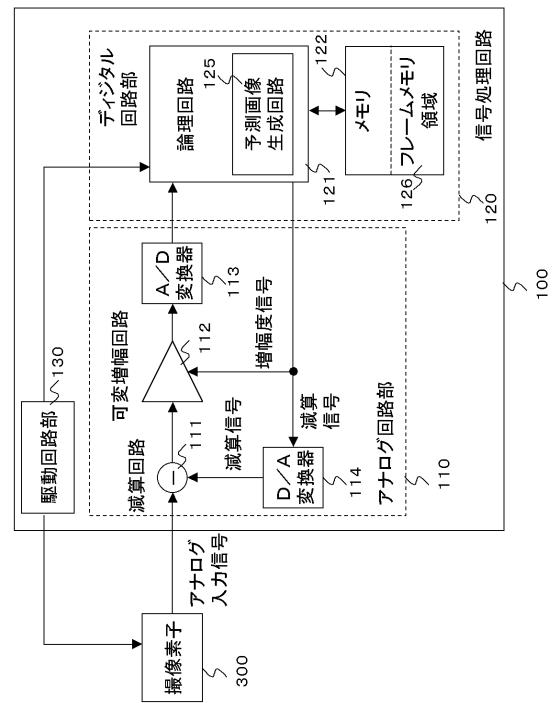

図4は、さらに別の実施の形態に係る信号処理回路100の構成を示したブロック図である。この信号処理回路100は、入力画像データと予測画像データから差分画像データを算出し、この差分画像データに対して演算を行う。従来は、差分画像データの算出をデジタル回路部で行っていたが、本実施の形態では、撮像素子300から入力されたアナログ信号に対して、デジタル回路部で生成した予測画像信号を減算して差分画像信号を得、この差分画像信号を増幅して、デジタル信号に変換する。この構成は、図2に示し

た信号処理回路 100 の構成と類似しているので、この実施の形態に特徴的な点のみを説明し、それ以外の説明は省略する。なお、本実施の形態においても、信号処理回路 100 と撮像素子 300 により、デジタルカメラを構成することができる。

#### 【0049】

デジタル回路部 120 のメモリ 122 には、フレームメモリ領域 126 が設けてあり、そこにあらかじめ複数枚の画像データが参照画像データとして記憶されている。また、論理回路 121 には、予測画像生成回路 125 が備えられている。

#### 【0050】

撮像素子 300 により出力される画像信号に対し、参照画像による予測処理を行わない場合、アナログ回路部 110 は減算回路 111 による減算処理を行うことなく、アナログ入力信号をそのまま可変増幅回路 112 で増幅後、A/D 変換器 113 でデジタル信号に変換して、デジタル回路部 120 へ入力する。

一方、撮像素子 300 により出力される画像信号に対し、参照画像による予測処理を行う場合は、以下のような動作を行う。

#### 【0051】

まず、駆動回路部 130 により生成されたアドレスにしたがって、予測画像生成回路 125 は、現在、撮像素子 300 より入力されているアナログ入力信号が撮像素子 300 のどの領域から出力されたかを判断し、あらかじめフレームメモリ領域 126 に記憶されている参照画像データから、必要な領域の画像データを 1 つ、或いは複数読み出し、所定の処理を施して、予測画像データを生成する。そして、論理回路 121 は、駆動回路部 130 により生成されたアドレスにより、現在入力されているアナログ入力信号の画素位置に合わせて、予測画像の中から対応する画素データを選択する。この画素データに相当する信号が減算信号としてアナログ回路部 110 に出力される。したがって、この減算信号は、現在入力されているアナログ入力信号が撮像素子 300 のどの領域、およびどの画素から出力されたか、というアナログ入力信号の属性によって、適応的に変化する。

#### 【0052】

この減算信号は D/A 変換器 114 を通って減算数として減算回路に入力される。減算回路は、アナログ入力信号から予測画像データに相当する信号を減算して差分画像データを求める。この差分画像データが、可変増幅回路 112 で A/D 変換器 113 の入力範囲を超えない範囲で決定された増幅度信号に基いて増幅され、A/D 変換器 113 によってデジタル信号に変換されて、デジタル回路部 120 に出力される。

#### 【0053】

したがって、以上の構成によれば、予測画像データを適応的に生成し、これを可変増幅回路で増幅する前にアナログ入力信号から除去して差分画像データを求めることができる。この差分画像データを可変増幅回路で増幅するため、差分画像データに対して、より精度の高い信号処理が実現できる。

以上、本発明を実施の形態をもとに説明した。これらの実施の形態は例示であり、これらの各構成要素の組合せにいろいろな変形例が可能のこと、またこうした変形例も本発明の範囲にあることは当業者に理解されるところである。

#### 【0054】

例えば、図 2 の信号処理回路 100 と図 3 の信号処理回路 100 を組み合わせて信号処理回路を構成してもよい。この場合、スミア雑音と固定パターン雑音の両方を、実施の形態で説明した方法に基いてデジタル回路部 120 で予測し、これらの和を減算信号として入力信号から除去できる。また、入力信号に含まれる雑音において、固定パターン雑音がスミア雑音と比して無視できるほど小さい場合は、スミア雑音のみを予測し、これを減算信号としてもよい。或いは、スミア雑音が固定パターン雑音と比して無視できるほど小さい場合は、固定パターン雑音のみを予測して、これを減算信号としてもよい。この構成によれば、入力を発生した系に応じて雑音信号を予測するので、様々な入力に対してより精度の高い信号処理が実現できる。

#### 【図面の簡単な説明】

10

20

30

40

50

## 【 0 0 5 5 】

【図1】(a)、(b)、(c)は、フレーム転送方式CCDの構成と、フレーム転送方式CCDで蓄積された信号電荷の内訳を説明する図である。

【図2】本発明の実施の形態に係る信号処理回路のブロック図である。

【図3】本発明の別の実施の形態に係る信号処理回路のブロック図である。

【図4】本発明のさらに別の実施の形態に係る信号処理回路のブロック図である。

## 【符号の説明】

## 【 0 0 5 6 】

- 100 信号処理回路、

110 アナログ回路部、

111 減算回路、

112 可変増幅回路、

113 A/D変換器、

114 D/A変換器、

120 デジタル回路部、

121 論理回路、

122 メモリ、

123 スミア雑音予測回路、

124 固定パターン雑音記憶領域、

125 予測画像生成回路、

126 フレームメモリ領域、

130 駆動回路部、

200 フレーム転送方式CCD、

300 撮像素子。

10

20

20

## 【図1】

(a) フレーム転送方式CCD

(b) 蓄積部に蓄積された信号電荷の内訳

(c) 信号電荷内訳の画素位置依存性

## 【図2】

【 図 3 】

【 図 4 】