(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5618528号

(P5618528)

(45) 発行日 平成26年11月5日(2014.11.5)

(24) 登録日 平成26年9月26日(2014.9.26)

(51) Int.Cl.

H04N 1/04 (2006.01)

H04N 1/028 (2006.01)

F 1

H04N 1/04 105

H04N 1/028 A

請求項の数 6 (全 12 頁)

(21) 出願番号 特願2009-272798 (P2009-272798)

(22) 出願日 平成21年11月30日 (2009.11.30)

(65) 公開番号 特開2011-119801 (P2011-119801A)

(43) 公開日 平成23年6月16日 (2011.6.16)

審査請求日 平成24年11月29日 (2012.11.29)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 読取装置、読み取り装置の制御方法、および、プログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

ラインごとに画像を読み取り画像信号を生成する画像読み取り部と、前記画像信号を信号処理する信号処理部と、基準クロック信号を生成する基準クロック生成部と、前記基準クロック信号から前記画像読み取り部と前記信号処理部とのいずれかを駆動するための駆動クロック信号を生成するPLL部とを含む読み取り装置であって、

前記PLL部のアンロック状態を検出する検出手段と、

前記画像読み取り部による画像読み取り動作中に前記検出手段が前記PLL部のアンロック状態を検出した場合、前記PLL部のアンロック状態を検出するために要する時間に基づいて導出されたライン分戻した位置から画像を読み取るように前記画像読み取り部を制御する制御手段と、

を備えることを特徴とする読み取り装置。

## 【請求項 2】

前記制御手段は、余裕分の1ライン周期を含む前記PLL部のアンロック状態を検出するためには要する時間に基づいて導出されたライン分戻した位置から画像を読み取るように前記画像読み取り部を制御することを特徴とする請求項1に記載の読み取り装置。

## 【請求項 3】

前記制御手段により戻される位置に相当する第1ラインのデータの蓄積と当該第1ラインの1つ前の第2ラインのデータの転送とが並行して行われていた場合、前記制御手段は、前記第2ラインから画像を読み取るように前記画像読み取り部を制御することを特徴とする

請求項 1 又は 2 に記載の読み取り装置。

【請求項 4】

前記PLL部のアンロック状態を検出するためには、動作状態が不安定になりやすいと判断された回路部分に応じて変更されることを特徴とする請求項1乃至3のいずれか1項に記載の読み取り装置。

【請求項 5】

ラインごとに画像を読み取り画像信号を生成する画像読み取り部と、前記画像信号を信号処理する信号処理部と、基準クロック信号を生成する基準クロック生成部と、前記基準クロック信号から前記画像読み取り部と前記信号処理部とのいずれかを駆動するための駆動クロック信号を生成するPLL部とを含む読み取り装置において実行される読み取り装置の制御方法であって、

10

前記読み取り装置の検出手段が、前記PLL部のアンロック状態を検出する検出工程と、前記読み取り装置の画像読み取り制御手段が、前記画像読み取り部による画像読み取り動作中に前記検出工程において前記PLL部のアンロック状態を検出した場合、前記PLL部のアンロック状態を検出するためには、前記PLL部のアンロック状態を検出する検出手段に基づいて導出されたライン分岐した位置から画像を読み取るように前記画像読み取り部を制御する制御工程と、

を有することを特徴とする読み取り方法。

【請求項 6】

ラインごとに画像を読み取り画像信号を生成する画像読み取り部と、前記画像信号を信号処理する信号処理部と、基準クロック信号を生成する基準クロック生成部と、前記基準クロック信号から前記画像読み取り部と前記信号処理部とのいずれかを駆動するための駆動クロック信号を生成するPLL部とを含む読み取り装置を制御するためのプログラムであって、

20

前記PLL部のアンロック状態を検出する検出手段と、

前記画像読み取り部による画像読み取り動作中に前記検出手段が前記PLL部のアンロック状態を検出した場合、前記PLL部のアンロック状態を検出するためには、前記PLL部のアンロック状態を検出する検出手段に基づいて導出されたライン分岐した位置から画像を読み取るように前記画像読み取り部を制御する制御手段と、

してコンピュータを機能させるためのプログラム。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、画像を読み取る読み取り装置、読み取り装置の制御方法、および、プログラムに関する。

【背景技術】

【0002】

電子機器は、一般的に、何の対策も施さなければ、近くの他の機器の放射する電磁波や、雷のような自然現象、ユーザのオペレーション中に発生した静電気等により、機能低下や誤作動、停止、記録の消失などの影響を受けてしまうおそれがある。従って、各種の電子機器においては、法規制や工業団体による自主規制によって定められた一定以上のEMS (Electro Magnetic Susceptibility: 電磁耐性) 規格を満たすことが義務付けられている。電子機器の設計者はEMS規格と装置の性能を両立させる必要があり、外来電磁波の影響を除去する電気回路上の手法や、電気回路を金属のメカ筐体で囲うなど電磁波が混入し難いような構成上の手法等によって対策を行う。

40

【0003】

電子機器の一つである画像読み取り装置は主に、イメージセンサ、A/D変換機、及び、論理回路やメモリ・CPUを含むデジタル回路で構成されている。それぞれの半導体プロセスは異なるので、それらが1つのICに収められることは稀である。従って、基板上で、ある程度の距離を持って配線される場合が多い。また、1次元のイメージセンサを副走査方向に走査させて原稿の読み取りを行うような画像読み取り装置の場合には特に、イメージセンサとCPUとの間をFFC (Flexible flat cable) ケーブルのような長い配線で接続さ

50

れる場合が多い。例えば、A4サイズの原稿を読み取る画像読取装置においては、数10cmから1m近いFFCケーブルが用いられる。

#### 【0004】

一般的に、基板が複数枚に分割されて、離れた基板間でケーブルを通して電気信号のやり取りを行う場合には、それぞれの基板グランド電位の間でインピーダンスが発生し、高周波的にグランド電位を共通にすることができない。そのため、外部からの電磁波やノイズ、グランド電位の変動に対して弱くなってしまう。また、基板間を接続するケーブルがアンテナとなって外部からの電磁波を受信してしまう傾向が強くなる。

#### 【0005】

このような理由から、画像読取装置は、外来電磁波、静電気等の影響を受けやすい。そのため、画像の読み取り中に装置が誤動作した場合には、その誤動作を認識する構成がないと、読み取った画像の品質が保たれなかつたり失われたりしてしまう。

#### 【0006】

特許文献1には、画像読取装置のPLLの誤動作を検知する手法が記載されている。特許文献1によると、1ラインの同期信号間でPLLが生成するクロック数をカウントして、設定されたカウント数でないとクロックが正常に供給できなかったとしてPLLの異常を判定して装置の動作を停止する。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開2003-324350号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、特許文献1に記載の手法は、画像読取装置に特化したPLLのロック状態（同期状態）の検知方法を提案する手法である。つまり、PLL単体の動作の不良や不安定（同期ずれ状態）を検知することを目的としており、画像読み取り中の突発的なPLLの動作不安定や、読み取り動作のリカバリを考慮したものではない。

#### 【0009】

上記の点に鑑み、本発明は、PLLの同期ずれを検出した場合に、予め定められた分、読み取り位置を戻して画像の読み取りを行う読み取り装置、読み取り装置の制御方法、および、プログラムを提供することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0010】

上記課題を解決するため、本発明に係る読み取り装置は、ラインごとに画像を読み取り画像信号を生成する画像読取部と、前記画像信号を信号処理する信号処理部と、基準クロック信号を生成する基準クロック生成部と、前記基準クロック信号から前記画像読取部と前記信号処理部とのいずれかを駆動するための駆動クロック信号を生成するPLL部とを含む読み取り装置であって、前記PLL部のアンロック状態を検出する検出手段と、前記画像読取部による画像読取動作中に前記検出手段が前記PLL部のアンロック状態を検出した場合、前記PLL部のアンロック状態を検出するために要する時間に基づいて導出されたライン分戻した位置から画像を読み取るように前記画像読取部を制御する制御手段と、を備えることを特徴とする。

40

#### 【発明の効果】

#### 【0011】

本発明によれば、PLLの同期ずれを検出した場合に、予め定められた分、読み取り位置を戻して画像の読み取りを行うことができる。

#### 【図面の簡単な説明】

#### 【0012】

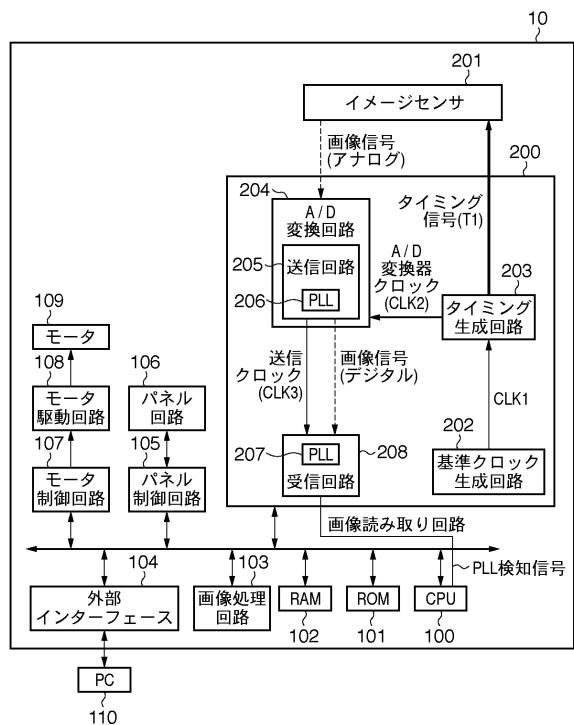

【図1】本発明に係る実施例における読み取り装置の構成の概要を示す図である。

50

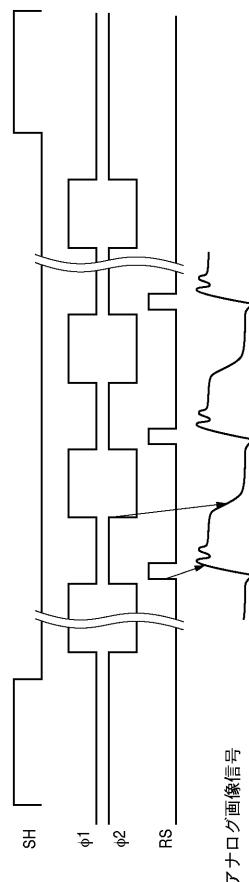

【図2】タイミング信号の一例を示す図である。

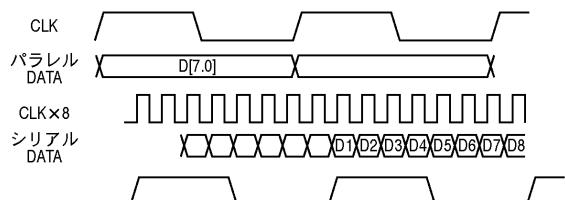

【図3】送信回路と受信回路との間のタイミングチャートを示す図である。

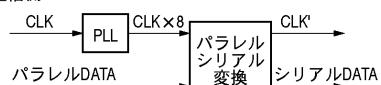

【図4】PLL回路の動作を説明する図である。

【図5】PLLのアンロック状態を検知する動作を説明する図である。

【図6】PLLのアンロック状態を検知する動作を説明する他の図である。

【図7】本実施例における読み取り動作の制御の処理の手順を示す図である。

【図8】画像読み取り回路周辺の他の構成例を示す図である。

【発明を実施するための形態】

【0013】

以下に、本発明を実施するための形態について、図面を参照しながら詳しく説明する。

10

なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

【0014】

図1は、本発明に係る実施例における画像読み取り装置10の構成を示す図である。画像読み取り装置10は、モータ109、モータ109を駆動するモータ駆動回路108、モータ駆動回路108を制御するモータ制御回路107、イメージセンサ(画像読み取り部)201、画像処理回路103、画像読み取り回路200を含む。また、画像読み取り装置10は、CPU100、ROM101、RAM102、PCとデータを送受信するための外部インタフェース104、ユーザが指示を入力するパネル回路106、パネル回路106を制御するパネル制御回路105を含む。画像読み取り回路200は、各部に駆動信号を生成するタイミング生成回路203、タイミング生成回路203用の基準となるクロック信号(以下、単にクロックともいう)を生成する基準クロック生成回路202を含む。また、画像読み取り回路200は、A/D変換回路(信号処理部)204、A/D変換回路204内の送信回路205から送信された画像データを受信する受信回路208を含む。送信回路205及び受信回路208は、それぞれPLL部(以下、単にPLL、又は、PLL回路という)206、207を含み、画像データの転送レートの変換や、シリアル・パラレル変換を行う。PLL207のPLL検知信号は、物理的に配線でCPU100が搭載されたLSIまで接続され、信号レベルは所定のレジスタに保持されるか、CPU100に割り込み信号として入力される。図1に示すタイミング生成回路により生成された信号はPLL用の基準クロック信号として用いられるので、タイミング生成回路は、本実施例における基準クロック生成部の一例である。

20

【0015】

ユーザがパネル回路106上の不図示のキースイッチを押下すると、CPU100が読み取り開始の命令を画像読み取り回路200とモータ制御回路107に送信する。モータ制御回路107は、所定の速度テーブルに基づいてモータ109を加速し、その後、一定の速度とする。イメージセンサ201の走査速度が一定となり所定の読み取り開始位置に移動すると、CPU100の命令でタイミング生成回路203は、イメージセンサ201にタイミング信号T1を供給し、A/D変換回路204にA/D変換器クロックCLK2を供給する。光電変換されたアナログ画像信号は、A/D変換回路204に取り込まれ、デジタルデータに変換された後、送信回路205により受信回路208に送信される。受信回路208は、送信回路205から送信される送信クロックCLK3に基づいて画像信号を受信し、読み取り終了位置にセンサが移動すると画像信号の取り込みを停止する。その後、モータは減速して、一旦停止後、読み取り初期位置まで戻り、画像読み取り処理を終了する。

30

【0016】

本実施例において、画像読み取り中のモータの駆動タイミングは、読み取りデバイス用のタイミング生成回路203を基準にして生成される。ここで、さらに、モータの駆動タイミングからライン同期信号を生成するようにしても良い。A/D変換回路204でデジタル化されたデジタル画像信号は、画像処理回路103に入力され、所定の画像処理を施された後、RAM102に保存されるか、USB等の各種外部インタフェース104を介して、PC110に送信される。

【0017】

40

50

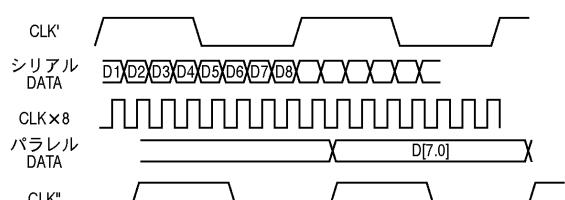

図2は、タイミング生成回路203で生成されるタイミング信号T1の内容を示す図である。タイミング信号T1とは、図2に示されるように、1ラインの同期信号SH、イメージセンサ201の出力を増幅するアンプのリセット信号RS、イメージセンサ201がCCDの場合のアナログシフトレジスタの転送クロック1、2等である。これらは、図1に示される基準クロック生成回路202のクロックCLK1を基準として、タイミング生成回路203内で分周又は遅倍して生成される。また、A/D変換回路204へも上記のタイミング信号T1に同期したクロックCLK2が供給される。従って、イメージセンサ201とA/D変換回路204の間で同期を取って画像信号を取り込むことができる。

## 【0018】

10

受信回路208内にはPLL207が搭載されており、クロックとデータを受信する。図3の(a)、(b)は、クロックとデータの転送方法の一例を示すタイミングチャートである。図3の(a)、(b)において、データ信号はクロック信号の遅倍周波数で動作しており、例えば、受信回路208内でクロック信号を8遅倍してシリアル・パラレル変換を行っているとする。このように構成すると、クロック信号はデータ信号に比べて周波数が一定であるのでクロック信号の高調波成分が機器の外部に不要電磁波として放射しやすいことを考慮して、クロック信号の動作周波数を低く抑えることができる。一旦、送信回路205で低くしたクロック周波数は遅倍してデータ信号の周波数にまで復元する必要があるので、受信回路208内にはクロック遅倍用のPLL207が搭載されている。

## 【0019】

20

送信回路205においても、データ信号をパラレルデータのまま信号を基板上に引き回すと信号数やスペースが増えてしまうため、一旦、シリアル化して動作周波数を上げた状態で伝送する。画像読取回路200の回路構成で、CLK1、CLK3、デジタル画像信号をフラットケーブルを通して伝送するとする。その場合には、信号の駆動ドライバ回路は、通常のCMOS/TTLロジックではなく、LVDsに代表されるような振幅の小さい2本の差動信号を用いることにより不要電磁波の影響を抑えるような構成にすることが多い。なお、送信回路205と受信回路208との間でデータを送受信する方法は、特に図3の(a)、(b)に限定されるものではない。例えば、送信クロックCLK3を遅倍して伝送するのではなくデジタル画像信号と同じ周期で伝送するようにしてもよい。また、データ信号からクロック情報を抽出するクロックリカバリ回路を受信回路208に用いるエンベデッドクロックと呼ばれる手法を用いても良い。その場合には、送信クロックCLK3は不要となる。また、クロックリカバリ回路のPLLにもロック/アンロック状態が発生するため、物理的にクロックそのものを使用しない伝送方法であっても、本実施例を適用できる。

## 【0020】

30

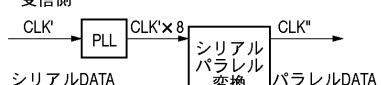

図4は、一般的なPLL回路を用いた周波数シンセサイザの構成の概念を示す図である。図4に示す基準クロック信号Finの周波数がFbackと等しくなる状態を、PLLがロック状態であるという。基準クロック信号Finの入力後、VCOから出力されたFbackがFinよりも速い場合、位相比較器から誤差信号パルスが出力される。このパルスはローパスフィルタで平滑化されVCOに入力される。その結果、負帰還がかかり、VCOの出力が低くなっていくことでFin = Fbackとなりロック状態となる。ここで、図4に示すように、駆動クロック信号foutとFbackの間に分周器を挿入することでfout = Fin × (分周比N)となり、入力のN倍の出力周波数を得ることができる。

## 【0021】

40

以上のように、PLLは、動作の原理上、フィードバックが必要であって、基準クロック信号の入力開始からロック状態に移行するまでに一定の時間を必要とする。また、PLLの状態がロック状態かロック状態でないアンロック状態かを検知する構成は、例えば、位相比較器の誤差出力パルスをモニタする等の方法で実現できる。しかしながら、PLL回路そのもののロック状態を遅延無く検知することはできない場合が多い。PLL回路は

50

、フィードバック回路やアナログ回路を含む。通常、PLL - I C メーカやPLLマクロを提供するベンダは、ある一定時間（数  $10 \mu\text{sec}$  ~ 数  $10 \text{ msec}$  程度）内でロック状態となること、又は、ロック状態の検知回路がロック状態を判定することを保証している。これらの値は、I C やマクロを使用する場合に、データシートから事前に知ることが可能であり、実測することも可能である。本実施例ではPLL回路を例にしているが、VCOの代わりにディレイラインを用いるDLL(Delay Locked Loop)回路を用いてもよい。DLL回路においても、PLLと同様に入力されるクロックの状態に依存してロック状態、アンロック状態が発生するので同様に本実施例を適用できる。PLL回路のロック／アンロック検知機能は、例えば電源投入時などにPLLが安定動作していることを確認するためのフェイルセーフとして存在している。本実施例においては、PLL回路の所定のロック／アンロック検知機能から、PLLに入力された送信クロックCLK3の動作状態の安定／不安定を判定することによって、画像不良が発生していることを予測する。そして、動作状態が不安定と判定した場合には、読み取り動作を中断し、動作不安定状態で読み取ったラインの手前まで戻って読み取り動作をやり直す。その結果、最終的な画像の出力として正しい画像データのみを取り込むことができる。

#### 【0022】

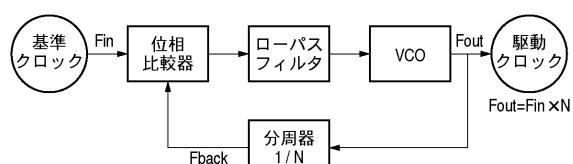

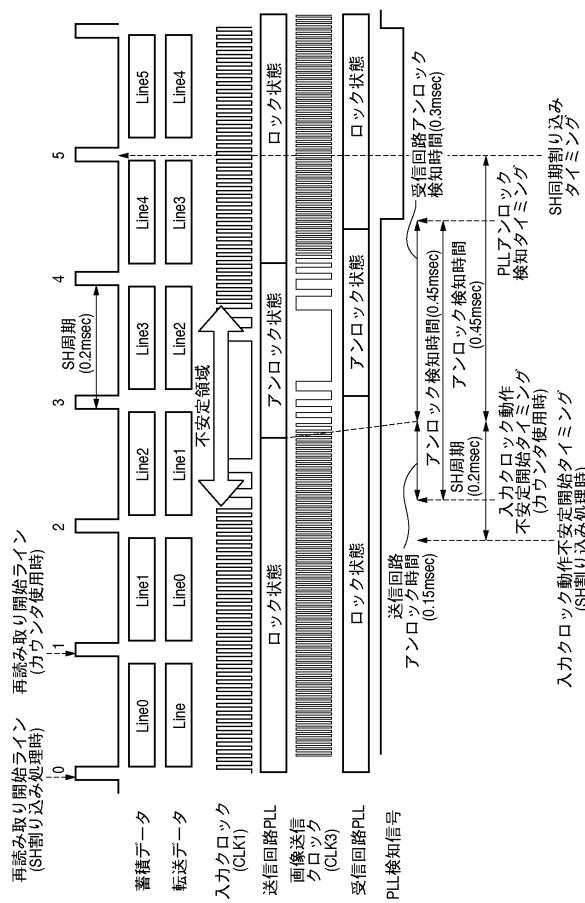

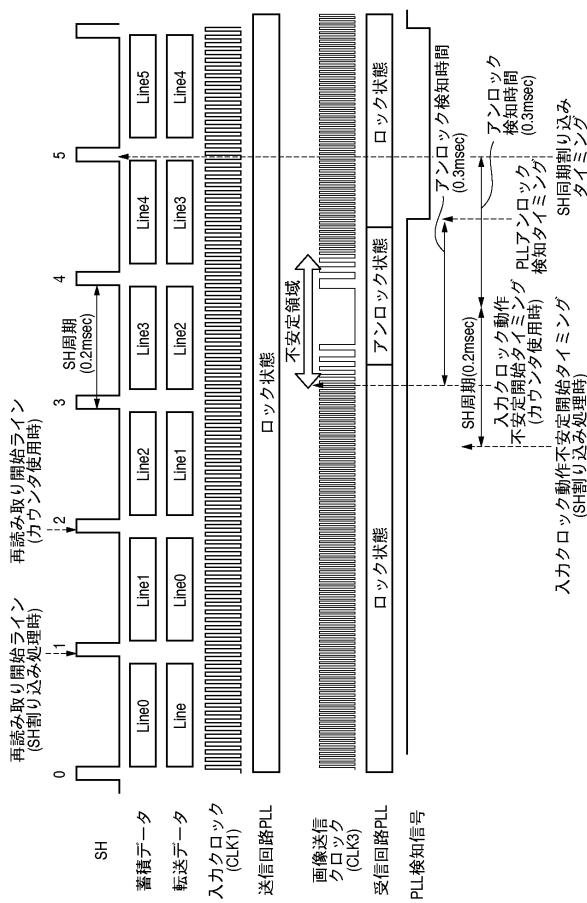

図5は、図1に図示する入力クロックCLK1が不安定になった場合の画像読み取り回路200における各信号のタイミングチャートを示す図である。PLLロック検知信号は、Hレベルでロック状態、Lレベルでアンロック状態を示す。ここで、入力クロックCLK1が不安定となってからアンロック状態を検知するまでの時間（図5に示すアンロック検知時間）を  $0.45 \text{ msec}$  、1ラインの同期信号SHは  $0.2 \text{ msec}$  周期と仮定する。

#### 【0023】

図1に示すようにCLK1とCLK3の間には送信回路205のPLL206が存在しているので、アンロック検知時間  $0.45 \text{ msec}$  は「（送信回路アンロック時間）+（受信回路アンロック検知時間）」となる。また、ここで、受信回路アンロック検知時間は、受信回路208のPLL207についての「（ロック状態からアンロック状態への移行時間）+（アンロック検知回路の検知時間）」となる。

#### 【0024】

CPU100がSH毎の割り込みで処理内容を変更することができるファームウェアが構成されている場合に、図5に示すように、4番目と5番目のSHの間で、PLLアンロック状態が検知されている。つまり、CPU100は、5番目のSHの割り込み時にPLL207のアンロック状態を検出する。CPU100により認識されると、通常の読み取り動作をストップし、読み取り動作が不安定となった場所まで戻り、読み取り動作をやり直す。

#### 【0025】

図5に示すように、5番目のSHの割り込み時でPLL207のアンロック状態を検出している。そのため、4番目と5番目のSH間のどのタイミングでアンロック状態を検出したかは判定していない。従って、本実施例においては、1ライン（SH周期）分の余裕をもたせることとして読み取り動作をやり直すタイミングを特定する。即ち、本実施例においては、（アンロック検知最大時間  $0.45 \text{ msec}$  ）+（1ライン同期信号周期  $0.2 \text{ msec}$  ）分戻ったタイミングでデータの蓄積と転送を行っていたラインのデータを不良データの始まりと判定する。つまり、図5に示すように、1番目と2番目のSHの間で入力クロックCLK1の動作が不安定になったと判定する。

#### 【0026】

CCDに代表される汎用的なイメージセンサが構成されている場合には、画像信号電荷の蓄積と転送は並行に動作する。図5に示すようなタイミングでクロックCLK1が不安定になった場合には、LINE1のデータの蓄積とLINE0のデータの転送は並行して行われている。従って、その場合には、LINE0のデータの蓄積から戻ってやり直す。また、PLL検知信号のアンロック状態のタイミングを知る構成としては、カウンタで計測して入力クロックの動作不安定タイミングを見積もるようにも良い。その場合には

10

20

30

40

50

、アンロック検知時間分戻ったタイミングが入力クロックの動作不安定開始タイミングとなる。

【0027】

図6は、図1に図示する送信クロックCLK3が不安定となった場合の画像読取回路200における各信号のタイミングチャートを示す図である。図6においては、送信クロックCLK3のみが不安定になっているため、送信用PLL206は、ロック状態のまま安定動作している。従って、アンロック検知時間は、受信回路208におけるアンロック検知時間のみを考慮すればよい。ここで、受信回路208のアンロック検知時間は、図5と同様に、受信回路208のPLL207の「(ロック状態からアンロック状態への移行時間) + (アンロック検知回路の検知時間)」である。図5の場合と同様に、5番目のSHの割り込みのタイミングでCPU100がアンロック状態を検出すると、アンロック検知時間とSH周期分戻ったタイミング、即ち、図6に示す2番目と3番目のSHの間で送信クロックCLK3が不安定となったと判定する。その結果、LINE1のデータの蓄積から戻ってやり直す。

10

【0028】

ここで、もし、回路・配線のレイアウト構成上、送信クロックCLK3の動作が不安定になることが事前に分かっているのであれば、図5の場合に比べてアンロック検知時間は短く特定することも可能である。図6に示すようなSH周期とアンロック検知時間であれば、図5に比べて1SH周期分、戻る量を減らすことができる。

20

【0029】

図5、図6の構成だけに関わらず、クロックCLK1から、受信回路208のPLL207に最終的に入力されるクロックCLK3までの間でどの回路部分が不安定になりやすいかに応じてアンロック検知時間を変更するようにしてもよい。不安定箇所が特定部分に限定できない場合は、受信回路208のPLL207に入力されるクロックCLK3を生成する元になるクロックCLK1が不安定になったと想定して、アンロック検知時間を見積もればよい。そのようにすると、画像読取動作中に、画像読取回路200のいずれの部分で動作が不安定になったとしても、現在の読取位置から最適な位置までのライン分戻して、画像読み取りを行うことができる。

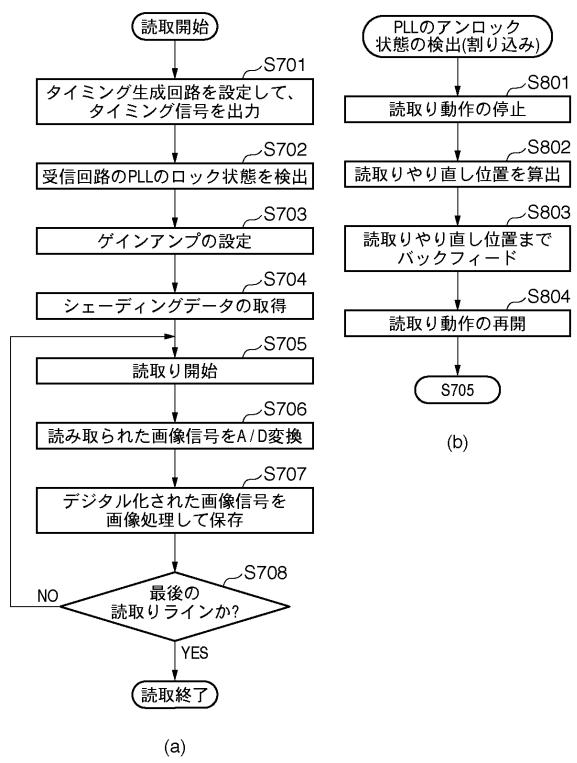

【0030】

図7の(a)は、本記録装置による通常の読取動作の手順を示すフローチャートであり、図7の(b)は、PLLがアンロック状態となった場合に、その旨の割り込みを検出して行われる画像読取制御の処理の手順を示すフローチャートである。まず、図7の(a)を説明する。ユーザが、例えば、パネルから不図示の読取開始ボタンを押すと、CPU100は、タイミング生成回路203に所定の読み取り動作のためのタイミング設定を行う(S701)。すると、基準クロック生成回路202から一定の周波数でCLK1がタイミング生成回路203に出力される。タイミング生成回路203は、タイミング信号T1をイメージセンサ201に出力し、A/D変換器クロックCLK2をA/D変換回路204に出力する。次に、送信回路205のPLL206は、所定の時間後、ロック状態となって送信クロックCLK3を受信回路208に出力する。続けて、所定の時間後、受信回路208のPLL207がロック状態となる。CPU100は、所定時間待機するか、ロック状態を示す信号のポーリングにより、受信回路208のPLL207のロック状態を検出する(S702)。検出後、不図示の読取用光源とA/D変換回路204のゲインアンプの設定を行い、出力を所望のレンジに調整する(S703)。その後、シェーディングデータの取得を行い(S704)、モータ109を動作させて読み取り動作を開始する(S705)。受信回路208で受信した画像信号は、A/D変換回路204においてA/D変換され(S706)、画像処理回路103において画像処理された後、RAM等の記憶領域に格納される(S707)。このときにRAM102に保存されるか、画像処理回路103で所定の画像処理が行われた後にUSB等の外部インターフェース104を介して、PC110に転送されてもよい。また、記憶領域に画像処理された画像信号は、その読み取られた対象のラインについての情報(ライン数等)も合わせて格納する。現在の読み

30

40

50

取られた対象のラインが最後の読み取りラインであるか否かが判定される(S708)。ここで、最後の読み取りラインであると判定された場合には、読み取りを終了し、最後の読み取りラインでないと判定された場合には、S705から処理を繰り返す。

### 【0031】

次に、図7の(b)を説明する。図7の(a)のS705における読み取り開始後、CPU100がPLLのアンロック状態を検出すると、図7の(b)に示されるような割り込み処理を行う。アンロック状態を検知した場合に、モータ109の駆動を停止して、読み取り動作を停止する。このとき、モータ109は、所定の加減速テーブルに基づいて停止する(S801)。CPU100は、前述したアンロック検知時間及びSH周期と、S707において格納された現在のライン情報とから、再読み取り位置を算出する(S802)。その後、イメージセンサ201は、モータ109の加減速領域を考慮して再読み取り位置の手前までのライン分バックフィードし(S803)、加速および定速動作後、再読み取り開始位置に達した場所から読み取り動作を再開する(S804)。この後は、図7の(a)のS705からの処理と同じである。このとき、受信回路208のPLL207が再度ロック状態となつたことを確認してから読み取り動作をやり直しても良いが通常はバックフィード時間が十分長いため、PLL207は確実にロック状態となる場合が多い。なお、再読み取りされた画像データは、動作の不安定を検知後に取り込んだ画像データのメモリ領域の最初のメモアドレスから続けて上書きすればよい。そして、所定の読み取り領域まで読み取り動作が終了すると、モータ109はバックフィードして初期位置まで戻る。

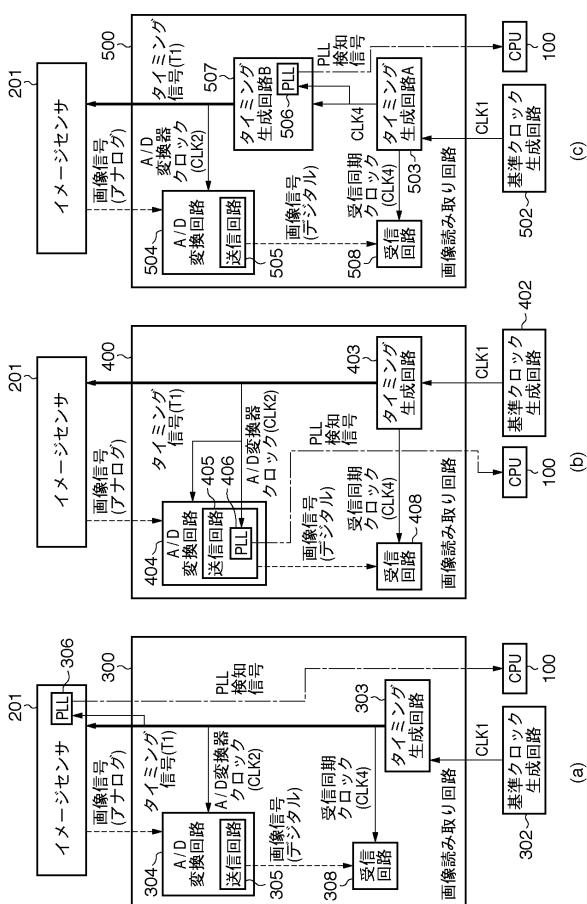

### 【0032】

図8の(a)は、画像読み取り回路の周辺についての他の構成例を示す図である。画像読み取り回路300以外の構成要素は、図1と同じである。図8の(a)に示す画像読み取り回路300は、各部に駆動信号を生成するタイミング生成回路303、タイミング生成回路303で用いられる基準となるクロックを生成する基準クロック生成回路302、A/D変換回路304を含む。A/D変換回路304の送信回路305から送信された画像データは受信回路308で受信される。本構成においては、イメージセンサ201、A/D変換回路304、受信回路308は、タイミング生成回路303で生成された駆動信号に同期して動作する。イメージセンサ201が実装された基板の中に、PLL306が搭載されている。PLL306は、タイミング信号T1内の1、2またはこれらに同期したクロックにより動作する。PLL306のPLL検知信号は、物理的に配線でCPU100が搭載されたLSIまで接続され、信号レベルは所定のレジスタに保持されるか、CPU100に割り込みとして入力される。本構成では、タイミング信号T1の不安定を検知して、再読み取り動作を行う。再読み取り動作を行う処理の手順と各信号のタイミングは、図5、図7と同じである。即ち、タイミング信号T1の不安定となつた箇所からアンロック検知時間が経過し、その後続のSHの割り込み時にCPU100がPLL306のアンロック状態を検知する。再読み取り動作を行うタイミングの算出は、既に説明したとおり、アンロック検知時間とSH周期分戻ったタイミングとして求められる。

### 【0033】

図8の(b)の構成について説明する。画像読み取り回路400以外の構成要素は、図1と同じである。画像読み取り回路400は、各部に駆動信号を生成するタイミング生成回路403、タイミング生成回路403で用いられる基準となるクロックを生成する基準クロック生成回路402、A/D変換回路404を含む。A/D変換回路404の送信回路405から送信された画像信号は、受信回路408で受信される。イメージセンサ201、A/D変換回路404、受信回路408は、タイミング生成回路403で生成された駆動信号に同期して動作する。A/D変換回路404の送信回路405にはPLL406が搭載され、CLK2により動作する。PLL406のPLL検知信号は、物理的に配線でCPU100が搭載されたLSIまで接続され、信号レベルは所定のレジスタに保持されるか、CPU100に割り込みとして入力される。本構成では、CLK2の不安定を検知して、再読み取り動作を行う。再読み取り動作を行う処理の手順と各信号のタイミングは、図5、図7と同じである。即ち、CLK2の不安定となつた箇所からアンロック検知時間が経過し、

10

20

30

40

50

その後続の S H の割り込み時に C P U 1 0 0 が P L L 4 0 6 のアンロック状態を検知する。再読み取り動作を行うタイミングの算出は、既に説明したとおり、アンロック検知時間と S H 周期分戻ったタイミングとして求められる。

#### 【 0 0 3 4 】

図 8 の ( c ) の構成について説明する。画像読取回路 5 0 0 以外の構成要素は、図 1 と同じである。画像読取回路 5 0 0 は、タイミング生成回路 A 5 0 3 とタイミング生成回路 B 5 0 7 を含む。タイミング生成回路 B 5 0 7 は、各部に駆動信号を生成する。タイミング生成回路 A 5 0 3 は、タイミング生成回路 B 5 0 7 に所定のクロック C L K 4 を供給する。また、基準クロック生成回路 5 0 2 は、タイミング生成回路 A 5 0 3 に用いられる基準となるクロックを生成する。A / D 変換回路 5 0 4 内の送信回路 5 0 5 から送信された画像信号は受信回路 5 0 8 で受信される。イメージセンサ 2 0 1 、 A / D 変換回路 5 0 4 は、タイミング生成回路 B 5 0 7 で生成された駆動信号に同期して動作している。

10

#### 【 0 0 3 5 】

タイミング信号 T 1 の本数が多かったり周波数が高い場合、タイミング生成回路を 2 つに分け、イメージセンサの近くにタイミング生成回路 B 5 0 7 を配置することで、フラットケーブルのピン数を削減したり、外からの電磁波に弱い信号を減らすことができる。ただし、図 8 における C L K 4 はフラットケーブルを通る構成となる。タイミング生成回路 B 5 0 7 には P L L 5 0 6 が搭載され、 C L K 4 に基づいて動作する。 P L L 5 0 6 の P L L 検知信号は、物理的に配線で C P U 1 0 0 が搭載された L S I まで接続され、信号レベルは所定のレジスタに保持されるか、 C P U 1 0 0 に割り込み信号として入力される。本構成では C L K 4 の不安定を検知して、再読み取り動作を行う。再読み取り動作を行う処理の手順と各信号のタイミングは、図 5 、図 7 と同じである。即ち、 C L K 4 の不安定となった箇所からアンロック検知時間が経過し、その後続の S H の割り込み時に C P U 1 0 0 が P L L 5 0 6 のアンロック状態を検知する。再読み取り動作を行うタイミングの算出は、既に説明したとおり、アンロック検知時間と S H 周期分戻ったタイミングとして求められる。

20

#### 【 0 0 3 6 】

図 8 の ( a ) 、 ( b ) 、 ( c ) に示すように、各場合において、イメージセンサ 2 0 1 、 A / D 変換回路 4 0 4 、タイミング生成回路 B 5 0 7 に P L L が構成されている。しかし、複数の箇所に P L L を構成するようにしてもよい。また、 P L L を複数構成し、図 1 で示すように一方が他方のクロックを元に動作する場合は、元となるクロックの不安定開始時間を予測するようにすれば良い。

30

#### 【 0 0 3 7 】

##### < その他の実施例 >

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（または C P U や M P U 等）がプログラムを読み出して実行する処理である。

【図1】

【図2】

【図3】

送信側

(a)

受信側

(b)

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 北井 聰

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 宮島 潤

(56)参考文献 特開2003-324350 (JP, A)

特開平9-149202 (JP, A)

特開2003-69794 (JP, A)

特開平1-272372 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/04 - 1/207

G06T 1/00

H04N 1/00

H04N 1/024 - 1/036