(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4851694号

(P4851694)

(45) 発行日 平成24年1月11日(2012.1.11)

(24) 登録日 平成23年10月28日(2011.10.28)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 652H

H01L 29/78 658A

H01L 29/78 658E

H01L 29/78 658B

請求項の数 3 (全 13 頁)

(21) 出願番号

特願2004-243613 (P2004-243613)

(22) 出願日

平成16年8月24日 (2004.8.24)

(65) 公開番号

特開2006-66421 (P2006-66421A)

(43) 公開日

平成18年3月9日 (2006.3.9)

審査請求日

平成19年7月18日 (2007.7.18)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100109900

弁理士 堀口 浩

(72) 発明者 山下 敦子

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72) 発明者 松田 哲朗

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の半導体基板の主面上に、第1導電型の第1半導体ピラー層と前記第1半導体ピラー層に隣接した第2導電型の第2半導体ピラー層と前記第2半導体ピラー層に隣接した第1導電型の第3半導体ピラー層の各下側領域を形成する工程と、

前記第1乃至第3半導体ピラー層の各下側領域上にそれぞれ前記第1乃至第3半導体ピラー層と同じ導電型で、且つキャリア濃度が高い半導体ピラー層を積み上げ、第1乃至第3半導体ピラー層の各上側領域を形成する工程と、

前記第2半導体ピラー層の上側領域の主面上に第2導電型の半導体ベース層を形成し、前記半導体ベース層に絶縁ゲート電界効果トランジスタを形成する工程と

を有することを特徴とする半導体装置の製造方法。

## 【請求項 2】

前記第1乃至第3半導体ピラー層の各下側領域は、前記半導体基板の主面上に第1導電型の第1半導体層を形成して前記第1半導体層の所定の領域へ第2導電型の不純物を選択的に注入する工程を繰り返した後、熱処理を施して前記第2導電型の不純物が拡散した領域を上下相互に接続することで形成し、

前記第1乃至第3半導体ピラー層の各上側領域は、前記第1半導体層上に前記第1半導体層よりキャリア濃度の高い第1導電型の第2半導体層を形成し、前記所定の領域上の前記第2半導体層に前記第1半導体層に達するトレンチを形成した後、前記トレンチ内に前記第2導電型の不純物が拡散した領域よりキャリア濃度の高い第2導電型の第3半導体層

を埋め込むことで形成することを特徴とする請求項 1 に記載の半導体装置の製造方法。

【請求項 3】

前記第 1 乃至第 3 半導体ピラー層の各下側領域は、前記半導体基板の主面上に第 1 導電型の第 1 半導体層を形成して前記第 1 半導体層の所定の領域へ第 2 導電型の不純物を選択的に注入する工程を繰り返した後、熱処理を施して前記第 2 導電型の不純物が拡散した領域を上下相互に接続することで形成し、

前記第 1 乃至第 3 半導体ピラー層の各上側領域は、前記第 1 半導体層上に第 2 半導体層を形成し、前記第 2 半導体層に前記第 1 半導体層に達するトレンチを前記第 2 導電型の不純物を選択的に注入した領域の両側に形成した後、前記トレンチの側面に第 1 導電型の不純物、および前記第 1 導電型の不純物より拡散係数の大きい第 2 導電型の不純物を注入して熱処理することで形成することを特徴とする請求項 1 に記載の半導体装置の製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に係り、特にパワーMOSトランジスタを有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来、プレーナ型のパワーMOSトランジスタでは電流経路と耐圧を維持する領域が同一なので、高耐圧化のためにエピタキシャル層の膜厚を厚くするとオン抵抗が上がり、逆にエピタキシャル層の膜厚を薄くしてオン抵抗を下げると耐圧も下がるという、相反する関係が存在し、両者をともに満足することが困難であった。

20

【0003】

最近、電流経路と耐圧を維持する領域を分離したスーパージャンクション (Super Junction) 構造と呼ばれるパワーMOSトランジスタが提案されている。このパワーMOSトランジスタでは、電流経路となるn型半導体ピラー層と電流仕切り領域となるp型半導体ピラー層が水平方向に交互に配列され、p型半導体ピラー層の上部表面に形成されたp型半導体ベース層にn型ソース領域およびゲート電極が形成されている。(例えば、特許文献1または特許文献2参照。)。

【0004】

30

これにより、オン抵抗はドレイン電流をn型半導体ピラー層に流しているのでn型半導体ピラー層のキャリア濃度に依存し、一方、耐圧は空乏層を水平方向へ伸ばしているのでn型およびp型半導体ピラー層のキャリア濃度および幅に依存する。

【0005】

特許文献1に開示されたパワーMOSトランジスタでは、n型シリコン(Si)基板に形成した厚いn型エピタキシャルSi層にSi基板に達する深いトレンチを形成した後、トレンチの側面にp型不純物として硼素(B)とn型不純物としてBより拡散係数の小さい砒素(As)を同時に注入して熱処理を施し、トレンチで挟まれた領域にBとAsを同時に拡散させることにより、トレンチで挟まれた領域の中央部にp型半導体ピラー層と外周部にn型半導体ピラー層とを同時に形成している。

40

【0006】

特許文献2に開示されたパワーMOSトランジスタでは、n型Si基板に薄いn型エピタキシャルSi層を形成する工程とn型エピタキシャルSi層の所定の位置にp型不純物としてBを注入する工程を交互に繰り返して厚い半導体層を形成した後、熱処理を施して半導体層内にBを拡散させることにより、Bが拡散した領域が上下相互に接続されたp型半導体ピラー層を形成し、半導体層内のBが拡散していない領域をn型半導体ピラー層としている。

【0007】

特許文献1または特許文献2に開示されたパワーMOSトランジスタでは、半導体ピラー層の上側領域と下側領域のキャリア濃度が等しく設定され、低オン抵抗化と高耐圧化の

50

両立を図っている。

【0008】

然しながら、半導体ピラー層の上側領域と下側領域のキャリア濃度が等しいと半導体ピラー層のチャージアンバランスマージンが狭いので、設計通りの半導体ピラー層のキャリア濃度と幅が得られない場合に、パワーMOSトランジスタの耐圧が低下するという問題がある。

【0009】

特に、パワーMOSトランジスタの単位面積当たりのオン抵抗を下げるために、半導体ピラー層の幅を狭くし、キャリア濃度を高くするほどパワーMOSトランジスタの耐圧の低下が顕著になる。

10

【0010】

ここで、チャージアンバランスマージンとは、n型半導体ピラー層のキャリア濃度と幅の積で表されるピラーチャージ量 $Q_n$ とp型半導体ピラー層のキャリア濃度と幅の積で表されるピラーチャージ量 $Q_p$ とが等しい、すなわち完全空乏化できる理想の状態からのずれ( $Q_n - Q_p$ ) /  $Q_n$ に対して、耐圧を低下させることなく、半導体ピラー層のキャリア濃度および幅の設計許容値がどれだけあるかを意味している。

【0011】

パワーMOSトランジスタの製造工程での種々のばらつきを考慮すると、チャージアンバランスマージンは±15%以上あることが望まれている。

【特許文献1】特開2002-170955号公報(5-8頁、図3)

20

【特許文献2】特開2001-119022号公報(4-5頁、図1)

【発明の開示】

【発明が解決しようとする課題】

【0012】

本発明は、十分なチャージアンバランスマージンを得るのに好適な構造を有する半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0014】

また、本発明の一態様の半導体装置の製造方法では、第1導電型の半導体基板の主面上に、第1導電型の第1半導体ピラー層と前記第1半導体ピラー層に隣接した第2導電型の第2半導体ピラー層と前記第2半導体ピラー層に隣接した第1導電型の第3半導体ピラー層の各下側領域を形成する工程と、前記第1乃至第3半導体ピラー層の各下側領域上にそれぞれ前記第1乃至第3半導体ピラー層と同じ導電型で、且つキャリア濃度が高い半導体ピラー層を積み上げ、第1乃至第3半導体ピラー層の各上側領域を形成する工程と、前記第2半導体ピラー層の上側領域の正面に第2導電型の半導体ベース層を形成し、前記半導体ベース層に絶縁ゲート電界効果トランジスタを形成する工程と、を有することを特徴としている。

30

【発明の効果】

【0015】

本発明によれば、十分な耐圧と信頼性の高いパワーMOSトランジスタを備えた半導体装置を提供することができる。

40

【発明を実施するための最良の形態】

【0016】

以下、本発明の実施例について図面を参照しながら説明する。

【実施例1】

【0017】

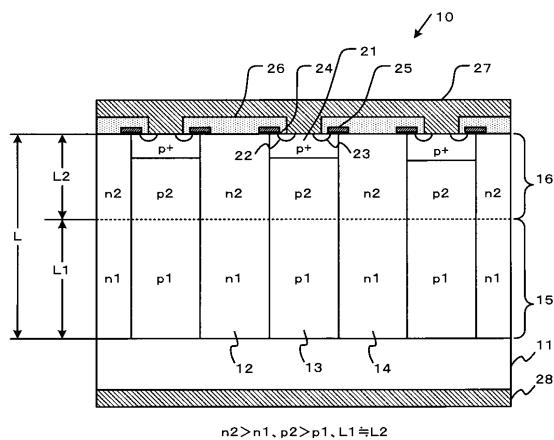

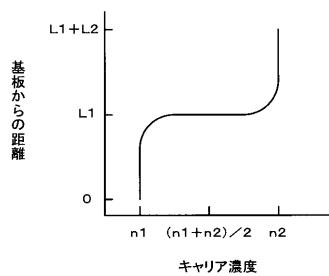

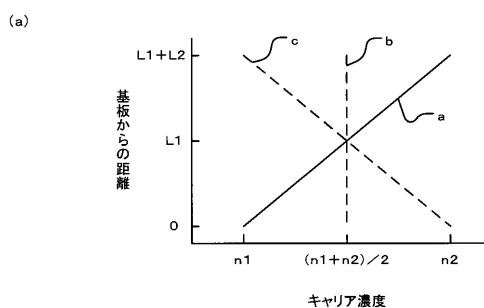

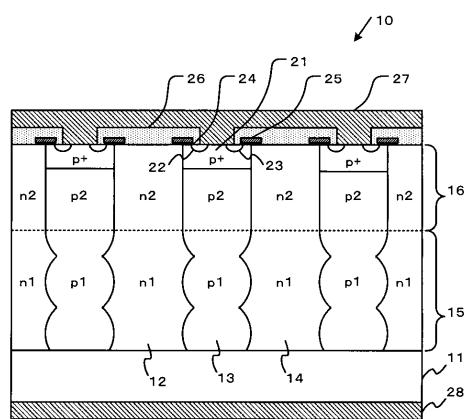

本発明の実施例1に係る半導体装置について、図1乃至図3を用いて説明する。図1は半導体装置の構成を示す断面図、図2は半導体ピラー層の基板からのキャリア濃度分布を示す図、図3は半導体ピラー層のキャリア濃度分布とチャージアンバランスマージンとの関係を模式的に示す図である。

50

## 【0018】

本実施例は、耐圧900V系、オン抵抗150mΩ系のパワーMOSトランジスタを有する半導体装置の例である。

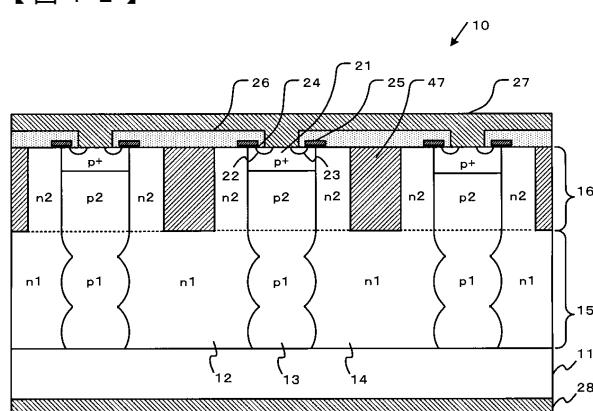

## 【0019】

図1に示すように、本実施例の半導体装置10では、n型Si基板11の正面に、長さLのn型第1半導体ピラー層12と、n型第1半導体ピラー層12に隣接してp型第2半導体ピラー層13、p型第2半導体ピラー層13に隣接してn型第3半導体ピラー層14が形成されている。

## 【0020】

第1乃至第3半導体ピラー層12～14は長さL1、キャリア濃度n1、p1の下側領域15と、長さL2、キャリア濃度n2、p2の上側領域16に区分されている。

## 【0021】

p型第2半導体ピラー層13の上部表面にはp型半導体ベース層21が形成されている。p型第2半導体ベース層21の表面のn型第1半導体ピラー層12側にn型第1半導体ソース領域22が形成され、n型第3半導体ピラー層14側にn型第2半導体ソース領域23が形成されている。

## 【0022】

n型第1半導体ソース領域22とn型第1半導体ピラー層12の間のp型半導体ベース層21上およびn型第2半導体ソース領域23とn型第3半導体ピラー層14の間のp型半導体ベース層21上に、ゲート絶縁膜24が形成され、ゲート絶縁膜24上にゲート電極25が形成されている。

## 【0023】

第1乃至第3半導体ピラー層12～14表面およびゲート電極25は層間絶縁膜26で保護され、層間絶縁膜26上にソース電極27が形成されている。

ソース電極27は層間絶縁膜26の開孔を通してn型第1および第2ソース領域22、23とp型半導体ベース層21に接続されている。n型Si基板11の正面と反対の面にはドレイン電極28が形成されている。

## 【0024】

図2に示すように、n型第1および第3半導体ピラー層12、14の上側領域16のキャリア濃度n2、例えば6E15cm<sup>-3</sup>程度、は下側領域15のキャリア濃度n1、例えば4E15cm<sup>-3</sup>程度、より高く設定されている。

## 【0025】

同じく、p型第2半導体ピラー層13の上側領域16のキャリア濃度p2は下側領域15のキャリア濃度p1より高く設定され、p1とn1およびp2とn2はそれぞれほぼ等しく設定されている。

## 【0026】

次に、第1乃至第3半導体ピラー層12～14のキャリア濃度分布とチャージアンバランスマージンについて詳しく説明する。

## 【0027】

図3(a)は、p型半導体ピラー層の深さ方向(基板からの距離)のキャリア濃度分布を模式的に示す図で、実線aは半導体ピラー層の上側領域が下側領域よりキャリア濃度が高い場合、破線bは上側領域と下側領域のキャリア濃度が等しい場合、破線cは上側領域が下側領域よりキャリア濃度が低い場合のキャリア濃度分布を示している。

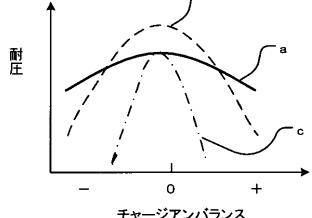

## 【0028】

図3(b)は、チャージアンバランス量(Qn-Qp)/QnとパワーMOSトランジスタのドレイン耐圧の関係を模式的に示す図で、実線aはキャリア濃度分布が図3(a)の実線aの場合、破線bはキャリア濃度分布が図3(a)の破線bの場合、破線cはキャリア濃度分布が図3(a)の破線cの場合の耐圧分布を示している。

## 【0029】

いずれのキャリア濃度分布a、b、cにおいても、チャージアンバランス量(Qn-Qp)/Qn

10

20

30

40

50

$p$  ) /  $Q_n$  が零、即ち完全空乏化したときに最大のドレン耐圧が得られ、チャージアンバランス量が零からずれるに従ってドレン耐圧が低下する耐圧分布 a、b、c を示している。

【 0 0 3 0 】

キャリア濃度分布 a では、従来のキャリア濃度分布 b より、半導体ピラー層の上部が p 型半導体ベース層 2 1 の濃度により近くなるため、チャージアンバランス量の変化に対して各々の部分での耐圧劣化分が小さくなるので、全体としてドレン耐圧の低下が抑えられる。

【 0 0 3 1 】

一方、キャリア濃度分布 c では、従来のキャリア濃度分布 b より、半導体ピラー層の上部が p 型半導体ベース層 2 1 との濃度差がより大きくなるため、各々の部分での耐圧劣化分が大きくなるので、チャージアンバランス量の変化に対して全体としてドレン耐圧は急激に低下する。 10

【 0 0 3 2 】

従って、半導体ピラー層の上側領域のキャリア濃度を下側領域のキャリア濃度より高く設定することにより、チャージアンバランス量の変動に対して完全空乏化時のドレン耐圧の低下を抑えることが可能である。その結果、十分なチャージアンバランスマージンが得られる。

【 0 0 3 3 】

実験によれば、第 1 乃至第 3 半導体ピラー層 1 2 ~ 1 4 のキャリア濃度の平均値に対して、第 1 乃至第 3 半導体ピラー層 1 2 ~ 1 4 の上側領域 1 6 のキャリア濃度が 1 倍を超える、1.2 倍以下の範囲にあり、第 1 乃至第 3 半導体ピラー層 1 2 ~ 1 4 の下側領域 1 5 のキャリア濃度が 0.8 倍以上、1 倍未満の範囲にあり、下側領域 1 5 の長さ  $L_1$  と上側領域 1 6 の長さ  $L_2$  がほぼ等しい条件が適当である。 20

【 0 0 3 4 】

なぜならば、上側領域 1 6 のキャリア濃度が 1.2 倍より高すぎたり、下側領域 1 5 のキャリア濃度が 0.8 倍より低すぎたりすると、深さ方向の全体としての濃度差が大きくなつてチャージバランス時のドレン耐圧自体が低下し、低いドレン耐圧しか得られなくなるからである。

【 0 0 3 5 】

一般に、オン抵抗  $R_{on}$  は、n 型第 1 半導体ピラー層 1 2 の平均キャリア濃度を  $N_n$  、n 型第 1 半導体ピラー層 1 2 の幅を  $W_n$  、p 型第 2 半導体ピラー層 1 3 の幅を  $W_p$  として、 $R_{on} = (1 / N_n) \times (W_n + W_p) / W_n$  で表わされる。 30

【 0 0 3 6 】

高い耐圧と低いオン抵抗を同時に得るためにには、狭幅長尺なピラー層が有利のため、耐圧 900V、オン抵抗 150m を得るためにには、第 1 乃至第 3 半導体ピラー層 1 2 、 1 3 、 1 4 の長さ  $L$  は、例えば 90  $\mu m$  程度、半導体ピラー層下側領域 1 5 の長さは、例えば 60  $\mu m$  程度、半導体ピラー層上側領域 1 6 の長さは、例えば 30  $\mu m$  程度が望ましい。 40

【 0 0 3 7 】

また、第 1 乃至第 3 半導体ピラー層 1 2 、 1 3 、 1 4 の幅  $W_n$  、  $W_p$  は互いにほぼ等しく、例えば 10  $\mu m$  程度が望ましい。即ち、p 型半導体ピラー層 1 3 と n 型半導体ピラー層 1 2 、 1 4 の間で空乏層を広げて完全空乏化させることにより高耐圧を得るために、ピラー層の幅  $W_n$  を狭くし、n 型半導体ピラー層 1 2 、 1 4 のキャリア濃度を高くすることにより、オン抵抗を低減することが可能である。

【 0 0 3 8 】

以上説明したように、本発明の実施例 1 に係る半導体装置によれば、p 型および n 型半導体ピラー層の上側領域 1 6 のキャリア濃度を下側領域 1 5 のキャリア濃度より高くしたので、耐圧を低下させることなく十分なチャージアンバランスマージンが得られる。

【 実施例 2 】

50

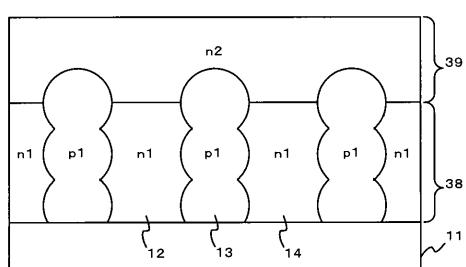

## 【0039】

次に、本発明の実施例2に係る半導体装置の製造方法について、詳しく説明する。図4乃至図12は半導体装置10の製造工程を示す断面図で、上側領域のキャリア濃度が下側領域のキャリア濃度より高い半導体ピラー層を形成する工程を順に示す断面図である。

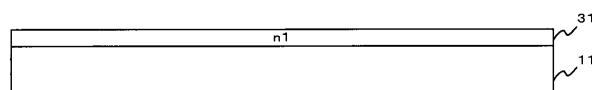

## 【0040】

図4に示すように、キャリア濃度が、例えば1E18cm-3程度のn型Si基板11の正面に、キャリア濃度がn1、例えば4E15cm-3程度のn型Siエピタキシャル層31を、例えば5μm程度成長させる。

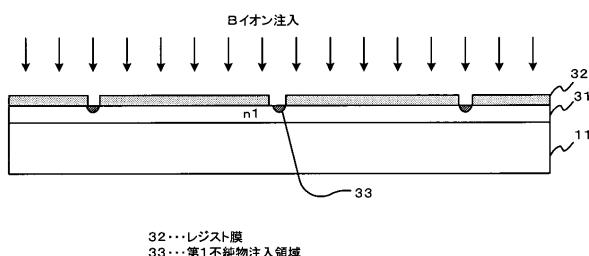

## 【0041】

次に、図5に示すように、Siエピタキシャル層31上にレジスト膜32を形成した後、レジスト膜32をマスクとしてBを、熱処理後にキャリア濃度がp1、例えば4E15cm-3程度になるように注入して、Siエピタキシャル層31表面に第1不純物注入領域33を形成する。第1不純物注入領域33の間隔は、p型第2半導体ピラー層13が配列される間隔と等しい間隔である。

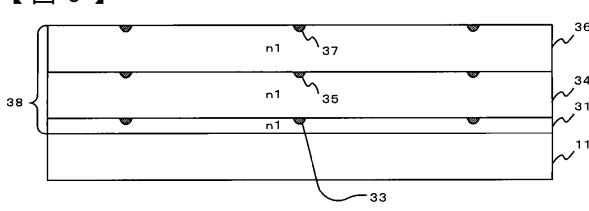

## 【0042】

次に、図6に示すように、レジスト膜32を除去した後、キャリア濃度がn1のn型Siエピタキシャル層34を、Siエピタキシャル層31より厚く、例えば10μm程度成長させた後、p型第2半導体ピラー層13が形成される位置にBを注入して、第1不純物注入領域35を形成する。

## 【0043】

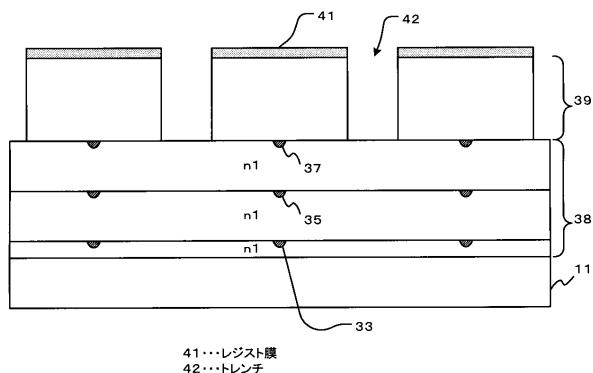

同様に、n型Siエピタキシャル層36を成長させた後、第1不純物注入領域37を形成してSiエピタキシャル層を積み増しすることを必要回数繰り返して、所定の厚さ、例えば60μm程度のn型第1半導体層38を形成する。

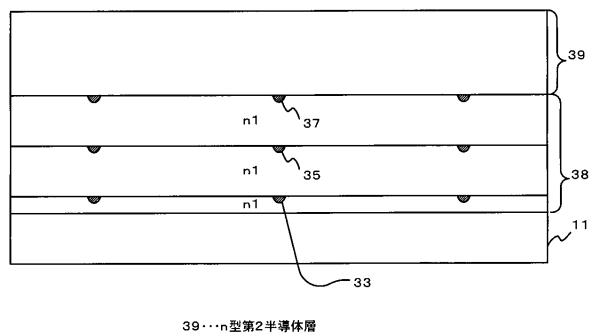

## 【0044】

次に、図7に示すように、n型第1半導体層38上にn型Siエピタキシャル層を、例えば30μm程度成長させ、厚いn型第2半導体層39を形成する。

## 【0045】

次に、図8に示すように、フォトリソグラフィ法によりレジスト膜41を形成した後、レジスト膜41をマスクとしてRIE(Reactive Ion Etching)によりn型第1半導体層38に達する深いトレンチ42をn型第2半導体層39に開口する。トレンチ42の深さはn型第2半導体層39の厚さとほぼ等しく、幅は例えば5μm程度、間隔はp型第1不純物注入領域33が水平方向に配列されている間隔にほぼ等しい。

## 【0046】

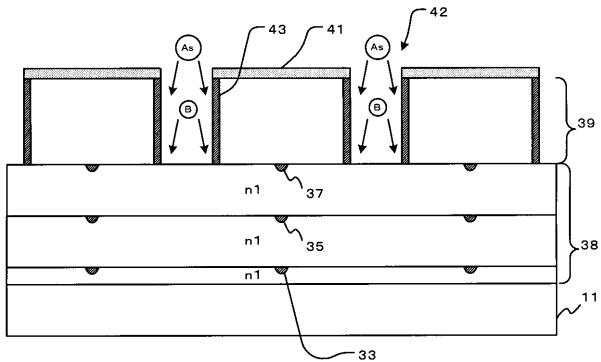

次に、図9に示すように、回転イオン注入法により、レジスト膜41をマスクとしてAsおよびBを注入角度5°~7°にて、熱処理後にキャリア濃度がn2およびp2、例えば、それぞれ6E15cm-3程度となるようにトレンチ42の側面に注入し、第2不純物注入領域43を形成する。

## 【0047】

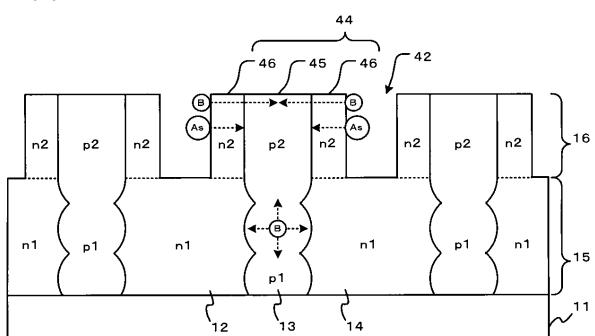

次に、図10に示すように、熱処理を、例えば1140×24H程度おこなって、第1不純物注入領域33、35、37からBをn型第1半導体層38中に拡散させ、第2不純物注入領域43からトレンチ42で挟まれた不純物拡散領域44にBおよびAsを同時に拡散させる。

## 【0048】

これにより、第1不純物注入領域33、35、37からBが拡散した領域が上下相互に接続されたp型第1半導体ピラー層13の下側領域15が形成され、p型第1半導体ピラー層13の下側領域15を挟んでn型第1および第3半導体ピラー層12、14の下側領域15が形成される。

## 【0049】

同時に、Bの拡散係数はAsの拡散係数より一桁程度大きいためBはAsより深く拡散するので、トレンチ42で挟まれた不純物拡散領域44の中央部にBが拡散した領域が左

10

20

30

40

50

右に接続された p 型拡散領域 4 5 が形成され、 p 型拡散領域 4 5 の周りに A s が拡散した n 型拡散領域 4 6 が自己整合的に形成される。

【 0 0 5 0 】

その結果、 p 型拡散領域 4 5 が p 型第 2 半導体ピラー層 1 2 の下側領域 1 5 と上下に接続されて p 型第 2 半導体ピラー層 1 3 が形成され、 n 型拡散領域 4 6 が n 型第 1 および第 3 半導体ピラー層 1 2 、 1 4 の下側領域 1 5 と上下に接続されて n 型第 1 および第 3 半導体ピラー層 1 2 、 1 4 が形成される。

【 0 0 5 1 】

これにより、上側領域 1 6 のキャリア濃度が下側領域 1 5 のキャリア濃度より高い第 1 乃至第 3 半導体ピラー層 1 2 ～ 1 4 を形成することが可能である。

10

【 0 0 5 2 】

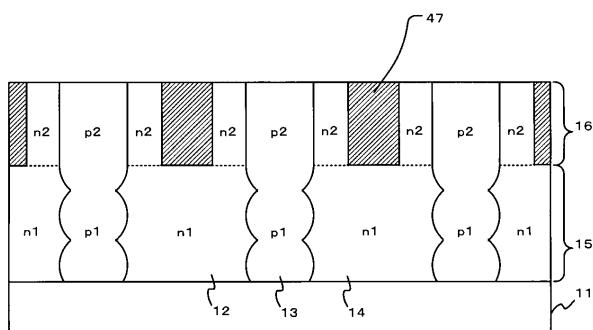

次に、図 1 1 に示すように、トレンチ 4 2 を埋め込むように絶縁膜 4 7 を全面に形成した後、 C M P (Chemical Mechanical Etching) により表面を平坦化するとともに、トレンチ 4 2 の外部の不要な絶縁膜 4 7 を除去する。

【 0 0 5 3 】

絶縁膜 4 7 は、例えばトレンチ 4 2 の側面に熱酸化によりシリコン酸化膜を形成し、その後、 C V D (Chemical Vapor Deposition) により、シリコン酸化膜またはシリコン窒化膜を全面に堆積することにより形成される。

【 0 0 5 4 】

次に、図 1 2 に示すように、周知のパワー M O S ドラインジスタの製造工程に従って、 p 型半導体ピラー層 1 3 の上部に p 型半導体ベース層 2 1 を形成した後、 p 型半導体ベース層 2 1 の表面に選択的に n 型第 1 および第 2 半導体ソース領域 2 2 、 2 3 を形成する。

20

【 0 0 5 5 】

次に、ゲート絶縁膜 2 4 、ゲート電極 2 5 、層間絶縁膜 2 6 、ソース電極 2 7 、ドレイン電極 2 8 をそれぞれ形成して、上側領域 1 6 のキャリア濃度が下側領域 1 5 のキャリア濃度より高い、狭幅長尺の半導体ピラー層 1 2 、 1 3 、 1 4 を有するパワー M O S ドラインジスタを備えた半導体装置 1 0 が完成する。

【 0 0 5 6 】

以上説明したように、実施例 2 に係る半導体装置の製造方法によれば、エピタキシャル層中に形成した p 型および n 型半導体ピラー層とトレンチに挟まれた領域に形成した p 型および n 型半導体ピラー層とをそれぞれ上下に接続して延伸したピラー層としたので、狭幅長尺なピラー層が得られ微細な幅でオン抵抗を下げることができる。

30

【 0 0 5 7 】

また、エピタキシャル層の形成と不純物のイオン注入を必要回数繰り返す場合に比べ、トレンチの側面から不純物のイオン注入を行なう方法では、キャリア濃度を高めてもピラー層の狭幅長尺化を容易に実現できるため、キャリア濃度が上側で高い狭幅長尺の半導体ピラー層を形成するうえで非常に有効である。

【 0 0 5 8 】

従って、十分な耐圧と信頼性の高いパワー M O S ドラインジスタを備えた半導体装置を提供することができる。

40

【 実施例 3 】

【 0 0 5 9 】

図 1 3 乃至図 1 6 は本発明の実施例 3 に係るパワー M O S ドラインジスタを有する半導体装置の製造工程を示す断面図で、上側領域のキャリア濃度が下側領域のキャリア濃度より高い、狭幅長尺化な半導体ピラー層を形成する工程を順に示す断面図である。

【 0 0 6 0 】

本実施例において上記実施例 1 と同一の構成部分には同一符号を付してその説明は省略し、異なる部分についてのみ説明する。

本実施例が実施例 2 と異なる点は、トレンチ内部に p 型半導体層を埋め込んで p 型半導体ピラー層の上側領域を形成したことにある。

50

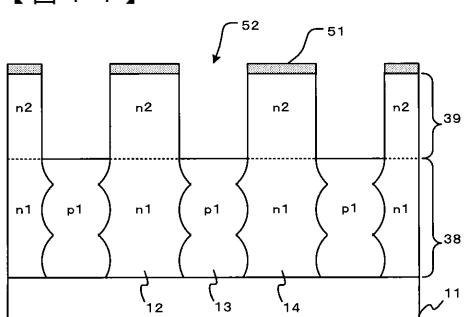

## 【0061】

即ち、図4乃至図7で示した工程に従い、n型Si基板11の正面に、エピタキシャル成長によりキャリア濃度n1のn型第1半導体層38とキャリア濃度n2のn型第2半導体層39を形成する。n型第1半導体層38には、第1不純物注入領域33、35、37が形成されている。

## 【0062】

次に、図13に示すように、熱処理を、例えば1140×24H程度おこなって、第1不純物注入領域33、35、37からBをn型第1半導体層38内に拡散させる。

これにより、第1不純物注入領域33、35、37からBが拡散した領域が上下相互に接続されたp型第2半導体ピラー層13の下側領域15が形成され、p型第2半導体ピラーレ13の下側領域15を挟んでn型第1および第3半導体ピラー層12、14の下側領域15が形成される。

## 【0063】

次に、図14に示すように、フォトリソグラフィ法によりレジスト膜51を形成した後、RIE(Reactive Ion Etching)によりレジスト膜51をマスクとしてn型第1半導体層38に達する深いトレンチ52をn型第2半導体層39に開口する。トレンチ52の深さはn型第2半導体層39の厚さとほぼ等しく、幅はp型第2半導体ピラー層13の幅とほぼ等しく、間隔はp型第2半導体ピラー層13が水平方向に配列されている間隔にほぼ等しい。

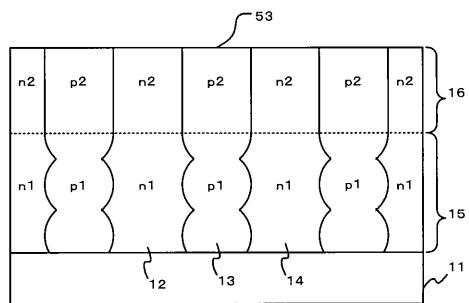

## 【0064】

次に、図15に示すように、トレンチ内部に選択的にキャリア濃度がp2のp型Siエピタキシャル層53を形成した後、表面をCMPにより平坦化するとともに、トレンチ52の外部の不要なp型Siエピタキシャル層53を除去することにより、トレンチ52内をp型Siエピタキシャル層53で埋め込む。

## 【0065】

その結果、p型第2半導体ピラー層13の下側領域15とp型Siエピタキシャル層53とが上下に接続されてp型第2半導体ピラー層13が形成され、n型第1および第3半導体ピラー層12、14の下側領域15とn型第2半導体層39が上下に接続されてn型第1および第3半導体ピラー層12、14が形成される。

## 【0066】

これにより、上側領域16のキャリア濃度が下側領域15のキャリア濃度より高い第1乃至第3半導体ピラー層12～14を形成することが可能である。

## 【0067】

次に、図16に示すように、周知のパワーMOSトランジスタの製造工程に従って、上側領域16のキャリア濃度が下側領域15のキャリア濃度より高い、狭幅長尺の半導体ピラー層12～14を有するパワーMOSトランジスタを備えた半導体装置10が完成する。

## 【0068】

以上説明したような実施例3に係る半導体装置の製造方法においても、エピタキシャル層の形成と不純物のイオン注入を必要回数繰り返す場合に比べ、トレンチ内部に半導体層を埋め込む方法では、キャリア濃度を高めてもピラー層の狭幅長尺化を容易に実現でき、キャリア濃度が上側で高い狭幅長尺な半導体ピラー層を形成するうえで非常に有効である。しかも、n型第2半導体層39中に絶縁膜47を形成する必要が無いので、チップサイズを縮小できる利点がある。

## 【図面の簡単な説明】

## 【0069】

【図1】本発明の実施例1に係るパワーMOSトランジスタを備えた半導体装置の要部の構成を示す断面図。

【図2】本発明の実施例1に係る半導体ピラー層のキャリア濃度分布を示す図。

【図3】本発明の実施例1に係る半導体ピラー層のキャリア濃度分布とチャージアンバラ

10

20

30

40

50

ンスマージンの関係を説明する図。

- 【図 4】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 5】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 6】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 7】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 8】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 9】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 10】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 11】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 12】本発明の実施例 2 に係る半導体装置の製造工程を示す断面図。

- 【図 13】本発明の実施例 3 に係る半導体装置の製造工程を示す断面図。

- 【図 14】本発明の実施例 3 に係る半導体装置の製造工程を示す断面図。

- 【図 15】本発明の実施例 3 に係る半導体装置の製造工程を示す断面図。

- 【図 16】本発明の実施例 3 に係る半導体装置の製造工程を示す断面図。

10

【符号の説明】

【0070】

- 1 0 半導体装置

- 1 1 n 型シリコン基板

- 1 2 n 型第 1 半導体ピラー層

- 1 3 p 型第 2 半導体ピラー層

- 1 4 n 型第 3 半導体ピラー層

- 1 5 半導体ピラー層下側領域

- 1 6 半導体ピラー層上側領域

- 2 1 p 型半導体ベース層

- 2 2 n 型第 1 半導体ソース領域

- 2 3 n 型第 2 半導体ソース領域

- 2 4 ゲート絶縁膜

- 2 5 ゲート電極

- 2 6 層間絶縁膜

- 2 7 ソース電極

- 2 8 ドレイン電極

- 3 1、3 4、3 6 n 型 Si エピタキシャル層

- 3 2、4 1、5 1 レジスト膜

- 3 3、3 5、3 7 第 1 不純物注入領域

- 3 8 n 型第 1 半導体層

- 3 9 n 型第 2 半導体層

- 4 2、5 2 トレンチ

- 4 3 第 2 不純物注入領域

- 4 4 不純物拡散領域

- 4 5 p 型不純物拡散領域

- 4 6 n 型不純物拡散領域

- 4 7 絶縁膜

- 5 3 p 型 Si エピタキシャル層

20

30

40

【図1】

- 10…半導体装置

11…n型Si基板

12…n型第1半導体ビラーレンジ

13…p型第2半導体ビラーレンジ

14…n型第3半導体ビラーレンジ

15…半導体ビラーレンジ下側領域

16…半導体ビラーレンジ上側領域

21…p型半導体ベース層

22…n型第1半導体ソース領域

23…n型第2半導体ソース領域

24…ゲート絶縁膜

25…ゲート電極

26…層間絶縁膜

27…ソース電極

28…ドレイン電極

【図2】

【図3】

(b)

【図4】

31…n型Siエピタキシャル層

【図5】

【図6】

34, 36…n型Siエピタキシャル層

35…第1不純物注入領域

38…n型第1半導体層

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

### 53···p型Siエピタキシャル層

### 【図16】

---

フロントページの続き

(72)発明者 奥村 秀樹

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 土谷 政信

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 瀧内 健夫

(56)参考文献 特開2004-072068(JP, A)

特開2002-124675(JP, A)

特開2004-119611(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336