(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6121853号

(P6121853)

(45) 発行日 平成29年4月26日(2017.4.26)

(24) 登録日 平成29年4月7日(2017.4.7)

(51) Int.Cl.

G05B 23/02 (2006.01)

F 1

G 05 B 23/02 302 Z

請求項の数 4 (全 17 頁)

(21) 出願番号 特願2013-193473 (P2013-193473)

(22) 出願日 平成25年9月18日 (2013.9.18)

(65) 公開番号 特開2015-60398 (P2015-60398A)

(43) 公開日 平成27年3月30日 (2015.3.30)

審査請求日 平成28年5月9日 (2016.5.9)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73) 特許権者 501137636

東芝三菱電機産業システム株式会社

東京都中央区京橋三丁目1番1号

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100103034

弁理士 野河 信久

最終頁に続く

(54) 【発明の名称】出力装置およびその診断方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1負荷および前記第1負荷より信号に対する応答時間が長い第2負荷に接続される出力装置であって、

前記第1負荷に信号を出力する第1出力素子および前記第1出力素子に接続される第1遮断素子を有する第1デジタル出力回路と、

前記第2負荷に信号を出力する第2出力素子および前記第2出力素子に接続される第2遮断素子を有する第2デジタル出力回路と、

前記第1および第2遮断素子を一括して駆動させる遮断素子用の单一の駆動回路と、

所定タイミングより前記第2負荷の応答時間だけ早いタイミングで前記第2出力素子からの信号をOFFさせ、前記所定タイミングより前記第1負荷の応答時間だけ早いタイミングで前記第1および第2出力素子からの信号をONさせて前記第1および第2遮断素子からの信号をOFFさせる信号制御手段と、10

前記所定タイミングで前記第1デジタル出力回路からの信号に基づいて前記第1遮断素子が正常か故障かを診断し、前記所定タイミングで前記第2デジタル出力回路からの信号に基づいて前記第2遮断素子が正常か故障かを診断する診断手段とを備えたことを特徴とする出力装置。

## 【請求項 2】

前記第1および第2遮断素子と前記第1および第2出力素子とは電界効果トランジスタであって、

前記駆動回路が前記第1および第2遮断素子のゲートに接続され、

前記第1遮断素子のソースが前記第1出力素子のドレインに接続され、

前記第2遮断素子のソースが前記第2出力素子のドレインに接続され、

前記第1負荷は、

入力端が前記第1出力素子のソースに接続されて、出力端が前記第1および第2遮断素子のドレインに接続されて、

前記第2負荷は、

入力端が前記第2出力素子のソースに接続されて、出力端が前記第1および第2遮断素子のドレインに接続されて、

前記診断手段は、

前記所定タイミングで前記第1出力素子からの信号に基づいて前記第1遮断素子が正常か故障かを診断し、前記第2出力素子からの信号に基づいて前記第2遮断素子が正常か故障かを診断する

ことを特徴とする請求項1に記載の出力装置。

#### 【請求項3】

前記第1および第2遮断素子と前記第1および第2出力素子とは電界効果トランジスタであって、

前記駆動回路が前記第1および第2遮断素子のゲートに接続され、

前記第1出力素子のソースが前記第1遮断素子のドレインに接続され、

前記第2出力素子のソースが前記第2遮断素子のドレインに接続され、

前記第1負荷は、

入力端が前記第1および第2遮断素子のソースに接続されて、出力端が前記第1出力素子のドレインに接続されて、

前記第2負荷は、

入力端が前記第1および第2遮断素子のソースに接続されて、出力端が前記第2出力素子のドレインに接続されて、

前記診断手段は、

前記所定タイミングで前記第1負荷からの信号に基づいて前記第1遮断素子が正常か故障かを診断し、前記所定タイミングで前記第2負荷からの信号に基づいて前記第2遮断素子が正常か故障かを診断する

ことを特徴とする請求項1に記載の出力装置。

#### 【請求項4】

第1負荷および前記第1負荷より信号に対する応答時間が長い第2負荷に接続される出力装置であって、前記第1負荷に信号を出力する第1出力素子および前記第1出力素子に接続される第1遮断素子を有する第1デジタル出力回路と、前記第2負荷に信号を出力する第2出力素子および前記第2出力素子に接続される第2遮断素子を有する第2デジタル出力回路と、前記第1および第2遮断素子を一括して駆動させる遮断素子用の単一の駆動回路とを有する出力装置の診断方法であって、

信号制御手段により、所定タイミングより前記第2負荷の応答時間だけ早いタイミングで前記第2出力素子からの信号をOFFさせ、前記所定タイミングより前記第1負荷の応答時間だけ早いタイミングで前記第1および第2出力素子からの信号をONさせて前記第1および第2遮断素子からの信号をOFFさせ、

診断手段により、前記所定タイミングで前記第1デジタル出力回路からの信号に基づいて前記第1遮断素子が正常か故障かを診断し、前記所定タイミングで前記第2デジタル出力回路からの信号に基づいて前記第2遮断素子が正常か故障かを診断する

ことを特徴とする出力装置の診断方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明の実施形態は、出力装置およびその診断方法に関する。

10

20

30

40

50

**【背景技術】****【0002】**

近年、装置の製造者・供給者に対して、国際標準の機能安全規格が国際電気標準化会議の規格IEC61508「電気・電子・プログラマブル電子安全関連系の機能安全」として纏められている。更に、特定の産業用機能安全システムにおいては、特定の用途に合わせた派生規格が定められている。例えば、安全計装システムについては、システムの設計者・インテグレータ・ユーザに対しては、国際標準のプロセス用アプリケーション規格としてIEC61511が定められている。

**【0003】**

これらの規格では、システムの設計、保守、廃棄に至るライフサイクルにおける安全を評価し、リスク軽減の要求レベルである安全度水準(SIL; Safety Integrity Level)を定量的な評価尺度として定めている。10

**【0004】**

高い安全度水準を求められる安全計装システムにおいては、デジタル出力回路の故障の検出が必要となる。システム起動時だけでなくシステム稼働中においても対象のデジタル出力回路に対する診断が必要となる。そして故障を検出した際には、システム出力を安全状態に遷移させる必要がある。

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2013-54427号公報20

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

出力遮断回路を有するデジタル出力回路から制御装置(負荷)となる入力回路への接続において、制御装置の無応答時間内で出力遮断回路内の出力素子の故障診断を行っている。

しかし、制御装置の無応答時間は装置毎に異なるため、接続される制御装置の応答特性に応じてデジタル出力回路毎に診断タイミングを変えて故障診断を行う必要がある。

**【0007】**

このため、遮断素子と出力素子の故障診断を行う為には、遮断素子と出力素子とをそれぞれ制御する必要があり、制御装置数が多くなるにつれて機器コストや部品実装面積が大きくなってしまう。

**【0008】**

本発明が解決しようとする課題は、応答特性が異なる負荷に接続されるデジタル出力回路の診断を行うための機器コストや実装面積を削減することが可能な出力装置およびその診断方法を提供することである。

**【課題を解決するための手段】****【0009】**

実施形態によれば、出力装置は、第1負荷および前記第1負荷より信号に対する応答時間が長い第2負荷に接続される出力装置であって、前記第1負荷に信号を出力する第1出力素子および前記第1出力素子に接続される第1遮断素子を有する第1デジタル出力回路と、前記第2負荷に信号を出力する第2出力素子および前記第2出力素子に接続される第2遮断素子を有する第2デジタル出力回路と、前記第1および第2遮断素子を一括して駆動させる遮断素子用の単一の駆動回路とを備える。この出力装置は、所定タイミングより前記第2負荷の応答時間だけ早いタイミングで前記第2出力素子からの信号をOFFさせ、前記所定タイミングより前記第1負荷の応答時間だけ早いタイミングで前記第1および第2出力素子からの信号をONさせて前記第1および第2遮断素子からの信号をOFFさせる信号制御手段と、前記所定タイミングで前記第1デジタル出力回路からの信号に基づいて前記第1遮断素子が正常か故障かを診断し、前記所定タイミングで前記第2デジタル

4050

出力回路からの信号に基づいて前記第2遮断素子が正常か故障かを診断する診断手段とをもつ。

**【図面の簡単な説明】**

**【0010】**

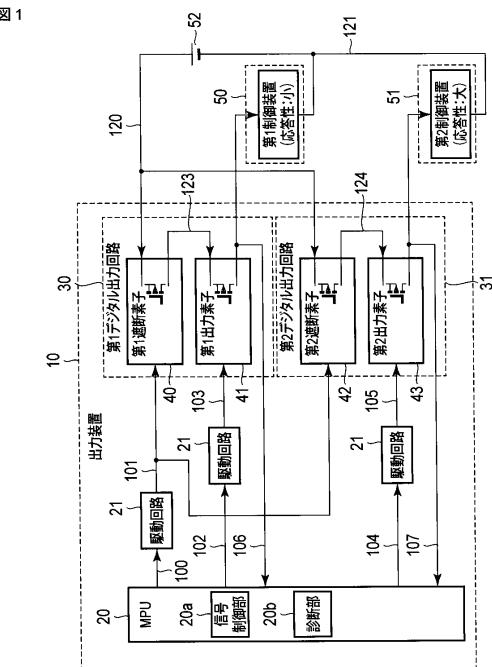

【図1】第1の実施形態における出力装置の構成例を示す回路図。

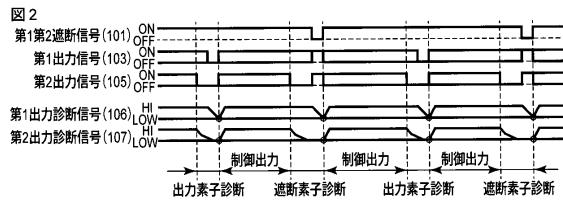

【図2】第1の実施形態における出力装置による素子診断タイミングの全体動作を説明するための図。

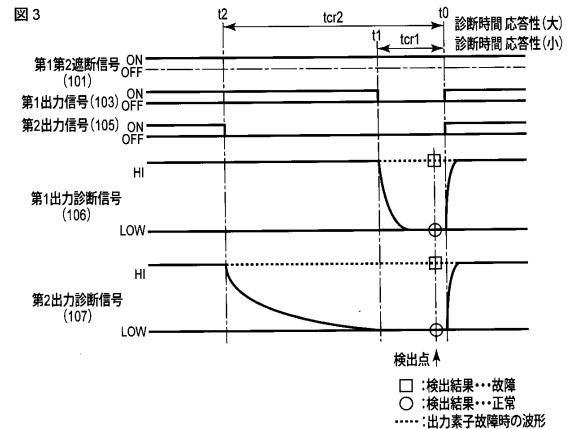

【図3】第1の実施形態における出力装置による出力素子診断動作を説明するための図。

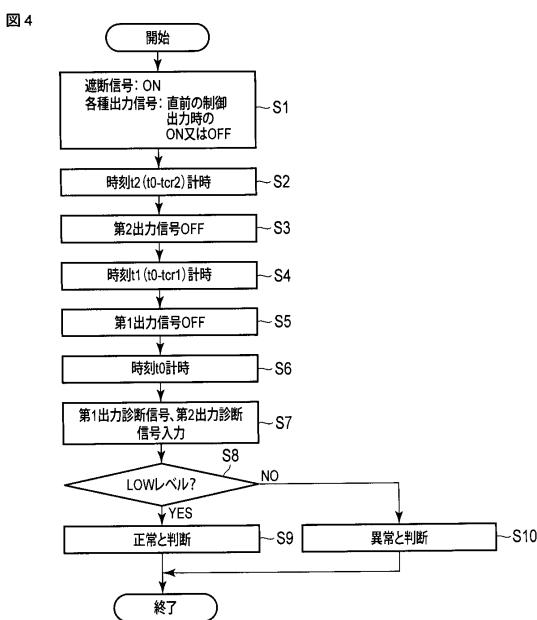

【図4】第1の実施形態における出力装置による第1出力素子と第2出力素子の診断のための手順の一例を示すフローチャート。 10

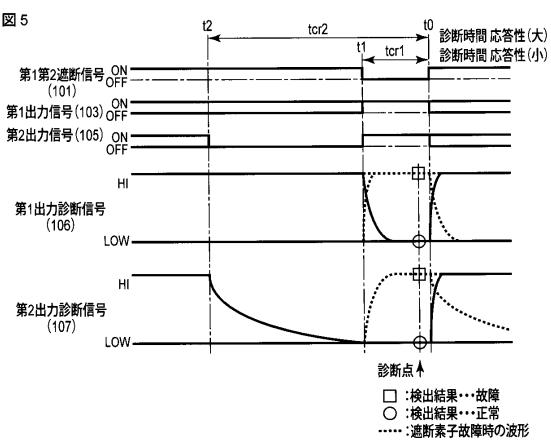

【図5】第1の実施形態における出力装置による遮断素子診断動作を説明するための図。

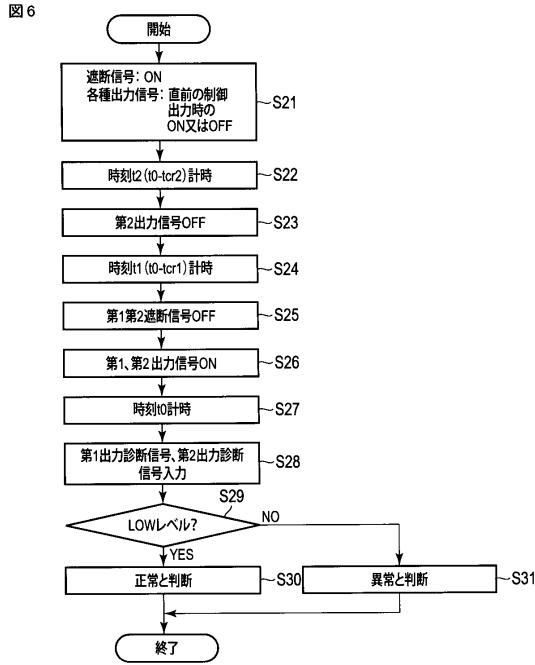

【図6】第1の実施形態における出力装置による第1遮断素子と第2遮断素子の診断のための手順の一例を示すフローチャート。

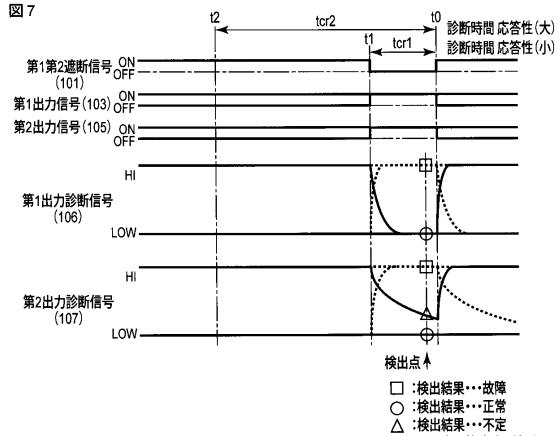

【図7】第1の実施形態における出力装置による各種出力信号がONであるときの遮断素子診断動作を説明するための図。

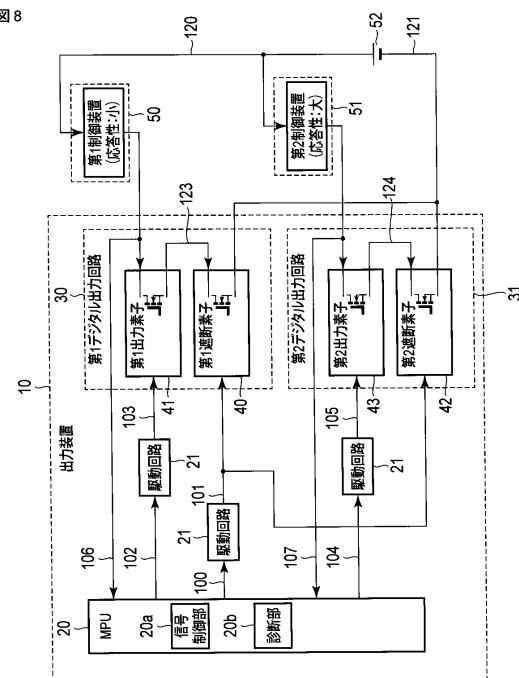

【図8】第2の実施形態における出力装置の構成例を示す回路図。

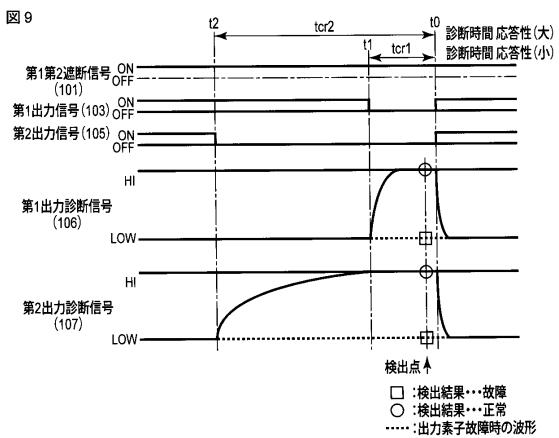

【図9】第2の実施形態における出力装置による出力素子診断動作を説明するための図。

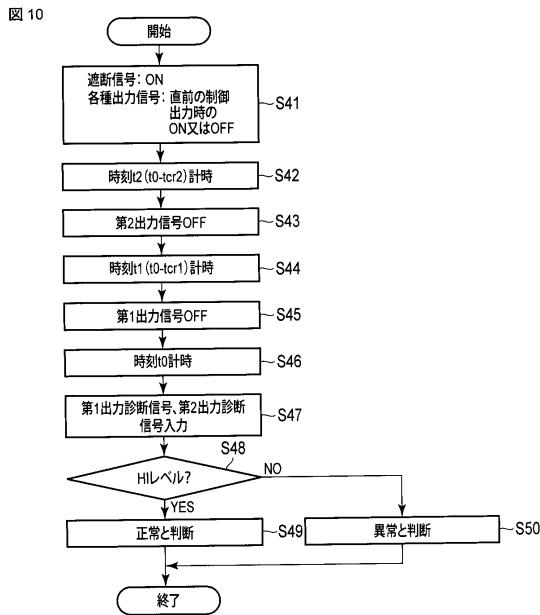

【図10】第2の実施形態における出力装置による第1出力素子と第2出力素子の診断のための手順の一例を示すフローチャート。 20

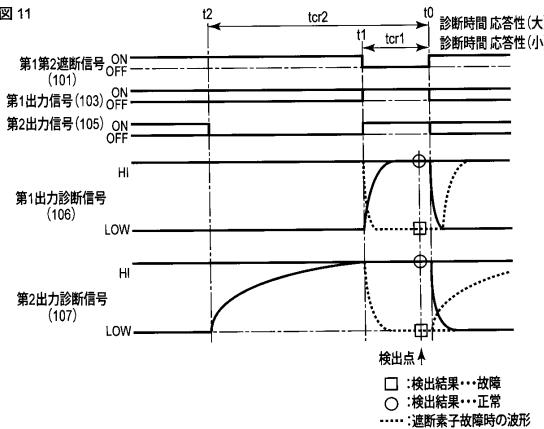

【図11】第1の実施形態における出力装置による遮断素子診断動作を説明するための図。

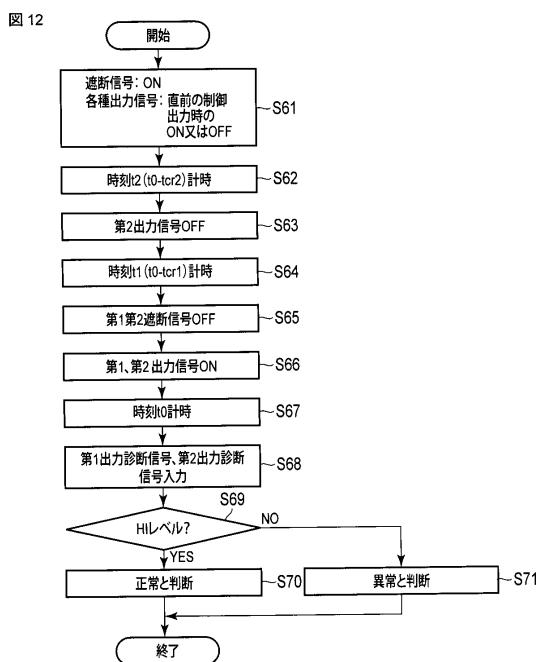

【図12】第1の実施形態における出力装置による第1遮断素子と第2遮断素子の診断のための手順の一例を示すフローチャート。

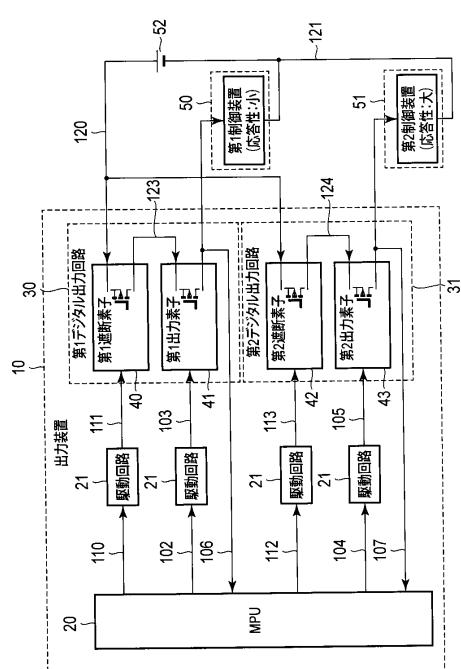

【図13】従来方式の遮断・出力素子診断回路の構成例を示す図。

**【発明を実施するための形態】**

**【0011】**

以下、実施形態について、図面を参照して説明する。

実施形態の理解を容易にするために、まず、従来の出力装置のデジタル出力回路の構成について説明する。

図13は、従来の出力装置のデジタル出力回路の構成例を示す図である。 30

出力装置10は、第1デジタル出力回路30と第2デジタル出力回路31とを有する。出力装置10は、これら第1デジタル出力回路30と第2デジタル出力回路31の診断機能を有する。

**【0012】**

まず、第1デジタル出力回路30について説明する。

第1デジタル出力回路30は、負荷としての第1制御装置50を駆動するためのスイッチング素子として動作する第1出力素子41のMOSFET（電界効果トランジスタ）を有する。第1出力素子41のソースは、MPU20および第1制御装置50の入力端に接続される。MPU20は、第1デジタル出力回路30の出力状態を監視する。

**【0013】**

また、第1デジタル出力回路30は、この回路の遮断を行うためのスイッチング素子として動作する第1遮断素子40のMOSFETを有する。第1遮断素子40のソースは、第1遮断素子第1出力素子接続線123を介して第1出力素子41のドレインと接続される。第1出力素子41のゲートは第1出力素子41用の駆動回路21に接続される。 40

**【0014】**

第1遮断素子40のドレインは外部電源装置52のプラス線120を介して外部電源装置52のプラス側と接続される。第1遮断素子40のゲートは第1遮断素子40用の駆動回路21に接続される。

第1出力素子41用の駆動回路21と第1遮断素子40用の駆動回路21とは、第1出力素子41と第1遮断素子40とを駆動するためのMPU20と接続される。 50

**【0015】**

次に、第2デジタル出力回路31について説明する。

第2デジタル出力回路31は、負荷としての第2制御装置51を駆動するためのスイッチング素子として動作する第2出力素子43のMOSFETを有する。第2出力素子43のソースは、MPU20および第2制御装置51の入力端に接続される。MPU20は、第2デジタル出力回路31の出力状態を監視する。

**【0016】**

第1デジタル出力回路30の第1出力素子41に接続される第1制御装置50には速い応答特性を有する、例えば時定数が小さい( $t_{cr1} < t_{cr2}$ )制御装置が用いられる。

10

**【0017】**

また、第2デジタル出力回路31の第2出力素子43に接続される第2制御装置51には第1制御装置50より遅い応答特性を有する、例えば時定数の大きい( $t_{cr2} > t_{cr1}$ )制御装置が用いられる。

**【0018】**

第2デジタル出力回路31は、この回路の遮断を行うためのスイッチング素子として動作する第2遮断素子42のMOSFETを有する。第2遮断素子42のソースは、第2遮断素子第2出力素子接続線124を介して第2出力素子43のドレインと接続される。第2出力素子43のゲートは第2出力素子43用の駆動回路21に接続される。第2遮断素子42のゲートは第2遮断素子42用の駆動回路21に接続される。

20

第2出力素子43用の駆動回路21と第2遮断素子42用の駆動回路21とは、第2出力素子43と第2遮断素子42とを駆動するためのMPU20と接続される。

**【0019】**

また、第1制御装置50および第2制御装置51の出力端は、外部電源装置52のマイナス線121を介して外部電源装置52のマイナス側と接続される。また、外部電源装置52のプラス側は、第2遮断素子42のドレインと接続される。

上記の様に、図13に示した従来の構成では、MPU20は、第1遮断素子40と第2遮断素子42とを別々の駆動回路21を介して駆動させる。

**【0020】**

MPU20は、第1遮断素子40を制御するための第1遮断素子制御信号110を第1遮断素子40用の駆動回路21に出力する。この駆動回路21は、第1遮断素子40に第1遮断信号(第1遮断素子駆動信号)111を出力する。

30

**【0021】**

第1遮断素子40が正常であれば、第1遮断信号111がON状態となると第1遮断素子40はON状態となる。また、第1遮断素子40が正常であれば、第1遮断信号111がOFF状態となると第1遮断素子40はOFF状態となる。

**【0022】**

MPU20は、第1出力素子41を制御するための第1出力素子制御信号102を第1出力素子41用の駆動回路21に出力する。この駆動回路21は、第1出力素子41に第1出力信号(第1出力素子駆動信号)103を出力する。

40

**【0023】**

第1出力素子41が正常であれば、第1出力信号103がON状態となると第1出力素子41はON状態となる。また、第1出力素子41が正常であれば、第1出力信号103がOFF状態となると第1出力素子41はOFF状態となる。

**【0024】**

MPU20は、第2遮断素子42を制御するための第2遮断素子制御信号112を第2遮断素子42用の駆動回路21に出力する。この駆動回路21は、第2遮断素子42に第2遮断信号(第2遮断素子駆動信号)113を出力する。

**【0025】**

第2遮断素子42が正常であれば、第2遮断信号113がON状態となると第2遮断素

50

子 4 2 は O N 状態となる。また、第 2 遮断素子 4 2 が正常であれば、第 2 遮断信号 1 1 3 が O F F 状態となると第 2 遮断素子 4 2 は O F F 状態となる。

#### 【 0 0 2 6 】

M P U 2 0 は、第 2 出力素子 4 3 を制御するための第 2 出力素子制御信号 1 0 4 を第 2 出力素子 4 3 用の駆動回路 2 1 に出力する。この駆動回路 2 1 は、第 2 出力素子 4 3 に第 2 出力信号（第 2 出力素子駆動信号）1 0 5 を出力する。

#### 【 0 0 2 7 】

第 2 出力素子 4 3 が正常であれば、第 2 出力信号 1 0 5 が O N 状態となると第 2 出力素子 4 3 は O N 状態となる。また、第 2 出力素子 4 3 が正常であれば、第 2 出力信号 1 0 5 が O F F 状態となると第 2 出力素子 4 3 は O F F 状態となる。

10

#### 【 0 0 2 8 】

M P U 2 0 は、各種素子に対する信号制御に応じた第 1 出力診断信号 1 0 6 および第 2 出力診断信号 1 0 7 に基づいて、各種素子が正常（O N / O F F 出力出来る）であるか故障（O F F 出力することが出来ない）であるかを診断する。各種素子を O N 出力出来るか否かの診断を O N 診断と呼ぶことがあり、各種素子を O F F 出力出来るか否かの診断を O F F 診断と呼ぶことがある。

#### 【 0 0 2 9 】

つまり、従来の構成では、第 1 遮断素子 4 0 、第 2 遮断素子 4 2 の診断を行う場合、制御装置の応答特性に応じて個々に診断を行う必要がある。このため、第 1 遮断素子 4 0 用の駆動回路 2 1 と第 2 遮断素子 4 2 用の駆動回路 2 1 とがそれぞれ必要となる。

20

#### 【 0 0 3 0 】

M P U 2 0 は、第 1 出力素子 4 1 、第 2 出力素子 4 3 、第 1 遮断素子 4 0 および第 2 遮断素子 4 2 の O N 診断を、制御出力中で出力が O N の時に一括して行う。

つまり、M P U 2 0 は、第 1 出力素子 4 1 、第 2 出力素子 4 3 の O F F 診断と第 1 遮断素子 4 0 および第 2 遮断素子 4 2 の O F F 診断と、第 1 出力素子 4 1 、第 2 出力素子 4 3 、第 1 遮断素子 4 0 および第 2 遮断素子の一括 O N 診断により各素子の O N / O F F 故障診断を行う。

#### 【 0 0 3 1 】

##### ( 第 1 の実施形態 )

次に、第 1 の実施形態について説明する。

30

図 1 は、第 1 の実施形態における出力装置のデジタル出力回路の構成例を示す図である。

。

ここでは、図 1 に示した構成のうち、図 1 3 に示した構成と異なる構成を中心に説明する。

図 1 に示した構成は、図 1 3 に示した構成と異なり、第 1 遮断素子 4 0 および第 2 遮断素子 4 2 のそれぞれに対して駆動回路 2 1 を設ける代わりに、第 1 遮断素子 4 0 および第 2 遮断素子 4 2 に共通する 1 つの駆動回路 2 1 を設ける。この駆動回路 2 1 は、第 1 遮断素子 4 0 のゲートおよび第 2 遮断素子 4 2 のゲートのそれぞれに接続される。この共通する駆動回路を必要に応じて各遮断素子用の駆動回路 2 1 と呼ぶ。

#### 【 0 0 3 2 】

40

M P U 2 0 は、各種素子への信号を制御するための信号制御部 2 0 a と、この信号制御に応じた第 1 出力診断信号 1 0 6 および第 2 出力診断信号 1 0 7 に基づいて、各種素子が正常であるか故障であるかを診断するための診断部 2 0 b とを有する。

#### 【 0 0 3 3 】

また、この各遮断素子用の駆動回路 2 1 は、M P U 2 0 の信号制御部 2 0 a からの遮断素子制御信号 1 0 0 に応じて、第 1 遮断素子 4 0 および第 2 遮断素子 4 2 のそれぞれに共通の信号としての第 1 第 2 遮断信号（遮断素子駆動信号）1 0 1 を出力する構成としている。

#### 【 0 0 3 4 】

第 1 遮断素子 4 0 と第 2 遮断素子 4 2 が正常であれば、第 1 第 2 遮断信号 1 0 1 が O N

50

状態となると第1遮断素子40と第2遮断素子42はON状態となる。また、第1遮断素子40と第2遮断素子42が正常であれば、第1第2遮断信号101がOFF状態となると第1遮断素子40と第2遮断素子42はOFF状態となる。

#### 【0035】

上記の様に、本実施形態では、第1遮断素子40と第2遮断素子42は遮断素子用の一つの駆動回路21に接続されるので、図13に示した構成と比較して駆動回路21の数を削減する事ができる。

#### 【0036】

図2は、第1の実施形態における出力装置による素子診断タイミングの全体動作を説明するための図である。

10

図2では、第1出力素子41、第2出力素子43、第1遮断素子40、第2遮断素子42のそれぞれをOFF診断するためのタイミングを示している。

まず、第1出力素子41と第2出力素子43をOFF診断するための各種信号の制御について説明する。

第1出力素子41と第2出力素子43をOFF診断するための所定のタイミングの前では、MPU20の信号制御部20aは、第1第2遮断信号101をON状態としている。

#### 【0037】

第1第2遮断信号101をON状態とするには、MPU20の信号制御部20aから第1第2遮断信号101をON状態にするための遮断素子駆動信号100を各遮断素子用の駆動回路21に出力する。すると、この駆動回路21は、ON状態とした遮断素子駆動信号101を第1遮断素子40および第2遮断素子42に出力する。第1第2遮断信号101をOFF状態にする場合は、ON/OFFが異なる他は同様である。

20

#### 【0038】

第1出力素子41と第2出力素子43をOFF診断するための所定のタイミングになると、MPU20の信号制御部20aは、第1第2遮断信号101をONした状態で、第1制御装置50、第2制御装置51の応答時間内で第1出力信号103と第2出力信号105とをそれぞれOFF状態にするための信号出力をを行う。

#### 【0039】

第1出力信号103をOFF状態にするには、MPU20の信号制御部20aから第1出力信号103をOFF状態にするための出力素子制御信号102を第1出力素子41用の駆動回路21に出力する。すると、この駆動回路21は、OFF状態とした第1出力信号103を第1出力素子41に出力する。第1出力信号103をON状態にする場合の信号出力は、ON/OFFが異なる他は同様である。

30

#### 【0040】

第2出力信号105をOFF状態にするには、MPU20の信号制御部20aから第2出力信号105をOFF状態にするための出力素子制御信号104を第2出力素子43用の駆動回路21に出力する。すると、この駆動回路21からOFF状態にした第2出力信号105を第2出力素子43に出力する。第2出力信号105をON状態にする場合の信号出力は、ON/OFFが異なる他は同様である。

#### 【0041】

MPU20の診断部20bは、このように第1出力信号103をOFFさせた時間に第1出力診断信号106の電圧のレベルを判断することで、第1出力素子41のOFF診断を行う。

40

また、MPU20の診断部20bは、第2出力信号105をOFFさせた時間に第2出力診断信号107の電圧のレベルを判断することで、第2出力素子43のOFF診断を行う。

#### 【0042】

次に、第1遮断素子40と第2遮断素子42のOFF診断のための各種信号の制御について説明する。

第1遮断素子40と第2遮断素子42をOFF診断するための所定のタイミングの前で

50

は、MPU20の信号制御部20aは、第1出力信号103および第2出力信号105について、直前の制御出力時のON又はOFF状態を継続して出力させる。

#### 【0043】

第1遮断素子40や第2遮断素子42をOFF診断するための所定のタイミングになると、MPU20の信号制御部20aは、第1出力信号103や第2出力信号105をON状態にするための信号出力をを行う。また、このタイミングでは、MPU20の信号制御部20aは、第1第2遮断信号101を第1制御装置50、第2制御装置51の応答時間内でOFF状態にするための信号出力をを行う。

#### 【0044】

MPU20の診断部20bは、第1第2遮断信号101をOFFした時間に第1出力診断信号106の電圧レベルを判断することで第1遮断素子40のOFF診断を行う。また、MPU20の診断部20bは、このように第1第2遮断信号101をOFFした時間に第2出力診断信号107の電圧レベルを判断することで第2遮断素子42のOFF診断を行う。

10

#### 【0045】

図3は、第1の実施形態における出力装置による出力素子OFF診断動作を説明するための図である。

図3では、第1出力素子41および第2出力素子43のOFF診断を時間経過に合わせて示している。

第1出力素子41と第2出力素子43のOFF診断は、第1出力素子41を第1制御装置50に接続して、第2出力素子43を第2制御装置51に接続した状態で行われる。このため、第1制御装置50、第2制御装置51の応答特性に合わせた診断時間を設け、MPU20の診断部20bは、この診断時間に第1出力素子41と第2出力素子43のOFF診断を行う。

20

#### 【0046】

図4は、第1の実施形態における出力装置による第1出力素子41と第2出力素子43のOFF診断のための手順の一例を示すフローチャートである。

MPU20の信号制御部20aは、初期状態では、第1出力素子41と第2出力素子43をOFF診断するタイミングとしての診断判定点(検出点)t0より時間tcr2だけ早い時刻t2より前では、第1第2遮断信号101をON出力し、第1出力信号103、第2出力信号105について、直前の制御出力時のON又はOFF状態を継続して出力させる(S1)。

30

#### 【0047】

そして、MPU20の信号制御部20aは、前述した時刻t2を計時すると(S2)、第2出力素子43のOFF診断のために、第2出力素子43用の駆動回路21を介して、応答特性の遅い第2制御装置51側の第2出力素子43の駆動信号としての第2出力信号105をOFF状態にするための信号出力をを行う(S3)。

#### 【0048】

MPU20の信号制御部20aは、診断判定点t0より時間tcr1だけ早い時刻t1より前では、第1出力信号103について、直前の制御出力時のON又はOFF状態を継続して出力させる。

40

#### 【0049】

次に、MPU20の信号制御部20aは、前述した時刻t1を計時すると(S4)、第1出力素子41のOFF診断のために、応答性の速い第1制御装置50側の第1出力素子41の駆動信号としての第1出力信号103をOFF状態にするための信号出力をを行う(S5)。

#### 【0050】

そして、MPU20の診断部20bは、診断判定点t0の時刻を計時すると(S6)、で第1出力素子41からの第1出力診断信号106と第2出力素子43からの第2出力診断信号107とを入力する(S7)。診断判定点t0以後は、MPU20の診断部20b

50

は、第1第2遮断信号101をON状態を継続して出力させるとともに、第1出力信号103、第2出力信号105について、直前の制御出力時のON又はOFF状態を継続して出力させる。

#### 【0051】

MPU20の診断部20bは、第1出力診断信号106の電圧レベルがLOWレベルであれば(S8のYES)、第1出力素子41は正常と判断し(S9)、この電圧レベルがHIGH(HI)レベルであれば(S8のNO)、第1出力素子41は故障と判断する(S10)。このようにして第1出力素子41のOFF診断が行える。

#### 【0052】

同様に、MPU20の診断部20bは、第2出力診断信号107の電圧レベルがLOWレベルであれば第2出力素子43は正常と判断し、この電圧レベルがHIGHレベルであれば第2出力素子43は故障と判断する。このようにして第2出力素子43のOFF診断が行える。

#### 【0053】

図5は、第1の実施形態における出力装置による遮断素子OFF診断動作を説明するための図である。図6は、第1の実施形態における出力装置による第1遮断素子と第2遮断素子のOFF診断のための手順の一例を示すフローチャートである。図7は、第1の実施形態における出力装置による、各種出力信号がONであるときの遮断素子診断動作を説明するための図である。

図5、図7では、第1遮断素子40および第2遮断素子42のOFF診断を時間経過に合わせて示している。

本実施形態では、第1遮断素子40と第2遮断素子42とを一括して制御する。第1第2遮断信号101、第1出力信号103、第2出力信号105の制御の一例を図7を参照して説明する。診断判定点t0より時間tcr1だけ早い時刻t1より前では、MPU20の信号制御部20aは、図7に示すように第1出力信号103、第2出力信号105について直前の制御のON又はOFF状態を継続して出力させる。この状態で、MPU20の信号制御部20aは、各遮断素子のOFF診断タイミングを応答特性の速い第1制御装置50にあわせて、図7に示すように、診断判定点t0より時間tcr1だけ早い時刻t1に第1出力信号103、第2出力信号105をONさせるとともに第1第2遮断信号101をOFFさせる。この場合、第1遮断素子40と第2遮断素子42とは同じ動作となる。

#### 【0054】

このため、第2出力素子43を応答特性の遅い第2制御装置51と接続していた場合、前述のように応答特性の速い第1制御装置50にあわせて時刻t2より遅い時刻t1に第2出力信号105をONとして第1第2遮断信号101をOFFさせると、図7に示すように、診断判定点t0での第2出力診断信号107の電圧レベルは、LOWレベルとHIGHレベルとの中間レベル(不定)を示してしまう。この場合、診断部20bによる第1遮断素子40と第2遮断素子42の故障診断が行えない。

#### 【0055】

次に、第1第2遮断信号101の制御のもう1つの例を説明する。診断判定点t0より時間tcr2だけ早い時刻t2より前では、MPU20の信号制御部20aは、第1出力信号103、第2出力信号105について直前の制御のON又はOFF状態を継続して出力させる。この状態で、各遮断素子のOFF診断タイミングを応答特性が遅い第2制御装置51にあわせて、MPU20の信号制御部20aは、診断判定点t0より時間tcr2だけ早い時刻t2に第1出力信号103、第2出力信号105をONさせるとともに第1第2遮断信号101をOFFさせる。しかし、このような制御とすると、第1第2遮断信号101がOFF状態となる時間が長くなるので、応答性が速い第1制御装置50は第1出力素子41のOFFを検出して誤動作する場合がある。

#### 【0056】

そこで、本実施形態では、第1または第2の出力信号をOFFからONにするときは出

10

20

30

40

50

力先の第1または第2の制御装置の応答時間が速い特性、および第1または第2の出力信号をONからOFFにするときは出力先の第1または第2の制御装置の応答時間が遅い特性を用いて、各遮断素子のOFF診断を行う。

#### 【0057】

図5に示すように、本実施形態では、診断判定点t0より時間tcr2だけ早い時刻t2に第2出力信号105をOFFとする。この時刻t2は第1第2遮断信号101をOFFにする時刻t1よりも前で、第2制御装置51の応答時間分だけ早い時刻である。

#### 【0058】

制御について時刻t2より前の時点から改めて説明する。まず、MPU20の信号制御部20aは、時刻t2より前では、各種駆動回路21を介して、第1第2遮断信号101をON状態とし、第1出力信号103、第2出力信号105について、直前の制御出力時のON又はOFF状態を継続して出力させる(S21)。

10

MPU20の信号制御部20aは、時刻t2を計時すると(S22)、第2出力信号105をOFF状態にするための信号出力を(S23)。

#### 【0059】

MPU20の信号制御部20aは、時刻t1より前では、第1出力信号103について、時刻t2より前と同様に、直前の制御出力時のON又はOFF状態を継続して出力させる。

次に、MPU20の信号制御部20aは、時刻t1を計時すると(S24)、第1第2遮断信号101をOFF状態にするための信号出力を(S25)とともに、第1出力信号103および第2出力信号105をON状態にするための信号出力を(S26)。

20

#### 【0060】

MPU20の診断部20bは、診断判定点t0を計時すると(S27)、第1出力診断信号106と第2出力診断信号107を入力する(S28)。診断判定点t0以後は、MPU20の診断部20bは、第1第2遮断信号101をON状態にするための信号出力を(S29)とともに、第1出力信号103、第2出力信号105について、直前の制御出力時のON又はOFF状態を継続して出力させる。

#### 【0061】

MPU20の診断部20bは、第1出力診断信号106の電圧レベルがLOWレベルであれば(S29のYES)、第1遮断素子40は正常と判断し(S30)、この電圧レベルがHIGHレベルであれば(S29のNO)、第1遮断素子40は故障と判断する(S31)。

30

#### 【0062】

また、MPU20の診断部20bは、第2出力診断信号107の電圧レベルがLOWレベルであれば第2遮断素子42は正常と判断し、この電圧レベルがHIGHレベルであれば第2遮断素子42は故障と判断する。

#### 【0063】

前述したように、従来では第1遮断素子40や第2遮断素子42のOFF診断のための所定のタイミングで第1出力信号103や第2出力信号105を一律のタイミングでON状態にしていた。これに対し、本実施形態では、MPU20は各制御装置の応答特性に合わせて、第1出力信号103や第2出力信号105を個別のタイミングでOFF状態にするための信号出力を(S32)。

40

#### 【0064】

具体的には、MPU20は、各種出力信号のうち、応答特性の遅い第2制御装置51に関わる第2出力信号105を、診断判定点t0より第2制御装置51の応答時間だけ早いタイミングでOFF状態にした後、この第2出力信号105を応答特性の速い第1制御装置50の応答時間に合わせた早いタイミングでON状態にする。これにより、応答特性の遅い第2制御装置51に関わる出力信号の電圧レベルが診断判定点t0において中間レベルになってしまふことを防止できる。

50

**【0065】**

また、MPU20は、各種出力信号のうち、応答特性の速い制御装置に関わる出力信号を、この制御装置の応答時間だけ早いタイミングにON状態にする。これにより、第1第2遮断信号101を不必要に早いタイミングでOFF状態にする必要がなくなる。よって、第1第2遮断信号101がOFF状態となる時間が長くなることに起因して、応答性が速い第1制御装置50が第1出力素子41のOFFを検出して誤動作することを防止できる。

**【0066】**

よって、各種遮断素子用の駆動回路21を共通の1つの回路とした場合でも、第1遮断素子40や第2遮断素子42の診断判定点t0における第1出力診断信号106と第2出力診断信号107の電圧レベルに基づいて第1遮断素子40や第2遮断素子42のOFF診断を正しく行うことができる。10

**【0067】**

つまり、各制御装置の応答特性に応じた各遮断素子を一括して診断するための時間を確保することが可能となり、各デジタル出力回路の負荷の応答特性に応じて各遮断素子を一括して診断することができる。

**【0068】****(第2の実施形態)**

次に、本発明の第2の実施形態について説明する。なお、本実施形態における出力装置の機能のうち図1に示した機能と同一の機能には同一の符号を付してその詳しい説明を省略し、ここでは異なる機能について主に述べる。20

図8は、第2の実施形態における出力装置の構成例を示す回路図である。

出力装置10の第1デジタル出力回路30と第2デジタル出力回路31と、各種駆動回路21との接続については図1に示した構成と同じである。

図8に示した構成はいわゆるシンク駆動の制御装置を負荷とする構成である。図1に示した構成と異なる点として、第1遮断素子40および第2遮断素子42のソースは、外部電源装置マイナス線121を介して外部電源装置52のマイナス側に接続される。

外部電源装置52のプラス側は、外部電源装置プラス線120を介して第1制御装置50および第2制御装置51の入力端に接続される。

**【0069】**

第1制御装置50の出力端は第1出力素子41のドレインおよびMPU20に接続される。つまり、第1出力診断信号106は第1制御装置50から出力される。

第2制御装置51の出力端は第2出力素子43のドレインおよびMPU20に接続される。つまり、第2出力診断信号107は第2制御装置51から出力される。

**【0070】**

第1出力素子41のソースは、第1遮断素子第1出力素子接続線123を介して第1遮断素子40のドレインに接続される。つまり、第1出力素子41と第1遮断素子40との接続関係が図1に示した構成と逆になっている。

**【0071】**

第2出力素子43のソースは、第2遮断素子第2出力素子接続線124を介して第2遮断素子42のドレインに接続される。つまり、第2出力素子43と第2遮断素子42との接続関係が図1に示した構成と逆になっている。40

**【0072】**

図9は、第2の実施形態における出力装置による出力素子診断動作を説明するための図である。

図9では、第1出力素子41と第2出力素子43のOFF診断を時間経過に合わせて示している。

第1の実施形態と同様に、第1デジタル出力回路30の第1出力素子41に接続される第1制御装置50には応答性の速い、例えば時定数の小さい( $t_{cr1} < t_{cr2}$ )制御装置が用いられる。また、第2デジタル出力回路31の第2出力素子43に接続される第50

2 制御装置 5 1 には応答性の遅い、例えば時定数の大きい ( $t_{c r 2} > t_{c r 1}$ ) 制御装置が用いられる。

#### 【 0 0 7 3 】

図 1 0 は、第 2 の実施形態における出力装置による第 1 出力素子と第 2 出力素子の O F F 診断のための手順の一例を示すフロー チャートである。

まず、第 1 の実施形態で説明した S 1 から S 5 までの、診断判定点  $t_0$  より時間  $t_{c r 2}$  だけ早い時刻  $t_2$  を計時したときや診断判定点  $t_0$  より時間  $t_{c r 1}$  だけ早い時刻  $t_1$  を計時したときの各種信号の制御がなされる (S 4 1 ~ S 4 5)。

#### 【 0 0 7 4 】

そして、M P U 2 0 の信号制御部 2 0 a は、診断判定点  $t_0$  の時刻を計時すると (S 4 10 6)、第 1 制御装置 5 0 からの第 1 出力診断信号 1 0 6 の電圧レベルと第 2 制御装置 5 1 からの第 2 出力診断信号 1 0 7 を入力する (S 4 7)。

#### 【 0 0 7 5 】

M P U 2 0 の診断部 2 0 b は、第 1 出力診断信号 1 0 6 の電圧レベルが H I G H レベルであれば (S 4 8 の Y E S)、第 1 出力素子 4 1 は正常と判断し (S 4 9)、この電圧レベルが L O W レベルであれば (S 4 8 の N O)、第 1 出力素子 4 1 は故障と判断する (S 5 0)。

#### 【 0 0 7 6 】

同様に、M P U 2 0 の診断部 2 0 b は、第 2 出力診断信号 1 0 7 の電圧レベルが H I G H レベルであれば第 2 出力素子 4 3 は正常と判断し、この電圧レベルが L O W レベルであれば第 2 出力素子 4 3 は故障と判断する。 20

#### 【 0 0 7 7 】

図 1 1 は、第 1 の実施形態における出力装置による遮断素子診断動作を説明するための図である。

図 1 1 では、第 1 遮断素子 4 0 と第 2 遮断素子 4 2 の O F F 診断を時間経過に合わせて示している。

図 1 2 は、第 1 の実施形態における出力装置による第 1 遮断素子と第 2 遮断素子の O F F 診断のための手順の一例を示すフロー チャートである。

まず、第 1 の実施形態で説明した S 2 1 から S 2 6 までの、診断判定点  $t_0$  より時間  $t_{c r 2}$  だけ早い時刻  $t_2$  を計時したときや診断判定点  $t_0$  より時間  $t_{c r 1}$  だけ早い時刻  $t_1$  を計時したときの各種信号の制御がなされる (S 6 1 ~ S 6 6)。 30

#### 【 0 0 7 8 】

次に、M P U 2 0 の診断部 2 0 b は、診断判定点  $t_0$  を計時すると (S 6 7)、第 1 出力診断信号 1 0 6 と第 2 出力診断信号 1 0 7 を入力する (S 6 8)。

M P U 2 0 の診断部 2 0 b は、第 1 出力診断信号 1 0 6 の電圧レベルが H I G H レベルであれば (S 6 9 の Y E S)、第 1 遮断素子 4 0 は正常と判断し (S 7 0)、この電圧レベルが L O W レベルであれば (S 6 9 の N O)、第 1 遮断素子 4 0 は故障と判断する (S 7 1)。

#### 【 0 0 7 9 】

同様に、M P U 2 0 の診断部 2 0 b は、第 2 出力診断信号 1 0 7 の電圧レベルが H I G H レベルであれば第 2 遮断素子 4 2 は正常と判断し、この電圧レベルが L O W レベルであれば第 2 遮断素子 4 2 は故障と判断する (S 7 1)。 40

このように、第 2 の実施形態では、シンク駆動を用いた構成でも第 1 の実施形態と同様の効果を得ることができる。

#### 【 0 0 8 0 】

なお、上記の各実施形態に記載した手法は、コンピュータに実行させることのできるプログラムとして、磁気ディスク (フロッピー (登録商標) ディスク、ハードディスクなど)、光ディスク (C D - R O M、D V D など)、光磁気ディスク (M O)、半導体メモリなどの記憶媒体に格納して頒布することもできる。

また、この記憶媒体としては、プログラムを記憶でき、かつコンピュータが読み取り可 50

能な記憶媒体であれば、その記憶形式は何れの形態であっても良い。

また、記憶媒体からコンピュータにインストールされたプログラムの指示に基づきコンピュータ上で稼働しているOS（オペレーティングシステム）や、データベース管理ソフト、ネットワークソフト等のMW（ミドルウェア）等が上記実施形態を実現するための各処理の一部を実行しても良い。

さらに、各実施形態における記憶媒体は、コンピュータと独立した媒体に限らず、LANやインターネット等により伝送されたプログラムをダウンロードして記憶または一時記憶した記憶媒体も含まれる。

また、記憶媒体は1つに限らず、複数の媒体から上記の各実施形態における処理が実行される場合も本発明における記憶媒体に含まれ、媒体構成は何れの構成であっても良い。

10 なお、各実施形態におけるコンピュータは、記憶媒体に記憶されたプログラムに基づき、上記の各実施形態における各処理を実行するものであって、パソコン等の1つからなる装置、複数の装置がネットワーク接続されたシステム等の何れの構成であっても良い。

また、各実施形態におけるコンピュータとは、パソコンに限らず、情報処理機器に含まれる演算処理装置、マイコン等も含み、プログラムによって本発明の機能を実現することが可能な機器、装置を総称している。

発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

20

#### 【符号の説明】

#### 【0081】

10 ...出力装置、20 ...MPU、21 ...駆動回路、30 ...第1デジタル出力回路、31 ...第2デジタル出力回路、40 ...第1遮断素子、41 ...第1出力素子、42 ...第2遮断素子、43 ...第2出力素子、50 ...第1制御装置、51 ...第2制御装置、52 ...外部電源装置、100 ...遮断素子制御信号、101 ...遮断素子駆動信号、102 ...第1出力素子制御信号、103 ...第1出力素子駆動信号、104 ...第2出力素子制御信号、105 ...第2出力素子駆動信号、106 ...第1出力診断信号、107 ...第2出力診断信号、110 ...第1遮断素子制御信号、111 ...第1遮断素子駆動信号、112 ...第2遮断素子制御信号、113 ...第2遮断素子駆動信号、120 ...外部電源プラス線、121 ...外部電源マイナス線、123 ...第1遮断素子第1出力素子接続線、124 ...第2遮断素子第2出力素子接続線。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100172580

弁理士 赤穂 隆雄

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(72)発明者 毛利 文隆

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 登古 誠

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 中谷 博司

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 大西 直哉

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 野島 章

東京都港区三田三丁目13番16号 東芝三菱電機産業システム株式会社内

審査官 川東 孝至

(56)参考文献 特開2012-226426(JP,A)

特開2000-298515(JP,A)

特開2013-054427(JP,A)

特開2002-082714(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 05 B 23/00 - 23/02

G 05 B 9/00 - 9/05

G 05 B 19/04 - 19/05

H 03 K 17/74 - 17/98