(12) 发明专利

(10) 授权公告号 CN 107710418 B

(45) 授权公告日 2021.08.10

(21) 申请号 201680033538.X

(22) 申请日 2016.05.09

(65) 同一申请的已公布的文献号

申请公布号 CN 107710418 A

(43) 申请公布日 2018.02.16

(30) 优先权数据

14/706,927 2015.05.07 US

(85) PCT国际申请进入国家阶段日

2017.12.08

(86) PCT国际申请的申请数据

PCT/US2016/031517 2016.05.09

(87) PCT国际申请的公布数据

W02016/179598 EN 2016.11.10

(73) 专利权人 德克萨斯仪器股份有限公司

地址 美国德克萨斯州

(72) 发明人 H·卡瓦哈勒 S·斯瑞达

C·B·科措 S·J·莫洛伊

H·杨

(74) 专利代理机构 北京纪凯知识产权代理有限公司 11245

代理人 赵志刚 赵蓉民

(51) Int.CI.

H01L 29/78 (2006.01)

审查员 倪敬涵

权利要求书3页 说明书10页 附图28页

(54) 发明名称

多屏蔽沟槽栅极场效应晶体管

(57) 摘要

在所描述的示例中，半导体器件(100)包含具有在沟槽(110)中的沟槽栅极(120)的垂直型MOS晶体管(104)，该沟槽(110)通过垂直的漂移区域(108)延伸到漏极区域(106)。沟槽(110)在栅极(120)下具有场板(116)。场板(116)邻近漏极区域(108)并极有多个段(122)和(124)。在沟槽(110)中的将场板(116)与漂移区域(108)分离的电介质衬垫(112)具有比在栅极(120)和主体(130)之间的栅极电介质层(118)大的厚度。相比于紧接栅极(120)下面的上段(124)，电介质衬垫(112)在沟槽(110)的底部(114)处在场板(116)的下段(122)上更厚。

1. 一种半导体器件，其包含：

包括半导体材料的衬底；

布置在所述衬底的所述半导体材料中的垂直型金属氧化物半导体晶体管即垂直型MOS晶体管的漏极区域；

在所述半导体材料中布置在所述漏极区域上方的所述垂直型MOS晶体管的垂直漂移区域；

在所述衬底中布置在所述垂直漂移区域中的沟槽；

布置在所述沟槽中的电介质衬垫；

在所述沟槽中布置在所述电介质衬垫上方的所述垂直型MOS晶体管的栅极电介质层；

布置在所述沟槽中的所述垂直型MOS晶体管的沟槽栅极，其与所述栅极电介质层接触；

在所述衬底中布置在所述垂直漂移区域上方的所述垂直型MOS晶体管的主体；以及

多个场板段，其布置在所述沟槽中，通过所述电介质衬垫与所述衬底分开，所述多个场板段包括：在所述沟槽的底部处的下场板段；和布置在所述下场板段上方并且在所述沟槽栅极下面的上场板段，所述下场板段加上所述上场板段处于RESURF配置；

其中，在所述沟槽的侧壁上布置的在所述下场板段与所述衬底之间的所述电介质衬垫比在所述沟槽的所述侧壁上布置的在所述上场板段与所述衬底之间的所述电介质衬垫厚，且在所述沟槽的所述侧壁上布置的在所述上场板段与所述衬底之间的所述电介质衬垫比在所述沟槽的所述侧壁上布置的在所述沟槽栅极与所述衬底之间的所述栅极电介质层厚；

其中，所述上场板段与所述沟槽中的所述沟槽栅极连接。

2. 根据权利要求1的所述半导体器件，其中，所述上场板段与所述下场板段电绝缘。

3. 根据权利要求1的所述半导体器件，其中，所述上场板段与所述下场板段连接。

4. 根据权利要求1的所述半导体器件，其中，所述多个场板段包括布置在所述上场板段和所述下场板段之间的中场板段，且其中，将所述下场板段与所述衬底分离的所述电介质衬垫比将所述中场板段与所述衬底分离的所述电介质衬垫厚，且将所述中场板段与所述衬底分离的所述电介质衬垫比将所述上场板段与所述衬底分离的所述电介质衬垫厚。

5. 一种形成半导体器件的方法，其包含：

提供包括半导体材料的衬底；

在所述衬底中形成垂直型MOS晶体管的漏极区域；

在所述半导体材料中在所述漏极区域上方形成所述垂直型MOS晶体管的垂直漂移区域；

在所述垂直漂移区域中形成沟槽；

在所述沟槽中形成邻接所述衬底的电介质衬垫；

在所述沟槽中在所述电介质衬垫上形成下场板段；

移除所述下场板段上方的至少部分所述电介质衬垫；

在所述沟槽中在所述下场板段上方形成上场板段，其中，在所述上场板段和所述衬底之间的电介质材料提供在所述上场板段和所述衬底之间的所述电介质衬垫，且在所述沟槽的侧壁上布置的在所述下场板段与所述衬底之间的所述电介质衬垫比在所述沟槽的所述侧壁上布置的在所述上场板段与所述衬底之间的所述电介质衬垫厚；

从所述上场板段上方的所述沟槽中移除所述电介质衬垫；

在所述沟槽中在所述上场板段上方形成邻接所述衬底的所述垂直型MOS晶体管的栅极电介质层，所述栅极电介质层比在所述上场板段与所述衬底之间的所述电介质衬垫薄；

在所述沟槽中形成所述垂直型MOS晶体管的沟槽栅极，其与所述栅极电介质层接触；以及

在所述衬底中在所述垂直漂移区域上方形成邻接所述栅极电介质层的所述垂直型MOS晶体管的主体；

所述方法进一步包括在形成所述上场板段之前，移除所述下场板段上的电介质材料，使得所述上场板段与所述下场板段接触。

6. 根据权利要求5的所述方法，其中，在所述沟槽中形成所述电介质衬垫包括在所述沟槽中形成邻接所述衬底的热氧化层且在所述沟槽中在所述热氧化层上形成第一沉积二氧化硅层，使得所述下场板段在所述第一沉积二氧化硅层上。

7. 根据权利要求6的所述方法，其中：

移除在所述下场板段上方的至少部分所述电介质衬垫包括移除在所述下场板段上方的至少部分所述第一沉积二氧化硅层，留下在所述下场板段上方的适当位置中的大部分的所述热氧化层；以及

在所述上场板段和所述衬底之间的剩余热氧化层提供在所述上场板段和所述衬底之间的在所述沟槽的所述侧壁上的至少部分所述电介质衬垫。

8. 根据权利要求7的所述方法，包括在移除所述第一沉积二氧化硅层后且在形成所述上场板段之前，在所述下场板段上方在所述剩余热氧化层上形成第二沉积二氧化硅层，使得在所述沟槽的所述侧壁上的将所述上场板段与所述衬底分离的所述电介质衬垫包括所述第二沉积二氧化硅层。

9. 根据权利要求7的所述方法，其中，在所述下场板段上方在所述剩余热氧化层上形成所述上场板段，使得在所述下场板段上方的所述剩余热氧化层提供在所述沟槽的所述侧壁上的将所述上场板段与所述衬底分离的所述电介质衬垫。

10. 根据权利要求5的所述方法，其中，移除在所述下场板段上方的至少部分所述电介质衬垫包括移除在所述下场板段上方的所有所述电介质衬垫，且所述方法包括：

在形成所述下场板段后，在所述沟槽中在所述下场板段上方形成邻接所述衬底的热氧化层，使得所述热氧化层提供在所述沟槽的所述侧壁上在所述上场板段和所述衬底之间的至少部分所述电介质衬垫。

11. 根据权利要求5的所述方法，包括在形成所述沟槽栅极之前，移除在所述上场板段上的所述栅极电介质层，使得所述沟槽栅极与所述上场板段接触。

12. 根据权利要求5的所述方法，其中，在所述上场板段上的部分所述栅极电介质层上形成所述沟槽栅极，使得所述沟槽栅极与所述上场板段电绝缘。

13. 根据权利要求5的所述方法，其中，形成所述下场板段包括在所述沟槽中且在所述衬底的顶部表面之上形成多晶硅层，且从所述衬底的所述顶部表面之上和从部分所述沟槽中移除所述多晶硅层，留下在所述沟槽中的部分所述多晶硅层以提供所述下场板段。

14. 一种形成半导体器件的方法，其包含：

提供包括半导体材料的衬底；

在所述衬底中形成垂直型MOS晶体管的漏极区域；

在所述半导体材料中在所述漏极区域上方形成所述垂直型MOS晶体管的垂直漂移区域；

在所述垂直漂移区域中形成沟槽；

在所述沟槽中形成邻接所述衬底的热氧化层；

在所述沟槽中在所述热氧化层上形成第一沉积二氧化硅层；

在所述沟槽中在所述第一沉积二氧化硅层上形成下场板段，其中所述热氧化层和所述第一沉积二氧化硅层的组合提供在所述沟槽的侧壁上将所述下场板段与所述衬底分离的电介质衬垫；

在所述热氧化层上的所述沟槽中形成第二沉积二氧化硅层；

移除所述下场板段上方的至少部分所述第二沉积二氧化硅层，留下在所述下场板段上方的适当位置中的大部分的所述热氧化层；

在所述沟槽中在所述下场板段上方形成中间场板段，其中所述中间场板段接触所述下场板段，并且其中在所述中间场板段和所述衬底之间的剩余热氧化层提供在所述沟槽的所述侧壁上在所述中间场板段和所述衬底之间的至少部分所述电介质衬垫，且在所述沟槽的所述侧壁上布置的在所述下场板段与所述衬底之间的所述电介质衬垫比在所述沟槽的所述侧壁上布置的在所述中间场板段与所述衬底之间的所述电介质衬垫厚；

在所述热氧化层上的所述沟槽中形成第三沉积二氧化硅层；

移除所述中间场板段上方的至少部分所述第三沉积二氧化硅层，留下在所述中间场板段上方的适当位置中的大部分的所述热氧化层；

在所述沟槽中在所述中间场板段上方形成上场板段，其中所述上场板段与所述中间场板段电绝缘，并且其中在所述上场板段和所述衬底之间的剩余热氧化层提供在所述沟槽的所述侧壁上在所述上场板段和所述衬底之间的至少部分所述电介质衬垫，且在所述沟槽的所述侧壁上布置的在所述中间场板段与所述衬底之间的所述电介质衬垫比在所述沟槽的所述侧壁上布置的在所述上场板段与所述衬底之间的所述电介质衬垫厚；

从所述上场板段上方的所述沟槽中移除所述热氧化层；

在所述沟槽中在所述上场板段上方形成邻接所述衬底的所述垂直型MOS晶体管的栅极电介质层，其比在所述沟槽的所述侧壁上在所述上场板段与所述衬底之间的所述电介质衬垫薄；

在所述沟槽中形成所述垂直型MOS晶体管的沟槽栅极，其与所述栅极电介质层接触，其中所述上场板段接触所述沟槽栅极；以及

在所述衬底中在所述垂直漂移区域上方形成所述垂直型MOS晶体管的主体，其邻接所述栅极电介质层。

## 多屏蔽沟槽栅极场效应晶体管

### 技术领域

[0001] 本申请涉及半导体器件，且具体地，涉及在半导体器件中的垂直型MOS晶体管。

### 背景技术

[0002] 具有在沟槽中的沟槽栅极的垂直型金属氧化物半导体(MOS)晶体管具有栅极电介质层和栅极，该栅极穿过主体延伸到沟槽下，与主体下的垂直漂移区域邻接。由于栅极电介质层不支持在漂移区域中的高电场，所以沟槽必须比所期望的更深，以支持期望的操作电压。如果栅极电介质层的厚度增加，则不期望地增加处于开态的沟道区域的电阻。

### 发明内容

[0003] 在所描述的示例中，半导体器件包含具有在沟槽中的沟槽栅极的垂直型MOS晶体管。沟槽经过垂直型MOS晶体管的主体延伸到半导体器件的衬底中，从而邻近接该主体下面的垂直型MOS晶体管的漂移区域。沟槽具有在栅极下的场板。该场板邻近漏极区域并具有多个段。在沟槽中的将场板与漂移区域分离的电介质衬垫具有比在栅极和主体之间的栅极电介质层更大的厚度。相比于紧接栅极下面的上段，电介质衬垫在沟槽的底部处在场板的下段上更厚。

### 附图说明

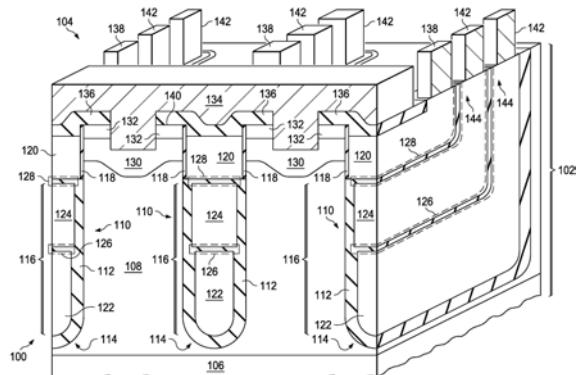

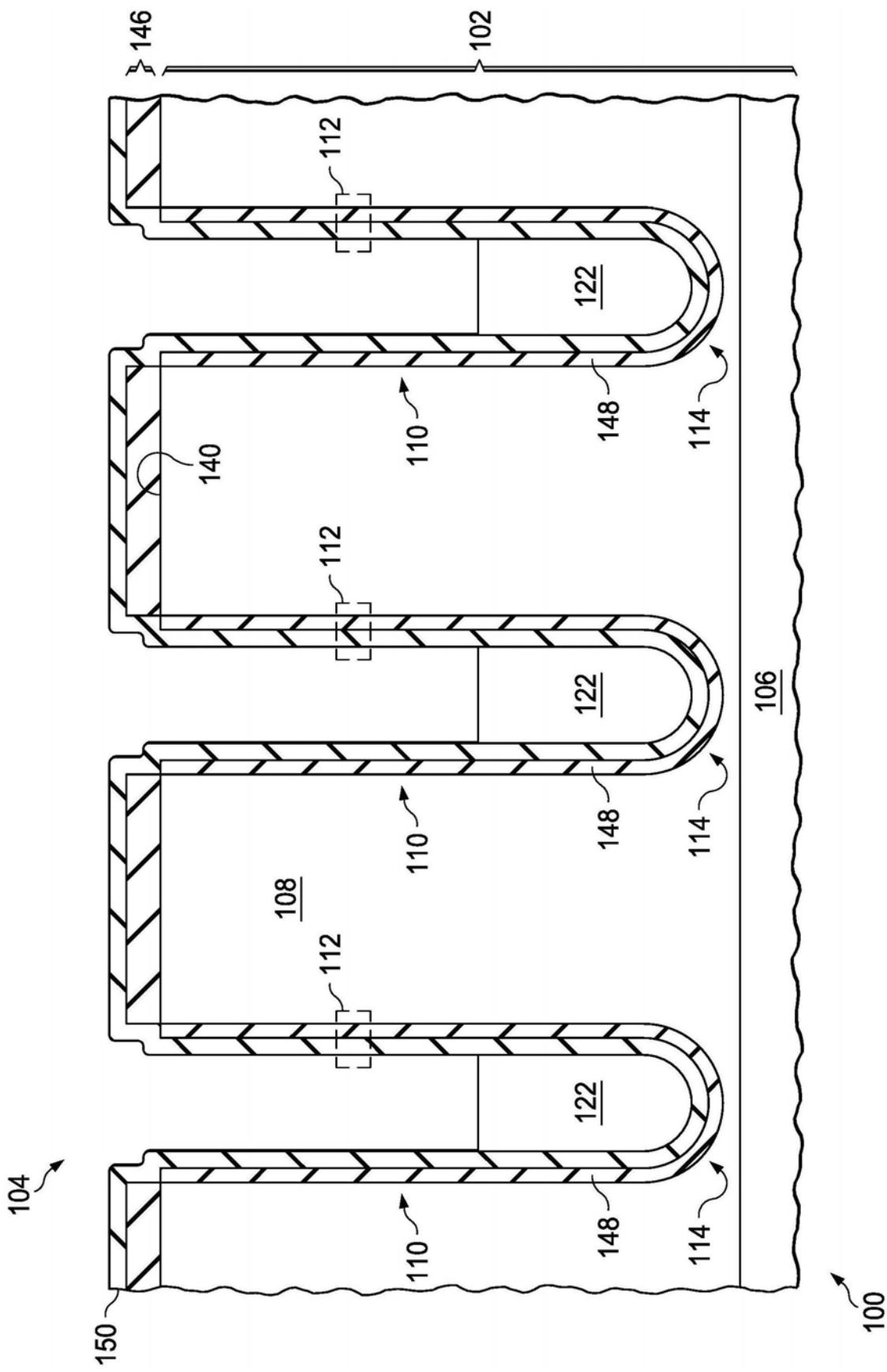

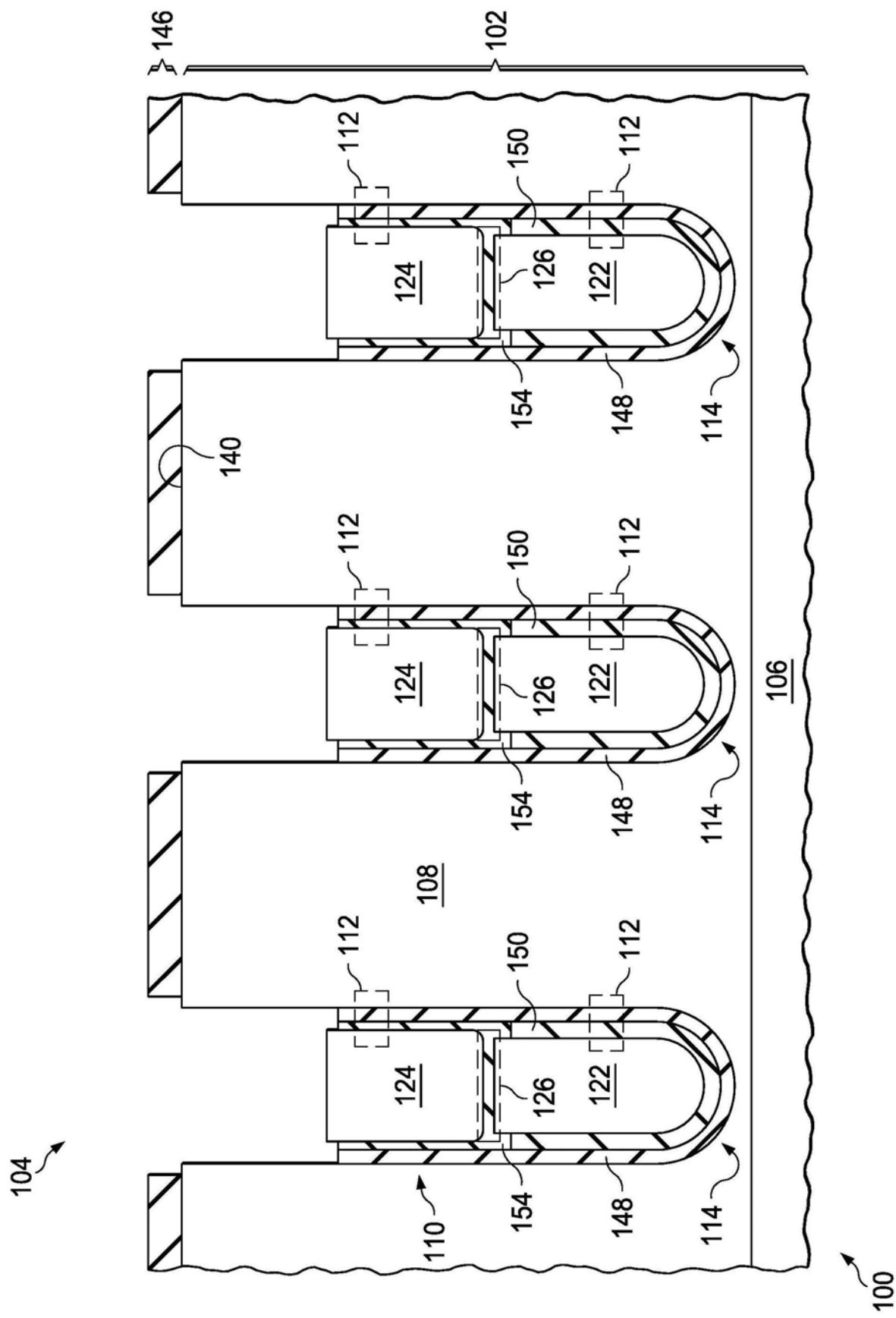

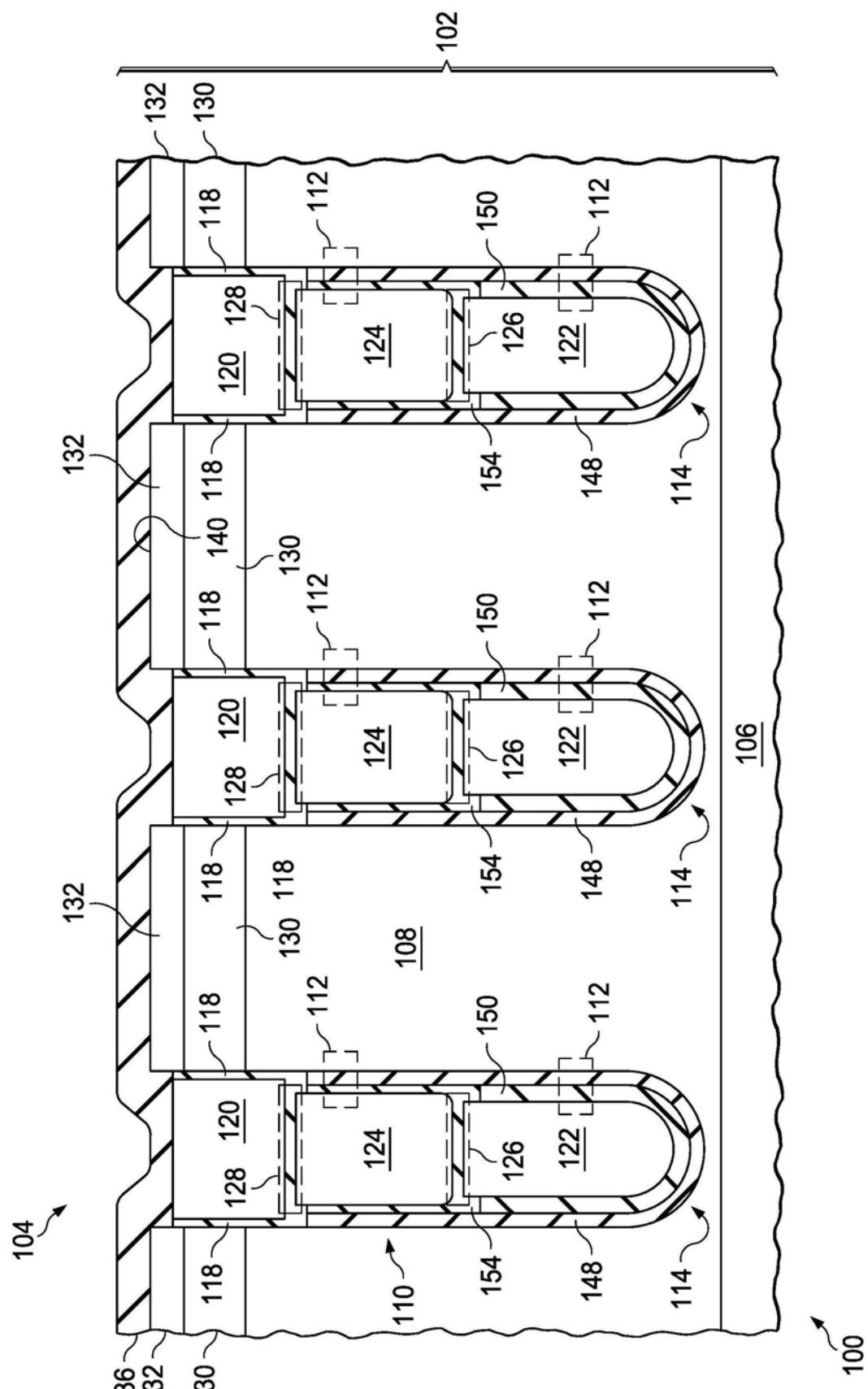

[0004] 图1是包含垂直型n沟道MOS晶体管的示例半导体器件的横截面图。

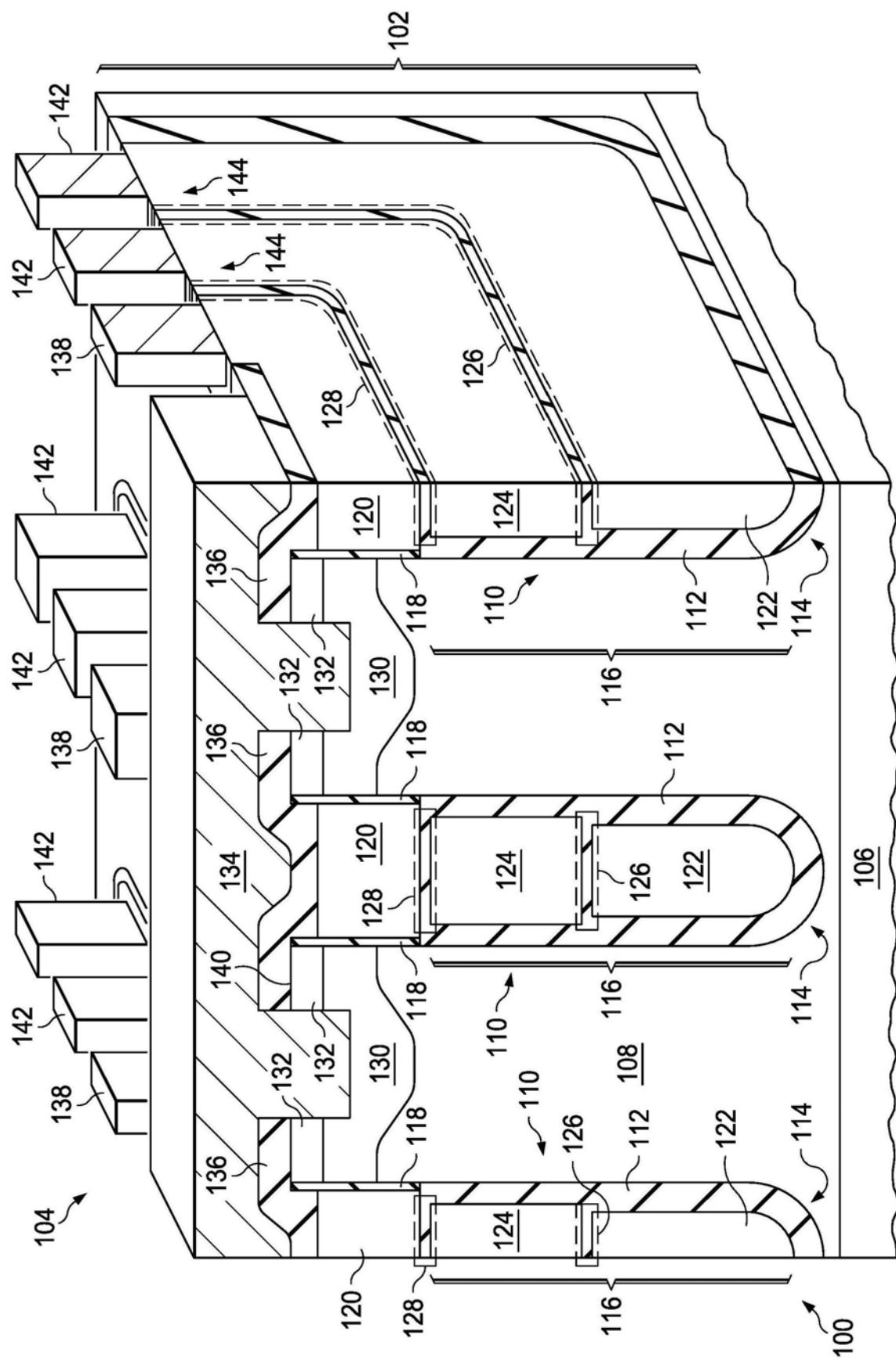

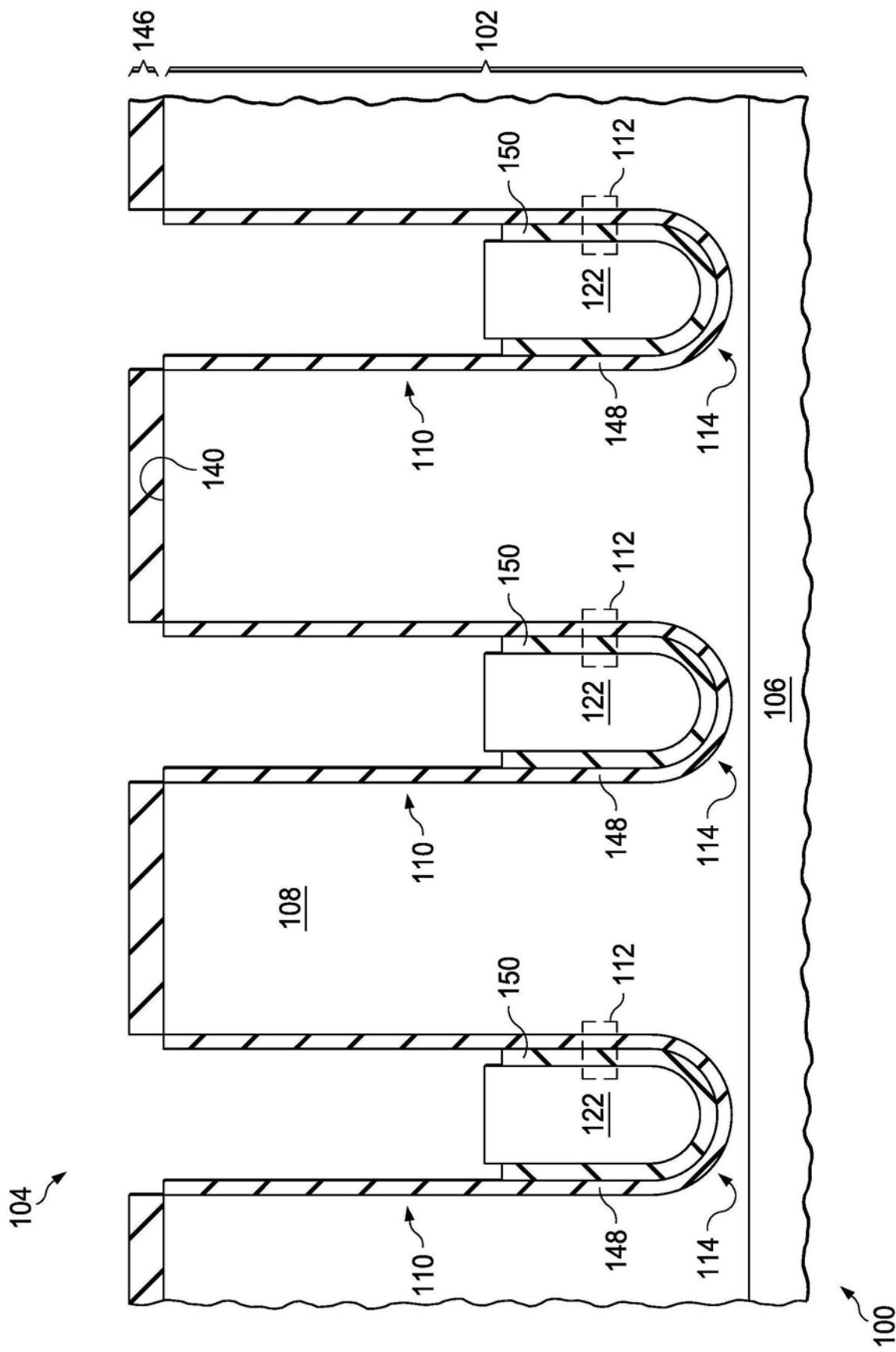

[0005] 图2A到图2K是在连续制造阶段中描绘的图1的半导体器件的横截面图。

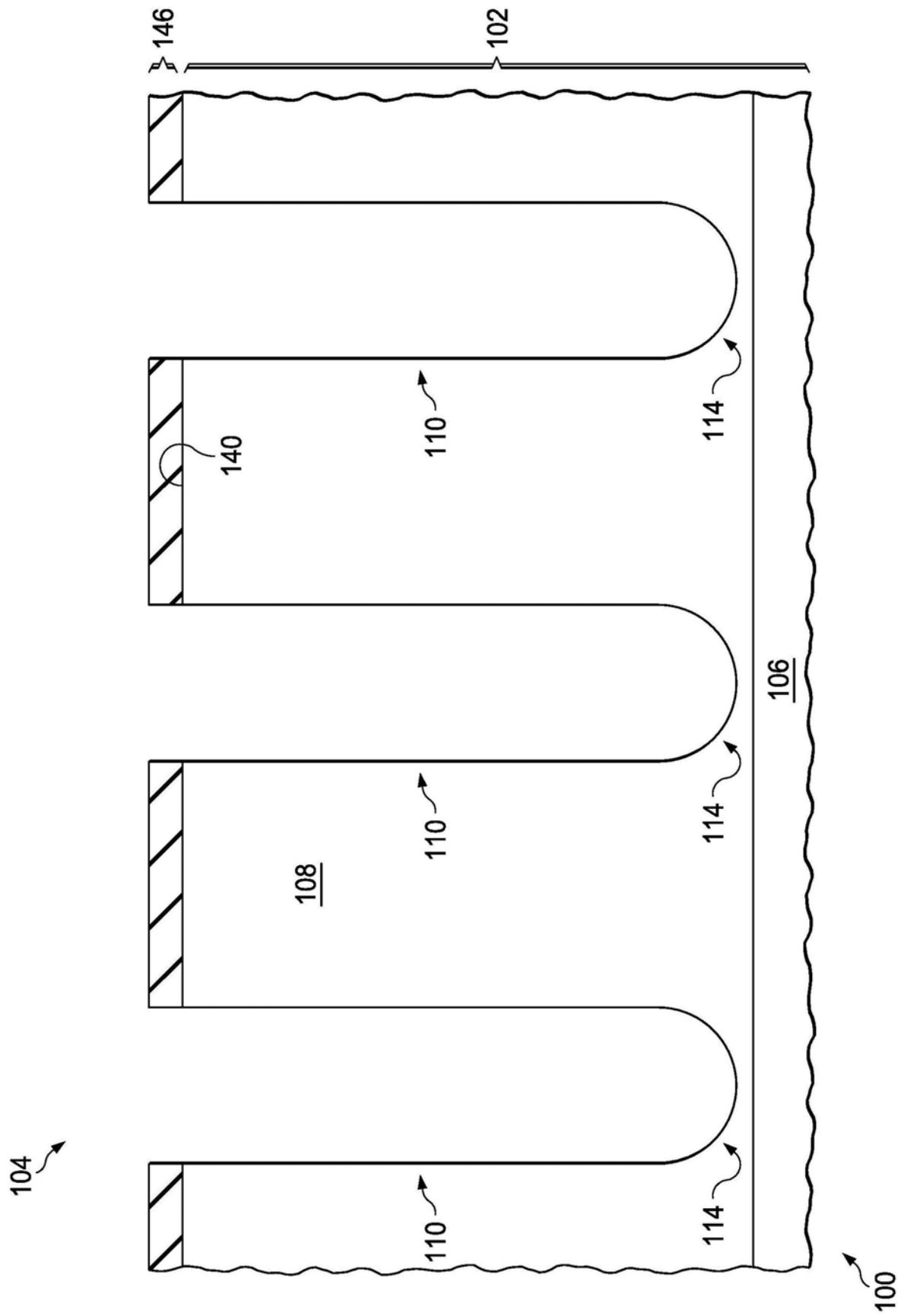

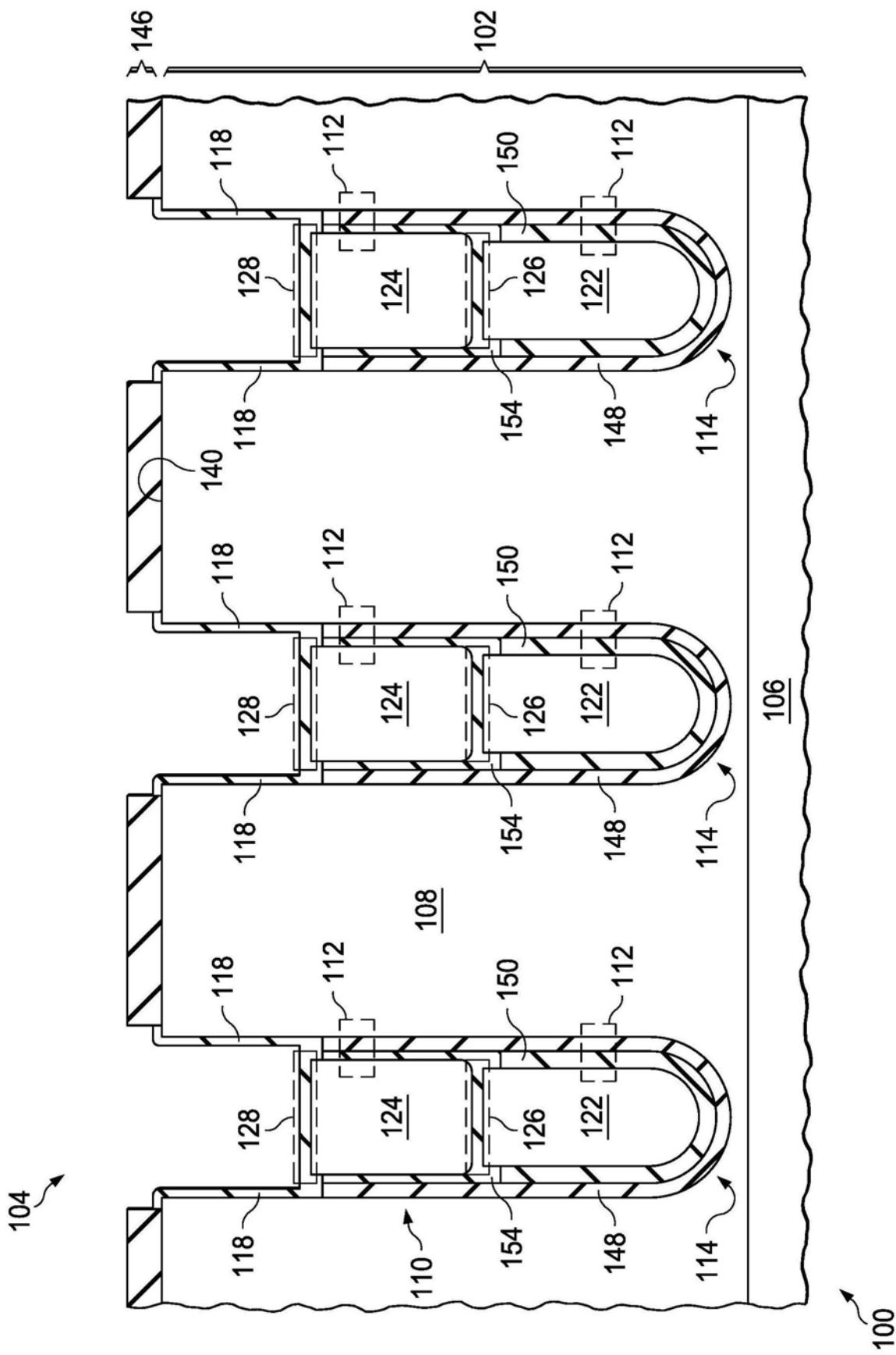

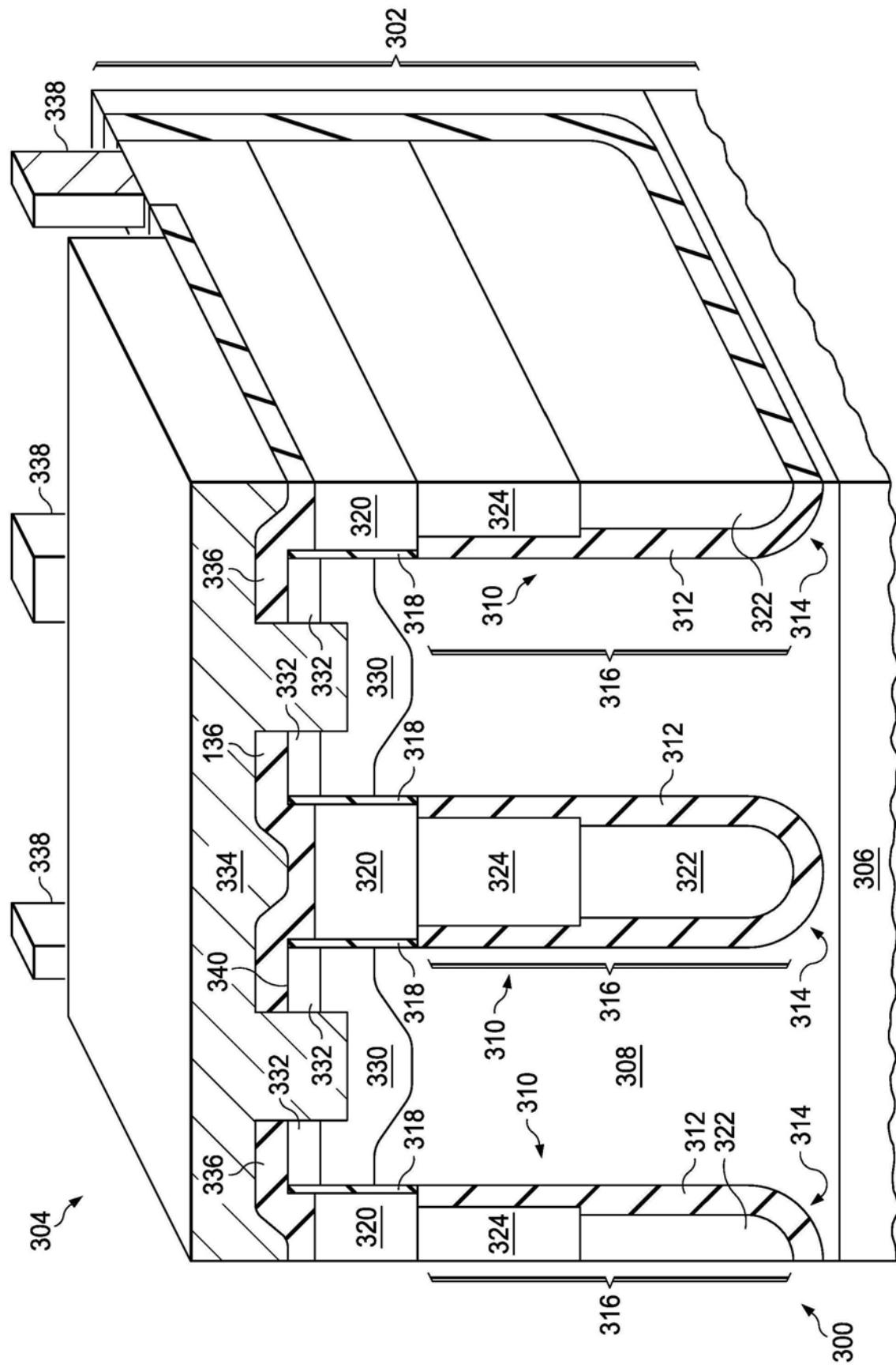

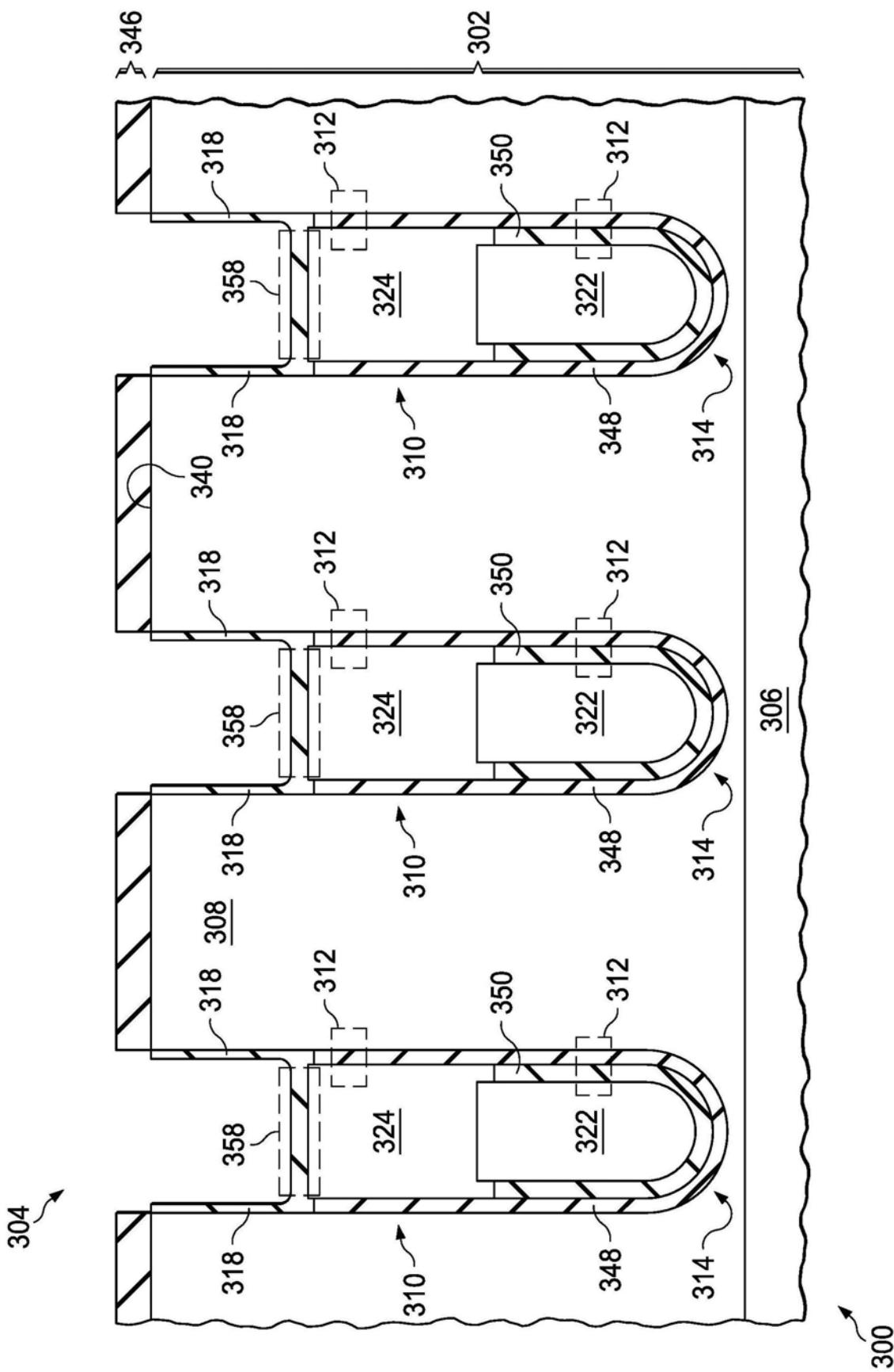

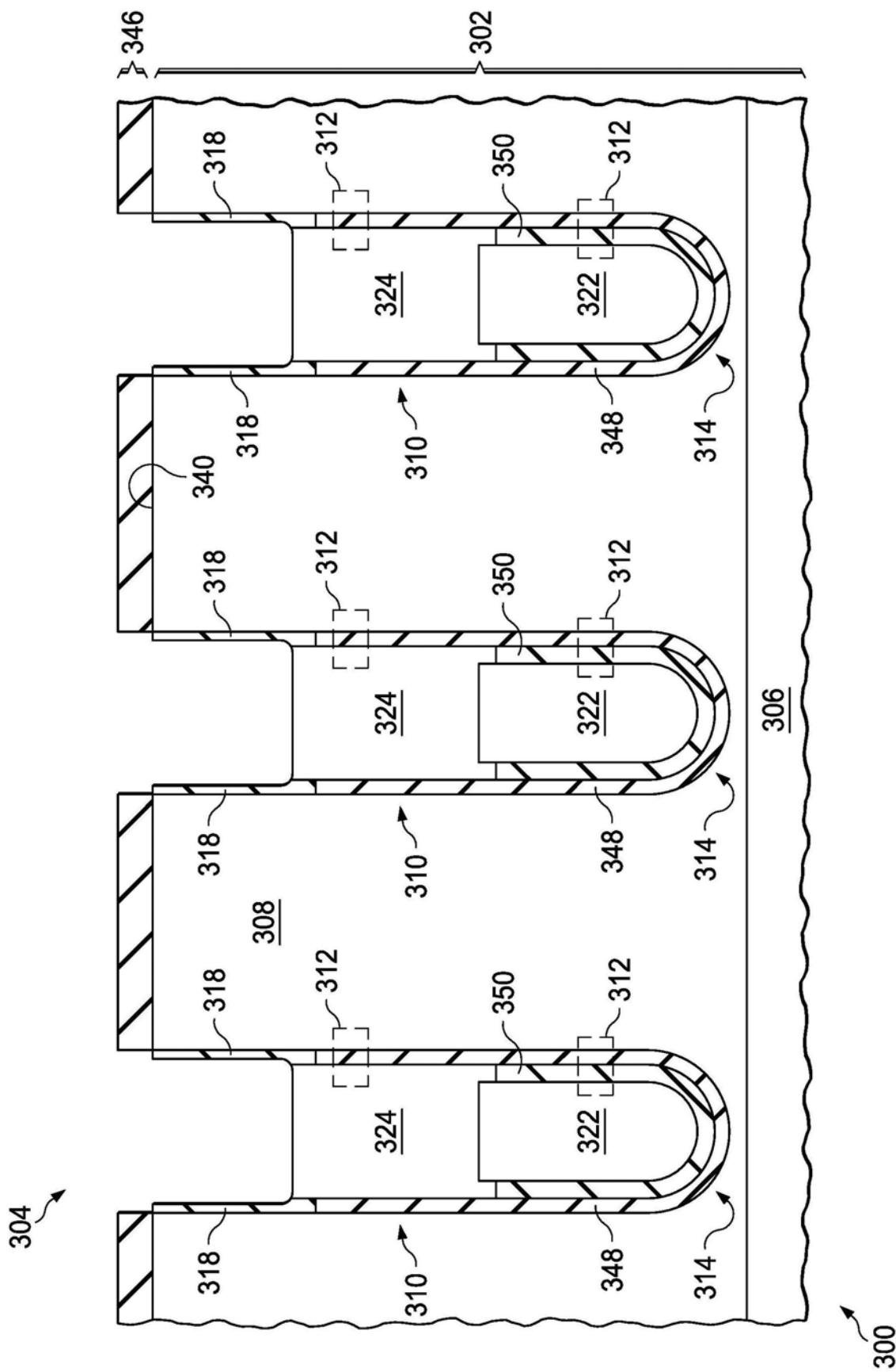

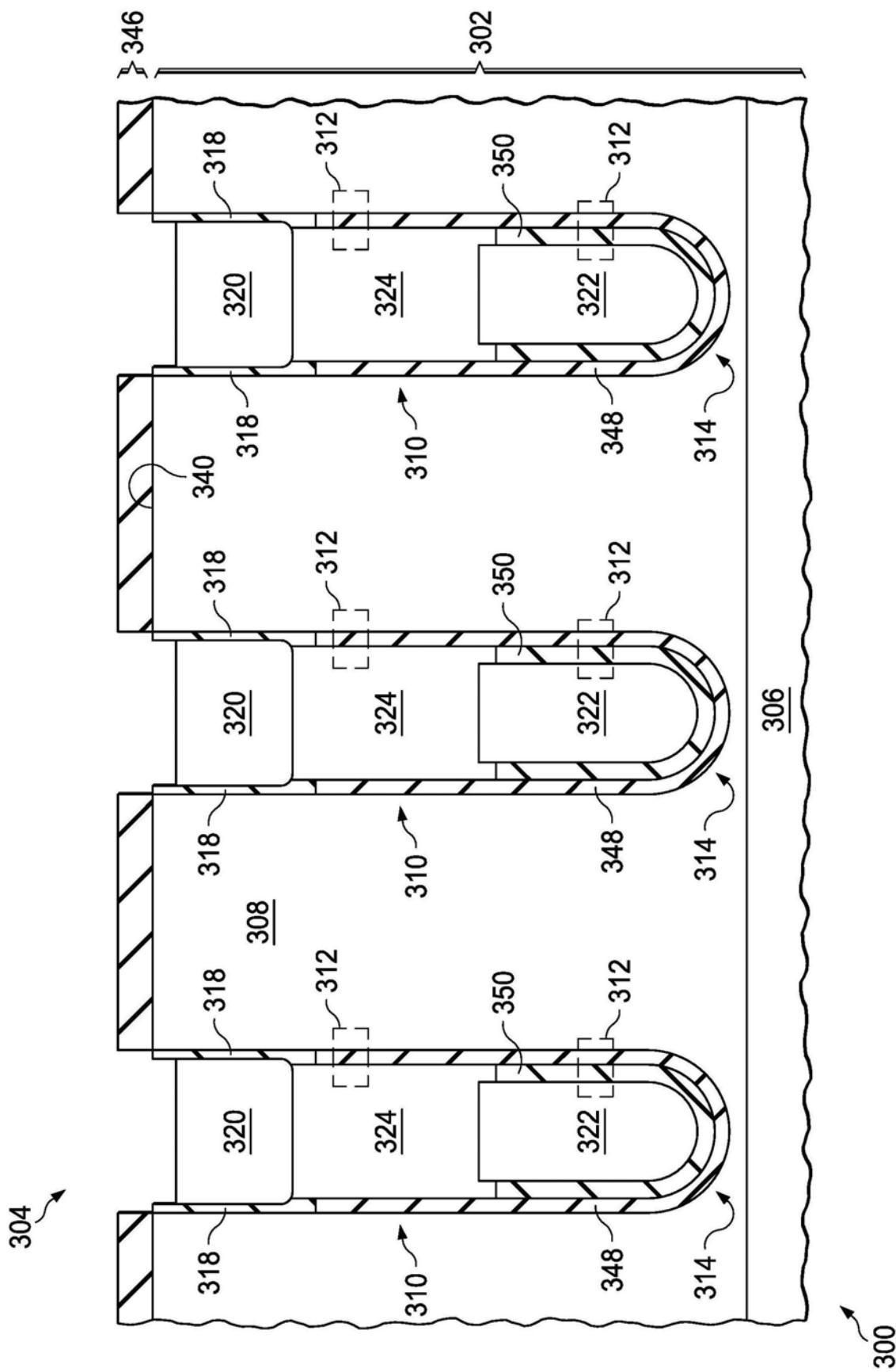

[0006] 图3是包含垂直型n沟道MOS晶体管的另一示例半导体器件的横截面图。

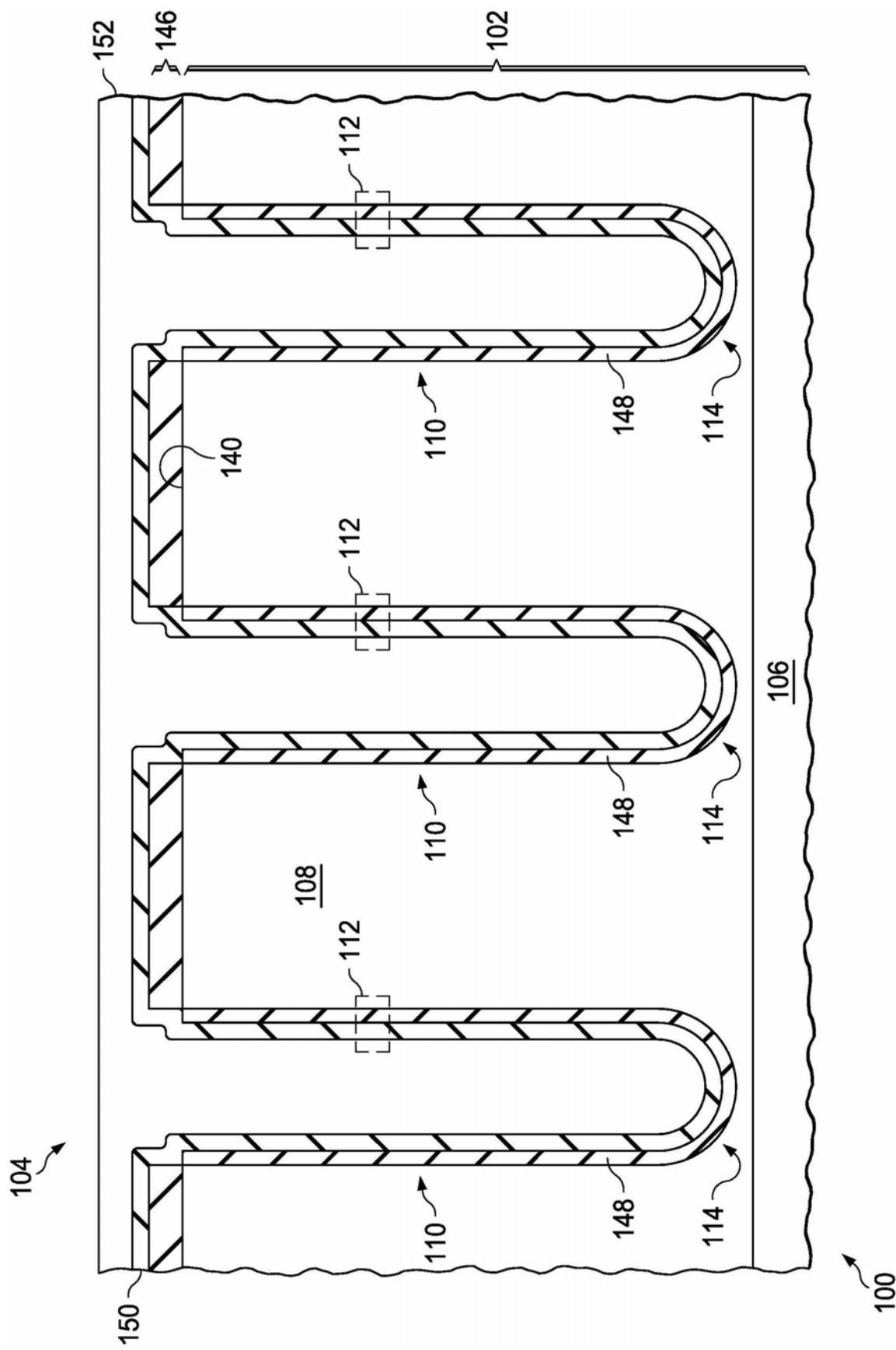

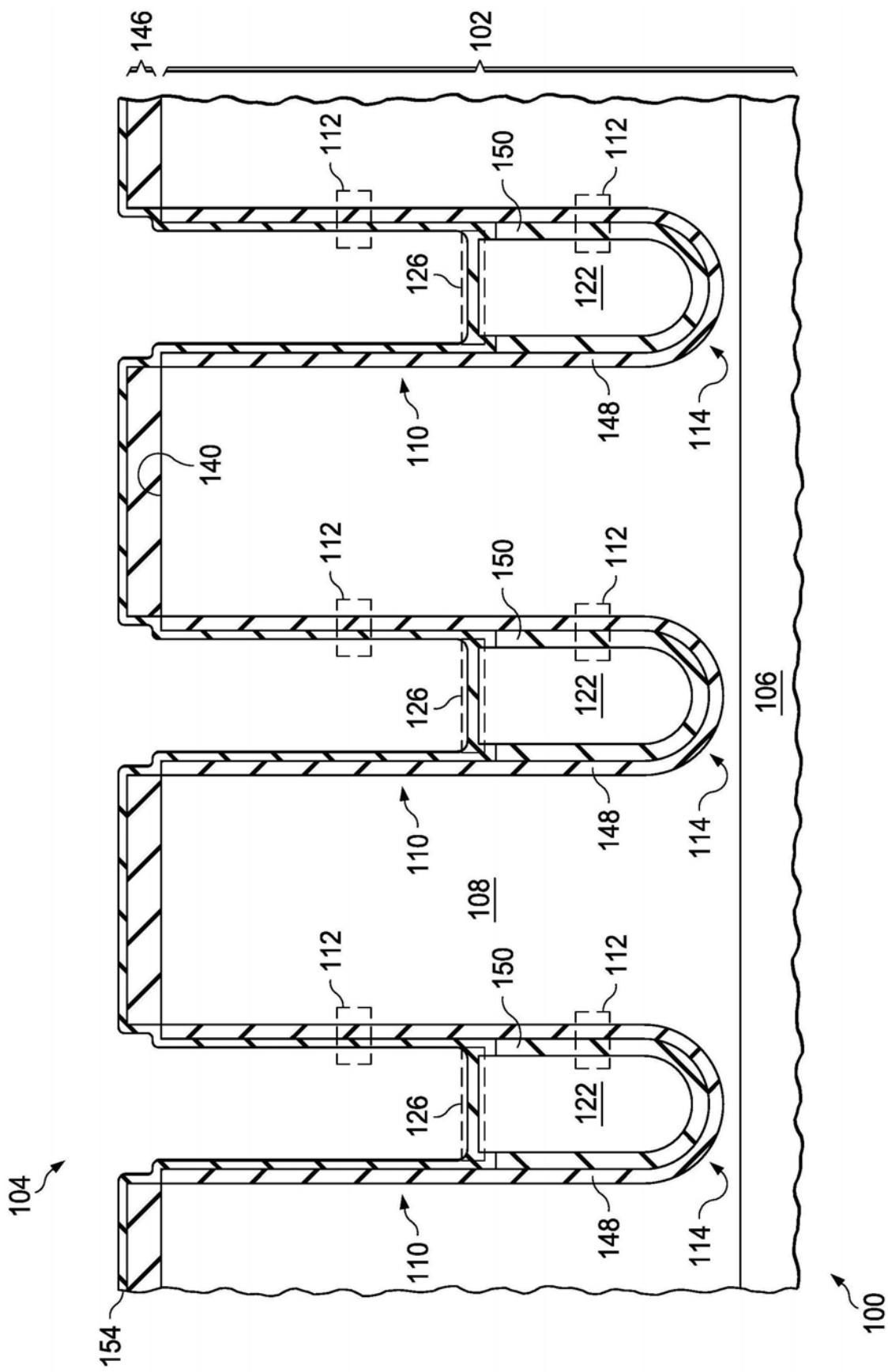

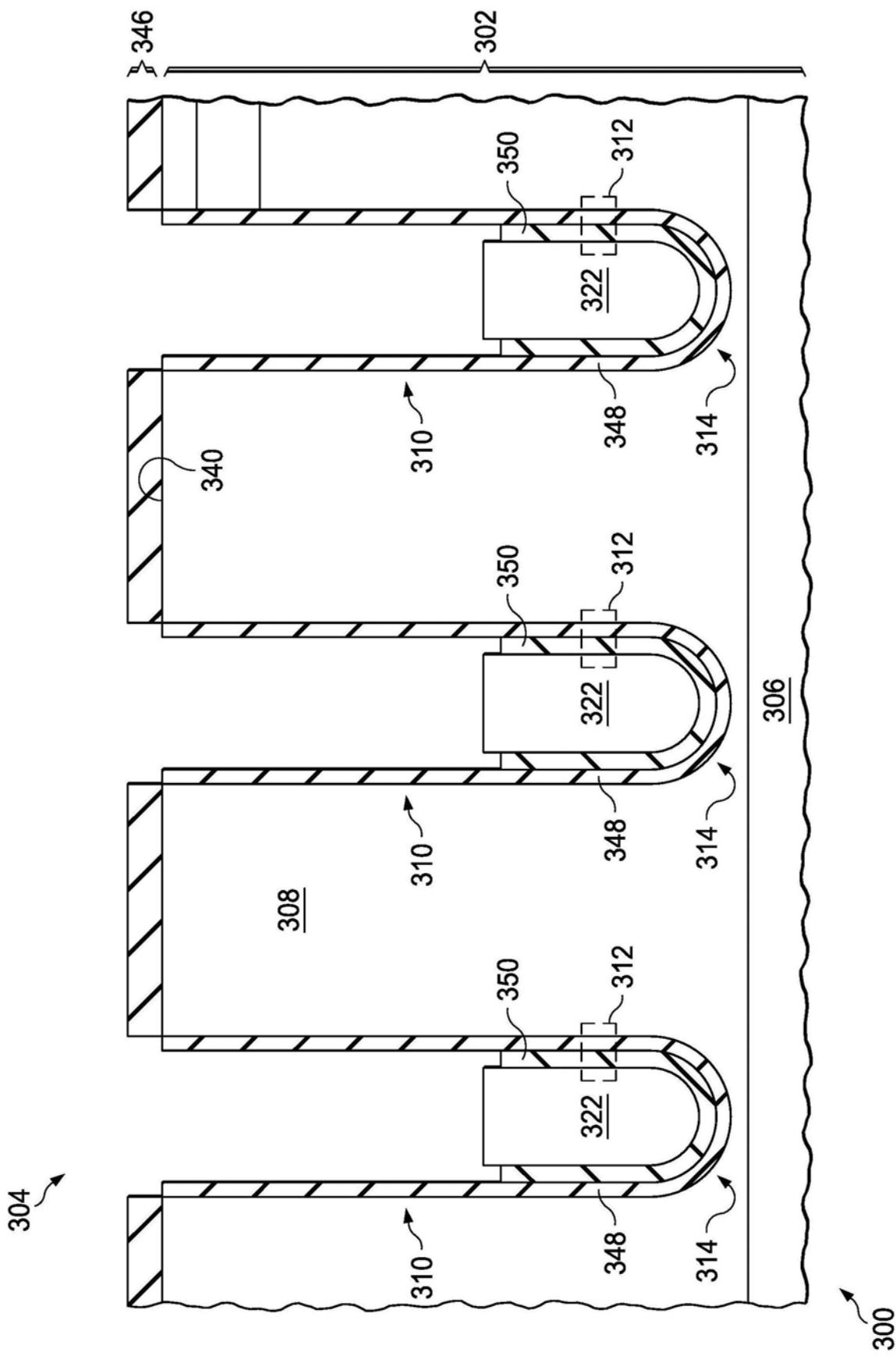

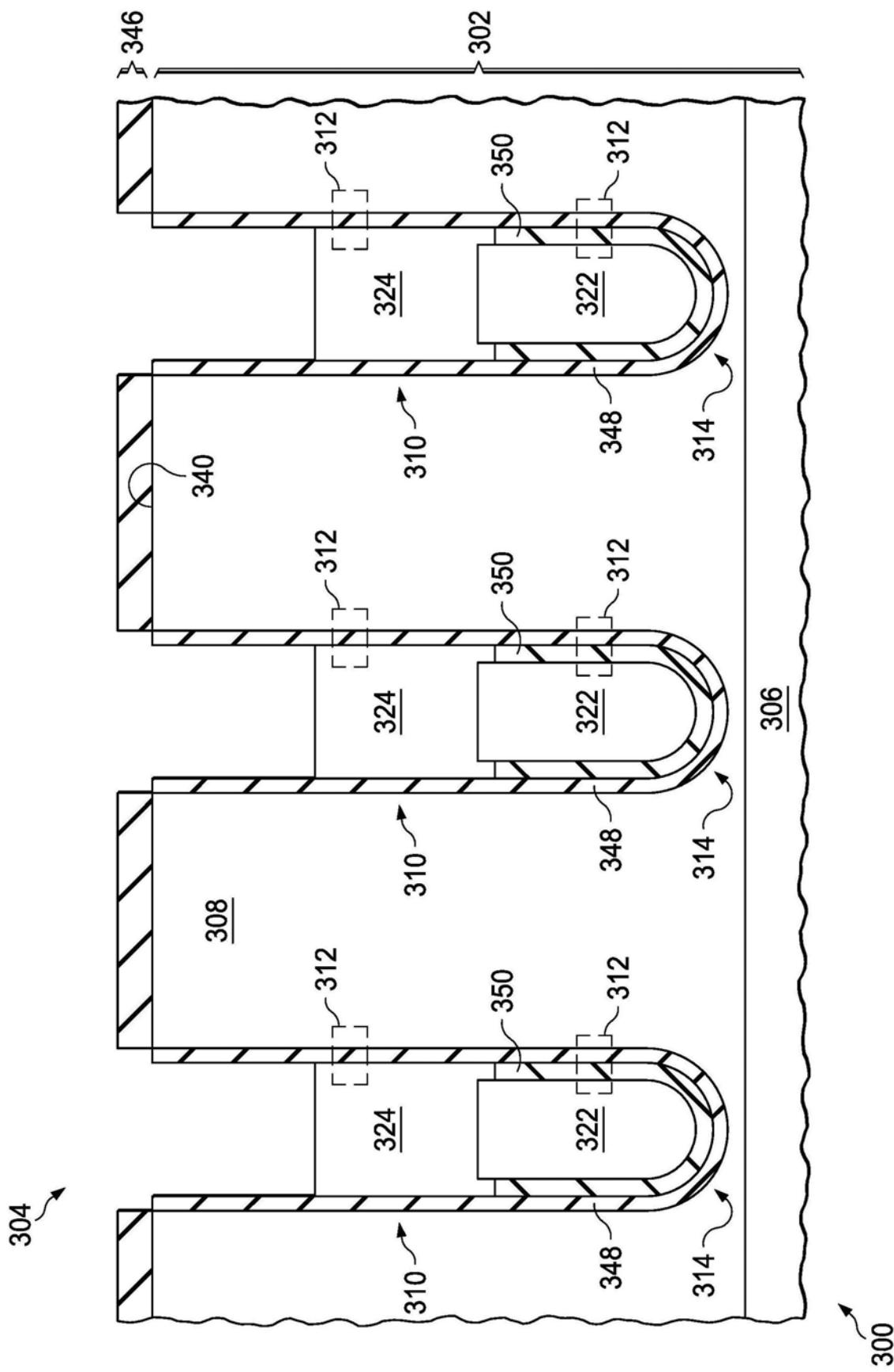

[0007] 图4A到图4E是在连续制造阶段中描绘的图3的半导体器件的横截面图。

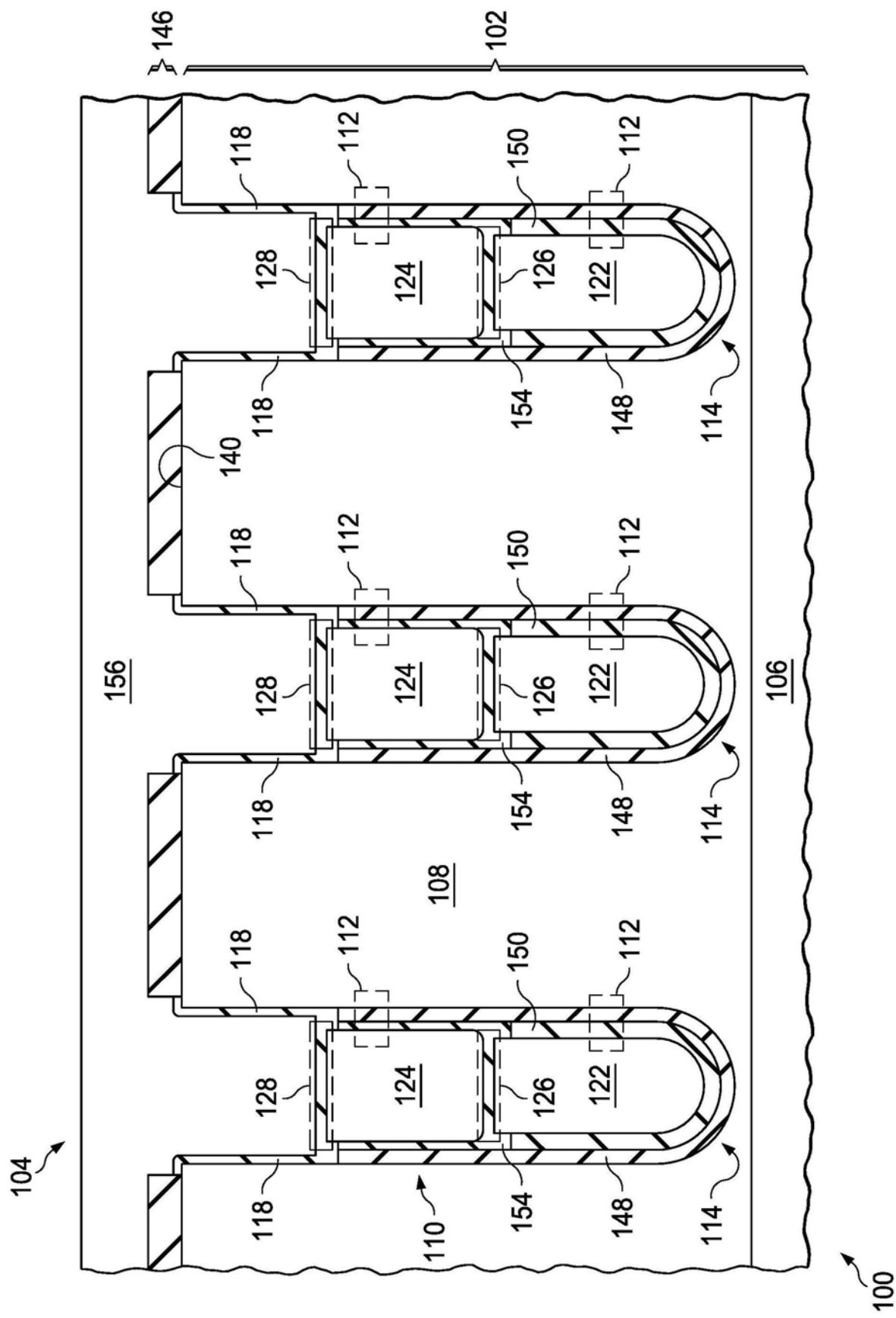

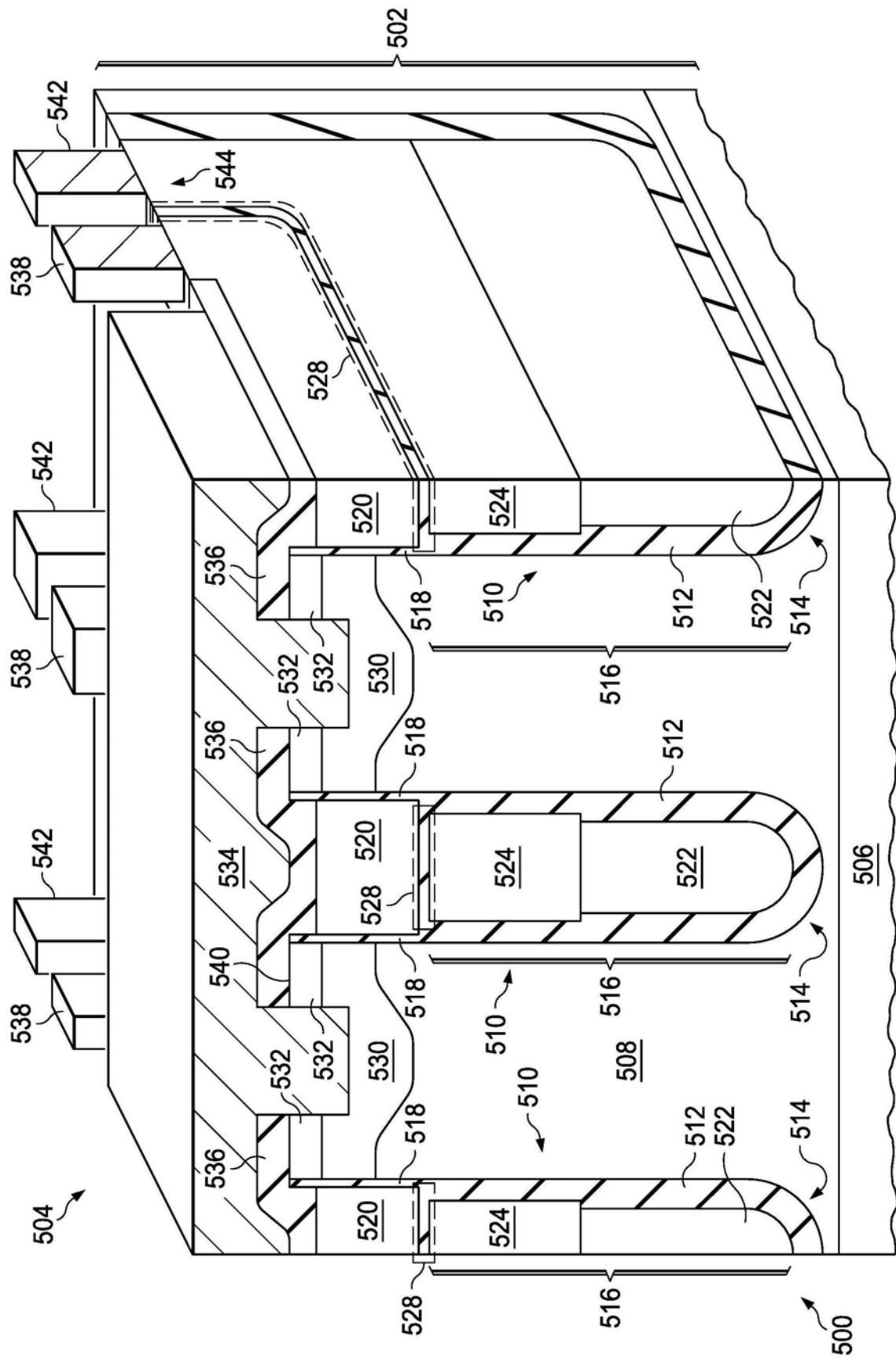

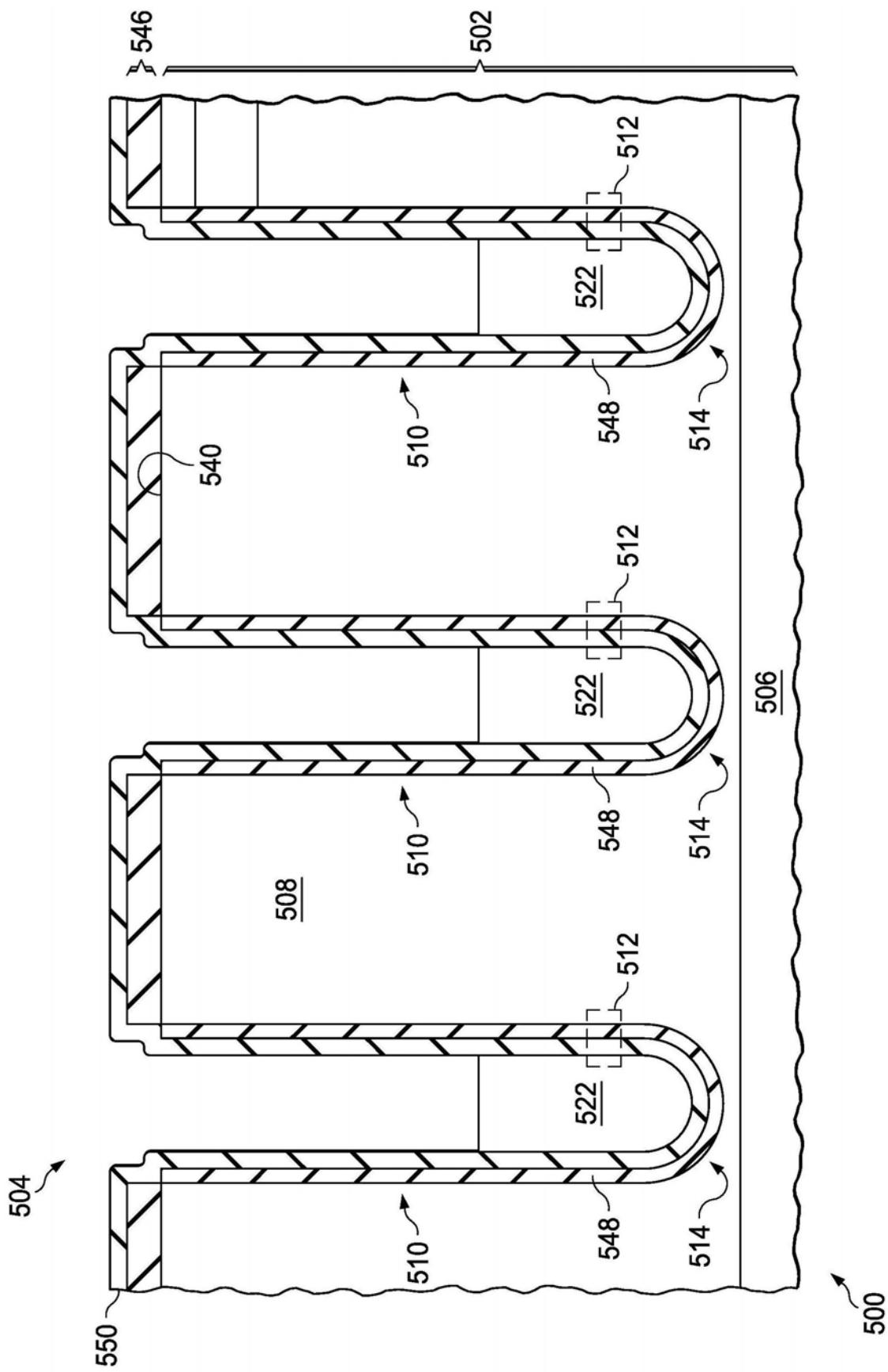

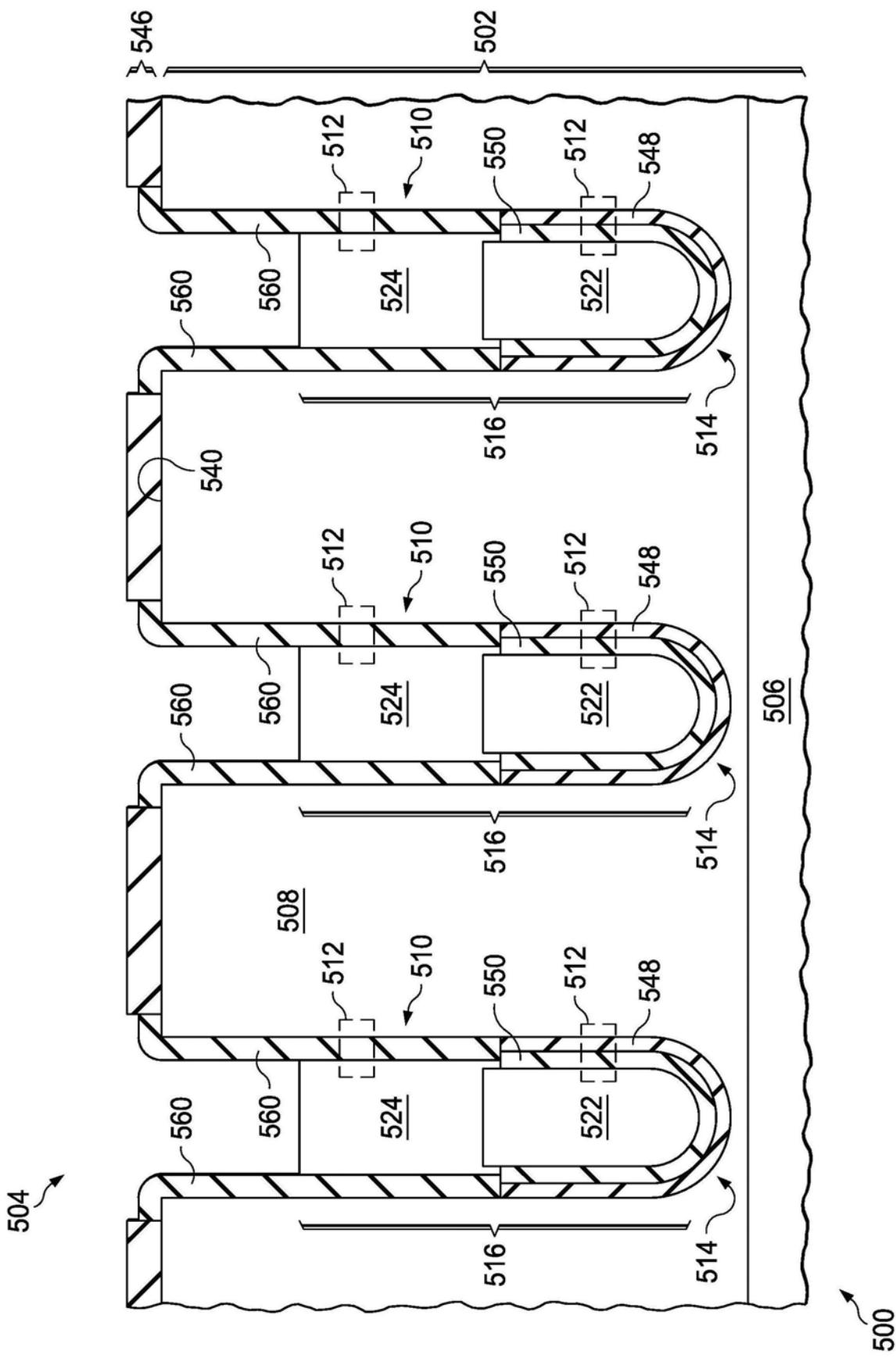

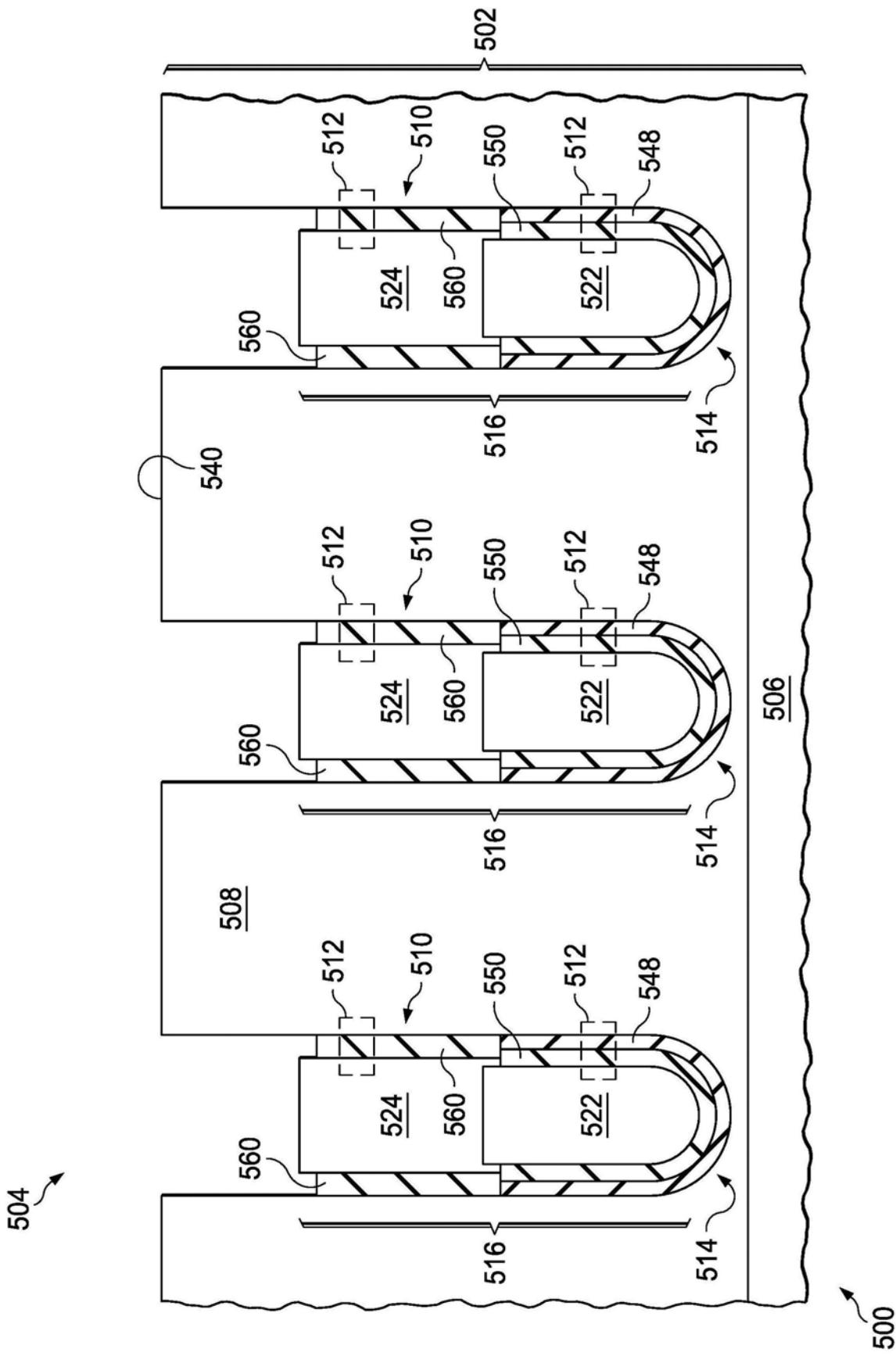

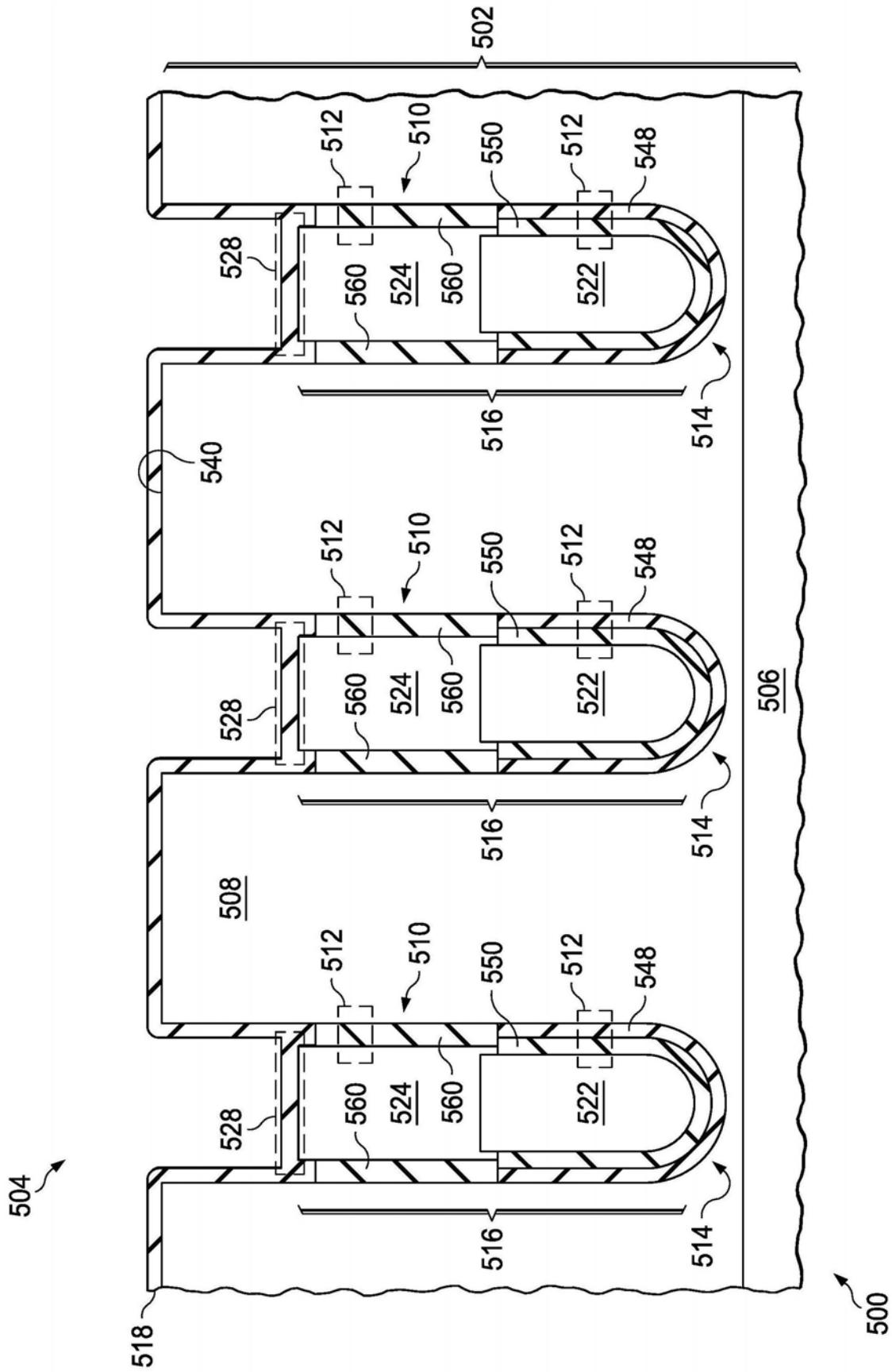

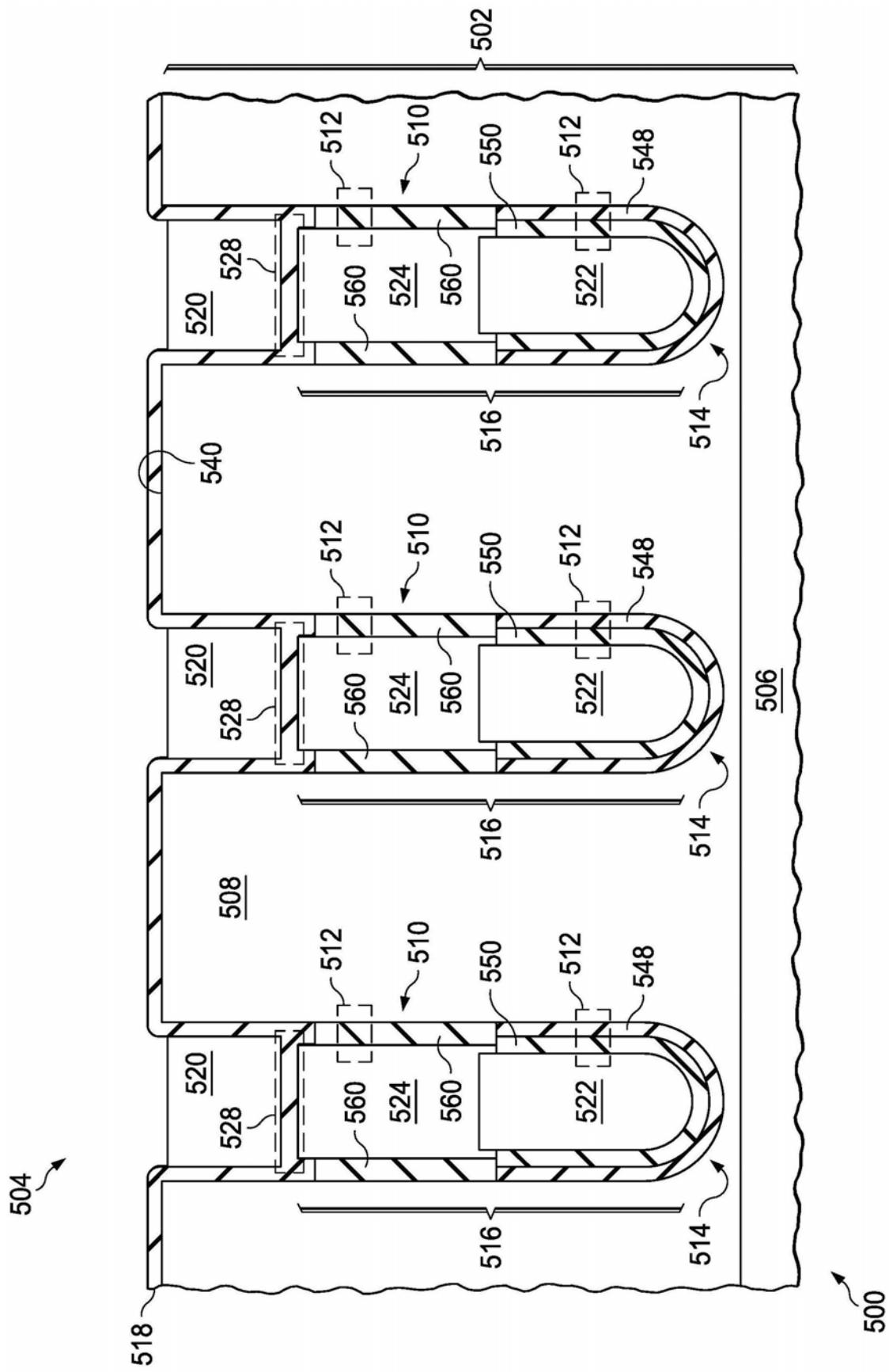

[0008] 图5是包含垂直型p沟道MOS晶体管的示例半导体器件的横截面图。

[0009] 图6A到图6H是在连续制造阶段中描绘的图5的半导体器件的横截面图。

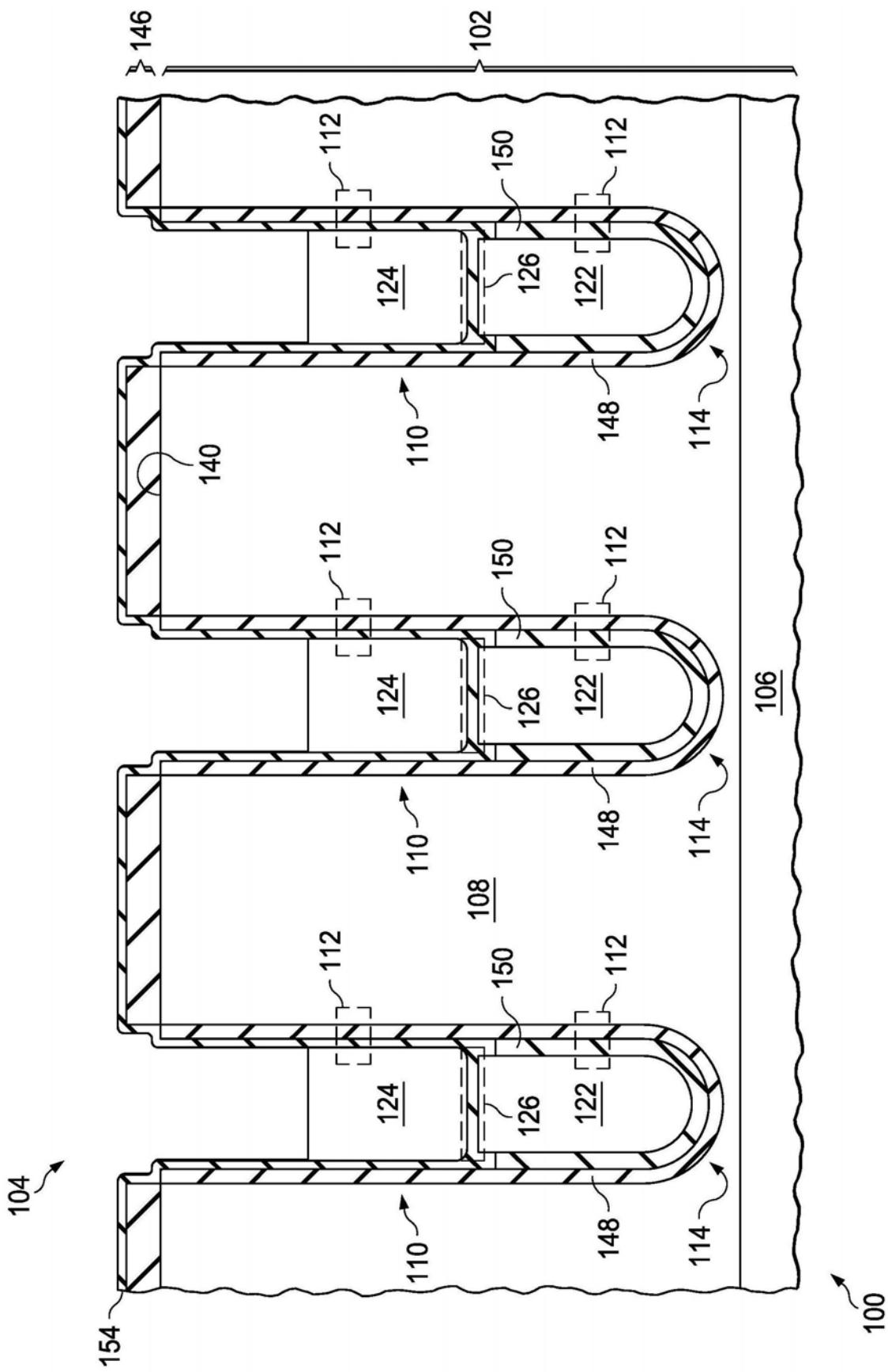

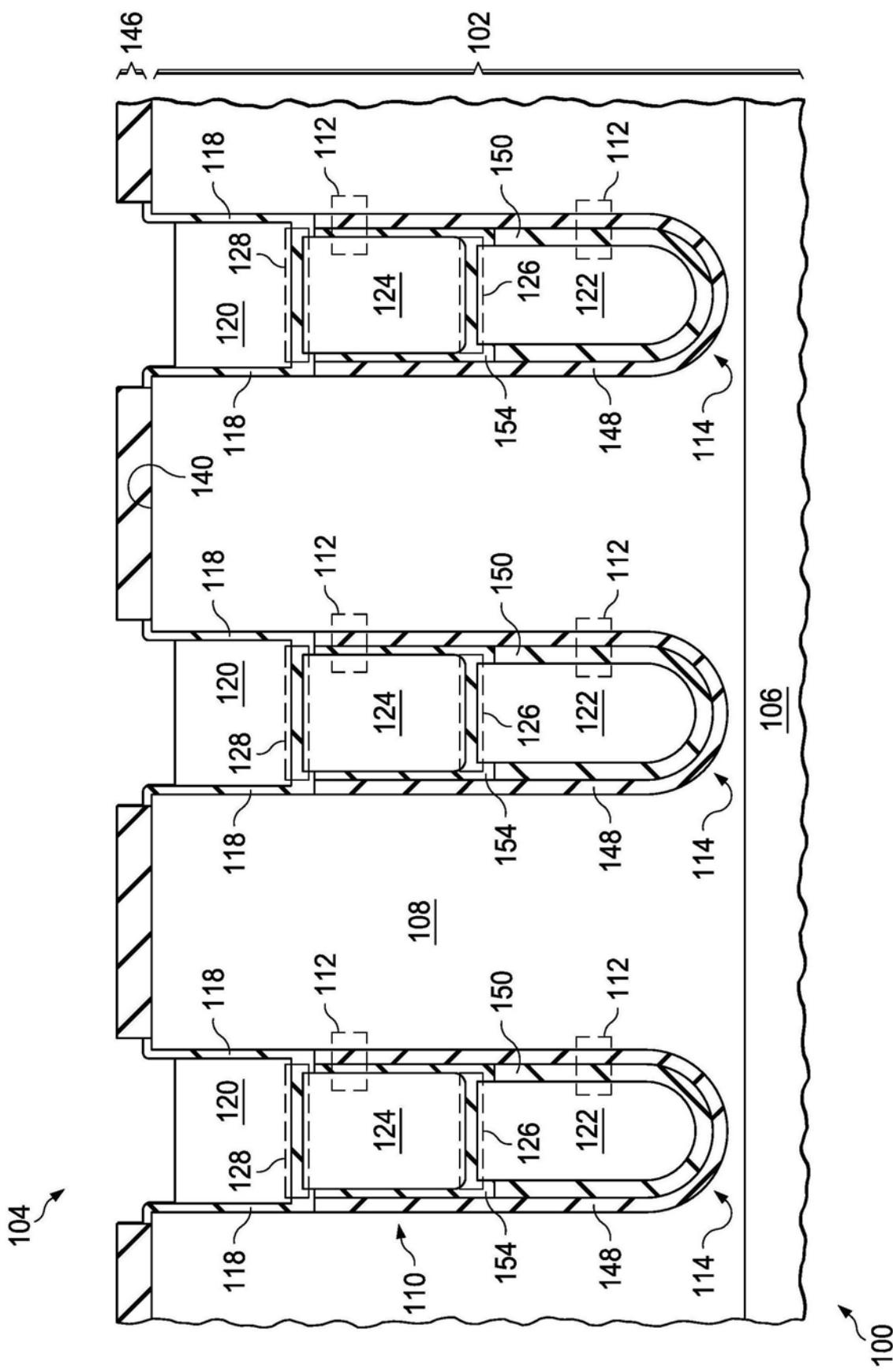

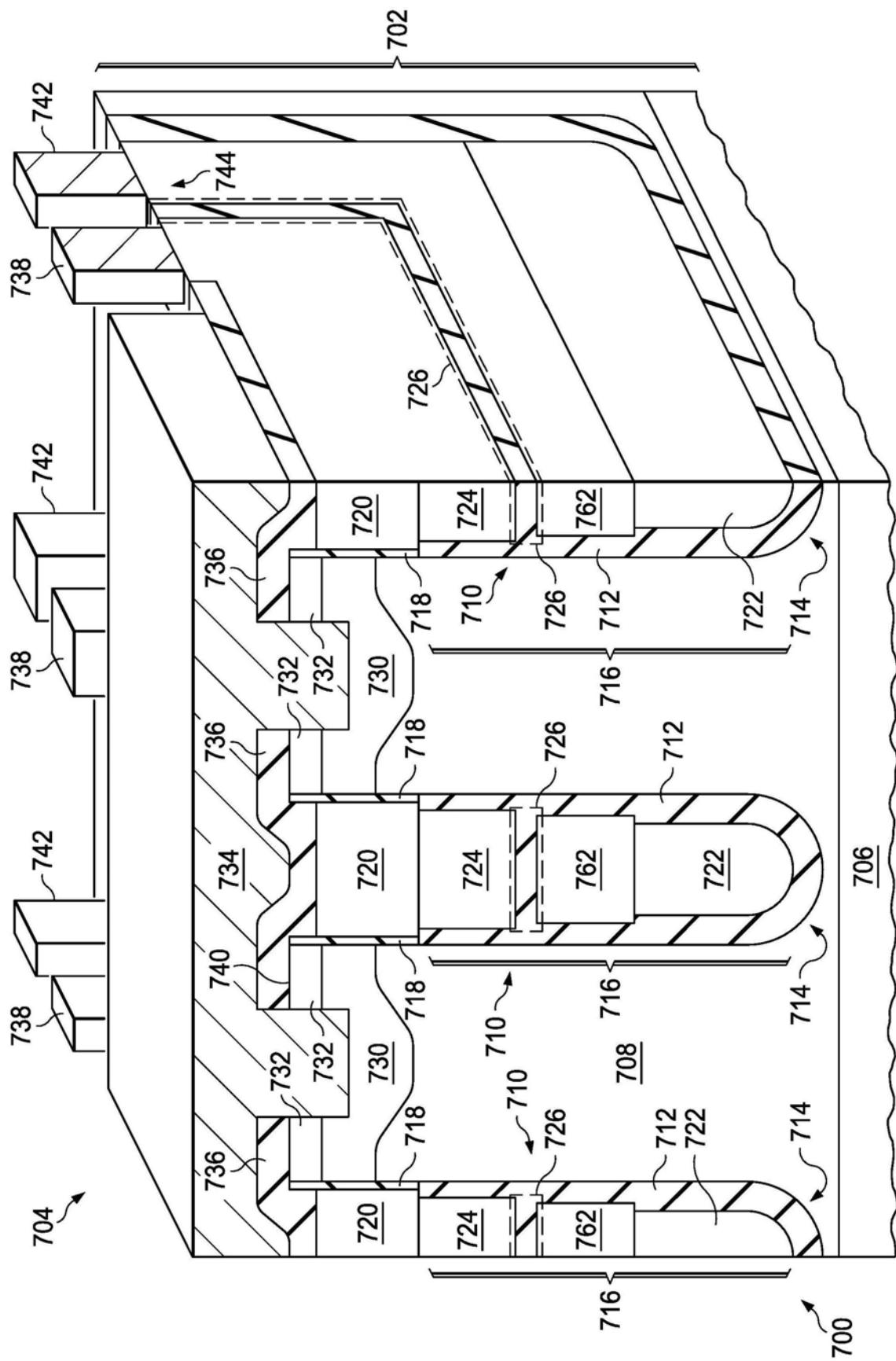

[0010] 图7是包含垂直型n沟道MOS晶体管的另一示例半导体器件的横截面图。

### 具体实施方式

[0011] 附图未按照比例绘制。一些动作可能以不同的顺序发生和/或与其他的动作或事件同时发生。并非所有说明的动作或事件都需要实现根据实施例的方法。

[0012] 半导体器件包含具有沟槽的垂直型MOS晶体管，该沟槽延伸到半导体器件的衬底中。垂直型MOS晶体管的漏极区域在衬底中布置在沟槽底部处或下面。漂移区域在衬底中布置在漏极区域上方并在沟槽之间。垂直型MOS晶体管的主体在衬底中布置在漂移区域上方并邻接沟槽。垂直型MOS晶体管的源极布置在主体上方。垂直型MOS晶体管的栅极邻近主体布置在沟槽中，其通过栅极电介质层与主体分离。具有多段的场板在沟槽中布置在栅极下面，其通过沟槽的侧壁上的电介质衬垫与漂移区域分离。相比于紧接栅极下面的上段，电介质衬垫在沟槽的底部处的场板的下段上更厚。场板段可彼此连接或可彼此电绝缘。上场板

段可与栅极连接或与栅极电绝缘。垂直型MOS晶体管可以是n沟道MOS晶体管或p沟道MOS晶体管。

[0013] 根据本描述的目的,术语“RESURF (reduced surface field,降低表面电场)”指的是减小相邻半导体区域中的电场的一种材料。例如,RESURF区域可能是具有与邻近半导体区域相反的导电类型的半导体区域。RESURF结构在Appels等人在1980年飞利浦研究杂志第35期第1-13页(Philips J,Res.351-13,1980)的“薄层高压器件(Thin Layer High Voltage Devices)”中被描述。

[0014] 图1是包含垂直型n沟道MOS晶体管的示例半导体器件的横截面图。半导体器件100在衬底102上形成,衬底102包括半导体材料。n沟道垂直型MOS晶体管104(此处称为晶体管104)可以是半导体器件100的仅一个有源元件或者可以是半导体器件100内的多个有源元件之一。晶体管104包括n型漏极区域106,其在衬底102内布置在n型垂直漂移区域108下面。

[0015] 半导体器件100包括沟槽110,该沟槽110穿过垂直漂移区域108垂直延伸到接近漏极区域106(如图1描绘的),或可能进入漏极区域106。沟槽110包含在沟槽110的侧壁上的电介质衬垫112其延伸到沟槽110的底部114,并邻接衬底102与在电介质衬垫112上的多场板段116。沟槽110进一步包含在电介质衬垫112上方的栅极电介质层118,其邻接衬底102与晶体管104的沟槽栅极120,沟槽栅极120与栅极电介质层118接触。在此示例中,场板段116包括在沟槽110的底部114处在相应的电介质衬垫112上的相应下场板段122和布置在相应的下场板段122上方的相应的上场板段124。场板段116和沟槽栅极120可主要包括多晶硅(polycrystalline silicon)(称为多晶硅(polysilicon))。电介质衬垫112可主要包括二氧化硅。电介质衬垫将下场板段122和上场板段124与衬底102分离。在沟槽110的侧壁上布置在下场板段122和衬底102之间的电介质衬垫112比在沟槽110的侧壁上布置在上场板段124和衬底102之间的电介质衬垫112更厚。在沟槽110的侧壁上布置在上场板段124和衬底102之间的电介质衬垫112比在沟槽110的侧壁上布置在沟槽栅极120和衬底102之间的栅极电介质层118更厚。例如,在其中晶体管104被设计操作高达250伏的这个示例的版本中,在沟槽110的侧壁上布置在下场板段122和衬底102之间的电介质衬垫112可能是900纳米到1000纳米厚,且在沟槽110的侧壁上布置在上场板段124和衬底102之间的电介质衬垫112可能是300纳米到400纳米厚。

[0016] 在该示例中,下场板段122通过第一绝缘层126与上场板段124电绝缘,第一绝缘层126布置在下场板段122和上场板段124之间。而且,在该示例中,上场板段124通过第二绝缘层128与沟槽栅极120电绝缘,第二绝缘层128布置在上场板段124和沟槽栅极120之间。第一绝缘层126和第二绝缘层128包括如二氧化硅的电介质材料,且可具有与电介质衬垫112类似的组成。

[0017] 晶体管104包括在衬底102中的在垂直漂移区域108上方的p型主体130,其与栅极电介质层118邻接。晶体管104进一步包括在主体130上方并邻接栅极电介质层118的n型源极132。沟槽栅极120与垂直漂移区域108和源极132部分地同延/共同延伸(coextensive)。源电极134布置在衬底102上方,其与源极132和主体130电接触。源电极134通过在沟槽栅极120上方的电介质帽层136与沟槽栅极120电绝缘。

[0018] 在其中晶体管104被设计操作高达250伏的这个示例的版本中,沟槽110可为13微米到17微米深和2.5微米到2.8微米宽。垂直漂移区域108可为0.5微米到0.3微米宽,即在邻

近沟槽110之间,且具有 $1.4 \times 10^{16} \text{ cm}^{-3}$ 到 $1.6 \times 10^{16} \text{ cm}^{-3}$ 的平均掺杂密度。

[0019] 可在衬底102的顶部表面140处通过在栅极的暴露区域上的栅极触点138与沟槽栅极120电连接。可通过在场板上升管(riser)144上的场板触点142与场板段116电连接,场板上升管144从场板段116向上延伸到衬底102的顶部表面140。用于与场板段116电连接的其他结构在本示例的范围内。

[0020] 在半导体器件100的操作期间,相比于具有平面栅极的类似的垂直型MOS晶体管,布置在沟槽110内的沟槽栅极120有利地提供在被晶体管104占据的顶部表面140的区域中的更高的开态电流。上场板段124和下场板段122的组合提供了RESURF配置来将垂直漂移区域108中的电场维持在期望值,相比于具有单个场板的类似的垂直型MOS晶体管,该期望值具有在垂直漂移区域108中更高的掺杂浓度。因此,通过形成具有上场板段124和下场板段122的组合的垂直型MOS晶体管104,使得晶体管104能够具有比具有单个场板的类似垂直型MOS晶体管更浅的沟槽110,从而有利地减少半导体器件100的制造成本。形成彼此电绝缘的下场板段122、上场板段124和沟槽栅极120可有利地进行独立地偏置下场板段122和上场板段124以增加在晶体管104内的电流密度。

[0021] 图2A到图2K是在连续制造阶段中描绘的图1的半导体器件的横截面图。参照图2A,半导体器件100在衬底102上形成,例如体硅晶片或具有延伸到顶部表面140的外延层的硅晶片。在衬底102中的其他半导体材料在此示例范围内。在衬底102内形成漏极区域106以具有大于 $1 \times 10^{20} \text{ cm}^{-3}$ 的掺杂浓度。例如,通过将n型掺杂剂(如,锑和(可能地)砷)注入衬底102中,接着在注入的n型掺杂剂上方对n型半导体材料退火和外延生长,使得外延层提供垂直漂移区域108,可形成漏极区域106。在垂直漂移区域108中的n型掺杂剂(如,磷)可在外延生长期间被掺入或可在之后被注入,接着是热驱动以扩散和激活注入的掺杂剂。

[0022] 在衬底102上方形成硬掩膜146,其暴露沟槽110的区域。硬掩膜146可以是几百纳米的二氧化硅,且可通过刻蚀通过光刻胶掩膜而被图案化。通过将材料从由硬掩膜146暴露的区域中的衬底102移除,形成沟槽110。通过定时反应离子刻蚀(RIE)过程从衬底102移除材料来达到沟槽110的期望深度。

[0023] 参照图2B,图1中的邻接下场板段122的电介质衬垫112可形成为热氧化层148和第一沉积二氧化硅层150的组合层。在沟槽110的侧壁和底部114处形成热氧化层148。热氧化层148可为50纳米到200纳米厚。在热氧化层148上形成第一沉积二氧化硅层150。第一沉积二氧化硅层150可为200纳米到400纳米厚,并可使用二氯硅烷和氧气通过亚大气压化学气相沉积(SACVD)过程形成。替代地,第一沉积二氧化硅层150可使用正硅酸乙酯(又名四乙氧基硅烷或TEOS)通过等离子体增强化学气相沉积(PECVD)过程形成。随后,第一沉积二氧化硅层150可在退火步骤中致密。用于电介质衬垫112的其它层结构和其他过程在本示例的范围内。

[0024] 第一多晶硅层152在电介质衬垫112上形成,并在衬底102的顶部表面140上方延伸。例如,第一多晶硅层152可以在顶部表面140上方为500纳米到700纳米厚。并且,例如,可在形成期间用磷掺杂第一多晶硅层152以具有 $1 \times 10^{18} \text{ cm}^{-3}$ 到 $5 \times 10^{18} \text{ cm}^{-3}$ 的平均掺杂浓度。替代地,可通过以 $1 \times 10^{14} \text{ cm}^{-2}$ 到 $5 \times 10^{15} \text{ cm}^{-2}$ 的剂量离子注入掺杂剂(例如,磷)来掺杂第一多晶硅层152,且随后以900°C到1000°C退火第一多晶硅层152以10到60分钟。

[0025] 参照图2C,毯覆式回蚀(blanket etchback)过程将多晶硅从图2B的在顶部表面

140上方和在沟槽110中的第一多晶硅层152移除，在沟槽110的较低的部分中留下多晶硅，以形成低场板段122。例如，可使用包括氟自由基的定时等离子体刻蚀和/或利用胆碱、氢氧化铵或四甲基氢氧化铵的定时湿法刻蚀，实现毯覆式回蚀。毯覆式回蚀可在多个刻蚀步骤中实现。在此示例中的一个版本中，毯覆式回蚀不移除大量的电介质衬垫112。

[0026] 参照图2D，第一毯覆式氧化回蚀过程从衬底102的顶部表面140上方和从下场板段122上方的沟槽110移除至少部分、且可能所有的第一沉积二氧化硅层150。下场板段122阻止第一沉积二氧化硅层150从下场板段122顶部下面的沟槽110移除。第一毯覆式氧化回蚀过程完成后，大多数且可能所有的热氧化层148留在沟槽110的侧壁上。例如，第一毯覆式氧化回蚀过程可包括利用缓冲氢氟酸溶液的定时湿法刻蚀。示例缓冲氢氟酸溶液是在去离子水中的40%的氟化铵中的10份(part)和在去离子水中49%的氢氟酸中的1份；该缓冲氢氟酸展示了致密的SACVD二氧化硅的刻蚀速率是热氧化刻蚀速率的两倍以上。

[0027] 参照图2E，第二沉积二氧化硅层154在沟槽110中的热氧化层148上方和在下场板段122上方形成。例如，第二沉积二氧化硅层154可以是160纳米到280纳米厚，并可能通过SACVD过程或PECVD过程形成。第二沉积二氧化硅层154可随后在退火步骤中致密。与热氧化层148组合的第二沉积二氧化硅层154提供与图1中的上场板段124邻接的电介质衬垫112。在下场板段122上的第二沉积二氧化硅层154的一部分提供第一绝缘层126。

[0028] 参照图2F，第二多晶硅层在沟槽110中的电介质衬垫112上和在衬底102的顶部表面140上方形成，例如参照图2B所描述。随后的回蚀过程从顶部表面140上方和从沟槽110的顶部部分移除多晶硅，留在在第二沉积二氧化硅层154上的多晶硅以形成上场板段124。回蚀过程可以是定时等离子体刻蚀和/或定时湿法刻蚀，如参照图2C所描述。在此示例中，上场板段124与下场板段122通过第二沉积二氧化硅层154电绝缘。

[0029] 参照图2G，第二毯覆式氧化回蚀过程从衬底102的顶部表面140上方和从上场板段124上方的沟槽110移除第二沉积二氧化硅层154和热氧化层148。上场板段124阻止从上场板段124的顶部下面的沟槽110中移除第二沉积二氧化硅层154。硬掩膜146的一部分可通过第二毯覆式氧化回蚀过程移除，如图2G描绘。第二毯覆式氧化回蚀过程可以实现，使得基本没有半导体材料从衬底102移除。

[0030] 参照图2H，栅极电介质层118在上场板段124上方在沟槽110的侧壁上形成，且第二绝缘层128同时在上场板段124上形成。栅极电介质层118和第二绝缘层128可通过热氧化或热氧化和电介质材料的沉积的组合形成。移除热氧化层148以暴露沟槽110的侧壁有利地改进栅极电介质层118的厚度的过程控制。

[0031] 参照图2I，形成第三多晶硅层156，其接触栅极电介质层118且在衬底102的顶部表面140上方。第三多晶硅层156可在形成期间用n型掺杂剂掺杂，或可随后注入n型掺杂剂，接着是退火。

[0032] 参照图2J，毯覆式回蚀过程从衬底102的顶部表面140上方移除来自图2I的第三多晶硅层156的多晶硅，以留下与栅极电介质层118接触的多晶硅，以形成晶体管104的沟槽栅极120。在此示例中，沟槽栅极120与上场板段124通过第二绝缘层128电绝缘。

[0033] 参照图2K，通过在垂直漂移区域108上方将p型掺杂剂(如，硼)注入衬底102，形成主体130。沟槽栅极120可以可选择地通过注入剂掩膜被覆盖同时p型掺杂被注入，以防止反向掺杂沟槽栅极120。通过在主体130上方将n型掺杂剂(如，磷和砷)注入衬底102，形成源极

132。衬底102随后被退火以激活注入的掺杂剂。主体130和源极132横跨衬底102在相邻沟槽110之间延伸。在主体130和源极132形成后，通过沉积二氧化硅和可选择地氮化硅子层，形成帽层136。可通过PECVD过程使用TEOS形成帽层136。在帽层136形成后，通过帽层136并通过源极132进入主体130形成源极接触开口。附加的p型掺杂剂可注入到主体130内由源极接触开口暴露的地方，其在图1中描绘的主体中提供向下的凸出部分。图1的源电极134随后被形成，并且进一步的制造提供图1的结构。

[0034] 图3是包含垂直型n沟道MOS晶体管的另一示例半导体器件的横截面图。半导体器件300在衬底302上形成，其包括半导体材料。n沟道垂直型MOS晶体管304，此处称为晶体管304，包括n型漏极区域306，其在衬底302中布置在n型垂直漂移区域308下面。

[0035] 半导体器件300包括沟槽310，沟槽310穿过垂直漂移区域308垂直延伸到接近漏极区域306，或可能延伸进入漏极区域306。沟槽310包含延伸到沟槽310的底部314的电介质衬垫312，其邻接衬底302与在电介质衬垫312上的多场板段316。沟槽310进一步包含在电介质衬垫312上方的栅极电介质层318，其邻接衬底302与晶体管304的沟槽栅极320，沟槽栅极320与栅极电介质层318接触。在此示例中，场板段316包括相应的下场板段322和相应的上场板段324，下场板段322在沟槽310的底部314处在相应的电介质衬垫312上，且上场板段324布置在相应的下场板段322上方。场板段316和沟槽栅极320可主要包括n型多晶硅。电介质衬垫312可主要包括二氧化硅。电介质衬垫312将下场板段322和上场板段324与衬底302分离。将下场板段322与衬底302分离的电介质衬垫312比将上场板段324与衬底302分离的电介质衬垫312厚。布置在沟槽310的侧壁上在上场板段324和衬底302之间的电介质衬垫312比布置在沟槽310的侧壁上在沟槽栅极320和衬底302之间的栅极电介质层318厚。例如，在此示例的版本中，其中，晶体管304被设计操作高达40伏，布置在沟槽310的侧壁上在下场板段322和衬底302之间的电介质衬垫312可以是100纳米到150纳米厚，且布置在沟槽310的侧壁上在上场板段324和衬底302之间的电介质衬垫312可以是50纳米到80纳米厚。

[0036] 在此示例中，下场板段322与沟槽310内的上场板段324接触。上场板段324与沟槽310内的沟槽栅极320接触。在此示例中，应用到沟槽栅极320的偏置电压也将上场板段324和下场板段322偏置为同样的偏置电压。

[0037] 晶体管304在衬底302内包括在垂直漂移区域308上方的p型主体330，其与栅极电介质层318邻接。晶体管304进一步包括在主体330上方并邻接栅极电介质层318的n型源极332。沟槽栅极320与垂直漂移区域308和源极332部分地同延。源电极334布置在衬底302上方，以与源极332和主体330电接触。源电极334通过沟槽栅极320上方的电介质帽层336与沟槽栅极320电绝缘。用于关于源极332和主体330的源电极334的其他配置是在此示例的范围内。

[0038] 在此示例的版本中，其中，晶体管304被设计操作高达40伏，沟槽310可为2.2微米到2.8微米深和600纳米到700纳米宽。垂直漂移区域308可为500纳米到1.5微米宽，即在相邻沟槽310之间，并具有 $1.8 \times 10^{16} \text{ cm}^{-3}$ 到 $2.0 \times 10^{16} \text{ cm}^{-3}$ 的平均掺杂密度。

[0039] 可在衬底302的顶部表面340处通过在栅极的暴露区域上的栅极触点338与沟槽栅极320电连接。用于与沟槽栅极320电连接的其他结构是在此示例的范围内。形成上场板段324以与沟槽310内的沟槽栅极320接触，且形成下场板段322以与沟槽310内的上场板段324接触使得可通过栅极触点338与上场板段324和下场板段322电连接，可有利地减小半导体

器件300的复杂性和制造成本。

[0040] 在半导体器件300的操作期间,沟槽栅极320有利地提供较高电流密度,如参照图1所解释的。场板段316提供RESURF配置来维持垂直漂移区域308中的电场处于期望值,如参照图1所解释的。因此,通过形成具有上场板段324和下场板段322的组合的垂直型MOS晶体管304,使得晶体管304比具有单个场板的类似的垂直型MOS晶体管具有更浅的沟槽310,从而有利地减少半导体器件300的制造成本。

[0041] 图4A到图4E是在连续制造阶段中描绘的图3的半导体器件的横截面图。参照图4A,半导体器件300在衬底302上形成。在衬底302内形成漏极区域306,以具有大于 $1 \times 10^{20} \text{ cm}^{-3}$ 的掺杂浓度。在垂直漂移区域308中的n型掺杂剂例如磷可在外延生长期间被掺入或可在之后被注入。硬掩膜346在衬底302上方形成,其暴露用于沟槽310的区域。通过将材料从由硬掩膜346暴露的区域中的衬底302移除,形成沟槽310。漏极区域306、硬掩膜346和沟槽310可如参照如图2A所述被形成。

[0042] 在沟槽310的侧壁和底部314处形成热氧化层348。在此示例中,热氧化层348足够厚以提供在沟槽310的侧壁上在图3的上场板段324和衬底302之间的完整的电介质衬垫312,如,针对40伏的操作电压的70纳米到80纳米厚。在热氧化层348上形成沉积的二氧化硅层350。沉积的二氧化硅层350可为130纳米到170纳米厚,其通过SACVD过程或PECVD过程形成。

[0043] 在沟槽310中,下场板段322在沉积的二氧化硅层350上形成,例如参考图2B和图2C所述。与沉积的二氧化硅层350组合的热氧化层348提供电介质衬垫312,其将下场板段322与衬底302分离。

[0044] 第一毯覆式氧化回蚀过程从下场板段322上方的沟槽310移除至少部分且可能所有的沉积的二氧化硅层350。下场板段322防止从在下场板段322的顶部下面的沟槽310移除沉积的二氧化硅层350。在此示例中,在第一毯覆式氧化回蚀过程完成后,基本所有的热氧化层348留在沟槽310的侧壁上。第一毯覆式氧化回蚀过程暴露下场板段322的顶部。

[0045] 参照图4B,在沟槽310中在热氧化层348上并在下场板段322上形成上场板段324,例如参照图2F所描述。在此示例中,热氧化层348提供电介质衬垫312,其将上场板段324与衬底302分离,这将有利地减少半导体器件300的制造复杂性和成本。

[0046] 参照图4C,第二毯覆式氧化回蚀过程从在上场板段324上方的沟槽310移除热氧化层348。上场板段324阻止从在上场板段324的顶部下面的沟槽310中移除热氧化层348。可以执行第二毯覆式氧化回蚀过程,以致基本没有半导体材料从衬底302移除。

[0047] 栅极电介质层318在上场板段324上方在沟槽310的侧壁上形成,且电介质材料358同时在上场板段324上形成。栅极电介质层318可通过热氧化或热氧化和沉积的电介质材料的组合形成。移除热氧化层348暴露沟槽310的侧壁有利地改进栅极电介质层318的厚度的过程控制。由于相比于单晶硅的在多晶硅上的较高热氧化生长速率,在上场板段324上的电介质材料358可比栅极电介质层318更厚。

[0048] 参照图4D,各向异性刻蚀过程例如RIE过程从上场板段324的顶部移除图4C中的电介质材料358,而没有显著劣化栅极电介质层318。在此示例的一个版本中,当电介质层358被移除时,可通过多晶硅或氮化硅的牺牲层保护栅极电介质层318,之后,移除牺牲层,而没有显著劣化栅极电介质层318。

[0049] 参照图4E,形成沟槽栅极320,其接触栅极电介质层318和上场板段324。参照图2I和图2J描述,可形成沟槽栅极320。在此示例中,从上场板段324的顶部移除图4C的电介质材料358使沟槽栅极320与上场板段324电接触。进一步的制造提供图3的结构。

[0050] 图5是包含垂直型p沟道MOS晶体管的示例半导体器件的横截面图。半导体器件500在衬底502上形成,其包括半导体材料。p沟道垂直型MOS晶体管504,此处称为晶体管504,包括p型漏极区域506,其在衬底502中布置在p型垂直漂移区域508下面。

[0051] 半导体器件500包括沟槽510,沟槽510穿过垂直漂移区域508垂直延伸到接近漏极区域506,或可能延伸进入漏极区域506。沟槽510包含延伸到沟槽510的底部514的电介质衬垫512,其邻接衬底502与在电介质衬垫512上的多场板段516。沟槽510进一步包含在电介质衬垫512上方的栅极电介质层518,其邻接衬底502与晶体管504的沟槽栅极520,沟槽栅极520与栅极电介质层518接触。在此示例中,场板段516包括相应的下场板段522和相应的上场板段524,下场板段522在沟槽510的底部514处在相应的电介质衬垫512上,且上场板段524布置在相应的下场板段522上方。场板段516和沟槽栅极520可主要包括p型多晶硅。电介质衬垫512可主要包括二氧化硅。电介质衬垫512将下场板段522和上场板段524与衬底502分离。将下场板段522与衬底502分离的电介质衬垫512比将上场板段524与衬底502分离的电介质衬垫512更厚。在沟槽510的侧壁上布置在上场板段524和衬底502之间的电介质衬垫512比在沟槽510的侧壁上布置在沟槽栅极520和衬底502之间的栅极电介质层518更厚。例如,在此示例的版本中,其中,晶体管504被设计操作高达100伏,在沟槽510的侧壁上布置在下场板段522和衬底502之间的电介质衬垫512可以是400纳米到500纳米厚,且在沟槽510的侧壁上布置在上场板段524和衬底502之间的电介质衬垫512可能是150纳米到200纳米厚。

[0052] 在此示例中,下场板段522与沟槽510中的上场板段524接触。上场板段524通过绝缘层528与沟槽栅极520绝缘,其布置在上场板段524和沟槽栅极520之间。在此示例中,应用到上场板段524的偏置电压也将下场板段522偏置为相同的偏置电压。

[0053] 晶体管504在衬底502中包括在垂直漂移区域508上方的n型主体530,其与栅极电介质层518邻接。晶体管504进一步包括在主体530上方并邻接栅极电介质层518的p型源极532。沟槽栅极520与垂直漂移区域508和源极532部分地同延。源电极534布置在衬底502上方,以与源极532和主体530电接触。源电极534通过沟槽栅极520上方的电介质帽层536与沟槽栅极520电绝缘。用于关于源极532和主体530的源电极534的其他配置是在此示例的范围内。

[0054] 在此示例的一个版本中,其中,晶体管504被设计操作高达100伏,沟槽510可为6微米到7微米深和1.2微米到1.4微米宽。垂直漂移区域508可为0.5微米到2.0微米宽,即,在相邻沟槽510之间,并具有 $1.8 \times 10^{16} \text{ cm}^{-3}$ 到 $2.0 \times 10^{16} \text{ cm}^{-3}$ 的平均掺杂密度。

[0055] 可在衬底502的顶部表面540处通过栅极的暴露区域上的栅极触点538与沟槽栅极520电连接。可通过在场板上升管544上的组合的场板触点542与场板段516电连接,场板上升管544从场板段516向上延伸到衬底502的顶部表面540。用于与沟槽栅极520和场板段516电连接的其他结构在此示例范围内。形成与沟槽栅极520绝缘的上场板段524可有利地进行独立地偏置场板段516以增加晶体管504中的电流密度,同时在沟槽510中形成下场板段522以与上场板段524接触,以便通过组合的场板触点542可形成与上场板段524和下场板段522的电连接,这可有利地减小半导体器件500的复杂性和制造成本。

[0056] 在半导体器件500的操作期间,沟槽栅极520有利地提供较高电流密度,如参照图1所解释的。场板段516提供RESURF配置以维持垂直漂移区域508中的电场处于期望值,如参照图1所解释的。因此,通过形成具有上场板段524和下场板段522的组合的垂直型MOS晶体管504,使得晶体管504比具有单个场板的类似的垂直型MOS晶体管有具更浅的沟槽510,从而有利地减少半导体器件500的制造成本。

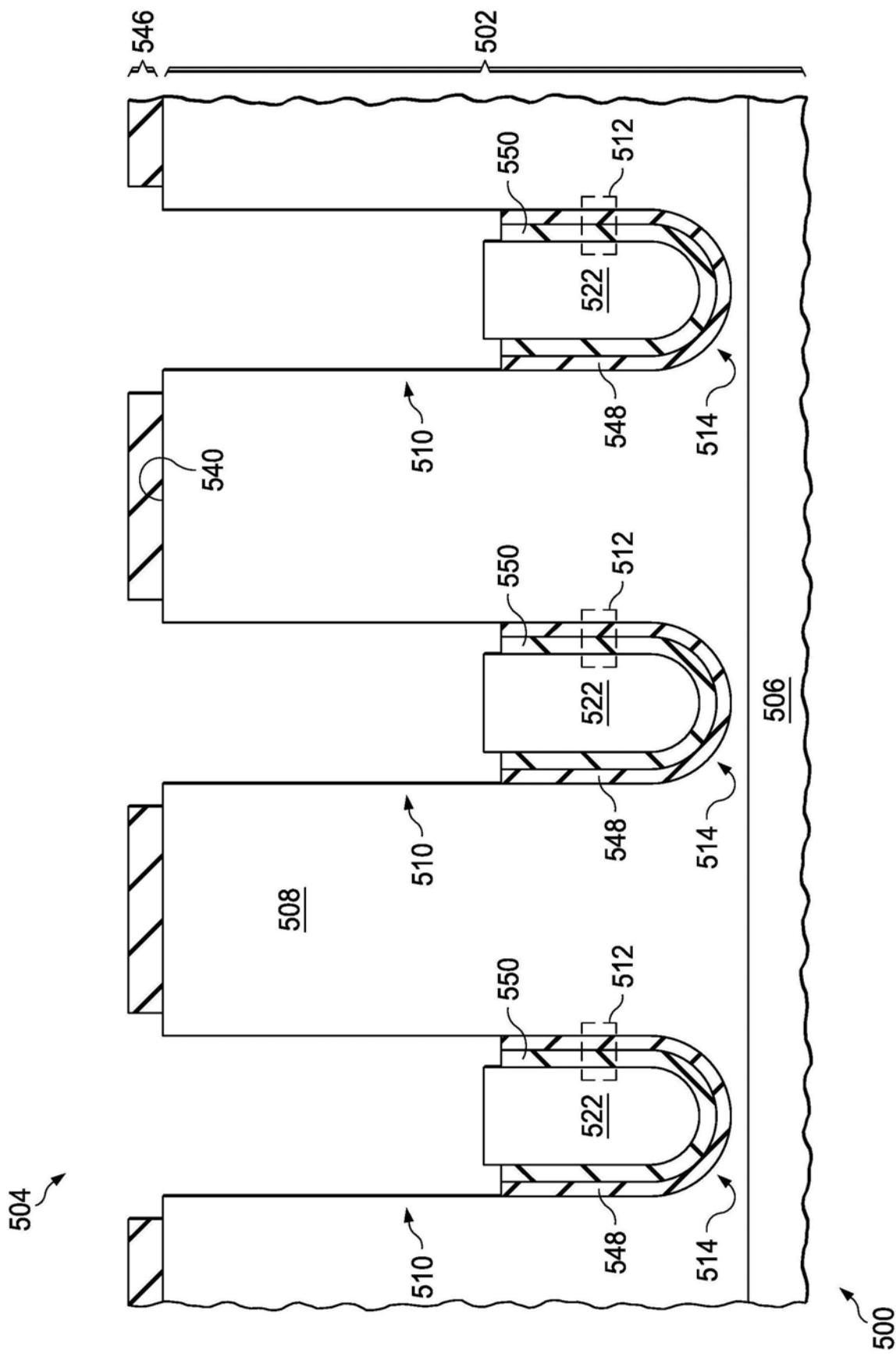

[0057] 图6A到图6H是在连续制造阶段中描绘的图5的半导体器件的横截面图。参照图6A,半导体器件500在衬底502上形成。在衬底502内形成漏极区域506以具有大于 $1 \times 10^{20} \text{ cm}^{-3}$ 的掺杂浓度。在垂直漂移区域508中的p型掺杂剂(如,硼)可在外延生长期间被掺入或可在之后被注入。在衬底502上方形成硬掩膜546,其暴露用于沟槽510的区域。通过将材料从衬底502的由硬掩膜546暴露的区域中移除,形成沟槽510。漏极区域506、硬掩膜546和沟槽510可参照如图2A所述形成。

[0058] 在沟槽510的侧壁和底部514处形成第一热氧化层548。在热氧化层548上通过SACVD过程或PECVD过程形成沉积的二氧化硅层550。下场板段522在沟槽510中在沉积的二氧化硅层550上形成,例如参照图2B和图2C所描述。在此示例中,下场板段522可以是p型多晶硅以在垂直漂移区域508的RESURF结构中提供有效电荷平衡。与沉积的二氧化硅层550组合的第一热氧化层548提供将下场板段522与衬底502分离的电介质衬垫512。例如,在此示例中,针对100伏操作电压,第一热氧化层548可为70纳米到80纳米厚,且沉积的二氧化硅层550可为330纳米到420纳米厚。

[0059] 参照图6B,第一毯覆式氧化回蚀过程从下场板段522上方的沟槽510移除基本上所有的电介质衬垫512、第一热氧化层548和沉积的二氧化硅层550。下场板段522阻止从在下场板段522的顶部下面的沟槽510移除电介质衬垫512。例如,第一毯覆式氧化回蚀过程可包括使用缓冲氢氟酸溶液的定时湿法刻蚀。

[0060] 参照图6C,第二热氧化层560在沟槽510的侧壁处在下场板段522上方并在下场板段522的顶部表面上形成。在此示例中,第二热氧化层560在图5的上场板段524和衬底502之间提供电介质衬垫512。第二热氧化层560可为150纳米到200纳米厚,以为晶体管504提供100伏操作。

[0061] 参照图6D,各向异性刻蚀过程例如RIE过程从下场板段522的顶部表面移除第二热氧化层560,以暴露下场板段522的顶部表面。执行各向异性刻蚀过程以避免显著劣化在沟槽510的侧壁上的第二热氧化层560。各向异性刻蚀过程可在沟槽510的侧壁上的第二热氧化层560上形成保护聚合物,其随后在下场板段522的顶部表面被暴露后被移除。

[0062] 参照图6E,上场板段524在第二热氧化层560上并在沟槽510中的下场板段522上形成,如参照图2F所述。在此示例中,上场板段524可以是p型多晶硅,如参照图6E解释的。在此示例中,第二热氧化层560提供将上场板段524和衬底502分离的电介质衬垫512,这可有利地减小半导体器件500的制造复杂性和成本,从而消除需要在将上场板段524与衬底502分离的电介质衬垫512中形成第二电介质层。

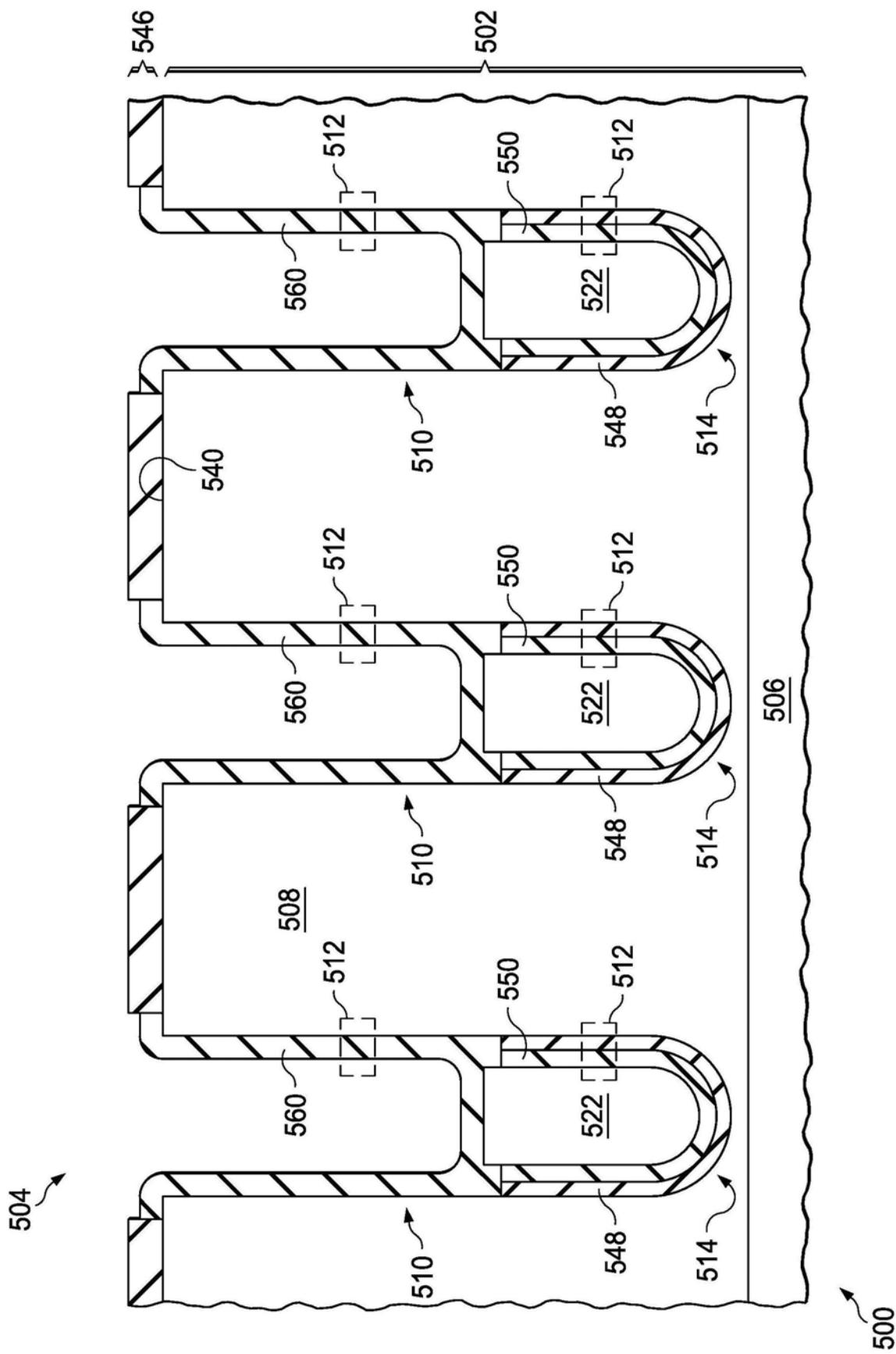

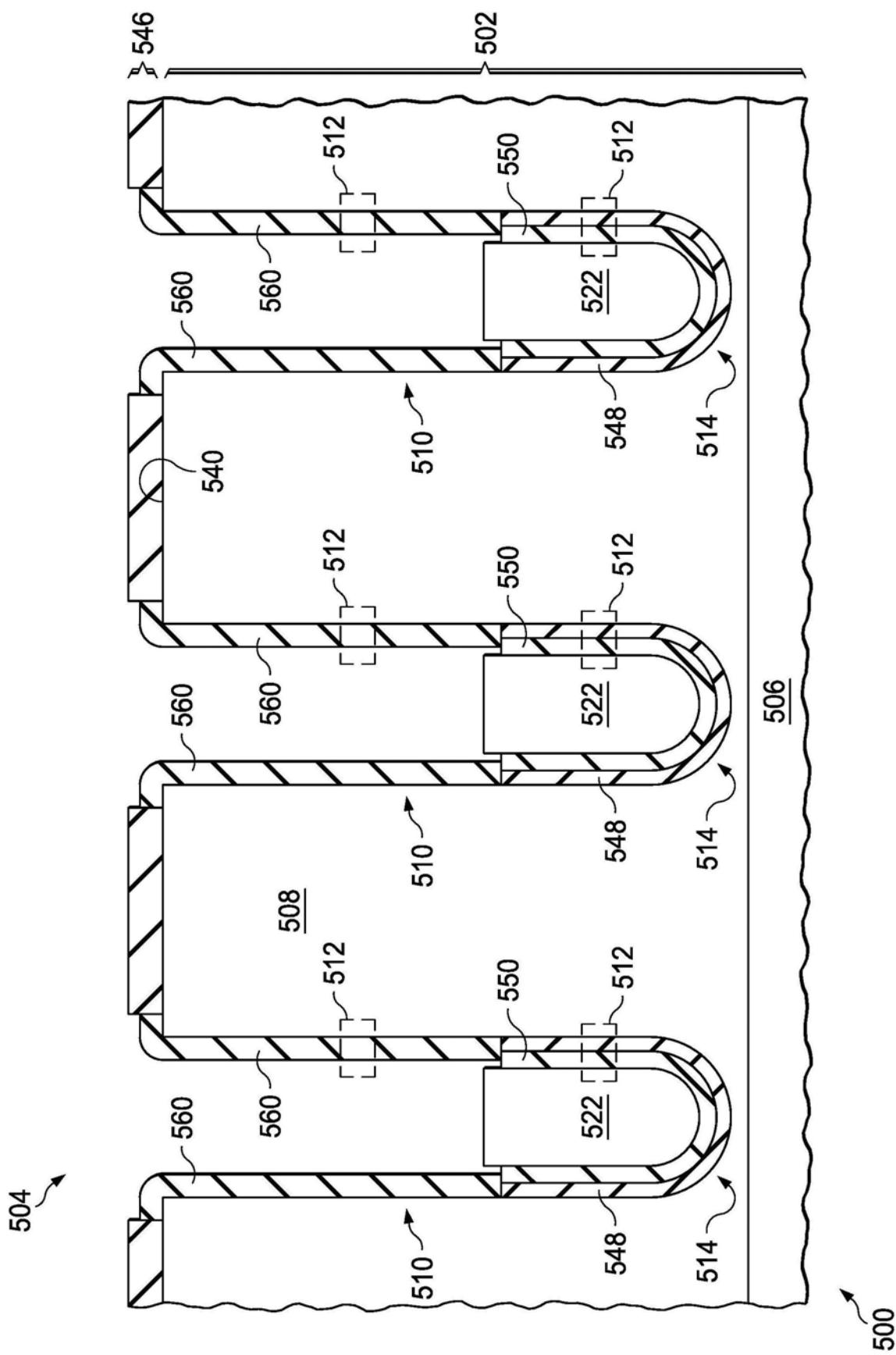

[0063] 参照图6F,第二毯覆式氧化回蚀过程从上场板段524上方的沟槽510移除第二热氧化层560。上场板段524阻止从上场板段524的顶部下面的沟槽510移除第二热氧化层560。可执行第二毯覆式氧化回蚀过程,使得基本上没有半导体材料从衬底502移除。图6E的硬掩膜546可通过第二毯覆式回蚀被移除,以暴露衬底502的顶部表面540,参照图6F描绘的。

[0064] 参照图6G,栅极电介质层518在沟槽510的侧壁上形成,且同时绝缘层528在上场板段524的顶部表面上形成。在此示例中,如果衬底502的顶部表面540通过参考图6F讨论的第二毯覆式回蚀被暴露,栅极电介质层518也可在顶部表面540上形成,如图6G所描绘的。栅极电介质层518和绝缘层528可通过热氧化或热氧化或沉积电介质材料的组合形成。由于相比于单晶硅的在多晶硅上的较高热氧化生长速率,在绝缘层528中的热氧化层可比在栅极电介质层518中的热氧化层更厚。

[0065] 参照图6H,形成沟槽栅极520,其接触栅极电介质层518和绝缘层528。可如参照图2I和图2J所描述形成沟槽栅极520。在此示例中,在上场板段524的顶部上的绝缘层528将场板段516和沟槽栅极520电绝缘,从而进行关于沟槽栅极520的场板段516的独立偏置电压。进一步的制造提供了图5的结构。

[0066] 图7是包含垂直型n沟道MOS晶体管的另一示例半导体器件的横截面图。半导体器件700在衬底702上形成,其包括半导体材料。n沟道垂直型MOS晶体管704,此处称为晶体管704,包括n型漏极区域706,其在衬底702中布置在n型垂直漂移区域708下面。

[0067] 半导体器件700包括沟槽710,该沟槽710穿过垂直漂移区域708垂直延伸到接近漏极区域706,或可能进入漏极区域706。沟槽710包含延伸到沟槽710的底部714的电介质衬垫712,其邻接衬底702与在电介质衬垫712上的多个场板段716。沟槽710进一步包含在电介质衬垫712上方的栅极电介质层718,其邻接衬底702与晶体管704的沟槽栅极720,沟槽栅极720与栅极电介质层718接触。在此示例中,场板段716包括相应的下场板段722、相应的中场板段762和相应的上场板段724,下场板段722在沟槽710的底部714处在相应的电介质衬垫712上,中场板段762布置在相应的下场板段722上方,以及上场板段724布置在相应的中场板段762上方和相应的沟槽栅极720下面。场板段716和沟槽栅极720可主要包括n型多晶硅。电介质衬垫712可主要包括二氧化硅。电介质衬垫712将下场板段722、中场板段762和上场板段724与衬底702分离。将下场板段722与衬底702分离的电介质衬垫712比将中场板段762与衬底702分离的电介质衬垫712更厚,其进而比将上场板段724与衬底702分离的电介质衬垫712更厚。在沟槽710的侧壁上布置在上场板段724和衬底702之间的电介质衬垫712比在沟槽710的侧壁上布置在沟槽栅极720和衬底702之间的栅极电介质层718更厚。

[0068] 在此示例中,下场板段722与沟槽710中的中场板段762接触,且上场板段724与沟槽710中的沟槽栅极720接触,而中场板段762通过绝缘层726与上场板段724分离,绝缘层726布置在上场板段724和沟槽栅极720之间。在此示例中,应用到沟槽栅极720的偏置电压也因此应用到上场板段724,而应用到中场板段762的独立偏置电压也将下场板段722偏置到相同的独立偏置电压。

[0069] 晶体管704在衬底702中包括在垂直漂移区域708上方的p型主体730,其与栅极电介质层718邻接。晶体管704进一步包括在主体730上方并邻接栅极电介质层718的n型源极732。沟槽栅极720与垂直漂移区域708和源极732部分地同延。源电极734布置在衬底702上方,以与源极732和主体730电接触。源电极734通过沟槽栅极720上方的电介质帽层736与沟槽栅极720电绝缘。用于关于源极732和主体730的源电极734的其他配置在此示例的范围内。

[0070] 可在衬底702的顶部表面740处通过在栅极的暴露区域上的栅接触点738与沟槽栅极720和上场板段724电连接。可通过在场板上升管744上的组合的场板触点742与中场板段

762和下场板段722电连接,场板上升管744从中场板段762向上延伸到衬底702的顶部表面740。用于沟槽栅极720与中场板段762的电连接的其他结构在此示例范围内。形成沟槽栅极720和上场板段724与中场板段762和下场板段722绝缘有利地能够平衡如参照图1所讨论的用于沟槽栅极720和场板段716的独立偏压的优点以及如参照图3所讨论的组合的场板接触点742的优点。

[0071] 在半导体器件700的操作期间,沟槽栅极720有利地提供较高的电流密度,如参照图1所解释的。场板段716提供RESURF配置来维持垂直漂移区域708中的电场处于期望值,如参照图1所解释的。因此,通过形成具有上场板段724和下场板段722的组合的垂直型MOS晶体管704,使得晶体管704与具有单个场板的类似的垂直型MOS晶体管相比具有更浅的沟槽710,从而有利地减少半导体器件700的制造成本。

[0072] 在所描述的实施例中,修改是可能的,并且在权利要求范围内,其他实施例是可能的。

图1

图2A

图2B

图2C

图2D

图2E

图2F

图2G

图2H

图2I

图2J

图2K

图3

图4A

图4B

图4C

图4D

图4E

图5

图6A

图6B

图6C

图6D

图6E

图6F

图6G

图6H

图7