(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5343727号

(P5343727)

(45) 発行日 平成25年11月13日(2013.11.13)

(24) 登録日 平成25年8月23日(2013.8.23)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/372 (2011.01)  | HO4N 5/335 720 |

| HO4N 5/225 (2006.01)  | HO4N 5/225 F   |

| HO1L 27/148 (2006.01) | HO1L 27/14 B   |

| HO4N 101/00 (2006.01) | HO4N 101:00    |

請求項の数 7 (全 15 頁)

(21) 出願番号 特願2009-146500 (P2009-146500)

(22) 出願日 平成21年6月19日 (2009.6.19)

(65) 公開番号 特開2011-4246 (P2011-4246A)

(43) 公開日 平成23年1月6日 (2011.1.6)

審査請求日 平成24年6月14日 (2012.6.14)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100088100

弁理士 三好 千明

(72) 発明者 柏木 基志

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

(72) 発明者 中田 浩之

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

(72) 発明者 伊東 孝司

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

最終頁に続く

(54) 【発明の名称】デジタルカメラ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

被写体像を光電変換することによって、被写体像を表すアナログ信号を出力する固体撮像素子と、

前記固体撮像素子から出力されるアナログ信号に対してアナログ信号処理を施す信号処理手段と、

半押しと全押しの2段階での操作が可能なシャッターキーと、

前記シャッターキーが押されていない時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を、ライブビュー画像として表示手段に表示させる表示制御手段と、

前記シャッターキーが半押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報に基づき、被写体にピントを合わせるためのフォーカス制御を行うフォーカス制御手段と、

前記シャッターキーが全押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を記録媒体に保存するための記録制御を行う記録制御手段と、

前記シャッターキーが押されていない時を除いて、前記シャッターキーが半押し又は全押しされた時の前記フォーカス制御又は前記記録制御の最中における、画素情報として使用されない所定の電荷からなるアナログ信号が、画素情報として使用される電荷からなるアナログ信号よりも高速に前記固体撮像素子から書き出される高速書き出し期間中に、前記信号処理手段によるアナログ信号処理を停止させる停止制御手段と

を備えたことを特徴とするデジタルカメラ装置。

【請求項 2】

前記停止制御手段は、前記信号処理手段が固体撮像素子から出力されたアナログ信号を処理するための電力の供給を遮断することによって、前記信号処理手段による前記所定の電荷からなるアナログ信号のアナログ信号処理を停止させる

ことを特徴とする請求項1記載のデジタルカメラ装置。

【請求項 3】

前記画素情報として使用されない所定の電荷とは、前記固体撮像素子が有する全画素領域内における特定の画素領域であって、前記フォーカス制御手段によるフォーカス制御に際して画素情報として使用されない画素の電荷である

10

ことを特徴とする請求項1又は2記載のデジタルカメラ装置。

【請求項 4】

前記固体撮像素子は電荷転送型であり、

前記画素情報として使用されない所定の電荷とは、各画素の電荷の転送経路に時間の経過とともに蓄積される暗電流である

ことを特徴とする請求項1乃至3いずれか記載のデジタルカメラ装置。

【請求項 5】

前記停止制御手段は、さらに前記記録制御の最中における前記固体撮像素子での露光期間中にも前記信号処理手段によるアナログ信号処理を停止させる

ことを特徴とする請求項1乃至4いずれか記載のデジタルカメラ装置。

20

【請求項 6】

被写体像を光電変換することによって、被写体像を表すアナログ信号を出力する固体撮像素子と、前記固体撮像素子から出力されるアナログ信号に対してアナログ信号処理を施す信号処理手段と、半押しと全押しの2段階での操作が可能なシャッターキーとを備えたデジタルカメラ装置が有するコンピュータを、

前記シャッターキーが押されていない時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を、ライブビュー画像として表示手段に表示させる表示制御手段、

前記シャッターキーが半押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報に基づき、被写体にピントを合わせるためのフォーカス制御を行うフォーカス制御手段、

30

前記シャッターキーが全押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を記録媒体に保存するための記録制御を行う記録制御手段、

前記シャッターキーが押されていない時を除いて、前記シャッターキーが半押し又は全押しされた時の前記フォーカス制御又は前記記録制御の最中における、画素情報として使用されない所定の電荷からなるアナログ信号が、画素情報として使用される電荷からなるアナログ信号よりも高速に前記固体撮像素子から書き出される高速書き出し期間中に、前記信号処理手段によるアナログ信号処理を停止させる停止制御手段

として機能させることを特徴とするプログラム。

【請求項 7】

前記停止制御手段は、さらに前記記録制御の最中における前記固体撮像素子での露光期間中にも前記信号処理手段によるアナログ信号処理を停止させる

ことを特徴とする請求項6記載のプログラム。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CCD等の電荷転送型の固体撮像素子を備えたデジタルカメラ装置に関するものである。

【背景技術】

【0002】

50

従来、撮像装置の消費電力を削減するための技術として以下の技術が提案されている。例えば下記の特許文献1には、撮像装置に、撮像素子を駆動しているときのブランкиング期間中には、相関二重サンプリング処理のためのサンプルホールドのタイミングを示すタイミング信号を停止させて、ブランкиング期間中に相関二重サンプリング処理を停止させる動作を行わせる技術が提案されている。また、下記の特許文献2には、撮像装置に、長時間露光が行われた場合、長時間露光により得られた撮像信号が固体撮像素子から出力されるまでの期間は、CDSとPGAとアナログデジタル変換回路とからなるAFEを停止させる動作を行わせる技術が提案されている。さらに、下記の特許文献3には、撮像装置に、画像をくり返し撮像する際に、画像信号の読み出し期間以外の期間中は、AFEを停止させる動作を行わせる技術が提案されている。

10

#### 【先行技術文献】

##### 【特許文献】

###### 【0003】

【特許文献1】特開2008-160369号公報

【特許文献2】特開2007-104278号公報

【特許文献3】特開2006-81048号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

###### 【0004】

しかしながら、上記の各技術によれば撮像期間中における撮像装置の消費電力を削減することができるが、上記の各技術をデジタルカメラ装置に採用したとしても、ユーザによって撮影操作が行われている間における消費電力の削減効果が未だ十分とはいえないという問題があった。

20

###### 【0005】

本発明は、かかる従来の課題に鑑みてなされたものであり、デジタルカメラ装置において、撮影操作が行われている間の消費電力を従来に比べ一層削減することを目的とする。

##### 【課題を解決するための手段】

###### 【0006】

本発明の第1の観点に係るデジタルカメラ装置にあっては、被写体像を光電変換することによって、被写体像を表すアナログ信号を出力する固体撮像素子と、前記固体撮像素子から出力されるアナログ信号に対してアナログ信号処理を施す信号処理手段と、半押しと全押しの2段階での操作が可能なシャッターキーと、前記シャッターキーが押されていない時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を、ライブビュー画像として表示手段に表示させる表示制御手段と、前記シャッターキーが半押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報に基づき、被写体にピントを合わせるためのフォーカス制御を行うフォーカス制御手段と、前記シャッターキーが全押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を記録媒体に保存するための記録制御を行う記録制御手段と、前記シャッターキーが押されていない時を除いて、前記シャッターキーが半押し又は全押しされた時の前記フォーカス制御又は前記記録制御の最中における、画素情報として使用されない所定の電荷からなるアナログ信号が、画素情報として使用される電荷からなるアナログ信号よりも高速に前記固体撮像素子から掃き出される高速掃き出し期間中に、前記信号処理手段によるアナログ信号処理を停止させる停止制御手段とを備えたことを特徴とする。

30

###### 【0007】

本発明の第2の観点に係るプログラムにあっては、被写体像を光電変換することによって、被写体像を表すアナログ信号を出力する固体撮像素子と、前記固体撮像素子から出力されるアナログ信号に対してアナログ信号処理を施す信号処理手段と、半押しと全押しの2段階での操作が可能なシャッターキーとを備えたデジタルカメラ装置が有するコンピュータを、前記シャッターキーが押されていない時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を、ライブビュー画像として表示手段に表示させる表示

40

50

制御手段、前記シャッターキーが半押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を基づき、被写体にピントを合わせるためのフォーカス制御を行うフォーカス制御手段、前記シャッターキーが全押しされた時に、前記信号処理手段によるアナログ信号処理後の信号からなる画像情報を記録媒体に保存するための記録制御を行う記録制御手段、前記シャッターキーが押されていない時を除いて、前記シャッターキーが半押し又は全押しされた時の前記フォーカス制御又は前記記録制御の最中における、画素情報として使用されない所定の電荷からなるアナログ信号が、画素情報として使用される電荷からなるアナログ信号よりも高速に前記固体撮像素子から掃き出される高速掃き出し期間中に、前記信号処理手段によるアナログ信号処理を停止させる停止制御手段として機能させることを特徴とする。

10

## 【発明の効果】

## 【0008】

本発明によれば、デジタルカメラ装置において、撮影操作が行われている間の消費電力を従来に比べ一層削減することが可能となる。

## 【図面の簡単な説明】

## 【0009】

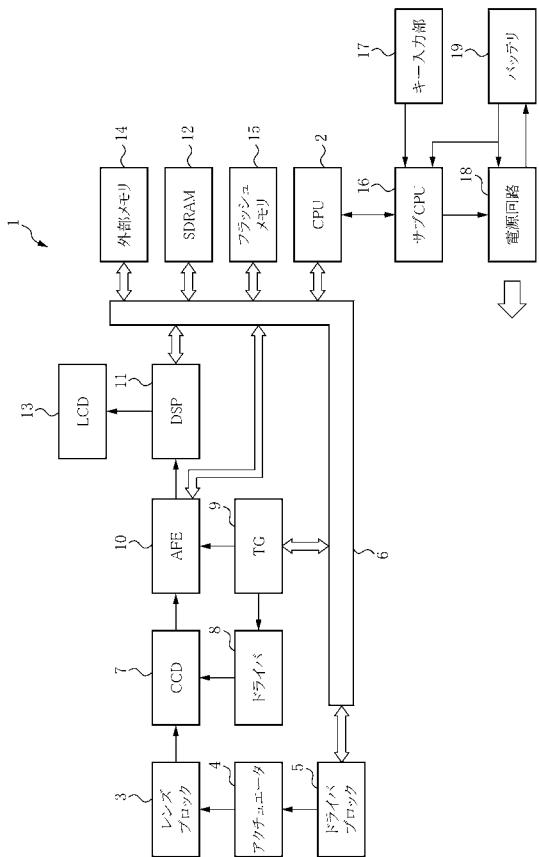

【図1】本発明を適用したデジタルカメラ装置のハードウェア構成の一例を示すブロック図である。

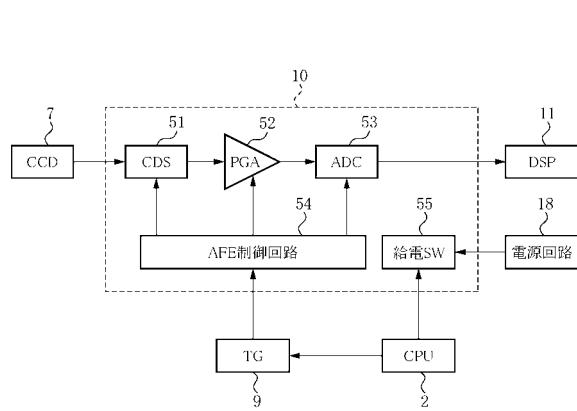

## 【図2】A F E の構成を示す図である。

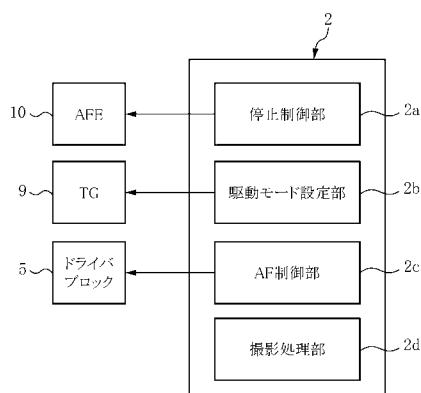

## 【図3】C P U の機能ブロック図である。

20

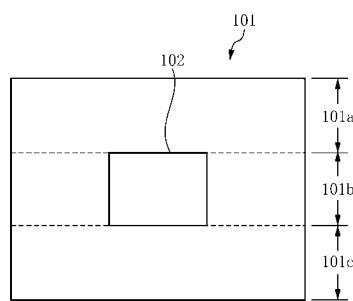

## 【図4】C C D の全画素領域に相当する撮像画面を示す図である。

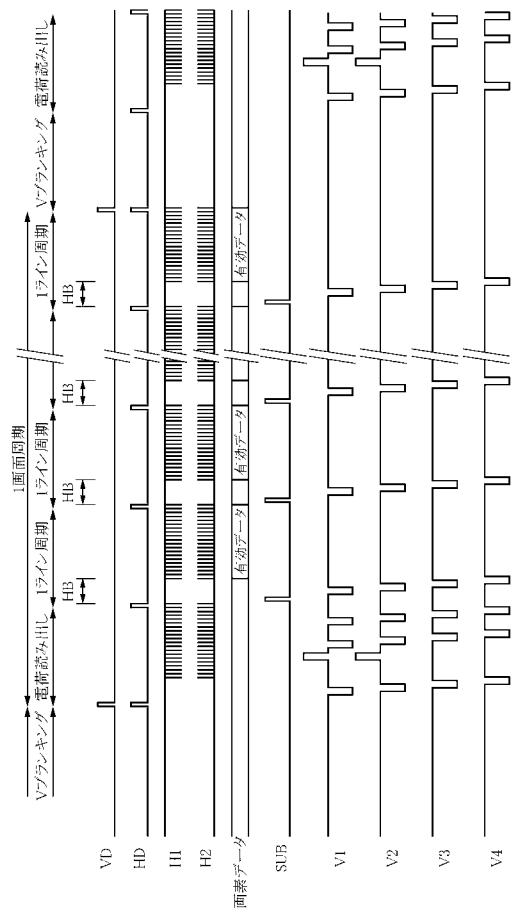

## 【図5】C C D のドラフトモードにおける動作を示すタイミングチャートである。

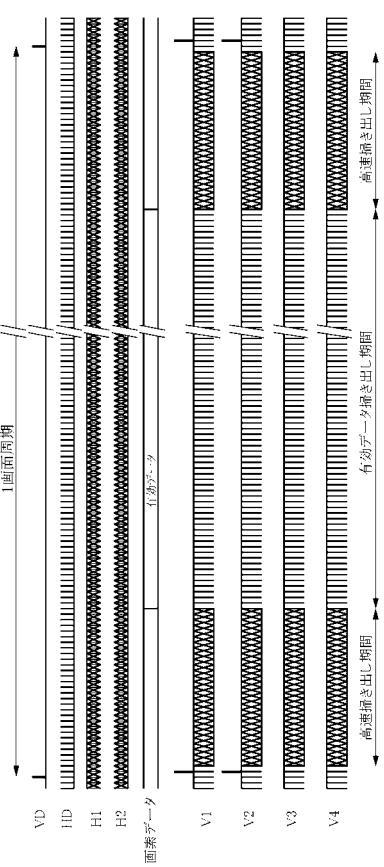

## 【図6】C C D のA F モードにおける動作を示すタイミングチャートである。

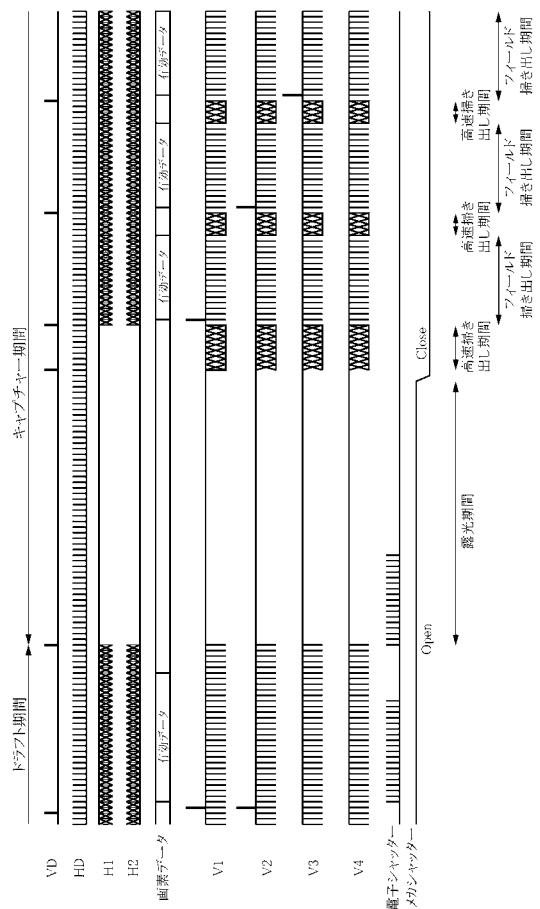

## 【図7】C C D のキャプチャーモードにおける動作を示すタイミングチャートである。

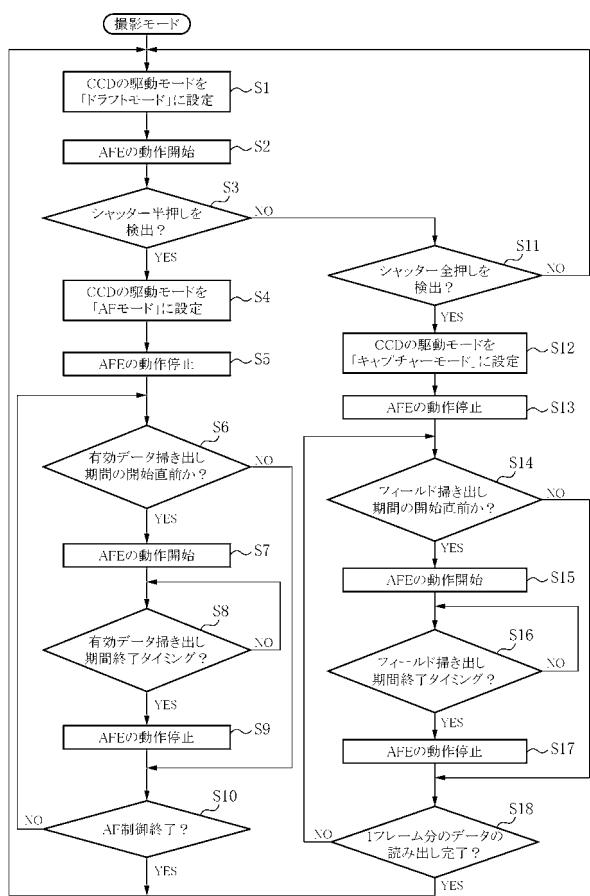

## 【図8】C P U の処理内容を示すフローチャートである。

## 【発明を実施するための形態】

## 【0010】

以下、本発明を適用した実施形態について、図を参照しながら説明する。図1は、本発明の実施形態として例示するデジタルカメラ装置1のハードウェア構成の概略を示すブロック図である。

30

## 【0011】

デジタルカメラ装置1は、C P U (Central Processing Unit) 2によってシステムの全体を制御される構成である。デジタルカメラ装置1は、フォーカスレンズを含む光学系とメカニカルシャッターからなるレンズブロック3と、レンズブロック3内における光学系、メカニカルシャッターをそれぞれ駆動するためのモータ等のアクチュエータ4とを有している。そして、アクチュエータ4を駆動するための各種のドライバにより構成されるドライバブロック5がバス6を介して接続されている。

## 【0012】

また、デジタルカメラ装置1は、被写体を撮像するための固体撮像素子としてC C D (Charge Coupled Device) 7を有している。C C D 7は公知の電荷転送型の固体撮像素子であり、図示しないが、水平及び垂直方向に多数配置されて各々が画素を構成する多数のフォトダイオードが設けられるとともに、フォトダイオードの各列に複数の垂直転送C C Dの列が隣接し、最後の行の垂直転送C C Dに隣接して水平転送C C Dが1本設けられた構造である。

40

## 【0013】

ドライバ8は、T G (Timing Generator) 9が生成した垂直C C D駆動タイミング信号と、水平C C D駆動タイミング信号と、電子シャッタタイミング信号とに従い、C C D駆動信号を生成する。そして、ドライバ8は、生成したC C D駆動信号をC C D 7へ供給してC C D 7を駆動する。

## 【0014】

50

T G 9 は、上記の垂直 C C D 駆動タイミング信号と、水平 C C D 駆動タイミング信号と、電子シャッタタイミング信号とからなる駆動タイミング信号を、C P U 2 により設定された駆動モードに応じて生成する。C C D 7 の駆動モードは、ドラフトモードと A F モードとキャプチャーモードとの3種類である。T G 9 は、C C D 7 の駆動モードの種類を示す設定値を記憶するレジスタを内部に有しており、上記設定値がC P U 2 により設定されることにより、各々の駆動モードに応じた上記の駆動タイミング信号（垂直 C C D 駆動タイミング信号、水平 C C D 駆動タイミング信号、電子シャッタタイミング信号）を生成する。

#### 【 0 0 1 5 】

C C D 7 は、ドライバ 8 によって駆動されることにより、レンズプロック 3 の光学系において結像された被写体の光学像（被写体像）を光電変換することによって、被写体像を表すアナログの撮像信号を A F E (Analog Front End) 10 に供給する。 10

#### 【 0 0 1 6 】

図 2 は、A F E 10 の構成を示した図である。A F E 10 は、C D S (Correlated Double Sampling) 5 1 と、P G A (Programmable Gain Amp) 5 2、A D C (Analog-to-Digital converter) 5 3、A F E 制御回路 5 4、給電スイッチ 5 5 から構成され、信号処理手段として機能する。

#### 【 0 0 1 7 】

C D S 5 1 は、C C D 7 から供給されたアナログの撮像信号に含まれるノイズを相関二重サンプリングによって除去し、ノイズ除去後の撮像信号を P G A 5 2 へ供給する。P G A 5 2 は、ノイズ除去後の撮像信号を増幅し、増幅後の撮像信号を A D C 5 3 へ供給する。A D C 5 3 は、増幅後の撮像信号をデジタルの撮像信号に変換し、変換後のデジタル撮像信号を D S P (Digital Signal Processor) 11 へ出力する。C D S 5 1 による撮像信号からのノイズ除去と、P G A 5 2 による撮像信号の増幅と、A D C 5 3 による撮像信号のデジタル変換とからなる一連の信号処理が A F E 10 のアナログ信号処理である。 20

#### 【 0 0 1 8 】

A F E 制御回路 5 4 は、T G 9 から供給される A F E 駆動信号を受け取る。A F E 駆動信号とは、A F E 10 におけるアナログ信号処理の処理タイミングを規定する信号である。A F E 制御回路 5 4 は、A F E 駆動信号が示すタイミングで C D S 5 1 と P G A 5 2 と A D C 5 3 との各アナログ回路の駆動を制御する。給電スイッチ 5 5 は、電源回路 1 8 から上記の各アナログ回路へ供給される駆動電流を、C P U 2 から供給される駆動開始信号および駆動停止信号に従いオン・オフ制御する。各アナログ回路へ供給される駆動電流は、各アナログ回路を駆動するための電流である。 30

#### 【 0 0 1 9 】

D S P 1 1 は、入力した撮像信号に対しペデスタルクランプ等の処理を施して R G B データに変換し、さらに R G B データを輝度 (Y) 成分及び色差 (U V) 成分からなる Y U V データに変換する。また、D S P 1 1 は、Y U V データにオートホワイトバランス、輪郭強調、画素補間などの画品質向上のためのデジタル信号処理を施し、順次 S D R A M 1 2 に記憶させる。 40

#### 【 0 0 2 0 】

撮影用の記録モードでは、S D R A M 1 2 に1フレーム分（1画面分）のY U V データ（画像データ）が蓄積される毎に、Y U V データが液晶モニタ 1 3 へ送られてライブビュー画像として画面表示される。また、シャッターキーが押された撮影時には、C P U 2 が S D R A M 1 2 に一時記憶されるY U V データを圧縮し、所定のフォーマットの画像ファイルとして外部メモリ 1 4 に記録する。外部メモリ 1 4 は、図示しないカードインターフェイスを介してカメラ本体に接続された着脱自在なメモリカードである。

#### 【 0 0 2 1 】

再生モードにおいてC P U 2 は、外部メモリ 1 4 に記録された画像ファイルをユーザの選択操作に応じて読み出して伸張し、Y U V データとして S D R A M 1 2 に展開させた後、液晶モニタ 1 3 に表示させる。 50

## 【0022】

フラッシュメモリ15は、CPU2にカメラ全体を制御させるための複数種のプログラムやデータが記憶されているプログラム格納用メモリである。フラッシュメモリ15に記憶されているプログラムには、レンズブロック3の光学系を、公知のコントラスト検出方式によって被写体にピントが合うフォーカス位置へ自動制御するAF(auto focus)制御を行うためのAF制御プログラムが含まれる。

## 【0023】

CPU2によるAF制御は、画角内の中央部分に存在する被写体にピントを合わせる中央重点方式である。AF制御に際してCPU2は、レンズブロック3の光学系を移動させながら、CCD2の有効画素領域101における予め決められている中央部分102(図4参照)に相当する画像データにおけるコントラストを逐次検出し、コントラストが最大となる位置、つまりフォーカス位置に光学系を移動させるものである。

10

## 【0024】

一方、CPU2にはサブCPU16が接続されている。サブCPU16には電源ボタンや撮影を指示するためのシャッターキー、ズーム操作ボタン、モード切替キー等のスイッチ類から構成されるキー入力部17と電源回路18が接続されている。キー入力部17におけるシャッターキーは、半押し操作(ハーフシャッター)と全押し操作との2段階操作が可能な所謂ハーフシャッター機能を備えたものであり、記録モードではシャッターキーの半押し操作がCPU2によるAF制御の開始トリガとなる。

## 【0025】

20

サブCPU16は、キー入力部17におけるスイッチ類の操作状態を定常的にスキャンし、ユーザによるスイッチ操作の内容に応じた操作信号をCPU2へ送る。電源回路18は、カメラ本体に収容されたバッテリ19を電源として、デジタルカメラ装置1の基準電圧、及び前述した各部が必要とする電圧を生成し各部に供給する。

## 【0026】

30

図3は、デジタルカメラ装置1に記録モードが設定されているとき、CPU2が、フラッシュメモリ15に記憶されている前述したプログラムに基づき動作することにより実現される機能の一部を示した機能ブロック図である。記録モードにおいてCPU2は、停止制御部2a、駆動モード設定部2b、AF制御部2c、撮影処理部2dとして機能する。そして、記録モードにおいては停止制御部2aが必要に応じて前述したAFE10の動作を停止させる。また、駆動モード設定部2bが、デジタルカメラ装置1の動作に応じてCCD7の駆動モードを設定し、設定した駆動モードに応じた駆動タイミング信号をTG9に生成させる。また、AF制御部2cが、ドライバブロック5を制御することによりレンズブロック3の光学系を移動させる。また、撮影処理部2dが、デジタルカメラ装置1における上記以外の種々の動作を制御する。

## 【0027】

ここで、前述したCCD7の駆動モードについて説明する。CCD7の駆動モードは、ドラフトモードとAFモードとキャプチャーモードとの3種類である。

## 【0028】

40

ドラフトモードは、液晶モニタ13がライブビュー画像を表示している間に設定される駆動モードである。図5は、ドラフトモードにおいてドライバ8が出力するCCD駆動信号を示したタイミングチャートである。垂直同期信号VDは、1画面周期のタイミング信号、つまりCCD7に蓄積された1フレーム分の電荷の読み出し開始タイミングを示す信号である。水平同期信号HDは、1ライン周期のタイミング信号、つまりCCD7に蓄積された1ライン分の電荷の読み出し開始タイミングを示す信号である。ここで、1ラインとは、CCD7において水平及び垂直方向に配置されているフォトダイオードが並ぶ水平方向の各々の行(水平方向に連なる一列分の画素)である。

## 【0029】

ドライバ8は、図5に示したように、垂直同期信号VDの出力間隔である1画面周期において、電荷の垂直転送用の電圧を印加するための電極数(ここでは4電極)に応じた4

50

相の垂直 C C D 駆動パルス V 1 ~ V 4 と、電荷の水平転送用の電圧を印加するための電極数（ここでは 2 電極）に応じた 2 相の水平 C C D 駆動パルス H 1 , H 2 と、電子シャッターパルス S U B を出力する。

#### 【 0 0 3 0 】

C C D 7 のフォトダイオードに蓄積された各画素の電荷は、1 画面周期内において、垂直同期信号 V D の立ち上がり直後の電荷読み出し期間（図 5 で「電荷読み出し」）に垂直転送 C C D へ転送される。さらに、水平同期信号 H D の出力間隔である 1 ライン周期毎に、垂直 C C D 駆動パルス V 1 ~ V 4 によって、垂直転送 C C D ( 転送経路 ) へ転送された各ラインの電荷が水平転送 C C D ( 水平転送路 ) へ順に垂直転送されて、1 ライン分の電荷が水平転送 C C D へ転送される。そして、水平転送 C C D へ転送された 1 ライン分の電荷が、水平 C C D 駆動パルス H 1 , H 2 に同期して順に C C D 7 から出力される。また、ドライバ 8 は、垂直 C C D 駆動パルス V 1 ~ V 4 を出力する期間、水平 C C D 駆動パルス H 1 , H 2 の出力を停止する。水平 C C D 駆動パルス H 1 , H 2 が停止している期間（図 5 で「 H B 」）は H ブランкиング期間と呼ばれる。

10

#### 【 0 0 3 1 】

そして、1 画面周期に C C D 7 の全画素分（1 フレーム分）の電荷が撮像信号として出力され、複数ライン分の蓄積電荷の画素データ、つまり図 5 に示した有効データに基づきライブビュー画像が生成される。なお、1 画面周期は C C D 7 の全画素分の蓄積電荷の出力にかかる時間よりも長く設定されており、全画面分の蓄積電荷が出力し終わると C C D 7 からは無効な蓄積電荷が出力される。この無効な蓄積電荷が出力される期間（図 5 で「 V ブランкиング」）は、一般に V ブランкиング期間と呼ばれる。

20

#### 【 0 0 3 2 】

また、前述した A F モードは、C P U 2 が A F 制御を行っている A F 制御期間、より具体的にはユーザによりシャッターキーの半押し操作が行われた直後から、レンズロック 3 の光学系がフォーカス位置に移動するまでの期間に設定される駆動モードである。図 6 は、ドライバ 8 が、C C D 7 を A F モードで駆動している間の 1 画面周期内に出力する C C D 駆動信号を示したタイミングチャートである。

#### 【 0 0 3 3 】

前述したように C P U 2 による A F 制御はコントラスト検出方式で、かつ中央重点方式であるため、画面の中央部分の画素データのみが A F 制御に必要であり、中央部分を除く他の部分の画素データは A F 制御に不要である。そのため A F モードでの 1 画面周期内においてドライバ 8 は、図 4 に示した C C D 7 の有効画素領域 1 0 1 の中央部分 1 0 2 の上側の上側画素領域 1 0 1 a と、中央部分 1 0 2 の下側の下側画素領域 1 0 1 c とに配置されているフォトダイオードの蓄積電荷を掃き捨てる。そして、上側画素領域 1 0 1 a と下側画素領域 1 0 1 c とに挟まれた中央部分 1 0 2 を含む中間画素領域 1 0 1 b に配置されているフォトダイオードの蓄積電荷のみを C C D 7 から出力させる。

30

#### 【 0 0 3 4 】

すなわち 1 画面周期内にドライバ 8 は、図 4 に示した C C D 7 の有効画素領域 1 0 1 の上側画素領域 1 0 1 a と下側画素領域 1 0 1 c の蓄積電荷を読み出す複数ライン分のライン周期内に、垂直 C C D 駆動パルス V 1 ~ V 4 と水平 C C D 駆動パルス H 1 , H 2 を同時に output する高速掃き出し駆動という駆動を行う。すなわちドライバ 8 は、上側画素領域 1 0 1 a と下側画素領域 1 0 1 c をそれぞれ構成する複数ライン分の蓄積電荷をフォトダイオードから垂直転送 C C D に転送した後、一気に垂直転送して水平転送 C C D に送る。さらに、ドライバ 8 は、水平転送 C C D に溜まった（加算された）複数ライン分の電荷を一気に水平転送して掃き出させる。

40

#### 【 0 0 3 5 】

ドライバ 8 が高速掃き出し駆動を行う期間が図 6 に示した高速掃き出し期間である。すなわち高速掃き出し期間は、C C D 7 の有効画素領域 1 0 1 の上側画素領域 1 0 1 a と下側画素領域 1 0 1 c における、A F 制御において画素情報として使用されない所定の画素の電荷を、C C D 7 の有効画素領域 1 0 1 の中間画素領域 1 0 1 b における A F 制御に

50

おいて画素情報として使用される画素よりも高速で掃き出させる駆動期間である。

【0036】

また、ドライバ8は、高速掃き出し期間を除く、図4に示したCCD7の有効画素領域101の中間画素領域101bに対応する複数ライン分のライン周期、つまり図6に示した有効データ掃き出し期間には、ドラフトモードの場合と同様の垂直CCD駆動パルスV1～V4と水平CCD駆動パルスH1, H2とを出力する。そして、ドライバ8は、CCD7の有効画素領域101の中間画素領域101bの連続する複数ライン分の蓄積電荷、すなわちフォーカス制御時に画素情報として使用される画素の電荷を1ライン分ずつ水平転送CCDに垂直転送した後、1ライン毎に水平転送して水平転送CCDから掃き出せる。

10

【0037】

そして、AF制御期間においては、CPU2によって、CCD7の有効画素領域101の中間画素領域101bにおいて隣接する複数ライン分の蓄積電荷の画素データ、つまり図6に示した有効データのみに基づいたAF制御が行われる。

【0038】

また、キャプチャーモードは、ユーザによりシャッターキーの全押し操作が行われた直後から、シャッター速度に応じて露光時間が経過した後、露光時間内にフォトダイオードに蓄積された全画素分の蓄積電荷のCCD7からの掃き出しが完了するまでの期間に設定される駆動モードである。図7は、キャプチャーモードにおいてドライバ8が出力するCCD駆動信号を示したタイミングチャートである。

20

【0039】

キャプチャーモードにおける図5に示したドラフトモードとの違いは、以下の通りである。すなわちキャプチャーモードにおいてドライバ8は、露光期間中はメカニカルシャッターを使用するため、垂直CCD駆動パルスV1～V4と水平CCD駆動パルスH1, H2の出力を停止する。

【0040】

また、露光期間終了後にドライバ8は、垂直CCD駆動パルスV1～V4と水平CCD駆動パルスH1, H2とを出力することによって、露光期間中に各フォトダイオードに蓄積された全画素分（複数ライン分）の電荷を、1フィールドを単位として水平転送CCDから掃き出せる。

30

【0041】

ここで、1フィールド分のアナログ信号（撮像信号）はnライン間隔の複数ラインに属する画素の電荷により構成される。例えば「n=3」の場合には、水平転送CCDに接するラインを1番目として、1フィールド目が1番目、4番目、7番目、・・・の各ラインで構成され、2フィールド目が2番目、5番目、8番目、・・・の各ラインで構成され、3フィールド目が3番目、6番目、9番目、・・・の各ラインで構成される。

【0042】

上記の例に従い具体的に説明すると、ドライバ8は、まず1フィールド目の複数ライン（1番目、4番目、7番目、・・・の各ライン）のフォトダイオードの蓄積電荷を垂直転送CCDに転送し、垂直転送CCDに転送した各ラインの電荷を水平転送CCDに順に垂直転送した後、1ライン毎に水平転送して水平転送CCDから掃き出せる。次に、2フィールド目の複数ライン（2番目、5番目、8番目、・・・の各ライン）のフォトダイオードの蓄積電荷を上記と同様の手順の転送動作によって水平転送CCDから順に掃き出せる。さらに、3フィールド目の複数ライン（3番目、6番目、9番目、・・・の各ライン）のフォトダイオードの蓄積電荷を上記と同様の手順の転送動作によって水平転送CCDから順に掃き出せる。

40

【0043】

つまり上記の例では、ドライバ8は、複数ライン分のライン周期からなるフィールド単位の転送動作を3回繰り返すことによって、全画素分の電荷を水平転送CCDから掃き出せる。図7に示したフィールド掃き出し期間がドライバ8による各フィールドの蓄積電

50

荷の掃き出しが行われる期間である。

【0044】

また、キャプチャーモードにおいては、露光期間の終了直後と1フィールド目のフィールド掃き出し期間との間、及びその後における相前後する各々のフィールド掃き出し期間の間に高速掃き出し期間が存在する。そして、ドライバ8は、各々の高速掃き出し期間には、垂直CCD駆動パルスV1～V4と水平CCD駆動パルスH1, H2を同時に出力する高速掃き出し駆動を行う。

【0045】

ただし、キャプチャーモードにおける高速掃き出し駆動は、図6に示したAFモードにおける高速掃き出し駆動とは次の点で異なる。すなわち、キャプチャーモードにおける高速掃き出し駆動に際してドライバ8は、全ての垂直転送CCDに蓄積されている電荷を一気に水平転送CCDに転送した後、水平転送CCDに溜まった（加算された）全てのライン分の電荷を一気に水平転送して掃き出させる。ここで、前述した全てのラインの垂直転送CCDに蓄積されている電荷は、垂直転送CCDに時間の経過とともに蓄積される暗電流と呼ばれる、固定パターンノイズの原因となる電荷である。

10

【0046】

つまりキャプチャーモードでの駆動中における高速掃き出し期間は、AFモードでの駆動中における高速掃き出し期間とは異なり、画素情報として使用されない垂直転送CCDにおいて蓄積された見かけ上の画素の電荷（暗電流）を、フォトダイオードで蓄積されて画素情報として使用される実際の画素の電荷よりも高速で掃き出させる駆動期間である。

20

【0047】

次に、図3に示したCPU2の各機能部分によって実現される記録モードでのCPU2の処理内容を図8のフローチャートに従い説明する。

【0048】

記録モードにおいては、まず撮影処理部2dが、CCD7の駆動モードをドラフトモードに設定する（ステップS1）。すなわち撮影処理部2dは、ドラフトモードに応じた駆動タイミング信号をTG9に生成させ、ドライバ8に図5に示したCCD7のドラフトモードでの駆動を開始させる。

【0049】

また、撮影処理部2dは、CCD7のドラフトモードでの駆動開始と並行してAFE10を動作状態とする（ステップS2）。ここで、AFE10における動作状態とは、AFE10が、CDS51とPGA52とADC53による一連のアナログ信号処理を行う状態である。係るステップS2の処理において撮影処理部2dは、TG9に、AFE駆動信号の生成、及びAFE制御回路54へのAFE駆動信号の出力を開始させる。同時に、撮影処理部2dは、給電スイッチ55に駆動開始信号を送ることによって、CDS51とPGA52とADC53の各アナログ回路への駆動電流の供給を開始する。

30

【0050】

以後、撮影処理部2dは、ユーザによるシャッターキーの半押し操作の有無、及びシャッターキーの全押し操作の有無を逐次確認する（ステップS3、ステップS11）。そして、ユーザによるシャッターキーの半押し操作、及びシャッターキーの全押し操作が検出できない間は（ステップS3：NO、ステップS11：NO）、そのままCCD7をドラフトモードで駆動する。

40

【0051】

その後、CPU2においては、CCD7をドラフトモードで駆動している間に、撮影処理部2dがシャッターキーの半押し操作を検出すると（ステップS3：YES）、駆動モード設定部2bが、直ちにCCD7の駆動モードをAFモードに設定する（ステップS4）。すなわち駆動モード設定部2bは、AFモードに応じた駆動タイミング信号をTG9に生成させ、ドライバ8に図6に示したCCD7のAFモードでの駆動を開始させる。

【0052】

また、CPU2においては、CCD7のAFモードでの駆動開始と並行して、停止制御

50

部2aが、AFE10をいったん停止状態とする(ステップS5)。ここで、AFE10における停止状態とは、AFE10がCDS51とPGA52とADC53による一連のアナログ信号処理を停止した状態である。係るステップS5の処理において停止制御部2aは、TG9に、AFE駆動信号の生成を停止させる。同時に、停止制御部2aは、給電スイッチ55に駆動停止信号を送ることによって、CDS51とPGA52とADC53の各アナログ回路への駆動電流の供給を停止する。なお、図示しないがCPU2においては、ステップS5の処理と並行して撮影処理部2dが前述したAF制御を開始する。

#### 【0053】

その後、撮影処理部2dは、CCD7をAFモードで駆動しているとき、前述したいずれかの1画面周期内における有効データ掃き出し期間の開始タイミングが到来する直前までの間、つまり前述した高速掃き出し期間は(ステップS6: NO)、AFE10を停止状態に保持する。やがて、撮影処理部2dは、有効データ掃き出し期間の開始直前のタイミングが到来したら(ステップS6: YES)、有効データ掃き出し期間の開始直前のタイミングに同期してAFE10を動作状態とする(ステップS7)。係るステップS7の処理における具体的な処理内容は、前述したステップS2の処理と同様である。

10

#### 【0054】

なお、撮影処理部2dが、AFE10を停止状態から動作状態とするタイミングが有効データ掃き出し期間の開始タイミングではなく、開始直前のタイミングであるのは以下の理由による。すなわちCPU2がAFE10を動作状態としてから、AFE10の前述した各アナログ回路における信号処理動作が安定するまでには一定時間が必要であるためである。

20

#### 【0055】

引き続き、撮影処理部2dは、有効データ掃き出し期間の終了タイミング、つまり高速掃き出し期間の開始タイミングが到来するまでは(ステップS8: NO)、AFE10を動作状態に保持する。やがて、有効データ掃き出し期間の終了タイミング(高速掃き出し期間の開始タイミング)が到来すると(ステップS8: YES)、停止制御部2aが、有効データ掃き出し期間の終了タイミングに同期してAFE10を再び停止状態とする(ステップS9)。係るステップS9の処理における具体的な処理内容は、前述したステップS5の処理と同様である。

30

#### 【0056】

以後、CPU2においては、AF制御が完了するまでの間は(ステップS10: NO)、ステップS6の処理に戻り、前述したステップS6～S9の各処理を繰り返し行う。そして、AF制御が完了した時点で(ステップS10: YES)、前述したステップS1の処理に戻って、撮影処理部2dが、CCD7の駆動モードを再びドラフトモードに設定し、かつAFE10を再び動作状態とする(ステップS2)。

#### 【0057】

一方、CPU2においては、CCD7をドラフトモードで駆動している間に、撮影処理部2dがシャッターキーの全押し操作を検出すると(ステップS3: NO、ステップS11: YES)、駆動モード設定部2bが、直ちにCCD7の駆動モードをキャプチャーモードに設定する(ステップS12)。すなわち駆動モード設定部2bは、キャプチャーモードに応じた駆動タイミング信号をTG9に生成させ、ドライバ8に図7に示したCCD7のキャプチャーモードでの駆動を開始させる。

40

#### 【0058】

また、CCD7のキャプチャーモードでの駆動開始と並行して、停止制御部20aがAFE10をいったん停止状態とする(ステップS13)。係るステップS13の処理における具体的な処理内容は、前述したステップS5, S9の処理と同様である。なお、図示しないがCPU2においては、ステップS12及びステップS13の処理と並行して、撮影処理部2dがCCD7の露光時間のカウントを開始する。

#### 【0059】

その後、撮影処理部2dが、CCD7をキャプチャーモードで駆動しているとき、最初

50

の前述したフィールド掃き出し期間、すなわち 1 フィールド分の画素の電荷を掃き出させる駆動期間が到来する直前までの間、言い換えると、前述した露光期間と、露光期間に続いている垂直転送 CCD に蓄積されている暗電流を高速に掃き出させる高速掃き出し期間は（ステップ S14：NO）、AFE10 を停止状態に保持する。やがて、フィールド掃き出し期間の開始直前のタイミングが到来すると（ステップ S14：YES）、停止制御部 20a が、フィールド掃き出し期間の開始直前のタイミングに同期して AFE10 を動作状態とする（ステップ S15）。係るステップ S15 の処理における具体的な処理内容は、前述したステップ S2, S7 の処理と同様である。

#### 【0060】

引き続き、CPU2 においては、撮影処理部 2d が、フィールド掃き出し期間の終了タイミング、つまり 2 回目の高速掃き出し期間の開始タイミングが到来するまでは（ステップ S16：NO）、AFE10 を動作状態に保持する。やがて、撮影処理部 2d は、フィールド掃き出し期間の終了タイミング（高速掃き出し期間の開始タイミング）が到来したら（ステップ S16：YES）、停止制御部 20a が、フィールド掃き出し期間の終了タイミングに同期して AFE10 を再び停止状態とする（ステップ S17）。係るステップ S17 の処理における具体的な処理内容は、前述したステップ S5, S9, S13 の処理と同様である。

#### 【0061】

以後、CPU2 においては、CCD7 から 1 フレーム分のアナログ信号（撮像信号）の読み出しが完了するまでの間は（ステップ S18：NO）、ステップ S14 の処理に戻り、前述したステップ S14～S17 の各処理を繰り返し行う。そして、全フレームデータの読み出しが完了した時点で（ステップ S18：YES）、前述したステップ S1 の処理に戻って、撮影処理部 2d が、CCD7 の駆動モードを再びドラフトモードに設定し、かつ AFE10 を再び動作状態とする（ステップ S2）。

#### 【0062】

そして、CPU2 においては、デジタルカメラ装置 1 に記録モードが設定されている間、撮影処理部 2d が、ユーザによるシャッターキーの半押し操作、又は全押し操作を検出する毎に前述したステップ S3 以降の処理を繰り返し実行する。

#### 【0063】

以上述べたように CPU2 は、記録モードにおいて CCD7 を AF モード、及びキャプチャーモードで駆動しているとき、各々の駆動モードにおける高速掃き出し期間には、AFE10 のアナログ信号処理を停止した状態とする。つまり CPU2 は、AF モードでは、AF 制御において画素情報として使用されない所定の画素の電荷を CCD7 から高速に掃き出させている駆動期間に AFE10 のアナログ信号処理を停止させる。また、CPU2 は、キャプチャーモードでは、画素情報として使用されない、垂直転送 CCD において蓄積された見かけ上の画素の電荷（暗電流）を CCD7 から高速に掃き出させている駆動期間に AFE10 のアナログ信号処理を停止させる。なお、CPU2 は、CCD7 をキャプチャーモードで駆動している間、露光期間においても AFE10 のアナログ信号処理を停止させる。

#### 【0064】

したがって、本実施形態のデジタルカメラ装置 1 においては、記録モードが設定された状態において前述した高速掃き出し期間の AFE10 における無用の動作、すなわち画素情報として使用されない所定の画素の電荷からなるアナログ信号に対するアナログ信号処理による電力消費をなくすことができる。よって、撮影操作を行っている間の消費電力を従来に比べてより一層削減することができる。なお、画素情報として使用されない所定の画素の電荷とは、アナログ信号として CCD7 から出力される電荷のうちで被写体像の表現（再現）に寄与しない電荷である。

#### 【0065】

ここで、本実施形態のデジタルカメラ装置 1 には、高速掃き出し期間に AFE10 を停止状態とするとき、CDS51 と PGA52 と ADC53 の各アナログ回路の全ての動作

10

20

30

40

50

を停止させる構成を採用した。しかし、本発明の実施に際しては、例えばデジタルカメラ装置1の構成を、A F E 1 0の何れか1つ、または何れか2つのアナログ回路の動作を停止させる構成に変更することができる。つまりA F E 1 0の少なくとも何れか1つの動作を高速掃き出し期間に停止させる構成であっても、撮影操作を行っている間の消費電力を従来に比べてより一層削減することができる。

#### 【0066】

また、本実施形態のデジタルカメラ装置1には、A F E 1 0の各アナログ回路の動作を停止させるとき、T G 9に、A F E 1 0へ供給するA F E 駆動信号の生成を停止させ、同時に、A F E 1 0の各アナログ回路への駆動電流の供給を停止させる構成を採用した。しかし、例えばデジタルカメラ装置1の構成を、A F E 1 0の各アナログ回路の動作を停止させるとき、T G 9におけるA F E 駆動信号の生成の停止か、またはA F E 1 0の各アナログ回路への駆動電流の供給の停止の何れか一方のみを実施する構成に変更しても構わない。

10

#### 【0067】

また、本実施形態では、C P U 2によるA F 制御が中央重点方式であり、撮像した画像の中央領域のみの画像情報（コントラスト）に基づきピントを合わせる構成について説明した。しかし、C P U 2によるA F 制御は、撮像した画像の中央領域以外の他の領域（1又は複数の領域）の画像情報に基づくものに変更することができる。ただし、撮像した画像の中央領域以外の他の領域の画像情報に基づくA F 制御を行う構成では、C C D 7をA F モードで駆動するとき、ドライバ8には、中央領域以外の他の領域に応じた駆動期間に高速掃き出し駆動を行わせる必要がある。

20

#### 【0068】

また、前述したデジタルカメラ装置1は、記録モードにおいてC C D 7がA F モード、又はキャプチャーモードのいずれか一方の駆動モードに設定されているときだけ、高速掃き出し期間にA F E 1 0を動作状態とする構成とすることもできる。A F モード、又はキャプチャーモードにおける高速掃き出し期間にA F E 1 0を動作状態とする構成であっても、撮影操作を行っている間の消費電力は従来に比べてより一層削減することができる。

#### 【0069】

また、本実施形態においてC P U 2により実現される停止制御部2aの機能は、必要に応じて他のハードウェア構成によって実現させる構成に適宜変更することができる。

30

#### 【符号の説明】

#### 【0070】

- |     |            |

|-----|------------|

| 1   | デジタルカメラ    |

| 2   | C P U      |

| 3   | レンズブロック    |

| 5   | ドライバブロック   |

| 7   | C C D      |

| 8   | ドライバ       |

| 9   | T G        |

| 1 0 | A F E      |

| 1 1 | D S P      |

| 1 8 | 電源回路       |

| 1 9 | バッテリ       |

| 5 1 | C D S      |

| 5 2 | P G A      |

| 5 3 | A D C      |

| 5 4 | A F E 制御回路 |

| 5 5 | 給電スイッチ     |

40

【 図 1 】

【 図 2 】

【図3】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

審査官 若林 治男

(56)参考文献 特開平11-275445 (JP, A)

特開2008-187614 (JP, A)

特開2001-078097 (JP, A)

特開2007-074363 (JP, A)

特開2008-067281 (JP, A)

特開2000-354189 (JP, A)

特開2001-324672 (JP, A)

特開2010-130235 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257

H01L 27/148