(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6594296号

(P6594296)

(45) 発行日 令和1年10月23日(2019.10.23)

(24) 登録日 令和1年10月4日(2019.10.4)

(51) Int.Cl.

F 1

|               |           |              |   |

|---------------|-----------|--------------|---|

| HO 1 L 21/329 | (2006.01) | HO 1 L 29/90 | D |

| HO 1 L 29/866 | (2006.01) | HO 1 L 29/91 | B |

| HO 1 L 29/868 | (2006.01) | HO 1 L 29/91 | D |

| HO 1 L 29/861 | (2006.01) |              |   |

請求項の数 4 (全 8 頁)

(21) 出願番号 特願2016-516551 (P2016-516551)

(86) (22) 出願日 平成26年9月26日 (2014.9.26)

(65) 公表番号 特表2016-536778 (P2016-536778A)

(43) 公表日 平成28年11月24日 (2016.11.24)

(86) 國際出願番号 PCT/US2014/057577

(87) 國際公開番号 WO2015/050776

(87) 國際公開日 平成27年4月9日 (2015.4.9)

審査請求日 平成29年9月22日 (2017.9.22)

(31) 優先権主張番号 14/043,431

(32) 優先日 平成25年10月1日 (2013.10.1)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 508121463

ヴィシェイ ジェネラル セミコンダクタ

ー、エルエルシー

VISHAY GENERAL SEMI

CONDUCTOR, LLC

アメリカ合衆国・ニューヨーク・1178

8・ホーポージ・モーター・パークウェイ

・150

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

(74) 代理人 100133400

弁理士 阿部 達彦

最終頁に続く

(54) 【発明の名称】 改善された逆サージ能力及び削減されたリーク電流のポリシリコン層を有するツエナーダイオード

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスを製造するための方法であつて、

半導体基板の残りの部分が露出されるように、第1酸化物層を、第1導電型を有する第1半導体材料から形成された前記半導体基板の一部分にわたって形成する工程と、

前記半導体基板の第1表面上に、及び前記第1酸化物層上に保護層を形成する工程と、

第2導電型のドーパントを、前記保護層を通じて前記半導体基板内に導入して、前記半導体基板との接合を画定する接合層を形成する工程と、

第1導電層を前記接合層にわたって形成する工程と、

前記半導体基板の前記第1表面とは反対側である前記半導体基板の第2表面上に第2導電層を形成する工程と、を含み、

前記ドーパントは、イオン注入により前記半導体基板内に導入され、

前記保護層は、導電材料を含む、方法。

## 【請求項 2】

前記保護層は、ポリシリコンを含む、請求項1に記載の方法。

## 【請求項 3】

前記第2導電型の前記ドーパントを導入する工程の後に、前記保護層を取り除く工程を更に含む、請求項1に記載の方法。

## 【請求項 4】

前記半導体基板内に注入された前記ドーパントを、昇温して拡散する工程を更に含む、

10

20

請求項 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

ツェナーダイオードは 2 端子電子デバイスであり、これは順バイアスされると従来のダイオードとして働く（すなわち、一方向性導電性）が、特定の閾値の電圧を超えて逆バイアスされると、逆方向に導電する。用語「ツェナーダイオード」は、通常、例えばその接合が、約 5 V 超の逆バイアス電位でアバランシェ降伏を引き起こす従来の半導体材料（例えば、Si）で形成された p - n 接合からなるデバイスに適用され、このようなデバイスは、電圧調整、及び回路保護の回路で使用され得る。

10

【背景技術】

【0002】

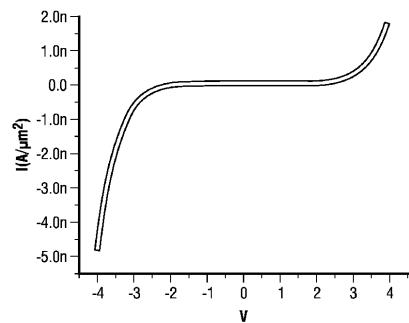

理想的なツェナーダイオードの電流 (I) 対電圧 (V) のプロットは図 1 に示されており、この図から、例えば、Si ベースのデバイスに対して一般的には 5 V を超える特定の電圧、すなわちツェナーダイオードの閾値電圧を超えて逆バイアスされると、突然の逆電流の上昇が生じることが明らかである。このように、順バイアスされると、ツェナーダイオードは通常の整流器として機能するが、逆バイアスされると、その I - V プロットにおいて膝状、又は鋭角の降伏を呈する。ツェナーダイオードの特徴は、一度、導電が逆バイアス下で生じると、デバイスにかかる電圧が、最大許容散逸率まで、逆電流の更なる増加に際し本質的に一定のままであることである。この特徴的な挙動ゆえに、ツェナーダイオードは、とりわけ、電圧レギュレータ、電圧リファレンス、及び過電圧保護器としての実用性を見出す。

20

【0003】

サージ事象中、デバイスにわたる電圧降下を最小値に制限することが望ましい。したがって、ツェナーダイオードの重要な特性は、その逆サージ能力である。

【発明の概要】

【課題を解決するための手段】

【0004】

本発明の 1 つの態様では、ツェナーダイオードなどの半導体デバイスが提供される。半導体デバイスは、第 1 導電型の第 1 半導体材料と、第 2 半導体材料及び第 2 半導体材料との間に接合を形成するように第 1 半導体材料と接触している、第 2 導電型の第 2 半導体材料と、を含む。第 1 酸化物層は、第 2 半導体材料の残りの部分が露出されるように、第 2 半導体材料の一部分にわたって、配設される。ポリシリコン層は、第 2 半導体材料の露出された部分上に、及び、第 1 酸化物層の一部分上に配設される。第 1 導電層は、ポリシリコン層上に配設される。第 2 導電層は、第 2 半導体材料と接触している第 1 半導体材料の表面と反対側である第 1 半導体材料の表面上に配設される。

30

【0005】

本発明の別の態様によると、半導体デバイスを製造する方法が提供される。方法は、第 1 酸化物層を、半導体基板の残りの部分が露出されるように、第 1 導電型を有する第 1 半導体基板から形成された半導体基板の一部分にわたって形成することを含む。保護層は、半導体基板の第 1 表面上、及び第 1 酸化物層上に形成される。第 2 導電型のドーパントは、保護層を通じて半導体基板内に導入され、半導体基板との接合を画定する接合層を形成する。第 1 導電層は、接合層にわたって形成される。第 2 導電層は、半導体基板の第 1 表面と反対側の半導体基板の第 2 表面上に形成される。

40

【図面の簡単な説明】

【0006】

【図 1】理想的なツェナーダイオードの電流 (I) 対電圧 (V) のプロットを示す。

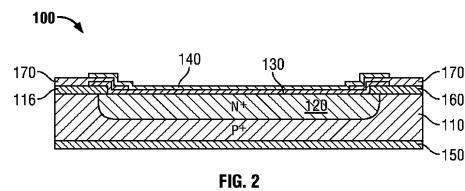

【図 2】改善された逆サージ能力及び削減されたリーク電流を有するツェナーダイオードの一例を示す。

【図 3】図 2 に示されたツェナーダイオードを製造するために使用され得る一連のプロセ

50

ステップの一例を示す。

【図4】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。

【図5】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。

【図6】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。

【図7】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。

【図8】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。 10

【図9】図2に示されたツェナーダイオードを製造するために使用され得る一連のプロセスステップの一例を示す。

【発明を実施するための形態】

【0007】

以下に詳細に説明するように、ツェナーダイオードは、改善された逆サージ能力及び削減されたリーク電流を有するように提供される。この改善は、1つの例示的ツェナーダイオードの設計について記載されるが、本明細書に記載の方法及び技術は、様々なツェナーダイオードの構成、並びに他の種類の過渡電圧サプレッサに同じように適用可能である。

【0008】 20

図2は、改善された逆サージ能力を有するツェナーダイオードの一例を示す。示されるように、ツェナーダイオード100は、この例では、P型ドーパントである、第1導電型のドーパントを高濃度でドープされた半導体基板110を含む。第2導電型の接合層120は、基板110内に形成される。この例では、接合層120はN+型の導電性を有する。P-N接合は、半導体基板110と接合層120との間の界面に配置される。ポリシリコン層130は、接合層上に配設される。電極として働く第1導電材料140は、ポリシリコン層130上に配設される。同様に、これも電極として働く第2導電材料150は、基板110の裏面上に配設される。ツェナーダイオード100はまた、基板110上に配設され、接合層120を形成するために使用されるフォトリソグラフィプロセスの一部として形成されエッチングされる第1酸化物層160を含む。加えて、低温酸化物(LTO)などの第2酸化物層170は、その第1部分が第1酸化物層160上に配設され、その第2部分がポリシリコン層130と第1導電材料140の間に介在される。第2酸化物層170は、第1導電材料140を形成するために使用されるフォトリソグラフィプロセスの一部として形成されエッチングされる。 30

【0009】

図2に示されるツェナーダイオードの製造プロセス中、ポリシリコン層130は、有利なことに、接合層120の前に形成される。その後、注入又は他のドーピングプロセスが使用され、ドーパントがポリシリコン層130上に堆積される。続いて熱処理プロセスが適用され、ドーパントがポリシリコン層130を通して基板110内に移動される。このような方法でのポリシリコン層130の使用は、ツェナーダイオードの逆サージ能力及びリーク電流の両方を改善することがわかっている。 40

【0010】

動作のいかなる理論にも束縛されずに、ポリシリコン層は、接合層120を形成するために使用されるドーピングプロセスによって生じる欠陥を減らすと考えられている。ドーパントが注入などによって基板110に直接的に導入される場合、欠陥は典型的には、基板内の特定の深さまで生じる。これらの欠陥は、得られるデバイスの逆サージ能力及びリーク電流に悪影響を与える。しかしながら、ドーパントをポリシリコン層上に及びポリシリコン層を通して導入することにより、基板内の欠陥は低減され得る。

【0011】

図2に示されたツェナーダイオードを製造するために使用され得るプロセスの一例が、

10

20

30

40

50

図3～9と関連して以下に説明される。

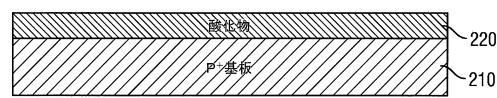

#### 【0012】

図3は、半導体基板及び酸化物層の断面図である。1つの実施形態では、基板210は、約 $1 \times 10^{-3}$ ・cmから約 $5 \times 10^{-3}$ ・cmの範囲内の抵抗率を有する低抵抗率のP<sup>+</sup>型<111>方向単結晶シリコンである。このシリコン結晶格子方向は、任意選択的に、<100>であり得る。別の実施形態では、基板210は、ガリウムヒ素などの他の種類の半導体材料からなる。更に、N型基板はまた、製造プロセスに対応する調整と共に使用され得ることが理解される。1つの実施形態では、P<sup>+</sup>型シリコン基板は、ボロンによってドープされる。もちろん、他のドーパントもまた、代替例において使用され得ることが理解される。

10

#### 【0013】

次に、酸化物層220が形成される。1つの実施形態では、酸化物層220は、ウエハを約1000の環境に約200分間、及び約1200で更に200分間、暴露することにより作製され得る。この時間の間、加熱された半導体材料は、窒素ガスと酸素ガスとの混合物に暴露される。1つの実施形態では、約1400～約1800の厚さの二酸化ケイ素層が、構造体の表面上に成長させられる。酸化物層を形成するための他のプロセスが、本発明に関連して使用され得ることが理解される。更に、酸化物層は、異なる厚さであり得る。

#### 【0014】

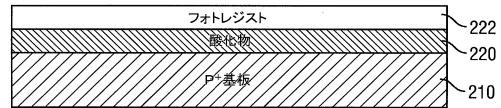

次に、フォトリソグラフィステップが、酸化物層内に開口部を作るために実行される。まず、図4に示されるように、フォトレジスト材料222が、酸化物層220の表面に適用される。1つの実施形態では、フォトレジストが約1.3μmの厚さで適用される。フォトレジスト材料222は、パターンマスクを通して光に露光され、次にフォトレジスト材料の露光された部分は、酸化物層の表面から取り除かれる。1つの実施形態では、酸化物は、フォトレジストに転写されたパターンの詳細に従って、反応性イオンエッチング(「RIE」)技術を使用して構造体の表面からエッチングされる。他の酸化物エッチングプロセスもまた、反応性イオンエッチングプロセスの代替例として使用され得ることが理解される。フォトレジスト被覆領域の下の酸化物領域は、このエッチングプロセスでは取り除かれない。

20

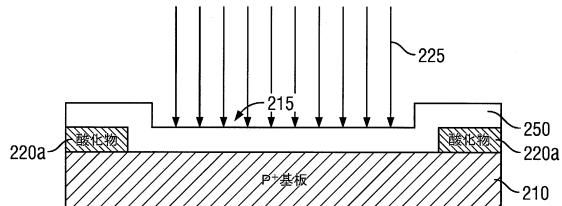

#### 【0015】

図5に示されるように、酸化物層220の中央部分は、ウィンドウ215を形成するように上記のようにエッチングされる。区域220aは、エッチングされなかった酸化物層220の部分に対応する。1つの実施形態では、残りのフォトレジストは、次のステップの前に、フォトレジスト剥離溶液を用いてウエハから取り除かれる。次に非ドープであり得るポリシリコンが、基板210にわたって、及び酸化物層220aの少なくとも一部分にわたって堆積されてポリシリコン層250を形成する。一部の実施形態では、ポリシリコン層250は、1から4μmの厚さを有してもよい。

30

#### 【0016】

次にイオン注入プロセスが、実行される。エッチングされなかった残りの酸化物は、ハードマスクを形成し、イオンが基板210に入らないようにイオンがそこを通るのを防止する。一部の場合は、約1.3μm厚さの残りのフォトレジスト材料は、イオン注入処理の後までウエハ上に残され得、酸化物が露光されたウィンドウを除く領域のイオンを吸収するのを助ける。

40

#### 【0017】

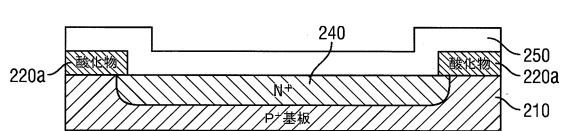

図5において、イオン注入プロセスは、矢印225によって示される。矢印225は、ポリシリコン層250上に導入されるリン又はヒ素などのN<sup>+</sup>型ドーパントを表す。1つの実施形態では、N<sup>+</sup>型ドーパントは、140keVのエネルギーで $1.72 \times 10^{13}$ イオン/cm<sup>2</sup>の照射量のリンのイオン注入を使用して導入され、約1μmの深さの層を形成する。代替的な実施形態では、かなり低いエネルギーがイオン注入プロセスにおいて使用され得る。その後、拡散ステップが、注入されたイオンを更に基板210内へ移動さ

50

するために、昇温して実行され、これにより、図6に示されるようにN+型接合層240が形成される。

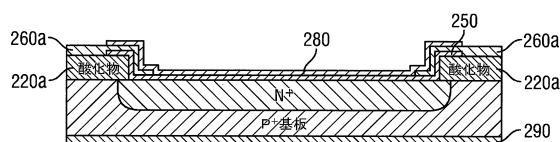

#### 【0018】

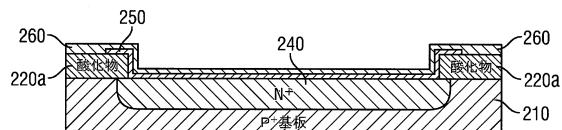

図7に示されるように、酸化物層260は、ポリシリコン層250にわたって形成される。一部の実施形態では、酸化物層260は、低温酸化物(LTO)層260である。

#### 【0019】

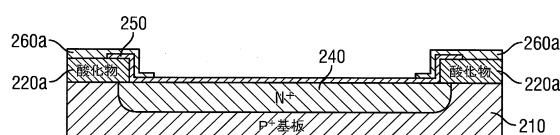

図8は、任意のパッシベーション層(図示せず)及び導電材料を堆積させるために、開口部を形成するための上記のフォトリソグラフィ技術を使用したエッチング後のLTO層260の区域260aを図示する。図9に図示される導電材料280は、例えば、銀などの好適な金属であり得る。導電材料280は、LTO層260内の開口部によって露出された、ポリシリコン層250の部分にわたって形成される。導電材料280はまた、LTO層260の区域260aにわたって形成される。

#### 【0020】

逆サージ能力及びリーク電流における改善が達成され得ることを明らかにするために、一連のツェナーダイオードが、異なる厚さのポリシリコン層を使用して製造された。一連の5Vダイオード、及び一連の7Vダイオードに関する結果が、表1に示される。それぞれの一連のダイオードについて3つのサンプルが製造され、1つは比較例としてポリシリコンを有さず、1つは厚さ1μmのポリシリコン層を有し、及び1つは厚さ2μmのポリシリコン層を有する。最小、平均、最大逆サージ能力及びリーク電流が、各デバイスについて計測された。表1が示すように、逆サージ能力は、ポリシリコン厚さが増加すると増加する。同様に、リーク電流は、ポリシリコン厚さが増加すると、減少し、これにより、デバイス構造が完成する。

#### 【0021】

#### 【表1】

表1

| サンプル番号 | 電圧<br>(Vwm) | ポリシリコンの<br>厚さ(μm)設計 | サージ10×1000(ワット) |     |     | Ir @ Vwm(μA) |      |      |

|--------|-------------|---------------------|-----------------|-----|-----|--------------|------|------|

|        |             |                     | 最小              | 平均  | 最大  | 最小           | 平均   | 最大   |

| 1      | 5V          | 無し                  | 548             | 615 | 696 | 26.0         | 38.5 | 81.7 |

| 2      | 5V          | 1 μm                | 601             | 661 | 726 | 18.0         | 19.8 | 22.3 |

| 3      | 5V          | 2 μm                | 666             | 698 | 710 | 2.7          | 3.2  | 3.7  |

| 4      | 7V          | 無し                  | 441             | 565 | 657 | 3.5          | 3.7  | 5.6  |

| 5      | 7V          | 1 μm                | 521             | 611 | 704 | 2.7          | 3.2  | 3.8  |

| 6      | 7V          | 2 μm                | 618             | 668 | 711 | 2.7          | 3.1  | 3.7  |

10

20

30

40

#### 【0022】

2μm超の厚さのポリシリコン層を有するツェナーダイオードもまた製造された。これらのデバイスに関して、逆サージ能力は、ポリシリコンの厚さが2μmを超えて増加すると減少するということがわかった。これは、ポリシリコン層に起因する低い熱放散によるものと推察される。したがって、少ない接合欠陥及び低い熱放散のトレードオフは、5及び7Vのツェナーダイオードに対して約1から2μmが最適なポリシリコン厚さになる。

#### 【0023】

しかしながら、これらの同じデバイスに関して、リーク電流は、ポリシリコン層厚さが、サンプルのテストの厚さ限度である4μmまで増加するにつれ、減り続けた。4μm厚

50

さのポリシリコン層を有するデバイスに関するリーク電流は、比較サンプルのリーク電流の10分の1未満まで減少した。したがって、一部の低電圧ダイオードの実施形態に関して、1から4μm厚さのポリシリコン層、及びより具体的には、1から2μm厚さの層は、逆サージ能力において十分な増加、並びにリーク電流における減少を提供し得る。

## 【0024】

当業者は、上記から、逆サージ能力を改善するポリシリコン層の使用は、異なる構成及び組成を有するデバイスに適用可能であることを認識するであろう。更に、上記とは異なる製造技術が、デバイスを製造するために使用され得る。例えば、1つの代替の実施形態では、P-N接合を形成する1対の半導体層として半導体基板を使用する代わりに、P-N接合を画定する両層を、イオン注入などによって半導体基板内に形成してもよい。

10

## 【0025】

他の実施形態では、ドーパントがそこを通って導入されて接合層が形成される層を形成するために、ポリシリコン以外の材料が使用されてもよい。ドーピングプロセス中に起こる損傷から基板表面を保護する保護層として働き得る任意の適当な材料が、ドーパント拡散のための障壁を形成せずに使用され得る。電気的に導電するポリシリコンなどの材料を使用する利点は、ドーピングプロセスが完了した後、それらを取り除く必要がないということである。例えば、酸化物層は、ポリシリコン層の代わりに使用されてもよいが、酸化物層は、電気的導電材料ではないので、構造体がドーピングされた後、取り除かれる必要がある。

## 【0026】

20

本発明の例示的な実施形態及び特定の用途が、図示され説明されてきたが、本明細書に開示された発明の概念から逸脱することなく、本発明の他の多くの変形及び適用が可能であることは明らかである。したがって、添付の請求項の範囲内において、本発明は、具体的に詳述されたもの以外も実行され得、本発明は、添付の特許請求の範囲の精神を除いて限定されるべきではないことが理解される。本発明の特徴のいくつかは、従属請求項に記載され得るが、各特徴は独立して使用される場合、利点を有し得る。

## 【符号の説明】

## 【0027】

- 100 ツエナーダイオード

- 110 半導体基板

- 120 接合層

- 130 ポリシリコン層

- 140 第1導電材料

- 150 第2導電材料

- 160 第1酸化物層

- 170 第2酸化物層

- 210 基板

- 220 酸化物層

- 220a 区域

- 222 フォトレジスト材料

- 250 ポリシリコン層

- 260 酸化物層

- 280 導電材料

30

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 シー - クアン・チェン

台湾・台北市・シティ・フワン - ヘ・イースト・ロード・セクション・4・ナンバー・10・1

7エフ

(72)発明者 ワン - ラン・チアン

台湾・台北市・シティ・ミンチュアン・イースト・ロード・セクション・6・ナンバー・119

・9エフ・3

(72)発明者 イー - イン・リン

台湾・台北市・シティ・ルイ - アン・ストリート・レーン・222・46・1・エフ

(72)発明者 ミン - タイ・チアン

台湾・台北市・シティ・ユン - ヘ・シティ・アンレ・ロード・ナンバー・306・2エフ・8

(72)発明者 チー - ピン・ペン

台湾・台北市・シティ・チュンシャオ・イースト・ロード・セクション・3・レーン・251・

アレー・7・ナンバー・4・3・4エフ

審査官 杉山 芳弘

(56)参考文献 米国特許出願公開第2010/0244194(US, A1)

特開平08-064843(JP, A)

特開2010-199165(JP, A)

特開平01-081265(JP, A)

実開平04-137042(JP, U)

特開2006-179518(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 29/866

H01L 29/868

H01L 21/329